(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-326866

(P2005-326866A)

(43) 公開日 平成17年11月24日(2005.11.24)

| (51) Int.Cl. <sup>7</sup> | F 1        | テマコード (参考) |

|---------------------------|------------|------------|

| <b>G09F 9/30</b>          | G09F 9/30  | 338 3K007  |

| <b>H05B 33/02</b>         | G09F 9/30  | 365Z 5C094 |

| <b>H05B 33/10</b>         | H05B 33/02 |            |

| <b>H05B 33/14</b>         | H05B 33/10 |            |

|                           | H05B 33/14 | A          |

審査請求 未請求 請求項の数 9 O L (全 14 頁)

|            |                              |          |                                               |

|------------|------------------------------|----------|-----------------------------------------------|

| (21) 出願番号  | 特願2005-168024 (P2005-168024) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日   | 平成17年6月8日(2005.6.8)          | (74) 代理人 | 100079108<br>弁理士 稲葉 良幸                        |

| (62) 分割の表示 | 特願平11-167555の分割              | (74) 代理人 | 100080953<br>弁理士 田中 克郎                        |

| 原出願日       | 平成11年6月14日(1999.6.14)        | (74) 代理人 | 100093861<br>弁理士 大賀 真司                        |

|            |                              | (72) 発明者 | 木村 瞳<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内         |

|            |                              | (72) 発明者 | 前田 浩<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内         |

最終頁に続く

(54) 【発明の名称】表示装置、回路基板、回路基板の製造方法

## (57) 【要約】

【課題】 画素間および画面全体の輝度ムラを生じない表示装置の回路配置や製造方法を提供する。

【解決手段】 電界発光層の電源となる給電配線203と電界発光層に電流を供給するための画素電極205との間に薄膜トランジスタ12を備える。薄膜トランジスタ12は、ゲート電極202が長手に形成されている。また、画素電極205と接続するための第1のコンタクトホール303が長手に形成され、給電配線203と接続するための第2のコンタクトホール304が長手に形成されている。これらゲート電極202とコンタクトホール303および304は、長手方向が平行になっており、キャリアの流れる方向と長手方向と直角をなしている。このため引出配線無しで最短距離で均一に電流を電界発光素子10に供給可能になっている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

電流が供給されることによって発光する電界発光層を備える表示装置において、発光層の電源となる配線と発光層に電流を供給するための画素電極との間に能動素子を備え、前記能動素子と前記画素電極とを接続する第1のコンタクトホールが長手に形成されていることを特徴とする表示装置。

**【請求項 2】**

電流が供給されることによって発光する発光層を備える表示装置において、発光層の電源となる配線と発光層に電流を供給するための画素電極との間に能動素子を備え、前記能動素子と前記配線とを接続する第2のコンタクトホールが長手に形成されていることを特徴とする表示装置。10

**【請求項 3】**

前記能動素子は、長手に形成されたゲート電極を備えていることを特徴とする請求項1または請求項2のいずれか一項に記載の表示装置。

**【請求項 4】**

前記第1のコンタクトホールにおける長手方向、前記ゲート電極における長手方向または前記第2のコンタクトホールにおける長手方向のうちいずれか二以上が平行に形成されている請求項3に記載の電界発光表示装置。

**【請求項 5】**

複数の導電体層が絶縁層を介して積層されている回路基板であって、第1の導電体層によって形成されている第1の配線パターンとは異なる第2の導電体層によって、当該第1の配線パターンに沿った第2の配線パターンが形成されており、前記第1の配線パターンと前記第2の配線パターンとが少なくとも一部でコンタクトホールにより電気的に接続されていることを特徴とする回路基板。20

**【請求項 6】**

前記第1の導電体層または第2の導電体層のいずれか一方は、複数の導電体層のうち最も抵抗率の低い材料で形成された導電体層である請求項5に記載の回路基板。

**【請求項 7】**

請求項5に記載の回路基板における配線パターンを、発光層に電源を供給するための電源配線に適用することを特徴とする表示装置。30

**【請求項 8】**

エネルギーを供給することによって半導体を結晶化させる工程を備える回路基板の製造方法において、線状にエネルギーを供給して半導体層を結晶化させる場合に、当該半導体層においてキャリアが流れる方向と略平行な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させることを特徴とする回路基板の製造方法。

**【請求項 9】**

エネルギーを供給することによって半導体を結晶化させる工程を備える回路基板の製造方法において、線状にエネルギーを供給して半導体層を結晶化させる場合に、当該半導体層に形成するゲート電極における長手方向と略直角な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させることを特徴とする回路基板の製造方法。40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、いわゆる電界発光（以下「EL」（Electro-Luminescence）という。）素子を備えた表示装置に係り、特にEL素子を駆動する駆動回路の配置や製造方法の改良に関する。

**【背景技術】****【0002】**

EL素子を用いた表示装置における基板配置に関する公知技術としては、本願出願人の発明に係る特開平11-24604号公報に記載されるようなものがあった。このような回路では、回路の寄生容量を下げることができていた。

### 【0003】

EL素子を駆動するための能動素子に関しては、論文 "High Resolution Light Emitting Polymer Display Driven by Low Temperature Polysilicon Thin Film Transistor with Integrated Driver", Asia Display 98, pp217-220, に記載されているように、ポリシリコンを利用した薄膜トランジスタが適している。これらEL素子と薄膜トランジスタとの組み合わせを用いることにより、軽量化、薄形化、低消費電力化、広い視角および高速応答が可能になっていた。

【非特許文献1】 "High Resolution Light Emitting Polymer Display Driven by Low Temperature Polysilicon Thin Film Transistor with Integrated Driver", Asia Display 98, pp217-220

### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0004】

しかしながら、上記公知技術を利用した表示装置であっても画素間における明るさの斑(ムラ)、画面全体の輝度傾斜、筋上の斑などが生じるという問題点があった。

### 【0005】

画素間における明るさの斑は、EL素子は電流駆動形であるため、能動素子であるTFトを介してEL薄膜に流れる電流量に差が生じ、電流量の差がそのまま輝度の差に繋がることが原因であった。

### 【0006】

画面全体の輝度傾斜は、駆動回路から各EL素子に対して電圧降下が生じ、駆動回路から遠いEL素子である程暗くなることが原因であった。

### 【0007】

筋状の斑は、給電配線ごとにその電圧降下が異なることが原因であった。

#### 【課題を解決するための手段】

### 【0008】

この問題点に鑑み、本発明の第1の課題は、画素間の輝度斑を排除可能な回路配置を提供することにより、画素間において均一な明るさが得られる表示装置を提供することである。

### 【0009】

本発明の第2の課題は、給電配線における電圧降下を防止可能な回路配置を提供することにより、表示装置においては画面全体において均一な明るさが得られ、筋状の斑などが発生しない回路基板を提供することである。

### 【0010】

本発明の第3の課題は、画素間の輝度斑を防止するのに適する結晶化方法を提供することにより、電界発光素子においては画素間において均一な明るさが得られるような回路基板の製造方法を提供することである。

### 【0011】

本発明の第1の課題を解決する発明は、電流が供給されることによって発光する発光層を備える表示装置において、発光層の電源となる配線と発光層に電流を供給するための画素電極との間に能動素子を備え、能動素子と画素電極とを接続する第1のコンタクトホールが長手に形成されていることを特徴とする表示装置である。

### 【0012】

本発明の他の態様は、電流が供給されることによって発光する発光層を備える表示装置において、発光層の電源となる配線と発光層に電流を供給するための画素電極との間に能動素子を備え、能動素子と配線とを接続する第2のコンタクトホールが長手に形成されていることを特徴とする表示装置である。

10

20

30

40

50

**【 0 0 1 3 】**

上記能動素子は、長手に形成されたゲート電極を備えていることを特徴とする。

**【 0 0 1 4 】**

上記能動素子において、第1のコンタクトホールにおける長手方向、ゲート電極における長手方向または第2のコンタクトホールにおける長手方向のうちいずれか二以上が平行に形成されている。

**【 0 0 1 5 】**

本発明の第2の課題を解決する発明は、複数の導電体層が絶縁層を介して積層されている回路基板であって、第1の導電体層によって形成されている第1の配線パターンとは異なる第2の導電体層によって、当該第1の配線パターンに沿った第2の配線パターンが形成されており、第1の配線パターンと第2の配線パターンとが少なくとも一部でコンタクトホールにより電気的に接続されていることを特徴とする回路基板である。

10

**【 0 0 1 6 】**

ここで、上記第1の導電体層または第2の導電体層のいずれか一方は、複数の導電体層のうち最も抵抗率の低い材料で形成された導電体層である。

**【 0 0 1 7 】**

本発明は、例えば、上記回路基板における配線パターンを、発光層に電源を供給するための電源配線に適用したことを特徴とする表示装置である。

**【 0 0 1 8 】**

本発明の第3の課題を解決する発明は、エネルギーを供給することによって半導体を結晶化させる工程を備える回路基板の製造方法において、線状にエネルギーを供給して半導体層を結晶化させる場合に、当該半導体層においてキャリアが流れる方向と略平行な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させることを特徴とする回路基板の製造方法である。

20

**【 0 0 1 9 】**

本発明の他の態様は、エネルギーを供給することによって半導体を結晶化させる工程を備える回路基板の製造方法において、線状にエネルギーを供給して半導体層を結晶化させる場合に、当該半導体層に形成するゲート電極における長手方向と略直角な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させることを特徴とする回路基板の製造方法である。

30

**【 発明の効果 】****【 0 0 2 0 】**

第1の課題を解決する発明によれば、画素間の輝度斑を排除可能な回路配置を備えたので、画素間に均一な明るさが得られる表示装置を提供することが可能である。

**【 0 0 2 1 】**

第2の課題を解決する発明によれば、給電配線における電圧降下を防止可能な回路配置を備えたので、電界発光素子を用いた表示装置においては画面全体において均一な明るさが得られ、筋状の斑が発生しない回路基板を提供することが可能である。

**【 0 0 2 2 】**

第3の課題を解決する発明によれば、画素間の輝度斑を防止するのに適する結晶化方法を備えたので、電界発光素子においては画素間に均一な明るさが得られるような回路基板の製造方法を提供することが可能である。

40

**【 発明を実施するための最良の形態 】****【 0 0 2 3 】**

次に本発明の好適な実施の形態を、図面を参照して説明する。

**( 実施形態 1 )**

本発明の実施形態1は、画素間の輝度斑を解消可能な表示装置の回路配置に関する。

**【 0 0 2 4 】**

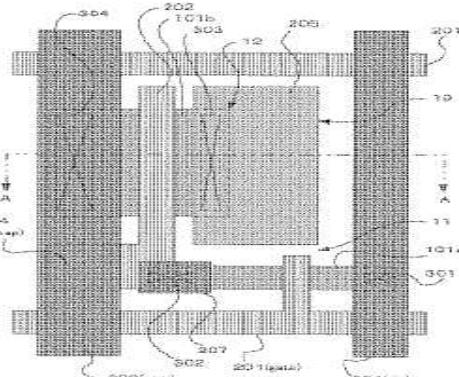

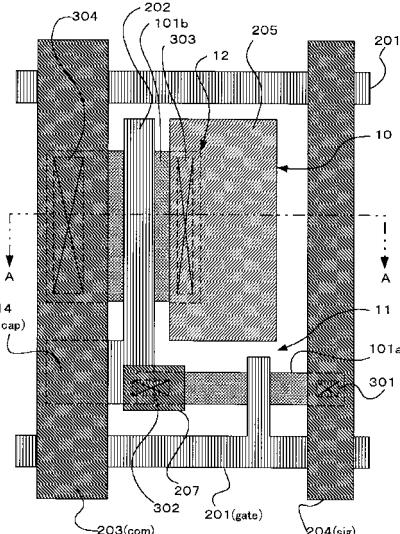

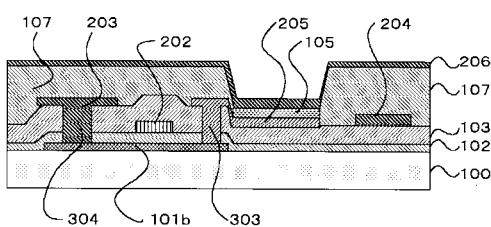

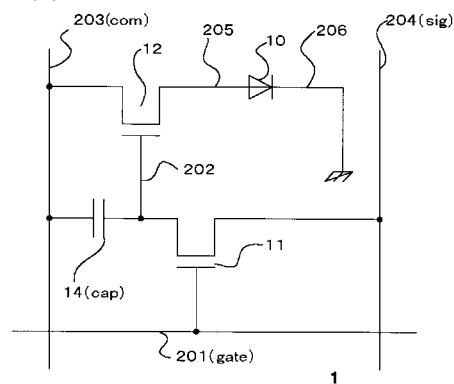

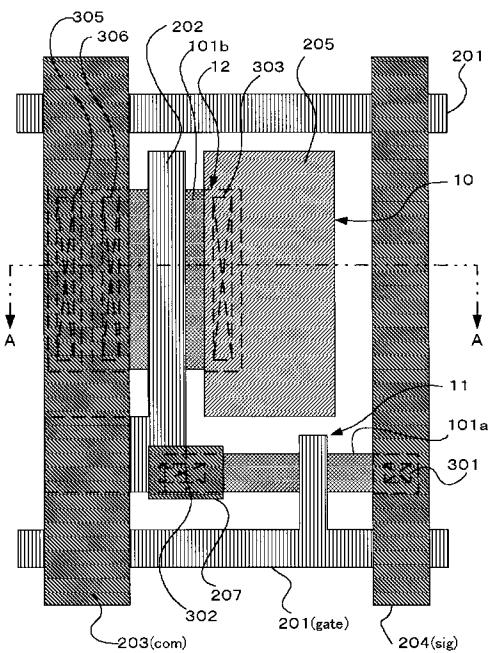

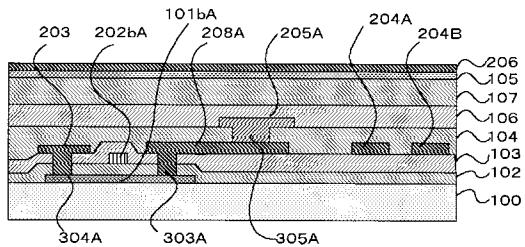

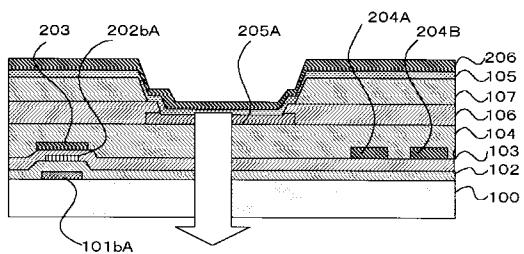

図1に本実施形態の表示装置における画素構造の平面図、図2に図1におけるA-A切断面の断面図を示す。これらの図は一つの画素領域について拡大して示したものである

50

。図1は、配線層上の層構造を削除して示している。

【0025】

表示装置は、図1に示すように、画素領域1ごとに、電界発光素子10、制御トランジスタ11および駆動トランジスタ12が形成されて構成される。

【0026】

制御トランジスタ11および駆動トランジスタ12は、薄膜トランジスタ(TFT)としての構造を備えている。

【0027】

制御トランジスタ11において、第1の半導体層101aのソース側はコンタクトホール301を介して信号配線204(sig)に電気的に接続されている。第1の半導体層101aのドレイン側は、電極207が設けられ、1つのコンタクトホール302を介し、当該コンタクトホール302内で駆動トランジスタ12のゲート電極202に電気的に接続されている。10

【0028】

駆動トランジスタ12においては、図2に示すように、第2の半導体層101bのソース側は、コンタクトホール304を介して給電配線203(com)に電気的に接続されている。第2の半導体層101bのドレイン側は、コンタクトホール303を介して画素電極205に電気的に接続されている。

【0029】

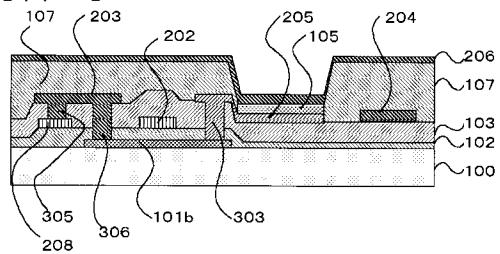

また駆動トランジスタ12部分では、図2に示すように、基板上に第2の半導体層101bが形成され、当該半導体層101b上にゲート絶縁膜102を介してゲート電極202が形成されている。ゲート絶縁膜102上には層間絶縁膜103が形成されている。第2の半導体層101bのドレイン側には、層間絶縁膜103上で、かつ、層間絶縁膜103に貫通されたコンタクトホール303を介して画素電極205が電気的に接続して設けられ、当該画素電極の領域に対応して電界発光素子が設けられる。電界発光素子10の断面構造は、図2に示すように、画素電極205上に発光層105および共通電極206が積層された構造となっている。特にインクジェット法等により画素電極205上に選択的に発光層105を形成することができる。発光層105には、後述するような電流で発光する有機発光材料を使用する。画素電極205を陽極、共通電極206を陰極として駆動させる場合、発光層105と画素電極205間に必要に応じて正孔注入層を、発光層105と画素電極205間に電子輸送層を設けてもよい。層間絶縁膜上の画素電極の領域以外の駆動トランジスタに対応する領域に、画素を区画するバンク層107を設ける。2030

【0030】

上記の構造の他に、図9で後述するように、半導体層101bのドレイン側にドレイン電極を、層間絶縁膜103上に第2の層間絶縁膜(104)を、当該第2の層間絶縁膜(104)上に画素電極205を各々設け、当該第2の層間絶縁膜(104)に設けたコンタクトホール305Aを介して画素電極205とドレイン電極とを電気的に接続し、当該画素電極領域において発光層105を形成し、第2の層間絶縁膜(104)上の画素電極の領域以外の駆動トランジスタに対応する領域にバンク層(107)を設けることもできる。40

【0031】

本実施形態では、特に、能動素子である駆動トランジスタ12と画素電極205とを接続する第1のコンタクトホール303が長手に形成されている点、駆動トランジスタ12と給電配線203とを接続する第2のコンタクトホール304が長手に形成されている点、および駆動トランジスタ12が長手に形成されたゲート電極を備えている点に特徴を有する。第1のコンタクトホール304における長手方向、ゲート電極202における長手方向および第2のコンタクトホール303における長手方向が、互いに実質的に平行に形成されている点にも特徴がある。

【0032】

材料に関し、透明基板100は、光透過性があり、一定の機械的強度を有するガラス、50

石英などが使用される。第1および第2の半導体層101a, bは、例えば実施形態3で説明するように、パターン化されたアモルファスシリコンにレーザ光を照射して重合化したポリシリコンで形成され、ソース・ドレインに不純物がドーピングされている。ゲート絶縁膜102、層間絶縁膜103、バンク層104は、酸化珪素、窒化珪素、ポリイミドなどの絶縁材料で形成されている。ゲート電極201, 202、給電配線203、信号配線204、電極層207としては、アルミニウム、タンタル、モリブデン、チタン、タンゲステン、銅などを使用可能である。ゲート電極201・202は、ゲート絶縁膜102上で同時にパターン形成が可能である。共通電極206には、電界発光素子における陰極としてアルミニウムまたはアルミニウムと他の元素(リチウムやカルシウムなど)の合金を使用可能である。画素電極205には、電界発光素子の陽極として、ITOなど光透過性と導電性を有する材料を使用可能である。発光層105には、低分子または高分子の有機発光材料が用いられる。有機発光材料としては公知技術の種々の材料を適用可能である。

10

20

30

40

50

### 【0033】

ここで給電配線203や信号配線204は、当該回路基板上に使用する金属層のうち最も抵抗率の小さい材料(例えばアルミニウム)の層で形成することが好ましい。給電配線や信号配線は、特に電界発光素子を用いた表示装置では多くの電流が流れるため、抵抗率が小さいほど電圧降下を少なくすることができるからである。電圧降下が少なければ、配線の末端にある画素領域にも所定の電圧が供給でき、駆動回路に近い画素領域と同様の明るさで電界発光素子を発光させることができるのである。

### 【0034】

図3に画素領域1における等価回路を示す。

### 【0035】

上記回路基板の配置により、制御トランジスタ11のソースが信号配線204、ゲートがゲート電極201(走査配線gate)、ドレインが駆動トランジスタ12のゲート電極202に接続されている。このゲート電極202の配線は、図1に示すように給電配線203と重なる延設部を備えることにより電位を保持するための保持容量14を形成している。駆動トランジスタ12のソースは給電配線203に接続され、ドレインは電界発光素子10のアノード(陽極)に接続されている。電界発光素子10のカソード(陰極)は共通電極206となり、一定の電位に接地されている。

### 【0036】

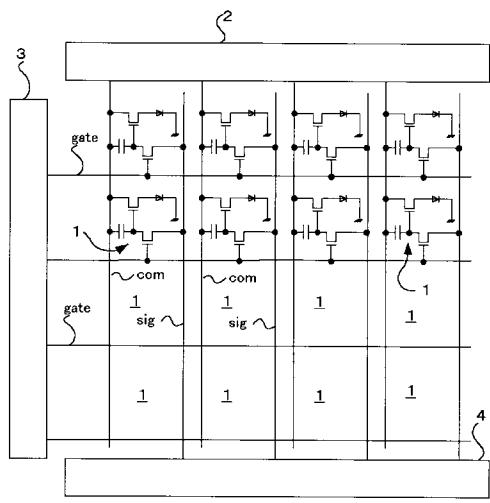

図4に上記画素領域1の集合である表示装置の全体回路図を示す。

### 【0037】

当該表示装置は、信号配線sigに信号側駆動回路2および検出回路4が接続され、画像信号を信号配線sigに供給するようになっている。給電配線comには、一定電圧に電流を供給可能に維持されている。走査配線gateには走査側駆動回路3が接続され、走査信号を走査配線gateに供給するようになっている。信号側駆動回路2および走査側駆動回路3は、N型のトランジスタとP型のトランジスタとで相補型トランジスタ回路が形成されている。相補型トランジスタによって、駆動回路として機能させるためのシフトレジスタ、レベルシフタ、アナログスイッチ、ラッピングなどの基本回路が構成されている。

### 【0038】

上記構成において、走査配線gateを介して走査信号が制御トランジスタ11のゲート電極201に供給されると、制御トランジスタ11がオン状態になり、信号配線sigを介して画像信号の電位がドレインに供給される。この電位は保持容量14において保持される。画像信号として画素を点灯させる電位が供給されると、駆動トランジスタ12がオン状態になり、ソースを介して画素電極205に電源電流が供給されるようになる。発光層105では、画素電極205から輸送された正孔と共に共通電極206から輸送された電子とが結合して電界発光現象を生じ発光する。発光層105からの光は透明電極である画素電極205を介して透明基板100より射出される。

**【 0 0 3 9 】**

このとき、駆動トランジスタ 1 2 のソースと給電電極 2 0 3 を直接コンタクトホールで接続したり、ドレインと画素電極 2 0 5 とを直接コンタクトホールで接続したりしてあるので、能動素子から配線までの引出配線が無く、給電配線 2 0 3 を介して最短距離で画素電極 2 0 5 に電流を供給できる。また第 1 コンタクトホール 3 0 4 や第 2 コンタクトホール 3 0 3 が長手に形成されているので、接触抵抗が少ない。このため電圧降下を最小限に押さえることができる。コンタクトホールはゲート電極や給電配線と長手方向が平行に形成されており、引出配線のための面積が不要なので、抵抗をさらに下げることが可能となり、面積効率がよい。すなわち画素間、さらには画素内における輝度斑を少なくし、明るい表示を可能にすることができます。

10

**【 0 0 4 0 】**

さらに引出配線による電力消費も無くすことができ、発熱を抑制できる。これらの作用により、表示装置としての画質を向上させることができる。

**(実施形態 2 )**

本発明の実施形態 2 は、画素間の輝度斑をさらに低減可能な電界発光素子を用いた表示装置の回路配置に関する。

**【 0 0 4 1 】**

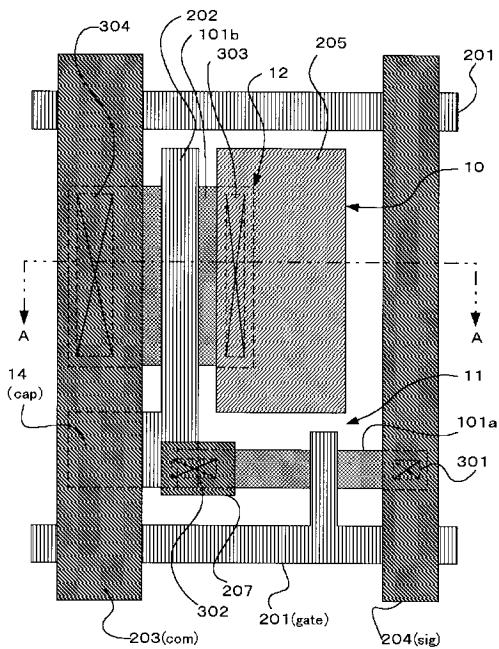

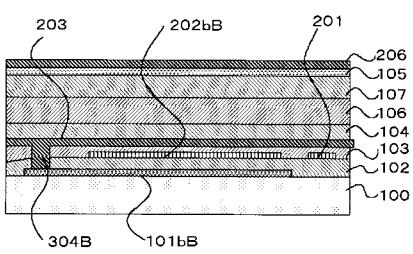

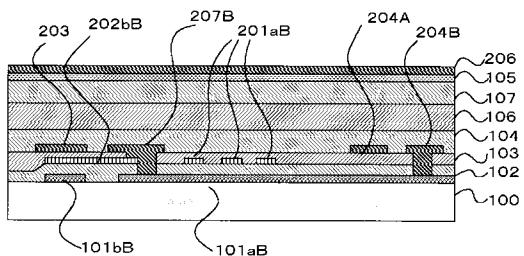

図 5 に本実施形態の表示装置における画素構造の平面図、図 6 に、図 5 における A - A 切断面の断面図を示す。これらの図は一つの画素領域について拡大して示したものである。図 5 は、配線層の上の層構造を削除して示している。

20

**【 0 0 4 2 】**

当該表示装置は、これらの図に示すように、ほぼ実施形態 1 と同様の回路配置および層構造を備えている。ただし、給電配線 2 0 3 と駆動トランジスタ 1 2 とのコンタクトホール部分の構成が異なる。他の構成は実施形態 1 と同様であるため同一の符号を付し、その説明を省略する。

**【 0 0 4 3 】**

駆動トランジスタ 1 2 は、図 5 に示すように、コンタクトホール 3 0 6 を介して給電配線 2 0 3 に電気的に接続されている。特に本実施形態では、第 1 の導電体層によって形成されている第 1 の配線パターンとは異なる第 2 の導電体層によって、当該第 1 の配線パターンに沿った第 2 の配線パターンが形成されており、第 1 の配線パターンと第 2 の配線パターンとが少なくとも一部でコンタクトホールにより電気的に接続されている点に特徴がある。具体的には、第 1 の導電体層はアルミニウムで形成された給電配線 2 0 3 であり、第 2 の導電体層は例えばタンタルなどで形成された電極層 2 0 8 である。電極層 2 0 8 は、薄膜トランジスタのゲート電極層 2 0 2 を形成する際に、全体に形成され、パターニングされた電極層である。つまり、上層に形成される給電配線 2 0 3 の部分と平行して、ゲート電極層 2 0 2 と同一の層がパターニングされたものである。コンタクトホール 3 0 5 により電極層 2 0 8 と給電配線 2 0 3 とが電気的に接続され、コンタクトホール 3 0 6 により給電配線 2 0 3 と第 2 の半導体層 1 0 1 b とが電気的に接続されている。

30

**【 0 0 4 4 】**

このような構成では、複数の導電体層が電気的に接続されることにより、結果的に配線パターンの断面積を大きくしていることになる。二つの導電体層を併せた低効率は両者の抵抗率の並列接続に等価なものとなり、いずれか単独で配線した場合より明らかに抵抗率が下がる。

40

**【 0 0 4 5 】**

したがって、このような回路配置および層構造を備えることによって、当該回路基板は配線における抵抗値を下げることができる。このため電界発光素子に多量の電流を流す場合でも給電配線の下流における電圧降下を最小限に押さえることができ、画素間の輝度斑を少なくすることができる。

**【 0 0 4 6 】**

また給電配線間の電圧降下の差を低減することにより、筋状の斑を抑制できる。

50

## 【0047】

このような作用効果は、その回路基板に形成されている複数の導電性層を配線のために相互に連結した回路配置を備えた回路基板で達成される。このような複数の導電体層を並行させる配線は、電流量の多いあらゆる配線に適用可能である。例え複数の導電体層を連結できる領域が断続的であっても、配線の長手方向における抵抗率を下げることができるため、効果的である。

## (実施形態3)

本発明の実施形態3は、上記実施形態のような能動素子に適する回路基板の製造方法に関する。

## 【0048】

本実施形態は、特に線状にエネルギーを供給して半導体層を結晶化させる工程において、当該半導体層に形成するゲート電極における長手方向と略直角な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させる点に特徴がある。

## 【0049】

以下、実施形態1に示した表示装置の製造工程においてこの特徴点について説明する。

## 【0050】

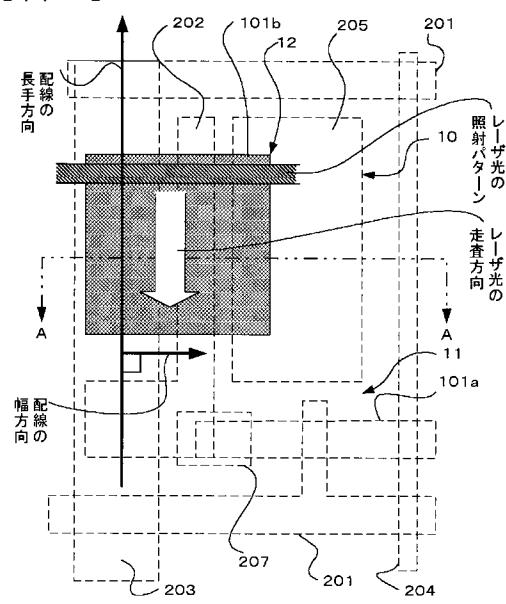

図7に本実施形態の回路基板の製造方法における特徴を説明する平面図を示す。

## 【0051】

まず、透明基板100に対してTEOS(テトラエトキシシラン)や酸素ガスなどを原料ガスとしてプラズマCVD法を適用し、約2000～5000オングストロームの下地保護層(図示せず)を形成する。次いで透明基板100の温度を一定に保持し、下地保護層上にプラズマCVD法を適用し、約100～1000オングストロームのアモルファスシリコン層101を形成する。この層は、薄膜トランジスタの半導体層を構成するものである。次いでこのアモルファスシリコン層101に線状エネルギーを供給する。例えはレーザアニール法では、例えは出力強度200mJ/cm<sup>2</sup>程度のエキシマレーザを線状に照射し、図7に示すような方向でアモルファスシリコン層上にレーザ光を照射していく。

## 【0052】

このとき、レーザ光の照射パターンの長手方向が配線の長手方向と直角、すなわち配線の幅方向に平行になるようにし、配線の長手方向にレーザ光を走査する点が重要である。言い換れば、当該アモルファスシリコン層においてキャリアが流れる方向と略平行な方向に当該線状に供給されるエネルギーの長手方向を一致させて当該半導体層全体を結晶化させるのである。

## 【0053】

レーザの出力強度がばらつくことは避けられないため、このような走査方向を探ることで、製造段階において結晶化が不十分なレーザ光の照射部が生じたとしても、他のレーザ光の照射部で補償され、寄生抵抗が均一化され動作不具合を発生する可能性を極めて低くすることができる。その結果として、画素間において均一な明るさで電界発光素子を発光させることができる。

## 【0054】

なお、キャリアの流れの方向と必ずしも平行でなくとも、レーザ光の照射パターンが薄膜トランジスタにおけるキャリアの流れを完全に分断しないように走査していくべき。線状の走査によりアモルファス状態のシリコンを結晶化させることができ方法であれば、レーザ光に限らず他のエネルギー供給手段を使用してもよい。

## 【0055】

なお、エネルギーが点状に供給されるレーザ光を用いることもできる。この場合には、レーザ光の照射点をキャリアの流れる方向に平行な方向に走査し、走査ラインを徐々に下げながら全体を走査する。そのとき上下の走査ラインが一部で重なるように走査する。すなわち、レーザの照射点におけるレーザ強度のピーク値の90%に相当する部分が走査ライン間で重なるようにして走査していく。

**【 0 0 5 6 】**

適正なレーザ光の照射により、アモルファス状態のシリコンが重合し、ポリシリコン層 105 が形成される。その後は公知技術を適用して表示素子としての層構造を形成していく。

**【 0 0 5 7 】**

まず半導体層 101a、b の形成後、ゲート酸化膜 102 を形成する。次いでアルミニウム、タンタル、モリブデン、チタン、タングステンなどの金属をスパッタ法等で蒸着し、ゲート電極 201、202 を形成し、パターニングを行う。この状態でイオンを打ち込んで自己整合的に駆動トランジスタ 12 や制御トランジスタ 11 にソース・ドレイン領域を形成する。層間絶縁膜 103 を酸化膜や窒化膜で形成してからコンタクトホールを形成し、配線 203、204、画素電極 205 をパターン形成する。バンク層 107 を形成した後、電界発光素子 10 を形成する画素領域のみバンク層を除去する。蒸着法、スパッタ法、スピンドルコートなどの塗布法、スキージ法、インクジェット法等を利用して画素領域に半導体材料を充填し発光層 105 を形成する。最後に共通電極 206 を全体的に形成して、回路配線を行えば表示装置が完成する。10

**( 実施例 )**

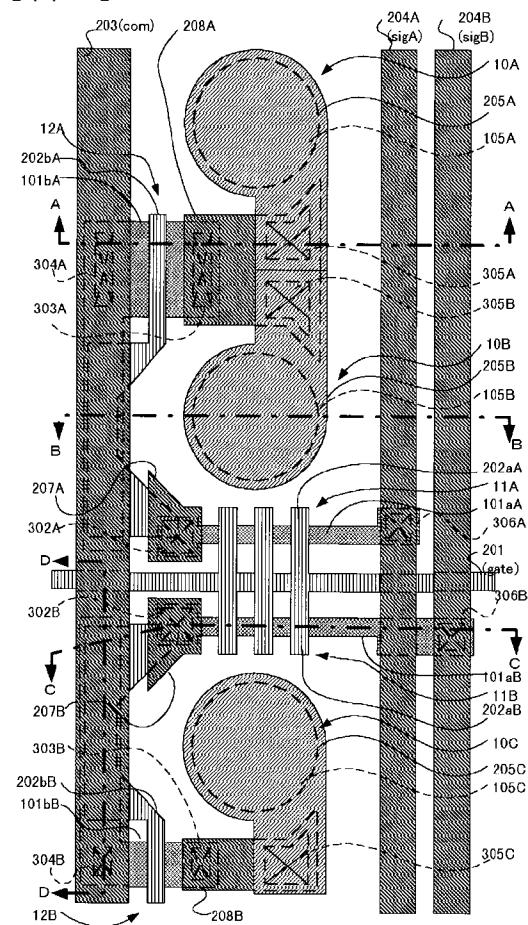

上記実施形態を実施して電界発光素子を用いた表示装置を製造した。図 8 に実施例の表示装置における一部の画素配置の平面図、図 9 にその AA 切断面の断面図、図 10 にその BB 切断面の断面図、図 11 に CC 切断面の断面図、図 12 にその DD 切断面の断面図を示す。実施形態 1 と同等な構成には、同様の符号を付してある。20

**【 0 0 5 8 】**

実施例の表示装置は、図 8 から判るように、3 つの発光素子 10A、10B および 10C で、一つの画素を表示するように構成されている。このように複数の発光素子で一つの画素を構成する技術は、輝度の階調を上げるために採用される。30

**【 0 0 5 9 】**

給電配線 203 (com)、一組の信号配線 204A (sig A) および B (sig B) 並びに走査配線 201 (gate) が各画素領域に配線されている。給電配線 203 の近傍には、駆動トランジスタ 12A と 12B とが設けられている。走査配線 201 は複数のゲート電極 202aA や 202aB がパターニングされ、制御トランジスタ 11A と 11B とが設けられている。30

**【 0 0 6 0 】**

制御トランジスタ 11A と駆動トランジスタ 12A とは発光素子 10A および 10B を駆動するものである。制御トランジスタ 11A は、第 1 の半導体層 101aA のソースがコンタクトホール 306A を介して信号配線 204A に電気的に接続されている。ドレインが 1 つのコンタクトホール 302A 内で電極層 207A を介して駆動トランジスタ 12A のゲート電極 202bA に接続されている。ゲート電極 202bA は給電配線 203 と重なる延設部が設けられており、保持容量を形成している。駆動トランジスタ 12A は、第 2 の半導体層 101bA のソースが給電配線 203 とコンタクトホール 304A で電気的に接続され、ドレインが電極層 208A とコンタクトホール 303A で電気的に接続されている。電極層 208A は、コンタクトホール 305A で発光素子 10A の画素電極 205A と、コンタクトホール 305B で発光素子 10B の画素電極 205B とそれぞれ電気的に接続されている。40

**【 0 0 6 1 】**

制御トランジスタ 11B と駆動トランジスタ 12B とは発光素子 10C を駆動するものである。制御トランジスタ 11B は、第 1 の半導体層 101aB のソースがコンタクトホール 306B を介して信号配線 204B に電気的に接続されている。ドレインが 1 つのコンタクトホール 302B 内で電極層 207B を介して駆動トランジスタ 12B のゲート電極 202bB に接続されている。ゲート電極 202bB は給電配線 203 と重なる延設部が設けられており、保持容量を形成している。駆動トランジスタ 12B は、第 2 の半導体層 101bB のソースが給電配線 203 とコンタクトホール 304B で電気的に接続され50

、ドレインが電極層 208B とコンタクトホール 303B で電気的に接続されている。電極層 208B は、コンタクトホール 305B で発光素子 10C の画素電極 205C と電気的に接続されている。

#### 【0062】

本実施例の層構造としては、図 9 乃至図 12 に示すように、ゲート絶縁膜 102 上に、走査配線 201 やゲート電極 202a や 202b を形成する電極層がパターニングされて設けられている。その上には、第 1 の層間絶縁膜 103 が設けられ、第 1 の層間絶縁膜 103 上に配線 203、204A、204B、208A、208B、204A、204B、電極層 207A、207B が設けられている。第 2 の層間絶縁膜 104 には、画素電極 205A、205B や画素間を区画するバンク層 106、107 が形成されている。画素電極 205A 上には発光層 105A が、画素電極 205B 上には発光層 105B が設けられている。なお、本実施例の表示装置は、例えば発光層 105A や 105B をスピンドルコートにより塗布することで、画素領域のみならずバンク上にも延設されている。10

#### 【0063】

上記構成において、発光素子 10A および 10B からなる組と発光素子 10C との発光の有無を制御することで、4 階調を表示可能になっている。すなわち、信号配線 204A および B に画像信号の輝度の階調に応じた電圧を供給することにより、どの発光素子を点灯させるかを制御するようになっている。駆動トランジスタ 12A および B のゲート電極 202bA、202bB、コンタクトホール 304A、303A、304B、303B は、実施形態で説明したような回路配置を備えている。このため画素間で輝度斑の無い表示が可能になっている。20

#### 【0064】

すなわち、本実施例では、実施形態と同様の作用効果が得られる他、電界発光領域が円形に形成されている点でも特徴がある。

#### (その他の変形例)

本発明は、上記実施形態に限定されることなく種々に変形して適用することが可能である。

#### 【0065】

例えば、実施形態 1 における上記駆動トランジスタにおいて説明したような、ゲート電極、コンタクトホール、配線などの回路配置は、比較的大きな電流を消費するあらゆる回路のための能動素子に適用可能である。30

#### 【0066】

同様に、実施形態 2 における複数の導電体層による配線は、電界発光素子を利用した表示装置に限ること無く、比較的大きな電流を消費する回路の配線に適用可能である。

#### 【0067】

実施形態 3 における回路基板の製造方法は、レーザアニールなどを行って半導体層を結晶化させるようなあらゆる製造の局面で適用可能である。すなわち半導体などにおけるキャリアの流れる方向を横切らないように、キャリアの流れに平行に線状エネルギーの長手方向を一致させて照射すれば、例え不十分なエネルギー照査の部分が生じても、素子自体が動作不良になることが少ないのである。40

#### 【図面の簡単な説明】

#### 【0068】

【図 1】実施形態 1 の表示装置の画素構造を説明する平面図。

【図 2】実施形態 1 の表示装置の画素構造を説明する断面図。

【図 3】画素の等価回路を説明する回路図。

【図 4】表示装置の全体回路を説明する回路図。

【図 5】実施形態 2 の表示装置の画素構造を説明する平面図。

【図 6】実施形態 2 の表示装置の画素構造を説明する断面図。

【図 7】実施形態 3 の回路基板の製造方法を説明する平面図。

【図 8】実施例の表示素子の画素構造を説明する平面図。

【図9】A-A切断面における断面図。

【図10】B-B切断面における断面図。

【図11】C-C切断面における断面図。

【図12】D-D切断面における断面図。

【符号の説明】

【0069】

10 電界発光素子

11 制御トランジスタ

12 駆動トランジスタ(能動素子)

14 キャパシタ(cap)

101 ポリシリコン層(p-Si)

102 ゲート絶縁膜

103 第1層間絶縁膜

104 第2層間絶縁膜

106、107 バンク層

105 発光層(必要に応じてキャリア輸送層含む)

201 走査配線(gate、A1)

202 ゲート電極(Ta)

203 給電配線(com、A1)

204 信号配線(sig)

205 画素電極(アノード、ITO)

206 共通電極(カソード、A1:Li)

303、304 コンタクトホール

10

20

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図12】

【図10】

【図11】

---

フロントページの続き

(72)発明者 松枝 洋二郎

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 北和田 清文

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 3K007 AB18 BA06 DB03 FA02

5C094 AA03 AA23 BA03 BA27 DA13 DB10 EA10 HA08

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，电路板和制造电路板的方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2005326866A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2005-11-24 |

| 申请号            | JP2005168024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2005-06-08 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 木村 瞳<br>前田 浩<br>松枝 洋二郎<br>北和田 清文                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 木村 瞳<br>前田 浩<br>松枝 洋二郎<br>北和田 清文                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | H05B33/02 G09F9/30 H01L27/32 H01L51/50 H05B33/10 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H05B33/02 H05B33/10 H05B33/14.A G09F9/30.365 H01L21/20 H01L27/32 H01L29/78.627.G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K007/AB18 3K007/BA06 3K007/DB03 3K007/FA02 5C094/AA03 5C094/AA23 5C094/BA03 5C094 /BA27 5C094/DA13 5C094/DB10 5C094/EA10 5C094/HA08 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC33 3K107/DD90 3K107/EE03 5F110/AA26 5F110/BB02 5F110/BB04 5F110/CC02 5F110 /DD02 5F110/DD03 5F110/DD13 5F110/EE02 5F110/EE03 5F110/EE04 5F110/EE44 5F110/FF01 5F110/FF02 5F110/FF03 5F110/GG02 5F110/GG13 5F110/GG25 5F110/GG45 5F110/HJ13 5F110 /HK02 5F110/HK03 5F110/HK04 5F110/HL02 5F110/HL03 5F110/HL04 5F110/NN02 5F110/NN23 5F110/NN24 5F110/NN27 5F110/NN73 5F110/PP03 5F110/PP05 5F110/PP06 5F110/PP24 5F110 /QQ06 5F110/QQ11 5F152/BB02 5F152/CC02 5F152/CC03 5F152/CD13 5F152/CE05 5F152/CE14 5F152/CE24 5F152/CE27 5F152/FF03 5F152/FG18 5F152/FG21 5F152/FG23 5F152/FH01 5F152 /FH06 |         |            |

| 代理人(译)         | 田中 克郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | <a href="#">JP2005326866A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

### 摘要(译)

解决的问题：提供一种不会引起像素与整个屏幕之间的亮度不均匀的显示装置的电路装置和制造方法。在用作电致发光层的电源的电源布线（203）和用于向电致发光层提供电流的像素电极（205）之间设置有薄膜晶体管（12）。薄膜晶体管12具有沿纵向形成的栅电极202。另外，在纵向上形成有用于与像素电极205连接的第一接触孔303，在纵向上形成有用于与电源布线203连接的第二接触孔304。栅电极202以及接触孔303和304的长度方向彼此平行，并且垂直于载流子流动方向。因此，可以在不使用引线的情况下以最短的距离向电致发光装置10均匀地供应电流。[选型图]图1