(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5209109号

(P5209109)

(45) 発行日 平成25年6月12日(2013.6.12)

(24) 登録日 平成25年3月1日(2013.3.1)

|                      |                |

|----------------------|----------------|

| (51) Int.CI.         | F 1            |

| H05B 33/06 (2006.01) | H05B 33/06     |

| H05B 33/04 (2006.01) | H05B 33/04     |

| H01L 51/50 (2006.01) | H05B 33/14 A   |

| G09F 9/30 (2006.01)  | G09F 9/30 365Z |

| H01L 27/32 (2006.01) |                |

請求項の数 1 (全 17 頁)

|            |                                     |

|------------|-------------------------------------|

| (21) 出願番号  | 特願2011-280161 (P2011-280161)        |

| (22) 出願日   | 平成23年12月21日(2011.12.21)             |

| (62) 分割の表示 | 特願2007-226206 (P2007-226206)<br>の分割 |

| 原出願日       | 平成13年3月28日(2001.3.28)               |

| (65) 公開番号  | 特開2012-104497 (P2012-104497A)       |

| (43) 公開日   | 平成24年5月31日(2012.5.31)               |

| 審査請求日      | 平成23年12月21日(2011.12.21)             |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 502356528<br>株式会社ジャパンディスプレイイースト<br>千葉県茂原市早野3300番地    |

| (73) 特許権者 | 506087819<br>パナソニック液晶ディスプレイ株式会社<br>兵庫県姫路市飾磨区妻鹿日田町1-6 |

| (74) 代理人  | 100093506<br>弁理士 小野寺 洋二                              |

| (72) 発明者  | 佐藤 敏浩<br>千葉県茂原市早野3300番地 株式会社<br>日立製作所 ディスプレイグループ内    |

| (72) 発明者  | 金子 好之<br>千葉県茂原市早野3300番地 株式会社<br>日立製作所 ディスプレイグループ内    |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示領域を構成する複数の画素と、走査線と、前記画素へデータ信号を供給するデータ線と、前記画素へ電流を供給する電流供給線と、前記走査線に走査信号を供給する走査駆動回路と、前記データ線へデータ信号を供給するデータ駆動回路と、を矩形の基板上に備えた有機EL表示装置であって、

前記画素は、

前記電流供給線から電流が供給される第1の電極層と、該第1の電極層上に形成された有機発光層と、該有機発光層上に形成された第2の電極層とを備える発光素子と、

前記発光素子の下層に保護膜を介して配置され、前記電流供給線、前記データ線、前記発光素子に電気的に接続され、前記電流供給線から前記発光素子に流れる電流を前記データ信号の大きさで制御するアクティブ素子と、

を基板上に備え、

前記データ駆動回路は、フレキシブルプリント基板が接続する外部端子が配置された前記基板の第1辺と前記表示領域の間の前記基板上に配置され、

前記走査駆動回路は、前記第1辺と隣接する辺の前記基板上に配置され、

前記基板の第2辺と前記表示領域の間で、前記保護膜よりも下層に、前記第2の電極層と電気的に接続された第2電極接続電極層を備え、

前記外部端子は、前記データ駆動回路に接続される端子、前記走査駆動回路に接続される端子、前記電流供給線に接続される端子、前記第2電極接続電極層に接続される端子と

10

20

を含み、

前記第2の電極層と前記第2電極接続電極層とは、前記第2電極接続電極層の上に形成された複数のコンタクトホールを介して接続され、

前記電流供給線は、前記基板の第2辺の前記封止領域内に前記保護膜で被覆されて形成された電流供給線バスラインに電気的に接続され、

前記第2電極接続電極層は前記電流供給バスラインよりも外側にあることを特徴とする有機EL表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

10

##### 【0001】

本発明は、アクティブ・マトリクス型表示装置に係り、特に有機半導体膜などの発光層に電流を流すことによって発光させるEL(エレクトロルミネッセンス)素子またはLED(発光ダイオード)素子等の発光素子で構成した画素と、この画素の発光動作を制御する画素回路を備えた表示装置に関する。

##### 【背景技術】

##### 【0002】

近年、高度情報化社会の到来に伴い、パーソナルコンピュータ、カーナビ、携帯情報端末、情報通信機器あるいはこれらの複合製品の需要が増大している。これらの製品の表示手段には、薄型、軽量、低消費電力のディスプレイデバイスが適しており、液晶表示装置あるいは自発光型のEL素子またはLEDなどの電気光学素子を用いた表示装置が用いられている。

20

##### 【0003】

後者の自発光型の電気光学素子を用いた表示装置は、視認性がよいこと、広い視角特性を有すること、高速応答で動画表示に適していることなどの特徴があり、映像表示には特に好適と考えられている。特に、近年の有機物を発光層とする有機EL素子(有機LED素子とも言う：以下OLEDと略称する場合もある)を用いたディスプレイは発光効率の急速な向上と映像通信を可能にするネットワーク技術の進展とが相まって、OLEDディスプレイへの期待が高い。OLEDは有機発光層を2枚の電極で挟んだダイオード構造を有する。

30

##### 【0004】

このようなOLED素子を用いて構成したOLEDディスプレイ(表示装置)における電力効率を高めるためには、後述するように、薄膜トランジスタ(以下、TFTとも称する)を画素のスイッチング素子としたアクティブ・マトリクス駆動が有効である。OLEDディスプレイをアクティブ・マトリクス構造で駆動する技術としては、例えば、特開平4-328791号公報、特開平8-241048号公報、あるいは米国特許第5550066号明細書などに記載されており、また、駆動電圧関係については国際特許公報WO98/36407号などに開示されている。

##### 【0005】

OLEDディスプレイの典型的な画素構造は、第1と第2のアクティブ素子である2つの薄膜トランジスタTFT(第1のTFTはスイッチングトランジスタ、第2のTFTはドライバトランジスタ)と1つのコンデンサ(蓄積容量：データ信号保持素子)で構成される画素駆動回路(以下、画素回路とも言う)からなり、この画素回路によりOLEDの発光輝度を制御する。画素はデータ信号(または、画像信号)が供給されるM本のデータ線と、走査信号が供給されるN本の走査線(以下、ゲート線とも言う)をN行×M列のマトリクスに配列した各交差部に配置される。

40

##### 【0006】

画素の駆動には、N行のゲート線に順次走査信号(ゲート信号)を供給してスイッチングトランジスタを導通状態に(ターンオン)し、1フレーム期間Tf内に垂直方向の走査を1回終えて、再び最初(1行目)のゲート線にターンオン電圧を供給する。

50

**【0007】**

この駆動方式では、1本のゲート線にターンオン電圧が供給される時間は  $T_f / N$  以下となる。一般的には、1フレーム期間  $T_f$  の値としては  $1 / 60$  秒程度が用いられる。なお、1フレームを2フィールドで表示する場合は、1フィールド期間は1フレーム期間の  $1 / 2$  となる。

**【0008】**

あるゲート線にターンオン電圧が供給されている間は、そのデータ線に接続されたスイッチングトランジスタは全て導通状態（オン状態）となり、それに同期して M 列のデータ線に同時にまたは順次にデータ電圧（画像電圧）が供給される。これはアクティブ・マトリクス液晶装置で一般的に用いられているものである。

10

**【0009】**

データ電圧はゲート線にターンオン電圧（以下、ターンオンを単にオンとも称する。同様に、ターンオフも単にオフとも称する）が供給されている間に蓄積容量（コンデンサ）に蓄えられ（保持され）、1フレーム期間（もしくは、1フィールド期間、以下同様）はほぼそれらの値に保たれる。蓄積容量の電圧値は、ドライバトランジスタのゲート電圧を規定する。

**【0010】**

したがって、ドライバトランジスタを流れる電流値が制御されて OLE D の発光が制御される。OLE D に電圧が印加されて、その発光が始まるまでの応答時間は  $1 \mu s$  以下であることが通常であり、動きの早い画像（動画像）にも追随できる。ドライバトランジスタに電流を供給するために、電流供給線が設けられており、蓄積容量に保持されたデータ信号に応じた表示用の電流が電流供給線から供給される。

20

**【0011】**

ところで、アクティブ・マトリクス駆動では、1フレーム期間にわたって発光が行われることで高効率を実現している。TFT を設けずに、OLE D のダイオード電極をそれぞれ走査線、データ線に直結して駆動する単純マトリクス駆動と比較すると、その差異は明確である。

**【0012】**

単純マトリクス駆動では、走査線が選択されている期間にのみ OLE D に電流が流れるので、その短い期間の発光のみで 1 フレーム期間の発光と同等の輝度を得るために、アクティブ・マトリクス駆動に比べて略走査線数倍の発光輝度が必要となる。それには、必然的に駆動電圧、駆動電流を大きくしなければならず、発熱などの消費電力の損失が大きくなつて電力効率が低下する。

30

**【0013】**

このように、アクティブ・マトリクス駆動は、単純マトリクス駆動に比べて消費電力の低減の観点から優位であると考えられる。

**【発明の概要】****【発明が解決しようとする課題】****【0014】**

上記した単純マトリクス型の表示装置では、基板上の表示領域に交差配置した走査線とデータ線をそのまま当該表示領域の外部に引き出して駆動回路に接続し、駆動回路を外部回路と接続するための端子パッドを設けている。しかし、このような端子構成をアクティブ・マトリクス型の表示装置にそのまま適用することは困難である。

40

**【0015】**

すなわち、アクティブ・マトリクス駆動の OLE D 表示装置では、1フレーム期間にわたって表示を保持するためのコンデンサへの電流供給を、当該コンデンサの一方の電極をスイッチングトランジスタの出力端子に接続し、他方の電極をコンデンサ用の共通電位線に接続したり、あるいは OLE D に電流を供給する電流供給線に接続している。

**【0016】**

図 9 は OLE D を用いた従来の表示装置の 1 構成例を模式的に説明するブロック図、図

50

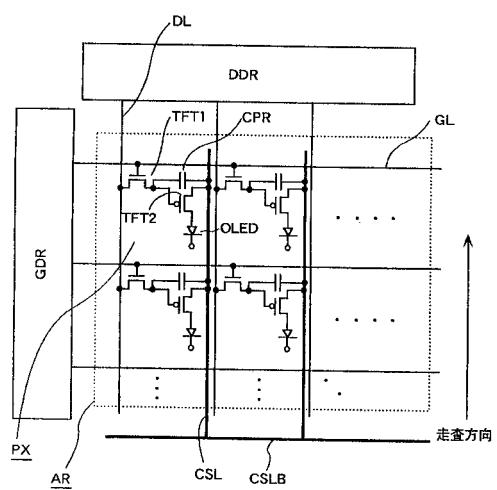

10は図9における画素構成の説明図である。この表示装置（画像表示装置）は、ガラス等の絶縁材からなる基板SUB上に複数のデータ線DLと複数のゲート線すなわち走査線GLとのマトリクス配列で形成した表示部AR（図中、点線で囲った内部）の周囲にデータ駆動回路DDR、走査駆動回路GDR、電流供給回路CSSを配置して構成されている。

#### 【0017】

データ駆動回路DDRはNチャンネル型とPチャンネル型の薄膜トランジスタTFTによる相補型回路またはNチャンネルのみかPチャンネルのみの单チャンネル型の薄膜トランジスタTFTで構成されるシフトレジスタ回路、レベルシフタ回路、アナログスイッチ回路などからなる。なお、電流供給回路CSSはバスラインのみとし、外部電源から供給するようにも構成できる。10

#### 【0018】

図9は表示部ARにコンデンサ用の共通電位線COMLを設けた方式であり、コンデンサの前記他端の電極は、この共通電位線COMLに接続される。共通電位線COMLは共通電位供給バスラインCOMBの端子COMTから外部の共通電位源に引き出されている。なお、共通電位線COMLを設けず、コンデンサを電流供給線に接続した方式も既知である。

#### 【0019】

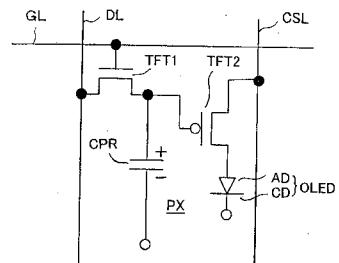

図10に示したように、画素PXはデータ線DLとゲート線GLで囲まれた領域に配置されたスイッチングトランジスタである第1の薄膜トランジスタTFT1、ドライバトランジスタである第2の薄膜トランジスタTFT2、コンデンサCPR、および有機発光素子OLEDで構成される。薄膜トランジスタTFT1のゲートはゲート線GLに、ドレイインはデータ線DLに接続されている。薄膜トランジスタTFT2のゲートは薄膜トランジスタTFT1のソースに接続され、この接続点にコンデンサCPRの一方の電極（+極）が接続されている。20

#### 【0020】

図11は図10の画素構成をもつ図9の表示装置の構成をさらに説明するブロック図である。薄膜トランジスタTFT2のドレイインは電流供給線CSLに、ソースは有機発光素子OLEDの第1の電極（ここでは陽極）ADに接続されている。そして、コンデンサCPRの他端（-極）は共通電位線バスラインCOMBから分岐した共通電位線COMLに接続されている。データ線DLはデータ駆動回路DDRで駆動され、走査線（ゲート線）GLは走査駆動回路GDRで駆動される。また、電流供給線CSLは電流供給バスラインCSLBを介して図8の電流供給回路CSSあるいは端子を介して外部電流源に接続している。30

#### 【0021】

図10と図11において、1つの画素PXが走査線GLで選択されて薄膜トランジスタTFT1がターンオンすると、データ線DLから供給される画像信号がコンデンサCPRに蓄積される。そして、薄膜トランジスタTFT1がターンオフした時点で薄膜トランジスタTFT2がターンオンし、電流供給線CSLからの電流が有機発光素子OLEDに流れ、ほぼ1フレーム期間にわたってこの電流が持続する。このとき流れる電流はコンデンサCPRに蓄積されている信号電荷で規定される。40

#### 【0022】

コンデンサCPRの動作レベルは共通電位線COMLの電位で規定される。これにより、画素の発光が制御される。有機発光素子OLEDから流れ出る電流は陰極CDから図示しない電流引抜き線に流れる。

#### 【0023】

この方式では、画素領域の一部を貫通して共通電位線COMLを設ける必要があるため、所謂開口率の低下をもたらし、表示装置全体としての明るさ向上を抑制してしまう。

#### 【0024】

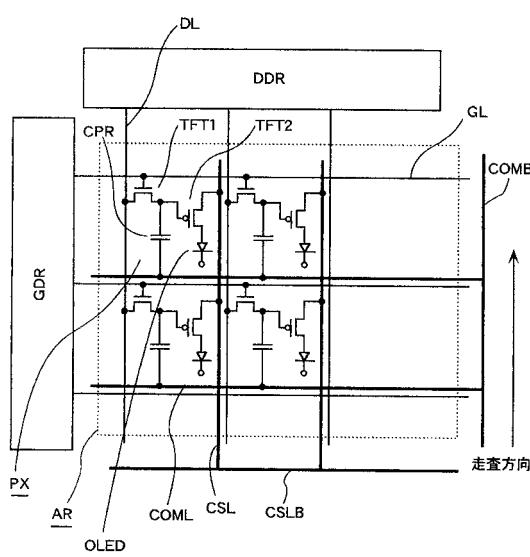

図12はOLEDを用いた従来の表示装置の他の構成例を模式的に説明する図11と同50

様のブロック図である。この例では、各画素を構成する薄膜トランジスタ T F T 1、T F T 2 およびコンデンサ C P R の基本配列は図 9 と同様であるが、コンデンサ C P R の他端を電流供給線 C S L に接続した点で異なる。

#### 【 0 0 2 5 】

すなわち、1つの画素 P X が走査線 G L で選択されて薄膜トランジスタ T F T 1 がターンオンすると、データ線 D L から供給される画像信号がコンデンサ C P R に蓄積され、薄膜トランジスタ T F T 1 がターンオフした時点で薄膜トランジスタ T F T 2 がターンオンしたとき、電流供給線 C S L からの電流が有機発光素子 O L E D に流れ、図 10 と同様に、ほぼ 1 フレーム期間（または、1 フィールド期間）にわたってこの電流が持続する。このとき流れる電流はコンデンサ C P R に蓄積されている信号電荷で規定される。コンデンサ C P R の動作レベルは電流供給線 C S L の電位で規定される。これにより、画素の発光が制御される。10

#### 【 0 0 2 6 】

図 9 ~ 図 12 で説明したこの種の表示装置においては、有機発光素子 O L E D の第 1 の電極（例えば陽極、以下第 1 の電極層とも称する）A D となる薄膜トランジスタ T F T 2 のソース電極は I T O（インジウム・チン・オキサイド）等の導電性薄膜で形成され、かつ各画素 P X の第 1 の電極 A D は個別に分離されている。

#### 【 0 0 2 7 】

また、発光素子を構成する第 2 の電極（例えば陰極、以下第 2 の電極層とも称する）C D は素子の最上層に位置するため、直接外気に触れて腐食が生じる恐れがある。通常、第 2 の電極層は全画素について共通のべた膜に形成されており、外部と電気的に接続をとる必要がある。この第 2 の電極層 C D への電流供給のための端子は当該第 2 の電極層の延長で基板の端子部（端子パッド）に直接引き出した場合は、その端子部近傍では外気との接触で腐食の発生が起こり易い。20

#### 【 0 0 2 8 】

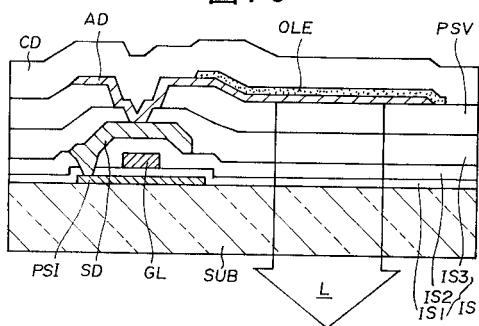

図 13 は有機発光素子を用いた表示装置の 1 画素付近の構造を説明する断面図である。この表示装置は、ガラス基板 S U B の上に低温ポリシリコンを好適とするポリシリコン半導体層 P S I 、第 1 の絶縁層 I S 1 、走査配線であるゲート配線（ゲート電極）G L 、第 2 の絶縁層 I S 2 、アルミニウム配線で形成したソース電極 S D 、第 3 の絶縁層 I S 3 、保護膜 P S V 、第 1 の電極層 A D 、有機発光層 O L E 、第 2 の電極層 C D を積み上げて構成される。30

#### 【 0 0 2 9 】

ポリシリコン半導体層 P S I とゲート配線 G L 、ソース電極 S D で構成される薄膜トランジスタ（この薄膜トランジスタはドライバトランジスタ）が選択されると、ソース電極 S D に接続した第 1 の電極層 A D と有機発光層 O L E および第 2 の電極層 C D で形成される有機発光素子が発光し、その光 L が基板 S U B 側から外部に出射する。

#### 【 0 0 3 0 】

このとき、当該画素の第 2 の電極層 C D に部分的な腐食や劣化があると、電流供給線 C S L から流れる電流が充分に供給されず、あるいは当該画素を迂回して流れ、発光が不十分になったり全く発光しないことになる。その結果、所謂点欠陥、領域欠陥等の表示不良をもたらす。40

#### 【 0 0 3 1 】

本発明の目的は、画素を構成する第 2 の電極層への給電構造を改良して第 2 の電極層の腐食を防止し、高品質の表示を可能とした表示装置を提供することにある。

#### 【 課題を解決するための手段】

#### 【 0 0 3 2 】

上記目的を達成するため、本発明は、第 2 の電極層と基板の一辺の端部に形成されて当該第 2 の電極層に電気的に接続される端子パッドとを、当該基板の当該一辊とは異なる他辺に設けられ且つ保護膜で被覆された第 2 電極接続電極層を介して接続し、第 2 の電極層が第 2 電極接続電極層に接するコンタクトホールを端子パッドの位置より遠ざけた。50

## 【0033】

この構成したことにより、陰極の腐食を防止し、高品質の表示を可能とした高信頼性の表示装置が提供される。本発明のより具体的な構成例を記述すると以下のとおりである。すなわち、

(1) 基板SUB上の封止領域SL内にマトリクス配列された複数の走査線GLと前記複数の走査線GLに交差する複数のデータ線DLとの交差部毎に設けられた複数の画素PXからなる表示領域AR、

前記基板SUB上の前記封止領域SL内且つ前記表示領域ARの外側に設けられた前記複数の走査線GLに走査信号を供給する走査駆動回路GDR及び前記複数のデータ線DLにデータ信号を供給するデータ駆動回路DDR、

前記画素PXの夫々に設けられた発光素子OLEDに電流を供給する複数の電流供給線CSL、及び

前記基板SUBの第1辺にはデータ駆動回路が設けられ、該第1辺の前記封止領域SLより外側に夫々設けられて、前記データ駆動回路DDRと電気的に接続される第1の端子パッドPAD1、前記走査駆動回路GDRと電気的に接続される第2の端子パッドPAD2、並びに前記複数の電流供給線CSLと電気的に接続される第3の端子パッドPAD3、を備えた表示装置において、

前記複数の画素PXの各々に、前記複数の走査線GLの一つに供給される前記走査信号によりターンオンされる第1のアクティプ素子TFT1と、該第1のアクティプ素子TFT1のターンオンに応じて前記データ線DLの一つから供給されるデータ信号を保持するデータ保持素子CPRと、該データ保持素子CPRに保持されたデータ信号に従って前記電流供給線CSLからの電流を前記発光素子OLEDに供給して該発光素子OLEDを発光させる第2のアクティプ素子TFT2とを有する画素回路を設け、

前記複数の画素PXの各々に設けられた前記発光素子OLEDを、前記画素回路を覆う保護膜PSV上に形成され且つ前記第2のアクティプ素子TFT2から前記電流を受ける第1の電極層ADと、該第1の電極層AD上に形成された有機発光層OLEと、該有機発光層OLE上に形成され且つ該複数の画素PXを覆う第2の電極層CDとで構成し、

前記基板SUBの前記第1辺とは異なる第2辺に沿う前記封止領域SL内に、前記第2の電極層CDに電気的に接続される第2電極接続電極層CNTBを、該第2の電極層CDより下層に且つ前記保護膜PSVで被覆させて形成し、該第2の電極層CDを前記保護膜PSVに形成されたコントクトホールCNTを通して該第2電極接続電極層CNTBに接触させ、

前記第2電極接続電極層CNTBを、前記基板SUBの前記第2辺から前記第1辺へ延在する第2電極接続電極引き回しラインCNTLにより該基板SUBの該第1辺の前記封止領域SLより外側に夫々設けられた第4の端子パッドPAD4に電気的に接続させた。

## 【0034】

(2)、(1)において、前記複数の電流供給線CSLを、前記基板SUBの前記第1辺とは異なる他辺の前記封止領域SL内に前記保護膜PSVで被覆されて形成された電流供給線バスラインCSBに電気的に接続し、

前記電流供給線バスラインCSBを、前記基板SUBの前記他辺から前記第1辺へ延在する電流供給線引回しラインCSLLにより第3の端子パッドPAD3に電気的に接続した。

## 【0035】

(3)、(2)において、前記第2電極接続電極層CNTB及び前記電流供給線バスラインCSBの双方を、前記画素回路に形成された絶縁層IS上に設け、且つ前記保護膜PSVで被覆した。

## 【0036】

(4)、(2)において、前記基板SUBの前記第2辺を該基板SUBの前記第1辺に隣接したものとし、該基板SUBの前記他辺は該基板SUBの該第2辺に隣接し且つ該第1辺に前記表示領域ARを介して対向するものとした。

## 【0037】

(5)、(4)において、前記電流供給線引回しラインCSLLを、前記封止領域SL内の前記

10

20

30

40

50

基板SUBの前記第2辺に沿う側にて、前記表示領域ARと前記第2電極接続電極層CNTBとに挟まれるように形成した。

**【0038】**

(6)、(5)において、前記走査駆動回路GDR及び前記データ駆動回路DDRを、前記基板SUBの前記第1辺及び該第1辺に隣接し且つ前記表示領域ARを介して前記第2辺と対向する第3辺に設けた。

**【0039】**

(7)、(2)において、前記基板SUBの前記第2辺と前記他辺とを、ともに前記表示領域ARを介して該基板SUBの前記第1辺と対向しているものとした。

**【0040】**

(8)、(7)において、前記電流供給線バスラインCSBを、前記基板SUBの前記第2辺に沿う前記封止領域SL内にて、前記表示領域ARと前記第2電極接続電極層CNTBとに挟まれるように形成した。

**【0041】**

(9)、(8)において、前記第2電極接続電極引き回しラインCNTL及び前記電流供給線引回しラインCSLLを、前記基板SUBの前記第1辺及び前記第2辺に夫々隣接する第3辺に沿う前記封止領域SL内に形成し、該電流供給線引回しラインCSLLを前記表示領域ARと該第2電極接続電極引き回しラインCNTLとの間に配置した。

**【0042】**

なお、本発明は上記の構成および後述する実施例の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変更が可能であることは言うまでもない。本発明の他の目的および構成は後述する実施の形態の記載から明らかになるであろう。

**【発明の効果】**

**【0043】**

本発明によれば、表示装置の画素を構成する電極層やその端子近傍での腐食が防止されるため表示不良の発生がない。また、電流供給線を通して電流を安定かつ充分に供給でき、高品質の表示を可能とした表示装置を提供することができる。

**【図面の簡単な説明】**

**【0044】**

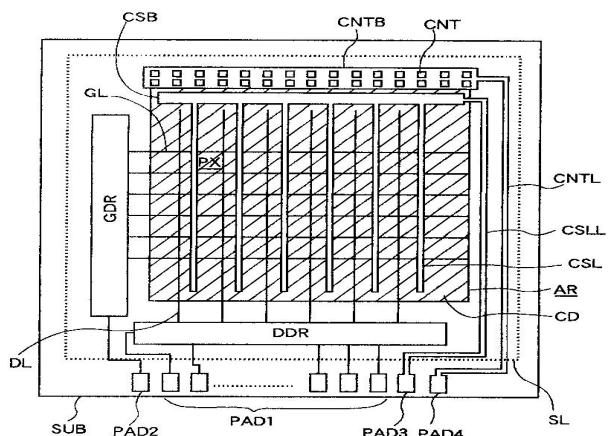

**【図1】**本発明による表示装置の第1実施例の構成を模式的に説明するブロック図である。

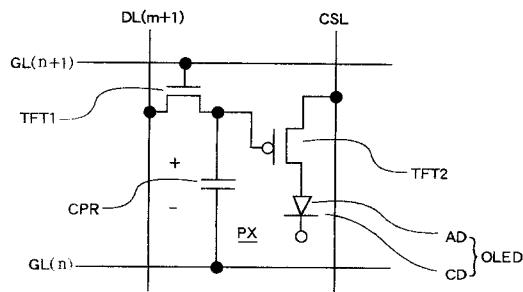

【図2】図1における1画素の画素回路の構成図である。

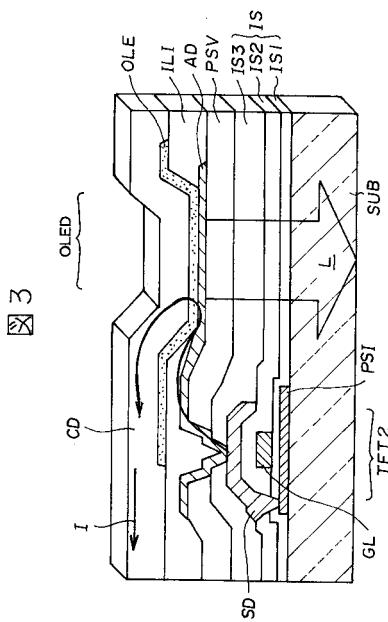

【図3】本発明による表示装置の発光メカニズムを説明する1画素付近の模式図である。

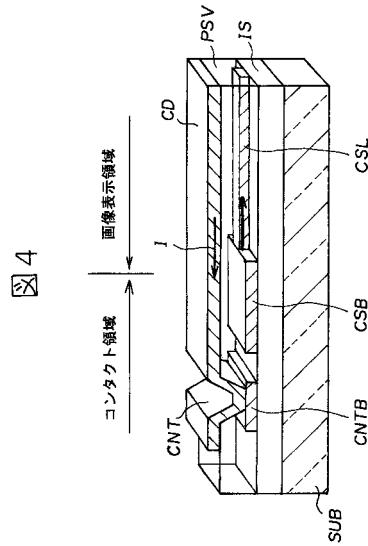

【図4】本発明による表示装置の第2の電極層と第2電極接続電極層との接続部分を説明する模式図である。

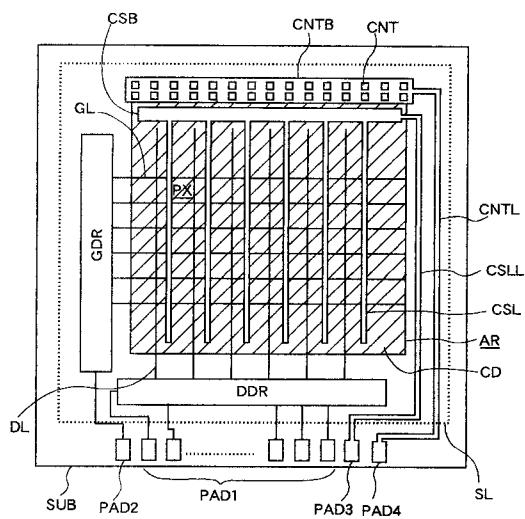

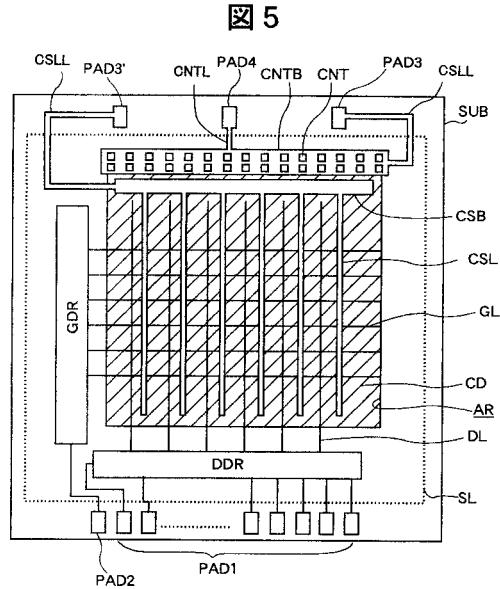

【図5】本発明による表示装置の第2実施例の構成を模式的に説明するブロック図である。

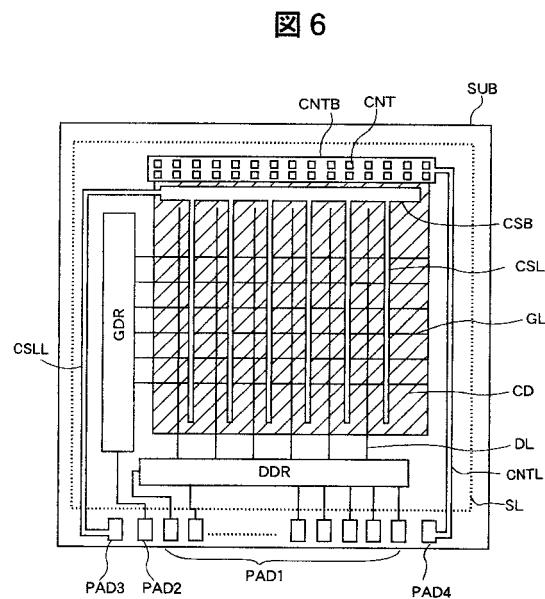

【図6】本発明による表示装置の第3実施例の構成を模式的に説明するブロック図である。

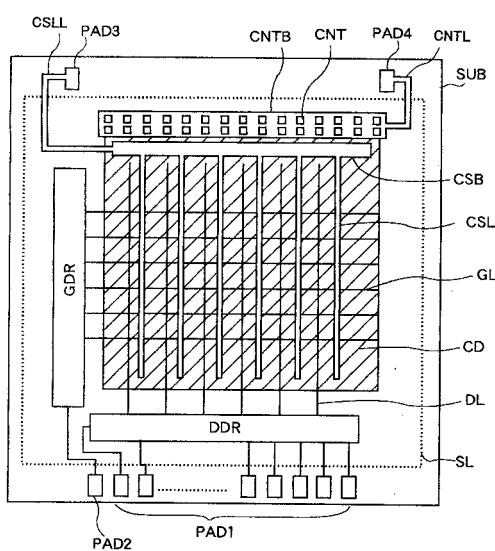

【図7】本発明による表示装置の第4実施例の構成を模式的に説明するブロック図である。

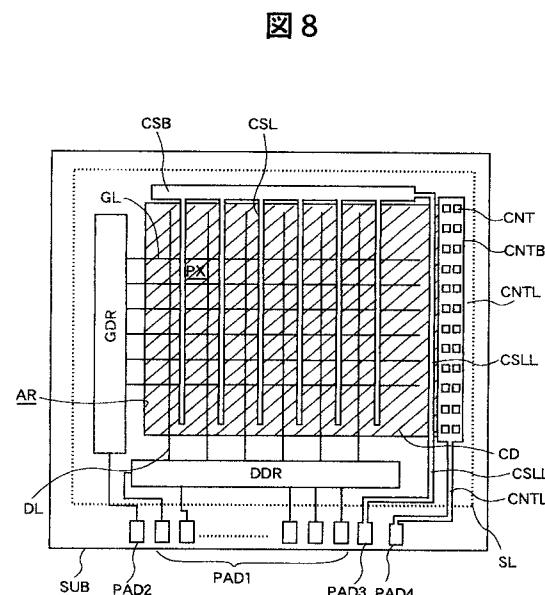

【図8】本発明による表示装置の第5実施例の構成を模式的に説明するブロック図である。

【図9】有機発光素子を用いた従来の表示装置の構成例を説明するブロック図である。

【図10】図9における画素構成の説明図である。

【図11】図10の画素構成をもつ図9の表示装置の構成をさらに説明するブロック図である。

【図12】有機発光素子を用いた従来の表示装置の他の構成例を模式的に説明する図11と同様のブロック図である。

【図13】有機発光素子を用いた表示装置の1画素付近の構造を説明する断面図である。

10

20

30

40

50

**【発明を実施するための形態】**

**【0045】**

以下、本発明の実施の形態につき、実施例の図面を参照して詳細に説明する。図示しないが、以降で説明する各画素に有する有機発光層は電流値に比例した輝度で、かつその有機材料に依存した色（白色も含む）で発光させてモノクロあるいはカラー表示を行わせるものと、白色発光の有機層に赤、緑、青等のカラーフィルタを組み合わせてカラー表示を行わせるものとがある。

**【実施例1】**

**【0046】**

図1は本発明による表示装置の第1実施例の構成を模式的に説明するブロック図である。

10

。本実施例の表示装置は、ガラス基板SUB上に走査駆動回路GDRとデータ駆動回路DDRを有する。

**【0047】**

そして、マトリクスに形成された走査駆動回路GDRで駆動される（走査される）走査線GL、データ駆動回路DDRで駆動されるデータ線DL、電流供給線CSLで囲まれた領域に1画素が形成される。また、基板SUBの1の辺には外部回路からデータ駆動回路DDR、走査駆動回路GDRへの信号や電圧を供給するための端子パッドPAD1、PAD2が形成されている。

**【0048】**

図2は図1における1画素の画素回路の構成図である。本実施例の概略構成は、1画素はデータ線DL(m+1)と走査線GL(n+1)、GL(n)および電流供給線CSLで囲まれた領域に形成される。ここでは、現在走査されている（選択されている）走査線をGL(n+1)として説明する。

20

**【0049】**

走査線GL(n+1)で選択されている複数の画素のうち、画素PXに着目する。アクティブ素子である第1の薄膜トランジスタTFT1はスイッチングトランジスタ、第2の薄膜トランジスタTFT2はドライバトランジスタである。第1の薄膜トランジスタTFT1のゲートは走査線GL(n+1)に接続され、そのドレインはデータ線DL(m+1)に、ソースは第2薄膜トランジスタTFT2のゲートに接続されている。

**【0050】**

第2の薄膜トランジスタTFT2のドレインは図1に示した電流供給線バスラインCSBから電流が供給される電流供給線CSLに接続されている。そして、そのソースはOLED24の第1の電極層ADに接続されている。第1の薄膜トランジスタTFT1のソースと第2の薄膜トランジスタTFT2のゲートの接続点にはデータ信号保持素子としてのコンデンサCPRの一方の端子が接続され、他方の端子は直前の走査線GL(n)に接続されている。

30

**【0051】**

図2に示した1画素の回路構成において、第1の薄膜トランジスタTFT1のソースと第2の薄膜トランジスタTFT2のゲートの接続点に接続されるコンデンサCPRの一方の端子は+極であり、走査線GL(n)に接続される他方の端子は-極である。

40

**【0052】**

また、有機発光素子OLEDは第1の電極層ADと第2の電極層CDの間に有機発光層（図示せず）を挟んだ構成であり、第1の電極層ADは第2の薄膜トランジスタTFT2のソース電極に接続し、第2の電極層CDは全画素にわたってべた形成されて図1の第2電極接続電極層CNTBに接続している。

**【0053】**

この第2電極接続電極層CNTBは、所謂電流引抜き配線（電極）であり、基板の下層に前記端子パッドPAD1、PAD2と同層に形成されており、第2の電極層CDをコンタクトホールCNTで接続し、第2電極接続電極引回しラインCNTLで前記端子パッドPAD1、PAD2と同層に形成された端子PAD4に接続されている。

50

**【 0 0 5 4 】**

なお、第1の電極層の配線である電流供給線C S Lも電流供給線バスラインC S Bと電流供給線引回しラインC S L Lで前記端子パッドP A D 1、P A D 2と同層に形成された端子P A D 3に接続されている。上記第2電極接続電極層C N T Bは電流供給線バスラインC S Bよりも基板の外側、かつ点線で示した基板の封止領域S Lの内側に配置されている。

**【 0 0 5 5 】**

このように、第2の電極層C DをコンタクトホールC N Tで接続する第2電極接続電極層C N T Bを電流供給線バスラインC S Bよりも基板S U Bの外側で、かつシール領域の内側に配置したことで、フレキシブルプリント基板を介して1辺で外部回路と接続する方式における基板上のレイアウトが容易となる。10

**【 0 0 5 6 】**

第1の薄膜トランジスタT F T 1のターンオンでコンデサC P Rに書き込まれ、電荷量として保持されたデータ信号は第1の薄膜トランジスタT F T 1のターンオフに伴う第2の薄膜トランジスタT F T 2のターンオンで電流供給線C S Lからの電流を当該コンデンサC P Rに保持された電荷量（データ信号の階調を示す）で制御された電流量として有機発光素子O L Eに流す。

**【 0 0 5 7 】**

有機発光素子O L E Dは供給される電流量にほぼ比例した輝度で、かつ当該有機発光素子を構成する有機発光層O L Eの材料に依存した色で発光する。カラー表示の場合は、通常は赤、緑、青の画素毎に有機発光層材料を変えるか、あるいは白色の有機発光層材料と各色のカラーフィルタの組合せを用いる。20

**【 0 0 5 8 】**

なお、データ信号の与え方はアナログ量でも、あるいは時分割のデジタル量でもよい。また、階調制御は、赤、緑、青の各画素の面積を分割した面積階調方式を組合せてよい。

**【 0 0 5 9 】**

本実施例では、電流供給線バスラインC S Bと、各画素回路の発光動作後に第2の電極層C Dから流れ出る電流を基板の下層に形成した全画素共通に形成した電流引抜き配線である第2電極接続電極層C N T Bから第2電極接続電極引回しラインC N T Lで端子パッドP A D 4から外部回路に流出させるように構成したものである。30

**【 0 0 6 0 】**

そのため、本実施例では、上層にべた形成した全画素共通の第2の電極層C DをコンタクトホールC N Tで第2電極接続電極層C N T Bに接続している。第2電極接続電極引回しラインC N T Lも第2電極接続電極層C N T Bと同層に形成される。

**【 0 0 6 1 】**

通常、この種の表示装置では、信頼性を確保するために缶などを用いた封止構造を採用している。基板S U Bには、この封止缶詰を接着するためのシール領域が設けられている。このシール領域の内側に上記の第2電極接続電極層C N T Bや第2電極接続電極引回しラインC N T Lを形成している。そして、少なくとも上記の第2電極接続電極層C N T Bを電流供給線バスラインC S Bの外側に配置している。40

**【 0 0 6 2 】**

上記第2電極接続電極層C N T B等は基板の下層に形成され、その上に絶縁層や保護膜が積層されるので、第2電極や第2電極接続電極層、好ましくは第2電極接続電極引回しラインも含めて外気との接触がなくなり、その腐食が防止されるため、信頼性が向上し、高品質の表示を可能とした表示装置を提供することができる。なお、上記のコンタクトホールの個数は1つでもよいが、複数個設けた方がより多くの電流を安定して流すことができるため、本実施例では複数個設けている。

**【 0 0 6 3 】**

図3は本発明による表示装置の発光メカニズムを説明する1画素付近の模式図、図4は50

第2電極層と第2電極接続電極層との接続部分を説明する模式図である。図1と同一参照符号は同一部分に対応する。また、図中の参照符号Iで示した矢印は発光に寄与する電流の経路を示す。

#### 【0064】

薄膜トランジスタTFT2はドライバトランジスタである。この薄膜トランジスタTFT2がゲート線GLで選択されたとき、電流供給線バスラインから分岐した電流供給線により、コンデンサに保持されたデータ信号に応じた階調の電流値の電流Iが当該薄膜トランジスタTFT2を通して有機発光素子OLEDの第1の電極層ADに供給される。

#### 【0065】

有機発光素子OLEDは、その有機発光層OLE内で第2の電極層CDからの電子と第1の電極層ADからのホールとが再結合し、当該有機発光層OLEの材料特性に応じたスペクトルの光Lを発光する。第1の電極層ADは各画素毎に独立であるが、第2の電極層CDは全画素についてべた膜状に形成されている。薄膜トランジスタTFT2から有機発光素子OLEDを通った電流Iは第2の電極層CDから図4に示した第2電極接続電極層CNTBを通して図1の第2電極接続電極引回しラインCNTLから端子パッドPAD4に流出する。このような画素が多数マトリクス配列されて2次元の表示装置が構成される。

10

#### 【実施例2】

#### 【0066】

図5は本発明による表示装置の第2実施例の構成を模式的に説明するブロック図である。図1と同一参照符号は同一機能部分に対応する。本実施例では、電流供給線CSLを接続する電流供給線バスラインCSBの2つの端子パッドPAD3とPAD3'、および第2電極接続電極層CNTBの端子パッドPAD4をデータ駆動回路の端子パッドPAD1および走査駆動回路GDRの端子パッドPAD2が配置される基板の1の辺と反対側の辺に設けた。

20

#### 【0067】

本実施例によっても、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置することで基板上のレイアウトが容易となる。

#### 【0068】

30

本実施例のように、電流供給線バスラインCSBからその端子パッドPAD3とPAD3'に引き回す電流供給線引回しラインCSLL、および第2電極接続電極層CNTBと端子パッドPAD4間を接続する第2電極接続電極引回しラインCNTLの基板上での引回し長さが短くなるため、より均一な電流供給と電流引抜きが可能となる。これにより、表示領域での発光分布が均一となり、より高品質の表示が得られる。なお、電流供給線引回しラインCSLLは2本としているが、何れか一方であってもよい。図5に示したように、電流供給線引回しラインCSLLを電流供給線バスラインCSBの一方及び他方からそれぞれ引き出して2本とした場合は対称性が良くなるという効果がある。

#### 【0069】

本実施例によって、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置することで、フレキシブルプリント基板を介して対向する2辺で外部回路と接続する方式における基板上のレイアウトが容易となる。

40

#### 【0070】

また、本実施例の構成としたことで、シール領域の近傍における配線パターンが少なくなるため、シール材料をUV硬化させる際のUV光の遮蔽物が少なくなり、当該シール材料を効果的に硬化させることができる。これにより、確実な封止が可能となり、表示装置の信頼性をさらに向上できる。

#### 【実施例3】

#### 【0071】

50

図6は本発明による表示装置の第3実施例の構成を模式的に説明するブロック図である。図1と同一参照符号は同一機能部分に対応する。本実施例では、電流供給線CSLを接続する電流供給線バスラインCSBのパッドPAD3と第2電極接続電極層CNTBの端子パッドPAD4をデータ駆動回路の端子パッドPAD1および走査駆動回路GDRの端子パッドPAD2が配置される基板の1の辺の両端に振り分けて設けた。

#### 【0072】

前記第1～第2実施例と同様に、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置した。他の構成は図1と同様なので繰り返しの説明は省略する。

10

#### 【0073】

本実施例によっても、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置したことで、フレキシブルプリント基板を介して1辺で外部回路と接続する方式における基板上のレイアウトが容易となる。

#### 【実施例4】

#### 【0074】

図7は本発明による表示装置の第4実施例の構成を模式的に説明するブロック図である。図1と同一参照符号は同一機能部分に対応する。本実施例では、電流供給線CSLを接続する電流供給線バスラインCSBのパッドPAD3と第2電極接続電極層CNTBの端子パッドPAD4をデータ駆動回路の端子パッドPAD1および走査駆動回路GDRの端子パッドPAD2が配置される基板の1の辺と反対側の辺に設けた。

20

#### 【0075】

前記第1～第3実施例と同様に、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置した。

#### 【0076】

本実施例によっても、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBよりも基板SUBの外側で、かつシール領域の内側に配置したことで、フレキシブルプリント基板を介して対向する2辺で外部回路と接続する方式における基板上のレイアウトが容易となる。他の構成は図6と同様なので繰り返しの説明は省略する。

30

#### 【0077】

本実施例のように、電流供給線バスラインCSBからその端子パッドPAD3に引き回す電流供給線引回しラインCSLL、および第2電極接続電極層CNTBと端子パッドPAD4間を接続する第2電極接続電極引回しラインCNTLの基板上での引回し長さが短くなるため、より均一な電流供給と電流引抜きが可能となる。これにより、表示領域での発光分布が均一となり、より高品質の表示が得られる。

#### 【0078】

また、本実施例の構成としたことで、シール領域の近傍における配線パターンが少なくなるため、シール材料をUV硬化させる際のUV光の遮蔽物が少なくなり、当該シール材料を効果的に硬化させることができる。これにより、確実な封止が可能となり、表示装置の信頼性をさらに向上できる。

40

#### 【0079】

以上説明した第2～第4実施例では、電流路である電流供給線引回しラインCSLLと第2電極接続電極引回しラインCNTLは、それぞれ基板上の広い領域に充分な太さの配線を形成でき、安定な電流路を確保することができる。また、特に第2実施例および第4実施例のように、パッドとの間の距離が短い場合は、より安定な電流路を確保することができる。

#### 【実施例5】

50

**【 0 0 8 0 】**

図8は本発明による表示装置の第5実施例の構成を模式的に説明するブロック図である。図1と同一参照符号は同一機能部分に対応する。本実施例では、基板上において、第2電極接続電極層CNTBを端子PAD1～4を配置した辺に隣接して前記ゲート走査駆動回路GDRとは反対側の辺、かつ前記電流供給線引回しラインCSLLよりも外側に設けた。

**【 0 0 8 1 】**

本実施例によって、第2の電極層CDをコンタクトホールCNTで接続する第2電極接続電極層CNTBを電流供給線バスラインCSBを端子パッドPAD3に引き回す電流供給線引回しラインCSLLよりも基板SUBの外側で、かつシール領域の内側に配置したことで、ゲート走査駆動回路GDRと対称配置のレイアウトとなり、全体としてバランスの取れた配置とすることができる。他の構成は図1と同様なので繰り返しの説明は省略する。

10

**【 0 0 8 2 】**

また、本実施例のように、端子パッドPAD4と第2電極接続電極引回しラインCNTLの基板上での引回し長さが短くなるため、より均一な電流供給と電流引抜きが可能となる。これにより、表示領域での発光分布が均一となり、より高品質の表示が得られる。

**【 0 0 8 3 】**

なお、上記の各実施例は、第1の電極層と第2の電極層のそれぞれを陰極層と陽極層に對応させることができるが、本発明はこれらを入れ換えた構造に対しても同様に適用できる。また、本発明は上記したOLEDを用いた表示装置に限るものではなく、OLEDと同様の発光動作で表示を行う他の表示装置にも同様に適用できる。

20

**【 符号の説明 】****【 0 0 8 4 】**

SUB 基板

GL ゲート線（走査線）

DL データ線

CSL 電流供給線

CSB 電流供給線バスライン

CSLL 電流供給線引回しライン

30

CD 陰極

CNT コンタクトホール

CNTB 陰極接続電極層

CNTL 陰極接続電極引回しライン

AD 陽極

OLED 有機発光層

OLED 有機発光素子。

【図1】

【図2】

図1

図2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

図9

図10

【図11】

【図12】

図11

図12

【図13】

図13

---

フロントページの続き

審査官 中山 佳美

(56)参考文献 特開平11-109886(JP,A)

特開平11-202366(JP,A)

特開2000-357584(JP,A)

特開2001-043971(JP,A)

特開2000-173766(JP,A)

特開2001-076873(JP,A)

国際公開第98/036407(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 51/50 - 51/56

H01L 27/32

H05B 33/00 - 33/28

G09F 9/30

|                |                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP5209109B2</a>                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2013-06-12 |

| 申请号            | JP2011280161                                                                                                                                                                                                                                                                                  | 申请日     | 2011-12-21 |

| [标]申请(专利权)人(译) | 株式会社日立制作所<br>松下液晶显示器股份有限公司                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司<br>松下液晶显示器有限公司                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 有限公司日本东显示器<br>松下液晶显示器有限公司                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 佐藤敏浩<br>金子好之                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 佐藤 敏浩<br>金子 好之                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | H05B33/06 H05B33/04 H01L51/50 G09F9/30 H01L27/32                                                                                                                                                                                                                                              |         |            |

| FI分类号          | H05B33/06 H05B33/04 H05B33/14.A G09F9/30.365.Z G09F9/30.365 H01L27/32 H05B33/12.B H05B33/22.Z H05B33/26.Z                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC23 3K107/CC33 3K107/DD11 3K107/DD22 3K107/DD28 3K107/DD37 3K107/DD38 3K107/DD89 3K107/DD90 3K107/DD91 3K107/EE03 3K107/EE46 3K107/FF15 3K107/HH05 5C094/AA07 5C094/AA23 5C094/AA38 5C094/BA03 5C094/BA27 5C094/DA09 5C094/DA13 5C094/DB02 5C094/FA02 5C094/FA04 |         |            |

| 代理人(译)         | 小野寺杨枝                                                                                                                                                                                                                                                                                         |         |            |

| 审查员(译)         | 中山 佳美                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | <a href="#">JP2012104497A</a>                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                     |         |            |

## 摘要(译)

要解决的问题：通过改进向构成像素的一个电极供电的结构来执行高质量显示，以防止电极腐蚀。解决方案：显示装置的基板SUB包括发光元件，该发光元件包括：a第一电极层，由有源元件驱动；有机发光层，其施加在第一电极层上；第二电极层CD形成在有机发光层上。在基板SUB上，设置第二电极连接电极层CNTB，该第二电极连接电极层CNTB是比第二电极层CD低的层并且涂覆有绝缘膜或保护膜，并且第二电极层CD连接到第二电极连接电极层CNTB通过接触孔CNT。

图 1