## 【特許請求の範囲】

## 【請求項 1】

画素回路を複数個マトリクス配置し、各行の画素回路を共通に走査線に接続し、各列の画素回路を共通にデータ線に接続してなる画像表示部を備え、走査線を順次選択すると同時に、選択した行の各画素の表示に応じたレベルの電流信号を当該画素が接続されたデータ線に印加して表示を行うエレクトロルミネッセンス表示装置において、

各画素回路は、該当列のデータ線に一端が接続された第1のスイッチと、該第1のスイッチの他端にドレインが接続され、ソースが電源に接続された電流駆動トランジスタ、該第1のスイッチの他端に入力端子が接続されたエレクトロルミネッセンス素子、該電流駆動トランジスタのゲートに一端が接続された第2のスイッチを有し、

各列のデータ線の画素回路前段に、データ線電圧を入力とするソースホロワ回路を設け、該ソースホロワ回路の出力端子と該当列の画素回路の第2のスイッチの他端を共通に補助データ線に接続したことを特徴とするエレクトロルミネッセンス表示装置。

## 【請求項 2】

上記ソースホロワ回路が電流源を含み、該電流源の電流値は所定期間にデータ線に供給される電流信号に対応している請求項1に記載のエレクトロルミネッセンス表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、電流の注入により発光するエレクトロルミネッセンス(EL)素子を画素毎に備え、各画素をアクティブマトリクス駆動して画像表示を行うEL表示装置に関する。

## 【背景技術】

## 【0002】

EL素子や液晶素子などを用いて構成されたフラットな表示装置においては、複数行、複数列に配置した画素を、行毎に走査線に、列毎にデータ線に共通に接続し、行走査回路より各走査線を選択すると同時に、列走査回路より各データ線に所定の表示信号を印加して、選択された該当行の画素に所定の表示を行わせるマトリクス駆動が一般的である。

## 【0003】

例えば、特許文献1には、アクティブマトリクス駆動によるEL表示装置が開示されている。

## 【0004】

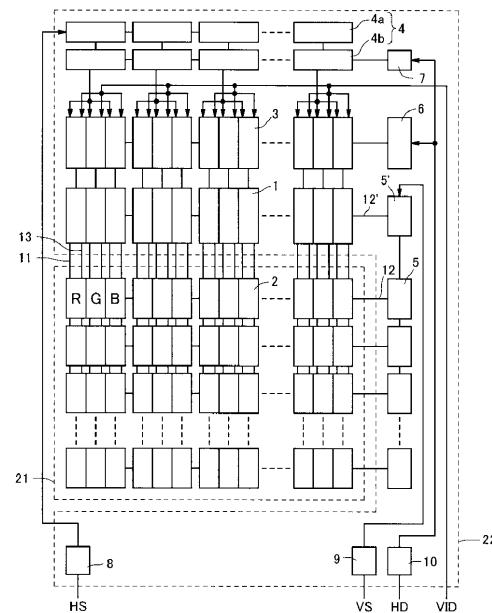

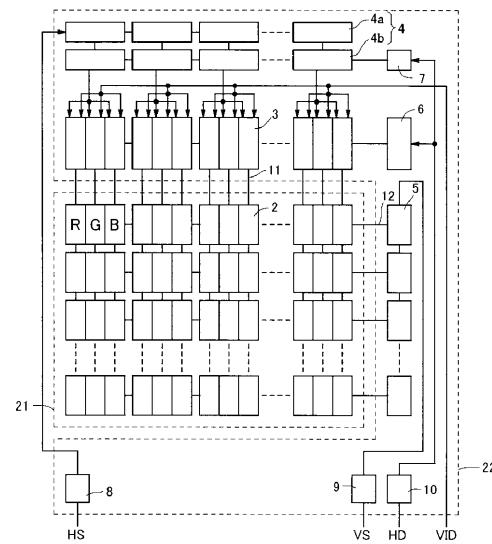

図4に、電流設定方式でカラー画像表示を行うEL表示装置の一例の表示パネルのプロック図を示す。本表示装置は、該表示パネルの外部に、該表示パネルに入力する、列走査制御信号、行走査制御信号、水平同期信号、映像信号といった信号を制御するための制御装置を備えている。

## 【0005】

図中、2は画素回路、3は列制御回路、4はシフトレジスタ、4aはレジスタ、4bはサンプリング信号発生回路、5はシフトレジスタ、6、7はゲート回路、8～10は入力回路、11はデータ線、12は走査線、21は画像表示部、22は駆動回路である。

## 【0006】

図4の表示パネルにおいて、画像表示部21は複数の画素回路2を複数行、複数列に配置し、各行の画素回路2を共通に走査線12に接続し、各列の画素回路2を共通にデータ線11に接続している。尚、行方向にR(赤)、G(緑)、B(青)をそれぞれ発光するEL素子を備えた3個の画素2を一組として、画像の最小表示単位とする。

## 【0007】

入力された映像情報VIDは、映像信号Videoと基準信号REFからなり、RGBの情報を備えており、画素列の表示色に応じた色の情報が列制御回路3に入力される。列制御信号HSはクロック信号と列走査開始信号からなり、入力回路8においてレベル変換された後、各画素列に対応して配置されたシフトレジスタ4のレジスタ4aに入力される。

## 【0008】

水平同期信号 H D は、入力回路 1 0 においてレベル変換された後、ゲート回路 6 、 7 に入力され、各ゲート回路 6 、 7 よりそれぞれ制御信号が出力され、列制御回路 3 とサンプリング信号発生回路 4 b に入力される。

## 【0009】

レジスタ 4 a は、入力された列制御信号 H S によりシフトパルスを出力し、後段のサンプリング信号発生回路 4 b は入力されたシフトパルスと制御信号によりサンプリング信号を発生する。サンプリング信号発生回路 4 b から出力されたサンプリング信号は、各画素列に対応して配置された列制御回路 3 に入力される。

## 【0010】

列制御回路 3 においては、入力された制御信号及びサンプリング信号により、映像信号 V i d e o より所定の画素回路 2 の電圧信号をサンプルホールドし、電流信号 i ( d a t a ) をデータ線 1 1 に出力する。

## 【0011】

行制御信号 V S はクロック信号と行走査開始信号とからなり、入力回路 9 においてレベル変換された後、シフトレジスタ群に送られ、シフトレジスタ 5 より走査線 1 2 に順次、走査信号が出力される。

## 【0012】

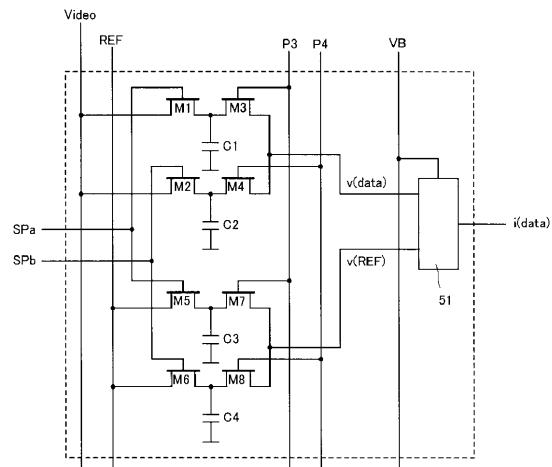

図 5 に、電流設定方式の E L 表示装置において、水平画素数と同数配列される列制御回路 3 の回路構成例を示す。図中、 5 1 は電圧電流変換回路、 M 1 ~ M 8 は n 型薄膜トランジスタ ( T F T ) であり、 C 1 ~ C 4 は容量、 P 3 , P 4 は制御信号、 V B は基準電流設定バイアス、 S P a , S P b はサンプリング信号である。尚、以下の説明において、トランジスタのソース、ドレイン、ゲートをそれぞれ、 / S 、 / D 、 / G と記載する。

## 【0013】

映像信号 V i d e o は M 1 / S 、 M 2 / S に入力され、基準信号 R E F は M 5 / S 、 M 6 / S に入力される。サンプリング信号発生回路 4 b より各列に出力されたサンプリング信号は S P a 及び S P b よりなり、 S P a は列制御回路 3 の M 1 / G 、 M 5 / G に、 S P b は M 2 / G 、 M 6 / G に入力される。 M 1 / D 、 M 2 / D 、 M 5 / D 、 M 6 / D にはそれぞれ容量 C 1 、 C 2 、 C 3 、 C 4 の一端が接続されるとともに、 M 3 / S 、 M 4 / S 、 M 7 / S 、 M 8 / S が接続されている。ゲート回路 6 より入力された制御信号 P 3 、 P 4 は、 P 3 が M 3 / G 、 M 7 / G に入力され、 P 4 が M 4 / G 、 M 8 / G に入力される。 M 3 / D と M 4 / D 、及び、 M 7 / D と M 8 / D はそれぞれ接続されて、各出力 v ( d a t a ) 及び v ( R E F ) が電圧電流変換回路 5 1 に入力される。電圧電流変換回路 5 1 には、基準電流設定バイアス V B が入力され、各画素回路 2 に供給される電流信号 i ( d a t a ) が出力される。

## 【0014】

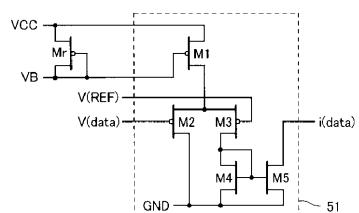

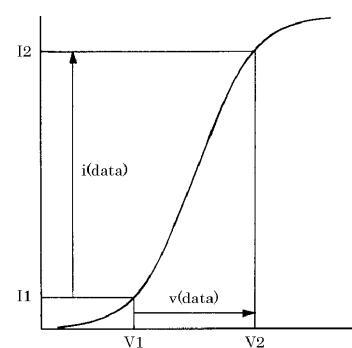

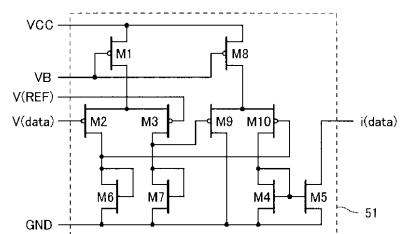

図 7 に、電圧電流変換回路 5 1 の回路構成例を示す。図中、 M r 、 M 1 ~ M 3 は p 型 T F T 、 M 4 , M 5 は n 型 T F T 、 V C C は電源である。当該回路の基本的動作は一般的であるので説明を省略するが、留意すべき点は、省電力を目指す E L 表示装置において、例えば 2 0 0 p p i のパネルを想定すると、各画素の E L 素子への注入電流が小さく、最大電流で 1  $\mu$  A を大きく下回り、 1 0 0 n A を想定していることである。この条件で、可能な限り線形な電圧電流変換特性を得るために、 M 2 、 M 3 のゲート領域の W / L 比を小さくして、電流駆動能力を小さくしておく必要がある。図 8 に、当該回路の電圧電流変換特性を示す。図 7 の回路では、最小電圧 V 1 ( 黒レベル ) における最小電流 I 1 ( 黒電流 ) をゼロにする設計が難しい。黒電流 I 1 をゼロにできないと、表示装置として重要なコントラストが確保できなくなる。

## 【0015】

この点に関して対策を講じた回路構成例を図 9 に示す。図中、 M 1 ~ M 3 , M 8 ~ M 9 は p 型 T F T , M 4 ~ M 7 は n 型 T F T である。図 9 の回路において、第 1 のソースカッフル回路 M 2 , M 3 の各ドレイン端子に、おののソースが接地され、ドレインとゲート

が短絡されたM 6 , M 7 のドレインが接続されている。さらに、ソースが電源V C Cに接続され、ゲートに基準電流バイアスV Bが入力されて第2の基準電流源として動作するM 8を設け、M 8 / Dを第2のソースカップル回路M 9 , M 1 0のソースに接続し、M 9 / GをM 7 / Dに、M 1 0 / GをM 6 / Dにそれぞれ接続する。そして、M 1 0 / Dから図7の電圧電流変換回路と同様に、M 4及びM 5のカレントミラー回路を介して電流信号i (data)を出力する。

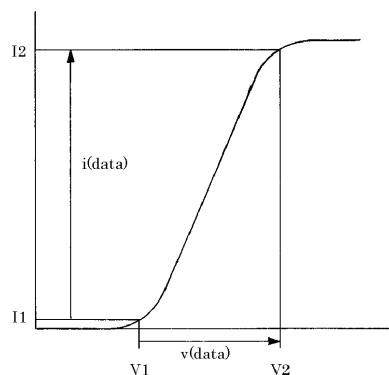

## 【0016】

図9の回路において、M 6及びM 7の電流駆動能力をM 9及びM 1 0より小さくするため、M 6及びM 7のゲート領域のW / L比をM 9及びM 1 0のゲート領域のW / L比より小さくしておく。このように設計された電圧電流変換回路の電圧電流変換特性を図10に示す。当該回路においては、電圧電流変換特性の線形性を崩すことなく、黒レベルV 1における黒電流I 1を小さくすることができる。

## 【0017】

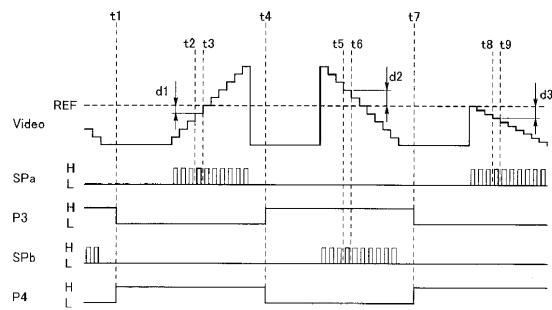

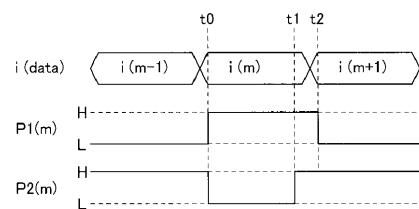

図5の列制御回路3の動作を図6のタイムチャートで説明する。

## 【0018】

時刻t 1において、制御信号P 3は「L」レベルに、P 4は「H」レベルに変化する。この時点では、M 3とM 7はオフ、M 4とM 8がオンである。時刻t 1～t 4の映像信号V videoの有効期間において、サンプリング信号S P aが発生し、時刻t 2～t 3において該当列のS P aが発生し、M 1とM 5がオンとなり(M 2とM 6はオフのまま)、この時点の映像信号V video及び基準信号R E Fが容量C 1及びC 3にサンプリングホールドされる。時刻t 4において、制御信号P 3は「H」レベルに、P 4は「L」レベルに変化し、M 3とM 7がオン、M 4とM 8がオフとなる。その結果、C 1, C 3にホールドされた信号がM 3, M 7を介してv (data)、v (R E F)として出力され、電圧電流変換回路5 1にそれぞれ入力され、その差d 1 = {v (data) - v (E E F)}に基づいて、電流信号i (data)が出力される。

## 【0019】

また、時刻t 4～t 7の映像信号V videoの有効期間において、サンプリング信号S P bが発生し、時刻t 5～t 6において該当列のS P bが発生し、M 2とM 6がオンとなり(M 1とM 5はオフのまま)、この時点の映像信号V video及び基準信号R E Fが容量C 2及びC 4にサンプリングホールドされる。時刻t 7において、制御信号P 3は「L」レベルに、P 4は「H」レベルに変化し、M 4とM 8がオン、M 3とM 7がオフとなる。その結果、C 2, C 4にホールドされた信号がM 4, M 8を介してv (data)、v (R E F)として出力され、電圧電流変換回路5 1にそれぞれ入力され、その差d 2 = {v (data) - v (E E F)}に基づいて、電流信号i (data)が出力される。

## 【0020】

以上の動作を繰り返すことにより、電流信号i (data)は、映像信号V videoの水平走査周期ごとに更新される線順次信号に変換される。

## 【0021】

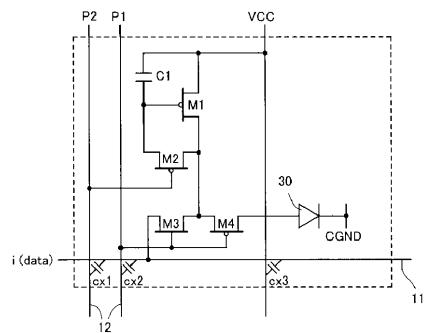

図11に電流設定方式の画素回路2の回路構成例を示す。図中、M 1, M 2, M 4はp型T F T, M 3はn型T F T, 3 0はE L素子、P 1, P 2は走査信号、V C Cは電源である。図12のタイムチャートにより当該回路の動作を説明する。

## 【0022】

時刻t 0以前において、該当m行のP 1は「L」レベル、P 2は「H」であるので、M 2及びM 3はともにオフであり、M 4がオンである。よって、容量C 1及びM 1のゲート容量に保持された充電電圧によって決定されたM 1 / G電圧によって、E L素子3 0に電流が注入され、これに応じてE L素子3 0は発光している。時刻t 0において、該当m行のP 1は「H」レベルに、P 2は「L」レベルに変化すると同時に、m行目の電流データi (m)が確定する。これにより、M 2及びM 3がオンとなると同時に、M 4がオフとなり、該当m行のE L素子3 0への電流注入は停止して該当m行のE L素子3 0は消灯する。さらに、M 2に電流信号i (m)が供給されるため、これに応じてM 2 / G電圧が設定

され、容量  $C_1$  及び  $M_1$  のゲート容量が充電される。電流信号  $i_{data}$  が確定している時刻  $t_1$  において、 $P_2$  は再び「H」に変化して  $M_2$  がオフとなり、 $M_1/G$  電圧の設定動作が終了して保持動作に移行する。時刻  $t_2$  において、 $P_1$  が「L」レベルに変化して  $M_1$  への電流供給を停止するとともに、 $M_4$  がオンとなって  $M_1/G$  電圧で設定された  $M_1/D$  電流が  $EL$  素子  $30$  に注入され、これに応じて  $EL$  素子  $30$  は再設定されたレベルで発光を開始し、次に再び設定されるまで当該発光を継続する。

【0023】

図11の電流設定方式の画素回路2は、各トランジスタのスレッシュ電圧  $V_{th}$  及び電流駆動係数 のばらつきに影響されず、 $M_1$  の出力電流は電流信号  $i_{data}$  により所望の値になり、安定した画像がパネル上に再現できる。

10

【0024】

図11の回路において、電流信号  $i_{data}$  は、走査信号  $P_1, P_2$  が入力される走査線と交差するため、各々寄生容量  $c_{x1}$  及び  $c_{x2}$  が存在し、加えて、電源  $V_{CC}$  との交差によって寄生容量  $c_{x3}$  が存在する。そのため、図12のチャートにおいて、時刻  $t_0 \sim t_1$  における  $M_2$  の駆動電流を設定するための容量  $C_1$  への充電動作を考慮する必要がある。時刻  $t_0 \sim t_1$  において、 $M_2/G$  に付加される容量  $C_{sum1}$  は下記式により示される。

【0025】

$$C_{sum1} = C_1 + N \times (c_{x1} + c_{x2} + c_{x3}) \quad \dots (1)$$

【0026】

上記式(1)において、 $N$  は画像表示部21の垂直画素数(画素行数)である。例えば、表示パネルがQVGA(320×240)サイズとすると、 $N = 240$ である。図11の画素回路を所望動作するためには、電流信号  $i_{data}$  によって容量  $C_1$  だけでなく、寄生容量  $c_{x1} \sim c_{x3}$  を含んだ容量  $C_{sum1}$  を充電する必要がある。

20

【0027】

【特許文献1】米国特許第6373454号明細書

【発明の開示】

【発明が解決しようとする課題】

【0028】

$EL$  表示装置においては、電流設定方式の画素回路によって、安定した画像が表示できるが、下記に示す課題を有していた。

30

【0029】

各画素回路2に含まれる $EL$ 素子は、アノード電極とカソード電極間にホール輸送層、発光層、電子輸送層を重ねた構造をしている。ホール輸送層、発光層、電子輸送層は各々厚さが数百程度の非常に薄い薄膜で構成されている。そのため、全 $EL$ 素子に対してリーク電流を抑えることは製造上非常に難しく、リーク電流が存在した場合には、 $EL$ 素子が所望の発光輝度を得られず、表示画像に影響を及ぼす恐れがある。

【0030】

本発明の課題は、上記問題を解決し、リーク電流の影響を抑えて、各画素において所望の発光輝度を得、高画質な画像表示を安定して実現することにある。

40

【課題を解決するための手段】

【0031】

本発明は、画素回路を複数個マトリクス配置し、各行の画素回路を共通に走査線に接続し、各列の画素回路を共通にデータ線に接続してなる画像表示部を備え、走査線を順次選択すると同時に、選択した行の各画素の表示に応じたレベルの電流信号を当該画素が接続されたデータ線に印加して表示を行う $EL$ 表示装置において、

各画素回路は、該当列のデータ線に一端が接続された第1のスイッチと、該第1のスイッチの他端にドレインが接続され、ソースが電源に接続された電流駆動トランジスタ、該第1のスイッチの他端に入力端子が接続された $EL$ 素子、該電流駆動トランジスタのゲートに一端が接続された第2のスイッチを有し、

50

各列のデータ線の画素回路前段に、データ線電圧を入力とするソースホロワ回路を設け、該ソースホロワ回路の出力端子と該当列の画素回路の第2のスイッチの他端を共通に補助データ線に接続したことを特徴とするEL表示装置である。

【0032】

本発明のEL表示装置において、上記ソースホロワ回路が電流源を含み、該電流源の電流値は所定期間にデータ線に供給される電流信号に対応していることを、好ましい態様として含む。

【発明の効果】

【0033】

本発明によれば、リーク電流によるEL素子の発光量誤差を大幅に減少させることができ、EL表示装置において、高画質な画像を安定して表示することができる。

【発明を実施するための最良の形態】

【0034】

図1は、本発明のEL素子の一実施形態の表示パネルのブロック図であり、先に説明した図4の表示パネルと同様の部材、動作については説明を省略し、図4の表示パネルとの差異について説明する。図中、1は電圧バッファ回路、5'はシフトレジスタ、12'は走査線、13は補助データ線である。

【0035】

本発明の表示パネルにおいては、画素回路2の前段にデータ線電圧を入力とするソースホロワ回路を設ける。本実施形態においては、該ソースホロワ回路として、各画素列に電圧バッファ回路1を配置しており、該電圧バッファ回路1と該当列の画素回路2が補助データ線13で接続されている。また、各画素回路2に行毎に走査信号を発生するシフトレジスタ5の前段には、電圧バッファ回路1を制御する制御信号を出力するために、シフトレジスタ5'と走査線12'が追加されている。

【0036】

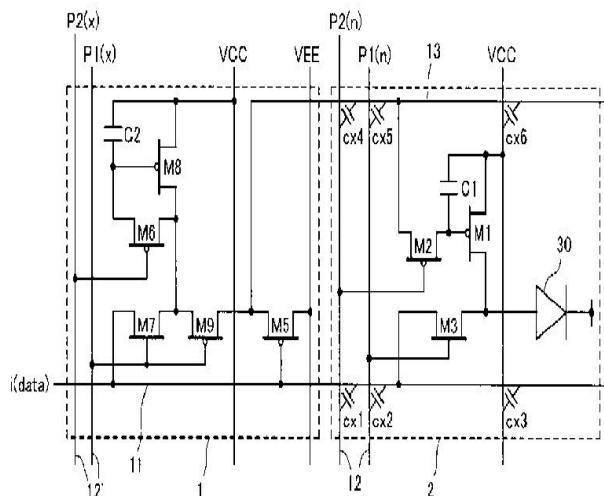

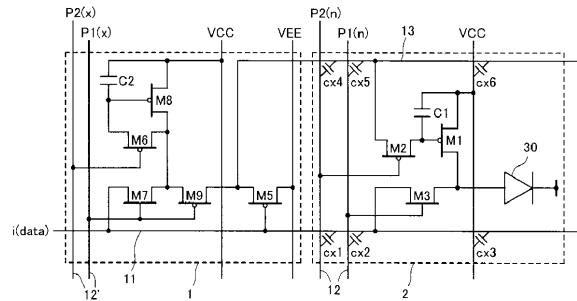

図2に、図1の表示パネルの電圧バッファ回路1と該当列の画素回路2の構成を示す。図中、M1, M2, M5, M6, M8, M9はp型TFT、M3, M7はn型TFT、C1, C2は容量、P1(x), P2(x)は電圧バッファ回路1に入力される制御信号である走査信号、P1(n), P2(n)はn行目の画素回路2に入力される走査信号、VCC, VEEは電源である。

【0037】

画素回路2は、画素行数だけ配置される。画素回路2には、走査線12より走査信号P1(n), P2(n)が入力され、データ線11より列制御回路3から出力された電流信号i(data)が入力される。画素回路2は、第1のスイッチとしてM3を、電流駆動トランジスタとしてM1を、第2のスイッチとしてM2を有しており、M3/Sはデータ線11に接続されている。また、M3/DはEL素子30の入力端子に接続されると同時に、M1/Dに接続されている。M1/Sは電源VCCに接続され、M1/GにはC1の一端と、P2(n)で制御されるM2/Dが接続される。C1の他端は電源VCCに接続されており、M2/Sは補助データ線13に接続されている。

【0038】

電圧バッファ回路1においては、M5/Gがデータ線11に接続されており、M5/Sは補助データ線13に接続されている。加えて、P1(x)で制御されるM7/Sがデータ線11に接続され、M7/DはM8/D及びP1(x)で制御されるM9/Sに接続されている。M8/Sは電源VCCに接続され、M8/Gは一端が電源VCCに接続されたC2の他端と、P2(x)で制御されるM6/Sが接続され、M6/DはM8/Dに接続されている。N9/DはM5/Sに接続され、M5/Dは電源VEEに接続されている。当該構成により、M5がM9から供給される所定電流によってソースホロワ回路が構成される。

【0039】

図2の画素回路2においては、データ線11に供給された電流信号i(data)を、

10

20

30

40

50

P1(n), P2(n)によってM1に電流設定し、該当EL素子30に次回の電流設定まで電流供給することができる。図2の回路構成では、各行の画素電流設定動作時において、データ線11に寄生する容量から各画素回路2の保持容量C1が除かれる。このことは、特に、データ線11に供給される電流信号が小さいときの電流設定動作に対して有効になる。

【0040】

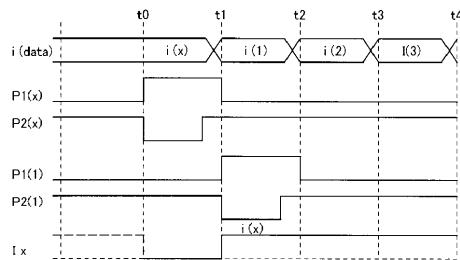

図2の回路における電流設定動作を、図3のタイムチャートにより説明する。図3中のIxはM9からM5に供給される電流である。

【0041】

1行目の画素の電流設定期間t1～t2の前に、期間t0～t1を設ける。期間t0～t1において、データ線11に供給される電流信号をi(x)としておくことにより、P1(x), P2(x)によってM8に電流i(x)が設定される。上記i(x)は映像信号Videoの垂直プランキング期間における信号レベルで容易に設定できる。

【0042】

1行目の画素の電流設定開始時刻t1からM9を介してM5にi(x)が供給され、M5はソースホロワ動作が可能になる。時刻t1から開始される各行の画素電流信号設定動作において、ソースホロワ動作のため、該当列のn行電流信号i(n)がM1に発生するための、補助データ線13の電圧と等しい駆動電圧M1/Gを得るように、データ線11の電圧は駆動電圧M1/Gよりも、M5のVgs(ゲート/ソース間電圧)だけ低下することになる。EL素子30のカソード電極電圧CGNDを適切に設定すると、EL素子30の発光電圧を下回り、EL素子30は消灯状態となるとともに絶縁された誘電体状態となる。該当EL素子30にリーク電流Iが存在すると、M1に流れる電流はおおむねIが加算された{i(n) + I}となる。

【0043】

P1(n)が「L」に、P2(n)が「H」になると、n行目の画素の電流設定動作が終了し、該当EL素子30に電流注入が開始され、EL素子30はリーク電流Iを除いた所望の電流I(n)で発光を開始する。

【0044】

各画素回路2において、カソード電極電圧CGNDの設定による、画素電流設定動作期間でのEL素子の消灯及び誘電体状態、及び、発光動作期間における電流駆動トランジスタM1のVgsの確保は容易に実現できる。該当列の画素回路2のM1のしきい値電圧Vth及び駆動係数のばらつき、各EL素子30の動作電圧ばらつき及び変動に対しても容易にカソード電極電圧CGNDを設定することができる。画素電流設定動作において誘電体状態のEL素子30の容量がデータ線11に追加されるが、画素回路2では、データ線11に寄生する容量から保持容量C1が除かれるため、従来の図4で示す表示パネルに比較して遜色のない書き込み動作が実現する。基準電流書き込み動作のための、P1(x), P2(x)はシフトレジスタ5の前段に追加したシフトレジスタ5'を用いずに、別途制御出力しても構わない。

【0045】

尚、図2の回路において、各トランジスタのn型、p型、P1(x), P2(x), P1(n), P2(n)の信号極性及びEL素子30の接続は、図2の構成に限定されるものでなく、適宜選択することができる。

【図面の簡単な説明】

【0046】

【図1】本発明のEL素子の一実施形態の表示パネルのブロック図である。

【図2】図1の表示パネルの電圧バッファ回路と該当列の画素回路の構成を示す図である。

【図3】図2の回路のタイムチャートである。

【図4】従来のEL素子の一例の表示パネルのブロック図である。

【図5】電流設定方式のEL表示装置における列制御回路の回路構成例を示す図である。

10

20

30

40

50

【図6】図5の列制御回路のタイムチャートである。

【図7】電圧電流変換回路の回路構成例を示す図である。

【図8】図7の電圧電流変換回路の電圧電流特性を示す図である。

【図9】電圧電流変換回路の他の回路構成例を示す図である。

【図10】図9の電圧電流変換回路の電圧電流特性を示す図である。

【図11】電流設定方式の画素回路の回路構成例を示す図である。

【図12】図11の画素回路のタイムチャートである。

【符号の説明】

【0047】

1 電圧バッファ回路

10

2 画素回路

3 列制御回路

4 シフトレジスタ

4 a レジスタ

4 b サンプリング信号発生回路

5、5' シフトレジスタ

6、7 ゲート回路

8~10 入力回路

11 データ線

12、12' 走査線

20

21 画像表示部

22 駆動回路部

30 E L素子

51 電圧電流変換回路

H D 水平同期信号

H S 列制御信号

i (data) 電流信号

M 1~M 10 トランジスタ

P 1、P 2 走査信号

P 3、P 4 制御信号

30

R E F 基準信号

S P a、S P b サンプリング信号

V B 基準電流設定バイアス

V C C 電源

V I D 映像情報

V i d e o 映像信号

V S 行制御信号

【 図 1 】

【 図 2 】

【 図 3 】

【 図 4 】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

---

フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 05 B 33/14

A

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2005165095A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2005-06-23 |

| 申请号            | JP2003405641                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2003-12-04 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 川崎素明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 川崎 素明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.D G09G3/20.623.A G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB08 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080 /AA06 5C080/BB05 5C080/CC03 5C080/DD10 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC31 3K107/EE04 3K107 /HH05 5C380/AA01 5C380/AB06 5C380/AB09 5C380/AB34 5C380/BA10 5C380/BA19 5C380/BA36 5C380/BA38 5C380/BA39 5C380/BA45 5C380/BB02 5C380/BB23 5C380/CA02 5C380/CA08 5C380 /CA13 5C380/CA16 5C380/CA17 5C380/CA24 5C380/CA51 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CC13 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC53 5C380/CC63 5C380/CD013 5C380 /CD014 5C380/CE08 5C380/CF06 5C380/CF07 5C380/CF12 5C380/CF22 5C380/CF24 5C380/CF31 5C380/CF43 5C380/DA02 5C380/DA06 5C380/DA49 |         |            |

| 代理人(译)         | 渡边圭佑<br>山口 芳広                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

解决的问题：在电流设定型EL显示装置中，通过减少漏电流的影响，获得良好的发光亮度，以实现具有高质量图像的图像显示。在电流设定型像素电路(2)的前面设有电压缓冲电路(1)，在像素电流设定期之前，将提供给数据线(11)的规定的电流信号*i*(*x*)设定为M8。在像素电流设置时段中，M5的源极跟随器操作将像素电路2的电流驱动晶体管M1设置为允许泄漏电流影响的电流值。[选择图]图2