(19) 日本国特許庁(JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2005-78073

(P2005-78073A)

(43) 公開日 平成17年3月24日(2005.3.24)

(51) Int. C1.<sup>7</sup>

G09 F 9/30

H05B 33/14

F |

GO9F

G09F

H05B 33/14

### テーマコード（参考）

3K007

5C094

- 1 -

審査請求 有 請求項の数 18 O.L. (全 11 頁)

(21) 出願番号 特願2004-207155 (P2004-207155)

(22) 出願日 平成16年7月14日 (2004. 7. 14)

(31) 優先権主張番号 2003-060016

(32) 優先日 平成15年8月28日 (2003. 8. 28)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 590002817

三星エスディアイ株式会社

大韓民国京畿道水原市靈通区▲しん▼洞5

75番地

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100095500

弁理士 伊藤 正和

(72) 発明者 朴商一

大韓民国ソウル市陽川区新亭4洞983-

12号

(72) 発明者 姜泰旭

大韓民国京畿道城南市盆唐区盆塘洞セッピ

ヨルマウルウバンアパート302棟110

3号

(54) 【発明の名称】有機電界発光表示装置

(57) 【要約】

【課題】ソース/ドレーン電極の過エッチング現象を防止し、アレイ部とパッド部との間の平坦化膜の厚さの差を除去する。

【解決手段】画素が配置されるアレイ部（A）と、外部電源と接触するパッド部（P）とが定義された基板上において、ソース/ドレーン電極（107a, 107b）を含む半導体構造物上に形成され、アレイ部（A）及びパッド部（P）におけるソース/ドレーン電極（107a, 107b）の所定の領域を露出させるビアホール200を備え、アレイ部（A）とパッド部（P）との間の前記ビアホール200の周辺の厚さが同一な平坦化膜（108, 109）；ビアホール200内に埋められた導電体層110；導電体層110を含む平坦化膜112の上部の全面に形成され、アレイ部（A）の導電体層110の所定の領域を露出させる画素領域112を備えた隔壁111；及び画素領域112に形成された有機EL層：を含む。

### 【選択図】図2

**【特許請求の範囲】****【請求項 1】**

画素が配置されるアレイ部と、外部電源と接触するパッド部とが定義された基板上において、ソース/ドレーン電極を含む半導体構造物上に形成され、前記アレイ部及びパッド部におけるソース/ドレーン電極の所定の領域を露出させるビアホールを備え、前記アレイ部とパッド部との間の前記ビアホールの周辺の厚さが同一な平坦化膜と、

前記ビアホール内に埋められた導電体層と、

前記導電体層を含む平坦化膜の上部の全面に形成され、前記アレイ部の導電体層の所定の領域を露出させる画素領域を備えた隔壁と、

前記画素領域に形成された有機EL層と、

を有することを特徴とする有機電界発光表示装置。

**【請求項 2】**

前記パッド部のビアホールの下部には、基板、ゲート絶縁膜、ゲート電極、層間絶縁膜、ソース/ドレーン電極が順に積層され、

前記アレイ部のビアホールの下部には、基板、ゲート絶縁膜、ダミーゲートパターン、層間絶縁膜、ソース/ドレーン電極が順に積層されることを特徴とする請求項1に記載の有機電界発光表示装置。

**【請求項 3】**

前記ダミーゲートパターンは前記ゲート電極と同時に形成されて、同一物質からなり、同一な厚さを有することを特徴とする請求項2に記載の有機電界発光表示装置。

**【請求項 4】**

前記アレイ部のビアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース/ドレーン電極が順に積層され、

前記パッド部のビアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース/ドレーン電極が順に積層されることを特徴とする請求項1に記載の有機電界発光表示装置。

**【請求項 5】**

前記平坦化膜は、均一な厚さを有し、下部の表面段差を露出する第1絶縁膜と、前記第1絶縁膜上に形成され、上面が平坦な第2絶縁膜とを有することを特徴とする請求項1に記載の有機電界発光表示装置。

**【請求項 6】**

前記アレイ部のソース/ドレーン電極の下部には、下部ソース領域及び下部ドレーン領域が各々連結されるように形成されることを特徴とする請求項1に記載の有機電界発光表示装置。

**【請求項 7】**

前記下部ソース領域及び下部ドレーン領域は、多結晶シリコン層の両側の縁に不純物がドーピングされることによって各々形成されたものであり、前記下部ソース領域及び下部ドレーン領域の間の多結晶シリコン層はチャンネル領域であることを特徴とする請求項6に記載の有機電界発光表示装置。

**【請求項 8】**

前記ゲート電極及びソース/ドレーン電極は金属物質からなることを特徴とする請求項1に記載の有機電界発光表示装置。

**【請求項 9】**

前記基板は絶縁物質からなり、

前記基板と多結晶シリコン層との界面と、前記基板とゲート絶縁膜との界面に形成された遮断層をさらに有することを特徴とする請求項7に記載の有機電界発光表示装置。

**【請求項 10】**

画素が配置されるアレイ部と、外部電源と接触するパッド部とが定義された基板上において、半導体構造物上に形成され、前記アレイ部とパッド部との間の上面の高さが同一なソース/ドレーン電極と、

前記ソース/ドレーン電極を含む半導体構造物上に形成され、前記アレイ部及びパッド

10

20

30

40

50

部におけるソース / ドレーン電極の所定の領域を露出させるピアホールを備えた平坦化膜と、

前記ピアホール内に埋められた導電体層と、

前記導電体層を含む平坦化膜の上部の全面に形成され、前記アレイ部の導電体層の所定の領域を露出させる画素領域を備えた隔壁と、

前記画素領域に形成された有機EL層と、

を有することを特徴とする有機電界発光表示装置。

#### 【請求項 1 1】

前記パッド部のピアホールの下部には、基板、ゲート絶縁膜、ゲート電極、層間絶縁膜、ソース / ドレーン電極が順に積層され、

前記アレイ部のピアホールの下部には、基板、ゲート絶縁膜、ダミーゲートパターン、層間絶縁膜、ソース / ドレーン電極が順に積層されることを特徴とする請求項 1 0 に記載の有機電界発光表示装置。

#### 【請求項 1 2】

前記ダミーゲートパターンは前記ゲート電極と同時に形成されて、同一物質からなり、同一な厚さを有することを特徴とする請求項 1 1 に記載の有機電界発光表示装置。

#### 【請求項 1 3】

前記アレイ部のピアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース / ドレーン電極が順に積層され、

前記パッド部のピアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース / ドレーン電極が順に積層されることを特徴とする請求項 1 0 に記載の有機電界発光表示装置。

#### 【請求項 1 4】

前記平坦化膜は、均一な厚さを有し、下部の表面段差を露出する第 1 絶縁膜と、前記第 1 絶縁膜上に形成され、上面が平坦な第 2 絶縁膜とを有することを特徴とする請求項 1 0 に記載の有機電界発光表示装置。

#### 【請求項 1 5】

前記アレイ部のソース / ドレーン電極の下部には、下部ソース領域及び下部ドレーン領域が各々連結されるように形成されることを特徴とする請求項 1 0 に記載の有機電界発光表示装置。

#### 【請求項 1 6】

前記下部ソース領域及び下部ドレーン領域は、多結晶シリコン層の両側の縁に不純物がドーピングされることによって各々形成されたものであり、前記下部ソース領域及び下部ドレーン領域の間の多結晶シリコン層はチャンネル領域であることを特徴とする請求項 1 5 に記載の有機電界発光表示装置。

#### 【請求項 1 7】

前記ゲート電極及びソース / ドレーン電極は金属物質からなることを特徴とする請求項 1 0 に記載の有機電界発光表示装置。

#### 【請求項 1 8】

前記基板は絶縁物質からなり、

前記基板と多結晶シリコン層との界面と、前記基板とゲート絶縁膜との界面に形成された遮断層をさらに有することを特徴とする請求項 1 6 に記載の有機電界発光表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は有機電界発光表示装置に係り、より詳しくは、アレイ部とパッド部との間のピアホールの周辺の平坦化膜の厚さの差を除去し、ソース / ドレーン電極の過エッチング現象が防止される、有機電界発光表示装置に関するものである。

##### 【背景技術】

##### 【0 0 0 2】

10

20

30

40

50

有機電界発光 (Electro Luminescent: 以下、便宜上 ‘EL’ とする) 表示装置は、電子注入電極 (cathode) と正孔注入電極 (anode) とから各々電子と正孔とを発光層の内部に注入し、このように注入された電子と正孔とが結合したエキシトン (exciton) が励起状態から基底状態にまで落ちる時に発光する原理を利用した素子である。

【0003】

このような原理によれば、従来の薄膜液晶表示装置とは異なって、別途の光源を必要としないので、素子の体積と重量とを減らすことができる長所がある。

【0004】

このような有機EL表示装置は、電流が流れる場合に、光を発する有機物質を画素別に分離してマトリックス状に配置しておき、これら有機物質に流れる電流の量を調節することによって画像を表示する。この有機EL表示装置は、低電圧駆動、軽量薄形、広視野角、及び高速応答などの長所により、次世代表示装置として期待されている。10

【0005】

有機EL表示装置は、通常、マトリックス状に配置されている複数の画素を含んでおり、各画素領域内には、スイッチング及び駆動素子である薄膜トランジスタ、画素電極、及び有機EL層などの多くの薄膜パターンが形成されている。

【0006】

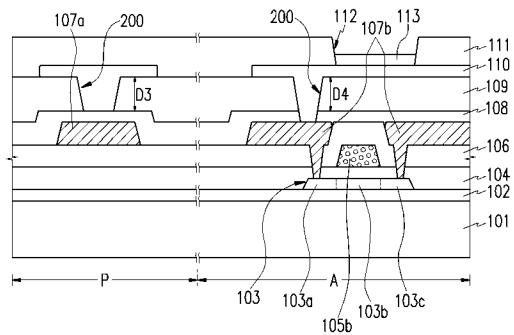

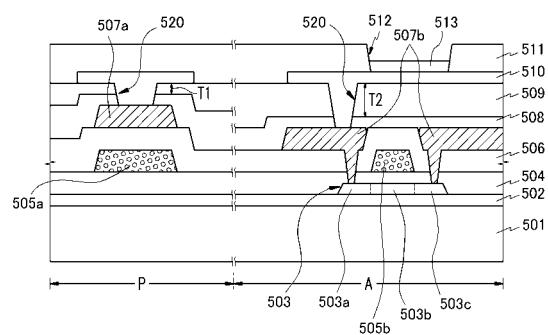

図4は、従来の有機EL表示装置を示した断面図である。図4には、画素が形成される領域であるアレイ (array) 部 (A) と、有機ELパネルの縁に位置し、外部電源と接触する回路パッド部 (P) とが共に示されている。20

【0007】

その構造を具体的に見てみると、まず、絶縁基板 501 上には、 $\text{SiO}_2$  などからなる遮断層 502 が形成されており、この遮断層 502 上には、所定の幅で多結晶シリコン層 503 が形成されている。20

【0008】

多結晶シリコン層 503 には、不純物が高濃度にドーピングされたソース領域 503a 及びドレーン領域 503c があり、ソース領域 503a とドレーン 503cとの間はチャネル領域 503b となる。

【0009】

多結晶シリコン層 503 を含む遮断層 502 の上部の全面には、 $\text{SiO}_2$  又は  $\text{Si}_3\text{N}_4$  などからなるゲート絶縁膜 504 が形成されている。30

【0010】

ゲート絶縁膜 504 上には、Alなどの金属からなるゲート電極 505a、505b が所定の幅で形成されており、ゲート電極 505a、505b を含むゲート絶縁膜 504 上には、層間絶縁膜 506 が形成されている。

【0011】

層間絶縁膜 506 上には、ソース領域 503a 及びドレーン領域 503c と連結されるように、Alなどの金属からなるソース/ドレーン電極 507a、507b が形成されており、ソース/ドレーン電極 507a、507b 上には、上面を平坦化させる平坦化膜 508、509 が形成されている。40

【0012】

ソース/ドレーン電極 507a、507b と連結されるように平坦化膜 508、509 が選択的にエッティングされており、エッティングされた部分には、ビア埋立層 510 が形成されており、その上には、隔壁 511 が形成されており、隔壁 511 の所定の領域が選択的にエッティングされて、画素領域 512 を形成している。

【0013】

このような従来の有機EL表示装置において、前記平坦化膜 508、509 は、第1絶縁層 508 をまず薄く形成した後、表面段差 (topology) を除去するために、上面の平坦な第2絶縁層 509 を厚く形成する。この時、第1絶縁層 508 は、その下の構造で用いられた一般的な絶縁膜と同様に、下部構造から均一な厚さに形成されて、下部構造の表面50

段差をそのまま露出するが、第2絶縁層509は下部構造の表面段差を除去して、ウエハーの全領域にわたって平坦な上面を有する。

#### 【0014】

このように、平坦化膜508、509が絶縁基板501の全領域にわたって平坦な上面を有するのは、その後のビアホール520の形成のための写真エッチング工程のために必須として要求される。

#### 【0015】

平坦化膜508、509の形成後には、ソース/ドレーン電極507a、507bを露出させるビアホール520を形成するが、この時、ビアホール520は、アレイ部(A)では画素電極を下部の金属と連結し、パッド部(P)ではパッド電極を下部の金属と連結する。

#### 【0016】

ところが、平坦化膜508、509は、下部構造の表面段差によって厚さの差が生じる。つまり、平坦化膜508、509の下部には、ソース/ドレーン電極だけが存在することもでき、ソース/ドレーン電極、及びゲート電極が存在することもでき、又はソース/ドレーン電極、ゲート電極及び多結晶シリコン層が全て存在することもできるなど、位置又は構造によって表面段差が生じる。

#### 【0017】

特に、アレイ部(A)とパッド部(P)との間では、平坦化膜508、509の厚さの差が必ず生じる。このような平坦化膜の厚さの差により、ビアホール520の形成のためのエッチングの深さが、アレイ部(A)とパッド部(P)との間で差が生じるようになる。

#### 【0018】

図4に示されているように、第2絶縁層509のエッチングの厚さが、パッド部(P)ではT1であり、アレイ部(A)ではT2であって、T1がT2より小さい値を有する。つまり、均一な厚さを有する第1絶縁層508を除けば、ビアホールの形成のためのエッチングの深さは、アレイ部(A)とパッド部(P)との間で、T2からT1を引いた値の分だけ差が生じる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0019】

このように、ビアホール520の形成のためのエッチングの深さの差が大きくなる場合、アレイ部(A)に位置するソース/ドレーン電極507bが露出されるまで厚い平坦化膜508、509をエッチングする間に、パッド部(P)の薄い平坦化膜508、509をエッチングし、その下部のソース/ドレーン電極507aを露出させた後にも、ソース/ドレーン電極507aをエッチングし続け、結果的に、過エッチングする(overetched)現象がたびたび発生するという問題点がある。

#### 【0020】

このようなパッド部(P)のソース/ドレーン電極を過エッチングする現象は、ビアホールの形成のための平坦化膜のエッチングの深さの差が3000以上である時にさらに甚だしくなり、このような過エッチングにより、コンタクトが不良となる問題点がある。

#### 【0021】

したがって、平坦化膜の厚さの差によってビアホールの形成工程で発生するソース/ドレーン電極の過エッチング現象を防止することが切実に要請される。

#### 【0022】

本発明が目的とする技術的課題は、ソース/ドレーン電極の過エッチング現象を防止することである。

本発明の他の技術的課題は、アレイ部とパッド部との間の平坦化膜の厚さの差を除去することである。

#### 【課題を解決するための手段】

10

20

30

40

50

## 【0023】

このような課題を解決するために、本発明では、アレイ部のソース/ドレーン電極の下部にダミーゲートパターンを形成することにより、アレイ部の平坦化膜の厚さを減らしてパッド部の平坦化膜の厚さと同一にしたり、又はパッド部の下部のゲート電極を除去して、パッド部の平坦化膜を厚くしてアレイ部の平坦化膜の厚さと同一にする。

## 【0024】

つまり、本発明による有機EL表示装置は、画素が配置されるアレイ部と、外部電源と接觸するパッド部とが定義された基板上において、ソース/ドレーン電極を含む半導体構造物上に形成され、アレイ部及びパッド部におけるソース/ドレーン電極の所定の領域を露出させるビアホールを備え、アレイ部とパッド部との間のビアホールの周辺の厚さが同一な平坦化膜；ビアホール内に埋められた導電体層；導電体層を含む平坦化膜の上部の全面に形成され、アレイ部の導電体層の所定の領域を露出させる画素領域を備えた隔壁；及び画素領域に形成された有機EL層；を含む構成である。10

## 【0025】

また、本発明による有機EL表示装置は、画素が配置されるアレイ部と、外部電源と接觸するパッド部とが定義された基板上において、半導体構造物上に形成され、アレイ部とパッド部との間の上面の高さが同一なソース/ドレーン電極；ソース/ドレーン電極を含む半導体構造物上に形成され、アレイ部及びパッド部におけるソース/ドレーン電極の所定の領域を露出させるビアホールを備えた平坦化膜；ビアホール内に埋められた導電体層；導電体層を含む平坦化膜の上部の全面に形成され、アレイ部の導電体層の所定の領域を露出させる画素領域を備えた隔壁；及び画素領域に形成された有機EL層；を含む構成である。20

## 【0026】

この時、パッド部のビアホールの下部には、基板、ゲート絶縁膜、ゲート電極、層間絶縁膜、ソース/ドレーン電極が順に積層され、アレイ部のビアホールの下部には、基板、ゲート絶縁膜、ダミー(dummy)ゲートパターン、層間絶縁膜、ソース/ドレーン電極が順に積層される。

## 【0027】

ダミーゲートパターンはゲート電極と同時に形成されて、同一物質からなり、同一な厚さを有することができる。アレイ部のビアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース/ドレーン電極が順に積層され、パッド部のビアホールの下部には、基板、ゲート絶縁膜、層間絶縁膜、ソース/ドレーン電極が順に積層される。平坦化膜は、均一な厚さを有し、下部の表面段差を露出する第1絶縁膜と、第1絶縁膜上に形成され、上面が平坦な第2絶縁膜とを含むことができる。アレイ部のソース/ドレーン電極の下部には、下部ソース及び下部ドレーンが各々連結されるように形成される。下部ソース及び下部ドレーンは、多結晶シリコン層の両側の縁に不純物がドーピングされることによって各自形成されたものであり、下部ソース及び下部ドレーンの間の多結晶シリコン層はチャンネル領域であるのが好ましい。ゲート電極及びソース/ドレーン電極は金属物質からなることができる。基板は絶縁物質からなり、基板と多結晶シリコン層との界面と、基板とゲート絶縁膜との界面に形成された遮断層をさらに含むことができる。30

## 【発明の効果】

## 【0028】

本発明では、アレイ部においてダミーゲートパターンを形成したり、又はパッド部においてゲート電極を除去することによって、アレイ部とパッド部との間の平坦化膜の厚さの差を除去し、したがって、ソース/ドレーン電極の過エッチング現象を防止する効果がある。

## 【発明を実施するための最良の形態】

## 【0029】

添付した図面を参照して、本発明の実施例について、本発明が属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様40

な相異する形態で実現することができ、ここで説明する実施例に限定されない。

【実施例 1】

【0030】

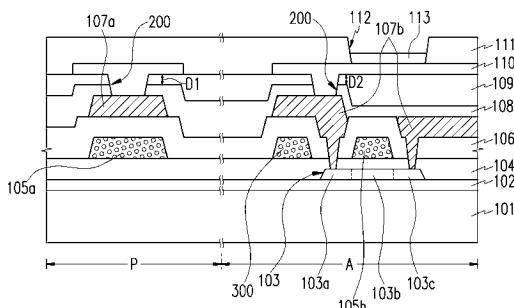

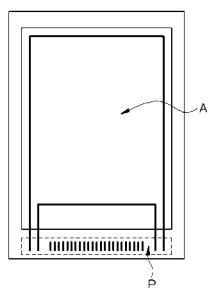

図1は、本発明による有機EL表示装置を概略的に示した平面図であり、図2は、本発明の第1実施例による有機EL表示装置を示した断面図である。

【0031】

図示されているように、本発明の有機EL表示装置は、そのパネル上に大きく画素が形成される領域であるアレイ部(A)と、前記パネルの縁に位置して、外部から前記有機EL表示装置が有する電源供給ライン、スキャン及びデータラインの駆動に必要な電気信号を前記各ラインに印加するパッドが形成される領域であるパッド部(P)とを含む。

【0032】

本発明の第1実施例による有機EL表示装置は、図2に示されているように、絶縁基板101上にはSiO<sub>2</sub>などからなる遮断層102が形成されており、この遮断層102上には、所定の幅の多結晶シリコン層103が形成されている。

【0033】

多結晶シリコン層103の両側の縁には、n型又はp型の不純物イオンが高濃度にドーピングされて、下部ソース領域103a及び下部ドレーン領域103cを形成し、下部ソース領域103aと下部ドレーン領域103cとの間は、電子又は正孔が移動するチャネル領域103bとなる。

【0034】

多結晶シリコン層103を含む遮断層102の上部の全面には、SiO<sub>2</sub>又はSi<sub>3</sub>N<sub>4</sub>などからなるゲート絶縁膜104が形成されている。この時、多結晶シリコン層103の厚さにより、多結晶シリコン層の上部に位置するゲート絶縁膜104が周辺より高いが、多結晶シリコン層の厚さが薄いために、これに起因した段差は無視できる程度の水準であるので、説明の便宜上、図面には段差を示していない。

【0035】

ゲート絶縁膜104上には、Alなどの金属からなるゲート電極105a、105b及びダミーゲートパターン300が所定の幅で形成されており、ゲート電極105a、105b及びダミーゲートパターン300を含むゲート絶縁膜104上には、層間絶縁膜106が形成されている。

【0036】

この時、ダミーゲートパターン300及びゲート電極105a、105bは、同一な蒸着及び写真エッチング工程でパターニングされて同時に形成されるのが好ましく、したがって、この二つは同一物質からなり、同一の厚さを有するのが好ましい。

【0037】

ダミーゲートパターン300は、その後ビアホールが形成される領域の下部に位置し、これは、アレイ部(A)におけるビアホール周辺の平坦化膜の厚さ、つまりビアホールの形成のためのエッチングの深さをパッド部(P)と同一な水準に下げるために、意図的に形成したものである。前記ダミーゲートパターン300の模様は特定の形状に限定されず、製作可能であればいかなる形状でもよい。

【0038】

パッド部(P)に形成されたゲート電極105aは、ビアホールを介して外部電源と電気的に接続するパッド電極に該当するソース/ドレーン電極107aの接触抵抗を下げる役割を果たす。

【0039】

層間絶縁膜106は下部構造の表面段差をそのまま露出する。つまり、ダミーゲートパターン300及びゲート電極105a、105bの上部の高さがその周辺よりさらに高く形成されている。

【0040】

このような層間絶縁膜106上には、Alなどの金属からなる所定の幅のソース/ドレ

10

20

30

40

50

ーン電極 107a、107b が形成されているが、パッド部 (P) では、ソース / ドレーン電極 107a がゲート電極 105a と連結されるように形成され (図示せず)、アレイ部 (A) では、ソース / ドレーン電極 107b が多結晶シリコン層の下部ソース領域 103a 及びドレーン領域 103c と連結されるように形成されている。

#### 【0041】

ソース / ドレーン電極 107a、107b を含む層間絶縁膜 106 の上部の全面には、上面を平坦化させる平坦化膜 108、109 が形成されている。

#### 【0042】

平坦化膜には、まず、下部構造の表面段差をそのまま露出する第 1 絶縁膜 108 が均一な厚さに形成されており、その上に、上面が平坦な第 2 絶縁膜 109 が形成されている。このように平坦化膜 108、109 がウエハーの全領域にわたって平坦な上面を有するのは、その後のビアホール 200 の形成のためのパターニング工程のために必須として要求される。

#### 【0043】

平坦化膜 108、109 は、選択的にエッチングされてソース / ドレーン電極 107a、107b の所定の領域を露出させるビアホール 200 を含んでおり、その上には、ビアホール 200 を埋める導電体層 110 が形成されている。

#### 【0044】

この時、ビアホール 200 は、アレイ部 (A) では画素電極を下部の金属と連結し、パッド部 (P) ではパッド電極を下部の金属と連結する。

#### 【0045】

この時、ビアホール 200 の周辺の平坦化膜 108、109 は、アレイ部 (A) とパッド部 (P) との間ににおいて、同一の厚さを有し、したがって、ビアホール 200 の形成のための平坦化膜 108、109 のエッチングの深さは同一である。

#### 【0046】

これを従来の図 4 と比較してみると、従来は、T1 と T2 とが互いに異なっていたのに比べて、本発明では、均一な第 1 絶縁膜 108 の厚さを除いて、残る第 2 絶縁膜 109 の厚さのパッド部 (P) におけるエッチングの深さ D1 とアレイ部 (A) におけるエッチングの深さ D2 とが同一である。

#### 【0047】

これを言い換えれば、パッド部 (P) におけるビアホール 200 の周辺の平坦化膜の厚さが、アレイ部 (A) におけるビアホール 200 の周辺の平坦化膜の厚さと同一ということである。

#### 【0048】

したがって、ビアホール 200 の形成のための平坦化膜 108、109 のエッチング時に、パッド部 (P) 及びアレイ部 (A) において同一の時点で各々ソース / ドレーン電極 107a、107b が露出されるので、従来のパッド部 (P) におけるソース / ドレーン電極の過エッチングは防止することができる。

#### 【0049】

導電体層 110 及び平坦化膜 109 上には、隔壁 111 が形成されており、隔壁 111 の所定の領域が選択的にエッチングされて、画素領域 112 を形成しており、画素領域 112 には、有機 E L 層 113 が形成される。

#### 【実施例 2】

#### 【0050】

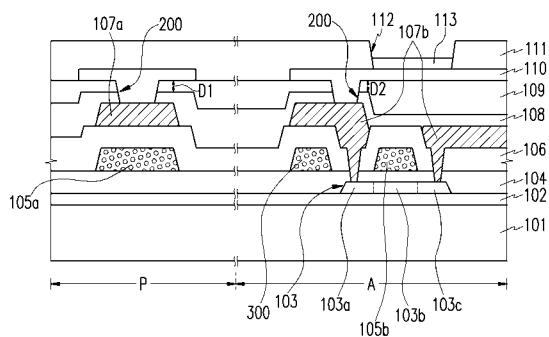

次に、本発明の第 2 実施例について、図 3 を参照して説明する。

#### 【0051】

アレイ部 (A) にダミーゲートパターン 300 を形成した第 1 実施例とは異なって、第 2 実施例では、パッド部 (P) のゲート電極 (図 2 における 105a) を除去したことが特徴である。

#### 【0052】

10

20

30

40

50

つまり、第2実施例では、パッド部(P)のゲート電極を除去して表面段差を小さくすることにより、パッド部(P)とアレイ部(A)との間のビアホールの周辺での平坦化膜の厚さの差を除去した。

#### 【0053】

このように、第2実施例では、第1絶縁膜108の厚さを除いて、残る第2絶縁膜109の厚さのパッド部(P)におけるエッチングの深さD3とアレイ部(A)におけるエッチングの深さD4とが互いに同一である。そして、これを第1実施例の場合と比較してみると、D3はD1よりは大きい。

#### 【0054】

以上で、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されるのではなく、本発明の請求の範囲で定義している本発明の基本概念を利用した当業者のいろいろな変形及び改良形態もまた、本発明の権利範囲に属する。10

#### 【図面の簡単な説明】

#### 【0055】

【図1】本発明による有機EL表示装置のアレイ部とパッド部を説明するために示した概略図である。

【図2】本発明の第1実施例による有機EL表示装置を示した断面図である。

【図3】本発明の第2実施例による有機EL素子を示した断面図である。

【図4】従来の有機EL表示装置を示した断面図である。

#### 【符号の説明】

#### 【0056】

101 絶縁基板

102 遮断層

103 多結晶シリコン層

104 ゲート絶縁膜

105a、105b ゲート電極

106 層間絶縁膜

107a、107b ソース/ドレーン電極

108、109 平坦化膜

111 隔壁

30

112 画素領域

200 ビアホール

103a 下部ソース領域

103c 下部ドレーン領域

110 導電体層

113 有機EL層

300 ダミーゲートパターン

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

F ターム(参考) 3K007 BA06 DB03 GA00

5C094 AA42 AA43 BA03 BA29 CA19 DB04

|                |                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示器                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2005078073A</a>                                                                                                                                                   | 公开(公告)日 | 2005-03-24 |

| 申请号            | JP2004207155                                                                                                                                                                    | 申请日     | 2004-07-14 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                    |         |            |

| [标]发明人         | 朴商一<br>姜泰旭                                                                                                                                                                      |         |            |

| 发明人            | 朴商一<br>姜泰旭                                                                                                                                                                      |         |            |

| IPC分类号         | H01L51/50 G09F9/30 H01L21/77 H01L21/84 H01L27/32 H05B33/22 H05B33/14                                                                                                            |         |            |

| CPC分类号         | H01L27/3248 H01L27/124 H01L27/1248 H01L27/3223 H01L27/3244 H01L27/3276                                                                                                          |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H05B33/14.A G09F9/30.365 H01L27/32                                                                                                                  |         |            |

| F-TERM分类号      | 3K007/BA06 3K007/DB03 3K007/GA00 5C094/AA42 5C094/AA43 5C094/BA03 5C094/BA29 5C094/CA19 5C094/DB04 3K107/AA01 3K107/BB01 3K107/CC45 3K107/DD89 3K107/DD90 3K107/EE03 3K107/EE46 |         |            |

| 代理人(译)         | 三好秀<br>伊藤雅一                                                                                                                                                                     |         |            |

| 优先权            | 1020030060016 2003-08-28 KR                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                       |         |            |

### 摘要(译)

要解决的问题：通过防止源/漏电极的过蚀刻现象来消除阵列部分和焊盘部分之间的平坦化膜的厚度差异。解决方案：有机电致发光显示装置包括平坦化膜（108和109），其在设置有阵列部分（A）的基板上的包括源极/漏极（107a和107b）的半导体结构上形成通孔200，具有像素和与外部电源接触以暴露阵列部分（A）和焊盘部分（P）中的源/漏电极（107a和107b）的规定区域并且厚度相同的焊盘部分（P）（A）和焊盘部分（P）之间的通孔200的周边的厚度；填充在通孔200内的导体层110；形成在包括导体层110的平坦化膜的上部的整个表面上并且设置有像素区域112以暴露阵列部分（A）的导体层110的规定区域的分隔物111；以及形成在像素区域112中的有机EL层。