(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-246204

(P2004-246204A)

(43) 公開日 平成16年9月2日(2004.9.2)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611H

5C080

G09G 3/20

624B

G09G 3/20

641D

HO5B 33/14

A

審査請求 未請求 請求項の数 40 O L (全 35 頁)

(21) 出願番号

特願2003-37256 (P2003-37256)

(22) 出願日

平成15年2月14日 (2003.2.14)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 湯本 昭

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内F ターム(参考) 3K007 AB05 AB17 BA06 DB03 GA04

5C080 AA06 BB05 DD05 EE28 EE29

FF11 JJ02 JJ03 JJ04

(54) 【発明の名称】画素回路、表示装置、および画素回路の駆動方法

## (57) 【要約】

【課題】画素内部の能動素子のしきい値のばらつきによらず、安定かつ正確に各画素の発光素子に所望の値の電流を供給でき、高品位な画像を表示することが可能な画素回路および表示装置を提供する。

【解決手段】駆動用 TFT 31 のソースと電源電位 V<sub>D</sub><sub>D</sub>間に接続され駆動線 D R V L 31 により導通制御される TFT 32 と、TFT 31 のソースとノード ND 31 間に接続されオートゼロ線 A Z L 31 により導通制御される TFT 33 と、TFT 31 のゲートと所定電位 V<sub>p</sub><sub>c</sub>間に接続されオートゼロ線 A Z L 31 により導通制御される TFT 35 と、データ線 D T L 31 とノード ND 31 間に接続され走査線 S C N L 33 1 により導通制御される TFT 34 と、ノード ND 31 と TFT 31 のゲート間に接続された結合キャパシタ C 31 を有し、OLED 36 が TFT 31 のドレインと基準電位 GND との間に接続されている。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、

少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、

少なくとも第1の制御線と、

ノードと、

第1および第2の基準電位と、

所定のプリチャージ電位と、

第1端子と第2端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給

10

ラインを流れる電流を制御する駆動トランジスタと、

上記駆動トランジスタの第1端子に接続された第1のスイッチと、

上記駆動トランジスタの第1端子と上記ノードとの間に接続された第2のスイッチと、

上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第3

のスイッチと、

上記データ線と上記ノードとの間に接続され、上記第1の制御線によって導通制御される

第4のスイッチと、

上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を

有し、

上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン

20

、上記第1のスイッチ、および上記電気光学素子が直列に接続されている

画素回路。

**【請求項 2】**

上記ノードに保持容量が接続されている

請求項1記載の画素回路。

**【請求項 3】**

上記所定のプリチャージ電位は上記データ線を通して供給される

請求項1記載の画素回路。

**【請求項 4】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記

30

第3のスイッチが第3の制御線により導通制御される

請求項1記載の画素回路。

**【請求項 5】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制

御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される

請求項1記載の画素回路。

**【請求項 6】**

上記電気光学素子を駆動する場合、

第1ステージとして、上記第2の制御線および上記第3の制御線により上記第1のスイッ

チ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、

所定時間経過後に上記第3の制御線により上記第2のスイッチおよび上記第3のスイッチ

40

が非導通状態に保持され、

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記

データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導

通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上

記電気光学素子に上記データ信号に応じた電流を供給する

請求項4記載の画素回路。

**【請求項 7】**

上記電気光学素子を駆動する場合、

10

20

30

40

50

第1ステージとして、上記第2の制御線、上記第3の制御線、および上記第4の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチが非導通状態に保持された後、上記第4の制御線により上記第3のスイッチが非導通状態に保持され、

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する 10

請求項5記載の画素回路。

**【請求項8】**

流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、

少なくとも輝度情報に応じた信号が供給されるデータ線と、

少なくとも第1の制御線と、

第1および第2の基準電位と、

所定のプリチャージ電位と、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと第1の基準電位との間に接続された第1のスイッチと、

上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、

上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、

上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続されている 30

画素回路。

**【請求項9】**

上記ノードに保持容量が接続されている

請求項8記載の画素回路。

**【請求項10】**

上記所定のプリチャージ電位は上記データ線を通して供給される

請求項8記載の画素回路。

**【請求項11】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記第3のスイッチが第3の制御線により導通制御される 40

請求項8記載の画素回路。

**【請求項12】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される

請求項8記載の画素回路。

**【請求項13】**

上記電気光学素子を駆動する場合、

第1ステージとして、上記第2の制御線および上記第3の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、

10

20

30

40

50

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチおよび上記第3のスイッチが非導通状態に保持され、

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する

請求項11記載の画素回路。

**【請求項14】**

上記電気光学素子を駆動する場合、

第1ステージとして、上記第2の制御線、上記第3の制御線、および上記第4の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチが非導通状態に保持された後、上記第4の制御線により上記第3のスイッチが非導通状態に保持され、

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する

請求項12記載の画素回路。

**【請求項15】**

上記プリチャージ電位は、上記第1の基準電位から上記電界効果トランジスタのしきい値の絶対値を減じた値より小さい値に設定されている

請求項13記載の画素回路。

**【請求項16】**

上記プリチャージ電位は、上記第1の基準電位から上記電界効果トランジスタのしきい値の絶対値を減じた値より小さい値に設定されている

請求項14記載の画素回路。

**【請求項17】**

流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、

少なくとも輝度情報に応じた信号が供給されるデータ線と、

少なくとも第1の制御線と、

第1および第2の基準電位と、

所定のプリチャージ電位と、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第1のスイッチと、

上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、

上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、

上記電気光学素子は上記第1のスイッチと第2の基準電位との間に接続されている画素回路。

10

20

30

40

50

**【請求項 18】**

上記ノードに保持容量が接続されている

請求項 17 記載の画素回路。

**【請求項 19】**

上記所定のブリッジ電位は上記データ線を通して供給される

請求項 17 記載の画素回路。

**【請求項 20】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記第3のスイッチが第3の制御線により導通制御される

請求項 17 記載の画素回路。 10

**【請求項 21】**

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される

請求項 17 記載の画素回路。

**【請求項 22】**

上記電気光学素子を駆動する場合、

第1ステージとして、上記第2の制御線および上記第3の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチおよび上記第3のスイッチが非導通状態に保持され、 20

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する

請求項 20 記載の画素回路。

**【請求項 23】**

上記電気光学素子を駆動する場合、

第1ステージとして、上記第2の制御線、上記第3の制御線、および上記第4の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、 30

第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチが非導通状態に保持された後、上記第4の制御線により上記第3のスイッチが非導通状態に保持され、

第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、

第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する 40

請求項 21 記載の画素回路。

**【請求項 24】**

上記ブリッジ電位は、上記電気光学素子のしきい値と上記電界効果トランジスタのしきい値とを足し合わせた値より大きい値に設定されている

請求項 22 記載の画素回路。

**【請求項 25】**

上記ブリッジ電位は、上記電気光学素子のしきい値と上記電界効果トランジスタのしきい値とを足し合わせた値より大きい値に設定されている

請求項 23 記載の画素回路。

**【請求項 26】**

50

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、

上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第1の制御線と、

第1および第2の基準電位と、

所定のプリチャージ電位と、を有し、

上記各画素回路は、

ノードと、

第1端子と第2端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給

ラインを流れる電流を制御する駆動トランジスタと、

上記駆動トランジスタの第1端子に接続された第1のスイッチと、

上記駆動トランジスタの第1端子と上記ノードとの間に接続された第2のスイッチと、

上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第3

のスイッチと、

上記データ線と上記ノードとの間に接続され、上記第1の制御線によって導通制御される

第4のスイッチと、

上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を

有し、

上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン

、上記第1のスイッチ、および上記電気光学素子が直列に接続されている

表示装置。

#### 【請求項27】

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記

第3のスイッチが第3の制御線により導通制御される

請求項26記載の表示装置。

#### 【請求項28】

上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制

御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される

請求項26記載の表示装置。

#### 【請求項29】

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、

上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第1の制御線と、

第1および第2の基準電位と、

所定のプリチャージ電位と、を有し、

上記各画素回路は、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと第1の基準電位との間に接続され、上記第1の制御

線により導通制御される第1のスイッチと、

上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、

上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のス

イッチと、

上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第

4のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、

を有し、

上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続

されている

10

20

30

40

50

表示装置。

【請求項 3 0】

上記第 1 のスイッチが第 2 の制御線により導通制御され、上記第 2 のスイッチおよび上記第 3 のスイッチが第 3 の制御線により導通制御される

請求項 2 9 記載の表示装置。

【請求項 3 1】

上記第 1 のスイッチが第 2 の制御線により導通制御され、上記第 2 のスイッチが第 3 の制御線により導通制御され、上記第 3 のスイッチが第 4 の制御線により導通制御される

請求項 2 9 記載の表示装置。

【請求項 3 2】

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、

上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第 1 の制御線と、第 1 および第 2 の基準電位と、

所定のプリチャージ電位と、を有し、

上記各画素回路は、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第 1 のスイッチと、

上記電界効果トランジスタのソースと上記ノードとの間に接続された第 2 のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第 3 のスイッチと、

上記データ線と上記ノードとの間に接続され、上記第 1 の制御線により導通制御される第 4 のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、

上記電気光学素子は上記第 1 のスイッチと第 2 の基準電位との間に接続されている表示装置。

【請求項 3 3】

上記第 1 のスイッチが第 2 の制御線により導通制御され、上記第 2 のスイッチおよび上記第 3 のスイッチが第 3 の制御線により導通制御される

請求項 3 2 記載の表示装置。

【請求項 3 4】

上記第 1 のスイッチが第 2 の制御線により導通制御され、上記第 2 のスイッチが第 3 の制御線により導通制御され、上記第 3 のスイッチが第 4 の制御線により導通制御される

請求項 3 2 記載の表示装置。

【請求項 3 5】

流れる電流によって輝度が変化する電気光学素子と、

第 1 端子と第 2 端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給ラインを流れる電流を制御する駆動トランジスタと、

ノードと、

上記駆動トランジスタの第 1 端子に接続された第 1 のスイッチと、

上記駆動トランジスタの第 1 端子と上記ノードとの間に接続された第 2 のスイッチと、

上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第 3 のスイッチと、

上記データ線と上記ノードとの間に接続された第 4 のスイッチと、

上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を有し、

10

20

30

40

50

上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン、上記第1のスイッチ、および上記電気光学素子が直列に接続されている画素回路の駆動方法であって、

上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、

上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、

上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、

上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップと

を有する画素回路の駆動方法。

**【請求項 3 6】**

上記第2のステップにおいて、上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する際、上記第2のスイッチを非導通状態に保持した後、上記第3のスイッチを非導通状態に保持する

請求項35記載の画素回路の駆動方法。

**【請求項 3 7】**

流れる電流によって輝度が変化する電気光学素子と、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと第1の基準電位との間に接続された第1のスイッチと、

上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと所定の電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続された第4のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、

上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続されている画素回路の駆動方法であって、

上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、

上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、

上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、

上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップと

を有する画素回路の駆動方法。

**【請求項 3 8】**

上記第2のステップにおいて、上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する際、上記第2のスイッチを非導通状態に保持した後、上記第3のスイッチを非導通状態に保持する

請求項37記載の画素回路の駆動方法。

**【請求項 3 9】**

流れる電流によって輝度が変化する電気光学素子と、

電界効果トランジスタと、

ノードと、

上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第1のスイッチと、

10

20

30

40

50

上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと所定の電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続された第4のスイッチと、

上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、

上記電気光学素子は上記第1のスイッチと第2の基準電位との間に接続されている画素回路の駆動方法であって、

上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、

上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、

10

上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、

上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップと

を有する画素回路の駆動方法。

#### 【請求項 40】

上記第2のステップにおいて、上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する際、上記第2のスイッチを非導通状態に保持した後、上記第3のスイッチを非導通状態に保持する

20

請求項 39 記載の画素回路の駆動方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、有機EL( E l e c t r o l u m i n e s c e n c e )ディスプレイなどの、電流値によって輝度が制御される電気光学素子を有する画素回路、並びにこの画素回路がマトリクス状に配列された画像表示装置のうち、特に各画素内部に設けられた絶縁ゲート型電界効果トランジスタによって電気光学素子に流れる電流値が制御される、いわゆるアクティブマトリクス型画像表示装置に関するものである。

##### 【0002】

##### 【従来の技術】

画像表示装置、たとえば液晶ディスプレイなどでは、多数の画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像を表示する。

これは有機ELディスプレイなどにおいても同様であるが、有機ELディスプレイは各画素回路に発光素子を有する、いわゆる自発光型のディスプレイであり、液晶ディスプレイに比べて画像の視認性が高い、バックライトが不要、応答速度が速い、等の利点を有する。

また、各発光素子の輝度はそれに流れる電流値によって制御される、すなわち発光素子が電流制御型であるという点で液晶ディスプレイなどとは大きく異なる。

##### 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とが可能であるが、前者は構造が単純であるものの、大型かつ高精細のディスプレイの実現が難しいなどの問題があるため、各画素内部の発光素子に流れる電流を、画素内部に設けた能動素子(一般にはTFT:Thin Film Transistor、薄膜トランジスタ)によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

40

##### 【0004】

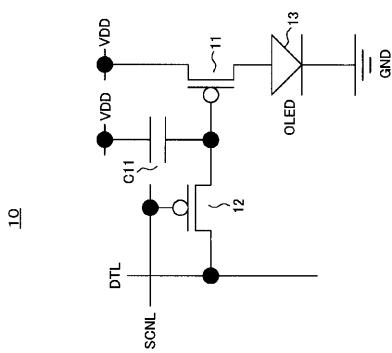

図1は、アクティブマトリクス型有機ELディスプレイにおける画素回路の構成例を示す回路図である(たとえば特許文献1、2参照)。

図1の画素回路10は、pチャネル薄膜電界効果トランジスタ(以下、TFTという)

1 50

1およびTFT12、キャパシタC11、発光素子である有機EL素子OLED13を有する。また、図1において、DTLはデータ線を、SCNLは走査線をそれぞれ示している。

有機EL素子は多くの場合整流性があるため、OLED(Organic Light Emission Diode)と呼ばれることがあり、図1その他では発光素子としてダイオードの記号を用いているが、以下の説明においてOLEDには必ずしも整流性を要求するものではない。

図1ではTFT11のソースが電源電位V<sub>DD</sub>に接続され、発光素子13のカソード(陰極)は接地電位GNDに接続されている。図1の画素回路10の動作は以下の通りである。

10

#### 【0005】

##### ステップST1:

走査線SCNLを選択状態(ここでは低レベル)とし、データ線DTLに書き込み電位V<sub>data</sub>を印加すると、TFT12が導通してキャパシタC11が充電または放電され、TFT11のゲート電位はV<sub>data</sub>となる。

#### 【0006】

##### ステップST2:

走査線を非選択状態(ここでは高レベル)とすると、データ線DTLとTFT11とは電気的に切り離されるが、TFT11のゲート電位はキャパシタC11によって安定に保持される。

20

#### 【0007】

##### ステップST3:

TFT11および発光素子13に流れる電流は、TFT11のゲート・ソース間電圧V<sub>gs</sub>に応じた値となり、発光素子13はその電流値に応じた輝度で発光し続ける。

上記ステップST1のように、走査線SCNLを選択してデータ線に与えられた輝度情報を画素内部に伝える操作を、以下「書き込み」と呼ぶ。

上述のように、図1の画素回路10では、一度V<sub>data</sub>の書き込みを行えば、次に書き換えられるまでの間、発光素子13は一定の輝度で発光を継続する。

30

#### 【0008】

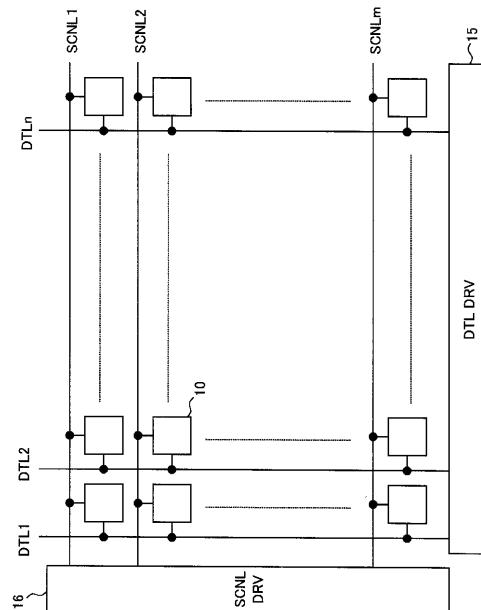

このような画素を図2のように、n×mのマトリクス状に多数配列し、走査線SCNL1～SCNLmを順次選択しながらデータ線DTL1～DTLnから書き込みを繰り返すことにより、アクティブマトリクス型画像表示装置を構成することができる。なお、図2において、各データ線DTL1～DTLnはデータ線駆動回路(DTLDRV)15により駆動され、各走査線SCNL1～SCNLmは走査線駆動回路(SCNLDRV)16により駆動される。

40

#### 【0009】

単純マトリクス型画像表示装置では、各発光素子は、選択された瞬間にのみ発光するのに対し、アクティブマトリクスでは、書き込み終了後も発光素子が発光を継続するため、単純マトリクスに比べて発光素子のピーク輝度、ピーク電流を下げられるなどの点で、とりわけ大型・高精細のディスプレイでは有利となる。

40

#### 【0010】

ところで、アクティブマトリクス型有機ELディスプレイにおいては、能動素子として一般にガラス基板上に形成されたTFT(Thin Film Transistor、薄膜電界効果トランジスタ)が利用される。

ところが、TFTは特性のばらつきが大きいことが良く知られている。特に、比較的大型のガラス基板上にポリシリコンTFTを形成する場合には、ガラス基板の熱変形等の問題を避けるため、通常、アモルファスシリコン膜の形成後、レーザアニール法によって結晶化が行われる。しかし、大きなガラス基板に均一にレーザエネルギーを照射することは難しく、ポリシリコンの結晶化の状態が基板内の場所によってばらつきを生ずることが避けられない。

50

この結果、同一基板上に形成した TFT でも、その V<sub>t h</sub> (しきい値) が画素によって数百 mV、場合によっては 1 V 以上ばらつくこともまれではない。

この場合、たとえば異なる画素に対して同じ電位 V<sub>d a t a</sub> を書き込んでも、画素によって TFT 11 のしきい値 V<sub>t h</sub> がばらつく結果、発光素子 (OLED) 13 に流れる電流 I<sub>d s</sub> は画素毎に大きくばらついて全く所望の値からはずれる結果となり、ディスプレイとして高い画質を期待することはできない。

#### 【0011】

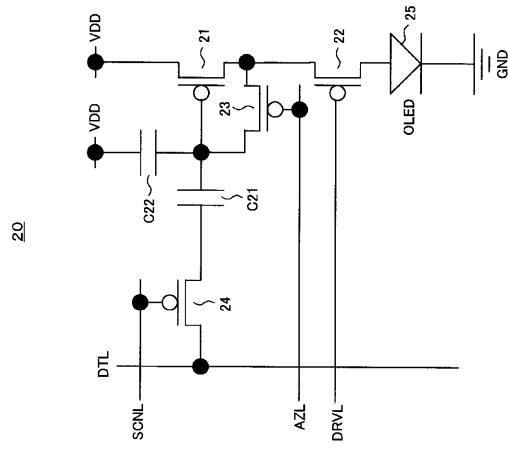

この問題を改善するため多数の画素回路が提案されているが、代表例を図 3 に示す（たとえば特許文献 3、または特許文献 4 参照）。

#### 【0012】

図 3 の画素回路 20 は、p チャネル TFT 21 ~ TFT 24、キャパシタ C21, C22、発光素子である有機 EL 素子 OLED 25 を有する。また、図 1 において、DTL はデータ線を、SCNL は走査線を、AZL はオートゼロ線を、DRV は駆動線をそれぞれ示している。

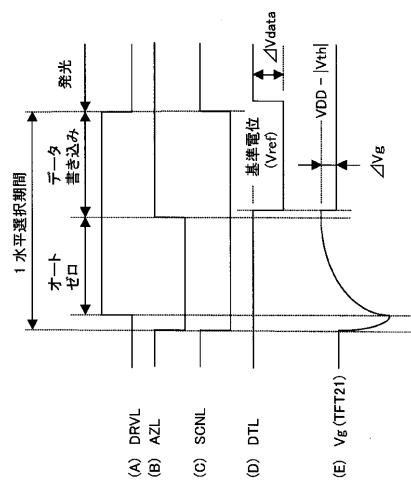

この画素回路 20 の動作について、図 4 に示すタイミングチャートを参照しながら以下に説明する。

#### 【0013】

##### ステップ ST 11 :

図 4 (A), (B) に示すように、駆動線 DRV 、オートゼロ線 AZL を低レベルとし、TFT 22 および TFT 23 を導通状態とする。このとき TFT 21 はダイオード接続された状態で発光素子 (OLED) 25 と接続されるため、TFT 21 に電流が流れる。

#### 【0014】

##### ステップ ST 12 :

図 4 (A) に示すように、駆動線 DRV を高レベルとし、TFT 22 を非導通とする。このとき走査線 SCNL は、図 4 (C) に示すように、低レベルで TFT 24 が導通状態とされ、データ線 DTL には、図 4 (D) に示すように、基準電位 V<sub>r e f</sub> が与えられる。TFT 21 に流れる電流が遮断されるため、図 4 (E) にしめすように TFT 21 のゲート電位 V<sub>g</sub> は上昇するが、その電位が V<sub>D D</sub> - |V<sub>t h</sub>| まで上昇した時点で TFT 21 は非導通状態となって電位が安定する。この動作を以後、「オートゼロ動作」と称することがある。

#### 【0015】

##### ステップ ST 13 :

図 4 (B), (D) に示すように、オートゼロ線 AZL を高レベルとして TFT 23 を非導通状態とし、データ線 DTL の電位を V<sub>r e f</sub> から V<sub>d a t a</sub> だけ低い電位とする。このデータ線電位の変化は、図 4 (E) に示すように、キャパシタ C21 を介して TFT 21 のゲート電位を V<sub>g</sub> だけ低下させる。

#### 【0016】

##### ステップ ST 14 :

図 4 (A), (C) に示すように、走査線 SCNL を高レベルとして TFT 24 を非導通状態とし、駆動線 DRV を低レベルとして TFT 22 を導通状態とすると、TFT 21 および発光素子 (OLED) 25 に電流が流れ、OLED が発光を開始する。

#### 【0017】

上記ステップ ST 13 で、寄生容量が無視できるとすれば、V<sub>g</sub> および TFT 21 のゲート電位 V<sub>g</sub> はそれぞれ次のようになる。

#### 【0018】

##### 【数 1】

$$V_g = V_{d a t a} \times C_1 / (C_1 + C_2) \quad \dots (1)$$

#### 【0019】

##### 【数 2】

$$V_g = V_{D D} - |V_{t h}| - V_{d a t a} \times C_1 / (C_1 + C_2) \dots (2)$$

10

20

30

40

50

## 【0020】

ここで、C1はキャパシタC21の容量値、C2はキャパシタC22の容量値をそれぞれ示している。

## 【0021】

一方、上記ステップST14で発光素子(OLED)25に流れる電流をIoledとすると、これはOLEDと直列に接続されるTFT21によって電流値が制御される。TFT21が飽和領域で動作すると仮定すれば、良く知られたMOSトランジスタの式および上記(2)式を用いて次の関係を得る。

## 【0022】

## 【数3】

$$\begin{aligned} I_{oled} &= \mu C_o x W / L / 2 (V_{DD} - V_g - |V_{th}|)^2 \\ &= \mu C_o x W / L / 2 (\Delta V_{data} \times C1 / (C1 + C2))^2 \\ &\dots (3) \end{aligned}$$

10

## 【0023】

ここで、 $\mu$ はキャリアの移動度、 $C_o x$ は単位面積当たりのゲート容量、Wはゲート幅、Lはゲート長をそれぞれ示している。

## 【0024】

(3)式によれば、IoledはTFT21のしきい値 $V_{th}$ によらず、外部から与えられる $V_{data}$ によって制御される。言い換えれば、図3の画素回路20を用いれば、画素毎にばらつくしきい値 $V_{th}$ の影響を受けず、電流の均一性、ひいては輝度の均一性が比較的高い表示装置を実現することができる。

20

## 【0025】

## 【特許文献1】

U S P 5 , 6 8 4 , 3 6 5

## 【特許文献2】

特開平8-234683号公報

## 【特許文献3】

U S P 6 , 2 2 9 , 5 0 6

30

## 【特許文献4】

特表2002-514320号公報のFIG.3

## 【0026】

## 【発明が解決しようとする課題】

上述のように、図1のような画素回路10を用いた場合、トランジスタのしきい値 $V_{th}$ のばらつきのため、画素間の輝度の均一性が損なわれ、高品位の表示装置を構成することは困難である。

## 【0027】

一方、図3の画素回路を用いれば、輝度の均一性が比較的高い表示装置を実現することが可能であるが、これには次のような問題がある。

40

## 【0028】

第1の問題は、外部から駆動するデータ振幅 $V_{data}$ に対し、駆動トランジスタのゲート振幅 $V_g$ は(1)式に従って減少する。逆に言えば、同じ $V_g$ を得るために大きな $V_{data}$ を与える必要があり、これは消費電力やノイズの点から望ましくない。

## 【0029】

第2の問題は、図3の画素回路20に関する上記動作説明は理想的なものであって、実際には、発光素子(OLED)25を駆動するTFT21の $V_{th}$ のばらつきの影響が無くなるわけではない。

これは、オートゼロ線AZLとTFT21のゲートノードがTFT23のゲート容量によって結合されており、オートゼロ線AZLが高レベルへ遷移してTFT23が非導通状態

50

となる過程において、TFT23のチャネル電荷がTFT21のゲートノードに流入するためである。この理由を次に説明する。

#### 【0030】

すなわち、オートゼロ動作終了後、TFT21のゲート電位は理想的には $VDD - |Vth|$ であるべきであるが、上記電荷の流入によって実際にはそれよりやや高い電位となり、なおかつこの電荷の流入量は $Vth$ の値によって変動する。なぜなら、オートゼロ動作終了直前におけるTFT21のゲート電位はほぼ $VDD - |Vth|$ である。したがって、この電位は $|Vth|$ がたとえば小さい程高い。

一方、オートゼロ動作終了時、オートゼロ線AZLの電位が上昇してTFT23が非導通に転ずる際、そのソース電位、すなわちTFT21のゲート電位が高い程、TFT23が非導通になるタイミングが遅れるため、より多くの電荷がTFT21のゲートに流入することになる。結果としてオートゼロ動作終了後のTFT21のゲート電位が $|Vth|$ の影響を受けるため、前述の(2)式や(3)式が厳密には成立せず、画素毎にばらつく $Vth$ の影響を受けることになる。

#### 【0031】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、画素内部の能動素子のしきい値のばらつきによらず、安定かつ正確に各画素の発光素子に所望の値の電流を供給でき、その結果として高品位な画像を表示することが可能な画素回路、表示装置、および画素回路の駆動方法を提供することにある。

#### 【0032】

##### 【課題を解決するための手段】

上記目的を達成するため、本発明の第1の観点は、流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、少なくとも第1の制御線と、ノードと、第1および第2の基準電位と、所定のプリチャージ電位と、第1端子と第2端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給ラインを流れる電流を制御する駆動トランジスタと、上記駆動トランジスタの第1端子に接続された第1のスイッチと、上記駆動トランジスタの第1端子と上記ノードとの間に接続された第2のスイッチと、上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線によって導通制御される第4のスイッチと、上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を有し、上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン、上記第1のスイッチ、および上記電気光学素子が直列に接続されている。

#### 【0033】

本発明の第2の観点は、流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、少なくとも輝度情報に応じた信号が供給されるデータ線と、少なくとも第1の制御線と、第1および第2の基準電位と、所定のプリチャージ電位と、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと第1の基準電位との間に接続された第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続されている。

#### 【0034】

本発明の第3の観点は、流れる電流によって輝度が変化する電気光学素子を駆動する画素回路であって、少なくとも輝度情報に応じた信号が供給されるデータ線と、少なくとも第1の制御線と、第1および第2の基準電位と、所定のプリチャージ電位と、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、

10

20

30

40

50

接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記第1のスイッチと第2の基準電位との間に接続されている。

## 【0035】

好適には、上記ノードに保持容量が接続されている

## 【0036】

好適には、上記所定のプリチャージ電位は上記データ線を通して供給される。

## 【0037】

また、好適には、上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記第3のスイッチが第3の制御線により導通制御される。

10

## 【0038】

また、好適には、上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される。

## 【0039】

好適には、上記電気光学素子を駆動する場合、第1ステージとして、上記第2の制御線および上記第3の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチおよび上記第3のスイッチが非導通状態に保持され、第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する。

20

## 【0040】

また、好適には、上記電気光学素子を駆動する場合、第1ステージとして、上記第2の制御線、上記第3の制御線、および上記第4の制御線により上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチが所定時間導通させられ、第2ステージとして、第2の制御線により上記第1のスイッチが非導通状態に保持され、所定時間経過後に上記第3の制御線により上記第2のスイッチが非導通状態に保持された後、上記第4の制御線により上記第3のスイッチが非導通状態に保持され、第3ステージとして、上記第1の制御線により上記第4のスイッチが導通させられ、上記データ線を伝播されるデータが上記ノードに書き込まれた後、上記第4のスイッチが非導通状態に保持され、第4ステージとして、上記第2の制御線により上記第1のスイッチが導通させられて、上記電気光学素子に上記データ信号に応じた電流を供給する。

30

## 【0041】

また、第2の観点において、好適には、上記プリチャージ電位は、上記第1の基準電位から上記電界効果トランジスタのしきい値の絶対値を減じた値より小さい値に設定されている。

40

## 【0042】

また、第3の観点において、好適には、上記プリチャージ電位は、上記電気光学素子のしきい値と上記電界効果トランジスタのしきい値とを足し合わせた値より大きい値に設定されている。

## 【0043】

本発明の第4の観点に係る表示装置は、マトリクス状に複数配列された画素回路と、上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第1の制御線と、第1および第2の基準電位と、所定のプリチャージ電位と、

50

を有し、上記各画素回路は、ノードと、第1端子と第2端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給ラインを流れる電流を制御する駆動トランジスタと、上記駆動トランジスタの第1端子に接続された第1のスイッチと、上記駆動トランジスタの第1端子と上記ノードとの間に接続された第2のスイッチと、上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線によって導通制御される第4のスイッチと、上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を有し、上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン、上記第1のスイッチ、および上記電気光学素子が直列に接続されている。

10

#### 【0044】

本発明の第5の観点に係る表示装置は、マトリクス状に複数配列された画素回路と、上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第1の制御線と、第1および第2の基準電位と、所定のプリチャージ電位と、を有し、上記各画素回路は、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと第1の基準電位との間に接続され、上記第1の制御線により導通制御される第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続されている。

20

#### 【0045】

本発明の第6の観点に係る表示装置は、マトリクス状に複数配列された画素回路と、上記画素回路のマトリクス配列に対して列毎に配線され、少なくとも輝度情報に応じたデータ信号が供給されるデータ線と、上記画素回路のマトリクス配列に対して行毎に配線された少なくとも第1の制御線と、第1および第2の基準電位と、所定のプリチャージ電位と、を有し、上記各画素回路は、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと上記プリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され、上記第1の制御線により導通制御される第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記第1のスイッチと第2の基準電位との間に接続されている。

30

#### 【0046】

好適には、上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチおよび上記第3のスイッチが第3の制御線により導通制御される。

40

#### 【0047】

好適には、上記第1のスイッチが第2の制御線により導通制御され、上記第2のスイッチが第3の制御線により導通制御され、上記第3のスイッチが第4の制御線により導通制御される。

#### 【0048】

本発明の第7の観点は、流れる電流によって輝度が変化する電気光学素子と、第1端子と第2端子間で電流供給ラインを形成し、制御端子の電位に応じて上記電流供給ラインを流れる電流を制御する駆動トランジスタと、ノードと、上記駆動トランジスタの第1端子に接続された第1のスイッチと、上記駆動トランジスタの第1端子と上記ノードとの間に接続された第2のスイッチと、上記駆動トランジスタの制御端子と上記所定のプリチャージ電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続され

50

た第4のスイッチと、上記ノードと上記駆動トランジスタの制御端子との間に接続された結合キャパシタと、を有し、上記第1の基準電位と第2の基準電位との間に、上記駆動トランジスタの電流供給ライン、上記第1のスイッチ、および上記電気光学素子が直列に接続されている画素回路の駆動方法であって、上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップとを有する。

10

## 【0049】

本発明の第8の観点は、流れる電流によって輝度が変化する電気光学素子と、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと第1の基準電位との間に接続された第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと所定の電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続された第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記電界効果トランジスタのドレインと第2の基準電位との間に接続されている画素回路の駆動方法であって、上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップとを有する。

20

## 【0050】

本発明の第9の観点は、流れる電流によって輝度が変化する電気光学素子と、電界効果トランジスタと、ノードと、上記電界効果トランジスタのソースと上記電気光学素子との間に接続された第1のスイッチと、上記電界効果トランジスタのソースと上記ノードとの間に接続された第2のスイッチと、上記電界効果トランジスタのゲートと所定の電位との間に接続された第3のスイッチと、上記データ線と上記ノードとの間に接続された第4のスイッチと、上記ノードと上記電界効果トランジスタのゲートとの間に接続された結合キャパシタと、を有し、上記電気光学素子は上記第1のスイッチと第2の基準電位との間に接続されている画素回路の駆動方法であって、上記上記第1のスイッチ、上記第2のスイッチ、および上記第3のスイッチを所定時間導通させる第1ステップと、上記第1のスイッチを非導通状態に保持し、所定時間経過後に上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する第2ステップと、上記第4のスイッチを導通させ、上記データ線を伝播されるデータを上記ノードに書き込んだ後、上記第4のスイッチを非導通状態に保持する第3ステップと、上記第1のスイッチを導通させて、上記電気光学素子に上記データ信号に応じた電流を供給する第4ステップとを有する。

30

## 【0051】

好適には、上記第2のステップにおいて、上記第2のスイッチおよび上記第3のスイッチを非導通状態に保持する際、上記第2のスイッチを非導通状態に保持した後、上記第3のスイッチを非導通状態に保持する。

40

## 【0052】

本発明によれば、たとえば第2の制御線、第3の制御線により、あるいは第2の制御線、第3の制御線、第4の制御線により第1のスイッチ、第2のスイッチ、および第3のスイッチを導通状態とする。

このとき、駆動トランジスタの制御端子、たとえばゲートは第3のスイッチによってプリチャージ電位 $V_{pc}$ となり、結合キャパシタの入力側電位（ノード電位）は、第1および

50

第2のスイッチが導通状態にあるため、第1の基準電位（電源電位 $V_{DD}$ ）またはその付近まで上昇する。

そして、第2の制御線により第1のスイッチを非導通状態とする。これにより駆動トランジスタに流れる電流が遮断されるため、駆動トランジスタの第2端子（たとえばドレイン）の電位は下降するが、その電位が $V_{PC} + |V_{TH}|$ まで下降した時点で駆動トランジスタは非導通状態となって電位が安定する。

このとき、キャパシタの入力側電位（ノード電位）は、第2のスイッチが導通状態にあるため、やはり $V_{PC} + |V_{TH}|$ である。ここで $|V_{TH}|$ は、駆動トランジスタのしきい値の絶対値である。

次に、第3の制御線により第2および第3のスイッチを非導通状態とする。あるいは、第3の制御線により第2のスイッチを非導通状態にした後、第4の制御線により第3のスイッチを非導通状態とする。キャパシタC31の入力側ノードの電位は、 $V_{PC} + |V_{TH}|$ であり、駆動トランジスタのゲート電位は $V_{PC}$ である。すなわち、キャパシタC31の端子間の電位差は $|V_{TH}|$ となる。10

次いで、第1の制御線により第4のスイッチを導通状態とし、データ線から輝度データに応じた電位 $V_{DATA}$ をキャパシタの入力側ノードに与える。

キャパシタ端子間の電位差は $|V_{TH}|$ のまま保持されるので、駆動トランジスタのゲート電位は、 $V_{DATA} - |V_{TH}|$ となる。

次に、第1の制御線により第4のスイッチを非導通状態とし、第2の制御線により第1のスイッチを導通状態とすると、駆動トランジスタおよび電気光学素子に電流が流れ、発光を開始する。20

このように、本発明に係る画素回路は、画素毎にばらつく駆動トランジスタのしきい値によらず、電気光学素子に電流を供給することができるため、高品位な画像を表示する表示装置を実現することができる。特に従来の技術と比較した場合、制御線から駆動トランジスタへのノイズの影響が少ない構成であるため、より高精度なしきい値ばらつきの補正が可能である。

### 【0053】

#### 【発明の実施の形態】

以下、本発明の実施形態を、図面に関連付けて詳細に説明する。

### 【0054】

#### 第1実施形態

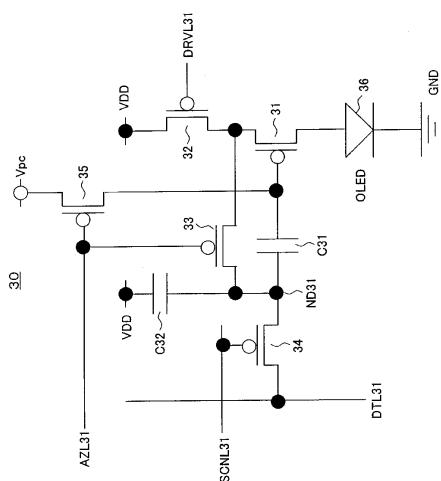

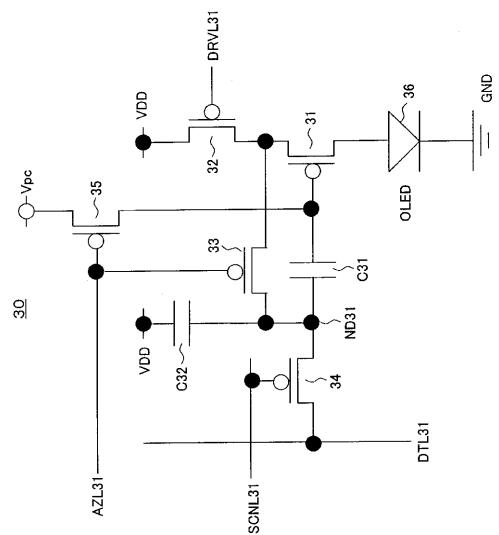

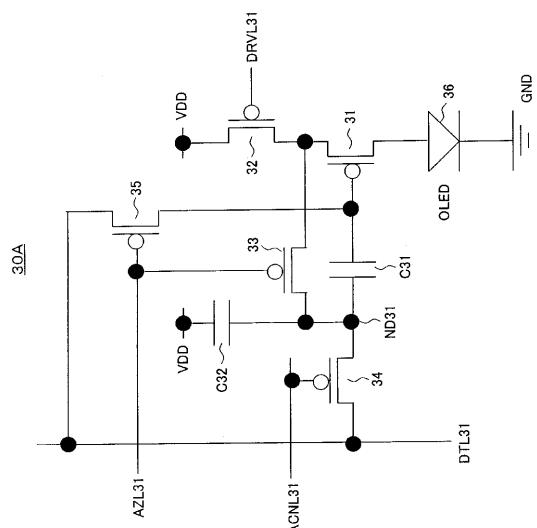

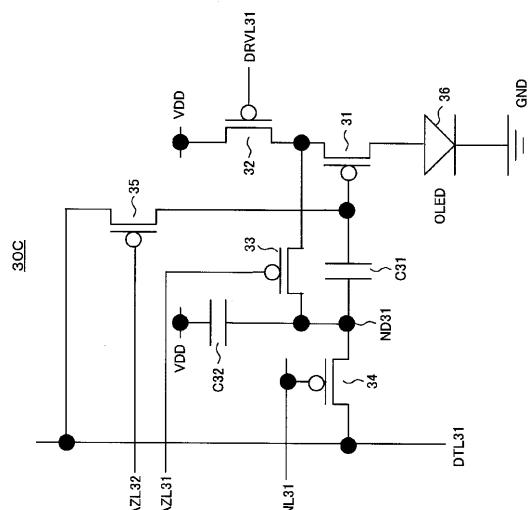

図5は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第1の実施形態を示す回路図である。

### 【0055】

本第1の実施形態に係る画素回路30は、図5に示すように、pチャネルTFT31～TFT35、キャパシタC31、C32、有機EL素子OLED（電気光学素子）からなる発光素子36、およびノードND31を有する。

また、図5において、DTL31はデータ線を、SCNL31は走査線を、AZL31はオートゼロ線を、DRVLL31は駆動線をそれぞれ示している。

これらの構成要素のうち、TFT31が本発明に係る電界効果トランジスタを構成、TFT32が第1のスイッチを構成し、TFT33が第2のスイッチを構成し、TFT35が第3のスイッチを構成し、TFT34が第4のスイッチを構成、キャパシタC31が本発明に係るキャパシタを構成している。40

また、走査線SCNL31が本発明に係る第1の制御線に対応し、駆動線DRVLL31が第2の制御線に対応し、オートゼロ線AZL31が第3の制御線に対応する。

また、電源電圧 $V_{DD}$ の供給ライン（電源電位）が第1の基準電位に相当し、接地電位GNDが第2の基準電位に相当している。

### 【0056】

画素回路30において、TFT31のドレインと第2の基準電位（本実施形態では基準電位GND）との間に光学素子（OLED）36が接続されている。具体的には、発光素子50

36のアノードがTFT31のドレインに接続され、カソード側が接地電位GNDに接続されている。

TFT31のソースと電源電圧 $V_{DD}$ の供給ラインに第1のスイッチとしてのTFT32のソース・ドレインがそれぞれ接続されている。そして、TFT32のゲートが駆動線DRV<sub>L</sub>31に接続されている。

また、TFT31のソースとノードND31に第2のスイッチとしてのTFT33のソース・ドレインがそれぞれ接続されている。そして、TFT33のゲートがオートゼロ線AZL31に接続されている。

TFT31のゲートと所定の電位(プリチャージ電位) $V_{PC}$ に第3のスイッチとしてのTFT35のソース・ドレインがそれぞれ接続されている。そして、TFT35のゲートがオートゼロ線AZL31に接続されている。10

データ線DTL31とノードND31に第4のスイッチとしてのTFT34のソース・ドレインがそれぞれ接続されている。そして、TFT34のゲートが走査線SCNL31に接続されている。

キャパシタC31の第1電極がノードND31に接続され、第2電極がTFT31のゲートに接続されている。

キャパシタC32の第1電極がノードND31に接続され、第2電極が電源電圧 $V_{DD}$ の供給ラインに接続されている。

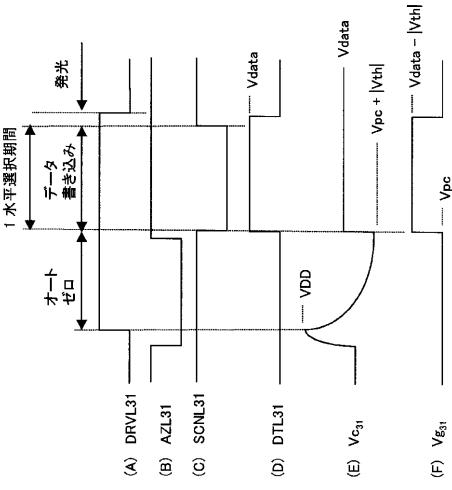

#### 【0057】

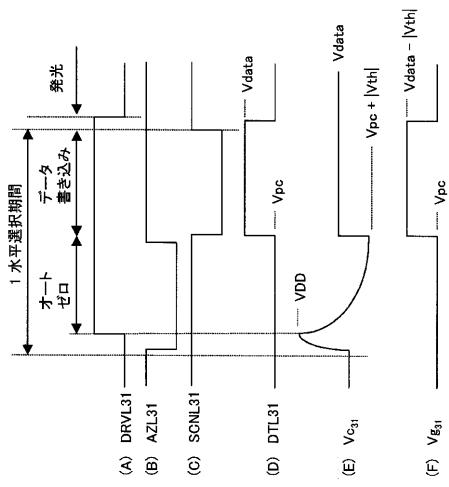

この画素回路30の動作について、図6に示すタイミングチャートを参照しながら以下に説明する。20

#### 【0058】

##### ステップST31:

まず、図6(A),(B)に示すように、駆動線DRV<sub>L</sub>31、オートゼロ線AZL31を低レベルとし、TFT32、TFT33、TFT35を導通状態とする。

このとき、TFT31のゲートは、TFT35によって図6(F)に示すようにプリチャージ電位 $V_{PC}$ となり、キャパシタC31の入力側電位 $V_{C31}$ は、TFT32、TFT33が導通状態にあるため図6(E)に示すように電源電圧 $V_{DD}$ またはその付近まで上昇する。

#### 【0059】

##### ステップST32:

図6(A)に示すように、駆動線DRV<sub>L</sub>31を高レベルとし、TFT32を非導通状態とする。TFT31に流れる電流が遮断されるため、TFT31のドレイン電位は下降するが、その電位が $V_{PC} + |V_{th}|$ まで下降した時点でTFT31は非導通状態となって電位が安定する。

このとき、キャパシタC31の入力側電位 $V_{C31}$ は、TFT33が導通状態にあるため、図6(E)に示すように、やはり $V_{PC} + |V_{th}|$ である。ここで $|V_{th}|$ は、TFT31のしきい値の絶対値である。

#### 【0060】

##### ステップST33:

図6(B)に示すように、オートゼロ線AZL31を高レベルとしてTFT33およびTFT35を非導通状態とする。キャパシタC31の入力側ノードの電位 $V_{C31}$ は、図6(E)に示すように、 $V_{PC} + |V_{th}|$ であり、TFT31のゲート電位 $V_{G31}$ は、図6(F)に示すように、 $V_{PC}$ である。すなわち、キャパシタC31の端子間の電位差は $|V_{th}|$ となる。

#### 【0061】

##### ステップST34:

図6(C),(D)に示すように、走査線SCNL31を低レベルとしてTFT34を導通状態とし、データ線DTL31から輝度データに応じた電位 $V_{data}$ をキャパシタC31の入力側ノードND31に与える。

10

30

40

50

キャパシタ C<sub>31</sub> 端子間の電位差は  $|V_{th}|$  のまま保持されるので、TFT<sub>31</sub> のゲート電位  $V_{g31}$  は、図 6 (F) に示すように、 $V_{data} - |V_{th}|$  となる。

【0062】

ステップ ST35 :

図 6 (A), (C) に示すように、走査線 SCNL<sub>31</sub> を高レベルとして TFT<sub>34</sub> を非導通とし、駆動線 DRVL<sub>31</sub> を低レベルとして TFT<sub>32</sub> を導通状態とすると、TFT<sub>31</sub> および発光素子 (OLED)<sub>36</sub> に電流が流れ、OLED が発光を開始する。

【0063】

なお、上記のステップ ST31 および ST32 の動作においては、 $V_{pc} + |V_{th}| < V_{DD}$  となるように  $V_{pc}$  の値を設定する必要があるが、これを満たす限り  $V_{pc}$  の値は任意である。 10

【0064】

上記動作を行った後に発光素子 (OLED)<sub>36</sub> に流れる電流  $I_{oled}$  を計算すると、TFT<sub>31</sub> が飽和領域で動作していれば、次のようになる。

【0065】

【数4】

$$\begin{aligned}

I_{oled} &= \mu C_{ox} W / L / 2 (V_{gs} - V_{th})^2 \\

&= \mu C_{ox} W / L / 2 (V_{DD} - V_g - |V_{th}|)^2 \\

&= \mu C_{ox} W / L / 2 (V_{DD} - V_{data} + |V_{th}| - |V_{th}|)^2 \\

&= \mu C_{ox} W / L / 2 (V_{DD} - V_{data})^2 \\

&\quad \cdots (4)

\end{aligned} \quad 20$$

【0066】

ここで、 $\mu$  はキャリアの移動度、 $C_{ox}$  は単位面積当たりのゲート容量、 $W$  はゲート幅、 $L$  はゲート長をそれぞれ示している。

(4) 式によれば、電流  $I_{oled}$  は TFT<sub>31</sub> のしきい値  $V_{th}$  に依存せず ( $V_{th}$  によらず)、外部から与えられる  $V_{data}$  によって制御される。

言い換えると、図 5 の画素回路 30 を用いれば、画素毎にばらつく  $V_{th}$  の影響を受けず、電流の均一性、ひいては輝度の均一性が比較的高い表示装置を実現することができる。 30

【0067】

また、TFT<sub>31</sub> がリニア領域で動作している場合においても、発光素子 (OLED)<sub>36</sub> に流れる電流  $I_{oled}$  は次のようになり、やはり  $V_{th}$  に依存しない。

【0068】

【数5】

$$\begin{aligned}

I_{oled} &= \mu C_{ox} W / L \{ (V_{gs} - V_{th}) V_{ds} - V_{ds}^2 / 2 \} \\

&= \mu C_{ox} W / L \{ (V_{DD} - V_g - |V_{th}|) (V_{DD} - V_d) - (V_{DD} \\

&\quad - V_d)^2 / 2 \} \\

&= \mu C_{ox} W / L \{ (V_{DD} - V_{data} + |V_{th}| - |V_{th}|) (V_{DD} - \\

&\quad V_d) - (V_{DD} - V_d)^2 / 2 \} \\

&= \mu C_{ox} W / L \{ (V_{DD} - V_{data}) (V_{DD} - V_d) - (V_{DD} - V_d)^2 \\

&\quad / 2 \} \\

&\quad \cdots (5) \quad 40

\end{aligned}$$

【0069】

ここで、 $V_d$  は TFT<sub>31</sub> のドレイン電位を示している。 50

**【 0 0 7 0 】**

以上のように、本第1の実施形態によれば、しきい値  $V_{th}$  のばらつきの影響をキャンセルできるという点において、図1の従来例より優れる。

図3の従来例に対しては、次の点において、より優れている。

第1に、図3の従来例においては、外部から駆動するデータ振幅  $V_{data}$  に対し、駆動トランジスタのゲート振幅  $V_g$  は(1)式に従って減少するという問題があったが、本発明においてデータ振幅はゲート振幅とほぼ等しく、したがってより小さなデータ線振幅で画素回路を駆動することができる。

これによって、より低消費電力、低ノイズの駆動が可能となる。

第2に、図3の従来例で問題となるオートゼロ線とTFTのゲートとの容量結合については、図5の画素回路30において、TFT33はTFT31のゲートとは直接接続されていないため、その影響が少ない。

一方、TFT35はTFT31のゲートと接続されているが、TFT35のソースは一定電位  $V_{pc}$  に接続されているため、オートゼロ動作終了時においてそのゲート電位が変化しても、TFT31のゲート電位はほぼ  $V_{pc}$  の電位に保たれる。

このように、図5の画素回路30においては、オートゼロ線AZL31とTFT31のゲートとの結合の影響が小さく、その結果図3の画素回路より正確に  $V_{th}$  ばらつきの補正が行われる。

すなわち、本実施形態によれば、トランジスタのしきい値のばらつきによらず、正確に画素回路の発光素子に所望の値の電流を供給し、その結果として輝度均一性の高い、高品位な画像を表示することが可能な有機EL用画素回路を実現できる。その結果、従来の類似回路より高精度なしきい値補正が可能となる。

**【 0 0 7 1 】**

なお、図5の画素回路30では、すべてPMOSを用いているが、これは一例であって、本発明はこれに限定されるものではない。たとえば、上述したように、TFT32～TFT35は単なるスイッチであるから、これらのすべて乃至一部をnチャネルMOS、あるいは他のスイッチ素子で構成することも可能なことは明らかである。

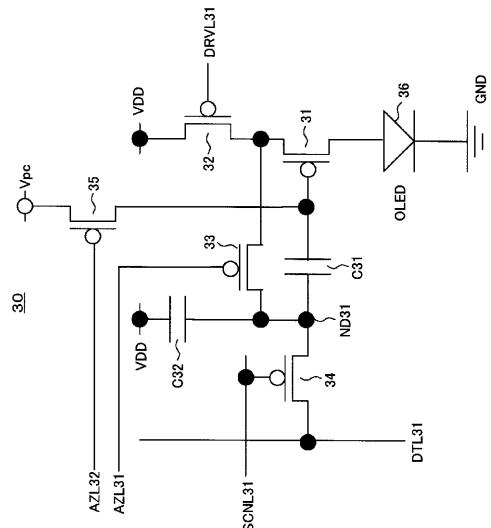

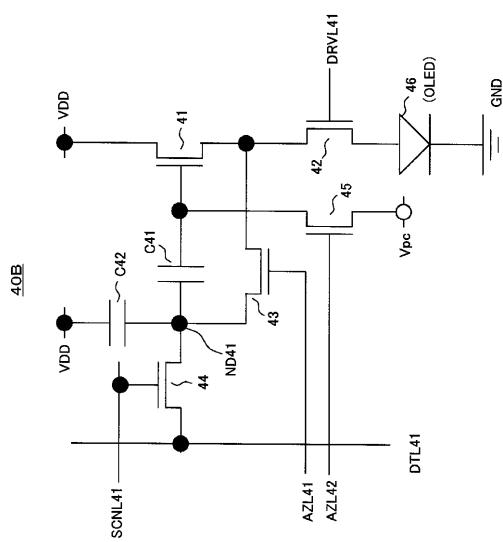

**【 0 0 7 2 】**第2実施形態

図7は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第2の実施形態を示す回路図である。また、図8は、図7の画素回路の動作を説明するためのタイミングチャートである。

**【 0 0 7 3 】**

本第2の実施形態が上述した第1の実施形態と異なる点は、第3のスイッチとしてのTFT35のソースが一定電位ではなく、データ線DTL31に接続されていることにある。

**【 0 0 7 4 】**

その他の構成は、上述した図5の回路と同様であり、その動作の詳細な説明はここでは省略する。

**【 0 0 7 5 】**

本第2の実施形態においては、オートゼロ動作時にはデータ線DTL31からプリチャージ電位  $V_{pc}$  が与えられるため、図5の回路のように専用の一定電位  $V_{pc}$  配線を用意する必要が無いという利点がある。

ただし、データ書き込みに先立って、データ線を必ず一旦  $V_{pc}$  電位にする必要がある。

**【 0 0 7 6 】**第3実施形態

図9は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第3の実施形態を示す回路図である。また、図10は、図9の画素回路の動作を説明するためのタイミングチャートである。

**【 0 0 7 7 】**

本第3の実施形態が上述した第1の実施形態と異なる点は、第2のスイッチとしてのTFT

10

20

30

40

50

T32のゲートと第3のスイッチとしてのTFT35のゲートを共通のオートゼロ線AZL31に接続する代わりに、第2のスイッチとしてのTFT32のゲートを第3の制御線としてのオートゼロ線AZL31に接続し、第3のスイッチとしてのTFT35のゲートを第4の制御線としてのオートゼロ線AZL32に接続し、かつ、ステップST33のオート動作を終了させる処理において、TFT33とTFT35を非導通状態に保持する際、TFT33を非導通状態に保持した後、TFT35を非導通状態に保持するように制御している点にある。

#### 【0078】

この画素回路30Bの動作について、図10に示すタイミングチャートを参照しながら以下に説明する。

10

#### 【0079】

##### ステップST31B:

まず、図10(A),(B),(C)に示すように、駆動線DRVLL31、オートゼロ線AZL31,AZL32を低レベルとし、TFT32、TFT33、TFT35を導通状態とする。

このとき、TFT31のゲートは、TFT35によって図10(G)に示すようにプリチャージ電位 $V_{pc}$ となり、キャパシタC31の入力側電位 $V_{C31}$ は、TFT32、TFT33が導通状態にあるため図6(F)に示すように電源電位 $V_{DD}$ またはその付近まで上昇する。

#### 【0080】

20

##### ステップST32B:

図10(A)に示すように、駆動線DRVLL31を高レベルとし、TFT32を非導通状態とする。TFT31に流れる電流が遮断されるため、TFT31のドレイン電位は下降するが、その電位が $V_{pc} + |V_{th}|$ まで下降した時点でTFT31は非導通状態となって電位が安定する。

このとき、キャパシタC31の入力側電位 $V_{C31}$ は、TFT33が導通状態にあるため、図10(F)に示すように、やはり $V_{pc} + |V_{th}|$ である。ここで $|V_{th}|$ は、TFT31のしきい値の絶対値である。

#### 【0081】

30

##### ステップST33B:

図10(C),(C)に示すように、オートゼロ線AZL31を高レベルとしてTFT33を非導通状態とした後、オートゼロ線AZL32を高レベルとしてTFT35を非導通状態とする。キャパシタC31の入力側ノードの電位 $V_{C31}$ は、図10(F)に示すように、 $V_{pc} + |V_{th}|$ であり、TFT31のゲート電位 $V_{g31}$ は、図10(G)に示すように、 $V_{pc}$ である。すなわち、キャパシタC31の端子間の電位差は $|V_{th}|$ となる。

#### 【0082】

40

##### ステップST34B:

図10(D),(E)に示すように、走査線SCNL31を低レベルとしてTFT34を導通状態とし、データ線DTL31から輝度データに応じた電位 $V_{data}$ をキャパシタC31の入力側ノードND31に与える。

キャパシタC31端子間の電位差は $|V_{th}|$ のまま保持されるので、TFT31のゲート電位 $V_{g31}$ は、図10(G)に示すように、 $V_{data} - |V_{th}|$ となる。

#### 【0083】

50

##### ステップST35B:

図10(A),(D)に示すように、走査線SCNL31を高レベルとしてTFT34を非導通とし、駆動線DRVLL31を低レベルとしてTFT32を導通状態とすると、TFT31および発光素子(OLED)36に電流が流れ、OLEDが発光を開始する。

#### 【0084】

本第3の実施形態によれば、上述した第1の実施形態の効果と同様の効果を得られ、また、確実なオートゼロ動作を行うことができる。

**【0085】**

第4実施形態

図11は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第4の実施形態を示す回路図である。

**【0086】**

本第4の実施形態が上述した第3の実施形態と異なる点は、第3のスイッチとしてのTFT35のソースが一定電位ではなく、データ線DTL31に接続されていることにある。

**【0087】**

その他の構成は、上述した図9の回路と同様であり、その動作の詳細な説明はここでは省略する。

**【0088】**

本第4の実施形態においては、オートゼロ動作時にはデータ線DTL31からプリチャージ電位V<sub>p c</sub>が与えられるため、図9の回路のように専用の一定電位V<sub>p c</sub>配線を用意する必要が無いという利点がある。

ただし、データ書き込みに先立って、データ線を必ず一旦V<sub>p c</sub>電位にする必要がある。

**【0089】**

第5実施形態

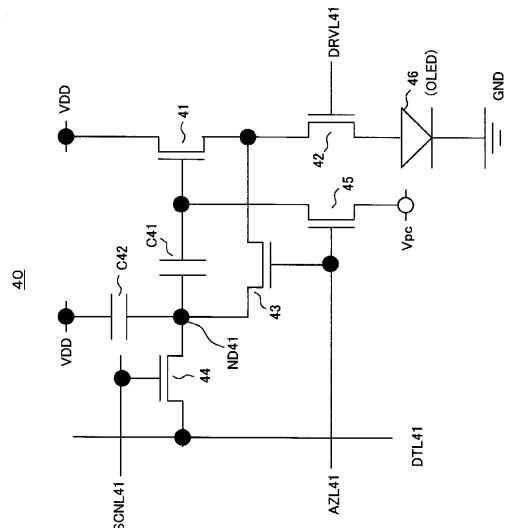

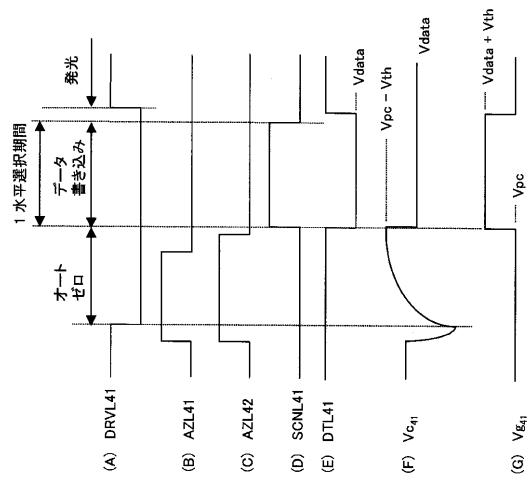

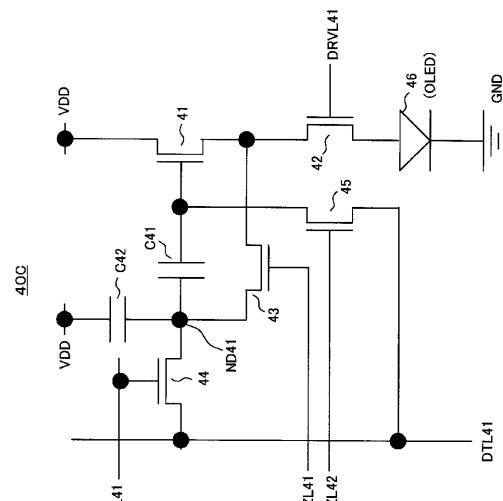

図12は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第5の実施形態を示す回路図である。

**【0090】**

本第5の実施形態に係る画素回路40は、図12に示すように、nチャネルTFT41～TFT45、キャパシタC41、C42、有機EL素子OLED（電気光学素子）からなる発光素子46、およびノードND41を有する。

また、図12において、DTL41はデータ線を、SCNL41は第1の制御線としての走査線を、AZL41は第3の制御線としてのオートゼロ線を、DRVL41は第2の制御線としての駆動線をそれぞれ示している。

これらの構成要素のうち、TFT41が本発明に係る電界効果トランジスタを構成、TFT42が第1のスイッチを構成し、TFT43が第2のスイッチを構成し、TFT45が第3のスイッチを構成し、TFT44が第4のスイッチを構成、キャパシタC41が本発明に係るキャパシタを構成している。

また、電源電圧V<sub>DD</sub>の供給ライン（電源電位）が第1の基準電位に相当し、接地電位GNDが第2の基準電位に相当している。

**【0091】**

画素回路40において、TFT41のドレインが第1の基準電位（本実施形態では電源電位V<sub>DD</sub>）に接続されている。

TFT41のソースと発光素子46（発光素子のアノード）に第1のスイッチとしてのTFT42のソース・ドレインがそれぞれ接続されている。そして、TFT42のゲートが駆動線DRV<sub>L</sub>41に接続されている。また、発光素子46のカソード側が接地電位GNDに接続されている。

また、TFT41のソースとノードND41に第2のスイッチとしてのTFT43のソース・ドレインがそれぞれ接続されている。そして、TFT43のゲートがオートゼロ線AZL41に接続されている。

TFT41のゲートと所定の電位（プリチャージ電位）V<sub>p c</sub>に第3のスイッチとしてのTFT45がソース・ドレインがそれぞれ接続されている。そして、TFT45のゲートがオートゼロ線AZL41に接続されている。

データ線DTL41とノードND41に第4のスイッチとしてのTFT44のソース・ドレインがそれぞれ接続されている。そして、TFT44のゲートが走査線SCNL41に接続されている。

10

20

30

40

50

キャパシタC41の第1電極がノードND41に接続され、第2電極がTFT41のゲートに接続されている。

キャパシタC42の第1電極がノードND41に接続され、第2電極が電源電圧V<sub>DD</sub>の供給ラインに接続されている。

#### 【0092】

図12の画素回路40と図5の画素回路30との最も大きな違いは、発光素子(OLED)46に流れる電流を制御するトランジスタTFT41がNMOSであり、そのソースとOLEDとが接続されている点である。

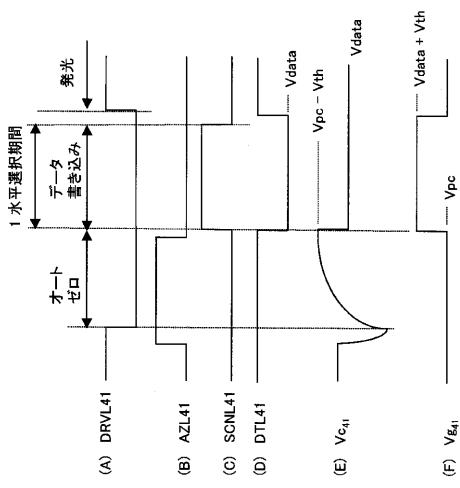

この画素回路40の動作について、図13に示すタイミングチャートを参照しながら以下に説明する。

10

#### 【0093】

##### ステップST41:

図13(A),(B)に示すように、駆動線DRV41、オートゼロ線AZL41を高レベルとし、TFT42、TFT43、TFT45を導通状態とする。このとき、TFT41のゲート電位V<sub>g41</sub>はTFT45によって、図13(F)に示すように、プリチャージ電位V<sub>pC</sub>となる。V<sub>pC</sub>を十分高い電位とすればTFT41が導通状態となり、TFT41および発光素子(OLED)46に電流が流れ。

#### 【0094】

##### ステップST42:

図13(A)に示すように、駆動線DRV41を低レベルとし、TFT42を非導通状態とする。TFT41に流れる電流が遮断されるため、TFT41のソース電位は上昇するが、その電位が(V<sub>pC</sub>-V<sub>th</sub>)まで上昇した時点でTFT41は非導通状態となって電位が安定する。

20

このとき、キャパシタC41の入力側電位V<sub>C41</sub>は、TFT43が導通状態にあるため、図13(E)に示すように、やはり(V<sub>pC</sub>-V<sub>th</sub>)である。ここでV<sub>th</sub>は、TFT41のしきい値である。

#### 【0095】

##### ステップST43:

図13(B)に示すように、オートゼロ線AZL41を低レベルとしてTFT43およびTFT45を非導通状態とする。キャパシタC41の入力側ノードND41の電位V<sub>C41</sub>は、図13(E)に示すように、(V<sub>pC</sub>-V<sub>th</sub>)であり、TFT41のゲート電位V<sub>g41</sub>は、図13(F)に示すようにV<sub>pC</sub>である。すなわち、キャパシタC41の端子間の電位差はV<sub>th</sub>となる。

30

#### 【0096】

##### ステップST44:

図13(C),(D)に示すように、走査線SCNL451を高レベルとしてTFT44を導通状態とし、データ線DTL41から輝度データに応じた電位V<sub>data</sub>をキャパシタC41の入力側ノードND41に与える。キャパシタC41の端子間の電位差はV<sub>th</sub>のまま保持されるので、TFT41のゲート電位V<sub>g41</sub>は、図13(F)に示すように、(V<sub>data</sub>+V<sub>th</sub>)となる。

40

#### 【0097】

##### ステップST45:

図13(A),(C)に示すように、走査線SCNL41を低レベルとしてTFT44を非導通状態とし、駆動線DRV41を高レベルとしてTFT42を導通状態とすると、TFT41および発光素子(OLED)46に電流が流れ、OLEDが発光を開始する。

#### 【0098】

なお、上記ステップST41およびST42の動作においては、V<sub>th</sub>\_e1をOLEDのしきい値としたとき、V<sub>pC</sub>-V<sub>th</sub>>V<sub>th</sub>\_e1となるようにV<sub>pC</sub>の値を設定する必要があるが、これを満たす限りV<sub>pC</sub>の値は任意である。

#### 【0099】

50

上記動作を行った後に発光素子(OLED)46に流れる電流 $I_{oled}$ を計算すると、TFT31が飽和領域で動作していれば、次のようになる。

【0100】

【数6】

$$\begin{aligned} I_{oled} &= \mu C_o x W / L / 2 (V_{gs} - V_{th})^2 \\ &= \mu C_o x W / L / 2 (V_{DD} - V_s - V_{th})^2 \\ &= \mu C_o x W / L / 2 (V_{data} + V_{th} - V_s - V_{th})^2 \\ &= \mu C_o x W / L / 2 (V_{data} - V_s)^2 \end{aligned}$$

10

… (6)

【0101】

ここで、 $\mu$ はキャリアの移動度、 $C_o x$ は単位面積当たりのゲート容量、 $W$ はゲート幅、 $L$ はゲート長をそれぞれ示している。

(6)式によれば、発光素子(OLED)46に流れる電流 $I_{oled}$ はTFT41のしきい値 $V_{th}$ によらず、外部から与えられる $V_{data}$ によって制御される。

言い換えると、図12の画素回路40を用いれば、画素毎にばらつく $V_{th}$ の影響を受けず、電流の均一性、ひいては輝度の均一性が比較的高い表示装置を実現することができる。これは、TFT41がリニア領域で動作する場合においても同様である。

20

【0102】

なお、図12ではすべてNMOOSを用いているが、これは一例であって、本発明はこれに限定されるものではない。たとえば、上述したように、TFT42～TFT45は単なるスイッチであるから、これらのすべて乃至一部をPMOS、あるいはその他のスイッチ素子で構成することも可能なことは明らかである。

【0103】

#### 第6実施形態

図14は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第4の実施形態を示す回路図である。

30

【0104】

本第6の実施形態が上述した第5の実施形態と異なる点は、第3のスイッチとしてのTFT45のソースが一定電位ではなく、データ線DTL41に接続されていることにある。

【0105】

その他の構成は、上述した図12の回路と同様であり、その動作の詳細な説明はここでは省略する。

【0106】

本第6の実施形態においては、オートゼロ動作時にはデータ線DTL41からプリチャージ電位 $V_{pc}$ が与えられるため、図12の回路のように専用の一定電位 $V_{pc}$ 配線を用意する必要が無いという利点がある。

ただし、データ書き込みに先立って、データ線を必ず一旦 $V_{pc}$ 電位にする必要がある。

40

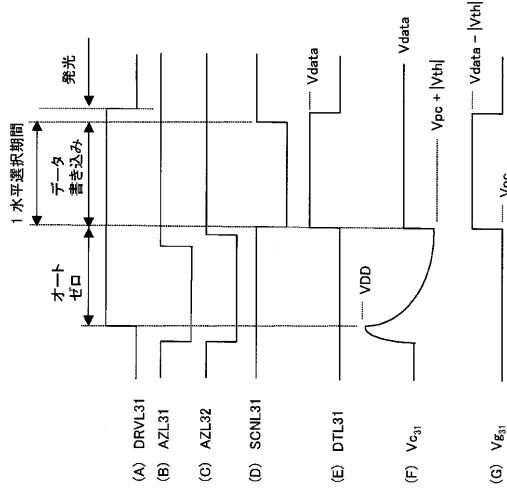

【0107】

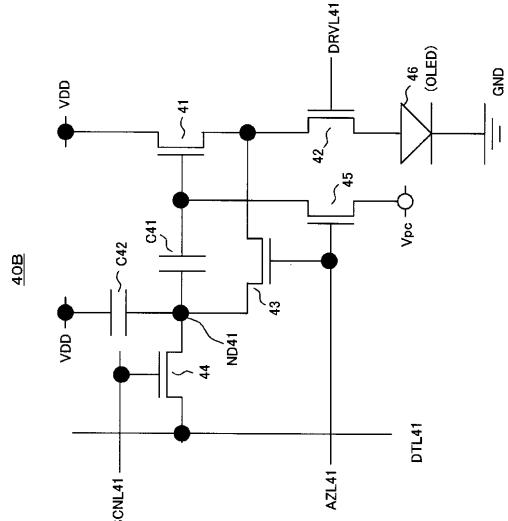

#### 第7実施形態

図15は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第7の実施形態を示す回路図である。また、図16は、図15の画素回路の動作を説明するためのタイミングチャートである。

【0108】

本第7の実施形態が上述した第5の実施形態と異なる点は、第2のスイッチとしてのTFT42のゲートと第3のスイッチとしてのTFT45のゲートを共通のオートゼロ線AZL41に接続する代わりに、第2のスイッチとしてのTFT42のゲートを第3の制御線としてのオートゼロ線AZL41に接続し、第3のスイッチとしてのTFT45のゲート

50

を第4の制御線としてのオートゼロ線AZL42に接続し、かつ、ステップST43のオート動作を終了させる処理において、TFT43とTFT45を非導通状態に保持する際、TFT43を非導通状態に保持した後、TFT45を非導通状態に保持するように制御している点にある。

#### 【0109】

この画素回路40Bの動作について、図16に示すタイミングチャートを参照しながら以下に説明する。

#### 【0110】

##### ステップST41B:

図16(A),(B),(C)に示すように、駆動線DRVLL41、オートゼロ線AZL41を高レベルとし、TFT42、TFT43、TFT45を導通状態とする。このとき、TFT41のゲート電位Vg41はTFT45によって、図16(G)に示すように、プリチャージ電位Vpcとなる。Vpcを十分高い電位とすればTFT41が導通状態となり、TFT41および発光素子(OLED)46に電流が流れ。 10

#### 【0111】

##### ステップST42B:

図16(A)に示すように、駆動線DRVLL41を低レベルとし、TFT42を非導通状態とする。TFT41に流れる電流が遮断されるため、TFT41のソース電位は上昇するが、その電位が(Vpc - Vth)まで上昇した時点でTFT41は非導通状態となって電位が安定する。 20

このとき、キャパシタC41の入力側電位VC41は、TFT43が導通状態にあるため、図16(F)に示すように、やはり(Vpc - Vth)である。ここでVthは、TFT41のしきい値である。

#### 【0112】

##### ステップST43B:

図16(B),(C)に示すように、オートゼロ線AZL41を低レベルとしてTFT43を非導通状態とした後、オートゼロ線AZL42を低レベルとしてTFT45を非導通状態とする。キャパシタC41の入力側ノードND41の電位VC41は、図16(F)に示すように、(Vpc - Vth)であり、TFT41のゲート電位Vg41は、図16(G)に示すようにVpcである。すなわち、キャパシタC41の端子間の電位差はVthとなる。 30

#### 【0113】

##### ステップST44B:

図16(D),(E)に示すように、走査線SCNL451を高レベルとしてTFT44を導通状態とし、データ線DTL41から輝度データに応じた電位VdataをキャパシタC41の入力側ノードND41に与える。キャパシタC41の端子間の電位差はVthのまま保持されるので、TFT41のゲート電位Vg41は、図16(G)に示すように、(Vdata + Vth)となる。 40

#### 【0114】

##### ステップST45B:

図16(A),(D)に示すように、走査線SCNL41を低レベルとしてTFT44を非導通状態とし、駆動線DRVLL41を高レベルとしてTFT42を導通状態とすると、TFT41および発光素子(OLED)46に電流が流れ、OLEDが発光を開始する。

#### 【0115】

本第7の実施形態によれば、上述した第5の実施形態の効果と同様の効果を得られ、また、確実なオートゼロ動作を行うことができる。

#### 【0116】

##### 第8実施形態

図17は、アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第8の実施形態を示す回路図である。 50

**【 0 1 1 7 】**

本第8の実施形態が上述した第7の実施形態と異なる点は、第3のスイッチとしてのTFT45のソースが一定電位ではなく、データ線DTL41に接続されていることにある。

**【 0 1 1 8 】**

その他の構成は、上述した図15の回路と同様であり、その動作の詳細な説明はここでは省略する。

**【 0 1 1 9 】**

本第4の実施形態においては、オートゼロ動作時にはデータ線DTL41からプリチャージ電位Vpcが与えられるため、図15の回路のように専用の一定電位Vpc配線を用意する必要が無いという利点がある。

ただし、データ書き込みに先立って、データ線を必ず一旦Vpc電位にする必要がある。

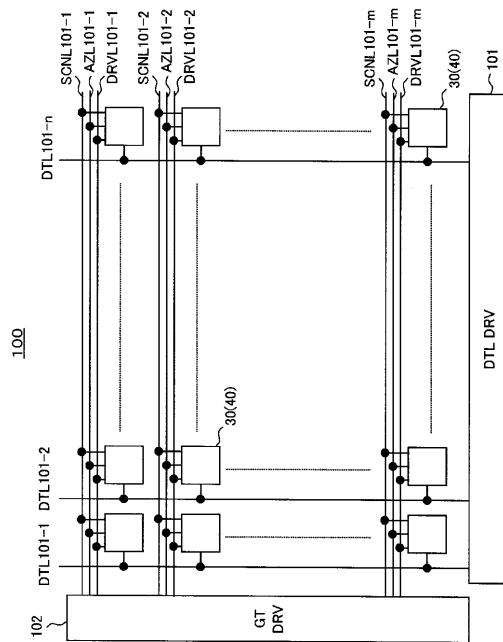

**【 0 1 2 0 】****第9実施形態**

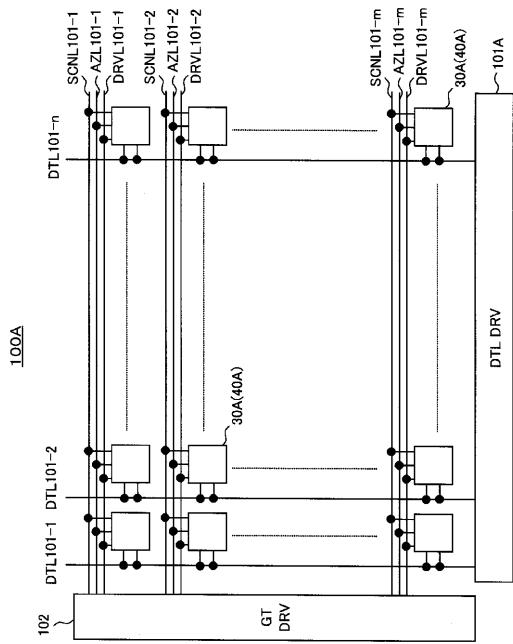

本第9の実施形態では、図5の画素回路30および図12の画素回路40を適用可能なアクティブマトリクス型画像表示装置の構成例について説明する。

**【 0 1 2 1 】**

図18は、本第9の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すブロック図である。

**【 0 1 2 2 】**

本第9の実施形態におけるアクティブマトリクス型画像表示装置100は、図18に示すように、画素回路30（または40）がn×mのマトリクス状に配列されている。

この画素回路30（40）のマトリクス配列に対して、データ線駆動回路（DTLDRV）101により駆動されるm列分のデータ線DTL101-1～DTL101-nが画素列毎に配線されている。

また、走査線駆動回路、オートゼロ線駆動回路、および駆動線駆動回路を含むゲート駆動回路（GTD RV）102により駆動される複数系統（本実施形態では3系統）の走査線SCNL101-1、オートゼロ線AZL101-1、駆動線DLVL101-1、…、走査線SCNL101-m、オートゼロ線AZL101-m、駆動線DLVL101-mが画素行毎にそれぞれ配線されている。

**【 0 1 2 3 】**

なお、図18の構成においては、各画素回路30（40）の第3のスイッチとしてのTFT35（またはTFT45）のソースは、プリチャージ電位Vpcに接続されている。

また、走査線SCNL101-1～SCNL101-mは、図5の走査線31（図12の走査線41）に相当し、オートゼロ線AZL101-1～AZL101-mは、図5のオートゼロ線AZL31（図12のオートゼロ線AZL41）に相当し、駆動線DLV101-1～DLV101-mは、図5の駆動線DRV31（図12の駆動線DLVL41）に相当する。

**【 0 1 2 4 】**

ゲート駆動回路102の、走査線SCNL101-1～SCNL101-m、オートゼロ線AZL101-1～AZL101-m、駆動線DLV101-1～DLV101-mの駆動方法、並びに、データ線駆動回路101のデータ線DTL101-1～DTL101-nの駆動方法は、図6または図13に関連付けて説明した画素回路の駆動方法と実質的に同様に行われる。したがって、ここではその詳細な説明は省略する。

**【 0 1 2 5 】**

本第9の実施形態によれば、高品位な画像を表示することが可能なアクティブマトリクス型画像表示装置を実現することができる。

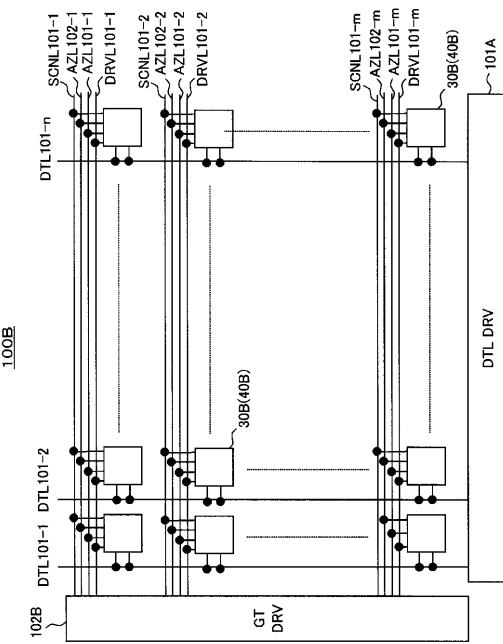

**【 0 1 2 6 】****第10実施形態**

本第10の実施形態では、図7の画素回路30Aおよび図14の画素回路40Aを適用可能なアクティブマトリクス型画像表示装置の構成例について説明する。

**【 0 1 2 7 】**

図19は、本第10の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すプロック図である。

**【 0 1 2 8 】**

本第10の実施形態におけるアクティブマトリクス型画像表示装置100Aは、図19に示すように、画素回路30A（または40A）が $n \times m$ のマトリクス状に配列されている。

この画素回路30A（40A）のマトリクス配列に対して、データ線駆動回路（DTLD RV）101Aにより駆動されるm列分のデータ線DTL101-1～DTL101-nが画素列毎に配線されている。

また、走査線駆動回路、オートゼロ線駆動回路、および駆動線駆動回路を含むゲート駆動回路（GTD RV）102により駆動される複数系統（本実施形態では3系統）の走査線SCNL101-1、オートゼロ線AZL101-1、駆動線DLVL101-1、…、走査線SCNL101-m、オートゼロ線AZL101-m、駆動線DLVL101-mが画素行毎にそれぞれ配線されている。

**【 0 1 2 9 】**

なお、図19の構成においては、各画素回路30A（40A）の第3のスイッチとしてのTFT35（またはTFT45）のソースは、対応する列に配線されたデータ線DTL101-1～DTL101-nに接続されている。

したがって、本第10の実施形態に係るデータ駆動回路101Aは、データ書き込みに先立って、データ線を必ず一旦Vpc電位に設定する。すなわち、オートゼロ動作時には所望のデータ線DTL101-1～DTL101-nからプリチャージ電位Vpcを与える。

また、走査線SCNL101-1～SCNL101-mは、図7の走査線31（図14の走査線41）に相当し、オートゼロ線AZL101-1～AZL101-mは、図7のオートゼロ線AZL31（図14のオートゼロ線AZL41）に相当し、駆動線DLV101-1～DLVL101-mは、図7の駆動線DRV101-1～DLVL41に相当する。

**【 0 1 3 0 】**

ゲート駆動回路102の、走査線SCNL101-1～SCNL101-m、オートゼロ線AZL101-1～AZL101-m、駆動線DLV101-1～DLVL101-mの駆動方法、並びに、データ線駆動回路101のデータ線DTL101-1～DTL101-nの駆動方法は、図8に関連付けて説明した画素回路の駆動方法と実質的に同様に行われる。したがって、ここではその詳細な説明は省略する。

**【 0 1 3 1 】**

本第10の実施形態によれば、高品位な画像を表示することが可能なアクティブマトリクス型画像表示装置を実現することができる。

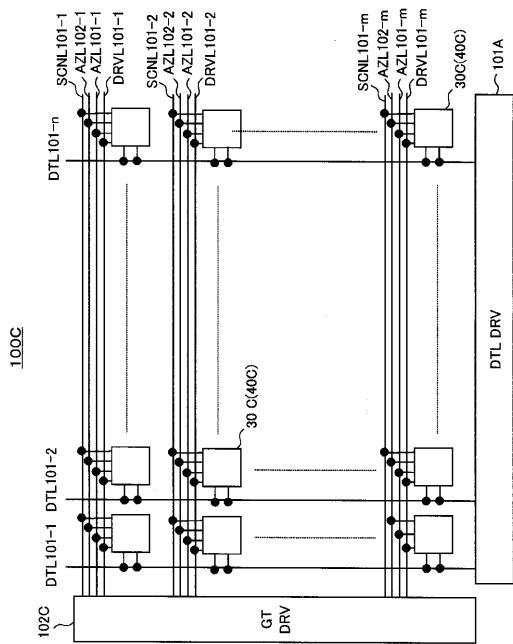

**【 0 1 3 2 】**第11実施形態

本第11の実施形態では、図9の画素回路30Bおよび図15の画素回路40Bを適用可能なアクティブマトリクス型画像表示装置の構成例について説明する。

**【 0 1 3 3 】**

図20は、本第11の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すプロック図である。

**【 0 1 3 4 】**

本第11の実施形態におけるアクティブマトリクス型画像表示装置100Bは、図20に示すように、画素回路30B（または40B）が $n \times m$ のマトリクス状に配列されている。

この画素回路30B（40B）のマトリクス配列に対して、データ線駆動回路（DTLD RV）101により駆動されるm列分のデータ線DTL101-1～DTL101-nが

10

20

30

40

50

画素列毎に配線されている。

また、走査線駆動回路、オートゼロ線駆動回路、および駆動線駆動回路を含むゲート駆動回路（G T D R V）102Bにより駆動される複数系統（本実施形態では3系統）の走査線S C N L 1 0 1 - 1、オートゼロ線A Z L 1 0 1 - 1、オートゼロ線A Z L 1 0 2 - 1、駆動線D L V L 1 0 1 - 1、・・・、走査線S C N L 1 0 1 - m、オートゼロ線A Z L 1 0 1 - m、オートゼロ線A Z L 1 0 2 - m、駆動線D L V L 1 0 1 - mが画素行毎にそれぞれ配線されている。

#### 【0135】

なお、図20の構成においては、各画素回路30B（40B）の第3のスイッチとしてのT F T 3 5（またはT F T 4 5）のソースは、プリチャージ電位V p cに接続されている。

また、走査線S C N L 1 0 1 - 1 ~ S C N L 1 0 1 - mは、図9の走査線31（図15の走査線41）に相当し、オートゼロ線A Z L 1 0 1 - 1 ~ A Z L 1 0 1 - mは、図9のオートゼロ線A Z L 3 1（図15のオートゼロ線A Z L 4 1）に相当し、オートゼロ線A Z L 1 0 2 - 1 ~ A Z L 1 0 2 - mは、図9のオートゼロ線A Z L 3 2（図15のオートゼロ線A Z L 4 2）に相当し、駆動線D L V 1 0 1 - 1 ~ D L V L 1 0 1 - mは、図9の駆動線D R V L 3 1（図15の駆動線D L V L 4 1）に相当する。

#### 【0136】

ゲート駆動回路102Bの、走査線S C N L 1 0 1 - 1 ~ S C N L 1 0 1 - m、オートゼロ線A Z L 1 0 1 - 1 ~ A Z L 1 0 1 - m、オートゼロ線A Z L 1 0 2 - 1 ~ A Z L 1 0 2 - m、駆動線D L V 1 0 1 - 1 ~ D L V L 1 0 1 - mの駆動方法、並びに、データ線駆動回路101のデータ線D T L 1 0 1 - 1 ~ D T L 1 0 1 - nの駆動方法は、図10または図16に関連付けて説明した画素回路の駆動方法と実質的に同様に行われる。したがって、ここではその詳細な説明は省略する。

#### 【0137】

本第11の実施形態によれば、高品位な画像を表示することが可能なアクティブマトリクス型画像表示装置を実現することができる。

#### 【0138】

##### 第12実施形態

本第12の実施形態では、図11の画素回路30Cおよび図17の画素回路40Cを適用可能なアクティブマトリクス型画像表示装置の構成例について説明する。

#### 【0139】

図21は、本第12の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すプロック図である。

#### 【0140】

本第12の実施形態におけるアクティブマトリクス型画像表示装置100Cは、図21に示すように、画素回路30C（または40C）がn×mのマトリクス状に配列されている。

この画素回路30C（40C）のマトリクス配列に対して、データ線駆動回路（D T L D R V）101Aにより駆動されるm列分のデータ線D T L 1 0 1 - 1 ~ D T L 1 0 1 - nが画素列毎に配線されている。

また、走査線駆動回路、オートゼロ線駆動回路、および駆動線駆動回路を含むゲート駆動回路（G T D R V）102Cにより駆動される複数系統（本実施形態では3系統）の走査線S C N L 1 0 1 - 1、オートゼロ線A Z L 1 0 1 - 1、オートゼロ線A Z L 1 0 2 - 1、駆動線D L V L 1 0 1 - 1、・・・、走査線S C N L 1 0 1 - m、オートゼロ線A Z L 1 0 1 - m、オートゼロ線A Z L 1 0 2 - m、駆動線D L V L 1 0 1 - mが画素行毎にそれぞれ配線されている。

#### 【0141】

なお、図21の構成においては、各画素回路30C（40C）の第3のスイッチとしてのT F T 3 5（またはT F T 4 5）のソースは、対応する列に配線されたデータ線D T L 1

10

20

30

40

50

01-1 ~ DTL101-n に接続されている。

したがって、本第12の実施形態に係るデータ駆動回路101Aは、データ書き込みに先立って、データ線を必ず一旦Vpc電位に設定する。すなわち、オートゼロ動作時には所望のデータ線DTL101-1 ~ DTL101-nからプリチャージ電位Vpcを与える。

また、走査線SCNL101-1 ~ SCNL101-mは、図11の走査線31(図17の走査線41)に相当し、オートゼロ線AZL101-1 ~ AZL101-mは、図11のオートゼロ線AZL31(図17のオートゼロ線AZL41)に相当し、オートゼロ線AZL102-1 ~ AZL102-mは、図11のオートゼロ線AZL32(図17のオートゼロ線AZL42)に相当し、駆動線DLV101-1 ~ DLV101-mは、図11の駆動線DRV101(図174の駆動線DLV101)に相当する。

10

#### 【0142】

ゲート駆動回路102Cの、走査線SCNL101-1 ~ SCNL101-m、オートゼロ線AZL101-1 ~ AZL101-m、オートゼロ線AZL102-1 ~ AZL102-m、駆動線DLV101-1 ~ DLV101-mの駆動方法、並びに、データ線駆動回路101のデータ線DTL101-1 ~ DTL101-nの駆動方法は、上述した画素回路の駆動方法と実質的に同様に行われる。したがって、ここではその詳細な説明は省略する。

#### 【0143】

本第12の実施形態によれば、高品位な画像を表示することが可能なアクティブマトリクス型画像表示装置を実現することができる。

20

#### 【0144】

#### 【発明の効果】

以上説明したように、本発明によれば、画素毎にばらつく駆動トランジスタのしきい値によらず、電気光学素子に電流を供給することができる。

このため、高品位な画像を表示する表示装置を提供することができる。

#### 【図面の簡単な説明】

【図1】従来の画素回路の第1の構成例を示す回路図である。

【図2】従来の画像表示装置の構成例を示す図である。

【図3】従来の画素回路の第2の構成例を示す回路図である。

30

【図4】図3の画素回路の駆動方法を説明するためのタイミングチャートである。

【図5】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第1の実施形態を示す回路図である。

【図6】図5の画素回路の動作を説明するためのタイミングチャートである。

【図7】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第2の実施形態を示す回路図である。

【図8】図7の画素回路の動作を説明するためのタイミングチャートである。

【図9】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第3の実施形態を示す回路図である。

【図10】図9の画素回路の動作を説明するためのタイミングチャートである。

40

【図11】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第4の実施形態を示す回路図である。

【図12】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第5の実施形態を示す回路図である。

【図13】図12の画素回路の動作を説明するためのタイミングチャートである。

【図14】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第6の実施形態を示す回路図である。

【図15】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第7の実施形態を示す回路図である。

【図16】図15の画素回路の動作を説明するためのタイミングチャートである。

50

【図17】アクティブマトリクス型画像表示装置に適用可能な本発明に係る画素回路の第8の実施形態を示す回路図である。

【図18】第9の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すブロック図である。

【図19】第10の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すブロック図である。

【図20】第11の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すブロック図である。

【図21】第12の実施形態に係るアクティブマトリクス型画像表示装置の構成例を示すブロック図である。 10

#### 【符号の説明】

30, 30A ~ 30C, 40, 40A ~ 40C ... 画素回路、31 ~ 35, 41 ~ 45 ... TFT、C31, C32, C41, C42 ... キャパシタ、ND31, ND41 ... ノード、SCNL31, SCNL41 ... 走査線（第1の制御線）、AZL31, AZL41 ... オートゼロ線（第3の制御線）、AZL42 ... オートゼロ線（第4の制御線）、DRV31, DRV41 ... 駆動線（第2の制御線）、100, 100A ~ 100C ... アクティブマトリクス型画像表示装置、101, 101A ... データ線駆動回路、102, 102B, 102C ... ゲート駆動回路、SCNL101 - 1 ~ SCNL101 - m ... 走査線、AZL101 - 1 ~ AZL101 - m ... オートゼロ線、AZL102 - 1 ~ AZL102 - m ... オートゼロ線、DLV101 - 1 ~ DLV101 - m ... 駆動線、DTL101 - 1 ~ DTL101 - n ... データ線。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図19】

【図20】

【図21】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，显示装置和像素电路的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2004246204A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2004-09-02 |

| 申请号            | JP2003037256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-02-14 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 湯本昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 湯本 昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/20.612.E<br>G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 3K007/AB05 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080<br>/DD05 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 3K107/AA01<br>3K107/BB01 3K107/CC33 3K107/EE04 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380<br>/BA01 5C380/BA08 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA12 5C380/CA54 5C380/CB16<br>5C380/CB17 5C380/CC02 5C380/CC04 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC30 5C380<br>/CC33 5C380/CC39 5C380/CC52 5C380/CC62 5C380/CC64 5C380/CC65 5C380/CD012 5C380<br>/CD024 5C380/CD025 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 佐藤隆久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | <a href="#">JP3901105B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

能够稳定且准确地向每个像素的发光元件提供期望值的电流的像素电路，而与像素内部的有源元件的阈值的变化无关，并且能够显示高质量的图像。和显示设备。TFT32连接在驱动TFT31的源极和电源电势VDD之间并由驱动线DRV131控制，以及TFT33连接在TFT31的源极和节点ND31之间并由自动调零线AZL31控制。连接在TFT31的栅极和预定电位Vpc之间并由自动调零线AZL31控制的导通的TFT35，连接在数据线DTL31和节点ND31之间并由扫描线SCNL331控制的导通的TFT34，以及节点ND31和TFT31。OLED 36连接在TFT 31的漏极和参考电位GND之间，并且耦合电容器C31连接在栅极之间。[选择图]图5