(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 224437

(P2003 - 224437A)

(43)公開日 平成15年8月8日(2003.8.8)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I          | テ-マコード <sup>8</sup> (参考) |

|--------------------------|------|--------------|--------------------------|

| H 0 3 F 3/34             |      | H 0 3 F 3/34 | C 5 C 0 8 0              |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20 | 611 H 5 J 0 5 5          |

|                          | 624  |              | 624 B 5 J 0 9 1          |

|                          | 641  |              | 641 D 5 J 5 0 0          |

| 3/30                     |      | 3/30         | J                        |

審査請求 未請求 請求項の数 20 O L (全 18数) 最終頁に続く

(21)出願番号 特願2002 - 21844(P2002 - 21844)

(71)出願人 000001889

三洋電機株式会社

(22)出願日 平成14年1月30日(2002.1.30)

大阪府守口市京阪本通2丁目5番5号

(72)発明者 佐野 景一

大阪府守口市京阪本通2丁目5番5号 三洋電

機株式会社内

(74)代理人 100111383

弁理士 芝野 正雅

最終頁に続く

(54)【発明の名称】 電流駆動回路および該電流駆動回路を備えた表示装置

(57)【要約】

【課題】駆動用トランジスタにおけるしきい値電圧のばらつきの影響を抑制することのできる電流駆動回路および該電流駆動回路を備えた表示装置を提供する。

【解決手段】有機発光素子(OLED)を発光体とする表示装置の各画素に、該OLEDを駆動するための電流駆動回路を設ける。表示信号V<sub>dsp</sub>は、画素スイッチング用トランジスタQ<sub>s</sub>を介して駆動用トランジスタQ<sub>d</sub>に入力される。駆動用トランジスタQ<sub>d</sub>は、薄膜トランジスタにより形成されており、半導体層の上下層にゲート電極が設けられて両ゲート電極はチャネル領域を共有した構造を有する。OLEDを駆動するにあたり、短絡用スイッチング素子Q<sub>1a</sub>およびQ<sub>1b</sub>と遮断用スイッチング素子Q<sub>2</sub>を用いて、それ以前に補償用キャパシタC<sub>s</sub>に駆動用トランジスタQ<sub>d</sub>のしきい値電圧「V<sub>t h</sub>」を蓄積保持しておく。そしてその状態にて、表示信号V<sub>dsp</sub>を駆動用トランジスタQ<sub>d</sub>に入力する。

**【特許請求の範囲】**

【請求項1】電流受容回路に電流を供給すべく、この受容量に対応したゲート電圧の印加に基づいて同電流受容回路に電流を供給する駆動用トランジスタを備える電流駆動回路において、

前記駆動用トランジスタとして、そのチャネル領域を共有する第1のゲートおよび第2のゲートの2種のゲートを有するトランジスタを備え、それらゲートの一方で当該トランジスタのしきい値電圧のばらつきを補償するようにしたことを特徴とする電流駆動回路。

【請求項2】請求項1記載の電流駆動回路において、前記駆動用トランジスタのソース端子と前記2種のゲートのうちの一方の端子との間に接続されて当該トランジスタのしきい値電圧に対応した電荷が蓄積保持されるキャパシタを備え、このキャパシタに前記しきい値電圧に対応した電荷が蓄積保持されている状態で前記駆動用トランジスタの他方のゲートに対する前記ゲート電圧の印加に基づく前記電流受容回路への電流の供給が行われることを特徴とする電流駆動回路。

【請求項3】請求項2記載の電流駆動回路において、前記駆動用トランジスタのドレイン端子と前記2種のゲートの各端子とを一時的に共通接続する手段と、前記駆動用トランジスタに流れるドレイン電流を一時的に遮断する手段とを備え、前記各端子を一時的に共通接続して前記キャパシタへの所要の充電電荷の確保および前記駆動用トランジスタに流れるドレイン電流の一時的な遮断により、該キャパシタへの充電電荷を同トランジスタの前記しきい値電圧に対応した電荷とすることを特徴とする電流駆動回路。

【請求項4】前記共通接続する手段による前記各端子の一時的な共通接続の実行から前記ドレイン電流を遮断する手段による前記ドレイン電流の一時的な遮断の実行までに所定の遅延時間が設定されてなる請求項3記載の電流駆動回路。

【請求項5】請求項3または4記載の電流駆動回路において、

前記印加されるゲート電圧を蓄積保持するためのキャパシタをさらに備えることを特徴とする電流駆動回路。

【請求項6】前記駆動用トランジスタはpチャネル型トランジスタであり、そのソース端子が前記ドレイン電流を流すための高電位に固定されるとともに、前記電流受容回路が、前記ドレイン電流の流れる経路において同トランジスタの下流側に設けられてなる請求項3～5のいずれかに記載の電流駆動回路。

【請求項7】前記電流受容回路が、前記駆動用トランジスタのドレイン端子と前記共通接続する手段によるドレイン配線上の共通接続点との間に設けられてなる請求項6記載の電流駆動回路。

【請求項8】前記駆動用トランジスタはnチャネル型トランジスタであり、その前記ゲート電圧が印加されるゲ

ート端子とソース端子との間にはそれら端子間の電位差を保持する電位差保持用のキャパシタが設けられるとともに、少なくとも前記ゲート電圧が印加される期間、前記ソース端子の電位を前記ゲート電圧の電位よりも低い所定の電位に保持する手段を備え、前記電流受容回路は、前記ドレイン電流の流れる経路において同トランジスタの下流側に設けられてなる請求項3または4記載の電流駆動回路。

【請求項9】前記電流受容回路が、少なくとも前記ゲート電圧が印加される期間だけ前記所定の電位に保持される駆動用トランジスタのソース端子と同トランジスタの前記しきい値電圧に対応した電荷が蓄積保持されるキャパシタのソース配線側接続点との間に設けられてなる請求項8記載の電流駆動回路。

【請求項10】前記駆動用トランジスタは、前記2種のゲートによって共有されるチャネル領域とそれら各ゲートの電極との間の容量が等しく設定されてなる請求項1～9のいずれかに記載の電流駆動回路。

【請求項11】発光素子を駆動すべくその駆動指令に対応したゲート電圧の印加に基づいて同発光素子に駆動電流を供給する駆動用トランジスタが表示基板上の各画素に対応したそれら発光素子毎に設けられてなる電流駆動回路を備えた表示装置において、前記各駆動用トランジスタとして、そのチャネル領域を共有する第1のゲートおよび第2のゲートの2種のゲートを有するトランジスタを備え、それらゲートの一方で当該トランジスタのしきい値電圧のばらつきを補償するようにしたことを特徴とする電流駆動回路を備えた表示装置。

【請求項12】請求項11記載の電流駆動回路を備えた表示装置において、

前記各駆動用トランジスタのソース端子と前記2種のゲートのうちの一方の端子との間に接続されて当該トランジスタのしきい値電圧に対応した電荷が蓄積保持されるキャパシタを備え、それらキャパシタに各しきい値電圧に対応した電荷が蓄積保持されている状態で前記各駆動用トランジスタの他方のゲートに対する前記ゲート電圧の印加に基づく各発光素子への駆動電流の供給が行われることを特徴とする電流駆動回路を備えた表示装置。

【請求項13】請求項12記載の電流駆動回路を備えた表示装置において、

前記各駆動用トランジスタのドレイン端子と前記2種のゲートの各端子とを一時的に共通接続する手段と、前記各駆動用トランジスタに流れるドレイン電流を一時的に遮断する手段とをそれぞれ備え、前記各端子を一時的に共通接続して前記キャパシタへの所要の充電電荷を確保したのち、前記駆動用トランジスタに流れるドレイン電流を一時的に遮断して、該キャパシタへの充電電荷を同トランジスタの前記しきい値電圧に対応した電荷とすることを特徴とする電流駆動回路を備えた表示装置。

【請求項14】前記共通接続する手段による前記各端子の一時的な共通接続の実行から前記ドレン電流を遮断する手段による前記ドレン電流の一時的な遮断の実行までに所定の遅延時間が設定されてなる請求項13記載の電流駆動回路を備えた表示装置。

【請求項15】請求項13または14記載の電流駆動回路を備えた表示装置において、

前記印加される各ゲート電圧を蓄積保持するためのキャパシタをさらに備えることを特徴とする電流駆動回路を備えた表示装置。

【請求項16】前記各駆動用トランジスタはpチャネル型トランジスタであり、その各ソース端子が前記ドレン電流を流すための高電位に固定されるとともに、前記発光素子が、前記ドレン電流の流れる経路において各々同トランジスタの下流側に設けられてなる請求項13～15のいずれかに記載の電流駆動回路を備えた表示装置。

【請求項17】前記各発光素子が、前記各駆動用トランジスタのドレン端子と前記共通接続する手段によるドレン配線上の共通接続点との間に設けられてなる請求項16記載の電流駆動回路を備えた表示装置。

【請求項18】前記各駆動用トランジスタはnチャネル型トランジスタであり、その前記各ゲート電圧が印加されるゲート端子とソース端子との間にはそれら端子間の電位差を保持する電位差保持用のキャパシタが各々設けられるとともに、少なくとも前記ゲート電圧が印加される期間、前記ソース端子の電位を前記ゲート電圧の電位よりも低い所定の電位に保持する手段を各々備え、前記各発光素子は、前記ドレン電流の流れる経路において前記各駆動用トランジスタの下流側に設けられてなる請求項13または14記載の電流駆動回路を備えた表示装置。

【請求項19】前記各発光素子が、少なくとも前記ゲート電圧が印加される期間だけ前記所定の電位に保持される各駆動用トランジスタのソース端子と同トランジスタの前記しきい値電圧に対応した電荷が蓄積保持される各キャパシタのソース配線側接続点との間に設けられてなる請求項18記載の電流駆動回路を備えた表示装置。

【請求項20】前記各駆動用トランジスタは、前記2種のゲートによって共有されるチャネル領域とそれら各ゲートの電極との間の容量が等しく設定されてなる請求項11～19のいずれかに記載の電流駆動回路を備えた表示装置。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明は、トランジスタを用いた電流駆動回路および該電流駆動回路を備えた表示装置に関する。

##### 【0002】

【従来の技術】MOS(Metal Oxide Semiconductor) 50

構造を有するトランジスタや薄膜トランジスタ(Thin Film Transistor; TFT)などは、ゲート-ソース間に電圧が印加されるとその電圧に応じた電流をドレンに流す、いわゆる電圧制御型の電流駆動素子である。これらの素子は、ゲート-ソース間にしきい値電圧を超える電圧を印加すると、そのチャネル領域に反転層が形成されてソース-ドレン間が導通するようになる。そして、このしきい値電圧は素子の電気特性を特徴づける重要なパラメータとなっている。

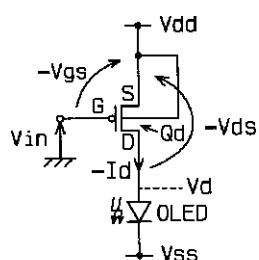

10 【0003】図20に、pチャネル型トランジスタQdを用いて有機発光素子(Organic Light Emitting Device; OLED)を発光させる従来の駆動回路の一例を示す。図20に示されるように、この回路においてはトランジスタQdのゲート端子Gに指令信号「Vin」を入力してゲート-ソース間に電圧「-Vgs」を与え、これによりドレン電流「-Id」を制御する。このドレン電流「-Id」は、トランジスタQdおよびOLEDに定電圧電源「Vdd」および「Vss」を印加した状態で、ゲート-ソース間電圧「-Vgs」を増加させたとき、その値がしきい値電圧「Vth」を超えたところを境界として急激に増加する特性を示す(図21(a))。そして、同従来の回路では、このゲート-ソース間電圧「-Vgs」を変化させることにより、OLEDに流す電流を調整して、その発光状態を制御するようしている。

##### 【0004】

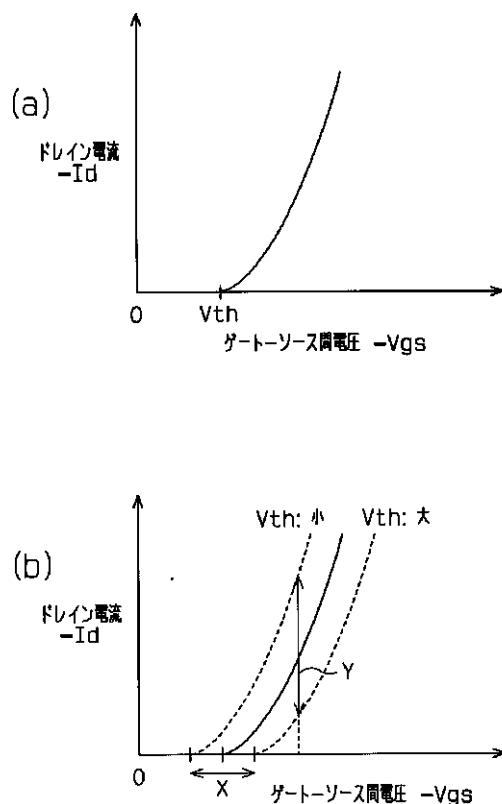

【発明が解決しようとする課題】ところで、上記電流駆動回路が複数設けられる場合、それら回路を構成するトランジスタ(Qd)のしきい値電圧「Vth」も含めてその電気特性を完全にそろえることは事実上困難である。すなわち、図21(b)に示すように、しきい値電圧「Vth」が矢印Xにて示した範囲でばらつくことがあると、たとえゲート-ソース間電圧「-Vgs」の値が同じであっても、ドレン電流「-Id」は矢印Yにて示した範囲で大きくばらつくようになる。

【0005】このため、たとえば上記OLEDを発光素子として用いる表示装置をアクティブマトリクス駆動方式により駆動すべく、各発光素子(画素)毎に駆動用のTFTが設けられた電流駆動回路を構成するような場合にも、それらTFTとしての素子ばらつきがその表示性能にとって無視できないものとなる。すなわちこの場合、OLEDを発光させるための電流は微小であるため、それらTFTによる駆動電流の制御を精度よく行わなければ、表示装置としての所望とされる表示品質を保つことはできない。しかし実際には、上記各TFTにも上述のしきい値電圧のばらつきが存在するため、たとえ同じ電位の表示信号をそれらTFTの各ゲート端子G(図20参照)に印加したとしても、それにより駆動される電流の大きさがすべて同じになるとは限らない。そして、こうした駆動電流のばらつきが、各画素の発光態

様（輝度）を不均一なものとしている。

【0006】なお、上記TFTを駆動用のトランジスタとする電流駆動回路に限らず、MOSトランジスタを上記駆動用のトランジスタに用いる電流駆動回路にあっても、これが複数の駆動対象毎に設けられる場合には、それらトランジスタのしきい値電圧のばらつきに起因するこうした実情もおおむね共通したものとなっている。

【0007】本発明は、上記実情に鑑みてなされたものであり、その目的は、駆動用トランジスタにおけるしきい値電圧のばらつきの影響を抑制することのできる電流駆動回路、および該電流駆動回路を備えた表示装置を提供することにある。

#### 【0008】

【課題を解決するための手段】以下、上記目的を達成するための手段について記載する。請求項1記載の発明は、電流駆動回路として、電流受容回路に電流を供給すべく、この受容量に対応したゲート電圧の印加に基づいて同電流受容回路に電流を供給する駆動用トランジスタを備えるものであって、前記駆動用トランジスタとして、そのチャネル領域を共有する第1のゲートおよび第2のゲートの2種のゲートを有するトランジスタを備え、それらゲートの一方で当該トランジスタのしきい値電圧のばらつきを補償するようにしたことをその要旨とする。

【0009】また、請求項2記載の発明は、請求項1記載の電流駆動回路において、前記駆動用トランジスタのソース端子と前記2種のゲートのうちの一方の端子との間に接続されて当該トランジスタのしきい値電圧に対応した電荷が蓄積保持されるキャパシタを備え、このキャパシタに前記しきい値電圧に対応した電荷が蓄積保持されている状態で前記駆動用トランジスタの他方のゲートに対する前記ゲート電圧の印加に基づく前記電流受容回路への電流の供給が行われることをその要旨とする。

【0010】また、請求項3記載の発明は、請求項2記載の電流駆動回路において、前記駆動用トランジスタのドレイン端子と前記2種のゲートの各端子とを一時的に共通接続する手段と、前記駆動用トランジスタに流れるドレン電流を一時的に遮断する手段とを備え、前記各端子を一時的に共通接続して前記キャパシタへの所要の充電電荷を確保したのち、前記駆動用トランジスタに流れるドレン電流を一時的に遮断して、該キャパシタへの充電電荷を同トランジスタの前記しきい値電圧に対応した電荷とすることをその要旨とする。

【0011】また、請求項4記載の発明は、請求項3記載の電流駆動回路において、前記共通接続する手段による前記各端子の一時的な共通接続の実行から前記ドレン電流を遮断する手段による前記ドレン電流の一時的な遮断の実行までに所定の遅延時間が設定されることをその要旨とする。

#### 【0012】また、請求項5記載の発明は、請求項3ま

たは4記載の電流駆動回路において、前記印加されるゲート電圧を蓄積保持するためのキャパシタをさらに備えることをその要旨とする。

【0013】また、請求項6記載の発明は、請求項3～5のいずれかに記載の電流駆動回路において、前記駆動用トランジスタはpチャネル型トランジスタであり、そのソース端子が前記ドレン電流を流すための高電位に固定されるとともに、前記電流受容回路が、前記ドレン電流の流れる経路において同トランジスタの下流側に設けられてなることをその要旨とする。

【0014】また、請求項7記載の発明は、請求項6記載の電流駆動回路において、前記電流受容回路が、前記駆動用トランジスタのドレン端子と前記共通接続する手段によるドレン配線上の共通接続点との間に設けられてなることをその要旨とする。

【0015】また、請求項8記載の発明は、請求項3または4記載の電流駆動回路において、前記駆動用トランジスタはnチャネル型トランジスタであり、その前記ゲート電圧が印加されるゲート端子とソース端子との間にはそれら端子間の電位差を保持する電位差保持用のキャパシタが設けられるとともに、少なくとも前記ゲート電圧が印加される期間、前記ソース端子の電位を前記ゲート電圧の電位よりも低い所定の電位に保持する手段を備え、前記電流受容回路は、前記ドレン電流の流れる経路において同トランジスタの下流側に設けられてなることをその要旨とする。

【0016】また、請求項9記載の発明は、請求項8記載の電流駆動回路において、前記電流受容回路が、少なくとも前記ゲート電圧が印加される期間だけ前記所定の電位に保持される駆動用トランジスタのソース端子と同トランジスタの前記しきい値電圧に対応した電荷が蓄積保持されるキャパシタのソース配線側接続点との間に設けられてなることをその要旨とする。

【0017】また、請求項10記載の発明は、請求項1～9のいずれかに記載の電流駆動回路において、前記駆動用トランジスタは、前記2種のゲートによって共有されるチャネル領域とそれら各ゲートの電極との間の容量が等しく設定されてなることをその要旨とする。

【0018】また、請求項11記載の発明は、表示装置として、発光素子を駆動すべくその駆動指令に対応したゲート電圧の印加に基づいて同発光素子に駆動電流を供給する駆動用トランジスタが表示基板上の各画素に対応したそれら発光素子毎に設けられてなる電流駆動回路を備えたものであって、前記各駆動用トランジスタとして、そのチャネル領域を共有する第1のゲートおよび第2のゲートの2種のゲートを有するトランジスタを備え、それらゲートの一方で当該トランジスタのしきい値電圧のばらつきを補償するようにしたことをその要旨とする。

【0019】また、請求項12記載の発明は、請求項1

1記載の電流駆動回路を備えた表示装置において、前記各駆動用トランジスタのソース端子と前記2種のゲートのうちの一方の端子との間に接続されて当該トランジスタのしきい値電圧に対応した電荷が蓄積保持されるキャパシタを備え、それらキャパシタに各しきい値電圧に対応した電荷が蓄積保持されている状態で前記各駆動用トランジスタの他方のゲートに対する前記ゲート電圧の印加に基づく各発光素子への駆動電流の供給が行われることをその要旨とする。

【0020】また、請求項13記載の発明は、請求項12記載の電流駆動回路を備えた表示装置において、前記各駆動用トランジスタのドレイン端子と前記2種のゲートの各端子とを一時的に共通接続する手段と、前記各駆動用トランジスタに流れるドレン電流を一時的に遮断する手段とをそれぞれ備え、前記各端子を一時的に共通接続して前記キャパシタへの所要の充電電荷を確保したのち、前記駆動用トランジスタに流れるドレン電流を一時的に遮断して、該キャパシタへの充電電荷を同トランジスタの前記しきい値電圧に対応した電荷とすることをその要旨とする。

【0021】また、請求項14記載の発明は、請求項13記載の電流駆動回路を備えた表示装置において、前記共通接続する手段による前記各端子の一時的な共通接続の実行から前記ドレン電流を遮断する手段による前記ドレン電流の一時的な遮断の実行までに所定の遅延時間が設定されることをその要旨とする。

【0022】また、請求項15記載の発明は、請求項13または14記載の電流駆動回路を備えた表示装置において、前記印加される各ゲート電圧を蓄積保持するためのキャパシタをさらに備えることをその要旨とする。

【0023】また、請求項16記載の発明は、請求項13～15のいずれかに記載の電流駆動回路を備えた表示装置において、前記各駆動用トランジスタはpチャネル型トランジスタであり、その各ソース端子が前記ドレン電流を流すための高電位に固定されるとともに、前記発光素子が、前記ドレン電流の流れる経路において各々同トランジスタの下流側に設けられてなることをその要旨とする。

【0024】また、請求項17記載の発明は、請求項16記載の電流駆動回路を備えた表示装置において、前記各発光素子が、前記各駆動用トランジスタのドレイン端子と前記各共通接続する手段によるドレン配線上の共通接続点との間に設けられてなることをその要旨とする。

【0025】また、請求項18記載の発明は、請求項13または14記載の電流駆動回路を備えた表示装置において、前記各駆動用トランジスタはnチャネル型トランジスタであり、その前記各ゲート電圧が印加されるゲート端子とソース端子との間にはそれら端子間の電位差を保持する電位差保持用のキャパシタが各々設けられると

ともに、少なくとも前記ゲート電圧が印加される期間、前記ソース端子の電位を前記ゲート電圧の電位よりも低い所定の電位に保持する手段を各々備え、前記各発光素子は、前記ドレン電流の流れる経路において前記各駆動用トランジスタの下流側に設けられてなることをその要旨とする。

【0026】また、請求項19記載の発明は、請求項18記載の電流駆動回路を備えた表示装置において、前記各発光素子が、少なくとも前記ゲート電圧が印加される期間だけ前記所定の電位に保持される各駆動用トランジスタのソース端子と同トランジスタの前記しきい値電圧に対応した電荷が蓄積保持される各キャパシタのソース配線側接続点との間に設けられてなることをその要旨とする。

【0027】そして、請求項20記載の発明は、請求項11～19のいずれかに記載の電流駆動回路を備えた表示装置において、前記各駆動用トランジスタは、前記2種のゲートによって共有されるチャネル領域とそれら各ゲートの電極との間の容量が等しく設定されてなることをその要旨とする。

#### 【0028】

【発明の実施の形態】(第1の実施の形態)以下、本発明にかかる電流駆動回路および該電流駆動回路を備えた表示装置を、電流駆動素子として有機発光素子(Organic Light Emitting Device; OLED)を駆動する電流駆動回路および該電流駆動回路を備えた表示装置に適用した第1の実施の形態について、図1～図8を参照しつつ説明する。

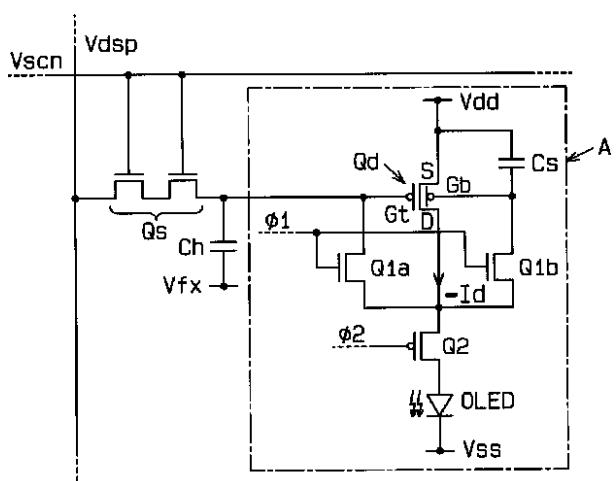

【0029】まず、この第1の実施の形態にかかる表示装置の概略構成を図1に示す。図1に示されるように、この表示装置は、表示部11とこれを制御するための周辺回路とを有して構成されている。そして、この周辺回路は、表示部11にタイミング信号を供給するVスキャナ12と、同表示部11に表示信号を供給するサンプリングスイッチアレイ13と、そのサンプリングスイッチアレイ13に切替信号を与えるHスキャナ14とを有して構成されている。

【0030】このうち、Vスキャナ12は、Vスキャナ用クロックおよびスタートパルスを受けて、表示部11の水平方向に延設されたタイミング信号配線15に順次タイミング信号を供給する。一方、Hスキャナ14は、Hスキャナ用クロックおよびスタートパルスを受けて、サンプリングスイッチアレイ13に切替信号を与える。サンプリングスイッチアレイ13は、その切替信号を受けて、表示部11の垂直方向に延設された表示信号配線16の対応する部分に順次、Hスキャナ用クロックおよびスタートパルスと同期して入力されてくる表示信号を供給する。すなわち、本実施の形態においては、Vスキャナ12が画素を駆動するためのタイミング回路として機能する。

【0031】そして、表示部11には、格子状に設けられた上記タイミング信号配線15と表示信号配線16との交差部分に対応して、発光素子であるOLEDおよびその発光状態を制御する電流駆動回路などが設けられ、表示装置の各画素を構成している。

【0032】なお、表示部11の水平方向および垂直方向には、上記タイミング信号配線15および表示信号配線16のほか、各種基準電位を与える複数の電源配線なども延設されているが、図1においてはこれら配線の図示を割愛した。

【0033】また、表示部11および周辺回路を構成する各回路および配線は、1枚のガラス基板上に薄膜形成技術により形成された表示基板上に構成されている。そして、それら回路を機能させるための能動素子として薄膜トランジスタ(TFT)が用いられている。

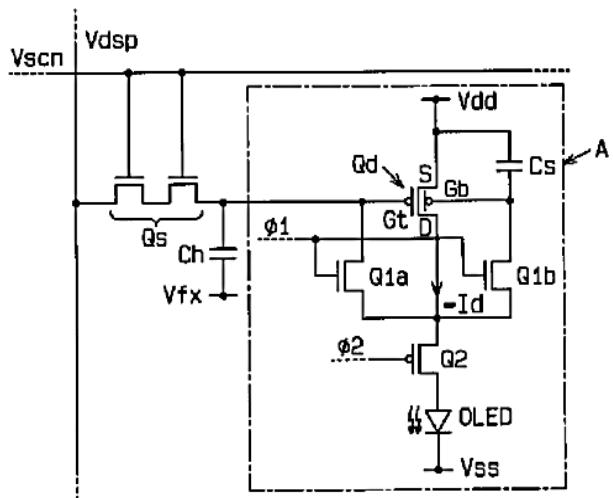

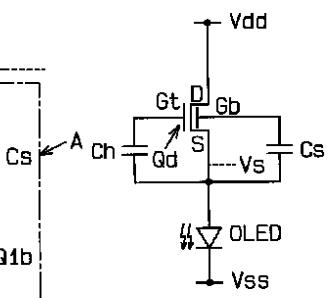

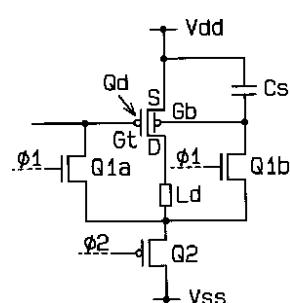

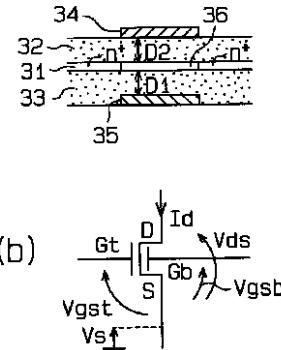

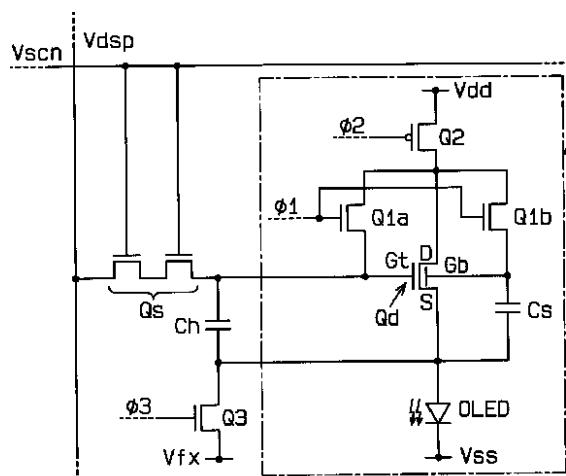

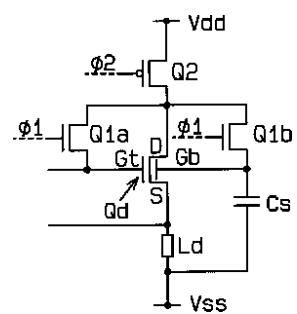

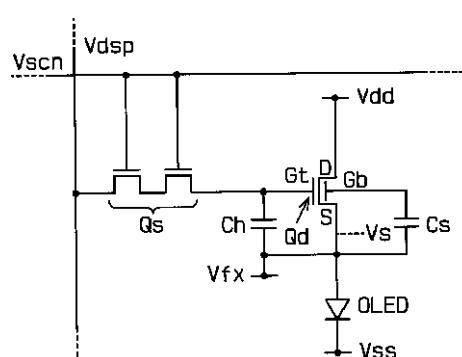

【0034】次に、上記表示部11を構成する各画素の回路について、図2に示す回路図を参照しつつ説明する。図2に示されるように、この画素には、走査信号V<sub>scn</sub>と、画素内のOLEDの発光状態を制御するためのパルス信号1および2とが、表示部11の水平方向にそれぞれに延設されたタイミング信号配線15を介して入力される。これら3つの信号V<sub>scn</sub>、1、および2が、各画素に与えられるタイミング信号となる。また同画素には、表示信号配線16を介して、表示信号V<sub>dsp</sub>も入力される。この表示信号V<sub>dsp</sub>がOLEDを駆動する駆動指令となる。さらに同画素には、水平または垂直方向に延設された電源配線を介して、そのOLEDを発光させるための電源となる基準電位「Vdd」、「Vss」、および「Vfx」が用意され、画素内の各回路要素に接続されている。

【0035】上記周辺回路から与えられる各種信号および基準電位によって、この画素内の各回路は概略、以下のように機能する。すなわちまず、表示信号配線16に当該画素を対象とした表示信号V<sub>dsp</sub>が与えられると、それに同期してタイミング信号配線15に活性化された走査信号V<sub>scn</sub>が与えられて画素スイッチング用トランジスタQ<sub>s</sub>のゲート端子に活性化信号が入力される。これにより、表示信号V<sub>dsp</sub>が駆動用トランジスタQ<sub>d</sub>のゲート端子のノードに伝達されるとともに、この表示信号V<sub>dsp</sub>は信号保持キャバシタC<sub>h</sub>に充電される。これにより、表示信号V<sub>dsp</sub>が画素内の信号保持キャバシタに駆動指令として所定の期間保持される。そして、この画素内に保持された駆動指令を受けて、駆動用トランジスタQ<sub>d</sub>はその入出力特性とOLEDの特性カーブと基準電位「Vdd」および「Vss」とによって定まる電流をOLEDに供給する。

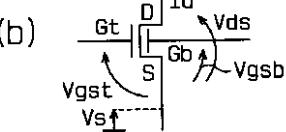

【0036】ここで、本実施の形態の電流駆動回路において用いられる駆動用トランジスタQ<sub>d</sub>は、pチャネル型TFTとして形成されており、相異なる電位に接続可能な2つのゲート端子を備えている。図3(a)は、こ

の駆動用トランジスタQ<sub>d</sub>の断面構造を示す図である。図3(a)に示されるように、この駆動用トランジスタQ<sub>d</sub>は、ガラス基板上にボトムゲート電極25、ボトムゲート絶縁膜23、半導体層21、トップゲート絶縁膜22、およびトップゲート電極24が、薄膜形成技術を用いてこの順に堆積して形成されている。そして、この半導体層21には、ボトムゲート電極25とトップゲート電極24とに対向している部分にチャネル領域26が形成されており、そのチャネル領域26の両側に隣接してp型の導電領域が形成されている。こうした構造において、ボトムゲート電極25またはトップゲート電極24と、上記導電領域の一方(ソース電極)との間に印加される電位差に基づいて、チャネル領域26にキャリアが生成されてソース電極と導電領域の他方(ドレイン電極)との間の導通が制御される。すなわち、この駆動用トランジスタQ<sub>d</sub>には、半導体層21の上下の層に各ゲート絶縁膜を介して形成されたトップゲート電極24とボトムゲート電極25により、チャネル領域26を共有したゲート構造が構成されている。

【0037】なお、本実施の形態においては、ボトムゲート電極25およびトップゲート電極24が半導体層21と対向している面積は等しく形成されている。また、ボトムゲート絶縁膜23およびトップゲート絶縁膜22は同じ材料にて構成されているとともに、それらによってボトムゲート電極25およびトップゲート電極24がそれぞれ半導体層21と離間している距離D1およびD2は相等しく形成されている。このため、ボトムゲート電極25およびトップゲート電極24が半導体層21のチャネル領域26に対してもつ容量は相等しくしてある。

【0038】また、本実施の形態において、トップゲート電極24は、電流駆動回路の駆動指令となる表示信号を受けてこの電位とソース端子との電位差(トップゲート-ソース間電圧)に基づき、ドレイン端子に流れるドレイン電流を制御する用途に使われる。一方、ボトムゲート電極25は、上記ドレイン電流の制御においてこれが顕著に増加し始めるトップゲートソース間電圧(しきい値電圧「Vth」)の値を補正する用途に使われる。

【0039】こうした構造を有する駆動用トランジスタQ<sub>d</sub>を、以下の説明においては、先の図2においてすでに示したように、図3(b)に示す回路記号にて表す。すなわち、図3(b)に示される回路記号は、ソース端子Sとドレイン端子Dとの間に形成されたチャネルに、トップゲート端子G<sub>t</sub>とボトムゲート端子G<sub>b</sub>とが互いに異なる電位に接続可能であることを示している。そして、トップゲート端子G<sub>t</sub>のソース端子Sに対する電位をトップゲート-ソース間電圧「Vgs<sub>t</sub>」、ドレイン端子Dに流れ込む電流(ドレイン電流)を「I<sub>d</sub>」、ボトムゲート端子G<sub>b</sub>のソース端子Sに対する電位をボトムゲート-ソース間電圧「Vgs<sub>b</sub>」、ドレイン端子D

のソース端子Sに対する電位をドレイン-ソース間電圧「 $V_{ds}$ 」、ドレイン端子Dの接地電位に対する電位をドレイン電位「 $V_d$ 」としてそれぞれ表す。ただし、本実施の形態においては、トップゲート-ソース間電圧として「 $-V_{gst}$ 」を、ドレイン電流として「 $-I_d$ 」を、ボトムゲート-ソース間電圧として「 $-V_{g sb}$ 」を、ドレイン-ソース間電圧として「 $-V_{ds}$ 」を、それぞれパラメータとして用いる。

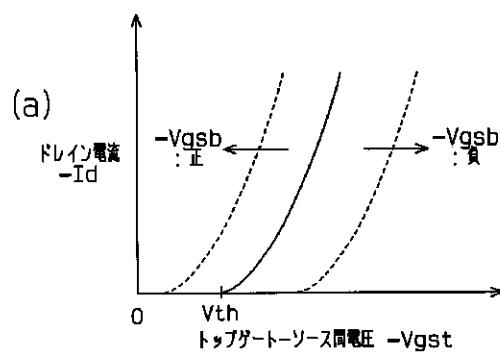

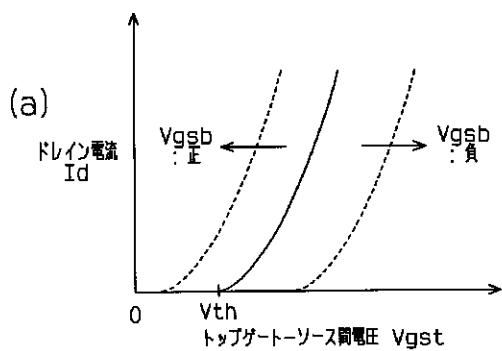

【0040】次に、この駆動用トランジスタQdの電気的特性について、図4を参照しつつ説明する。図4(a)は、駆動用トランジスタQdのドレイン-ソース間電圧「 $-V_{ds}$ 」が一定である条件においての、トップゲート-ソース間電圧「 $-V_{gst}$ 」とドレイン電流「 $-I_d$ 」との関係(以下「 $-V_{gst vs - I_d}$ 」カーブ、という)を示したものである。なお、ボトムゲート-ソース間電圧「 $-V_{g sb}$ 」は「0ボルト」である。図4(a)に実線にて示したように、ドレイン電流「 $-I_d$ 」はトップゲート-ソース間電圧「 $-V_{gst}$ 」を「0ボルト」から増加させてもその値がしきい値電圧「 $V_{th}$ 」を超えるまでは流れない。さらにトップゲート-ソース間電圧「 $-V_{gst}$ 」を増加させてその値がしきい値電圧「 $V_{th}$ 」を超えるようになると、ドレイン電流「 $-I_d$ 」は急激に増加する。ただしそれより正確には、トップゲート-ソース間電圧「 $-V_{gst}$ 」がしきい値電圧「 $V_{th}$ 」以下の値であってもドレイン電流「 $-I_d$ 」は流れるが、その値が無視できる程度の微小さな大きさである、と換言できる。

【0041】そして、この「 $-V_{gst vs - I_d}$ 」カーブは、ボトムゲート-ソース間電圧「 $-V_{g sb}$ 」を変化させることにより左右にシフトさせることができる。これは、トップゲート端子Gtとボトムゲート端子Gbとがチャネルを共有しているためであり、トップゲート端子Gtへの電圧印加とまったく同様に、ボトムゲート端子Gbへの電圧印加によっても同チャネルにキャリアが生成されるためである。すなわちこの場合、ボトムゲート-ソース間電圧「 $-V_{g sb}$ 」を正の値にしたときには、それによりチャネルにキャリアが生成されるため、電流がより流れやすくなっている。「 $-V_{gst vs - I_d}$ 」カーブは左にシフトする。また、ボトムゲート-ソース間電圧「 $-V_{g sb}$ 」を負の値にしたときには、同チャネルにおけるキャリアの生成が抑制されるため、電流がより流れにくくなっている。「 $-V_{gst vs - I_d}$ 」カーブは右にシフトする(図4(a)に点線にて図示)。

【0042】特に、本実施の形態においては上述したように、トップゲート端子Gtのゲート電極24およびボトムゲート端子Gbのゲート電極25が、それらの共有するチャネル領域26に対してもつそれぞれの容量は、相等しくなるように駆動用トランジスタQdが形成されている。したがって、上記「 $-V_{gst vs - I_d}$ 」カーブのシフト量は、ボトムゲート-ソース間電圧「 $-V_{g$

$s b$ 」の値に等しくなる。そして、ボトムゲート端子Gbとソース端子Sとの間に当該トランジスタQdのしきい値電圧を保持するようにすれば、「 $-V_{gst vs - I_d}$ 」カーブの特性が各トランジスタのしきい値電圧の値だけ左にシフトする。これにより、駆動用トランジスタQdは、その入出力特性を各トランジスタがそれぞれにもつしきい値電圧のばらつきに依存しない均一なものとすることができるようになる。

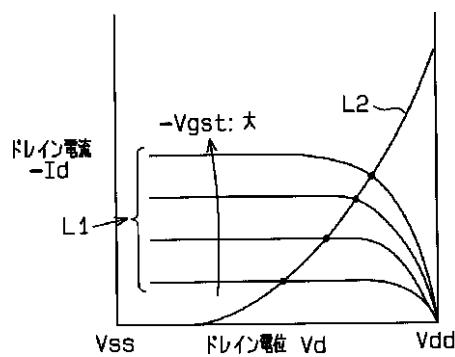

【0043】ちなみに、図4(b)に示す図は、トップゲート-ソース間電圧「 $-V_{gst}$ 」を一定として、ドレイン-ソース間電圧「 $-V_{ds}$ 」を変化させたときのドレイン電流「 $-I_d$ 」の特性を示したものである。図4(b)の実線に示したように、ドレイン電流「 $-I_d$ 」は、ドレイン-ソース間電圧「 $-V_{ds}$ 」の増加とともに増加し、やがて飽和する特性を示す。そして、このドレイン電流「 $-I_d$ 」の特性は、ボトムゲート-ソース間電圧「 $-V_{g sb}$ 」を正の値にすると増加(上)方向に相似形に拡大され、負の値にすると減少(下)方向に相似形に縮小される(図4(b)に点線にて図示)。

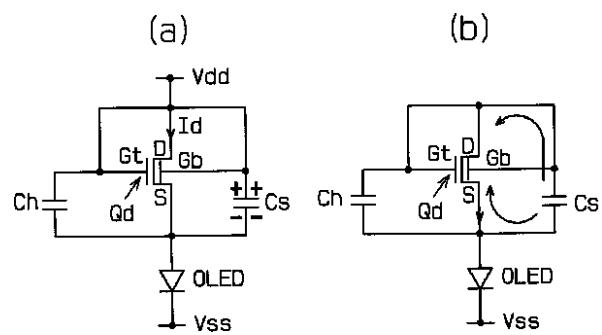

【0044】次に、上記特性をもつ駆動用トランジスタQdを用いて構成した、先の図2に示した電流駆動回路の動作について詳細に説明する。図2に示したように、この電流駆動回路は、画素スイッチング用トランジスタQsおよび駆動用トランジスタQdのほか、駆動用トランジスタQdの周辺にスイッチング素子Q1a、Q1b、およびQ2と、補償用キャパシタCsとを備えている。そして、駆動用トランジスタQdのドレイン端子Dには、トップゲート端子Gtおよびボトムゲート端子Gbとが短絡用スイッチング素子Q1aおよびQ1bを介して接続されており、これらの端子が一時的に共通接続されるようにしてある。また、駆動用トランジスタQdのソース端子Sには、ボトムゲート端子Gbとの間にこれら端子間に所定の期間、電圧を保持可能な補償用キャパシタCsが接続されている。そして、これらは電位の高い方から順に基準電位「 $V_{dd}$ 」、駆動用トランジスタQd、遮断用スイッチング素子Q2、OLED、および「 $V_{ss}$ 」が接続されて、ドレイン電流「 $-I_d$ 」の流れる経路を形成している。ここに、遮断用スイッチング素子Q2は、駆動用トランジスタQdのドレイン電流「 $-I_d$ 」の導通を一時的に遮断させるようにしたものである。なお、短絡用スイッチング素子Q1aおよびQ1bはnチャネル型TFTにて、また遮断用スイッチング素子Q2はpチャネル型TFTにて形成してある。

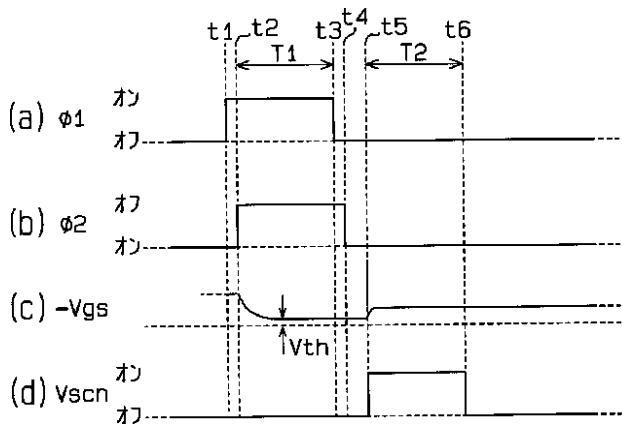

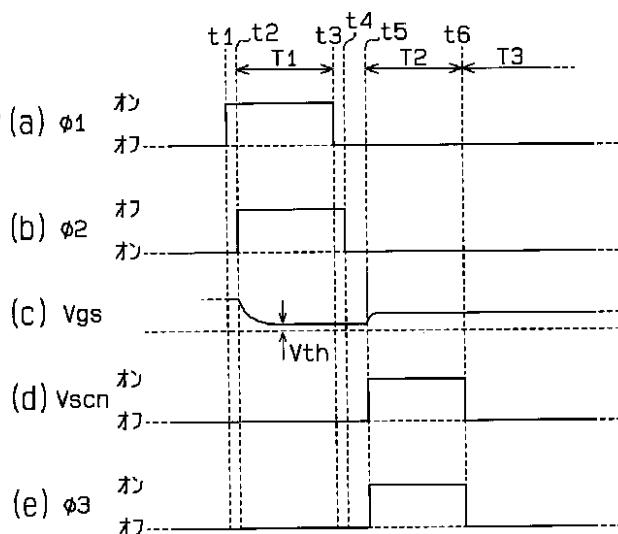

【0045】そして、上記3つのスイッチング素子Q1a、Q1b、およびQ2の開閉動作は、パルス信号1および2に基づいて行われる。図5は、Vスキャナ12(図1参照)からのタイミング信号であるパルス信号1および2と走査信号Vscnの変化を、駆動用トランジスタQdのトップゲート-ソース間電圧「 $-V_{g$

s t」の変化とともに示したタイミングチャートである。図5に示されるように、時刻t1以前においては、パルス信号1および2と走査信号Vscnがすべて「ロー(L)」となっている。すなわち、短絡用スイッチング素子Q1aおよびQ1bと画素スイッチング用トランジスタQsとが「オフ」の状態であり、遮断用スイッチング素子Q2が「オン」の状態である。この状態は、前回の走査信号Vscnによって前回の表示信号Vdspが信号保持キャパシタChに保持された状態であり、そのとき保持されたトップゲート-ソース間電圧「-Vgstd」に基づいて駆動用トランジスタQdがドレイン電流を供給しOLEDを駆動している。

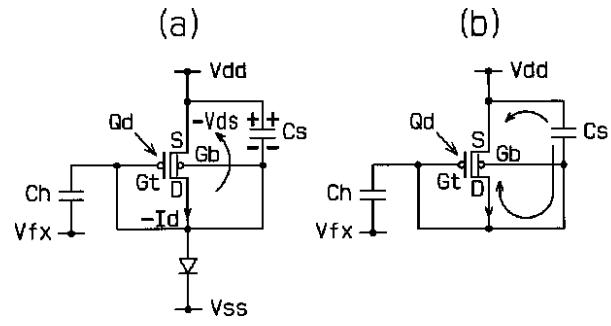

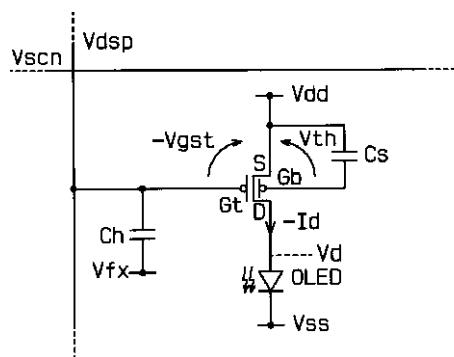

【0046】上記状態においてまず、時刻t1にパルス信号1が「L」から「ハイ(H)」に変化する。これにより、短絡用スイッチング素子Q1aおよびQ1bと遮断用スイッチング素子Q2とがともに「オン」の状態となり、この画素における等価回路が図6(a)に示すものとなる。この図6(a)に示される回路においては、駆動用トランジスタQdはそのトップゲート端子Gtとボトムゲート端子Gbとドレイン端子Dとが一時的に共通接続されて同電位のままドレイン電流「-Id」が流れる。このとき駆動用トランジスタQdのドレイン-ソース間電圧「-Vdds」が補償用キャパシタCsに充電される。続いて、時刻t2にパルス信号2が「H」から「L」に変化する。これにより、遮断用スイッチング素子Q2が「オフ」となり、この画素における等価回路が図6(b)に示すものとなる。この図6(b)に示される回路においては、先に補償用キャパシタCsに充電された電荷が矢印にて示した経路を通って放電され、最終的にソース端子Sとトップゲート端子Gt、ボトムゲート端子Gb、およびドレイン端子Dとの間に保持される電圧が当該駆動用トランジスタQdのしきい値電圧「Vth」と等しくなる(図5の(c)における期間T1)。続いて、時刻t3にパルス信号1が「L」となり、短絡用スイッチング素子Q1aおよびQ1bが「オフ」となる。これにより、補償用キャパシタCsに保持されたしきい値電圧「Vth」が確定される(図示略)。続いて、時刻t4にパルス信号2が「L」となり、遮断用スイッチング素子Q2が「オン」となる。これにより、ドレイン電流「-Id」が流れる経路が再度導通される(図示略)。そして時刻t5に走査信号Vscnが「H」となると画素スイッチング用トランジスタQsが「オン」になり、この画素における等価回路が図7に示すものとなる。すなわちこのとき、補償用キャパシタCsに駆動用トランジスタQdのしきい値電圧「Vth」が保持された状態にて、表示信号Vdspが駆動用トランジスタQdのトップゲート端子Gtに伝達される。同時に、信号保持キャパシタChがその表示信号Vdspによって充電される。これにより、駆動用トランジスタQdは、トップゲート端子Gtに伝達

された表示信号に、しきい値電圧のばらつきが補償された入出力特性(補正された入出力特性)にて動作するようになる。こうして、電流駆動素子であるOLEDは、駆動用トランジスタQdの補正された入出力特性と当該OLEDの特性カーブとによって定まるドレイン電流「Id」が供給され、その電流値に対応した輝度にて発光する。

【0047】図8は、上記駆動用トランジスタQdの補正された入出力特性とOLEDの特性カーブとを、同駆動用トランジスタQdのドレイン電位「Vd」を横軸にとって示したものである。このうち、駆動用トランジスタQdの補正された入出力特性は、図8の曲線群L1に示したように、ドレイン電位「Vd」が高電位側の基準電位「Vdd」のときに電流が流れず、同電位「Vd」が低くなるにつれてドレイン電流「-Id」が増加し、やがて飽和する。そして、このドレイン電流「-Id」の飽和値は、トップゲート-ソース間電圧「-Vgst」の値を大きくすると増加する特性を有する。一方、OLEDの特性カーブは、図8の曲線L2に示したように、ドレイン電位「Vd」が低電位側の基準電位「Vss」から高くなると、あるしきい値を超えた電位で電流が流れ始め、さらにドレイン電位「Vd」が高くなるにしたがって増加する。そして、実際のドレイン電位「Vd」は、これら曲線群L1と曲線L2との交点として定まる。この場合、OLEDの電流電圧特性にはばらつきが生じても、駆動用トランジスタで電流が飽和しているため、各OLEDでほぼ一定量の電流を供給できる。

【0048】以上説明したように、この第1の実施の形態にかかる電流駆動回路および該電流駆動回路を備えた表示装置によれば、以下のような効果を得ることができるようになる。

【0049】(1) 電流駆動回路として、駆動用トランジスタQdの備える2種のゲートのうちのボトムゲート側で、同駆動用トランジスタQdのしきい値電圧「Vth」のばらつきが補償される。このため、表示部11を構成する複数の電流駆動回路に対して、それら電流駆動回路の各駆動用トランジスタQdにおけるしきい値電圧のばらつきの影響が抑制されるようになる。

【0050】これにより、表示部11を構成する各画素のOLEDの駆動指令に対する発光状態(輝度)のばらつきが抑制され、表示装置としてその表示面が均一なものとなる。

【0051】(2) 駆動用トランジスタQdのソース端子Sとボトムゲート端子Gbとの間に当該トランジスタQdのしきい値電圧「Vth」に対応した電荷が補償用キャパシタCsに蓄積保持される。このため、この補償用キャパシタCsに上記しきい値電圧「Vth」に対応した電荷が蓄積保持されている状態で上記駆動用トランジスタQdのトップゲート端子Gtに対して駆動指令(表示信号Vdsp)を印加することにより、上記しき

い値電圧「 $V_{th}$ 」のばらつきを補償することができるようになる。

【0052】(3) 駆動用トランジスタQdのドレン端子Dとトップゲート端子Gtとボトムゲート端子Gbとを一時的に共通接続することができる。このため、補償用キャパシタCsに当該トランジスタQdのしきい値電圧「 $V_{th}$ 」に対応した電荷を保持することができるようになる。

【0053】(4) 補償用キャパシタCsに駆動用トランジスタQdのしきい値電圧「 $V_{th}$ 」を超える電圧に10 対応した所要の充電電荷を確保したのちに、上記ドレン端子Dとトップゲート端子Gtとボトムゲート端子Gbとの一時的な共通接続がなされる。このため、補償用キャパシタCsへのトランジスタQdのしきい値電圧「 $V_{th}$ 」に対応した電荷の保持を、より確かなものとすることができるようになる。

【0054】(5) トップゲート端子Gtに印加される駆動指令(表示信号Vdsp)を蓄積保持することができる。このため、駆動用トランジスタQdによる同駆動指令に基づくOLEDの駆動をより長期間保つことができるようになる。すなわち、表示装置として各画素の発光期間がより長くなるため、表示面の輝度を高めることができるようになる。

【0055】(6) 駆動用トランジスタQdとしてpチャネル型トランジスタが用いられ、OLEDが、ドレン電流「-Id」の流れる経路において同トランジスタQdの下流側に設けられた回路構成とすることができますようになる。

【0056】これにより、OLEDの製造工程に対応した電流駆動回路を備えた表示装置が、pチャネル型トランジスタを用いて適切に機能する回路により構成されるようになる。

【0057】(7) トップゲートおよびボトムゲートによって共有されるチャネル領域とそれら各ゲートの電極との容量が等しく設定される。このため、駆動用トランジスタQdのしきい値電圧「 $V_{th}$ 」のばらつきがより的確に補償されるようになる。

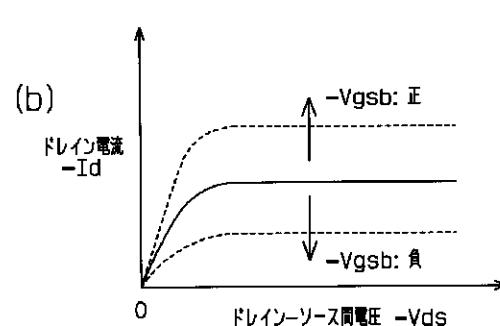

【0058】(第2の実施の形態) 次に、本発明にかかる電流駆動回路および該電流駆動回路を備えた表示装置を、電流駆動素子としてOLEDを駆動する電流駆動回路および該電流駆動回路を備えた表示装置に適用した第2の実施の形態について、図9～図18を参照しつつ、先の第1の実施の形態との相違点を中心に説明する。

【0059】この第2の実施の形態の表示装置としての概略構成も、先に説明した第1の実施の形態とまったく同じである。ただし、本実施の形態の表示装置においては、その表示部11を構成する各画素の電流駆動回路に用いられる駆動用トランジスタQdとして、nチャネル型TFTが用いられている。また、表示信号Vdspが表示信号配線16から画素内に伝達される期間、同駆動

用トランジスタQdのソース端子の電位を固定するためには、充電用スイッチング素子をさらに追加している。なお、先の第1の実施の形態と同様、OLEDはドレン電流の流れる経路においてもっとも低電位側に接続されている。

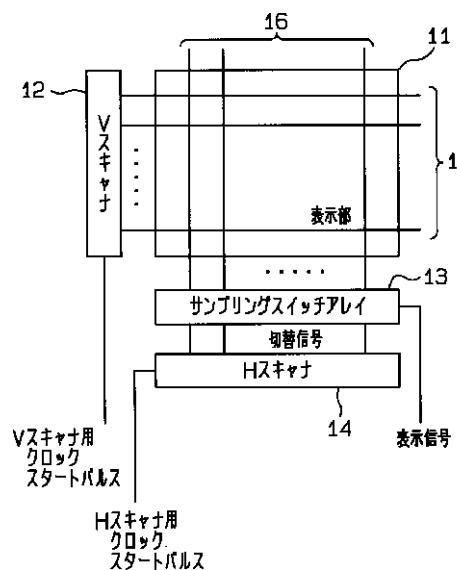

【0060】まず、本実施の形態の表示部11を構成する各画素について、図9に示す回路図を参照しつつ説明する。図9に示されるように、この画素には、走査信号Vscnと、画素内のOLEDの発光状態を制御するためのパルス信号1、2、および3とが、表示部11の水平方向にそれぞれに延設されたタイミング信号配線15を介して入力される。これら4つの信号Vscn、1、2、および3が、各画素に与えられるタイミング信号となる。また、同画素には、先の第1の実施の形態と同様、表示信号Vdspが入力されるとともに、基準電位「Vdd」、「Vbb」、および「Vfx」が用意され、画素内の各回路要素に接続されている。

【0061】そして、表示信号Vdspが走査信号Vscnに同期して画素内の信号保持キャパシタChに充電される動作は、基本的には先の第1の実施の形態のものと同様である。

【0062】ここで、本実施の形態の電流駆動回路において用いられる駆動用トランジスタQdは、上述のようにnチャネル型TFTとして形成されており、相異なる2つの電位に接続可能なゲート端子を備えている。図10(a)は、この駆動用トランジスタQdの断面構造を示す図である。図10(a)に示されるように、この駆動用トランジスタQdは、ガラス基板上にボトムゲート電極35、ボトムゲート絶縁膜33、半導体層31、トップゲート絶縁膜32、およびトップゲート電極34が、薄膜形成技術を用いてこの順に堆積して形成されている。先の第1の実施の形態と相違しているのは、この半導体層31のチャネル領域36の両側に隣接して形成されているのがn型の導電領域である点と、それら導電領域間はゲート電極35または34とソース電極との間への電圧印加に基づいて発生するnチャネルによりその導通が制御される点である。そして、この駆動用トランジスタQdにも、半導体層31の上下の層に各ゲート絶縁膜を介して形成されたトップゲート電極34とボトムゲート電極35により、チャネル領域36を共有したゲート構造が構成されている。なお、本実施の形態においても、トップゲートおよびボトムゲートについて、それぞれの電極面積、絶縁膜の材料、半導体層との離間距離D1およびD2は相等しく形成されている。したがって、ボトムゲート電極35およびトップゲート電極34が半導体層31のチャネル領域36に対してもつ容量は相等しくしてある。

【0063】また、本実施の形態においても、トップゲート電極34が、電流駆動回路の駆動指令となる表示信

号を受けてこの電位とソース端子との電位差（トップゲート - ソース間電圧）に基づき、ドレイン端子に流れるドレイン電流を制御する用途に使われる。一方、ボトムゲート電極25は、上記ドレイン電流の制御においてこれが顕著に増加し始めるトップゲートソース間電圧（しきい値電圧「 $V_{th}$ 」）の値を補正する用途に使われる。

【0064】こうした構造を有する駆動用トランジスタQdを、以下の説明においては、先の図9においてすでに示したように、図10(b)に示す回路記号にて表す。すなわち、図10(b)に示される回路記号は、ソース端子Sとドレイン端子Dとの間に形成されたチャネルに、トップゲート端子Gtとボトムゲート端子Gbが互いに異なる電位に接続可能であることを示している。そして、トップゲート端子Gtのソース端子Sに対する電位をトップゲート - ソース間電圧「 $V_{gst}$ 」、ドレイン端子Dに流れ込む電流（ドレイン電流）を「 $I_d$ 」、ボトムゲート端子Gbのソース端子Sに対する電位をボトムゲート - ソース間電圧「 $V_{g sb}$ 」、ドレイン端子Dのソース端子Sに対する電位をドレン - ソース間電圧「 $V_{ds}$ 」、ソース端子Sの接地電位に対する電位をソース電位「 $V_s$ 」としてそれぞれ表す。ただし、本実施の形態においては、トップゲート - ソース間電圧等これらのパラメータにその正負を逆転させる「-（マイナス）」は付さず、そのままの値を用いることとする。

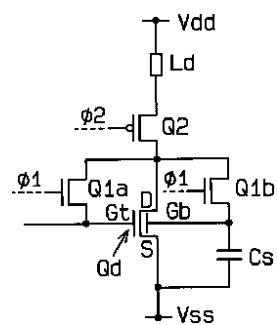

【0065】次に、この駆動用トランジスタQdの電気的特性について、図11を参照しつつ説明する。図11(a)は、駆動用トランジスタQdのドレン - ソース間電圧「 $V_{ds}$ 」が一定である条件においての、トップゲート - ソース間電圧「 $V_{gst}$ 」とドレイン電流「 $I_d$ 」との関係（以下「 $V_{gst}$  vs  $I_d$ 」カーブ、といふ）を示したものである。なお、ボトムゲート - ソース間電圧「 $V_{g sb}$ 」は「0ボルト」である。図11(a)に実線にて示されるように、ドレイン電流「 $I_d$ 」はトップゲート - ソース間電圧「 $V_{gst}$ 」を「0ボルト」から増加させても、その値がしきい値電圧「 $V_{th}$ 」を超えるまでは流れない。さらに、トップゲート - ソース間電圧「 $V_{gst}$ 」を増加させてその値がしきい値電圧「 $V_{th}$ 」を超えるようになると、ドレイン電流「 $I_d$ 」は急激に増加する。

【0066】そして、この「 $V_{gst}$  vs  $I_d$ 」カーブは、先の第1の実施の形態と同様、ボトムゲート - ソース間電圧「 $V_{g sb}$ 」を変化させることにより左右にシフトさせることができる。その理由も、先の第1の実施の形態に説明したとおりである。この場合、「 $V_{g sb}$ 」を正の値にしたときには、それによりチャネルにキャリアが生成されるため、電流がより流れやすくなっている。また、「 $V_{gst}$  vs  $I_d$ 」カーブは左にシフトする。また、ボトムゲート - ソース間電圧「 $V_{g sb}$ 」を負の値にした

ときには、同チャネルにおけるキャリアの生成が抑制されるため、電流がより流れにくくなっている。「 $V_{gst}$  vs  $I_d$ 」カーブは右にシフトする（図11(a)に点線にて図示）。

【0067】特に、本実施の形態においても、トップゲート端子Gtのゲート電極34およびボトムゲート端子Gbのゲート電極35が、それらの共有するチャネル領域36に対してもつそれぞれの容量は、相等しくなるよう駆動用トランジスタQdが形成されている。したがって、上記「 $V_{gst}$  vs  $I_d$ 」カーブのシフト量は、ボトムゲート - ソース間電圧「 $V_{g sb}$ 」の値に等しくなることも、先の第1の実施の形態の場合と同様である。そして、ボトムゲート端子Gbとソース端子Sとの間に当該トランジスタQdのしきい値電圧を保持するようすれば、「 $V_{gst}$  vs  $I_d$ 」カーブの特性が各トランジスタのしきい値電圧の値だけ左にシフトする。これにより、駆動用トランジスタQdは、その入出力特性を各トランジスタがそれぞれにもつしきい値電圧のばらつきに依存しない均一なものとすることができるようになる。

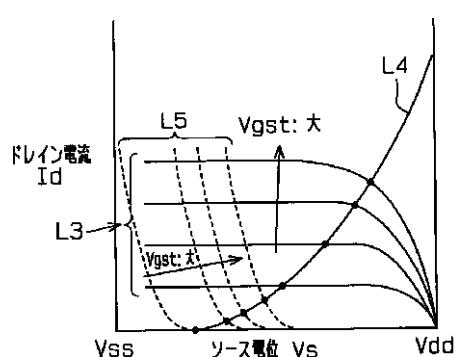

【0068】ちなみに、図11(b)に示す図は、トップゲート - ソース間電圧「 $V_{gst}$ 」を一定として、ドレン - ソース間電圧「 $V_{ds}$ 」を変化させたときのドレイン電流「 $I_d$ 」の特性を示したものである。図11(b)の実線にて示されるように、ドレイン電流「 $I_d$ 」は、ドレン - ソース間電圧「 $V_{ds}$ 」の増加とともに増加し、やがて飽和する特性を示す。そして、このドレイン電流「 $I_d$ 」の特性は、ボトムゲート - ソース間電圧「 $V_{g sb}$ 」を正の値にすると増加（上）方向に相似形に拡大され、負の値にすると減少（下）方向に相似形に縮小される（図11(b)に点線にて図示）。

【0069】次に、上記特性をもつ駆動用トランジスタQdを用いて構成した、先の図9に示した電流駆動回路の動作について詳細に説明する。この電流駆動回路は、先の第1の実施の形態と比較して、駆動用トランジスタQdとしてpチャネル型に代えてnチャネルを用いるためその接続が異なっている。すなわち、図9に示したように、駆動用トランジスタQdのドレイン端子Dには、トップゲート端子Gtおよびボトムゲート端子Gbとが短絡用スイッチング素子Q1aおよびQ1bを介して接続されている。また、同駆動用トランジスタQdのソース端子Sには、ボトムゲート端子Gbとの間にこれら端子間への所定の期間の電圧保持を可能にする補償用キャパシタC<sub>s</sub>が接続されている。そして、これらは電位の高いほうから順に基準電位「 $V_{dd}$ 」、遮断用スイッチング素子Q2、駆動用トランジスタQd、OLED、および「 $V_{ss}$ 」が接続されて、ドレイン電流「 $I_d$ 」の流れる経路を形成している。さらに、この第2の実施の形態において、信号保持キャパシタC<sub>h</sub>は、駆動用トランジスタQdのトップゲート端子Gtとソース端子との間に直接接続されており、該ソース端子Sと接続されて

いるノードは充電用スイッチング素子Q3を介して基準電位「Vfx」に接続されている。なお、この第2の実施の形態においては、短絡用スイッチング素子Q1aおよびQ1bと充電用スイッチング素子Q3とがnチャネル型TFTにて、また遮断用スイッチング素子Q2がpチャネル型TFTにて形成してある。

【0070】そして、上記4つのスイッチング素子Q1a、Q1b、Q2、およびQ3の開閉動作はパルス信号1、2、および3に基づいて行われる。図12は、Vスキャナ12(図1参照)からのタイミング信号であるパルス信号1、2、および3と走査信号Vscnの変化を、駆動用トランジスタQdのトップゲート-ソース間電圧「Vgst」の変化とともに示したタイミングチャートである。図12に示されるように、時刻t1以前においては、パルス信号1、2、および3と走査信号Vscnがすべて「L」となっている。

すなわち、短絡用スイッチング素子Q1aおよびQ1bと充電用スイッチング素子Q3と画素スイッチング用トランジスタQsとが「オフ」の状態であり、遮断用スイッチング素子Q2が「オン」の状態である。この状態は、前回の走査信号Vscnによって前回の表示信号Vdspが信号保持キャパシタChに保持された状態であり、そのとき保持されたトップゲート-ソース間電圧「Vgst」に基づいて駆動用トランジスタQdがドレン電流を供給しOLEDを駆動している。

【0071】上記状態においてまず、時刻t1にパルス信号1が「L」から「H」に変化する。これにより、短絡用スイッチング素子Q1aおよびQ1bと遮断用スイッチング素子Q2とともに「オン」の状態となり、この画素における等価回路が図13(a)に示すものとなる。この図13(a)に示される回路においては、駆動用トランジスタQdはそのトップゲート端子Gtとボトムゲート端子Gbとドレン端子Dとが一時的に共通接続されて同電位のままドレン電流「Id」が流れ、このとき駆動用トランジスタQdのドレン-ソース間電圧「Vds」が補償用キャパシタCsに充電される。続いて、時刻t2にパルス信号2が「H」から「L」に変化する。これにより、遮断用スイッチング素子Q2が「オフ」となり、この画素における等価回路が図13(b)に示すものとなる。この図13(b)に示される回路においては、先に補償用キャパシタCsに充電された電荷が矢印にて示した経路を通って放電され、最終的にソース端子Sとトップゲート端子Gt、ボトムゲート端子Gb、およびドレン端子Dとの間に保持される電圧が当該駆動用トランジスタQdのしきい値電圧「Vth」と等しくなる(図12の(c)における期間T1)。続いて、時刻t3にパルス信号1が「L」となり、短絡用スイッチング素子Q1aおよびQ1bが「オフ」となる。これにより、補償用キャパシタCsを保持されたしきい値電圧「Vth」が確定される(図示50

略)。続いて、時刻t4にパルス信号2が「L」となり、遮断用スイッチング素子Q2が「オン」となる。これにより、ドレン電流「Id」が流れる経路が再度導通される(図示略)。そして時刻t5に走査信号Vscnおよびパルス信号3がともに「H」となると画素スイッチング用トランジスタQsおよび充電用スイッチング素子Q3がともに「オン」になり、この画素における等価回路が図14に示すものとなる。すなわちこのとき、補償用キャパシタCsを駆動用トランジスタQdのしきい値電圧「Vth」が保持された状態にて、表示信号Vdspが駆動用トランジスタQdのトップゲート端子Gtに伝達される。同時に、信号保持キャパシタChがその表示信号Vdspによって充電される。ただしこのとき、ソース電位「Vs」が基準電位「Vfx」に固定される。そして本実施の形態においては、基準電位「Vfx」と基準電位「Vss」との電位差が、OLEDを十分な輝度にて発光させるに十分な値となっていない。したがって、トップゲート-ソース間電圧「Vgst」として十分大きい値が入力された場合であっても、OLEDは発光しない(図12の期間T2)。さらに、時刻t6に走査信号Vscnおよびパルス信号3が「L」になると画素スイッチング用トランジスタQsおよび充電用スイッチング素子Q3がともに「オフ」となり、この画素における等価回路が図15に示すものとなる。この図15に示される回路においては、トップゲート-ソース間電圧「Vgst」が先に信号保持キャパシタChに充電された値のまま、駆動用トランジスタQdのソース電位「Vs」は基準電位「Vfx」から開放される。こうして、駆動用トランジスタQdが、トップゲート端子Gtに伝達された表示信号Vdspに、しきい値電圧のばらつきが補償された入出力特性(補正された入出力特性)にて動作するようになる。それとともに、OLEDには、駆動用トランジスタQdの補正された入出力特性と当該OLEDの特性カーブとによって定まるドレン電流「Id」が供給され、その電流値に対応した輝度にて発光する(図12の期間T3)。なお、このパルス信号3が変化するタイミングと走査信号Vscnが変化するタイミングと同じにする場合には、充電用スイッチング素子Q3を制御するゲート信号として、パルス信号3に代えて走査信号Vscnを用いてよい。また、このパルス信号3が変化するタイミングは、必ずしも走査信号Vscnが変化するタイミングと同じにする必要はない。

【0072】図16は、上記駆動用トランジスタQdの補正された入出力特性とOLEDの特性カーブとを、同駆動用トランジスタQdのソース電位「Vs」を横軸にとって示したものである。このうち、駆動用トランジスタQdの補正された入出力特性は、図16の曲線群L3に示したように、ソース電位「Vs」が高電位側の基準電位「Vdd」のときに電流が流れず、同電位「Vs」

が低くなるにつれてドレン電流「 $I_d$ 」が増加し、やがて飽和する。そして、このドレン電流「 $I_d$ 」の飽和値は、トップゲート - ソース間電圧「 $V_{g s t}$ 」の値を大きくすると増加する特性を有する。一方、OLEDの特性カーブは、図16の曲線L4に示したように、ソース電位「 $V_s$ 」が低電位側の基準電位「 $V_{ss}$ 」から高くなると、あるしきい値を超えた電位で電流が流れ始め、さらにソース電位「 $V_s$ 」が高くなるにしたがって増加する。そして、実際のソース電位「 $V_s$ 」は、これら曲線群L3と曲線L4との交点として定まり、この場合、OLEDの電流電圧特性にはらつきが生じても、駆動用トランジスタで電流が飽和しているため、各OLEDでほぼ一定量の電流を供給できる。

【0073】なお、本実施の形態において、先に説明した第1の実施の形態のように、信号保持キャパシタChの電位基準とする側が基準電位「 $V_{fx}$ 」に接続されない場合、ドレン電流「 $I_d$ 」は以下のように駆動される。すなわち、表示信号Vdspが駆動用トランジスタQdのトップゲート端子Gtに入力されると、その同信号Vdspのソース端子Sに対する電位差に基づいてドレン電流「 $I_d$ 」が流れる。ところが、このドレン電流「 $I_d$ 」が流れることによりソース電位「 $V_s$ 」がもち上がるため、トップゲート - ソース間電圧「 $V_{g st}$ 」が低くなつてドレン電流「 $I_d$ 」は抑制される。こうして、ソース電位「 $V_s$ 」に対するドレン電流「 $I_d$ 」の特性は、OLEDの特性が反映されて図16の点線にて示す曲線群L5のようなものとなる。このため、トップゲート - ソース間電圧「 $V_{g st}$ 」とOLEDを流れる電流「 $I_d$ 」との関係は、同電圧「 $V_{g st}$ 」が小さい領域ではドレン電流「 $I_d$ 」があまり増加せず、同電圧「 $V_{g st}$ 」がある程度の大きさとなつてはじめてドレン電流「 $I_d$ 」の増加が顕著となる特性となる。したがつてこの場合、表示信号Vdspの信号レベルをその特性に対応させて決定したものとすることが好みしい。

【0074】このように、本実施の形態によっても、駆動用トランジスタQdの入出力特性は、同トランジスタQdのしきい値電圧のばらつきが補償されたものとなる。以上説明したように、この第2の実施の形態にかかる電流駆動回路および該電流駆動回路を備えた表示装置によれば、先の第1の実施の形態により得られる(1)～(4)および(7)の効果に加えて、以下のような効果を得ることができるようになる。

【0075】(8)駆動用トランジスタQdとしてnチャネル型トランジスタが用いられ、OLEDが、ドレン電流「 $I_d$ 」の流れる経路において同トランジスタQdの下流側に設けられた回路構成とすることができるようになる。それとともに、画素内に伝達される表示信号を、トップゲート端子Gtとソース端子Sとの間の電位差として好適に蓄積保持することができる。このため、

上記表示信号に基づいた駆動用トランジスタQdによるOLEDの駆動を、定電流動作とすることができます。

【0076】これにより、OLEDの製造工程に対応した電流駆動回路を備えた表示装置が、nチャネル型トランジスタを用いて適切に機能する回路により構成されるようになる。

【0077】(その他の実施の形態)なお、上記各実施の形態は以下のように変更して実施してもよい。

・上記各実施の形態においては、駆動用トランジスタのトップゲートおよびボトムゲートについて、それぞれの電極面積、絶縁膜の材料、半導体層との離間距離D1およびD2が相等しく形成されている場合について例示したが、必ずしもこの構成に限定されるものではない。ボトムゲート電極およびトップゲート電極が半導体層のチャネル領域に対してもつ容量が相等しく形成されていれば、上記各実施の形態によって得られる効果と同じ効果を得ることができる。ただし、同容量が相等しく形成されていない場合であっても、補償用キャパシタCsに駆動用トランジスタQdのしきい値電圧に対応した電荷を蓄積保持することによって、同しきい値電圧のばらつきを補償する上記各実施の形態に準じた効果を得ることができる。

【0078】・上記各実施の形態においては、駆動用トランジスタのトップゲートを表示信号の入力端子として、またボトムゲートをそのしきい値電圧のばらつきの補償用端子として用いた場合について例示したが、これら2つのゲートの機能を相互に入れ替えてもかまわない。また、上記2種の機能をもつゲート構造であれば、上記駆動用トランジスタQdとしてゲート電極を合計で3つ以上備えたものであつてもよい。要は、チャネル領域を共有して上記2種の機能をもつゲートを備えたものであればよい。

【0079】・上記各実施の形態において説明した時刻t1から時刻t2までの遅延時間は、必ずしも必要ではない。同遅延時間を設けない場合であつても、それら各実施の形態に準じた効果を得ることができる。

【0080】・上記各実施の形態においては、タイミング回路から発生されるパルス信号として、短絡用スイッチング素子Q1aおよびQ1bに対するパルス信号1と、遮断用スイッチング素子Q2に対するパルス信号2とを用いて電流駆動回路を機能させる場合について例示したが、必ずしもこの構成とする必要はない。たとえば、短絡用スイッチング素子Q1aおよびQ1bをタイミング回路からのパルス信号に基づいて動作させる一方、遮断用スイッチング素子Q2にはその入力段に同パルス信号に対する遅延素子を設け、これを介して遅延された信号に基づいて動作させるようにしてもよい。この場合、短絡用スイッチング素子Q1aおよびQ1bと遮断用スイッチング素子Q2とを共通のパルス信号に基づいて制御することができるとともに、タイミング信号

配線15の数を削減することができるようになる。

【0081】・短絡用スイッチング素子Q1aおよびQ1bと遮断用スイッチング素子Q2とを共通のパルス信号に基づいて制御しない場合、パルス信号1および2により制御されるスイッチング素子のチャネル型はそれぞれ任意に選ぶことができる。

【0082】・また特に、上記第2の実施の形態においては、充電用スイッチング素子Q3に対する入力として、パルス信号3に代えて走査信号Vscnを用いてもよい。この場合、OLEDを発光駆動させるタイミングが走査信号Vscnにより一意に決定されるほかは、同第2の実施の形態において得られるものと同じ効果が得られるようになる。

【0083】・上記各実施の形態においては、電流駆動回路によって駆動される電流駆動素子としてOLEDが用いられる場合について例示したが、必ずしもこの構成に限定されるものではない。同電流駆動素子としては、OLEDに限らず駆動用トランジスタQdによって駆動可能な任意のものとすることができる。もちろん、表示素子に限定されるものではなく、電流を受容してその機能を発揮する任意の電流受容回路であればよい。

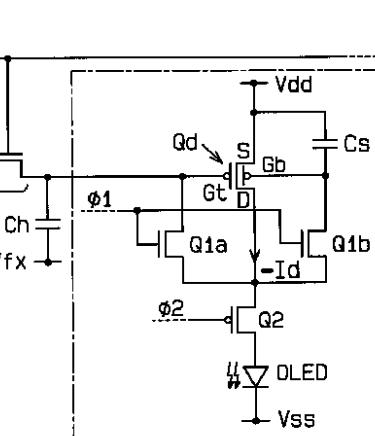

【0084】・上記各実施の形態においては、電流駆動回路の電流駆動素子(Ld)が、ドレイン電流「Id」の流れる経路においてもっとも低電位側に接続された場合について例示したが、必ずしもこの構成に限定されるものではない。同電流駆動素子Ldは、それよりも高電位側において任意の態様に接続してもよい。また、遮断用スイッチング素子Q2の接続態様についても、ドレイン電流「Id」の流れる経路を一時的に遮断できる範囲で変更してもよい。たとえば、図9のB部に対応する部分を、図17に示した回路としてもよい。

【0085】・上記各実施の形態においては、電流駆動回路の駆動用トランジスタQdのしきい値電圧「Vth」を補正する回路について例示したが、同電流駆動回路の電流駆動素子(Ld)もしきい値電圧を有する場合にはこれを含めて補正することもできる。たとえば、上記第1の実施の形態については、図2のA部に対応する部分に代えて図18に示した回路を用いることにより、電流駆動素子Ldのしきい値電圧の補正を含めた入出力特性をもつ電流駆動回路を実現することができる。また、上記第2の実施の形態については、図9のB部に対応する部分に代えて図19に示した回路を用いることにより、上記電流駆動回路と同様のものを実現することができる。

【0086】・上記各実施の形態において、スイッチング素子として必ずしもトランジスタを用いる必要はない。トランジスタに代えて等価回路を変更することのできる任意のスイッチング素子を用いることができる。

【0087】・上記各実施の形態においては、駆動用トランジスタQdをトップゲートとボトムゲートを備えた

TFTにより構成した場合について例示したが、必ずしもこの構成に限定されるものではない。同駆動用トランジスタQdとしては、チャネルを共有し、かつ互いに独立した電位に接続可能な複数のゲート端子をもつトランジスタであればよい。

#### 【0088】

【発明の効果】請求項1記載の発明によれば、電流駆動回路として、駆動用トランジスタの備える2種のゲートのうちの一方で、同駆動用トランジスタのしきい値電圧のばらつきが補償される。このため、たとえ複数の電流駆動回路が設けられた回路であっても、それら電流駆動回路の各駆動用トランジスタにおけるしきい値電圧のばらつきの影響が抑制されるようになる。

【0089】これにより、請求項11記載の、電流駆動回路を備えた表示装置を構成することができるようになる。この表示装置によれば、表示面を構成する各画素の発光素子の駆動指令に対する発光状態(輝度)のばらつきが抑制され、その表示面が均一なものとなる。

【0090】また、請求項2記載の発明によれば、請求項1記載の電流駆動回路において、上記駆動用トランジスタのソース端子と上記2種のゲートのうちの一方の端子との間に当該トランジスタのしきい値電圧に対応した電荷がキャパシタに蓄積保持される。このため、このキャパシタに上記しきい値電圧に対応した電荷が蓄積保持されている状態で上記駆動用トランジスタの他方のゲートに対するゲート電圧を印加することにより、上記しきい値電圧のばらつきを補償することができるようになる。

【0091】これにより、請求項12記載の、電流駆動回路を備えた表示装置を構成することができるようになる。また、請求項3記載の発明によれば、請求項2記載の電流駆動回路において、上記駆動用トランジスタのドレイン端子と前記2種のゲートの各端子とを一時的に共通接続することができる。このため、上記キャパシタに当該トランジスタのしきい値電圧に対応した電荷を保持することができるようになる。

【0092】これにより、請求項13記載の、電流駆動回路を備えた表示装置を構成することができるようになる。また、請求項4記載の発明によれば、請求項3記載の電流駆動回路において、上記キャパシタに所要の充電電荷を確保したのちに、上記ドレイン端子と2種のゲートの各端子との一時的な共通接続がなされる。このため、上記キャパシタへの当該トランジスタのしきい値電圧に対応した電荷の保持を、より確かなものとすることができるようになる。

【0093】これにより、請求項14記載の、電流駆動回路を備えた表示装置を構成することができるようになる。また、請求項5記載の発明によれば、請求項3または4記載の電流駆動回路において、印加されるゲート電圧を蓄積保持することができる。このため、上記駆動用

トランジスタによる同ゲート電圧に基づく電流駆動素子の駆動をより長期間保つことができるようになる。

【0094】これにより、請求項15記載の、電流駆動回路を備えた表示装置を構成することができるようになる。この表示装置によれば、各画素の発光期間がより長くなるため、表示面の輝度を高めることができるようになる。

【0095】また、請求項6記載の発明によれば、請求項3～5のいずれかに記載の電流駆動回路において、上記駆動用トランジスタとしてpチャネル型トランジスタが用いられ、上記電流駆動素子が、上記ドレン電流の流れる経路において同トランジスタの下流側に設けられた回路構成とができるようになる。

【0096】これにより、請求項16記載の、電流駆動回路を備えた表示装置を構成することができるようになる。特に、たとえば、有機発光素子(OLED)を上記電流駆動素子として用いる場合などのように、製造工程等による回路接続に制限がある場合にあっても、pチャネル型トランジスタを用いて適切に機能する回路が構成される。

【0097】また、請求項7記載の発明によれば、請求項6記載の電流駆動回路において、上記しきい値電圧のばらつきの補償を、上記電流駆動素子のしきい値電圧のばらつきを含めたものとすることができるようになる。

【0098】これにより、請求項17記載の、電流駆動回路を備えた表示装置を構成することができるようになる。また、請求項8記載の発明によれば、請求項3または4記載の電流駆動回路において、上記駆動用トランジスタとしてnチャネル型トランジスタが用いられ、上記電流駆動素子が、上記ドレン電流の流れる経路において同トランジスタの下流側に設けられた回路構成とができるようになる。それとともに、印加されるゲート電圧を、上記ゲート端子とソース端子との間の電位差として好適に蓄積保持することができる。このため、同ゲート電圧に基づいた上記駆動用トランジスタによる電流駆動素子の駆動を、定電流動作とすることができます。

【0099】これにより、請求項18記載の、電流駆動回路を備えた表示装置を構成することができるようになる。特に、たとえば、有機発光素子(OLED)を上記電流駆動素子として用いる場合などのように、製造工程等による回路接続に制限がある場合にあっても、nチャネル型トランジスタを用いて適切に機能する回路が構成される。

【0100】また、請求項9記載の発明によれば、請求項8記載の電流駆動回路において、印加されるゲート電圧を、上記ゲート端子とソース端子との間の電位差として蓄積保持することができる。このため、上記駆動用トランジスタによる同ゲート電圧に基づく電流駆動素子の駆動を、定電流動作とすることができます。それとも

に、上記しきい値電圧のばらつきの補償を、上記電流駆動素子のしきい値電圧のばらつきを含めたものとすることができるようになる。

【0101】これにより、請求項19記載の、電流駆動回路を備えた表示装置を構成することができるようになる。また、請求項10記載の発明によれば、請求項1～9のいずれかに記載の電流駆動回路において、上記2種のゲートによって共有されるチャネル領域とそれら各ゲートの電極との容量が等しく設定される。このため、上記駆動用トランジスタのしきい値電圧のばらつきがより的確に補償されるようになる。

【0102】これにより、請求項20記載の、電流駆動回路を備えた表示装置を構成することができるようになる。

#### 【図面の簡単な説明】

【図1】本発明にかかる電流駆動回路を備えた表示装置の実施の形態について、その構成例を模式的に示す図。

【図2】第1の実施の形態にかかる表示装置について、その各画素の回路構成を例示する図。

【図3】上記各画素の回路に用いられる駆動用トランジスタについて、これを例示して説明する図。

【図4】上記駆動用トランジスタの電気特性を例示する図。

【図5】第1の実施の形態の電流駆動回路の動作を例示するタイミングチャート。

【図6】上記電流駆動回路の動作を示す等価回路を示す図。

【図7】上記電流駆動回路の動作を示す等価回路を示す図。

【図8】上記電流駆動回路の電気特性とその動作点について説明する図。

【図9】第2の実施の形態にかかる表示装置について、その各画素の回路構成を例示する図。

【図10】上記各画素の回路に用いられる駆動用トランジスタについて、これを例示して説明する図。

【図11】上記駆動用トランジスタの電気特性を例示する図。

【図12】第2の実施の形態の電流駆動回路の動作を例示するタイミングチャート。

【図13】上記電流駆動回路の動作を示す等価回路を示す図。

【図14】上記電流駆動回路の動作を示す等価回路を示す図。

【図15】上記電流駆動回路の動作を示す等価回路を示す図。

【図16】上記電流駆動回路の電気特性とその動作点について説明する図。

【図17】本発明にかかる電流駆動回路の変形例について、その回路構成を例示する図。

【図18】本発明にかかる電流駆動回路の変形例につい

て、その回路構成を例示する図。

【図19】本発明にかかる電流駆動回路の変形例について、その回路構成を例示する図。

【図20】従来の電流駆動回路について、その回路構成を例示する図。

【図21】上記電流駆動回路に用いられる駆動用トランジスタの電気特性を例示する図。

#### 【符号の説明】

11...表示部、12...Vスキャナ、13...サンプリング\*

\*スイッチアレイ、14...Hスキャナ、15...タイミング信号配線、16...表示信号配線、21...半導体層、22...トップゲート絶縁膜、23...ボトムゲート絶縁膜、24...トップゲート電極、25...ボトムゲート電極、26...チャネル領域、31...半導体層、32...トップゲート絶縁膜、33...ボトムゲート絶縁膜、34...トップゲート電極、35...ボトムゲート電極、36...チャネル領域。

【図1】

【図2】

【図15】

【図4】

【図17】

【図18】

【図5】

【図6】

【図7】

【図8】

(a)

【図9】

【図12】

【図11】

【図13】

【図19】

【図14】

【図16】

【図20】

【図21】

フロントページの続き

|                           |      |               |                         |

|---------------------------|------|---------------|-------------------------|

| (51) Int.CI. <sup>7</sup> | 識別記号 | F I           | テ-マコト <sup>®</sup> (参考) |

| H 0 3 K 17/30             |      | H 0 3 K 17/30 | E                       |

| 17/693                    |      | 17/693        | C                       |

F ターム(参考) 5C080 AA06 BB05 DD05 EE28 FF11

JJ02 JJ03 JJ04 JJ05 JJ06

5J055 AX48 BX03 BX09 CX29 DX13

DX14 EX02 EY10 EY14 EY21

GX01 GX04 GX06 GX07

5J091 AA01 CA15 FA16 HA09 HA17

HA19 HA29 HA39 HA44 KA67

MA22 QA04 TA01 TA02 TA06

5J500 AA01 AC15 AF16 AH09 AH17

AH19 AH29 AH39 AH44 AK67

AM22 AQ04 AT01 AT02 AT06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电流驱动电路和具有电流驱动电路的显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2003224437A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2003-08-08 |

| 申请号            | JP2002021844                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2002-01-30 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 佐野景一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 佐野 景一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/20 G09G3/30 H01L51/50 H03F3/34 H03K17/30 H03K17/693                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | H03F3/34.C G09G3/20.611.H G09G3/20.624.B G09G3/20.641.D G09G3/30.J H03K17/30.E H03K17/693.C G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291 H03F3/34.230 H05B33/14.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5J055/AX48 5J055/BX03 5J055/BX09 5J055/CX29 5J055/DX13 5J055/DX14 5J055/EX02 5J055/EY10 5J055/EY14 5J055/EY21 5J055/GX01 5J055/GX04 5J055/GX06 5J055/GX07 5J091/AA01 5J091/CA15 5J091/FA16 5J091/HA09 5J091/HA17 5J091/HA19 5J091/HA29 5J091/HA39 5J091/HA44 5J091/KA67 5J091/MA22 5J091/QA04 5J091/TA01 5J091/TA02 5J091/TA06 5J500/AA01 5J500/AC15 5J500/AF16 5J500/AH09 5J500/AH17 5J500/AH19 5J500/AH29 5J500/AH39 5J500/AH44 5J500/AK67 5J500/AM22 5J500/AQ04 5J500/AT01 5J500/AT02 5J500/AT06 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE04 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/BA36 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB05 5C380/BB22 5C380/CA09 5C380/CA12 5C380/CA24 5C380/CB01 5C380/CB17 5C380/CC04 5C380/CC07 5C380/CC26 5C380/CC77 5C380/CD026 5C380/CD027 5C380/CE04 5C380/DA02 5C380/DA06 5C380/HA02 5C380/HA03 5C380/HA05 5C380/HA08 5C380/HA13 |         |            |

| 代理人(译)         | 柴野Seimiyabi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

要解决的问题：提供能够抑制驱动晶体管中的阈值电压的波动效应的电流驱动电路，以及配备有电流驱动电路的显示装置。解决方案：为显示装置的每个像素提供用于驱动OLED（有机发光装置）的电流驱动电路，其使用OLED作为光发射器。显示信号Vdsp经由像素开关晶体管Qs输入到驱动晶体管Qd。驱动晶体管Qd由薄膜晶体管形成，栅电极设置在半导体层的上/下层，并且两个栅电极包括共用沟道区的结构。在驱动OLED时，使用用于使Q1a和Q1b短路的开关元件和用于关断Q2的开关元件预先在阈值电压Vth累积并保持在补偿电容器Cs，并且在这种情况下，显示信号Vdsp被输入到驱动晶体管QD。