(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-128386

(P2012-128386A)

(43) 公開日 平成24年7月5日(2012.7.5)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 611H 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 642A 5C380  |

|                             | G09G 3/20 | 624B        |

|                             | G09G 3/20 | 660V        |

審査請求 未請求 請求項の数 32 O L (全 18 頁) 最終頁に続く

(21) 出願番号 特願2011-35463 (P2011-35463)

(22) 出願日 平成23年2月22日 (2011.2.22)

(31) 優先権主張番号 10-2010-0126489

(32) 優先日 平成22年12月10日 (2010.12.10)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 308040351

三星モバイルディスプレイ株式會社

Samsung Mobile Display Co., Ltd.

大韓民国京畿道龍仁市器興区農書洞山24

San #24 Nongseo-Dong,

Giheung-Gu, Yongin

-City, Gyeonggi-Do 4

46-711 Republic of

KOREA

(74) 代理人 100146835

弁理士 佐伯 義文

(74) 代理人 100089037

弁理士 渡邊 隆

最終頁に続く

(54) 【発明の名称】画素、これを用いた表示装置、及びその駆動方法

## (57) 【要約】

【課題】ヒステリシスによって発生する応答速度の問題を解決し、画面上のモーションブラーを改善すると同時に、駆動トランジスタのしきい電圧偏差を補償する画素回路構造を提案する。

【解決手段】本発明は、画素、これを含む表示装置、及びその駆動方法に関し、具体的に表示装置に含まれる画素は、有機発光ダイオード、前記有機発光ダイオードに前記伝達されるデータ信号による駆動電流を伝達する駆動トランジスタ、第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタ、前記駆動トランジスタのゲート電極電圧を初期化する初期化期間の間に、第2走査信号に対応して前記駆動トランジスタのソース電極に第1電源電圧を印加する第2トランジスタ、及び前記駆動トランジスタのゲート電極に接続する第1電極及び前記第1電源電圧に接続する第2電極を含むキャパシタを含む。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

複数の走査信号が伝達される複数の走査線、複数のデータ信号が伝達される複数のデータ線、及び複数の発光制御信号が伝達される複数の発光制御線にそれぞれ接続された複数の画素を含む表示部と、前記複数の走査信号を伝達する走査駆動部と、前記複数のデータ信号を伝達するデータ駆動部と、及び前記複数の発光制御信号を伝達する発光駆動部とを含み、

前記複数の画素それぞれは、

有機発光ダイオード；

前記有機発光ダイオードに前記伝達されたデータ信号による駆動電流を伝達する駆動トランジスタ；

第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタ；

前記駆動トランジスタのゲート電極電圧を初期化する初期化期間の間に、第2走査信号に対応して前記駆動トランジスタの第1電極に第1電源電圧を印加する第2トランジスタ；及び

前記駆動トランジスタのゲート電極に接続する第1電極及び前記第1電源電圧に接続する第2電極を含むキャパシタを含む表示装置。

## 【請求項 2】

前記初期化期間の間に前記駆動トランジスタのゲート電極電圧と第1電極電圧との電圧差は前記駆動トランジスタを動作させる電圧である、請求項1に記載の表示装置。

## 【請求項 3】

前記第1トランジスタは、前記第1走査信号によってスイッチング動作して、前記駆動トランジスタの第1電極に前記データ信号を伝達する、請求項1に記載の表示装置。

## 【請求項 4】

前記第2走査信号は、前記第1走査信号が伝達される走査線の前の走査線に伝達される走査信号である、請求項1に記載の走査信号の表示装置。

## 【請求項 5】

前記走査駆動部は、前記複数の画素それぞれに前記第1走査信号及び前記第2走査信号を伝達する、請求項1に記載の表示装置。

## 【請求項 6】

前記複数の画素それぞれは、

前記初期化期間の間に前記駆動トランジスタのゲート電極に初期化電圧を供給して、駆動トランジスタのゲート電極電圧を初期化させる初期化トランジスタをさらに含む、請求項1に記載の表示装置。

## 【請求項 7】

前記初期化トランジスタは、前記複数の画素それぞれの第1トランジスタに伝達される第1走査信号が伝達される走査線の前の走査線に伝達される第2走査信号に対応してスイッチング動作する、請求項6に記載の表示装置。

## 【請求項 8】

前記初期化期間は、前記初期化トランジスタに伝達される第2走査信号がゲートオン電圧レベルで伝達される期間である、請求項6に記載の表示装置。

## 【請求項 9】

前記初期化期間は、前記駆動トランジスタのしきい電圧が補償される期間より前である、請求項1に記載の表示装置。

## 【請求項 10】

前記複数の画素それぞれは、

前記初期化期間の後に、前記第1走査信号によってスイッチング動作して前記駆動トランジスタをダイオード接続し、前記駆動トランジスタのしきい電圧を補償するしきい電圧補償トランジスタをさらに含む、請求項1に記載の表示装置。

10

20

30

40

50

**【請求項 1 1】**

前記複数の画素それぞれは、

前記データ信号による駆動電流が伝達される前記有機発光ダイオードの発光を制御する少なくとも一つの発光制御トランジスタをさらに含む、請求項 1 に記載の表示装置。

**【請求項 1 2】**

前記発光制御トランジスタは、前記複数の画素それぞれに含まれている第 1 トランジスタ及び第 2 トランジスタにそれぞれゲートオン電圧レベルの第 1 走査信号及び第 2 走査信号が伝達された後、ゲートオン電圧レベルで伝達される発光制御信号に対応してスイッチング動作する、請求項 1 1 に記載の表示装置。

**【請求項 1 3】**

有機発光ダイオード；

前記有機発光ダイオードに前記伝達されたデータ信号による駆動電流を伝達する駆動トランジスタ；

第 1 走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第 1 トランジスタ；

前記駆動トランジスタのゲート電極電圧を初期化する初期化期間の間に、第 2 走査信号に対応して前記駆動トランジスタのソース電極に第 1 電源電圧を印加する第 2 トランジスタ；及び

前記駆動トランジスタのゲート電極に接続する第 1 電極及び前記第 1 電源電圧に接続する第 2 電極を含むキャパシタを含む画素。

**【請求項 1 4】**

前記初期化期間の間の前記駆動トランジスタのゲート電極電圧とソース電極電圧との電圧差は、前記駆動トランジスタを動作させる電圧である、請求項 1 3 に記載の画素。

**【請求項 1 5】**

前記第 1 トランジスタは、前記第 1 走査信号が伝達されるゲート電極、前記データ信号が伝達されるソース電極、及び前記駆動トランジスタのソース電極に接続されるドレイン電極を含み、

前記第 1 走査信号によってスイッチング動作して、前記駆動トランジスタのソース電極に前記データ信号を伝達する、請求項 1 3 に記載の画素。

**【請求項 1 6】**

前記第 2 走査信号は、前記第 1 走査信号が伝達される走査線の前の走査線に伝達される走査信号である、請求項 1 3 に記載の画素。

**【請求項 1 7】**

前記画素は、

前記初期化期間の間に前記駆動トランジスタのゲート電極に初期化電圧を供給して、駆動トランジスタのゲート電極電圧を初期化させる初期化トランジスタをさらに含む、請求項 1 3 に記載の画素。

**【請求項 1 8】**

前記初期化トランジスタは、

第 2 走査信号が伝達されるゲート電極、前記初期化電圧が印加されるソース電極、及び前記駆動トランジスタのゲート電極に接続されるドレイン電極を含み、前記第 2 走査信号に対応してスイッチング動作する、請求項 1 7 に記載の画素。

**【請求項 1 9】**

前記初期化期間は、前記初期化トランジスタに伝達される第 2 走査信号がゲートオン電圧レベルで伝達される期間である、請求項 1 7 に記載の画素。

**【請求項 2 0】**

前記初期化期間は、前記駆動トランジスタのしきい電圧が補償される期間より前である、請求項 1 3 に記載の画素。

**【請求項 2 1】**

前記画素は、

10

20

30

40

50

前記初期化期間の後に、前記第1走査信号によってスイッチング動作して前記駆動トランジスタをダイオード接続し、前記駆動トランジスタのしきい電圧を補償するしきい電圧補償トランジスタをさらに含む、請求項13に記載の画素。

**【請求項22】**

前記画素は、

前記第1電源電圧源と有機発光ダイオードとの間に接続し、前記データ信号による駆動電流が伝達される前記有機発光ダイオードの発光を制御する発光制御信号が伝達されるゲート電極を含む少なくとも一つの発光制御トランジスタをさらに含む、請求項13に記載の画素。

**【請求項23】**

前記発光制御信号は、

前記画素に含まれる第1トランジスタ及び第2トランジスタにそれぞれゲートオン電圧レベルの第1走査信号及び第2走査信号が伝達された後に、ゲートオン電圧レベルで伝達される、請求項22に記載の画素。

**【請求項24】**

前記発光制御トランジスタは、

前記発光制御信号が伝達されるゲート電極、前記駆動トランジスタのドレイン電極に接続されるソース電極、及び前記有機発光ダイオードのアノード電極に接続されるドレイン電極を含む、請求項22に記載の画素。

**【請求項25】**

前記発光制御トランジスタは、

前記発光制御信号が伝達されるゲート電極、前記第1電源電圧源に接続されるソース電極、及び前記駆動トランジスタのソース電極に接続されるドレイン電極を含む、請求項22に記載の画素。

**【請求項26】**

複数の画素を含み、前記複数の画素それぞれは、有機発光ダイオード、前記有機発光ダイオードにデータ信号による駆動電流を伝達する駆動トランジスタ、第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタ、第2走査信号に対応して前記駆動トランジスタに第1電源電圧を印加する第2トランジスタ、及び前記駆動トランジスタと前記第1電源電圧源との間に接続されるキャパシタを含む表示装置の駆動方法において、

前記駆動トランジスタのゲート電極電圧を初期化する段階；

前記駆動トランジスタのしきい電圧を補償し、前記駆動トランジスタに前記データ信号が伝達される段階；及び

前記データ信号による駆動電流で前記有機発光ダイオードが発光する段階を含み、

前記初期化する間に前記第2走査信号がゲートオン電圧レベルで伝達される表示装置の駆動方法。

**【請求項27】**

前記初期化する間の前記駆動トランジスタのゲート電極-ソース電極間の電圧は、前記駆動トランジスタを動作させる電圧である、請求項26に記載の表示装置の駆動方法。

**【請求項28】**

前記第2走査信号は、前記第1走査信号が伝達される走査線の前の走査線に伝達される走査信号である、請求項26に記載の表示装置の駆動方法。

**【請求項29】**

前記駆動トランジスタのゲート電極電圧を初期化する段階は、

前記第2走査信号によってスイッチング動作する初期化トランジスタにより、前記駆動トランジスタのゲート電極に初期化電圧が印加される、請求項26に記載の表示装置の駆動方法。

**【請求項30】**

前記駆動トランジスタのしきい電圧を補償する段階は、

10

20

30

40

50

前記第1走査信号によってスイッチング動作するしきい電圧補償トランジスタによって前記駆動トランジスタがダイオード接続する、請求項26に記載の表示装置の駆動方法。

### 【請求項31】

前記有機発光ダイオードが発光する段階は、

前記第1電源電圧源と有機発光ダイオードとの間に接続し、発光制御信号によってスイッチング動作する少なくとも一つ以上の発光制御トランジスタによって前記有機発光ダイオードの発光が制御される、請求項26に記載の表示装置の駆動方法。

### 【請求項32】

前記発光制御信号は、

画素に含まれる第1トランジスタ及び第2トランジスタにそれぞれゲートオン電圧レベルの第1走査信号及び第2走査信号が伝達された後、ゲートオン電圧レベルで伝達される、請求項31に記載の表示装置の駆動方法。

10

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、画素と、これを含む表示装置、及びその駆動方法に関し、具体的に画素駆動時の応答速度の遅延問題と画面のモーションブラー(motion blur)を改善するための画素構造、及びその駆動方法に関する。

#### 【背景技術】

#### 【0002】

近来、陰極線管(Cathode Ray Tube)の短所である重量と体積を減らせる各種平板表示装置が開発されている。平板表示装置としては、液晶表示装置(Liquid Crystal Display:LCD)、電界放出表示装置(Field Emission Display:FED)、プラズマ表示パネル(Plasma Display Panel:PDP)、及び表示装置(Organic Light Emitting Display:OLED)などがある。

20

#### 【0003】

平板表示装置のうちの表示装置は、電子と正孔の再結合によって光を発生する有機発光ダイオードを利用して映像を表示するもので、速い応答速度を有すると共に、低い消費電力で駆動され、発光効率、輝度、及び視野角に優れた長所があつて注目されている。

30

通常、有機電界発光表示装置(OLED)は、有機発光ダイオードを駆動する方式によってパッシブマトリックス型OLED(PMOLED)とアクティブマトリックス型OLED(AMOLED)に分類される。

#### 【0004】

この中で、解像度、コントラスト、動作速度の観点で、単位画素ごとに選択して点灯するアクティブマトリックス型OLED(AMOLED)が主流となっている。

アクティブマトリックス型OLEDの1画素は、有機発光ダイオード、有機発光ダイオードに供給される電流量を制御する駆動トランジスタ、及び駆動トランジスタに有機発光ダイオードの発光量を制御するデータ信号を伝達するスイッチングトランジスタを含む。

40

#### 【0005】

最近、アクティブマトリックス型OLEDの画素に含まれる駆動トランジスタのしきい電圧偏差を補償するための補償回路に対する研究が行われている。しかし、補償回路を使用して目的とする輝度を表示することにおいて、ヒステリシス(Hysteresis)によってデータ電圧の増減による応答速度が変化して正確な階調表現に困難がある。特に、応答速度はブラックからホワイトに輝度を表現するために駆動する時に遅延する問題があり、このような問題点は、画面でテキスト(text)をスクロール(scroll)する時、モーションブラー(motion blur)を発生する。

したがって、画素のしきい電圧トランジスタの偏差を補償すると同時に、ヒステリシスによる応答速度問題を解決するための画素回路に対する改善が必要である。

### 【発明の概要】

50

**【発明が解決しようとする課題】****【0006】**

本発明は上記問題点を解決するために案出されたものであって、本発明の目的は、ヒステリシスによって発生する応答速度の問題を解決し、画面上のモーションブラーを改善すると同時に、駆動トランジスタのしきい電圧偏差を補償する画素回路構造を提案することにある。

**【0007】**

また、本発明の他の目的は、駆動トランジスタのしきい電圧偏差を補償することができ、特に、輝度偏差が大きいデータ信号による映像を表示することにおいて、応答速度の遅延問題を解決して、正確な階調表現が行われる高品質、高画質の表示装置、及びその駆動方法を提供することにある。

10

**【0008】**

本発明が目的とする技術的課題は、以上で言及した技術的課題に制限されず、言及されないまた他の技術的課題は本発明の記載から当該分野における通常の知識を有する者に明確に理解できるはずである。

**【課題を解決するための手段】****【0009】**

上記目的を達成するための本発明の表示装置は、複数の走査信号が伝達される複数の走査線、複数のデータ信号が伝達される複数のデータ線、及び複数の発光制御信号が伝達される複数の発光制御線にそれぞれ接続される複数の画素を含む表示部と、前記複数の走査信号を伝達する走査駆動部と、前記複数のデータ信号を伝達するデータ駆動部と、前記複数の発光制御信号を伝達する発光駆動部とを含む表示装置である。

20

**【0010】**

この時、前記複数の画素それぞれは、有機発光ダイオードと、前記有機発光ダイオードに前記伝達されたデータ信号による駆動電流を伝達する駆動トランジスタと、第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタと、前記駆動トランジスタのゲート電極電圧を初期化する初期化期間の間に、第2走査信号に対応して前記駆動トランジスタの第1電極に第1電源電圧を印加する第2トランジスタと、前記駆動トランジスタのゲート電極に接続する第1電極及び前記第1電源電圧に接続する第2電極を含むキャパシタとを含む。

30

**【0011】**

前記初期化期間の間の前記駆動トランジスタのゲート電極電圧と第1電極電圧との電圧差は、前記駆動トランジスタを動作させられる電圧とことができる。即ち、本発明によれば、前記初期化期間の間の前記駆動トランジスタのゲート電極電圧と第1電極電圧との差に対応する電圧値( $V_{g s}$ )を、前記駆動トランジスタの動作時に必要な基準電圧以上に維持する。この時、前記基準電圧をオンバイアス(On bias)と定義できる。

**【0012】**

前記電圧値( $V_{g s}$ )をオンバイアス以上に維持するために、初期化期間の間に、前記駆動トランジスタのゲート電極に伝達される電圧はローレベルであり、前記駆動トランジスタの第1電極に伝達される第1電源電圧はハイレベルとすることができる。

40

**【0013】**

本発明の表示装置において、前記第1トランジスタは前記第1走査信号によってスイッチング動作して、前記駆動トランジスタの第1電極に前記データ信号を伝達できる。

前記第2走査信号は、前記第1走査信号が伝達される走査線の前の走査線に伝達される走査信号とすることができますが、これに必ずしも制限されることではない。

前記走査駆動部は、前記複数の画素それぞれに前記第1走査信号及び前記第2走査信号を伝達できる。

**【0014】**

一方、本発明の一実施形態において、前記複数の画素それぞれは、前記初期化期間の間に前記駆動トランジスタのゲート電極に初期化電圧を供給して、駆動トランジスタのゲー

50

ト電極電圧を初期化させる初期化トランジスタをさらに含むことができる。

この時、前記初期化トランジスタは、前記複数の画素それぞれの第1トランジスタに伝達される第1走査信号が伝達される走査線の前の走査線に伝達される第2走査信号に対応してスイッチング動作する。

【0015】

前記初期化期間は、前記初期化トランジスタに伝達される第2走査信号がゲートオン電圧レベルで伝達される期間である。

また、前記初期化期間は、前記駆動トランジスタのしきい電圧が補償される期間より前である。

【0016】

本発明の他の実施形態において、前記複数の画素それぞれは、前記初期化期間の後に前記第1走査信号によってスイッチング動作して前記駆動トランジスタをダイオード接続し、前記駆動トランジスタのしきい電圧を補償するしきい電圧補償トランジスタをさらに含むことができる。

【0017】

また、前記複数の画素それぞれは、前記データ信号による駆動電流が伝達される前記有機発光ダイオードの発光を制御する少なくとも一つの発光制御トランジスタをさらに含むことができる。

この時、前記発光制御トランジスタは、前記複数の画素それぞれに含まれる第1トランジスタ及び第2トランジスタにそれぞれゲートオン電圧レベルの第1走査信号及び第2走査信号が伝達された後、ゲートオン電圧レベルで伝達される発光制御信号に対応してスイッチング動作する。

【0018】

上記目的を達成するための本発明の画素は、有機発光ダイオードと、前記有機発光ダイオードに前記伝達されたデータ信号による駆動電流を伝達する駆動トランジスタと、第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタと、前記駆動トランジスタのゲート電極電圧を初期化する初期化期間の間に、第2走査信号に対応して前記駆動トランジスタのソース電極に第1電源電圧を印加する第2トランジスタと、前記駆動トランジスタのゲート電極に接続する第1電極及び前記第1電源電圧に接続する第2電極を含むキャパシタとを含む。

【0019】

この時、前記初期化期間の間の前記駆動トランジスタのゲート電極電圧とソース電極電圧との電圧差は、前記駆動トランジスタを動作させる電圧とすることができる。好ましくは、前記初期化期間の間に、前記ゲート電極に印加される電圧はローレベルであり、前記ソース電極に印加される第1電源電圧はハイレベルとすることができるが、これに必ずしも制限されることではなく、前記駆動トランジスタのゲート - ソース電圧差が駆動トランジスタを動作させるオンバイアスに維持されればよい。

【0020】

前記第1トランジスタは、前記第1走査信号が伝達されるゲート電極、前記データ信号が伝達されるソース電極、及び前記駆動トランジスタのソース電極に接続されるドレイン電極を含み、前記第1走査信号によってスイッチング動作して、前記駆動トランジスタのソース電極に前記データ信号を伝達する。

【0021】

本発明の画素において、前記第2走査信号は前記第1走査信号が伝達される走査線の前の走査線に伝達される走査信号とすることができる。

前記画素は、前記初期化期間の間に前記駆動トランジスタのゲート電極に初期化電圧を供給して、駆動トランジスタのゲート電極電圧を初期化させる初期化トランジスタをさらに含むことができる。

【0022】

この時前、記初期化トランジスタは、第2走査信号が伝達されるゲート電極、前記初期

10

20

30

40

50

化電圧が印加されるソース電極、及び前記駆動トランジスタのゲート電極に接続されるドレイン電極を含み、前記第2走査信号に対応してスイッチング動作する。

前記初期化期間は、前記初期化トランジスタに伝達される第2走査信号がゲートオン電圧レベルで伝達される期間である。

また、前記初期化期間は、前記駆動トランジスタのしきい電圧が補償される期間より前である。

#### 【0023】

前記画素は、前記初期化期間の後に、前記第1走査信号によってスイッチング動作して前記駆動トランジスタをダイオード接続し、前記駆動トランジスタのしきい電圧を補償するしきい電圧補償トランジスタをさらに含むことができる。

前記画素は、前記第1電源電圧源と有機発光ダイオードとの間に接続し、前記データ信号による駆動電流が伝達される前記有機発光ダイオードの発光を制御する発光制御信号が伝達されるゲート電極を含む少なくとも一つの発光制御トランジスタをさらに含むことができる。

#### 【0024】

この時、前記発光制御信号は、前記画素に含まれる第1トランジスタ及び第2トランジスタにそれぞれゲートオン電圧レベルの第1走査信号及び第2走査信号が伝達された後、ゲートオン電圧レベルで伝達できる。

#### 【0025】

前記発光制御トランジスタは、実施形態により、前記発光制御信号が伝達されるゲート電極、前記駆動トランジスタのドレイン電極に接続されるソース電極、及び前記有機発光ダイオードのアノード電極に接続されるドレイン電極を含むことができる。

また、他の実施形態により、前記発光制御トランジスタは、前記発光制御信号が伝達されるゲート電極、前記第1電源電圧源に接続されるソース電極、及び前記駆動トランジスタのソース電極に接続されるドレイン電極を含むことができる。

#### 【0026】

上記目的を達成するための本発明の表示装置の駆動方法は、複数の画素を含み、前記複数の画素それぞれは、有機発光ダイオードと、前記有機発光ダイオードにデータ信号による駆動電流を伝達する駆動トランジスタと、第1走査信号に対応して前記駆動トランジスタに前記データ信号を伝達する第1トランジスタと、第2走査信号に対応して前記駆動トランジスタに第1電源電圧を印加する第2トランジスタと、前記駆動トランジスタと前記第1電源電圧源との間に接続されるキャパシタとを含む表示装置の駆動方法に関する。

#### 【0027】

具体的に本発明の駆動方法は、前記駆動トランジスタのゲート電極電圧を初期化する段階と、前記駆動トランジスタのしきい電圧を補償し、前記駆動トランジスタに前記データ信号が伝達される段階と、前記データ信号による駆動電流で前記有機発光ダイオードが発光する段階とを含む。この時、前記初期化する間に前記第2走査信号がゲートオン電圧レベルで伝達される。

#### 【0028】

前記初期化する間の前記駆動トランジスタのゲート電極 - ソース電極間の電圧は、前記駆動トランジスタを動作させる電圧とすることができる。

前記第2走査信号は、前記第1走査信号が伝達される走査線の前の走査線に伝達される走査信号とすることができますが、これに必ずしも制限されることではない。

#### 【0029】

前記駆動トランジスタのゲート電極電圧を初期化する段階は、前記第2走査信号によってスイッチング動作する初期化トランジスタにより、前記駆動トランジスタのゲート電極に初期化電圧が印加される段階である。

また、前記駆動トランジスタのしきい電圧を補償する段階は、前記第1走査信号によってスイッチング動作するしきい電圧補償トランジスタにより、前記駆動トランジスタがダイオード接続する段階である。

10

20

30

40

50

**【0030】**

本発明の駆動方法において、前記第1走査信号に対応して前記しきい電圧トランジスタが導通し、前記第1トランジスタがスイッチング動作するので、駆動トランジスタのしきい電圧が補償される段階と、前記駆動トランジスタにデータ信号が伝達されてデータが書き込まれる段階とは共に行われる。

**【0031】**

前記有機発光ダイオードが発光する段階は、前記第1電源電圧源と有機発光ダイオードとの間に接続し、発光制御信号によってスイッチング動作する少なくとも一つ以上の発光制御トランジスタにより、前記有機発光ダイオードの発光が制御される段階である。

この時、前記発光制御信号は、画素に含まれる第1トランジスタ及び第2トランジスタにそれぞれゲートオン電圧レベルの第1走査信号及び第2走査信号が伝達された後、ゲートオン電圧レベルで伝達できる。

10

**【発明の効果】****【0032】**

本発明による画素及びこれを含む表示装置によれば、ヒステリシスによって発生する応答速度の問題を解決し、画面上のモーションブラーを改善することにより、正確な階調を表現することができる。

**【0033】**

また、本発明によれば、駆動トランジスタのしきい電圧偏差を補償すると同時に、輝度偏差が大きいデータ信号による映像を表示することにおいて、応答速度の遅延を防止できるので、高品質及び高画質を実現することができる。

20

**【図面の簡単な説明】****【0034】**

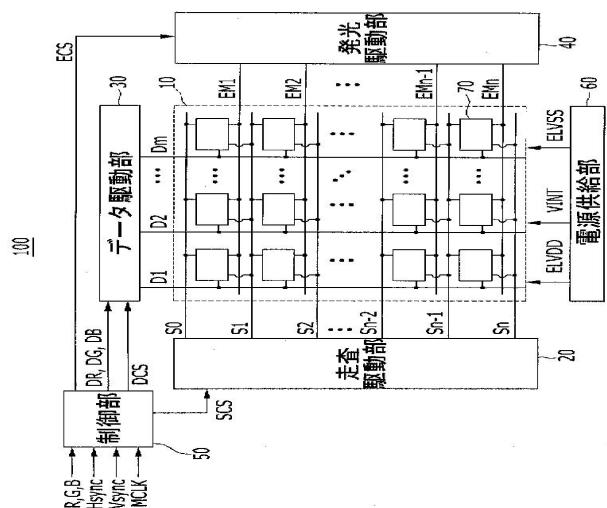

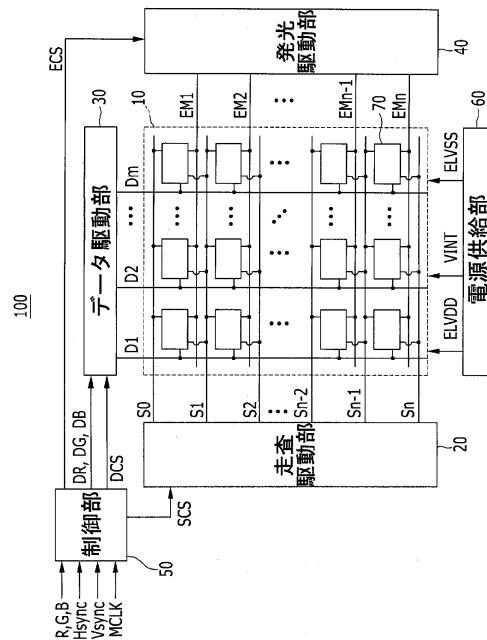

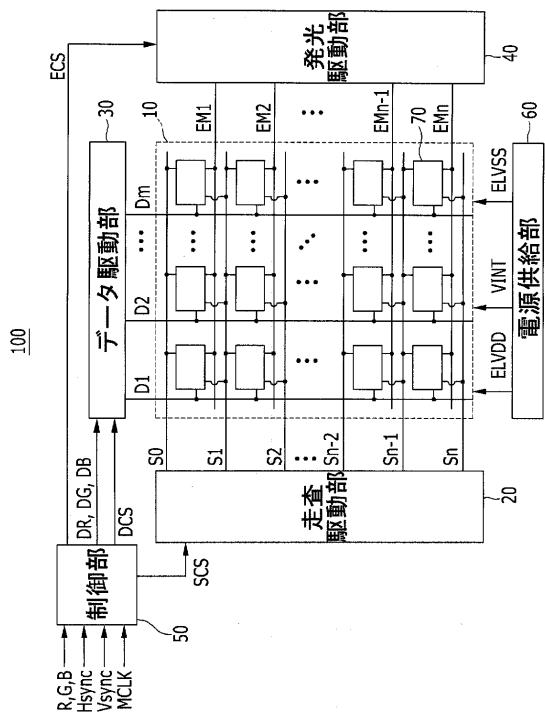

【図1】本発明の一実施形態による表示装置のブロック図である。

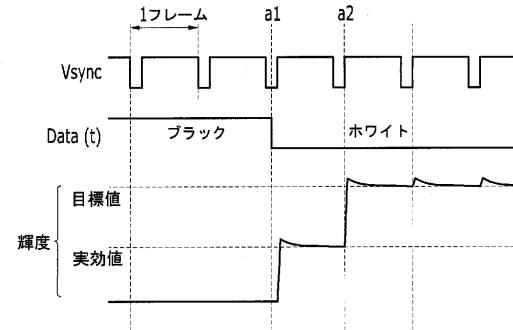

【図2】既存の画素回路における階調表現時にヒステリシスによる応答速度の遅延を示す波形図である。

【図3】図1に示した表示装置の画素回路構造を示す回路図である。

【図4】図3に示した画素の駆動動作を示すタイミング図である。

【図5】本発明の一実施形態に係る表示装置で応答速度が改善された状態を示す波形図である。

30

**【発明を実施するための形態】****【0035】**

以下、添付した図面を参照して、本発明の実施形態について本発明が属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。本発明は種々の異なる形態に実現でき、ここで説明する実施形態に限られない。

また、種々の実施形態において、同一の構成を有する構成要素に対しては同一の符号を付けて、代表的に第1実施形態で説明し、その他の実施形態では第1実施形態とは異なる構成についてのみ説明する。

**【0036】**

本発明を明確に説明するために説明上不必要的部分は省略し、明細書の全体にわたって同一または類似する構成要素に対しては同一の参照符号を付ける。

40

明細書の全体において、ある部分が他の部分と「接続」されているという時、これは「直接的に接続」されている場合だけでなく、その中間に他の素子を介在して「電気的に接続」されている場合も含む。また、ある部分がある構成要素を「含む」という時、これは特に反対になる記載がない限り、他の構成要素を除くことではなく、他の構成要素をさらに含むことができるのを意味する。

**【0037】**

図1は、本発明の一実施形態に係る表示装置のブロック図を示した。

本発明の実施形態に係る表示装置100は、複数の画素を含む表示部10、走査駆動部20、データ駆動部30、発光駆動部40、制御部50、及び表示装置に外部電圧を供給

50

する電源供給部 6 0 を含む。

【 0 0 3 8 】

複数の画素それぞれは、表示部 1 0 に伝達される複数の走査線 ( S 0 ~ S n ) のうちの二つの走査線に接続されている。図 1において、画素は当該画素ラインに対応する走査線と、その以前ラインの走査線に接続しているが、これに必ずしも制限されることではない。

また、複数の画素それぞれは、表示部 1 0 に伝達される複数のデータ線 ( D 1 ~ D m ) のうちの一つのデータ線、表示部 1 0 に伝達される複数の発光制御線 ( E M 1 ~ E M n ) のうちの一つの発光制御線に接続されている。

【 0 0 3 9 】

走査駆動部 2 0 は、複数の走査線 ( S 0 ~ S n ) を通じて各画素に二つの対応する走査信号を生成して伝達する。即ち、走査駆動部 2 0 は、各画素が含まれる画素ラインに対応する走査線を通じて第 1 走査信号を伝達し、当該画素ラインの前の画素ラインに対応する走査線を通じて第 2 走査信号を伝達する。

【 0 0 4 0 】

図 1 の実施形態において、n 番目画素ラインに含まれている複数の画素のうちの一つの画素 7 0 は、当該 n 番目画素ラインに対応する走査線 ( S n ) と、n 番目画素ラインの前の n - 1 番目画素ラインに対応する走査線 ( S n - 1 ) にそれぞれ接続される。

画素 7 0 は、上記走査線 ( S n ) を通じて第 1 走査信号が伝達され、同時に前記走査線 ( S n - 1 ) を通じて第 2 走査信号が伝達される。

【 0 0 4 1 】

データ駆動部 3 0 は、複数のデータ線 ( D 1 ~ D m ) を通じて各画素にデータ信号を伝達する。

発光駆動部 4 0 は、複数の発光制御線 ( E M 1 ~ E M n ) を通じて各画素に発光制御信号を生成して伝達する。

【 0 0 4 2 】

制御部 5 0 は、外部から伝達される複数の映像信号 ( R 、 G 、 B ) を複数の映像データ信号 ( D R 、 D G 、 D B ) に変更してデータ駆動部 3 0 に伝達する。また、制御部 5 0 は、垂直同期信号 ( V s y n c ) 、水平同期信号 ( H s y n c ) 、及びクロック信号 ( M C L K ) の伝達を受けて、前記走査駆動部 2 0 、データ駆動部 3 0 、及び発光駆動部 4 0 の駆動を制御するための制御信号を生成して、それぞれに伝達する。即ち、制御部 5 0 は、走査駆動部 2 0 を制御する走査駆動制御信号 ( S C S ) 、データ駆動部 3 0 を制御するデータ駆動制御信号 ( D C S ) 、及び発光駆動部 4 0 を制御する発光駆動制御信号 ( E C S ) をそれぞれ生成して伝達する。

【 0 0 4 3 】

また、表示部 1 0 は、複数の走査線 ( S 0 ~ S n ) 、複数のデータ線 ( D 1 ~ D m ) 、及び複数の発光制御線 ( E M 1 ~ E M n ) の交差部に位置する複数の画素を含む。

上記複数の画素は、電源供給部 6 0 から第 1 電源電圧 ( E L V D D ) 、第 2 電源電圧 ( E L V S S ) 、初期化電圧 ( V I N T ) などの外部電圧の供給を受ける。上記第 1 電源電圧 ( E L V D D ) は第 2 電源電圧 ( E L V S S ) より高い電圧レベルを有する。

【 0 0 4 4 】

表示部 1 0 はほぼ行列状に配列された複数の画素を含む。特に制限されないが、複数の走査線 ( S 0 ~ S n ) は、上記画素の配列形態からほぼ行方向に延びて、互いにほぼ平行し、複数のデータ線 ( D 1 ~ D m ) は、ほぼ列方向に延びて、互いにほぼ平行する。

複数の画素それぞれは、複数のデータ線 ( D 1 ~ D m ) を通じて伝達された対応するデータ信号によって有機発光ダイオードに供給される駆動電流により、所定輝度の光を発光する。

【 0 0 4 5 】

図 2 は、既存の画素回路における階調表現時にヒステリシスによる応答速度の遅延を示す波形図である。

駆動トランジスタのしきい電圧を補償する一般的な画素回路において、垂直同期信号( $V_{sync}$ )が伝達される1フレームごとに表示部の画素がスキャンされ、データ信号( $Data[t]$ )の伝達を受けて映像を表示するようになる。

#### 【0046】

万一、表示部の複数の画素それが、伝達されるデータ信号に対応してブラック映像またはホワイト映像に表示される時、長時間駆動される場合、駆動トランジスタに印加される電圧レベルが持続して、それによるヒステリシスが発生する。その場合、前のフレームの階調電圧に影響を受けて、現在フレームの映像を表示する時に、TFT特性曲線の左側または右側に異なるようにシフトできる。

#### 【0047】

例えば、ブラック映像で長時間駆動される場合、駆動トランジスタに印加される電圧レベルが駆動トランジスタの動作基準電圧以下のオフバイアス( $Off\ bias$ )であるので、次のフレームの映像信号による階調は、TFT特性曲線の右側にシフトされる。これに反し、ホワイト映像で長時間駆動される場合、駆動トランジスタに印加される電圧レベルは、駆動トランジスタの動作基準電圧以上のオンバイアス( $On\ bias$ )に持続するので、次のフレームの映像信号による階調はTFT特性曲線の左側にシフトされる。

#### 【0048】

したがって、このような画素の駆動トランジスタのヒステリシス現象により、前のフレームと現在フレーム間の輝度変化量によって同一の輝度表現時に応答速度が変化する問題が発生する。このような応答速度は、駆動トランジスタに印加されるオフバイアスまたはオンバイアスの印加時間によってさらに問題になり得る。

#### 【0049】

図2の波形図は、ブラックデータ信号( $Data[t]$ )により長時間ブラック輝度で表示された画素が、時点 $a_1$ にホワイト輝度で発光するホワイトデータ信号の伝達を受ける。図2を参照すれば分かるように、ホワイトデータ信号が伝達された時点 $a_1$ に同期されて、ホワイトデータ信号による輝度の目標値で発光せずに、1フレームが経過した時点 $a_2$ に輝度の目標値で発光する。

#### 【0050】

ブラックからホワイトに映像を表示するために駆動する場合、1フレームでホワイト輝度の目標値に上昇できず、中間輝度まで到達する。そのためホワイトからホワイトに映像を表示するために駆動する場合に比べて、応答速度が遅延される。このようなヒステリシスによる応答速度の遅延は、ディスプレイ画面でテキストのスクロール時にモーションブラーとして現れる。

本発明で提案する画素回路の構造と駆動方式は、このようなヒステリシスによって発生する応答速度の問題を解決するためのものである。

#### 【0051】

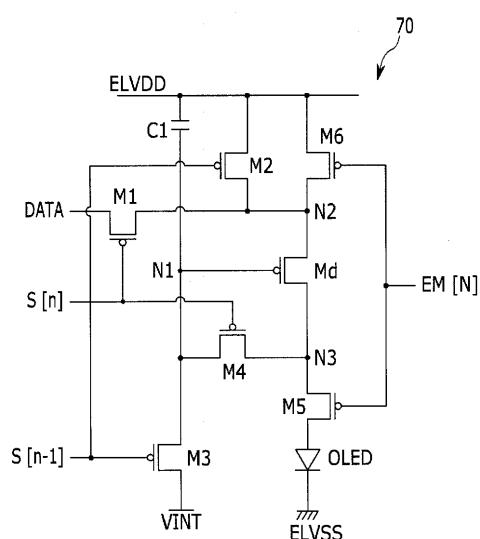

図3は、図1に示した本発明の一実施形態に係る表示装置100の画素70の回路構造を示す回路図である。

本発明の一実施形態に係る画素は、データ信号を伝達するために画素を活性化する第1走査信号を伝達する第1走査線以外に、初期化期間の間に駆動トランジスタ( $M_d$ )に初期化電圧( $V_{INT}$ )を印加し、駆動トランジスタ( $M_d$ )を動作電圧( $On\ bias$ )で維持するために制御する第2走査信号を伝達する第2走査線にそれぞれ接続される。

#### 【0052】

図3に示した画素70は、図1の表示装置100の中で、表示部10に含まれる複数の画素のうちのn番目走査線( $S_n$ )とn-1番目走査線( $S_{n-1}$ )にそれぞれ接続される。また、画素70は、m番目データ線( $D_m$ )とn番目発光制御線( $E_{Mn}$ )に接続される。

#### 【0053】

図3に示した画素70は、有機発光ダイオード(organic light emitting diode、OLED)と、有機発光ダイオード(OLED)のアノード電

極に接続される駆動トランジスタ ( $M_d$ ) と、駆動トランジスタ ( $M_d$ ) のソース電極に接続される第1トランジスタ ( $M_1$ ) と、駆動トランジスタ ( $M_d$ ) と第1トランジスタ ( $M_1$ ) が接続される接続点と第1電源電圧 ( $ELVDD$ )との間に接続される第2トランジスタ ( $M_2$ ) と、駆動トランジスタ ( $M_d$ ) と第1電源電圧 ( $ELVDD$ )との間に位置したキャパシタ ( $C_1$ ) を含む。

#### 【0054】

本発明の画素70は、初期化期間の間に初期化電圧 ( $VINT$ ) を伝達する初期化トランジスタ ( $M_3$ ) をさらに含むことができる。

画素70は、駆動トランジスタ ( $M_d$ ) のしきい電圧を補償するために駆動トランジスタ ( $M_d$ ) をダイオード接続するしきい電圧補償トランジスタ ( $M_4$ ) をさらに含むことができる。

10

#### 【0055】

また、画素70は、有機発光ダイオード ( $OLED$ ) のアノード電極に接続して、有機発光ダイオード ( $OLED$ ) の駆動電流による発光を調節する発光制御トランジスタを少なくとも一つ以上さらに含むことができる。図3の画素70に含まれる前記発光制御トランジスタは、有機発光ダイオード ( $OLED$ ) のアノード電極と駆動トランジスタ ( $M_d$ ) との間に接続された第1発光制御トランジスタ ( $M_5$ )、及び駆動トランジスタ ( $M_d$ ) と第1電源電圧 ( $ELVDD$ )との間に接続された第2発光制御トランジスタ ( $M_6$ ) を含む。

#### 【0056】

画素70の有機発光ダイオード ( $OLED$ ) はアノード電極とカソード電極を含み、対応するデータ信号による駆動電流によって発光する。本発明で前記データ信号による駆動電流は、表示部10に含まれる複数の画素それぞれの駆動トランジスタのしきい電圧に影響を受けないように補償される。

20

#### 【0057】

駆動トランジスタ ( $M_d$ ) は、第1電源電圧 ( $ELVDD$ ) が接続された第2ノード ( $N_2$ ) に接続されるソース電極と、第3ノード ( $N_3$ ) に接続するドレイン電極と、第1ノード ( $N_1$ ) に接続されるゲート電極とを含む。駆動トランジスタ ( $M_d$ ) は、第2ノード ( $N_2$ ) に接続されている第1トランジスタ ( $M_1$ ) を通じてデータ信号の伝達を受ける。

30

#### 【0058】

駆動トランジスタ ( $M_d$ ) は、ソース電極とゲート電極間の電圧差に対応する駆動電流を有機発光ダイオード ( $OLED$ ) に伝達して発光させる。

第1トランジスタ ( $M_1$ ) は、データ線 ( $DATA$ ) に接続してデータ信号が伝達されるソース電極と、第2ノード ( $N_2$ ) に接続するドレイン電極と、画素70が含まれた画素ラインに対応する走査線に接続して走査信号 ( $S[n]$ ) が伝達されるゲート電極とを含む。この時、前記対応する走査線は、画素70がn番目画素ラインに含まれるので、n番目走査線である。

30

#### 【0059】

n番目走査線を通じて走査信号 ( $S[n]$ ) が伝達されて第1トランジスタ ( $M_1$ ) が導通すれば、データ信号が第2ノード ( $N_2$ ) に伝達され、上記データ信号に対応するデータ電圧 ( $Vdata$ ) が駆動トランジスタ ( $M_d$ ) のソース電極に伝達される。

40

走査信号 ( $S[n]$ ) は、しきい電圧補償トランジスタ ( $M_4$ ) のゲート電極にも同時に伝達される。

#### 【0060】

しきい電圧補償トランジスタ ( $M_4$ ) は、駆動トランジスタ ( $M_d$ ) のゲート電極とドレイン電極との間に接続して、走査信号 ( $S[n]$ ) がゲートオン電圧レベルで伝達される間に導通して、駆動トランジスタ ( $M_d$ ) をダイオード接続する。このことにより、駆動トランジスタ ( $M_d$ ) のソース電極に印加されたデータ電圧から駆動トランジスタ ( $M_d$ ) のしきい電圧ほど降下した電圧 ( $Vdata - Vth$ ) が、駆動トランジスタ ( $M_d$ )

50

のゲート電極に印加される。駆動トランジスタ (M<sub>d</sub>) のゲート電極はキャパシタ (C<sub>1</sub>) の一端に接続しているので、電圧 (V<sub>d a t a</sub> - V<sub>t h</sub>) はキャパシタ (C<sub>1</sub>) によって維持される。駆動トランジスタ (M<sub>d</sub>) のしきい電圧 (V<sub>t h</sub>) が反映された電圧 (V<sub>d a t a</sub> - V<sub>t h</sub>) がゲート電極に印加されて維持されるので、駆動トランジスタ (M<sub>d</sub>) に流れる駆動電流は、駆動トランジスタ (M<sub>d</sub>) のしきい電圧による影響を受けない。

#### 【0061】

第2トランジスタ (M<sub>2</sub>) は、n - 1番目走査線に接続されて走査信号 (S[n - 1]) が伝達されるゲート電極と、第1電源電圧 (E<sub>L V D D</sub>) に接続されたソース電極と、第2ノード (N<sub>2</sub>) に接続されたドレイン電極を含む。

第2トランジスタ (M<sub>2</sub>) は、n番目走査線を通じて画素70に伝達される走査信号 (S[n]) が、ゲートオン電圧レベルで伝達される前に、n - 1番目走査線を通じてゲートオン電圧レベルで伝達される走査信号 (S[n - 1]) によって導通する。このことにより、走査信号 (S[n - 1]) によってスイッチングターンオンされる間に、第1電源電圧 (E<sub>L V D D</sub>) は駆動トランジスタ (M<sub>d</sub>) のソース電極に印加される。

#### 【0062】

初期化電圧 (V<sub>I N T</sub>) を駆動トランジスタ (M<sub>d</sub>) のゲート電極に伝達する初期化トランジスタ (M<sub>3</sub>) は、走査信号 (S[n - 1]) によってスイッチング動作する。

即ち、初期化トランジスタ (M<sub>3</sub>) は、n - 1番目走査線に接続するゲート電極と、初期化電圧 (V<sub>I N T</sub>) を伝達する電圧源に接続するソース電極と、駆動トランジスタ (M<sub>d</sub>) のゲート電極に接続されるドレイン電極とを含む。

#### 【0063】

走査信号 (S[n - 1]) がゲートオン電圧レベルで初期化トランジスタ (M<sub>3</sub>) に伝達される間に、駆動トランジスタ (M<sub>d</sub>) のゲート電極には初期化電圧 (V<sub>I N T</sub>) が印加される。走査信号 (S[n - 1]) がゲートオン電圧レベルで伝達される期間の間に、駆動トランジスタ (M<sub>d</sub>) のゲート電極は初期化電圧で初期化される。

#### 【0064】

走査信号 (S[n - 1]) がゲートオン電圧レベルで伝達される初期化期間の間に、駆動トランジスタ (M<sub>d</sub>) のソース電極に第1電源電圧 (E<sub>L V D D</sub>) が印加されると同時に、駆動トランジスタ (M<sub>d</sub>) のゲート電極に初期化電圧 (V<sub>I N T</sub>) が印加されるので、初期化期間の間の駆動トランジスタ (M<sub>d</sub>) のゲート - ソース電圧差 (V<sub>g s</sub>) は、E<sub>L V D D</sub> - V<sub>I N T</sub> となる。これは、駆動トランジスタ (M<sub>d</sub>) が動作する基準電圧以上の電圧値である。

#### 【0065】

初期化期間の間の駆動トランジスタ (M<sub>d</sub>) のゲート - ソース電圧差 (V<sub>g s</sub>) が前記基準電圧以上であるので、駆動トランジスタ (M<sub>d</sub>) はオンバイアスされる。

全ての画素の駆動トランジスタ (M<sub>d</sub>) が、このような動作によってオンバイアスされた状態で、データ電圧が駆動トランジスタに書き込まれるので、ヒステリシス特性を改善することができる。

#### 【0066】

複数の駆動トランジスタそれぞれは、前のフレームのデータ電圧が印加されているので、現在フレームのデータ電圧を書き込む前に、複数の駆動トランジスタそれぞれのゲート - ソース電圧は互いに異なるレベルとすることができます。

#### 【0067】

初期化期間がなければ、現在フレームのデータ電圧が前のフレームのデータ電圧に比べて、高い電圧印加或いは低い電圧印加によって駆動トランジスタのゲート - ソース電圧のヒステリシス特性が異なることもある。本発明の実施形態においては、初期化期間の間に全ての駆動トランジスタのゲート - ソース電圧を第1電源電圧 (E<sub>L V D D</sub>) - 初期化電圧 (V<sub>I N T</sub>) に作って、全ての駆動トランジスタを同一の条件でオンバイアスさせる。

したがって、ヒステリシス特性に影響を受けずに、全ての画素の駆動トランジスタのゲート - ソース電圧が、同一の条件で対応する現在フレームのデータ電圧により決定される

10

20

30

40

50

。

**【 0 0 6 8 】**

本発明の実施形態においては、第2トランジスタ(M2)及び初期化トランジスタ(M3)のスイッチング動作を制御する信号を、当該画素ラインに接続された走査線の前の走査線を通じて伝達される走査信号を利用したが、これに制限されず、別途の制御信号を伝達できることは勿論である。

**【 0 0 6 9 】**

一方、最初の画素ラインに含まれる画素の場合、第2トランジスタ(M2)及び初期化トランジスタ(M3)に伝達される走査信号は、走査駆動部20で生成して伝達するダミー走査信号とすることができます。10

**【 0 0 7 0 】**

具体的にキャパシタ(C1)は、第1ノード(N1)に接続された第1電極及び第1電源電圧(ELVDD)に接続された第2電極を含む。

キャパシタ(C1)は、駆動トランジスタ(Md)のゲート電極が接続された第1ノード(N1)に接続しているため、画素の駆動過程により駆動トランジスタ(Md)のゲート電極電圧値を保存する。

**【 0 0 7 1 】**

また、本発明の一実施形態に係る画素70の第1発光制御トランジスタ(M5)は、n番目発光制御線に接続して発光制御信号(EM[n])の伝達を受けるゲート電極と、第3ノード(N3)に接続されたソース電極と、有機発光ダイオード(OLED)のアノード電極に接続されたドレイン電極とを含む。20

**【 0 0 7 2 】**

画素70は、第2発光制御トランジスタ(M6)をさらに含むことができるが、第2発光制御トランジスタ(M6)は、n番目発光制御線に接続して発光制御信号(EM[n])の伝達を受けるゲート電極と、第1電源電圧(ELVDD)に接続されたソース電極と、第2ノード(N2)に接続されたドレイン電極とを含む。

**【 0 0 7 3 】**

本発明の発光制御トランジスタの構成は一つの実施形態であるため、必ずしもこのような構成に制限されることではない。

発光制御信号(EM[n])がゲートオン電圧レベルで伝達されると、第1発光制御トランジスタ(M5)及び第2発光制御トランジスタ(M6)は導通し、データの書き込み期間の間にキャパシタ(C1)に保存されたデータ信号によるデータ電圧に対応する駆動電流ほど有機発光ダイオード(OLED)に伝達して発光させる。上述のように、上記キャパシタ(C1)に保存されたデータ電圧は、しきい電圧(Vth)が考慮された電圧値(Vdata - Vth)があるので、対応する駆動電流ほど発光する時、しきい電圧の影響を排除できる。30

**【 0 0 7 4 】**

図3に示した画素の駆動回路図に含まれたトランジスタはPMOSであると想定して説明したが、これに制限されず、NMOSで具現することも可能である。

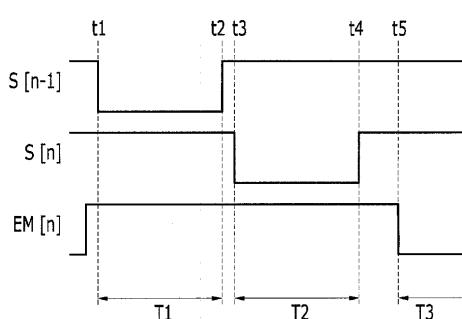

図3に示した画素70の駆動に対する理解を助けるために、図4の駆動タイミング図を活用して説明する。40

**【 0 0 7 5 】**

本発明の実施形態による画素70は、引き続いた二つの走査線に接続していて、それぞれ走査信号の伝達を受けて動作する。

まず、時点t1でn-1番目走査線を通じて伝達される走査信号(S[n-1])がローレベルに変化し、T1期間の間にローレベルを維持する。

**【 0 0 7 6 】**

画素から上記走査信号(S[n-1])の伝達を受ける第2トランジスタ(M2)及び初期化トランジスタ(M3)が同時に導通する。

このことにより、T1期間の間に駆動トランジスタ(Md)のソース電極には第2トランジスタ(M2)のゲート電極に接続された走査信号(S[n-1])が供給される。

ンジスタ (M2) を通じてハイレベルの第1電源電圧 (ELVDD) が印加され、駆動トランジスタ (Md) のゲート電極には初期化トランジスタ (M3) を通じて初期化電圧 (VINT) が印加される。

#### 【0077】

このようなT1期間の間に、駆動トランジスタ (Md) のゲート-ソース電圧差 (Vgs) は ELVDD - VINT に維持される。この時、初期化電圧 (VINT) がローレベルであるので、電圧差 (Vgs) は駆動トランジスタ (Md) を動作させる最小の基準電圧以上であり得る。したがって、各フレームで駆動トランジスタ (Md) のしきい電圧が補償され、データが書き込まれる期間の前に全ての画素に含まれた駆動トランジスタ (Md) がオンバイアスされるので、駆動トランジスタ (Md) のヒステリシス特性に影響を受けないで、目的とする階調に表現される映像を実現することができる。

10

#### 【0078】

その後、時点t2に走査信号 (S[n-1]) がハイレベルに遷移し、時点t3にn番目走査線を通じて伝達される走査信号 (S[n]) がローレベルに変化して、T2期間の間にローレベルを維持する。

T2期間の間に走査信号 (S[n-1]) がハイ状態で伝達されるので、第2トランジスタ (M2) 及び初期化トランジスタ (M3) は遮断され、第1ノード (N1) の電圧はフローティング (floating) される。

20

#### 【0079】

同時に、T2期間の間に画素から上記走査信号 (S[n]) の伝達を受ける第1トランジスタ (M1) 及びしきい電圧補償トランジスタ (M4) が導通する。このことにより、T2期間の間に駆動トランジスタ (Md) のソース電極には第1トランジスタ (M1) を通じてデータ信号 (DATA) によるデータ電圧 (Vdata) が伝達され、駆動トランジスタ (Md) はしきい電圧補償トランジスタ (M4) によってダイオード接続される。

20

#### 【0080】

したがって、T2期間の間にキャパシタ (C1) の一端に接続された第1ノード (N1) に維持される電圧は、駆動トランジスタ (Md) のゲート-ソース電極間の電圧差に相当する電圧 (Vgs) であって、データ電圧 (Vdata) から駆動トランジスタ (Md) のしきい電圧 (Vth) ほど下降した電圧値 (Vdata - Vth) である。

30

#### 【0081】

T1期間の初期化期間の間に、駆動トランジスタ (Md) がオンバイアスされてヒステリシス特性を改善したので、上記データ電圧 (Vdata) による階調表現時の応答速度の遅延問題を解決することができる。

30

#### 【0082】

時点t4に走査信号 (S[n]) がハイレベルに遷移すると、第1トランジスタ (M1) 及びしきい電圧補償トランジスタ (M4) が遮断される。このことにより、第1ノード (N1) の電圧はさらにフローティング (floating) される。

40

#### 【0083】

このことにより、発光制御信号 (EM[n]) が伝達される画素70の第1発光制御トランジスタ (M5) 及び第2発光制御トランジスタ (M6) は導通し、有機発光ダイオード (OLED) にキャパシタ (C1) に保存されたデータ信号によるデータ電圧の駆動電流が伝達されて発光する。

40

具体的に上記駆動電流を算出するための対応する電圧は、駆動トランジスタ (Md) のしきい電圧 (Vth) の影響が排除された ELVDD - Vdata となる。

#### 【0084】

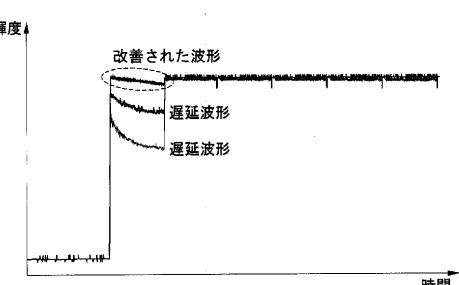

本発明の一実施形態による画素とそれを含む表示装置は、データ信号によって映像を表示することにおいて、駆動トランジスタのしきい電圧の影響を排除すると同時に、ヒステリシス特性による応答速度の問題を解決できるので、図5に示した波形図のように、応答

50

速度が遅れないで、当該フレームから直ちに目的とする輝度で発光して、鮮明な高品質の映像を提供することができる。

【0085】

図5の波形図を参照すると、既存の画素を用いて駆動すれば、ヒステリシスによって目的とする輝度で発光しないで中間程度の輝度まで表現した後、次のフレームで所望する輝度で発光する問題波形が現れる。これに比べて、本発明の画素を用いて駆動すれば、当該フレームで直ちに目的とする輝度まで表現する改善された波形が得られることが分かる。

【0086】

以上、本発明の具体的な実施形態と関連して本発明について説明したが、これは例示に過ぎず、本発明はこれに制限されない。当業者は本発明の範囲を逸脱せずに、説明された実施形態を変更または変形でき、このような変更または変形も本発明の範囲に属する。また、明細書で説明した各構成要素の物質は、当業者が公知された多様な物質から容易に選択して代替できる。また、当業者は本明細書で説明された構成要素のうちの一部を性能の劣化なしに省略したり、性能を改善するために構成要素を追加したりすることができる。それだけでなく、当業者は工程環境や装備により本明細書で説明した方法段階の順序を変更することもできる。したがって、本発明の範囲は、説明された実施形態ではなく、特許請求の範囲及びその均等物によって決定されなければならない。

10

20

【符号の説明】

【0087】

- 10 表示部

- 20 走査駆動部

- 30 データ駆動部

- 40 発光駆動部

- 50 制御部

- 60 電源供給部

- 70 画素

- 100 表示装置

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

H 0 5 B 33/14

A

(74)代理人 100108453

弁理士 村山 靖彦

(72)発明者 鄭 鎮泰

大韓民国京畿道龍仁市器興区農書洞山24

F ターム(参考) 3K107 AA01 BB01 CC33 CC41 EE03 HH02 HH04 HH05

5C080 AA06 BB05 CC03 DD01 EE19 JJ02 JJ03 JJ04

5C380 AA01 AB06 AB34 AB47 BA38 BA39 BB02 BE01 CA04 CA08

CA12 CB01 CB16 CB17 CB20 CB33 CC06 CC07 CC26 CC27

CC33 CC39 CC52 CC55 CC64 CD017 DA02 DA06 DA22 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素，使用其的显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2012128386A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2012-07-05 |

| 申请号            | JP2011035463                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2011-02-22 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三星移动显示的股票会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 鄭鎮泰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 鄭 鎮泰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2310/0251 G09G2320/0233 G09G2320/0252                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.624.B G09G3/20.660.V H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC41 3K107/EE03 3K107/HH02 3K107/HH04 3K107 /HH05 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD01 5C080/EE19 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB34 5C380/AB47 5C380/BA38 5C380/BA39 5C380 /BB02 5C380/BE01 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB20 5C380/CB33 5C380/CC06 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC33 5C380 /CC39 5C380/CC52 5C380/CC55 5C380/CC64 5C380/CD017 5C380/DA02 5C380/DA06 5C380/DA22 5C380/DA47 |         |            |

| 代理人(译)         | 佐伯喜文<br>渡边 隆<br>村山彥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 优先权            | 1020100126489 2010-12-10 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

## 摘要(译)

甲解决引起的滞后问题的响应速度，而在屏幕上改善运动模糊，我们提出用于补偿驱动晶体管的阈值电压偏差的像素电路结构。本发明涉及一种像素，包括其的显示装置，以及涉及一种驱动方法，包括在特定显示装置的像素，由所述数据驱动信号传输OLED时，有机发光二极管第一晶体管，用于将数据信号传输到与第一扫描信号对应的驱动晶体管，第一晶体管，用于响应于第一扫描信号将数据信号传输到驱动晶体管，用于将第一电源电压施加到与信号对应的驱动晶体管的源电极的第二晶体管，以及连接到驱动晶体管的栅电极的第一电极和连接到第一电源电压的第二电极包括电容器。点域1