(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-41532

(P2007-41532A)

(43) 公開日 平成19年2月15日(2007.2.15)

| (51) Int.CI.                | F 1                                 | テーマコード (参考)          |

|-----------------------------|-------------------------------------|----------------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30                           | K 3K107              |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/30                           | J 5C080              |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20<br>G09G 3/20<br>G09G 3/20 | 611H<br>642A<br>612F |

|                             | 審査請求 有 請求項の数 37 O L (全 35 頁)        | 最終頁に続く               |

|              |                              |          |                                                          |

|--------------|------------------------------|----------|----------------------------------------------------------|

| (21) 出願番号    | 特願2006-130865 (P2006-130865) | (71) 出願人 | 590002817<br>三星エスディアイ株式会社<br>大韓民国京畿道水原市靈通区▲しん▼洞5<br>75番地 |

| (22) 出願日     | 平成18年5月9日 (2006.5.9)         | (71) 出願人 | 506118135<br>学校法人漢陽大学校産学協力団<br>大韓民国ソウル特別市城東区杏堂洞 17       |

| (31) 優先権主張番号 | 10-2005-0070438              | (74) 代理人 | 100072349<br>弁理士 八田 幹雄                                   |

| (32) 優先日     | 平成17年8月1日 (2005.8.1)         | (74) 代理人 | 100110995<br>弁理士 奈良 泰男                                   |

| (33) 優先権主張国  | 韓国 (KR)                      | (74) 代理人 | 100114649<br>弁理士 宇谷 勝幸                                   |

最終頁に続く

(54) 【発明の名称】データ駆動回路、これを利用した有機発光表示装置、及びその駆動方法

## (57) 【要約】

【課題】均一な輝度の映像を表示するようにしたデータ駆動回路を提供する。

【解決手段】複数の階調電圧を生成するためのガンマ電圧部300と、外部から供給されるk (kは自然数)ビットの第1データData1を利用して前記階調電圧中いずれか一つの階調電圧をデータ信号で選択するための少なくとも一つのデジタルアナログ変換器と、前記kビットの第1データを利用してp (pは自然数)ビットの第2データを生成する少なくとも一つのデコーダと、水平期間の第1期間の間に画素から所定の電流の供給を受ける少なくとも一つの電流シンク部と、前記所定の電流に対応して生成される補償電圧及び前記第2データを利用して前記データ信号の電圧値を制御するための少なくとも一つの電圧制御器と、前記水平期間中前記第1期間を除いた第2期間の間に前記電圧値が制御された前記データ信号を前記画素に供給するための少なくとも一つのスイッチング部を備える。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

複数の階調電圧を生成するためのガンマ電圧部と、

外部から供給される k ビットの第 1 データを利用して前記複数の階調電圧の中でいずれか一つの階調電圧をデータ信号で選択するための少なくとも一つのデジタルアナログ変換器と、

前記 k ビットの第 1 データを利用して p ビットの第 2 データを生成する少なくとも一つのデコーダと、

水平期間の第 1 期間の間に画素から所定の電流の供給を受ける少なくとも一つの電流シンク部と、

前記所定の電流に対応して生成される補償電圧及び前記第 2 データを利用して前記データ信号の電圧値を制御するための少なくとも一つの電圧制御器と、

前記水平期間中の前記第 1 期間を除いた第 2 期間の間に前記電圧値が制御された前記データ信号を前記画素に供給するための少なくとも一つのスイッチング部と、を備えることを特徴とするデータ駆動回路。

**【請求項 2】**

前記デジタルアナログ変換器と前記スイッチング部との間に設置されて前記第 1 期間中の一部の期間の間にターンオンされ、前記データ信号を前記スイッチング部に伝達するための X トランジスターと、

前記 X トランジスターと前記スイッチング部との間に接続される第 1 バッファーと、をさらに備えることを特徴とする請求項 1 に記載のデータ駆動回路。

**【請求項 3】**

前記デコーダは、

前記第 1 データを二進数の加重値を持つように変換して前記第 2 データを生成することを特徴とする請求項 2 に記載のデータ駆動回路。

**【請求項 4】**

前記ガンマ電圧部は、

基準電源と電源の電圧とを分圧して前記階調電圧を生成するための複数の分圧抵抗と、

前記電源を前記電圧制御器に供給するためのバッファーと、を備えることを特徴とする請求項 3 に記載のデータ駆動回路。

**【請求項 5】**

前記電圧制御器は、

前記 X トランジスターと前記第 1 バッファーとの間のラインに一側端子が接続される p 個のキャパシタと、

前記キャパシタそれぞれの他側端子と前記電源を前記電圧制御器に供給するためのバッファーとの間に接続される Y トランジスターと、

前記キャパシタそれぞれの他側端子と前記電流シンク部との間に接続され、

前記 Y トランジスターと違う導電型に設定される Z トランジスターと、を備えることを特徴とする請求項 4 に記載のデータ駆動回路。

**【請求項 6】**

前記デコーダは、

前記第 1 期間の間に前記 Y トランジスターをターンオンさせて前記キャパシタの他側端子に前記電源の電圧を供給することを特徴とする請求項 5 に記載のデータ駆動回路。

**【請求項 7】**

前記キャパシタの容量は、

二進数の加重値の形態に設定されることを特徴とする請求項 5 に記載のデータ駆動回路。

。

**【請求項 8】**

前記デコーダは、

前記第 2 期間の間に前記第 2 データのビット値に対応して前記 Z トランジスターをターンオフする。

10

20

30

40

50

ンオン及びターンオフさせながら前記キャパシタの他側端子に前記補償電圧の供給の可否を制御することを特徴とする請求項7に記載のデータ駆動回路。

**【請求項9】**

前記電流シンク部は、

前記所定の電流の供給を受けるための電流源と、

前記画素と接続されたデータ線と前記電圧制御器との間に設置されて前記第1期間の間にターンオンされる第1の電流シンク部トランジスターと、

前記データ線と前記電流源との間に設置されて前記第1期間の間にターンオンされる第2の電流シンク部トランジスターと、

前記補償電圧を充電するためのキャパシタと、

前記第1の電流シンク部トランジスターと前記電圧制御器との間に設置されて前記補償電圧を前記電圧制御器に伝達するためのバッファーと、を備えることを特徴とする請求項1に記載のデータ駆動回路。

**【請求項10】**

前記所定の電流の電流値は、

前記画素が最大輝度に発光するときに流れる電流と同じに設定されることを特徴とする請求項9に記載のデータ駆動回路。

**【請求項11】**

前記スイッチング部は、

前記第2期間の間にターンオンされる少なくとも一つのトランジスターを備えることを特徴とする請求項1に記載のデータ駆動回路。

**【請求項12】**

前記スイッチング部は、

2個のトランジスターを具備して、前記2個のトランジスターはトランスマッシュゲート形態に接続されることを特徴とする請求項11に記載のデータ駆動回路。

**【請求項13】**

サンプリングパルスを生成するための少なくとも一つのシフトレジスターを含むシフトレジスター部と、

前記サンプリングパルスに応答して前記第1データの供給を受けるための少なくとも一つのサンプリングラッチを含むサンプリングラッチ部と、

前記サンプリングラッチに格納された第1データの供給を受け、その第1データを保存し、前記保存された第1データを前記デジタルアナログ変換器及びデコーダに供給するための少なくとも一つのホールディングラッチを含むホールディングラッチ部と、を備えることを特徴とする請求項1に記載のデータ駆動回路。

**【請求項14】**

前記ホールディングラッチに保存された前記第1データの電圧レベルを上昇させて前記デジタルアナログ変換器及びデコーダに供給するためのレベルシフター部をさらに備えることを特徴とする請求項13に記載のデータ駆動回路。

**【請求項15】**

走査線、データ線、及び発光制御線に接続されるように位置される複数の画素を含む画素部と、

前記走査線に走査信号を順次供給し、前記発光制御線に発光制御信号を順次供給するための走査駆動部と、

各水平期間の第1期間の間に前記走査信号によって選択された画素から所定の電流の供給を受け、前記所定の電流に対応して生成される補償電圧と外部から供給される第1データの加重値を変更して生成される第2データを利用してデータ信号の電圧値を制御し、前記電圧値が制御されたデータ信号を前記水平期間中の第1期間を除いた第2期間の間に前記データ線に供給するためのデータ駆動部と、を備えることを特徴とする有機発光表示装置。

**【請求項16】**

10

20

30

40

50

前記データ駆動部は、少なくとも一つのデータ駆動回路を具備して、

前記データ駆動回路それぞれは、

複数の階調電圧を生成するためのガンマ電圧部と、

$k$ ビットの前記第1データを利用して前記階調電圧の中でいずれか一つの階調電圧を前記データ信号で選択するための少なくとも一つのデジタルアナログ変換器と、

前記第1データを利用して $p$ ビットの前記第2データを生成する少なくとも一つのデコーダと、

前記第1期間の間に画素から前記所定の電流の供給を受ける少なくとも一つの電流シンク部と、

前記補償電圧及び前記第2データを利用して前記データ信号の電圧値を制御するための

少なくとも一つの電圧制御器と、

前記第2期間の間に前記電圧値が制御された前記データ信号を前記画素に供給するための

少なくとも一つのスイッチング部と、を備えることを特徴とする請求項15に記載の有機発光表示装置。 10

#### 【請求項17】

前記デジタルアナログ変換器と前記スイッチング部との間に設置されて前記第1期間中の一部期間の間にターンオンさせて前記データ信号を前記スイッチング部に伝達するためのXトランジスターと、

前記Xトランジスターと前記スイッチング部との間に接続される第1バッファーと、を

さらに備えることを特徴とする請求項16に記載の有機発光表示装置。 20

#### 【請求項18】

前記デコーダは、

前記第1データを二進数の加重値を持つように変更して前記第2データを生成することを特徴とする請求項17に記載の有機発光表示装置。

#### 【請求項19】

前記ガンマ電圧部は、

基準電源と電源の電圧とを分圧して前記階調電圧を生成するための複数の分圧抵抗と、

前記電源を前記電圧制御器に供給するためのバッファーと、を備えることを特徴とする

請求項18に記載の有機発光表示装置。 30

#### 【請求項20】

前記電圧制御器は、

前記Xトランジスターと前記第1バッファーとの間のラインに一側端子が接続される $p$

個のキャパシタと、

前記キャパシタそれぞれの他側端子と前記電源を前記電圧制御器に供給するためのバッ

ファーとの間に接続されるYトランジスターと、

前記キャパシタそれぞれの他側端子と前記電流シンク部との間に接続されて前記Yトラン

ジスターと違う導電型に設定されるZトランジスターと、を備えることを特徴とする

請求項19に記載の有機発光表示装置。 40

#### 【請求項21】

前記デコーダは、

前記第1期間の間に前記Yトランジスターをターンオンさせて前記キャパシタの他側端

子に前記電源の電圧を供給することを特徴とする請求項20に記載の有機発光表示装置。

#### 【請求項22】

前記キャパシタの容量は、

二進数加重値形態に設定されることを特徴とする請求項20に記載の有機発光表示装置

。 50

#### 【請求項23】

前記デコーダは、

前記第2期間の間に前記第2データのビット値に対応して前記Zトランジスターをタ

ーンオン及びターンオフさせながら前記キャパシタの他側端子に前記補償電圧の供給の可否

を制御することを特徴とする請求項 2 2 に記載の有機発光表示装置。

【請求項 2 4】

前記電流シンク部は、

前記所定の電流の供給を受けるための電流源と、

前記画素と接続されたデータ線と前記電圧制御器との間に設置されて前記第 1 期間の間にターンオンされる第 1 の電流シンク部トランジスターと、

前記データ線と前記電流源との間に設置されて前記第 1 期間の間にターンオンされる第 2 の電流シンク部トランジスターと、

前記補償電圧を充電するためのキャパシタと、

前記第 1 の電流シンク部トランジスターと前記電圧制御器との間に設置されて前記補償電圧を前記電圧制御器に伝達するためのバッファーと、を備えることを特徴とする請求項 1 6 に記載の有機発光表示装置。 10

【請求項 2 5】

前記所定の電流の電流値は、

前記画素が最大輝度に発光されるときに流れる電流と同じに設定されることを特徴とする請求項 2 4 に記載の有機発光表示装置。

【請求項 2 6】

前記スイッチング部は、

前記第 2 期間の間にターンオンされる少なくとも一つのトランジスターを備えることを特徴とする請求項 1 6 に記載の有機発光表示装置。 20

【請求項 2 7】

サンプリングパルスを生成するための少なくとも一つのシフトレジスターを含むシフトレジスター部と、

前記サンプリングパルスに応答して前記第 1 データの供給を受けるための少なくとも一つのサンプリングラッチを含むサンプリングラッチ部と、

前記サンプリングラッチに保存された第 1 データの供給を受け、前記第 1 データを保存し、前記保存された第 1 データを前記デジタルアナログ変換器及びデコーダに供給するための少なくとも一つのホルディングラッチを含むホルディングラッチ部と、を備えることを特徴とする請求項 1 6 に記載の有機発光表示装置。 30

【請求項 2 8】

前記ホルディングラッチに格納された前記第 1 データの電圧レベルを上昇させて前記デジタルアナログ変換器及びデコーダに供給するためのレベルシフター部をさらに備えることを特徴とする請求項 2 7 に記載の有機発光表示装置。

【請求項 2 9】

前記画素それぞれは、

第 1 電源と、

前記第 1 電源から電流の供給を受ける有機発光ダイオードと、

前記データ線に接続されて現在走査線に走査信号が供給されるときにターンオンされる第 1 トランジスター及び第 2 トランジスターと、

前記第 1 トランジスターの第 2 電極と基準電源との間に接続されて以前走査線に走査信号が供給されるときにターンオンされる第 3 トランジスターと、 40

前記有機発光ダイオードに供給される電流量を制御するための第 4 トランジスターと、

前記第 4 トランジスターのゲート電極と第 2 電極との間に接続されて前記以前走査線に走査信号が供給されるときにターンオンされて第 4 トランジスターをダイオード形態で接続させるための第 5 トランジスターと、を備えることを特徴とする請求項 1 5 に記載の有機発光表示装置。

【請求項 3 0】

前記画素それぞれは、

前記第 1 トランジスターの第 2 電極と前記第 1 電源との間に接続される第 1 キャパシタと、 50

前記第1トランジスターの第2電極と前記第4トランジスターのゲート電極との間に接続される第2キャパシタと、を備えることを特徴とする請求項29に記載の有機発光表示装置。

【請求項31】

前記画素それぞれは、

前記第4トランジスターのゲート電極と前記第1電源との間に接続される第1キャパシタと、

前記第1トランジスターの第2電極と前記第4トランジスターのゲート電極との間に接続される第2キャパシタと、を備えることを特徴とする請求項29に記載の有機発光表示装置。

10

【請求項32】

前記第4トランジスターの第2電極と前記有機発光ダイオードとの間に接続されて前記発光制御信号が供給されるときにターンオフされ、それ以外の期間の間にターンオンされる第6トランジスターをさらに備えることを特徴とする請求項29に記載の有機発光表示装置。

【請求項33】

外部から供給されるkビットの第1データに対応して複数の階調電圧の中でいずれか一つの階調電圧をデータ信号で選択する第1段階と、

前記第1データが二進数の加重値を持つように変換してpビットの第2データを生成する第2段階と、

水平期間の第1期間の間に走査信号によって選択された画素から所定の電流の供給を受ける第3段階と、

前記電流が供給されるときに生成される補償電圧と前記第2データを利用して前記データ信号の電圧値を制御する第4段階と、

前記第4段階で電圧値が制御されたデータ信号を前記水平期間中の第1期間を除いた第2期間の間に前記画素に供給する第5段階と、を含むことを特徴とする有機発光表示装置の駆動方法。

【請求項34】

前記所定の電流の電流値は、

前記画素が最大輝度に発光するときに流れる電流と同じに設定されることを特徴とする請求項33に記載の有機発光表示装置の駆動方法。

30

【請求項35】

前記第1段階で、

前記階調電圧は基準電源と第1電源の電圧とを分圧して生成されることを特徴とする請求項33に記載の有機発光表示装置の駆動方法。

【請求項36】

前記第4段階は、

前記第1期間の間に複数のキャパシタの端子に前記第1電源の電圧値を供給する段階と、

前記第2期間の間に前記第2データのビット値に対応して前記複数のキャパシタの端子に前記補償電圧の供給の可否を制御して前記データ信号の電圧値を制御する段階と、を含むことを特徴とする請求項35に記載の有機発光表示装置の駆動方法。

40

【請求項37】

前記キャパシタの容量は、

二進数の加重値の形態に設定されることを特徴とする請求項36に記載の有機発光表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ駆動回路、これを利用した有機発光表示装置、及びその駆動方法に関

50

し、より詳細には、均一な輝度の映像を表示できるようにしたデータ駆動回路、これを利用した発光表示装置、及びその駆動方法に関する。

#### 【背景技術】

##### 【0002】

近年、陰極線管（CRT：Cathode Ray Tube）の短所である重さと嵩を減らすことができる各種平板表示装置が開発されている。平板表示装置として、液晶表示装置（LCD：Liquid Crystal Display）、電界放出表示装置（FED：Field Emission Display）、プラズマ表示パネル（PDP：Plasma Display Panel）及び発光表示装置（LED：Light Emitting Display）などがある。平板表示装置の中で発光表示装置は、電子と正孔との再結合によって光を発生する発光素子を利用して映像を表示する。このような発光表示装置は、応答速度が速く、低い消費電力で駆動することができるという長所がある。10

##### 【0003】

図1は、従来の発光表示装置をあらわす図面である。

##### 【0004】

図1を参照すれば、従来の発光表示装置は、走査線S1ないしSn及びデータ線D1ないしDmに接続された複数の画素40を含む画素部30と、走査線S1ないしSnを駆動するための走査駆動部10と、データ線D1ないしDmを駆動するためのデータ駆動部20と、走査駆動部10及びデータ駆動部20を制御するためのタイミング制御部50とを備える。20

##### 【0005】

タイミング制御部50は、外部から供給される同期信号に対応してデータ駆動制御信号DCS及び走査駆動制御信号SCSを生成する。タイミング制御部50から生成されたデータ駆動制御信号DCSはデータ駆動部20に供給され、走査駆動制御信号SCSは走査駆動部10に供給される。そして、タイミング制御部50は、外部から供給されるデータDataをデータ駆動部20に供給する。

##### 【0006】

走査駆動部10は、タイミング制御部50から走査駆動制御信号SCSの供給を受ける。走査駆動制御信号SCSの供給を受けた走査駆動部10は走査信号を生成し、生成した走査信号を走査線S1ないしSnに順次供給する。30

##### 【0007】

データ駆動部20は、タイミング制御部50からデータ駆動制御信号DCSの供給を受ける。データ駆動制御信号DCSの供給を受けたデータ駆動部20は、データ信号を生成し、生成したデータ信号を走査信号と同期するようにデータ線D1ないしDmに供給する。

##### 【0008】

画素部30は、外部から第1電源ELVDD及び第2電源ELVSSの供給を受けて、それぞれの画素40に供給する。第1電源ELVDD及び第2電源ELVSSの供給を受けた画素40それぞれは、データ信号に対応して第1電源ELVDDから発光素子を経由して第2電源ELVSSに流れる電流を制御することでデータ信号に対応する光を生成する。40

##### 【0009】

すなわち、従来の発光表示装置で画素40それぞれは、データ信号に対応する所定の輝度の光を生成する。しかし、従来の発光表示装置には、画素40それぞれに含まれるトランジスターの閾値電圧のバラつき及び電子移動度（electron mobility）の偏差によって所望の輝度の映像を表示することができないという問題点がある。

##### 【0010】

実際に、画素40それぞれに含まれるトランジスターの閾値電圧は、画素40に含まれる画素回路の構造を制御することで、ある程度補償することができるが、電子移動度の偏

差は補償されない。したがって、電子移動度の偏差とは無関係に均一な画像を表示することができる発光表示装置が要求されている。

#### 【0011】

なお、上述した従来のデータ駆動回路、これを利用した発光表示装置、及びその駆動方法に関する技術を記載した文献としては、下記特許文献1がある。

【特許文献1】特開2003-186457号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0012】

したがって、本発明の目的は、均一な輝度の映像を表示することができるデータ駆動回路、これを利用した有機発光表示装置、及びその駆動方法を提供することである。10

#### 【課題を解決するための手段】

#### 【0013】

前記目的を果たすために、本発明の第1側面は、複数の階調電圧を生成するためのガンマ電圧部と、外部から供給されるk(kは自然数)ビットの第1データを利用して前記階調電圧の中でいずれか一つの階調電圧をデータ信号で選択するための少なくとも一つのデジタルアナログ変換器と、前記kビットの第1データを利用してp(pは自然数)ビットの第2データを生成する少なくとも一つのデコーダと、水平期間の第1期間の間に画素から所定の電流の供給を受ける少なくとも一つの電流シンク部と、前記所定の電流に対応して生成される補償電圧及び前記第2データを利用して前記データ信号の電圧値を制御するための少なくとも一つの電圧制御器と、前記水平期間中の前記第1期間を除いた第2期間の間に前記電圧値が制御された前記データ信号を前記画素に供給するための少なくとも一つのスイッチング部とを備えるデータ駆動回路を提供する。20

#### 【0014】

望ましくは、前記デジタルアナログ変換器と前記スイッチング部の間に設置されて前記第1期間中の一部期間の間にターンオンされて前記データ信号を前記スイッチング部に伝達するためのXトランジスターと、前記Xトランジスターと前記スイッチング部の間に接続される第1バッファーをさらに備える。前記デコーダは前記第1データを二進数の加重値(Binary Weighted)を持つように変換して前記第2データを生成する。30

#### 【0015】

また、前記電圧制御器は、前記Xトランジスターと前記第1バッファーの間のラインに一側端子が接続されるp個のキャパシタと、前記キャパシタそれぞれの他側端子とバッファーとの間に接続されるYトランジスターと、前記キャパシタそれぞれの他側端子と前記電流シンク部の間に接続されて前記Yトランジスターと違う導電型に設定されるZトランジスターを備える。

#### 【0016】

本発明の第2側面は、走査線、データ線、及び発光制御線に接続されるように位置される複数の画素を含む画素部と、前記走査線に走査信号を順次供給し、前記発光制御線に発光制御信号を順次供給するための走査駆動部と、各水平期間の第1期間の間に前記走査信号によって選択された画素から所定の電流の供給を受け、前記所定の電流に対応して生成される補償電圧と外部から供給される第1データの加重値を変更して生成される第2データを利用してデータ信号の電圧値を制御し、前記電圧値が制御されたデータ信号を前記水平期間中の第1期間を除いた第2期間の間に前記データ線に供給するためのデータ駆動部を備える有機発光表示装置を提供する。40

#### 【0017】

望ましくは、前記データ駆動部は、少なくとも一つのデータ駆動回路を具備して前記データ駆動回路それぞれは複数の階調電圧を生成するためのガンマ電圧部と、k(kは自然数)ビットの前記第1データを利用して前記階調電圧の中でいずれか一つの階調電圧を前記データ信号で選択するための少なくとも一つのデジタルアナログ変換器と、前記第1デ50

ータを利用して  $p$  ( $p$  は自然数) ビットの前記第 2 データを生成する少なくとも一つのデコーダと、前記第 1 期間の間画素から前記所定の電流の供給を受ける少なくとも一つの電流シンク部と、前記補償電圧及び前記第 2 データを利用して前記データ信号の電圧値を制御するための少なくとも一つの電圧制御器と、前記第 2 期間の間に前記電圧値が制御された前記データ信号を前記画素に供給するための少なくとも一つのスイッチング部とを備える。

#### 【0018】

本発明の第 3 側面は、外部から供給される  $k$  ビットの第 1 データに対応して複数の階調電圧の中でいずれか一つの階調電圧をデータ信号で選択する第 1 段階と、前記第 1 データが二進数の加重値を持つように変換して  $p$  ( $p$  は自然数) ビットの第 2 データを生成する第 2 段階と、水平期間の第 1 期間の間に走査信号によって選択された画素から所定の電流の供給を受ける第 3 段階と、前記電流が供給されるときに生成される補償電圧と前記第 2 データを利用して前記データ信号の電圧値を制御する第 4 段階と、前記第 4 段階で電圧値が制御されたデータ信号を前記水平期間中の第 1 期間を除いた第 2 期間の間に前記画素に供給する第 5 段階とを含む有機発光表示装置の駆動方法を提供する。10

#### 【0019】

望ましくは、前記所定の電流の電流値は前記画素が最大輝度に発光されるときに流れる電流と同じに設定される。前記第 1 段階で前記階調電圧は基準電源と第 1 電源の電圧とを分圧して生成される。前記第 4 段階は前記第 1 期間の間に複数のキャパシタの一側端子に前記第 1 電源の電圧値を供給する段階と、前記第 2 期間の間に前記第 2 データのビット値に対応して前記複数のキャパシタの一側端子に前記補償電圧の供給可否を制御して前記データ信号の電圧値を制御する段階とを含む。20

#### 【発明の効果】

#### 【0020】

上述したように、本発明のデータ駆動回路、これを利用した有機発光表示装置、及びその駆動方法によれば、画素から電流をシンクするときに発生する補償電圧を利用してデータ信号の電圧値を再設定するので、トランジスターの電子移動度とは無関係に均一な画像を表示することができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

以下、本発明の望ましい実施形態を、図 2 ないし図 11 を参照して、詳しく説明する。30

#### 【0022】

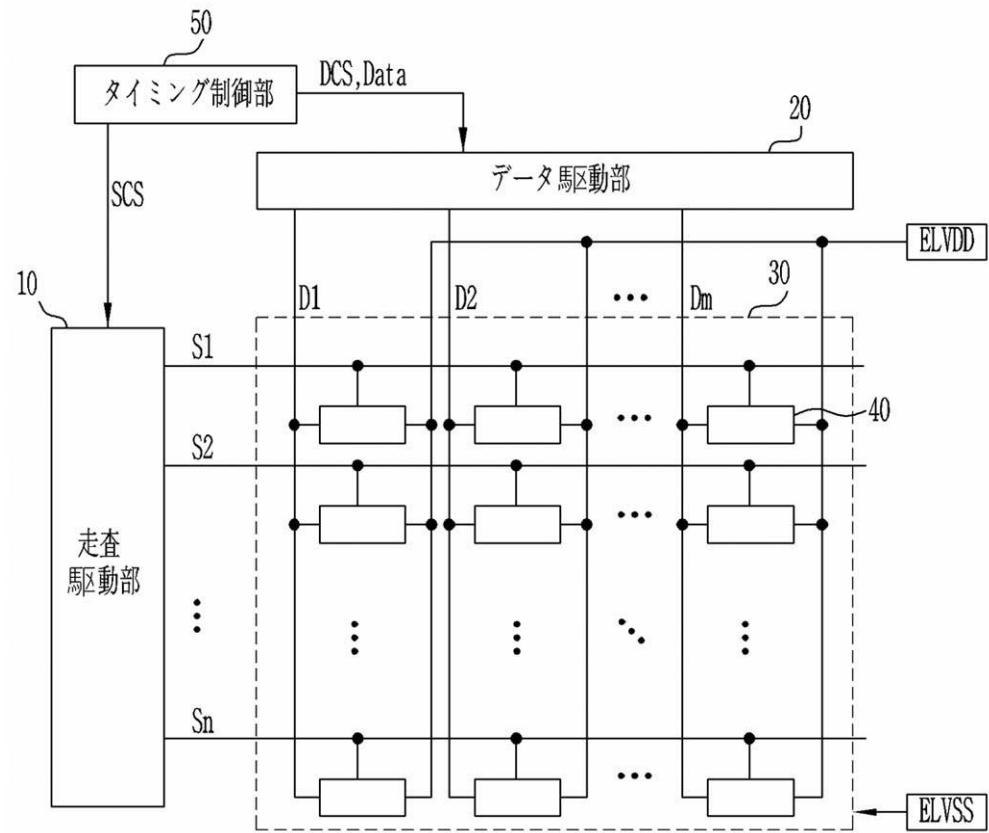

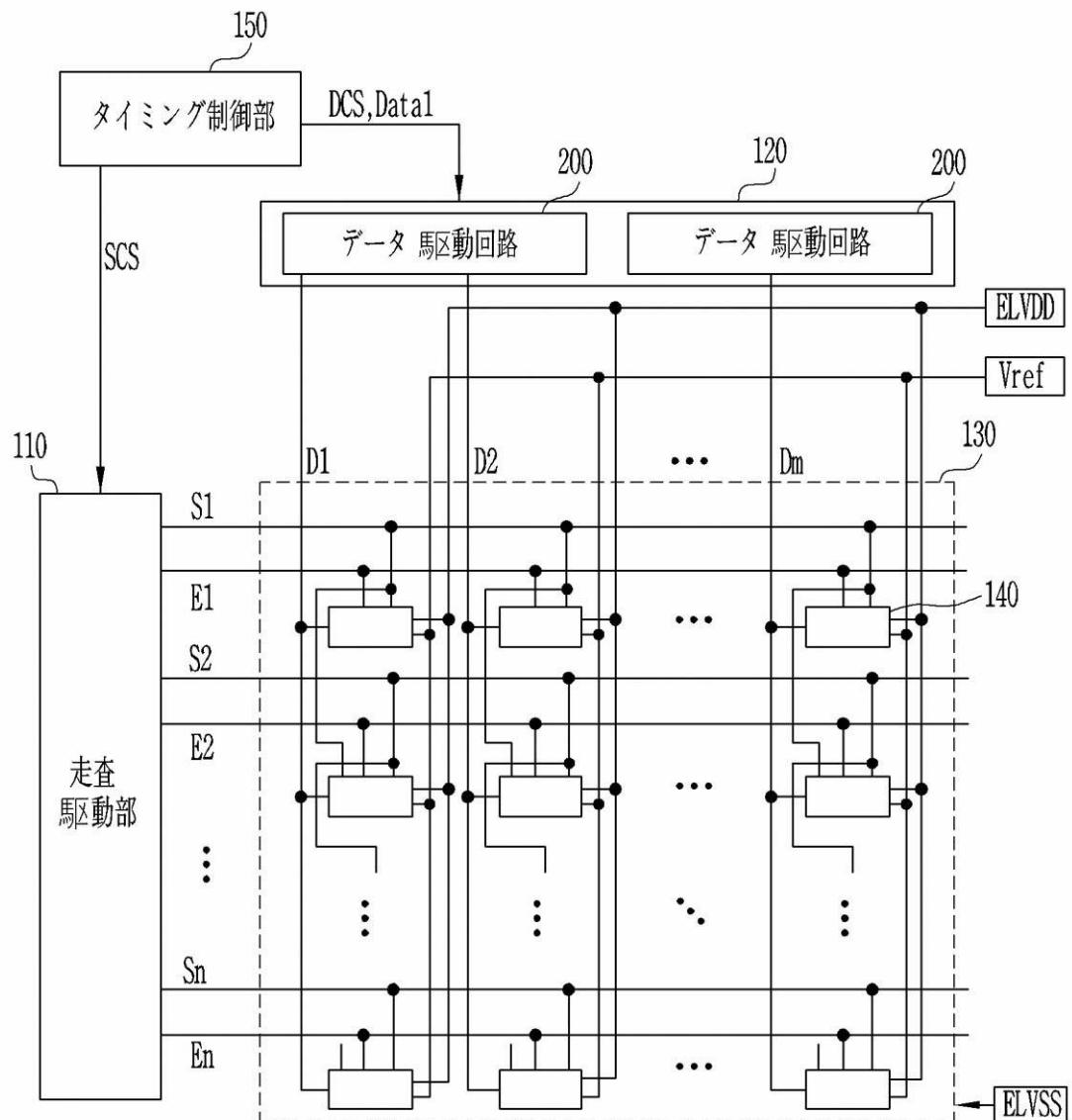

図 2 は、本発明の実施形態による有機発光表示装置をあらわす図面である。

#### 【0023】

図 2 を参照すれば、本発明の実施形態による発光表示装置は、走査線  $S_1 \text{ ないし } S_n$ 、発光制御線  $E_1 \text{ ないし } E_n$ 、及びデータ線  $D_1 \text{ ないし } D_m$  に接続される複数の画素 140 を含む画素部 130 と、走査線  $S_1 \text{ ないし } S_n$  及び発光制御線  $E_1 \text{ ないし } E_n$  を駆動するための走査駆動部 110 と、データ線  $D_1 \text{ ないし } D_m$  を駆動するためのデータ駆動部 120 と、走査駆動部 110 及びデータ駆動部 120 を制御するためのタイミング制御部 150 とを備える。40

#### 【0024】

画素部 130 は、走査線  $S_1 \text{ ないし } S_n$ 、発光制御線  $E_1 \text{ ないし } E_n$ 、及びデータ線  $D_1 \text{ ないし } D_m$  によって区画された領域に形成される複数の画素 140 を備える。画素 140 は外部から第 1 電源  $E_{LVD}\text{DD}$ 、第 2 電源  $E_{LVSS}$ 、及び基準電源  $V_{ref}$  の供給を受ける。基準電源  $V_{ref}$  の供給を受けた画素 140 それぞれは、基準電源  $V_{ref}$  と第 1 電源  $E_{LVD}\text{DD}$  の電圧差を利用して第 1 電源  $E_{LVD}\text{DD}$  の電圧降下を補償する。

#### 【0025】

そして、画素 140 それぞれは、データ信号に対応して、第 1 電源  $E_{LVD}\text{DD}$  から発光素子（図示せず）を経由して第 2 電源  $E_{LVSS}$  に所定の電流を供給する。このために、画素 140 それぞれは、図 3 または図 5 のように構成することができる。図 3 または図 550

に図示された画素 140 の詳細な構造は後述する。

【0026】

タイミング制御部 150 は、外部から供給される同期信号に対応してデータ駆動制御信号 DCS 及び走査駆動制御信号 SCS を生成する。タイミング制御部 150 から生成されたデータ駆動制御信号 DCS はデータ駆動部 120 に供給され、走査駆動制御信号 SCS は走査駆動部 110 に供給される。そして、タイミング制御部 150 は、外部から供給されるデータ Data をデータ駆動部 120 に供給する。

【0027】

走査駆動部 110 は、走査駆動制御信号 SCS の供給を受ける。走査駆動制御信号 SCS の供給を受けた走査駆動部 110 は、走査線 S1 ないし Sn に走査信号を順次供給する。そして、走査駆動制御信号 SCS の供給を受けた走査駆動部 110 は、発光制御線 E1 ないし En に発光制御信号を順次供給する。ここで、発光制御信号は 2 つの走査信号と重畠されるように供給される。このために、発光制御信号の幅（パルス幅）は走査信号の幅と同じか、または広く設定される。

10

【0028】

データ駆動部 120 は、タイミング制御部 150 からデータ駆動制御信号 DCS の供給を受ける。データ駆動制御信号 DCS の供給を受けたデータ駆動部 120 は、データ信号を生成し、生成したデータ信号をデータ線 D1 ないし Dm に供給する。ここで、データ駆動部 120 は、1 水平期間 (1H) 中の第 1 期間の間にデータ線 D1 ないし Dm に所定の電流を供給し、1 水平期間 (1H) 中の第 1 期間を除いた第 2 期間の間にデータ線 D1 ないし Dm に所定の電圧を供給する。このために、データ駆動部 120 は、少なくとも一つのデータ駆動回路 200 を備える。以下、説明の便宜性のために、第 2 期間の間にデータ線 D1 ないし Dm に供給される電圧を「データ信号」と称する。

20

【0029】

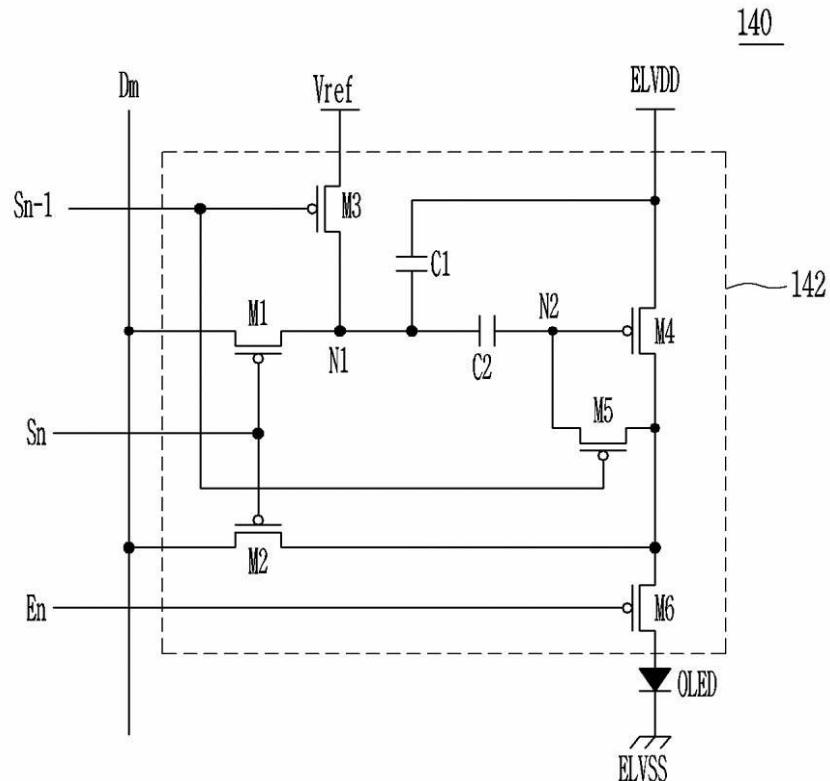

図 3 は、図 2 に図示された画素の一例をあらわす図面である。図 3 では、説明の便宜性のために第 m データ線 Dm、第 n - 1 走査線 Sn - 1、及び第 n 走査線 Sn、及び第 n 発光制御線 En に接続された画素を図示する。

20

【0030】

図 3 を参照すれば、本発明の実施形態の画素 140 は、発光素子 OLED、および発光素子 OLED に電流を供給するための画素回路 142 を備える。

30

【0031】

発光素子 OLED は、画素回路 142 から供給される電流に対応して所定の色の光を生成する。

【0032】

画素回路 142 は、第 n - 1 走査線 Sn - 1（以下、「以前走査線」と称する）に走査信号が供給されるときに第 1 電源 E<sub>L V D D</sub> の電圧降下と第 4 トランジスター M4 の閾値電圧とを補償し、第 n 走査線 Sn（以下、「現在走査線」と称する）に走査信号が供給されるときにデータ信号に対応する電圧を充電する。このために、画素回路 142 は、第 1 トランジスター M1 ないし第 6 トランジスター M6、第 1 キャパシタ C1、及び第 2 キャパシタ C2 を備える。現在走査線とは、実際に走査信号が供給されている走査線であり、以前走査線とは、現在走査線の前に走査信号が供給されていた走査線である。

40

【0033】

第 1 トランジスター M1 の第 1 電極はデータ線 Dm に接続されて、第 2 電極は第 1 ノード N1 に接続される。そして、第 1 トランジスター M1 のゲート電極は第 n 走査線 Sn に接続される。このような第 1 トランジスター M1 は第 n 走査線 Sn に走査信号が供給されるときにターンオンされて、データ線 Dm と第 1 ノード N1 とを電気的に接続させる。

【0034】

第 2 トランジスター M2 の第 1 電極はデータ線 Dm に接続されて、第 2 電極は第 4 トランジスター M4 の第 2 電極に接続される。そして、第 2 トランジスター M2 のゲート電極は第 n 走査線 Sn に接続される。このような第 2 トランジスター M2 は第 n 走査線 Sn に

50

走査信号が供給されるときにターンオンされて、データ線 D<sub>m</sub> と第 4 トランジスター M<sub>4</sub> の第 2 電極とを電気的に接続させる。

【 0 0 3 5 】

第 3 トランジスター M<sub>3</sub> の第 1 電極は、基準電源 V<sub>ref</sub> に接続されて、第 2 電極は第 1 ノード N<sub>1</sub> に接続される。そして、第 3 トランジスター M<sub>3</sub> のゲート電極は第 n - 1 走査線 S<sub>n-1</sub> に接続される。このような第 3 トランジスター M<sub>3</sub> は第 n - 1 走査線 S<sub>n-1</sub> に走査信号が供給されるときにターンオンされて基準電源 V<sub>ref</sub> と第 1 ノード N<sub>1</sub> を電気的に接続させる。

【 0 0 3 6 】

第 4 トランジスター M<sub>4</sub> の第 1 電極は、第 1 電源 E<sub>LVDD</sub> に接続されて、第 2 電極は第 6 トランジスター M<sub>6</sub> の第 1 電極に接続される。そして、第 4 トランジスター M<sub>4</sub> のゲート電極は第 2 ノード N<sub>2</sub> に接続される。このような第 4 トランジスター M<sub>4</sub> は第 2 ノード N<sub>2</sub> に印加される電圧、すなわち、第 1 キャパシタ C<sub>1</sub> 及び第 2 キャパシタ C<sub>2</sub> に充電された電圧に対応する電流を第 6 トランジスター M<sub>6</sub> の第 1 電極に供給する。

【 0 0 3 7 】

第 5 トランジスター M<sub>5</sub> の第 2 電極は、第 2 ノード N<sub>2</sub> に接続されて、第 1 電極は第 4 トランジスター M<sub>4</sub> の第 2 電極に接続される。そして、第 5 トランジスター M<sub>5</sub> のゲート電極は第 n - 1 走査線 S<sub>n-1</sub> に接続される。このような第 5 トランジスター M<sub>5</sub> は第 n - 1 走査線 S<sub>n-1</sub> に走査信号が供給されるときにターンオンされて第 4 トランジスター M<sub>4</sub> をダイオード形態で接続させる。

【 0 0 3 8 】

第 6 トランジスター M<sub>6</sub> の第 1 電極は第 4 トランジスター M<sub>4</sub> の第 2 電極に接続されて、第 2 電極は発光素子 O<sub>LED</sub> のアノード電極に接続される。そして、第 6 トランジスター M<sub>6</sub> のゲート電極は第 n 発光制御線 E<sub>n</sub> に接続される。このような第 6 トランジスター M<sub>6</sub> は第 n 発光制御線 E<sub>n</sub> に発光制御信号が供給されるときにターンオフされて、発光制御信号が供給されないときにターンオンされる。

【 0 0 3 9 】

ここで、第 n 発光制御線 E<sub>n</sub> に供給される発光制御信号は第 n - 1 走査線 S<sub>n-1</sub> 及び第 n 走査線 S<sub>n</sub> に供給される走査信号と重畠されるように供給される。したがって、第 6 トランジスター M<sub>6</sub> は第 n - 1 走査線 S<sub>n-1</sub> 及び第 n 走査線 S<sub>n</sub> に走査信号が供給されて第 1 キャパシタ C<sub>1</sub> 及び第 2 キャパシタ C<sub>2</sub> に所定の電圧が充電されるときにターンオフされて、それ以外の場合にはターンオンされて第 4 トランジスター M<sub>4</sub> と発光素子 O<sub>LED</sub> とを電気的に接続される。

【 0 0 4 0 】

一方、図 3 では説明の便宜性のためにトランジスター M<sub>1</sub> ないし M<sub>6</sub> を PMOS タイプに図示したが、本発明はこれに限定されない。

【 0 0 4 1 】

そして、図 3 に図示された画素 140 に供給される基準電源 V<sub>ref</sub> は、発光素子 O<sub>LED</sub> に電流を供給しない。すなわち、基準電源 V<sub>ref</sub> は画素 140 に電流を供給しないため、電圧降下が発生しない。したがって、基準電源 V<sub>ref</sub> は、画素 140 の位置とは無関係に同じ電圧値を維持することができる。ここで、基準電源 V<sub>ref</sub> の電圧値は、第 1 電源 E<sub>LVDD</sub> と同じに設定されるか、または異なるように設定することができる。

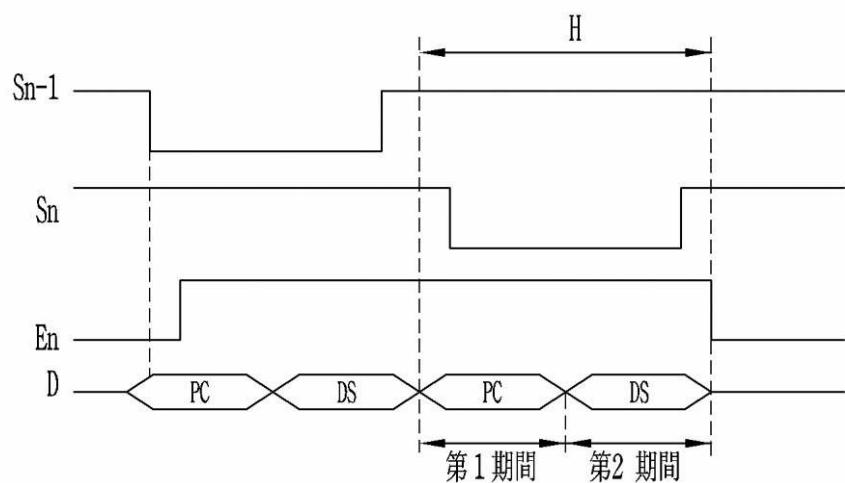

【 0 0 4 2 】

図 4 は、図 3 に図示された画素 140 が駆動する際の各種信号波形をあらわす波形図である。図 4 に示すように、1 水平期間 (1H) は、第 1 期間及び第 2 期間に分けられる。第 1 期間の間にデータ線 D<sub>1</sub> ないし D<sub>m</sub> には所定の電流 P<sub>C</sub> (Pre-determined Current) が流れ、第 2 期間の間にデータ信号 D<sub>S</sub> (Data Signal) が供給される。

【 0 0 4 3 】

実際に、第 1 期間の間には画素 140 からデータ駆動回路 200 に所定の電流 P<sub>C</sub> が供

10

20

30

40

50

給される(Current Sink)。そして、第2期間の間にはデータ駆動回路200から画素140にデータ信号DSが供給される。以後、説明の便宜性のために基準電源Vrefと第1電源ELVDDとの初期電圧値が同じに設定されると仮定する。

#### 【0044】

図3及び図4を参照して動作過程を詳しく説明すれば、まず、第n-1走査線Sn-1に走査信号が供給される。第n-1走査線Sn-1に走査信号が供給されれば第3トランジスターM3及び第5トランジスターM5がターンオンされる。第5トランジスターM5がターンオンされれば、第4トランジスターM4がダイオード形態に接続される。第4トランジスターM4がダイオード形態に接続されれば、第2ノードN2には第1電源ELVDDから第4トランジスターM4の閾値電圧を差し引いた電圧が印加される。

10

#### 【0045】

そして、第3トランジスターM3がターンオンされれば、基準電源Vrefの電圧が第1ノードN1に印加される。この時、第2キャパシタC2は、第1ノードN1と第2ノードN2との電圧差に対応する電圧を充電する。この場合、基準電源Vrefと第1電源ELVDDとの電圧値が同じだと仮定すれば、第2キャパシタC2には第4トランジスターM4の閾値電圧に対応する電圧が充電される。そして、第1電源ELVDDで所定の電圧降下が発生すれば、第2キャパシタC2には第4トランジスターM4の閾値電圧及び第1電源ELVDDの電圧降下に対応する電圧が充電される。

20

#### 【0046】

すなわち、本発明では第n-1走査線Sn-1に走査信号が供給される期間の間に第1電源ELVDDの電圧降下に対応する電圧及び第4トランジスターM4の閾値電圧が第2キャパシタC2に充電されることで、第1電源ELVDDの電圧降下を補償することができる。

20

#### 【0047】

第2キャパシタC2に所定の電圧が充電された後、第n走査線Snに走査信号が供給される。第n走査線Snに走査信号が供給されれば、第1トランジスターM1及び第2トランジスターM2がターンオンされる。第2トランジスターM2がターンオンされれば、1水平期間の第1期間の間に所定の電流PCが画素140からデータ線Dmを経由してデータ駆動回路200に供給される。

30

#### 【0048】

実際に、所定の電流PCは、第1電源ELVDD、第4トランジスターM4、第2トランジスターM2、及びデータ線Dmを経由してデータ駆動回路200に供給される。

#### 【0049】

データ駆動回路200は、所定の電流PCがシンクされるときに発生する所定の電圧(以下、「補償電圧」と称する)を利用してデータ信号DSの電圧を再設定し、再設定したデータ信号DSの電圧を水平期間の第2期間の間に第1トランジスターM1を経由して第1ノードN1に供給する。すると、第1キャパシタC1にはデータ信号DSと第1電源ELVDDとの電圧差に対応する電圧が充電される。この時、第2ノードN2はフローティング状態に設定されるので、第2キャパシタC2は以前に充電された電圧を維持する。

40

#### 【0050】

すなわち、本発明の実施形態では、以前走査線に走査信号が供給される期間の間に第2キャパシタC2に第4トランジスターM4の閾値電圧及び第1電源ELVDDの電圧降下に対応する電圧を充電することで、第1電源ELVDDの電圧降下及び第4トランジスターM4の閾値電圧を補償することができる。そして、本発明の実施形態では、現在走査線に走査信号が供給される期間の間に画素140に含まれたトランジスターの電子移動度などが補償されるようにデータ信号DSの電圧値を再設定し、電圧値が再設定されたデータ信号DSを画素140に供給する。したがって、本発明の実施形態では、トランジスターの閾値電圧、電子移動度などのバラつきを補償して均一な画像を表示することができる。

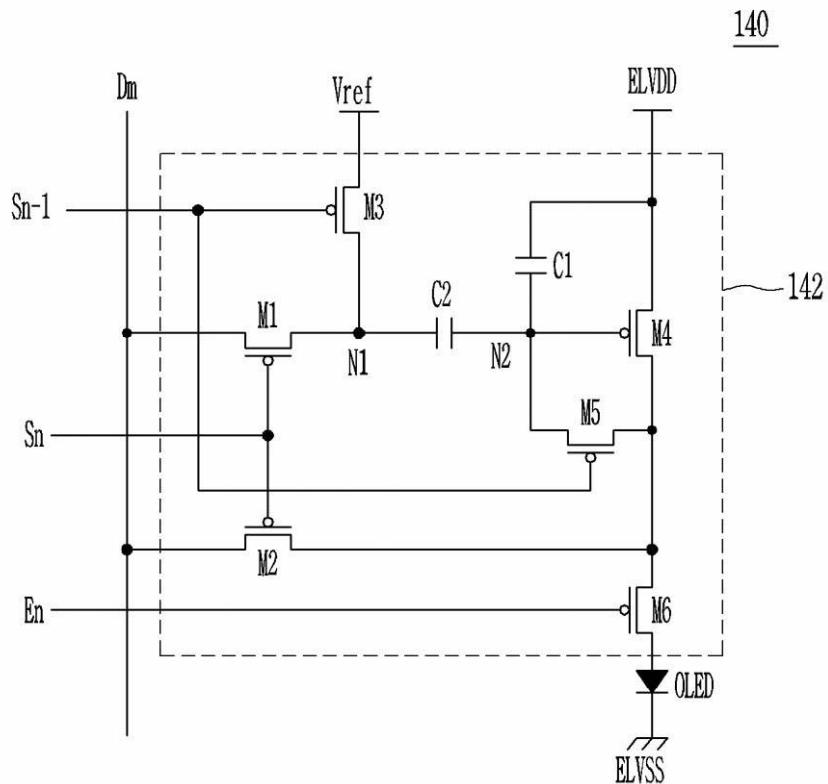

#### 【0051】

図5は、図2に図示された画素の他の例をあらわす図面である。図5は、第1キャパシ

50

タ C 1 が第 2 ノード N 2 と第 1 電源 E L V D D との間に設置されることを除き、図 3 と同じ構成で設定される。

#### 【 0 0 5 2 】

図 4 及び図 5 を参照して、動作過程を詳しく説明すれば、まず、第 n - 1 走査線 S n - 1 に走査信号が供給される。第 n - 1 走査線 S n - 1 に走査信号が供給されれば第 3 パーク M 3 及び第 5 パーク M 5 がターンオンされる。第 5 パーク M 5 がターンオンされれば、第 4 パーク M 4 がダイオード形態に接続される。第 4 パーク M 4 がダイオード形態に接続されれば、第 2 ノード N 2 には第 1 電源 E L V D D から第 4 パーク M 4 の閾値電圧を差し引いた電圧が印加される。したがって、第 1 キャパシタ C 1 には第 4 パーク M 4 の閾値電圧に対応する電圧が充電される。10

#### 【 0 0 5 3 】

そして、第 3 パーク M 3 がターンオンされれば、基準電源 V ref の電圧が第 1 ノード N 1 に印加される。すると、第 2 キャパシタ C 2 は、第 1 ノード N 1 と第 2 ノード N 2 との電圧差に対応する電圧が充電される。ここで、第 n - 1 走査線 S n - 1 に走査信号が供給される期間の間に第 1 パーク M 1 及び第 2 パーク M 2 がターンオフされるので、データ信号 D S は画素 140 に供給されない。

#### 【 0 0 5 4 】

次いで、第 n 走査線 S n に走査信号が供給されて第 1 パーク M 1 及び第 2 パーク M 2 がターンオンされる。第 2 パーク M 2 がターンオンされれば、1 水平期間の第 1 期間の間に所定の電流 P C が画素 140 からデータ線 D m を経由してデータ駆動回路 200 に供給される。20

#### 【 0 0 5 5 】

実際に、所定の電流 P C は、第 1 電源 E L V D D 、第 4 パーク M 4 、第 2 パーク M 2 、及びデータ線 D m を経由してデータ駆動回路 200 に供給される。

#### 【 0 0 5 6 】

データ駆動回路 200 は、所定の電流 P C がシンクされるときに発生される補償電圧を利用してデータ信号 D S の電圧を再設定し、電圧が再設定されたデータ信号 D S を水平期間の第 2 期間の間に第 1 パーク M 1 を経由して第 1 ノード N 1 に供給する。すると、第 1 キャパシタ C 1 及び第 2 キャパシタ C 2 にはデータ信号 D S に対応して所定の電圧が充電される。30

#### 【 0 0 5 7 】

実際に、データ信号 D S が供給されれば、第 1 ノード N 1 の電圧が降下する。第 2 ノード N 2 がフローティングされているので、第 1 ノード N 1 の電圧降下量に対応して第 2 ノード N 2 の電圧も降下する。この場合、第 2 ノード N 2 で降下する電圧は、第 1 キャパシタ C 1 及び第 2 キャパシタ C 2 の容量によって決まる。

#### 【 0 0 5 8 】

第 2 ノード N 2 の電圧が降下すれば、第 1 キャパシタ C 1 には、第 2 ノード N 2 の電圧に対応して所定の電圧が充電される。ここで、第 1 ノード N 1 の電圧降下量は、データ信号 D S によって決まり、これによって第 1 キャパシタ C 1 に充電される電圧もデータ信号 D S によって決まる。そして、本発明の実施形態では、画素 140 に含まれたパーカーの電子移動度などが補償されるようにデータ信号 D S の電圧を再設定するからパーカーの電子移動度などのバラつきを補償して画像を表示することができる。40

#### 【 0 0 5 9 】

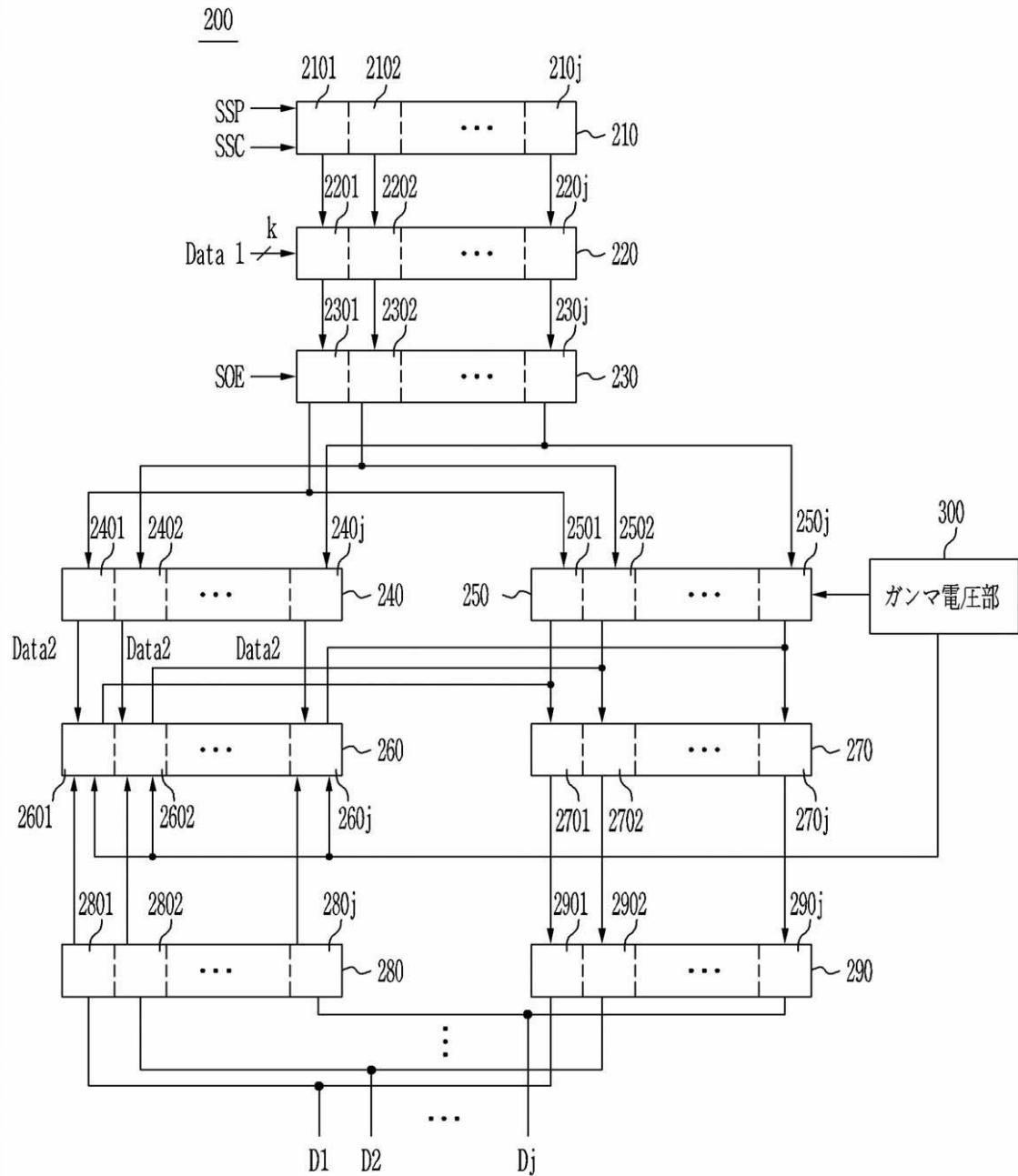

図 6 は、図 2 に図示されたデータ駆動回路の一例をあらわすブロック図である。図 6 では、説明の便宜性のためにデータ駆動回路 200 が j ( j は 2 以上の自然数 ) 個のチャンネルを持つと仮定する。

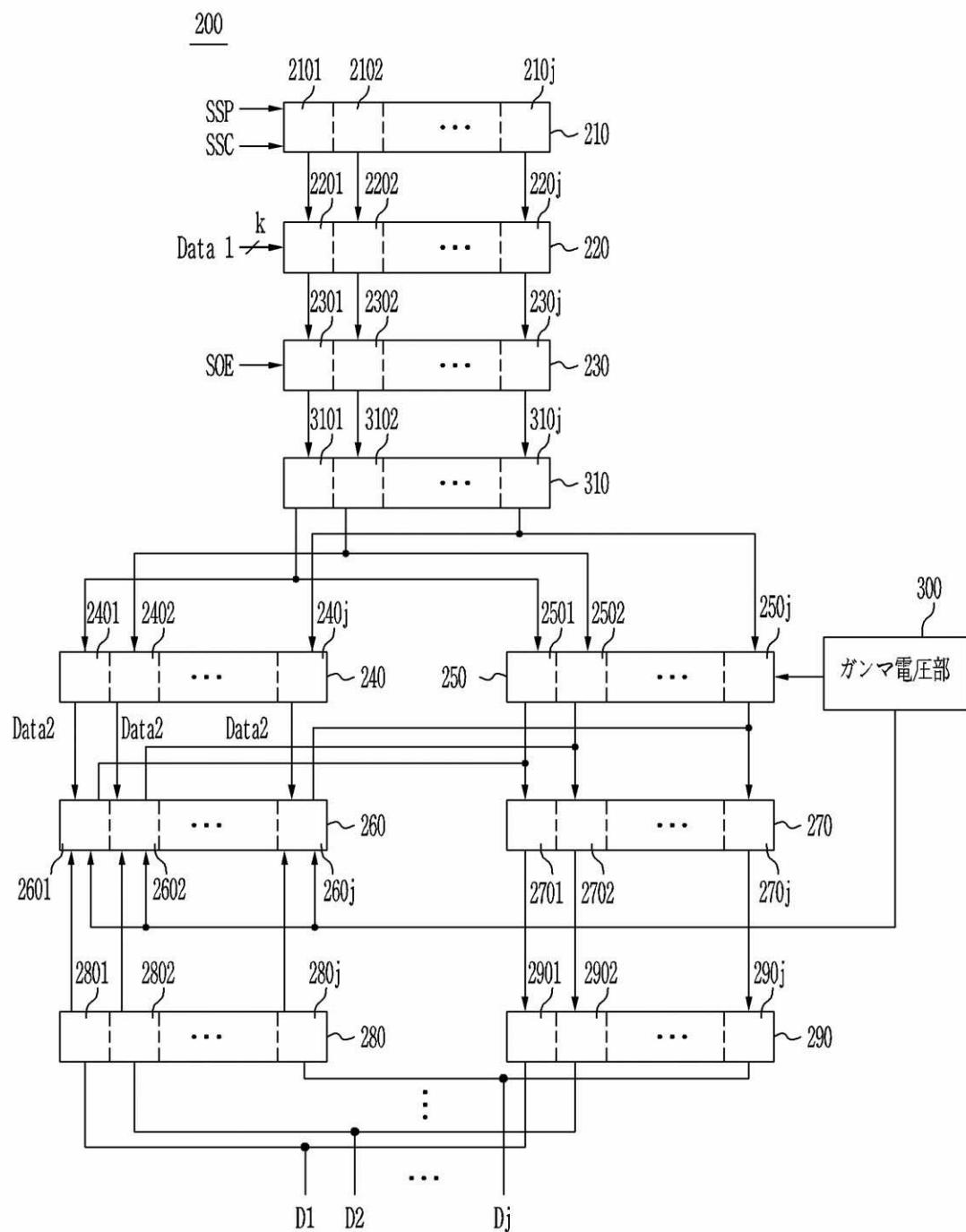

#### 【 0 0 6 0 】

図 6 を参照すれば、本発明のデータ駆動回路 200 は、シフトレジスター部 210 、サンプリングラッチ部 220 、ホールディングラッチ部 230 、デコーダ部 240 、デジタル

アナログ変換部（以下「D A C 部」と称する）250、電圧制御部260、第1バッファ一部270、電流供給部280、選択部290、及びガンマ電圧部300を備える。

#### 【0061】

シフトレジスター部210は、タイミング制御部150からソースシフトクロックSSC及びソーススタートパルスSSPの供給を受ける。タイミング制御部150からソースシフトクロックSSC及びソーススタートパルスSSPの供給を受けたシフトレジスター部210は、ソースシフトクロックSSCの1周期ごとにソーススタートパルスSSPをシフトさせながら順次j個のサンプリング信号を生成する。このために、シフトレジスター部210は、j個のシフトレジスター2101ないし210jを備える。

#### 【0062】

サンプリングラッチ部220は、シフトレジスター部210から順次供給されるサンプリング信号に応答してデータを順次保存する。ここで、サンプリングラッチ部220は、j個のデータを保存するためにj個のサンプリングラッチ2201ないし220jを備える。そして、それぞれのサンプリングラッチ2201ないし220jは、データのビット数に対応する大きさ（保存容量）を持つ。例えば、データがkビットで構成される場合、サンプリングラッチ2201ないし220iそれぞれはkビットの大きさに設定される。

#### 【0063】

ホルディングラッチ部230は、ソース出力イネーブルSOEの信号が入力されるとき、サンプリングラッチ部220からデータの入力を受けて保存する。そして、ホルディングラッチ部230は、ソース出力イネーブルSOEが入力されるとき、ホルディングラッチ部230自身に保存されたデータをD A C 部250に供給する。ここで、ホルディングラッチ部230は、j個のデータを保存するためにj個のホルディングラッチ2301ないし230jを備える。そして、それぞれのホルディングラッチ2301ないし230jは、データのビット数に対応される大きさを持つ。例えば、データがkビットで構成される場合、ホルディングラッチ2301ないし230jそれぞれは、データDataを保存することができるようkビットの大きさに設定される。

#### 【0064】

デコーダ部240は、j個のデコーダ2401ないし240jを備える。それぞれのデコーダ2401ないし240jは、デコーダ自身に供給されるkビットの第1データをp（pは自然数）ビットの第2データData2に変換する。ここで、デコーダ2401ないし240jは、二進数の加重値（Binary Weighted）を持つようにpビットの第2データData2を生成する。

#### 【0065】

これを詳しく説明すれば、外部から供給される第1データData1は、ガンマ電圧部300から所定の電圧が設定されるようにその加重値が決まる。すなわち、第1データData1は、ガンマ電圧部300から生成される複数の階調電圧の中で所望の階調電圧が選択されるようにビット値が決まる。

#### 【0066】

デコーダ2401ないし240jは、階調電圧に対応してビット値が設定されたkビットのデータを二進数の加重値を持つpビットの第2データData2に変換する。例えば、デコーダ2401ないし240jは、8ビットの第1データData1を利用して5ビットの第2データData2を生成する。

#### 【0067】

電流供給部280は、1水平期間の第1期間の間にデータ線D1ないしDjに接続された画素140から所定の電流PCをシンクする。実際に、電流供給部280は、それぞれの画素140に流れることができる最大電流、すなわち、画素140が最大輝度に発光するときに有機発光ダイオードOLEDに供給されるべき電流をシンクする。そして、電流供給部280は、電流がシンクされるときに発生される所定の補償電圧を比較部260に供給する。このために、電流供給部280は、j個の電流シンク部2801ないし280jを備える。

10

20

30

40

50

## 【0068】

ガンマ電圧部300は、 $k$ ビットの第1データData1に対応して所定の階調電圧を生成する。実際に、電圧生成部300は、図8に図示されたように複数の分圧抵抗R1ないしR1で構成されて $2^k$ 個の階調電圧を生成する。ガンマ電圧部300から生成された階調電圧は、DAC2501ないし250jに供給される。

## 【0069】

DAC部250は、j個のDAC2501ないし250jを備える。DAC2501ないし250jそれぞれは、ホルディングラッチ部2301ないし230jから供給される第1データData1のビット値に対応してガンマ電圧部300から供給される階調電圧の中でいずれか一つをデータ信号DSで選択する。

10

## 【0070】

電圧制御部260は、j個の電圧制御器2601ないし260jを備える。それぞれの電圧制御器2601ないし260jは、補償電圧、第2データData2、及び第3電源VSSの供給を受ける。ここで、第3電源VSSは、ガンマ電圧部300の一側端子に供給される電圧である。補償電圧、第2データData2、及び第3電源VSSの供給を受けた電圧制御器2601ないし260jは、画素140に含まれたトランジスターの電子移動度などが補償されるようにデータ信号DSの電圧値を制御する。

## 【0071】

第1バッファー部270は、電圧制御部260によって電圧が制御されたデータ信号DSを選択部290に供給する。このために、第1バッファー部270は、j個の第1バッファー2701ないし270jを備える。

20

## 【0072】

選択部290は、データ線D1ないしDjと第1バッファー2701ないし270jとの電気的連結を制御する。実際に、選択部290は、1水平期間の第2期間の間のみにデータ線D1ないしDjと第1バッファー2701ないし270jとを電気的に接続させ、それ以外にはデータ線D1ないしDjと第1バッファー2701ないし270jとを接続させない。このために、選択部290は、j個のスイッチング部2901ないし290jを備える。

## 【0073】

一方、本発明の実施形態のデータ駆動回路200は、図7に示すようにホルディングラッチ部230の次の段にレベルシフター部310をさらに含むことができる（第2実施形態）。レベルシフター部310は、ホルディングラッチ部230から供給される第1データData1の電圧レベルを上昇させてDAC部250及びデコーダ部240に供給する。

30

## 【0074】

外部システムからデータ駆動回路200に高い電圧レベルを持つ第1データData1が供給されれば、電圧レベルに対応して高い耐圧を有する回路部品を設置する必要があるため、製造コストが増加する。したがって、データ駆動回路200の外部では、低い電圧レベルを持つ第1データData1を供給し、この低い電圧レベルを持つ第1データData1をレベルシフター部310で高い電圧レベルに昇圧させる。

40

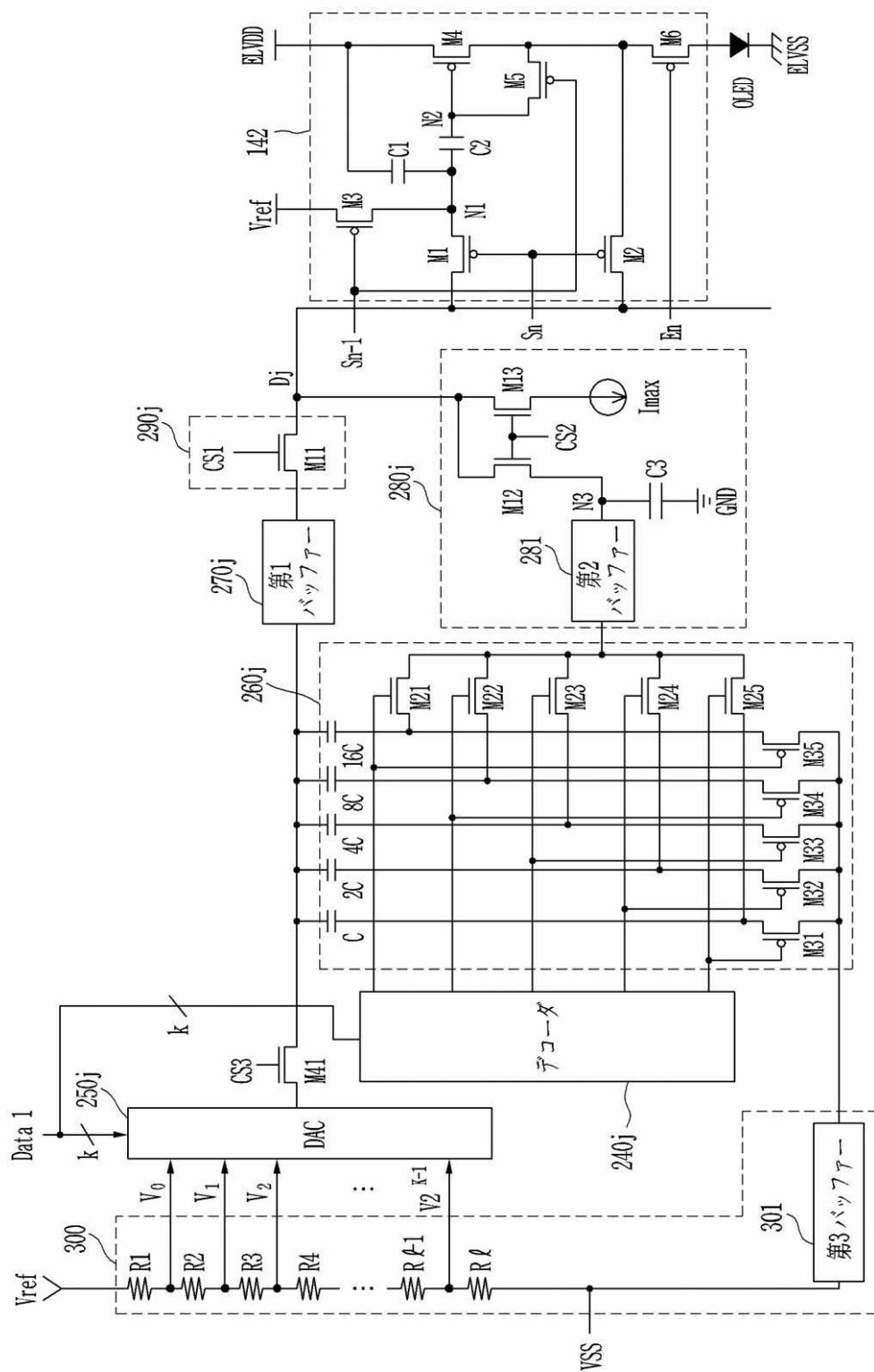

## 【0075】

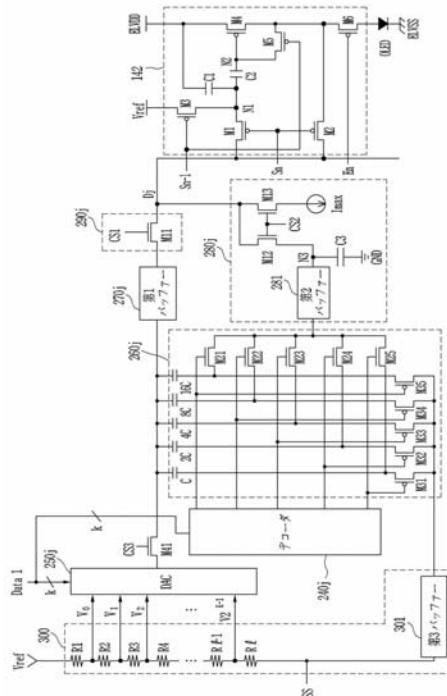

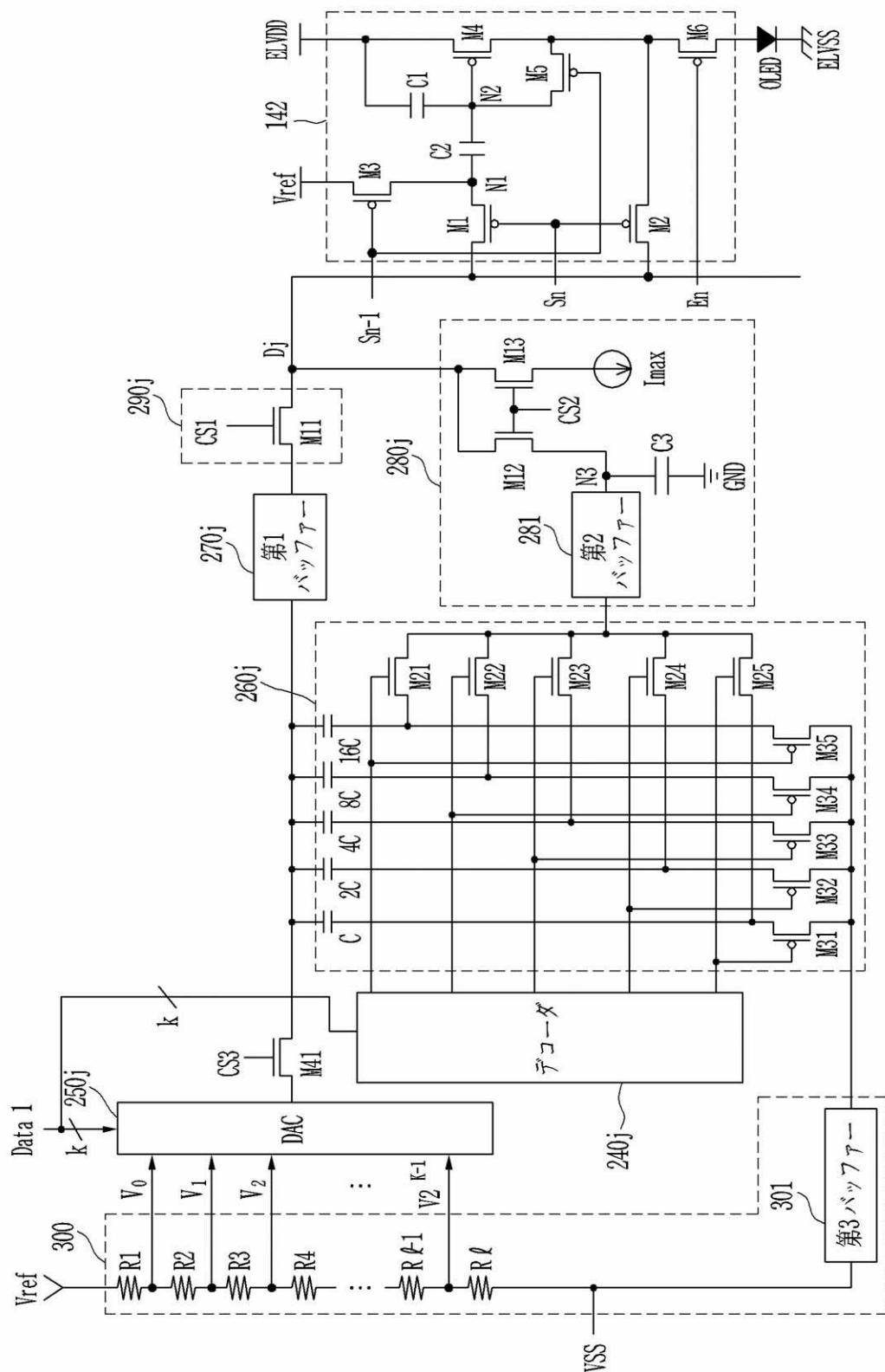

図8は、図6に図示されたガンマ電圧部、DAC、デコーダ、電圧制御器、スイッチング部、電流シンク部、及び画素の連結関係をあらわす図面である。図8では、説明の便宜性のためにj番目チャンネルを図示して、データ線Djが図3に図示された画素140と接続されると仮定する。

## 【0076】

図8を参照すれば、ガンマ電圧部300は、複数の分圧抵抗R1ないしR1を備える。分圧抵抗R1ないしR1は、基準電源Vrefと第3電源VSSとの間に位置されて電圧を分圧する。実際に、分圧抵抗R1ないしR1は基準電源Vrefと第3電源VSSとの間の電圧を分圧して複数の階調電圧V0ないしV2<sup>k-1</sup>を生成し、生成された階調電圧

50

V<sub>0</sub>ないし2<sup>K-1</sup>をD A C 2 5 0 jに供給する。

【0077】

そして、ガンマ電圧部300は、第3電源VSSの電圧を、第3バッファー301を経由して電圧制御器260jに供給する。

【0078】

D A C 2 5 0 jは、第1データD a t a 1のビット値に対応して階調電圧V<sub>0</sub>ないしV<sub>2<sup>K-1</sup></sub>の中でいずれか一つの階調電圧をデータ信号D Sで選択して第1バッファー270jに供給する。ここで、D A C 2 5 0 jと第1バッファー270jとの間には、図9に図示された第3制御信号C S 3によって制御される第41トランジスターM 4 1(Xトランジスター)が設置される。

10

【0079】

すなわち、第41トランジスターM 4 1は水平期間の第1期間中の一部期間の間にターンオンされて、D A C 2 5 0 jから供給されるデータ信号D Sを第1バッファー270jに供給する。実際に、第3制御信号C S 3は、第2制御信号C S 2より遅く上昇し、第2制御信号C S 2と同一時点で降下する。

【0080】

電流シンク部280jは、第2制御信号C S 2によって制御される第12トランジスターM 1 2(第1の電流シンク部トランジスター)及び第13トランジスターM 1 3(第2の電流シンク部トランジスター)と、第13トランジスターM 1 3の第1電極に接続される電流源I<sub>m a x</sub>と、第3ノードN 3とG N D(基底電圧源)との間に接続される第3キャパシタC 3と、第3ノードN 3と電圧制御器260jとの間に接続される第2バッファー281を備える。

20

【0081】

第12トランジスターM 1 2のゲート電極は、第13トランジスターM 1 3のゲート電極に接続され、第2電極は第13トランジスターM 1 3の第2電極とデータ線D jとに接続される。そして、第12トランジスターM 1 2の第1電極は第2バッファー281に接続される。このような第12トランジスターM 1 2は、第2制御信号C S 2によって1水平期間(1H)の第1期間の間にターンオンされて第2期間の間にターンオフされる。

【0082】

第13トランジスターM 1 3のゲート電極は、第12トランジスターM 1 2のゲート電極に接続され、第2電極はデータ線D jに接続される。そして、第13トランジスターM 1 3の第1電極は電流源I<sub>m a x</sub>に接続される。このような第13トランジスターM 1 3は、第2制御信号C S 2によって1水平期間(1H)の第1期間の間にターンオンされて第2期間の間にターンオフされる。

30

【0083】

電流源I<sub>m a x</sub>は、画素140が最大輝度に発光するとき、有機発光ダイオードO L E Dに供給されるべき電流を第12トランジスターM 1 2及び第13トランジスターM 1 3がターンオンされる第1期間の間に画素140から供給を受ける(C u r r e n t S i n k)。

【0084】

第3キャパシタC 3は、電流源I<sub>m a x</sub>によって画素140から電流がシンクされるとき第3ノードN 3に印加される補償電圧を格納する。実際に、第3キャパシタC 3は、第1期間の間に第3ノードN 3に印加される補償電圧を充電し、第12トランジスターM 1 2及び第13トランジスターM 1 3がターンオフされても第3ノードN 3の補償電圧を一定に維持する。第2バッファー281は、第3ノードN 3に印加された補償電圧を電圧制御器260jに伝達する。

40

【0085】

デコーダ240jは、デコーダ240j自身に供給されるkビットの第1データD a t a 1を二進数の加重値を持つようにpビットの第2データD a t a 2に変換する。そして、デコーダ240jは水平期間の第1期間の間に初期化信号を電圧制御器260jに供給

50

し、第2期間中pビットの第2データData2を電圧制御器260jに供給する。以後、説明の便宜性のためにpビットを5ビットと仮定する。

#### 【0086】

電圧制御器260jは、補償電圧、第2データData2、及び第3電源VSSの電圧の供給を受けてデータ信号DSの電圧値を制御する。このために、電圧制御器260jは、第41トランジスターM41と第1バッファー270jとの間のラインに一側端子が接続される5個（すなわちp個）の第4キャパシタと、p個の第4キャパシタと第3バッファー301との間に接続される5個のPMOSトランジスターM31, M32, M33, M34, M35(Yトランジスター)と、5個の第4キャパシタと第2バッファー281との間に接続される5個のNMOSトランジスターM21, M22, M23, M24, M25(Zトランジスター)と、を備える。10

#### 【0087】

5個の第4キャパシタのそれぞれの容量は、C, 2C, 4C, 8C, 16Cであり、 $2^0, 2^1, 2^2, 2^3, 2^4$ のように2の累乗数で容量は増加し、表現することができる。すなわち、第4キャパシタの容量は、第2データData2に対応して二進数の加重値の形態に設定される。

#### 【0088】

PMOSトランジスターM31, M32, M33, M34, M35それぞれは、5個の第4キャパシタの中でいずれか一つと第3バッファー301との間に設置される。このようなPMOSトランジスターM31, M32, M33, M34, M35は、デコーダ240jから初期化信号が供給されるときにターンオンされて第4キャパシタの一側端子の電圧を第3電源VSSの電圧に設定する。20

#### 【0089】

NMOSトランジスターM21, M22, M23, M24, M25それぞれは、第4キャパシタの中でいずれか一つと第2バッファー281との間に設置される。このようなNMOSトランジスターM21, M22, M23, M24, M25は、デコーダ240jから生成される第2データData2に対応して第2期間の間にターンオンまたはターンオフされる。

#### 【0090】

ここで、NMOSトランジスターM21, M22, M23, M24, M25は、第2データData2のビット加重値に対応する第4キャパシタが選択されるように制御される。例えば、デコーダ240jから生成される第2データData2のビットが“00011”に設定されれば、第24トランジスターM24及び第25トランジスターM25がターンオンされて、容量がC, 2Cの第4キャパシタの一側端子に補償電圧を印加する。30

#### 【0091】

つまり、 $2^0, 2^1$ に対応するビットが“1”的値を持つとき、 $2^0, 2^1$ に対応する容量を持つ第4キャパシタの一側端子に補償電圧が印加されるように、NMOSトランジスターM21, M22, M23, M24, M25のターンオン及びターンオフが制御される。

#### 【0092】

一方、第4キャパシタの中で少なくとも一つの一側端子に補償電圧が印加されれば、第41トランジスターM41と第1バッファー270jとの間のラインに印加されたデータ信号DSの電圧値が増加または減少される（実際に、データ信号DSの電圧値の増加または減少は補償電圧の電圧値によって決まる）。

#### 【0093】

ここで、データ信号DSの電圧値が補償電圧によって制御されるので、画素140に含まれたトランジスターの電子移動度が補償されるようにデータ信号DSの電圧値が制御され、これによって画素部130に均一な画像を表示することができる。

#### 【0094】

つまり、本発明のデータ駆動回路200は電子移動度などによって決まった補償電圧を50

を利用してデータ信号 D S の電圧値を制御するため、トランジスターの電子移動度のバラつき現象を補償することができる。

【0095】

第 1 バッファー 270j は、第 4 1 トランジスター M 4 1 と第 1 バッファー 270j との間のラインに印加されたデータ信号 D S をスイッチング部 290j に供給する。

【0096】

スイッチング部 290j は、第 1 1 トランジスター M 1 1 を備える。このような第 1 1 トランジスター M 1 1 は、図 9 に図示された第 1 制御信号 C S 1 によって制御される。すなわち、第 1 1 トランジスター M 1 1 は、1 水平期間 (1H) の第 2 期間の間にターンオンされて第 1 期間の間にターンオフされる。したがって、データ信号 D S は、1 水平期間 (1H) 中の第 2 期間の間にデータ線 D j に供給されて、それ以外の期間の間には供給されない。

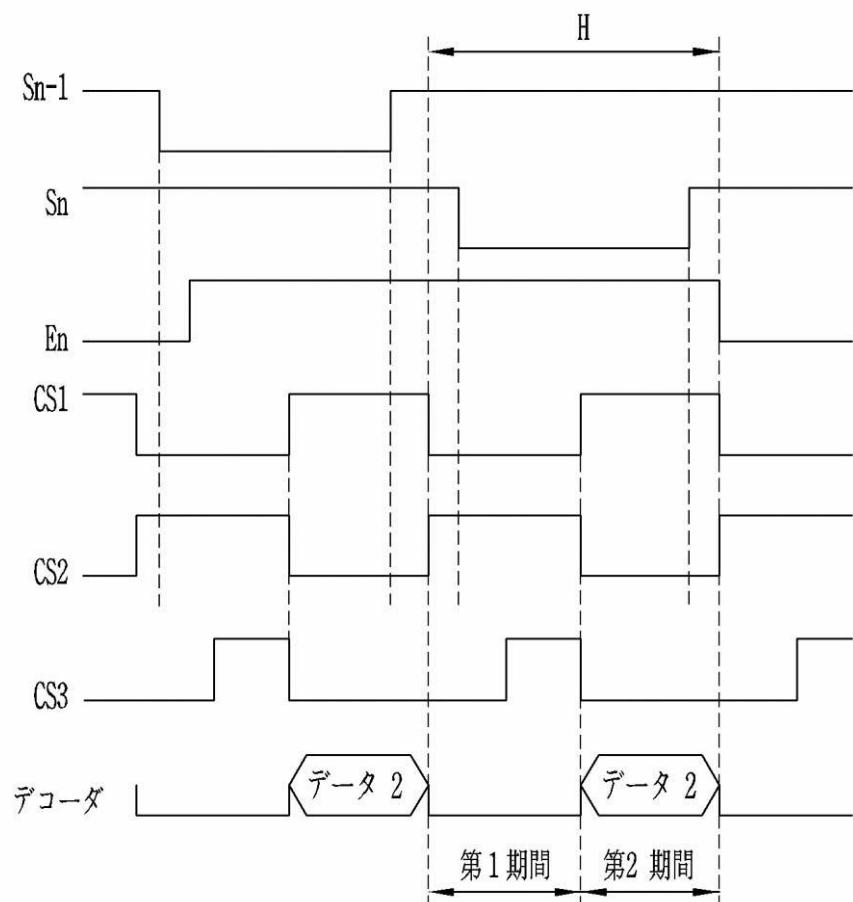

【0097】

図 9 は、図 8 に図示されたスイッチング部、電流シンク部、及び第 4 1 トランジスターに供給される駆動波形を現わす図面である。

【0098】

図 8 及び図 9 を参照して、画素 140 に供給されるデータ信号 D S の電圧制御過程を詳しく説明する。

【0099】

まず、第 n - 1 走査線 S n - 1 に走査信号が供給される。第 n - 1 走査線 S n - 1 に走査信号が供給されれば、第 3 トランジスター M 3 及び第 5 トランジスター M 5 がターンオンされる。すると、第 2 ノード N 2 には第 1 電源 E L V D D から第 4 トランジスター M 4 の閾値電圧を差し引いた電圧が印加され、第 1 ノード N 1 には基準電源 V r e f の電圧が印加される。この時、第 2 キャパシタ C 2 には、第 1 電源 E L V D D の電圧降下に対応する電圧及び第 4 トランジスター M 4 の閾値電圧に対応する電圧が充電される。

【0100】

実際に、第 1 ノード N 1 及び第 2 ノード N 2 それぞれに印加される電圧は、数式(1)のように表現することができる。

【0101】

【数 1】

$$V_{N1} = V_{ref} \quad V_{N2} = ELVDD - |V_{thM4}| \dots \quad (1)$$

【0102】

数式(1)で、 $V_{N1}$  は第 1 ノード N 1 に印加される電圧、 $V_{N2}$  は第 2 ノード N 2 に印加される電圧、 $V_{thM4}$  は第 4 トランジスター M 4 の閾値電圧をあらわす。

【0103】

一方、第 n - 1 走査線 S n - 1 に供給される走査信号がオフされる時点と第 n 走査線 S n に走査信号が供給される時点との間に第 1 ノード N 1 及び第 2 ノード N 2 は、フローティング状態に設定される。したがって、第 2 キャパシタ C 2 に充電される電圧値は変化しない。

【0104】

以後、第 n 走査線 S n に走査信号が供給されて第 1 トランジスター M 1 及び第 2 トランジスター M 2 がターンオンされる。そして、第 n 走査線 S n に走査信号が供給される期間中の第 1 期間の間に第 1 2 トランジスター M 1 2 及び第 1 3 トランジスター M 1 3 がターンオンされる。第 1 2 トランジスター M 1 2 及び第 1 3 トランジスター M 1 3 がターンオンされれば、第 1 電源 E L V D D 、第 4 トランジスター M 4 、第 2 トランジスター M 2 、データ線 D j 、及び第 1 3 トランジスター M 1 3 を経由して電流源 I m a x に対応する電流がシンクされる。

10

20

30

40

50

## 【0105】

この時、第4トランジスターM4には、電流源Imaxの電流が流れるので、数式(2)のように表現することができる。

## 【0106】

## 【数2】

$$Imax = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2 \quad \dots \quad (2)$$

10

## 【0107】

数式(2)で、uは移動度を現わし、 $C_{ox}$ は酸化層の容量、Wはチャンネルの幅、Lはチャンネルの長さを現わす。

## 【0108】

数式(2)のような電流が第4トランジスターM4に流れるときに第2ノードN2に印加される電圧は、数式(3)のように表現することができる。

## 【0109】

## 【数3】

$$V_{N2} = ELVDD - \sqrt{\frac{2Imax}{\mu_p C_{ox}} \frac{L}{W} - |V_{thM4}|} \quad \dots \quad (3)$$

20

## 【0110】

そして、第2キャパシタC2のカップリングによって、第1ノードN1に印加される電圧は、数式(4)のように表現することができる。

## 【0111】

## 【数4】

$$V_{N1} = Vref - \sqrt{\frac{2Imax}{\mu_p C_{ox}} \frac{L}{W}} = V_{N3} \quad \dots \quad (4)$$

30

## 【0112】

ここで、第1ノードN1に印加される電圧 $V_{N1}$ は、理想的に第3ノードN3に印加される電圧 $V_{N3}$ 及び第4ノードN4に印加される電圧 $V_{N4}$ と同じに設定される。すなわち、電流源Imaxによって、電流がシンクされるときに第4ノードN4には、数式(4)のような電圧が印加される。

## 【0113】

一方、数式(4)に図示されたように、第3ノードN3及び第4ノードN4に印加される電圧は、現在、電流がシンクされる画素140に含まれたトランジスターの電子移動度などの影響を受けるようになる。したがって、電流源Imaxによって、電流がシンクされるときに第3ノードN3に印加される電圧値は、それぞれの画素140ごとに相異なるようになる(電子移動度が相異なる場合)。

## 【0114】

一方、水平期間の第1期間中、DAC250jでは、第1データData1に対応してf(fは自然数)個の階調電圧の中のh(hはf以下の自然数)番目階調電圧を選択する。そして、DAC250jは、第41トランジスターM41がターンオンされる期間の間

40

50

に選択された階調電圧をデータ信号 D S として第 4 1 トランジスター M 4 1 と第 1 バッファー 2 7 0 j との間のラインに供給する。ここで、第 4 1 トランジスター M 4 1 と第 1 バッファー 2 7 0 j との間のラインの間の電圧 V<sub>L</sub> は、数式(5)のように表現することができる。

【0 1 1 5】

【数 5】

$$V_L = V_{ref} - \frac{h}{f} (V_{ref} - VSS) \quad \dots (5)$$

10

【0 1 1 6】

一方、デコーダ 2 4 0 j は、水平期間の第 1 期間の間に初期化信号を供給して第 3 1 トランジスター M 3 1 、第 3 2 トランジスター M 3 2 、第 3 3 トランジスター M 3 3 、第 3 4 トランジスター M 3 4 、及び第 3 5 トランジスター M 3 5 をターンオンさせる。すると、第 1 期間の間に第 4 キャパシタの一側端子が第 3 電源 V S S の電圧値に設定される。

【0 1 1 7】

ここで、第 3 電源 V S S の電圧値は、基準電源 V<sub>r e f</sub> の電圧値より低い電圧、例えば、画素部 1 3 0 に含まれた画素 1 4 0 で生成されうる補償電圧の平均電圧に設定することができる。

【0 1 1 8】

第 4 キャパシタの一側端子が第 3 電源 V S S の電圧値に設定された後、水平期間の第 2 期間の間にデコーダ 2 4 0 j から供給される第 2 データ D a t a 2 に対応して第 2 1 トランジスター M 2 1 、第 2 2 トランジスター M 2 2 、第 2 3 トランジスター M 2 3 、第 2 4 トランジスター M 2 4 、及び第 2 5 トランジスター M 2 5 がターンオンまたはターンオフされる。

【0 1 1 9】

実際に、デコーダ 2 4 0 j は、数式(5)で、h / f の値とほぼ同じ値を持つように第 2 1 トランジスター M 2 1 、第 2 2 トランジスター M 2 2 、第 2 3 トランジスター M 2 3 、第 2 4 トランジスター M 2 4 、及び第 2 5 トランジスター M 2 5 がターンオンまたはターンオフを制御する。

30

【0 1 2 0】

例えば、デコーダ 2 4 0 j から生成される第 2 データ D a t a 2 のビットが“0 0 0 1 1”に設定されれば、第 2 4 トランジスター M 2 4 及び第 2 5 トランジスター M 2 5 がターンオンされて、容量が C , 2 C の二つの第 4 キャパシタの一側端子に補償電圧を印加する。この場合、容量が C , 2 C の二つの第 4 キャパシタの一側端子に補償電圧が印加されるので、数式(6)のように表現することができる。

【0 1 2 1】

【数 6】

$$\frac{C+2C}{C+2C+4C+8C+16C} \equiv \frac{h}{f} \quad \dots (6)$$

40

【0 1 2 2】

ここで、第 2 データ D a t a 2 は、第 1 データ D a t a 1 によって生成されるので、数式(6)の値はおおよそ h / f に表現することができる。

【0 1 2 3】

一方、第 4 キャパシタの少なくとも一つに補償電圧が印加されれば、第 4 1 トランジスター M 4 1 と第 1 バッファー 2 7 0 との間のラインの間の電圧 V<sub>L</sub> は数式(7)のように表現することができる。

50

【 0 1 2 4 】

【 数 7 】

$$\begin{aligned}

V_L &= V_{ref} - \frac{h}{f} (V_{ref} - V_{SS}) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - V_{SS}) \\

&= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3}) \\

&= V_{ref} - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W} \quad \dots \quad (7)

\end{aligned}$$

10

20

30

【 0 1 2 5 】

数式(7)のような電圧は、第1バッファ-270jを経由して第11トランジスターM11に供給される。ここで、第2期間の間に第11トランジスターM11がターンオンされるため、第1バッファ-270jに供給された電圧は、第11トランジスターM11、データ線Dj、及び第1トランジスターM1を経由して第1ノードN1に供給される。

【 0 1 2 6 】

すなわち、第1ノードN1には数式(7)のような電圧が供給される。そして、第2キャパシタC2のカップリングによって、第2ノードN2に印加される電圧は、数式(8)のように表現することができる。

【 0 1 2 7 】

【 数 8 】

$$V_{N2} = ELVDD - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W} - |V_{thM4}| \quad \dots \quad (8)$$

40

【 0 1 2 8 】

この時、第4トランジスターM4を経由して流れる電流は、数式(9)のようにあらわすことができる。

【 0 1 2 9 】

【 数 9 】

$$\begin{aligned}

I_{N4} &= \frac{1}{2} \mu_p C_{OX} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2 \\

&= \frac{1}{2} \mu_p C_{OX} \frac{W}{L} \left( ELVDD - \left( ELVDD - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W} - |V_{thM4}| \right) - |V_{thM4}| \right)^2 \\

&= \left( \frac{h}{f} \right)^2 I_{max} \quad \dots \quad (9)

\end{aligned}$$

【 0 1 3 0 】

数式(9)を参照すれば、本発明の実施形態で第4トランジスターM4に流れる電流は、データ信号DSによって決まる。すなわち、本発明の実施形態では、第4トランジスター

50

一方、M4の閾値電圧、電子移動度などとは無関係にデータ信号DSによって決まった電流が第4トランジスターM4に流れることができ、これによって均一な画像を表示することができる。

### 【0131】

一方、本発明の実施形態で、スイッチング部290jの構成は、多様に設定することができる。例えば、スイッチング部290jは、図10のように第11トランジスターM11及び第14トランジスターM14をトランスマッシュゲート(Transmission Gate)形態で接続することができる。PMOSタイプに形成された第14トランジスターM14は、第2制御信号CS2の供給を受け、NMOSタイプに形成された第11トランジスターM11は、第1制御信号CS1の供給を受ける。ここで、第1制御信号CS1及び第2制御信号CS2は、互いに反対の極性を持つとすれば、第11トランジスターM11及び第14トランジスターM14は同じ時間にターンオン及びターンオフされる。

### 【0132】

一方、第11トランジスターM11及び第14トランジスターM14がトランスマッシュゲート形態で接続されれば、電圧-電流特性曲線がおよそ直線形態に設定されることによってスイッチングエラーを最小化することができる。

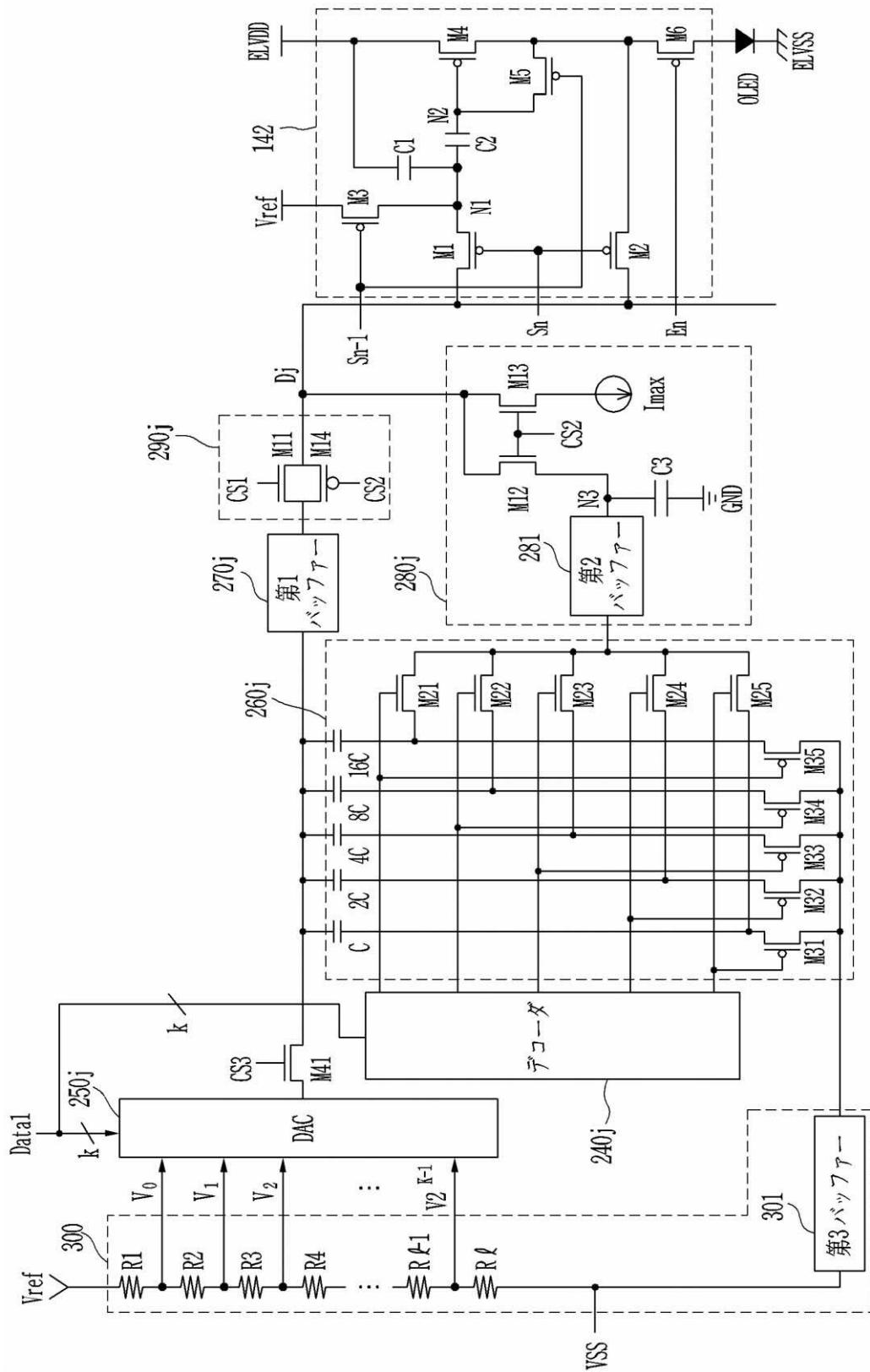

### 【0133】

図11は、図6に図示されたガンマ電圧部、DAC、デコーダ、電圧制御器、スイッチング部、電流シンク部、及び画素連結関係の他の例をあらわす図面である。図11では、説明の便宜性のためにj番目チャンネルを図示し、データ線Djが図5に図示された画素140と接続されると仮定する。

### 【0134】

図9及び図11を参照して、動作過程を説明すれば、まず、第n-1走査線Sn-1で走査信号が供給されるときに第1ノードN1及び第2ノードN2には数式(1)に記載された電圧が印加される。

### 【0135】

そして、第n走査線Snで走査信号が供給され、第12トランジスターM12及び第13トランジスターM13がターンオンされる第1期間の間に第4トランジスターM4に流れる電流は、数式(2)のように表現され、第2ノードN2に印加される電圧は数式(3)のように表現される。

### 【0136】

そして、第2キャパシタC2のカップリングによって、第1ノードN1に印加される電圧は数式(10)のように表現することができる。

### 【0137】

### 【数10】

$$V_{N1} = V_{ref} - \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2Imax}{\mu_p C_{ox}}} \frac{L}{W} = V_{N3} \quad \dots \quad (10)$$

10

20

30

40

### 【0138】

一方、水平期間の第1期間にDAC250jでは、第1データData1に対応してf(fは自然数)個の階調電圧の中のh(hはf以下の自然数)番目階調電圧を選択する。そして、DAC250jは、第41トランジスターM41がターンオンされる期間の間に選択された階調電圧をデータ信号DSとして、第41トランジスターM41と第1バッファ-270との間のラインに数式(5)のような電圧を印加する。

### 【0139】

一方、デコーダ240jは水平期間の第1期間の間に初期化信号を第31トランジスタ

50

—M31、第32トランジスターM32、第33トランジスターM33、第34トランジスターM34、及び第35トランジスターM35をターンオンさせる。すると、第1期間の間第4キャパシタの一側端子が第3電源VSSの電圧値に設定される。

## 【0140】

そして、デコーダ240jは、水平期間の第2期間の間にデコーダ240jから供給される第2データData2に対応して、第21トランジスターM21、第22トランジスターM22、第23トランジスターM23、第24トランジスターM24、及び第25トランジスターM25がターンオンまたはターンオフされる。実際に、デコーダ240jは数式(5)で $h/f$ の値とほぼ同じ値を持つように第21トランジスターM21、第22トランジスターM22、第23トランジスターM23、第24トランジスターM24、及び第25トランジスターM25がターンオンまたはターンオフを制御する。10

## 【0141】

この時、第41トランジスターM41と第1バッファー270との間のラインの間の電圧 $V_L$ は数式(11)のように表現することができる。

## 【0142】

## 【数11】

$$\begin{aligned} V_L &= V_{ref} - \frac{h}{f} (V_{ref} - V_{SS}) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - V_{SS}) \\ &= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3}) \\ &= V_{ref} - \frac{h}{f} \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W} \dots (11) \end{aligned}$$

20

## 【0143】

数式(11)のような電圧は、第1バッファー270jを経由して第11トランジスターM11に供給される。ここで、第2期間の間に第11トランジスターM11がターンオンされるため、第1バッファー270jに供給された電圧は、第11トランジスターM11、データ線Dj、及び第1トランジスターM1を経由して第1ノードN1に供給される。30

## 【0144】

すなわち、第1ノードN1には数式(11)のような電圧が供給される。

## 【0145】

そして、第2キャパシタC2のカップリングによって、第2ノードN2に印加される電圧は数式(8)のように表現することができる。したがって、第4トランジスターM4を経由して流れる電流は数式(9)のようにあらわすことができる。すなわち、本発明の実施形態で第4トランジスターM4を経由して発光素子OLEDに供給される電流は、第4トランジスターM4の閾値電圧、電子移動度などとは無関係にデータ信号DSによって決まるので、均一な画像を表示することができる。40

## 【0146】

一方、図5に図示されたような画素140は、第1ノードN1の電圧が大きく変わっても第2ノードN2の電圧が鈍感に変化する(すなわち、 $C1 + C2 / C2$ )。したがって、図5に図示された画素140が適用されれば、図3に図示された画素140が適用される場合よりガンマ電圧部300の電圧範囲を広く設定することができる。このように、ガンマ電圧部300の電圧範囲が広く設定されれば第11トランジスターM11及び第1トランジスターM1などのスイッチングエラーによる影響を減らすことができるという長所50

がある。

【0147】

本発明は、添付された図面に図示された実施形態を参照して説明されたが、これは例示的なものに過ぎず、当該技術分野における通常の知識を有する者であれば、多様な変形及び均等な他の実施形態が可能であるということを理解することができる。

【図面の簡単な説明】

【0148】

【図1】図1は、従来の発光表示装置を現わす図面である。

【図2】図2は、本発明の実施形態による発光表示装置を現わす図面である。

10

【図3】図3は、図2に図示された画素の一例を現わす回路図である。

【図4】図4は、図3に図示された画素の駆動方法を現わす波形図である。

【図5】図5は、図2に図示された画素の他の例を現わす回路図である。

【図6】図6は、図2に図示されたデータ駆動回路の第1実施形態を現わすブロック図である。

【図7】図7は、図2に図示されたデータ駆動回路の第2実施形態を現わすブロック図である。

【図8】図8は、図6に図示されたガンマ電圧部、デジタル・アナログ変換器、デコーダ、電圧制御器、スイッチング部、電流シンク部、及び画素の連結関係を現わす図面である。

20

【図9】図9は、図8に図示された制御信号の駆動波形を現わす波形図である。

【図10】図10は、図8に図示されたスイッチング部の他の例を現わす図面である。

【図11】図11は、図6に図示されたガンマ電圧部、デジタルアナログ変換器、デコーダ、電圧制御器、スイッチング部、電流シンク部、及び画素の連結関係の他の例を現わす図面である。

【符号の説明】

【0149】

- 110 走査駆動部、

- 120 データ駆動部、

- 130 画素部、

- 140 画素、

- 142 画素回路、

- 150 タイミング制御部、

- 200 データ駆動回路、

- 210 シフトレジスター部、

- 220 サンプリングラッチ部、

- 230 ホルディングラッチ部、

- 240 デコーダ部、

- 250 デジタル・アナログ変換部、

- 260 電圧制御部、

- 270 バッファー部、

- 280 電流供給部、

- 290 選択部、

- 300 ガンマ電圧部、

- 310 レベルシフター。

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 11】

## フロントページの続き

| (51)Int.Cl. | F I          | テーマコード(参考) |

|-------------|--------------|------------|

|             | G 09 G 3/20  | 6 2 3 F    |

|             | G 09 G 3/20  | 6 4 1 Q    |

|             | G 09 G 3/20  | 6 4 1 D    |

|             | G 09 G 3/20  | 6 2 4 B    |

|             | G 09 G 3/20  | 6 2 1 A    |

|             | H 05 B 33/14 | A          |

(72)発明者 鄭 寶 容

大韓民国ソウル特別市松坡区可樂2洞173-19

(72)発明者 柳 道 享

大韓民国京畿道水原市八達区靈通洞1028-2, 303

(72)発明者 金 た 権

大韓民国京畿道儀旺市旺谷洞 鮮京元暎アパート102-1506

(72)発明者 権 五 敬

大韓民国ソウル特別市松坡区7新川洞 薔薇アパート14-1102

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH04 HH05

5C080 AA06 BB05 DD05 EE28 EE29 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 数据驱动电路，使用其的有机发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2007041532A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2007-02-15 |

| 申请号            | JP2006130865                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2006-05-09 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社<br>学校法人汉阳大学产学合作局                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 鄭寶容<br>柳道享<br>金た權<br>權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 鄭寶容<br>柳道享<br>金▲た▼權<br>權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G3/3233 G09G3/2011 G09G3/3283 G09G3/3291 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0251 G09G2310/027 G09G2310/0289 G09G2320/0276 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.612.F G09G3/20.623.F G09G3/20.641.Q G09G3/20.641.D G09G3/20.624.B G09G3/20.621.A H05B33/14.A G09G3/20.641.P G09G3/20.642.P G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/BA05 5C380/BA20 5C380/BA28 5C380/BA32 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CA16 5C380/CA17 5C380/CA22 5C380/CA26 5C380/CA33 5C380/CA49 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB17 5C380/CC03 5C380/CC04 5C380/CC05 5C380/CC06 5C380/CC08 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC55 5C380/CC61 5C380/CD026 5C380/CE05 5C380/CE07 5C380/CF07 5C380/CF22 5C380/CF24 5C380/CF41 5C380/CF43 5C380/CF48 5C380/CF64 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 宇谷胜幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 优先权            | 1020050070438 2005-08-01 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP4611930B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

**摘要(译)**

解决的问题：提供一种用于显示均匀亮度图像的数据驱动电路。伽马电压单元用于产生多个灰度电压，并且从外部提供的第k个(k是自然数)位的第一数据Data1用于选择一个灰度电压。至少一个数模转换器，用于通过数据信号选择灰度电压；以及至少一个解码器，用于使用k位第一数据生成p(p是自然数)位第二数据。至少一个电流吸收单元在水平时段的第一时段期间从像素接收预定电流，对应于预定电流而生成的补偿电压以及第二数据。至少一个电压控制器，用于控制数据信号的电压值，并且在水平时段期间除了第一时段之外的第二时段期间将具有受控电压值的数据信号提供给像素。至少要做一件包括切换单元。[选择图]图8