(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-115144

(P2005-115144A)

(43) 公開日 平成17年4月28日(2005.4.28)

(51) Int.Cl.<sup>7</sup>

G09G 3/30

G09G 3/20

H05B 33/14

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/30

K

5C080

G09G 3/20

611H

G09G 3/20

622C

G09G 3/20

622D

審査請求 未請求 請求項の数 9 O L (全 18 頁) 最終頁に続く

(21) 出願番号

特願2003-350951 (P2003-350951)

(22) 出願日

平成15年10月9日 (2003.10.9)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤岡 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 池上 富雄

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA04

5C080 AA06 BB05 DD05 EE28 FF11

GG12 JJ02 JJ03 JJ04 JJ05

JJ06 KK43 KK47

(54) 【発明の名称】画素回路の駆動方法、駆動回路、電気光学装置および電子機器

## (57) 【要約】

【課題】 低階調表示時におけるOLED素子の輝度ムラを防止する。

【解決手段】 各画素回路をテスト期間と表示期間とに分けて駆動し、テスト期間では、走査線102を表示期間よりも遅い水平走査速度で順次選択し、各データ線112に低階調に相当する電流をそれぞれ流し、走査線の選択が終了する手前のタイミングにて、各データ線112の測定電圧から、選択走査線と測定データ線との交差に位置する駆動トランジスタの閾値電圧を求めて、不足電流分に相当する補正データをLUT28に書き込む。表示期間では、走査線102を順次選択するとともに、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画像データを、当該画素回路について求めた補正データで補正し、補正した画像データに応じた電流を、当該画素回路にデータ線112を介して流す。

**【特許請求の範囲】****【請求項 1】**

複数の走査線と複数のデータ線との交差において設けられた画素回路であって、各々が

、

走査線が選択されたときにデータ線に流れる電流に応じた電圧を保持する電圧保持素子と、

当該電圧保持素子の一端にゲートが接続された駆動トランジスタと、

前記駆動トランジスタによって制御された電流によって発光する電気光学素子と

を有する画素回路の駆動方法において、

各画素回路をテスト期間と表示期間とに分けて駆動し、

前記テスト期間では、

前記走査線を順次選択し、

走査線を選択したときに、各データ線に所定の電流をそれぞれ流し、

走査線の選択が終了する手前のタイミングにて、各データ線の電圧をそれぞれ測定し、

測定した電圧から、選択した走査線と電圧を測定したデータ線との交差に位置する画素

回路における駆動トランジスタの特性を求める、

前記表示期間では、

前記走査線を水平走査期間毎に順次選択するとともに、選択走査線に位置する画素回路

の電気光学素子の輝度を指定する画像データを、当該画素回路について求めた駆動トラン

ジスタの特性に基づいて補正し、

補正した画像データに応じた電流を、当該画素回路にデータ線を介して流す

画素回路の駆動方法。

**【請求項 2】**

前記テスト期間では、前記駆動トランジスタの特性として、その閾値電圧を求める、当該

閾値電圧を参照して補正データを算出するとともに、当該補正データを、選択した走査線

と電圧を測定したデータ線との交差に位置する画素回路に対応付けて記憶し、

前記表示期間では、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画

像データに、当該画素回路に対応付けて記憶した補正データを加算して、加算した画像デ

ータに応じた電流を、当該画素回路にデータ線を介して流す

請求項 1 に記載の画素回路の駆動方法。

**【請求項 3】**

前記テスト期間における走査線の選択期間を、前記表示期間における水平走査期間より

も長く設定し、

前記所定の電流を比較的小さくする

請求項 1 に記載の画素回路の駆動方法。

**【請求項 4】**

前記テスト期間における走査線の選択期間を、前記表示期間における水平走査期間と略

同一に設定し、

前記所定の電流を比較的大きくする

請求項 1 に記載の画素回路の駆動方法。

**【請求項 5】**

前記テスト期間について、

前記所定の電流を異ならせて、各画素回路に対し複数回にわたって実行する

請求項 1 に記載の画素回路の駆動方法。

**【請求項 6】**

前記テスト期間および前記表示期間において走査線を選択する前に、各データ線の電圧

を所定の電圧にプリチャージする

請求項 1 に記載の画素回路の駆動方法。

**【請求項 7】**

複数の走査線と複数のデータ線との交差において設けられた画素回路であって、各々が

10

20

30

40

50

走査線が選択されたときにデータ線に流れる電流に応じた電圧を保持する電圧保持素子と、

当該電圧保持素子の一端にゲートが接続された駆動トランジスタと、

前記駆動トランジスタによって制御された電流によって発光する電気光学素子とを有する画素回路を、テスト期間と表示期間とに分けて駆動する駆動回路であって、

前記テスト期間および前記表示期間に前記走査線を順次選択する走査線駆動回路と、

前記テスト期間では、走査線の選択が終了する手前のタイミングにて、各データ線の電圧をそれぞれ測定する電圧測定回路と、

測定された電圧から、選択された走査線と電圧が測定されたデータ線との交差に位置する画素回路の駆動トランジスタにおける閾値電圧を求め、当該閾値電圧を参照して補正データを算出する補正データ算出回路と、

算出された補正データを、選択した走査線と電圧が測定されたデータ線との交差に位置する画素回路に対応付けて記憶するテーブルと、

前記表示期間では、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画像データに、当該画素回路に対応付けて前記テーブルに記憶された補正データで補正する補正回路と、

前記テスト期間では、各データ線に所定の電流をそれぞれ流す一方、前記表示期間では、走査線が選択されたときに、補正された画像データに応じた電流を、当該画素回路にデータ線を介して流すデータ線駆動回路と

を備える画素回路の駆動回路。

#### 【請求項 8】

複数の走査線と複数のデータ線との交差において設けられた画素回路であって、各々が走査線が選択されたときにデータ線に流れる電流に応じた電圧を保持する電圧保持素子と、当該電圧保持素子の一端にゲートが接続された駆動トランジスタと、前記駆動トランジスタによって制御された電流によって発光する電気光学素子とを有する画素回路と、

テスト期間と表示期間とに分けて駆動する駆動回路とを有し、

前記駆動回路は、

前記テスト期間および前記表示期間に前記走査線を順次選択する走査線駆動回路と、

前記テスト期間では、走査線の選択が終了する手前のタイミングにて、各データ線の電圧をそれぞれ測定する電圧測定回路と、

測定された電圧から、選択された走査線と電圧が測定されたデータ線との交差に位置する画素回路における駆動トランジスタの閾値電圧を求め、当該閾値電圧を参照して補正データを算出する補正データ算出回路と、

算出された補正データを、選択した走査線と電圧が測定されたデータ線との交差に位置する画素回路に対応付けて記憶するテーブルと、

前記表示期間では、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画像データに、当該画素回路に対応付けて前記テーブルに記憶された補正データで補正する補正回路と、

前記テスト期間では、各データ線に所定の電流をそれぞれ流す一方、前記表示期間では、走査線が選択されたときに、補正された画像データに応じた電流を、当該画素回路にデータ線を介して流すデータ線駆動回路と

を備える電気光学装置。

#### 【請求項 9】

請求項 8 に記載の電気光学装置を表示装置として備えることを特徴とする電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、例えば有機発光ダイオード素子のような電気光学素子を有する画素回路の駆動方法、駆動回路、電気光学装置および電子機器に関する。

10

20

30

40

50

**【背景技術】****【0002】**

近年、液晶素子に代わる次世代の発光デバイスとして、有機発光ダイオード(Organic Light Emitting Diode、以下適宜OLEDと略称する)素子が注目されている。OLED素子は、有機エレクトロルミネッセンス素子や発光ポリマーとも呼ばれているものである。このOLED素子は、自発光型であるために視野角依存性が少なく、また、バックライトや反射光が不要であるために低消費電力化や薄型化に向いているなど、表示装置に用いた場合に優れた特性を有している。

ここで、OLED素子は、液晶素子のように電圧保持性を有さず、電流が途絶えると、発光状態が維持できなくなる電流型の被駆動素子である。このため、OLED素子をアクティブ・マトリクス方式で駆動する場合、電圧保持素子を設けて、OLED素子に電流を供給する駆動トランジスタのゲート電圧を保持するとともに、選択期間に、画素の階調に応じた電圧を駆動トランジスタのゲートに書き込む構成が一般的となっている。この構成によれば、非選択期間においても駆動トランジスタのゲート電圧が電圧保持素子によって保持されるので、当該ゲート電圧に応じた電流を当該OLED素子に継続して流すことが可能となる。

**【0003】**

ところで、この構成では、駆動トランジスタの閾値電圧がばらつくことによって、画素回路毎に、OLED素子の明るさが相違して表示品位が低下する問題が指摘された。このため、近年では、選択期間において当該駆動トランジスタをダイオード接続させるとともに、当該駆動トランジスタおよびデータ線に流れる電流を、画素の階調(輝度)を指示する画像データに応じた値となるように制御し、これによって、当該駆動トランジスタのゲートに、OLED素子に流すべき電流に応じた電圧を書き込むようにプログラミングして、駆動トランジスタの閾値電圧特性のばらつきを補償する技術が提案されている(例えば、特許文献1)。

【特許文献1】特開2003-22049号公報(図17参照)

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

しかしながら、この技術では、データ線の寄生容量が大きい場合にデータ線に流す電流が小さいとき、当該寄生容量の充放電に時間を要してしまい、選択期間内に、駆動トランジスタのゲートに目標とする電圧を書き込むことができない、といった問題が新たに指摘された。

データ線に流す電流が小さいときは、OLED素子を暗くして発光させるときに相当し、また、ゲートに書き込むべき電圧と実際に書き込まれた電圧との差である書き込み誤差は、後述するように駆動トランジスタの閾値電圧等の特性に依存する。そして、低階調表示時において選択期間内に書き込みが追いつかない点、および、駆動トランジスタの特性がばらつくことによって、駆動トランジスタのゲート電圧もばらつく結果、輝度ムラが目立つことになる。

本発明は、上述した事情に鑑みてなされたもので、その目的とするところは、データ線の寄生容量が大きい場合であって、データ線に流す電流が小さいときであっても、OLED素子のような電気光学素子の輝度ムラの発生を防止することが可能な画素回路の駆動方法、駆動回路、電気光学装置および電子機器を提供することにある。

**【課題を解決するための手段】****【0005】**

上記目的を達成するために本発明に係る画素回路の駆動方法は、複数の走査線と複数のデータ線との交差において設けられた画素回路であって、各々が、走査線が選択されたときにデータ線に流れる電流に応じた電圧を保持する電圧保持素子と、当該電圧保持素子の一端にゲートが接続された駆動トランジスタと、前記駆動トランジスタによって制御された電流によって発光する電気光学素子とを有する画素回路の駆動方法において、各画素回

10

20

30

40

50

路をテスト期間と表示期間とに分けて駆動し、前記テスト期間では、前記走査線を順次選択し、走査線を選択したときに、各データ線に所定の電流をそれぞれ流し、走査線の選択が終了する手前のタイミングにて、各データ線の電圧をそれぞれ測定し、測定した電圧から、選択した走査線と電圧を測定したデータ線との交差に位置する画素回路における駆動トランジスタの特性を求め、前記表示期間では、前記走査線を水平走査期間毎に順次選択するとともに、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画像データを、当該画素回路について求めた駆動トランジスタの特性に基づいて補正し、補正した画像データに応じた電流を、当該画素回路にデータ線を介して流す。

この駆動方法によれば、テスト期間において、駆動トランジスタの特性が求められると、当該駆動トランジスタのソース・ドレイン間に流すべき電流に対して、データ線に流すべき電流の不足分が判明する。したがって、表示期間において、画像データを駆動トランジスタの特性に基づいて補正することによって、当該不足分が加算された電流がデータ線に流れるので、駆動トランジスタのゲート電圧の書き込みが間に合わなくなることが防止される。

上記駆動方法において、前記テスト期間では、前記駆動トランジスタの特性として、その閾値電圧を求め、当該閾値電圧を参照して補正データを算出するとともに、当該補正データを、選択した走査線と電圧を測定したデータ線との交差に位置する画素回路に対応付けて記憶し、前記表示期間では、選択走査線に位置する画素回路の電気光学素子の輝度を指定する画像データに、当該画素回路に対応付けて記憶した補正データを加算して、加算した画像データに応じた電流を、当該画素回路にデータ線を介して流す方法が好ましい。

#### 【0006】

また、上記駆動方法において、前記テスト期間における走査線の選択期間を、前記表示期間における水平走査期間よりも長く設定し、前記所定の電流を比較的小さくすることが好ましい。これによれば、テスト期間では、表示期間よりも遅い速度で水平走査されるので、走査線の選択期間が終了する手前のタイミングでは、目標とする電圧が書き込まれる。このため、当該タイミングにおいて、データ線の電圧を測定すると、駆動トランジスタ特性が正確に求められる。

一方、上記駆動方法において、前記テスト期間における走査線の選択期間を、前記表示期間における水平走査期間と略同一に設定し、前記所定の電流を比較的大きくすることも好ましい。これによれば、テスト期間と表示期間とは同じ速度で水平走査されるので、テスト期間に要する時間が短縮される。

#### 【0007】

上記駆動方法において、前記テスト期間につき前記所定の電流を異ならせて、各画素回路に対し複数回にわたって実行するとしても良い。こうすると、駆動トランジスタの特性を精度良く求めることが可能となる。

また、上記駆動方法において、前記テスト期間および前記表示期間において走査線を選択する前に、各データ線の電圧を所定の電圧にプリチャージしても良い。こうすると、データ線に電流を流す前の状態が、それ以前の書き込み状態に依存せず、かつ、すべてのデータ線にわたって均一となる。

本発明は、電気光学装置の駆動方法に限られず、駆動回路としても、また、電気光学装置としても実現可能である。さらに、本発明における電子機器は、上記電気光学装置を表示装置として備えるので、輝度ムラの発生が抑えられた高品位の表示が可能となる。なお、このような電子機器としては、後述するものが挙げられる。

#### 【発明を実施するための最良の形態】

#### 【0008】

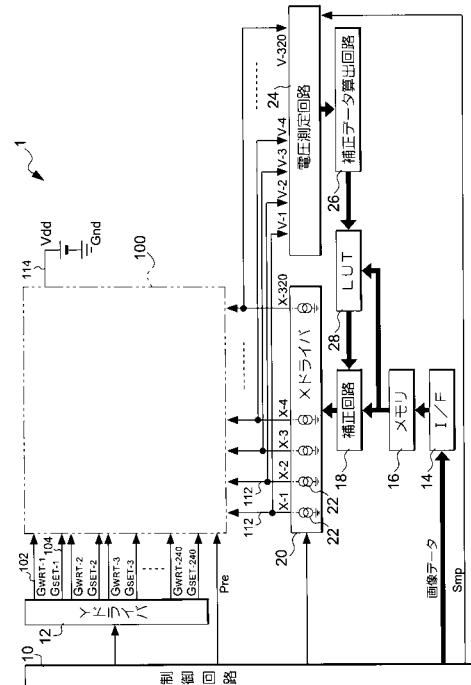

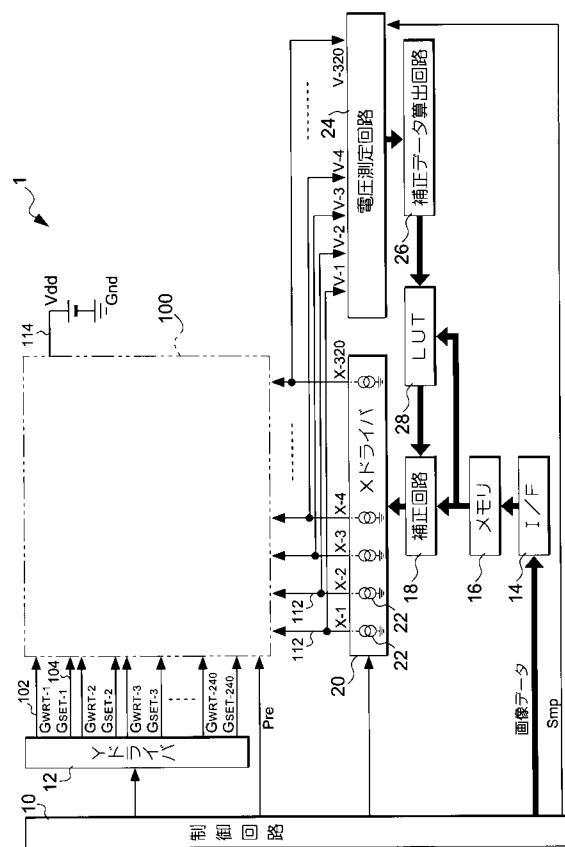

以下、本発明の実施形態について図面を参照して説明する。図1は、本発明の第1実施形態に係る電気光学装置の構成を示すブロック図であり、図2は、この電気光学装置における表示パネルの構成を示すブロック図である。

これらの図に示されるように、電気光学装置1においては、表示パネル100がYドライバ12およびXドライバ20によって駆動される。表示パネル100では、OLED素

10

20

30

40

50

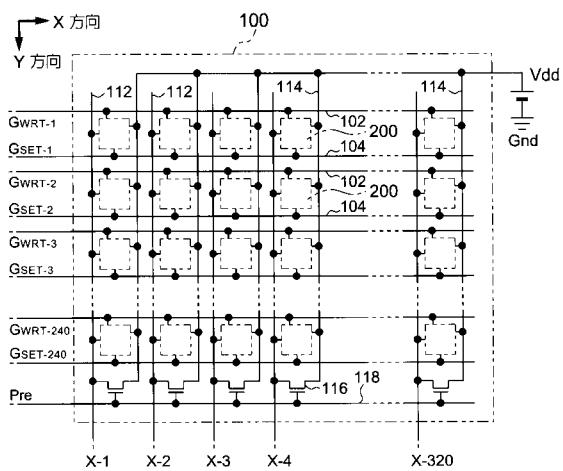

子を含む画素回路 200 が、図 2 に示されるように 240 行 × 320 列のマトリクス型に配列している。本実施形態では、この OLED 素子への電流量を画素回路 200 (画素) 每に制御することによって、所定の画像を階調表示しようとするものである。なお、本実施形態では、画素回路 200 の配列を 240 行 × 320 列のマトリクス型とするが、本発明をこの配列に限定する趣旨ではない。

### 【0009】

画素回路 200 の配列において、走査線 102 および点灯制御線 104 は、マトリクス配列の行数に相当するように 240 本ずつ設けられ、それぞれが X 方向に延設されている。そして、走査線 102 および点灯制御線 104 の 1 本ずつが 1 組となって、1 行分の画素回路 200 に兼用されている。

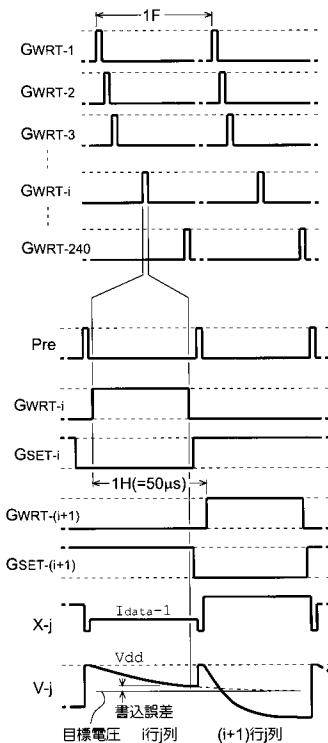

1 行目、2 行目、3 行目、…、240 行目の走査線 102 には、それぞれ走査信号  $G_{WRT-1}$ 、 $G_{WRT-2}$ 、 $G_{WRT-3}$ 、…、 $G_{WRT-240}$  が供給される。ここで、説明の便宜上、 $i$  行目 ( $i$  は、1  $\sim$  240 を満たす整数) の走査線 102 に供給される走査信号を  $G_{WRT-i}$  と表記する。また、 $i$  行目の点灯制御線 104 には制御信号  $G_{SET-i}$  が供給される。これらの走査線 102 および点灯制御線 104 は、それぞれ Y ドライバ (走査線駆動回路) 12 によって駆動される。

### 【0010】

一方、データ線 112 は、マトリクス配列の列数に相当するように 320 本、設けられ、それぞれが Y 方向に延設されるとともに、1 本のデータ線 112 が 1 列分の画素回路 200 に兼用されている。X ドライバ (データ線駆動回路) 20 は、1 列目、2 列目、3 列目、…、320 列目のデータ線 112 に、それぞれデータ電流  $X-1$ 、 $X-2$ 、 $X-3$ 、…、 $X-320$  を流して、これらのデータ線 112 を駆動する。ここで、説明の便宜上、 $j$  列目 ( $j$  は、1  $\sim$  320 を満たす整数) のデータ線 112 に流れるデータ電流を  $X-j$  と表記する。

### 【0011】

図 2 に示されるように、各データ線 112 には、それぞれに対応する N チャネル型のトランジスタ 116 が設けられている。各トランジスタ 116 のソースは、電源の高位側電圧  $V_{dd}$  が印加された電源線 114 に共通接続される一方、トランジスタ 116 のドレインは、対応するデータ線 112 に接続されている。そして、各トランジスタ 116 のゲートは、制御信号  $Pre$  が供給される制御線 118 に共通接続されている。このため、制御信号  $Pre$  が H レベルになると、トランジスタ 116 がオンするので、各データ線 112 が、電圧  $V_{dd}$  にプリチャージされる構成となっている。

電源線 114 は、すべての画素回路 200 に接続される。なお、図 2 では、電源線 114 は、マトリクス配列において Y 方向に延設されているが、X 方向に延設されても良い。また、図 1 および図 2 では省略されているが、すべての画素回路 200 は、電源の低位側電圧  $Gnd$  に共通接地されている。

### 【0012】

一方、制御回路 10 は、Y ドライバ 12 や X ドライバ 20 などの各部の動作を制御するとともに、各画素の階調を OLED 素子に流すべき電流の形式で指定する画像データを、240 行 × 320 列の画素毎に出力する。また、制御回路 10 は、上述した制御信号  $Pre$  や、後述する信号  $Smp$  も出力する。

I/F (インターフェイス) 14 は、制御回路 10 から出力される画像データを入力するものである。メモリ 16 は、240 行 × 320 列の画素に対応した記憶領域を有する。そして、メモリ 16 には、I/F 14 により入力された画像データが、当該画像データに対応する画素の記憶領域に書き込まれる一方、ある走査線 102 が選択される前に、その走査線に位置する 1 行分の画像データが一斉に読み出される構成となっている。

### 【0013】

一方、LUT (ルックアップテーブル) 28 は、240 行 × 320 列の各画素について、階調 (輝度) 每に補正データを記憶するものである。そして、LUT 28 からは、メモリ 16 から読み出される同一行同一列の画素に対応した画像データであって、当該画像デ

ータで指定された階調に対応する補正データが出力される。なお、画像データは、それぞれ1行分読み出されるので、LUT28からも1行分の補正データが出力される。また、LUT28の内容は、補正データ算出回路26によって書き換えられる。

補正回路18は、メモリ16から読み出された画像データを、当該画像データと同一行同一列の画素の補正データによって補正する。

【0014】

Xドライバ20は、データ線112毎に定電流回路22を有する。ここで、各定電流回路22について、例えばj列目のデータ線112に対応するもので代表して説明すると、表示期間であれば、走査信号G<sub>WRT-i</sub>がHレベルになれば、補正回路18によって補正された画像データであって、i行j列の画素の画像データで指定された電流を生成し、データ電流X-jとしてj列目のデータ線112に流す。一方、テスト期間では、すべての定電流回路22は、画像データとは無関係に、後述するように低階調に相当する電流を、データ電流X-jとしてデータ線112に流す。なお、データ電流X-jが流れる方向は、本実施形態では、データ線112から定電流回路22に向かう方向である。

【0015】

電圧測定回路24は、1列目から320列目までのデータ線112の電圧V-1、V-2、V-3、…、V-320を、信号Smpによって指定されたタイミングにて、それぞれ測定するものである。なお、信号Smpは、後述するテスト期間において、1行目から240行目までの各走査線102の選択が終了する直前のタイミング、すなわち、走査信号G<sub>WRT-1</sub>、G<sub>WRT-2</sub>、G<sub>WRT-3</sub>、…、G<sub>WRT-240</sub>がそれぞれHレベルからLレベルに切り替わる直前のタイミングにてそれぞれ出力されて、表示期間では出力されない。

補正データ算出回路26は、電圧測定回路24によって1列目から320列目までのデータ線112の電圧がそれぞれ測定されると、次のような動作を実行する。すなわち、補正データ算出回路26について、j列目のデータ線112の電圧V-jに関して代表して説明すると、第1に、測定された電圧V-jから、当該データ線112と選択されていた走査線102との交差に位置する画素回路200であって、当該画素回路200に含まれる駆動トランジスタ（後述する）の閾値電圧を求め、第2に、当該閾値電圧から補正データを階調毎に算出し、第3に、LUT28の記憶内容のうち、当該画素についての補正データを、算出した階調毎の補正データに書き換える。この動作を、補正データ算出回路26は、1列目から320列目までの1行分の画素についてそれぞれ実行する。

【0016】

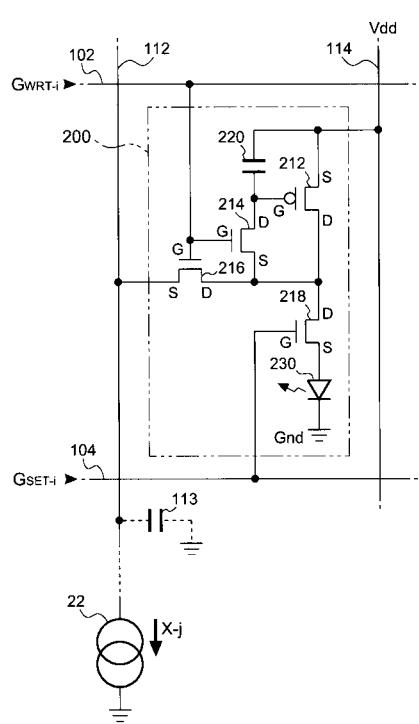

次に、画素回路200の電気的な構成について詳述する。図3は、i行j列に位置する画素回路200の構成を示す回路図である。

この図に示されるように、画素回路200は、駆動トランジスタ212と、スイッチング素子として機能するトランジスタ214、216、218と、電圧保持素子として機能する容量220と、電気光学素子たるOLED素子230とを有する。これらのうち、Pチャネル型の駆動トランジスタ212のソースは、電源線114に接続されている。駆動トランジスタ212のドレインは、Nチャネル型のトランジスタ214のソース、および、Nチャネル型のトランジスタ216、218の各ドレインに、それぞれ接続されている。

【0017】

トランジスタ218のソースは、OLED素子230の陽極に接続され、また、当該OLED素子230の陰極は、電源の低位側電圧Gndに接地されている。トランジスタ218のゲートは、i行目の点灯制御線104に接続されている。

一方、駆動トランジスタ212のゲートは、容量220の一端およびトランジスタ214のドレインに接続されている。また、容量220の他端は、電源線114に接続されている。さらに、トランジスタ216のソースは、j列目のデータ線112に接続される一方、そのゲートは、トランジスタ214のゲートとともに、i行目の走査線102に接続されている。

10

20

30

40

50

## 【0018】

なお、本発明と直接関係しないが、マトリクス型に配列する画素回路200は、例えばガラス等の透明基板上に、走査線102やデータ線112とともに形成される。このため、駆動トランジスタ212や、スイッチング素子としてのトランジスタ214、216、218は、ポリシリコンプロセスによるTFT（薄膜トランジスタ）によって構成される。また、OLED素子230は、基板上において、ITO（酸化錫インジウム）などの透明電極膜を陽極とし、アルミニウムやリチウムなどの単体金属膜またはこれらの積層膜を陰極として、発光層を挟持した構成となっている。

## 【0019】

ここで説明の便宜上、補正回路18、電圧測定回路24、補正データ算出回路26およびLUT28を有さず、メモリ16から読み出された画像データが補正されることなく、そのままXドライバ20に供給される構成（補正無構成と呼ぶ）の動作について説明する。

10

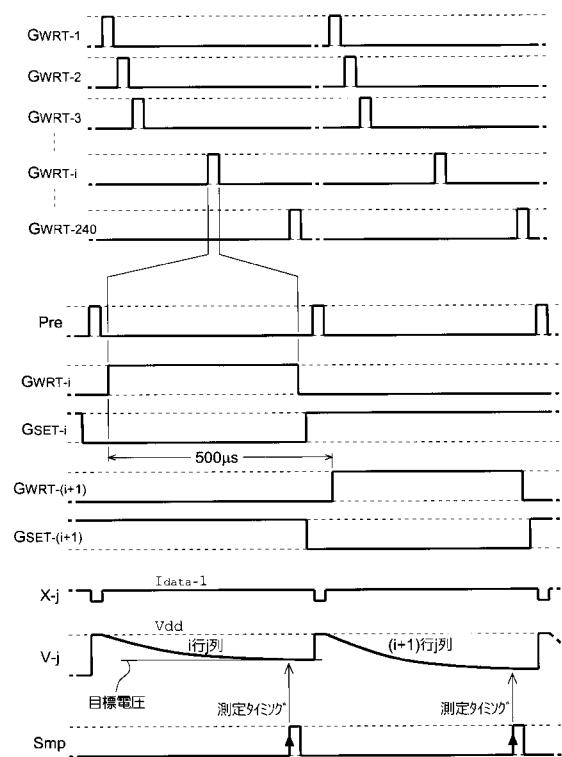

図4は、この補正無構成の動作を説明するためのタイミングチャートである。まず、Yドライバ12は、1垂直走査期間（1F）の開始時から、1行目、2行目、3行目、…、240行目の走査線102を、順番に1本ずつ1水平走査期間（1H）毎に選択して、選択した走査線102の走査信号のみをHレベルとする。ここで、画素回路200の動作について、i行j列に位置するもので代表して説明すると、まず、i行目の走査線102が選択される前に、すなわち、走査信号G<sub>WRT-i</sub>がHレベルになる前に、制御信号PreがHレベルとなるので、プリチャージされる結果、j列目のデータ線112の電圧V-jは、電源電圧Vddになる。

20

## 【0020】

この後、走査信号G<sub>WRT-i</sub>がHレベルになると、トランジスタ214がオン状態になるので、駆動トランジスタ212はダイオードとして機能する。また、走査信号G<sub>WRT-i</sub>がHレベルになると、トランジスタ216もオン状態となる。ただし、走査信号G<sub>WRT-i</sub>がHレベルになる期間では点灯信号G<sub>SET-i</sub>がHレベルにはならないので、トランジスタ218はオフ状態である。このため、データ電流X-jは、電源線114駆動トランジスタ212トランジスタ216データ線112という経路で流れる。したがって、駆動トランジスタ212のゲート電圧は、プリチャージ電圧Vddから徐々にデータ電流X-jに応じた電圧に至るとともに、容量220の一端に書き込まれることになる。なお、この補正無構成において、j列目のデータ線112に対応する定電流回路22は、i行j列の画素に対応する画像データを指定されたデータ電流X-jをj列目のデータ線112に流す。

30

## 【0021】

続いて、走査信号G<sub>WRT-i</sub>がLレベルになると、トランジスタ214、216はともにオフ状態になるが、容量220による電圧保持状態が保たれる。その後、制御信号G<sub>SET-i</sub>がHレベルになると、トランジスタ218がオンする。したがって、今度は、電流が電源線114駆動トランジスタ212トランジスタ218OLED素子230という経路で流れる。

このときにOLED素子230に流れる電流は、駆動トランジスタ212のゲート電圧で定まるが、そのゲート電圧は、走査信号G<sub>WRT-i</sub>がHレベルである場合であってデータ電流X-jがデータ線112に流れたときに容量素子220に保持された電圧である。このため、制御信号G<sub>SET-i</sub>がHレベルになったときに、OLED素子230に流れる電流は、十分な書き時間が確保されていれば、直前にデータ線112に流れていたデータ電流X-jにほぼ一致するので、走査線102が選択されたときにデータ線112に流れたデータ電流X-jが再生された形でOLED素子230に流れることになる。そして、以降、制御信号G<sub>SET-i</sub>がLレベルになるまで、当該電流に応じた輝度で発光し続けることになる。

40

## 【0022】

ただし、実際には、データ線112にデータ電流X-jを流しても、当該データ線11

50

2に寄生する容量113(図3参照)などのために、容量220の一端、すなわち駆動トランジスタ212のゲートは、目標とする電圧には迅速に達しない。走査線102は1水平走査期間(1H)毎に選択されるが、この期間が高精細化等に伴って短くなつて、例えば50μ秒程度しか確保できないと、走査信号G<sub>W R T - i</sub>がHレベルである期間がさらに短くなり、駆動トランジスタ212のゲートは、データ電流X-jを流すことにより最終的に書き込むべき目標電圧に達する前に、選択が終了してしまう。

この点を詳述すると、駆動トランジスタ212のゲート電圧は、トランジスタ214、216がオンしている場合であれば、j列目のデータ線112に現れるので、図4に示されるように、当該データ線112の電圧V-jが、目標電圧に達する前に、走査信号G<sub>W R T - i</sub>がLレベルとなつてしまつ。このため、補正無構成では、目標電圧と、実際に駆動トランジスタ212のゲートに書き込まれた電圧とに差が生じ、この差が書き込み誤差になつて、OLED素子230に流れる電流が目的とする電流から逸脱してしまう。

#### 【0023】

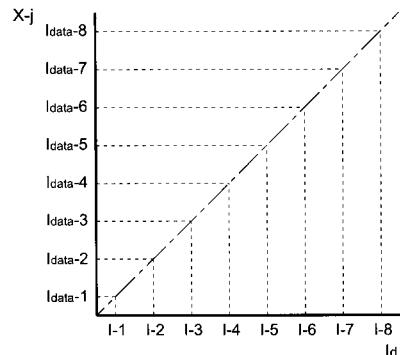

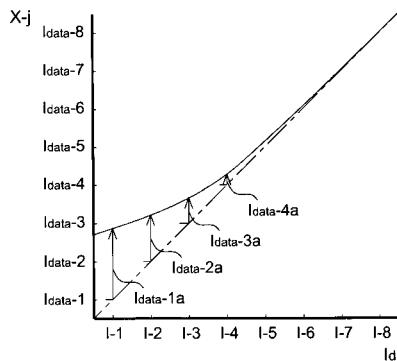

ここで、駆動トランジスタ212のソース・ドレイン間に流れる電流Id(制御信号G<sub>S E T - i</sub>がHレベルになつたときに、OLED素子230に流れる電流)と、補正前のデータ電流X-jとが図5に示されるような関係にあつて、画像データによってOLED素子230の輝度を8階調で指定する場合を考えてみる。すなわち、画像データによって階調レベル1~8が指定された場合に、それぞれ駆動トランジスタ212の電流Idが階調電流I-1~I-8になるように設定されるとともに、その場合にデータ線に流す設定電流がそれぞれI<sub>data-1</sub>~I<sub>data-8</sub>である場合を考えてみる。

#### 【0024】

図6は、この設定状態において、図4に示されるタイミングにて水平走査をした場合(すなわち、1水平走査期間(1H)が50μ秒である場合)、データ電流X-jを振つたとき、実際に駆動トランジスタ212のソース・ドレイン間に流れる電流Idがどうなつたかを示す図である。この図に示されるように、データ電流X-jが小さくなるにつれて(すなわち、駆動トランジスタの電流Idを小さくして、OLED素子230を暗く発光させることを指示するにつれて)、設定電流に対し、駆動トランジスタ212に電流Idが流れず、書き込み誤差が大きくなつてゐることが判る。

また、駆動トランジスタ212の閾値電圧が大きくなるにつれて、書き込み誤差が大きくなつ傾向も判る。このため、仮に駆動トランジスタ212の閾値電圧が画素回路200毎にばらついていると、同一のデータ電流を流したとしても、特に低階調表示時に駆動トランジスタ212のゲート電圧がばらつき、電流Idもばらつく結果、輝度ムラが目立つことになる。

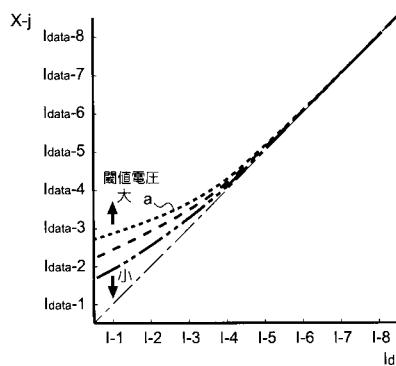

#### 【0025】

ところで、図6から判ることは、駆動トランジスタ212の閾値電圧さえ求めることができれば、OLED素子230に流す階調電流I-1~I-8に対して、それぞれ設定電流I<sub>data-1</sub>~I<sub>data-8</sub>に対する不足電流を求めることが出来る、という点である。詳細には、駆動トランジスタ212の閾値電圧が求まり、図6において特性aであると判明した場合、図7に示されるように、階調電流I-1~I-4の各々に対して、それぞれ設定電流I<sub>data-1</sub>~I<sub>data-4</sub>に対する不足電流は、図7において、それぞれI<sub>data-1</sub>a~I<sub>data-4</sub>aであることが判る。なお、設定電流が大きいとき、書き込み誤差は小さいので、例えば図7においては、設定電流I<sub>data-5</sub>~I<sub>data-8</sub>に対する不足電流はゼロである考へて良い。

そして、階調レベル1~4とするとき、設定電流I<sub>data-1</sub>~I<sub>data-4</sub>にそれぞれ不足電流I<sub>data-1</sub>a~I<sub>data-4</sub>aを加算したデータに相当する電流を、データ電流X-jとしてデータ線112に流す構成にすれば、駆動トランジスタ212のドレイン電流Idが階調電流I-1~I-4になつて、書き込み誤差による影響を抑えることができるはずである。

#### 【0026】

ただし、このためには、駆動トランジスタ212の閾値電圧を画素回路200毎に求め

10

20

30

40

50

なければならない。このため、本実施形態では、概略すれば、テスト期間なるものを設けて、駆動トランジスタ212の閾値電圧を画素回路200毎に求めるとともに、この閾値電圧から、不足電流に相当する補正データを画素回路200毎に算出してLUT28にセットする構成となっている。

なお、このテスト期間は、例えば、工場出荷時や、表示オン直前（電源オン直後であって表示前、または、スタンバイモードからの復帰直前）、表示オフ直後（電源オフ直前であって表示後、または、スタンバイモードに移行直後）などのように、表示が行わない時間が好ましい。また、このテスト期間は、制御回路10によって指示される。

#### 【0027】

そこでまず、本実施形態におけるテスト期間の詳細動作について説明する。図8は、テスト期間における動作を説明するためのタイミングチャートである。テスト期間の動作は、図4における補正無構成の動作と基本的相違しないが、時間的には、図4に示した走査よりも10倍遅い速度で各画素回路200が水平走査される。すなわち、テスト期間における1水平走査期間（1H）は500μ秒に設定されている。

#### 【0028】

一方、Xドライバ20における定電流回路22のすべては、OLED素子230における最低の階調電流I-1に相当する設定電流I<sub>data-1</sub>を、それぞれデータ電流としてデータ線112に流す。

図4に示されるように、1水平走査期間（1H）が充分に確保されておらず、走査信号G<sub>WRT-i</sub>がHレベルになる期間が短いと、駆動トランジスタ212のゲートが目標電圧に達する前に、走査線102の選択が終了してしまうが、図8に示されるように、走査信号G<sub>WRT-i</sub>がHレベルになる期間が充分に長いと、駆動トランジスタ212のゲートが目標電圧に達して、走査線102の選択が終了する。

#### 【0029】

ところで、設定電流I<sub>data-1</sub>は、換言すれば駆動トランジスタ212においてドレン電流が流れ始めるときの電流に相当するので、このときのゲート・ソース間電圧が、駆動トランジスタ212の閾値電圧と考えて良い。

したがって、走査信号G<sub>WRT-i</sub>がLレベルになる直前のタイミングにおいて、電圧V-jを求めるとともに、電圧V<sub>dd</sub>から電圧V-jを減じることによって、選択されていた走査線102とj列目のデータ線112との交差に位置する駆動トランジスタ212の閾値電圧を求めることができる。なお、閾値電圧を求める際には、厳密にいえば、トランジスタ216のオン抵抗や、データ線112、電源線114の配線抵抗等による電圧降下を考慮しなければならないが、設定電流I<sub>data-1</sub>は小さいので、そのときの電圧降下は無視できる。

#### 【0030】

閾値電圧を求めるために、本実施形態では、電圧測定回路24が信号Smpで示される当該タイミングにおいて1列目～320列目のデータ線112の電圧V-1～V-320をそれぞれ測定する。

電圧V-1～V-320がそれぞれ測定されると、補正データ算出回路26は、次のような動作を実行する。すなわち、補正データ算出回路26は、第1に、例えばj列目のデータ線112において測定された電圧V-jを、電源電圧V<sub>dd</sub>から減じて、i行j列の画素回路200における駆動トランジスタ212の閾値電圧を求める。補正データ算出回路26は、第2に、図7に示されるように、求めた閾値電圧の特性から、階調電流を流すのにそれぞれ必要な不足電流I<sub>data-1a</sub>～I<sub>data-8a</sub>を、階調レベル1～8毎に求める。ここで、階調レベルが大きい領域については、書き誤差が小さいので、不足分をゼロとしても良い。補正データ算出回路26は、第3に、求めた不足電流I<sub>data-1a</sub>～I<sub>data-8a</sub>に相当する分を、データ変換して補正データとして求めるとともに、LUT28において、i行j列の画素に対応する領域に書き込む。

#### 【0031】

このような補正データの変換および書き込みを、補正データ算出回路26は、i行目に

10

20

30

40

50

位置する 1 列目から 320 列目までの画素のすべてにわたって実行する。さらに、この 1 行分の動作を、補正データ算出回路 26 は、1 行目から 240 行目までのすべての行にわたって、走査線 102 が選択される毎に繰り返して実行する。これにより、LUT28 には、補正データが、240 行 × 320 列の画素のすべてにわたって階調レベル 1 ~ 8 毎に書き込まれることになる。そして、LUT28 に対する書き込みがすべての画素について完了すると、テスト期間が終了する。

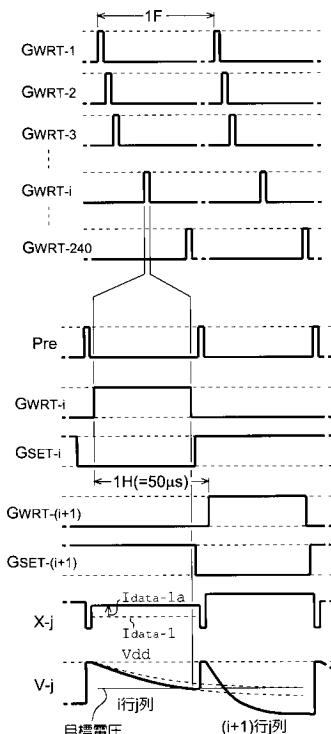

#### 【0032】

次に、表示期間の動作について説明する。図 9 は、表示期間における動作を説明するためのタイミングチャートである。表示期間の動作は、図 4 における補正無構成の動作と基本的相違しないが、X ドライバ 20 における定電流回路 22 は、i 行 j 列の画素に対応する画像データで指定された電流ではなく、補正データで補正された画像データで指定された電流を、データ電流 X - j として j 列目のデータ線 112 に流す。

#### 【0033】

この点を詳述すると、走査信号  $G_{WRT-i}$  が H レベルになる前に、メモリ 16 から i 行目の走査線 102 に位置する画素の画像データが 1 行分読み出される。このうち、j 列目のデータ線との交差に位置する画素、すなわち、i 行 j 列の画素について代表して説明すると、当該画素の画像データで指定された階調レベルに対応する補正データが LUT28 から読み出される。さらに、メモリ 16 から読み出された i 行 j 列の画素の画像データは、補正回路 18 によって LUT28 から読み出された i 行 j 列の画素の補正データと加算されて、補正される。そして、X ドライバ 20 における定電流回路 22 のうち、j 列目の定電流回路 22 は、走査信号  $G_{WRT-i}$  が H レベルになったときに、i 行 j 列の画素について補正された画像データで指定された電流を生成して、データ電流 X - j として j 列目のデータ線 112 に流す。これにより、画素の画像データによる設定電流に当該画素の不足電流分を加算される。例えば、j 列目の定電流回路 22 は、階調レベルが 1 であれば、図 9 に示されるように、設定電流  $I_{data-1}$  に補正データで示される不足電流  $I_{data-1}$  が加算された電流を、j 列目の定電流回路 22 は、データ電流 X - j として当該データ線 112 に流す。

#### 【0034】

このため、本実施形態によれば、走査信号  $G_{WRT-i}$  が H レベルから L レベルに切り替わる直前では、駆動トランジスタのゲート電圧（すなわち、j 列目のデータ線 112 の電圧  $V-j$ ）は、画像データで指定された階調レベルに相当する階調電流を流す電圧になっているので、上述したような書き誤差、および、これに起因する表示ムラを、それぞれ防止することが可能となる。

なお、第 1 実施形態では、テスト期間においてデータ線 112 に、最も低い輝度に相当する設定電流  $I_{data-1}$  を流したが、例えば、比較的輝度が暗い階調レベル、例えば、階調レベル 2 ~ 4 に相当する設定電流  $I_{data-2} \sim I_{data-4}$  を流して、そのときのデータ電圧から、駆動トランジスタ 212 の閾値電圧を求めて良い。ただし、電流が大きくなると、電圧降下を考慮しなければならないし、また、駆動トランジスタ 212 の閾値電圧を精度良く求めることができないので、やはり最も低い輝度に相当する設定電流  $I_{data-1}$  を流すのが望ましい。

#### 【0035】

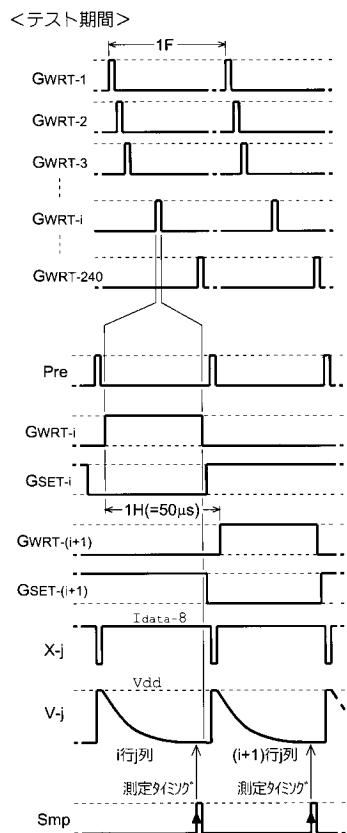

次に、本発明の第 2 実施形態について説明する。上述した第 1 実施形態では、駆動トランジスタ 212 の閾値電圧を求めるために、走査速度を、表示期間よりも遅くしたので、例えば、テスト期間を表示オン直前に実行する場合、実際に表示が開始されるまでに、それだけ時間を要してしまう、という欠点がある。そこで、この欠点を解消した第 2 実施形態について説明する。

#### 【0036】

図 10 は、第 2 実施形態において、テスト期間における動作を説明するためのタイミングチャートである。テスト期間の走査速度は、図 9 に示した第 1 実施形態における表示期間と同じである。ただし、第 1 実施形態では、テスト期間におけるデータ電流が、最も低

10

20

30

40

50

い輝度の階調レベル1に相当する設定電流I<sub>data-1</sub>であったのに対し、第2実施形態では、最も高い輝度の階調レベル8に相当する設定電流I<sub>data-8</sub>である点において相違する。

#### 【0037】

この相違点について説明すると、上述した図7に示したように、設定電流が大きくすると、容量113等の充放電が短時間のうちに完了するので、テスト期間の水平速度を表示期間と同様にしても、書き誤差は無視できる程度に小さくなるはずである。したがって、テスト期間の水平走査速度が表示期間と同様であっても、走査信号G<sub>WRT-i</sub>がHレベルからLレベルに切り替わる直前のタイミングでは、駆動トランジスタ212のゲート(容量220の一端)は、設定電流I<sub>data-8</sub>に対応した目標電圧に達していると考えられる。

#### 【0038】

ただし、設定電流I<sub>data-8</sub>は、第1実施形態における設定電流I<sub>data-1</sub>とは異なり、相当に大きいので、補正データ算出回路26は、次のようにして駆動トランジスタ212の閾値電圧を求める。

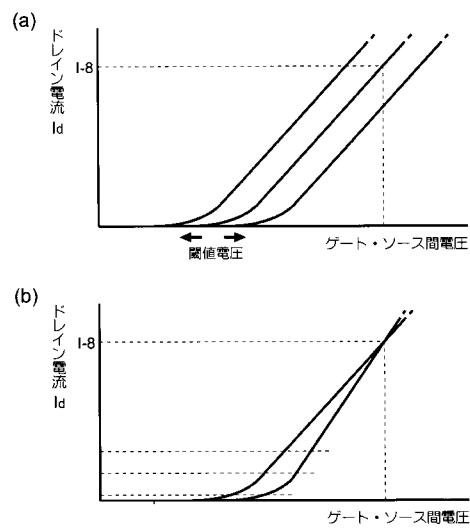

ここで、駆動トランジスタ212の特性のうち、閾値電圧だけが異なる場合、そのゲート・ソース電圧およびドレイン電流の特性は、例えば図11(a)に示されるように変化するが、データ線112に設定電流I<sub>data-8</sub>を流して、そのドレイン電流I<sub>d</sub>を階調電流I-8にすることと、そのときの測定したデータ電圧V-jを電源電圧V<sub>dd</sub>から減じて駆動トランジスタ212のゲート・ソース電圧を求めることによって、その特性が一意に定まる。そこで、補正データ算出回路26は、一意に定まる特性から、ドレイン電流I<sub>d</sub>が流れ始める閾値電圧を求めることができる。

#### 【0039】

補正データ算出回路26が駆動トランジスタ212の閾値電圧を求めた後の動作は、第1実施形態と同様である。

したがって、この第2実施形態によれば、テスト期間に要する時間を短縮でき、その後の表示期間において、上述したような書き誤差、および、これに起因する表示ムラを、それぞれ防止することが可能となる。

また、第2実施形態では、テスト期間においてデータ線112に、最も高い輝度に相当する設定電流I<sub>data-8</sub>を流したが、書き誤差が無視できる程度に小さければ、例えば、比較的輝度が明るい階調レベル、例えば、階調レベル5~7に相当する設定電流I<sub>data-5</sub>~I<sub>data-8</sub>であっても良い。

#### 【0040】

第2実施形態では、駆動トランジスタ212の特性のうち、閾値電圧だけが異なる場合を想定した。しかしながら、駆動トランジスタ212の特性において、閾値電圧のみならず、電流増幅率も画素回路200毎に相違している場合、図11(b)に示されるように、駆動トランジスタ212のドレイン電流およびゲート・ソース電圧を求めても、駆動トランジスタ212のゲート・ソース電圧およびドレイン電流の特性を一意に定めることはできない。

そこで、第2実施形態では、テスト期間において、駆動トランジスタ212のドレイン電流I<sub>d</sub>が、互いに異なるように、複数回に分けて流すとともに、各回においてデータ線112の電圧を測定すれば、駆動トランジスタ212のドレイン電流およびゲート・ソース間電圧の特性を一意に求めることができ、ドレイン電流I<sub>d</sub>が比較的小さいときの不足電流分をより正確に算出することができる。

第1実施形態についても、テスト期間において、駆動トランジスタ212のドレイン電流I<sub>d</sub>が、互いに異なるように、複数回に分けて流しても良いのはもちろんである。

#### 【0041】

また、第1、第2実施形態において、Yドライバ12は、例えば制御信号G<sub>SET-i</sub>を、走査信号G<sub>WRT-i</sub>がHレベルになる直前にLレベルとし、走査信号G<sub>WRT-i</sub>がLレベルになった直後にHレベルとしたが、制御信号G<sub>SET-1</sub>からG<sub>SET-24</sub>

10

20

30

40

50

までのすべてについて、Hレベルとなる期間が同一であれば良い。ここで、制御信号G<sub>SET-1</sub>からG<sub>SET-240</sub>までのすべてについて、Hレベルとなる期間を短くすると、すべてのOLED素子230にわたって、1垂直走査期間(1F)に占める発光期間の割合が短くなるので、表示画像が暗くなる一方、Hレベルとなる期間を長くすると、表示画像が明るくなるので、表示画像のブライトネスを調整することができる。

#### 【0042】

本発明は、上述した実施形態に限られず、種々の応用・変形が可能である。

例えば、実施形態では、単色の画素について階調表示をする構成になっていたが、3つの画素の各々に対して、R(赤)、G(緑)、B(青)にて発色するようにOLED素子230の発光層を選択するとともに、これらの3画素により1ドットを構成して、カラー表示を行うとしても良い。また、OLED素子230は、電流駆動型素子の一例であり、これに代えて、無機EL素子や、フィールドエミッショングリッド素子、LEDなどの他の発光素子、さらには、電気泳動素子、エレクトロ・クロミック素子などを用いても良い。

また、実施形態では、8階調表示としたが、これによりも低階調の4階調表示としても良いし、これよりも高階調の16、32、64、…、階調としても良いのは、もちろんである。

#### 【0043】

実施形態では、駆動トランジスタ212をPチャネル型としたが、Nチャネル型としても良い。また、スイッチング素子としてのトランジスタ214、216、218のチャネル型は、実施形態に限られず、Pチャネル型としても良い。さらに、スイッチング素子としてのトランジスタ214、216、218を、Pチャネル型およびNチャネル型を相補型に組み合わせたトランスマッショングートで構成すると、電圧降下がほぼ無視できる程度に抑えられるので、閾値電圧をより正確に求めることができる点において好ましい。

くわえて、トランジスタ214のソース側にOLED素子230を接続するのではなく、トランジスタ214のドレイン側にOLED素子230を接続しても良い。

#### 【0044】

次に、上述した実施形態に係る電気光学装置を電子機器に用いた例について説明する。

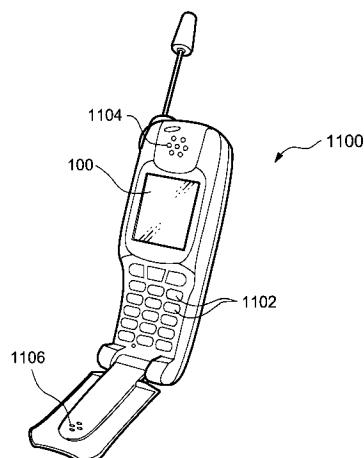

まず、電気光学装置1を、表示部に適用した携帯電話について説明する。図12は、この携帯電話の構成を示す斜視図である。

この図において、携帯電話1100は、複数の操作ボタン1102のほか、受話口1104、送話口1106とともに、表示部として、上述した電気光学装置1の表示パネル100を備えるものである。

#### 【0045】

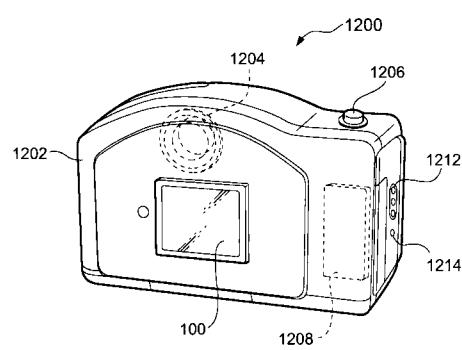

次に、上述した電気光学装置1を、ファインダに用いたデジタルスチルカメラについて説明する。

図13は、このデジタルスチルカメラの背面を示す斜視図である。銀塩カメラは、被写体の光像によってフィルムを感光させるのに対し、デジタルスチルカメラ1200は、被写体の光像をCCD(Charge Coupled Device)などの撮像素子により光電変換して撮像信号を生成・記憶するものである。ここで、デジタルスチルカメラ1200におけるケース1202の背面には、上述した電気光学装置1の表示パネル100が設けられる。この表示パネル100では、撮像信号に基づいて表示が行われるので、被写体を表示するファインダとして機能することになる。また、ケース1202の前面側(図12においては裏面側)には、光学レンズやCCDなどを含んだ受光ユニット1204が設けられている。

#### 【0046】

撮影者が表示パネル100によって表示された被写体像を確認して、シャッタボタン1206を押下すると、その時点におけるCCDの撮像信号が、回路基板1208のメモリに転送・記憶される。また、このデジタルスチルカメラ1200にあって、ケース1202の側面には、外部表示を行うためのビデオ信号出力端子1212と、データ通信用の入出力端子1214とが設けられている。

10

20

30

30

40

50

## 【0047】

なお、電子機器としては、図12の携帯電話や、図13のデジタルスチルカメラの他にも、テレビや、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種電子機器の表示部として、上述した電気光学装置が適用可能なのは言うまでもない。

## 【図面の簡単な説明】

## 【0048】

【図1】本発明の第1実施形態に係る駆動方法が適用される電気光学装置の構成を示すブロック図である。 10

【図2】同電気光学装置における表示パネルの構成を示すブロック図である。

【図3】同表示パネルにおける画素回路の構成を示す回路図である。

【図4】同電気光学装置における書き誤差を説明するための図である。

【図5】同表示パネルにおける駆動トランジスタのソース・ドレイン電流とデータ電流との関係を示す図である。

【図6】同電気光学装置における設定電流とOLED素子に流す電流との関係を示す図である。

【図7】同電気光学装置における補正データの算出手順を示す図である。

【図8】同表示パネルにおけるテスト期間の動作を示すタイミングチャートである。 20

【図9】同表示パネルにおける表示期間の動作を示すタイミングチャートである。

【図10】本発明の第2実施形態に係る駆動方法が適用される電気光学装置のテスト期間における動作を説明するためのタイミングチャートである。

【図11】本発明の応用形態に係る駆動方法を説明するための図である。

【図12】同電気光学装置を用いた携帯電話を示す図である。

【図13】同電気光学装置を用いたデジタルスチルカメラを示す図である。

## 【符号の説明】

## 【0049】

1...電気光学装置、10...制御回路、12...Yドライバ、18...補正回路、20...Xドライバ、22...定電流回路、24...電圧測定回路、26...補正データ算出回路、28...LUT、100...表示パネル、102...走査線、104...点灯制御線、112...データ線、114...電源線、200...画素回路、212...駆動トランジスタ、212、214、216、218...トランジスタ、220...容量、230...OLED素子、1100...携帯電話機、1200...デジタルスチルカメラ 30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

&lt;テスト期間&gt;

【図9】

&lt;表示期間&gt;

【図10】

【図11】

【図12】

【図13】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 3 1 V |

| G 0 9 G | 3/20  | 6 4 2 A |

| H 0 5 B | 33/14 | A       |

【要約の続き】

【選択図】 図1

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于驱动像素电路的方法，驱动电路，电光装置和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005115144A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2005-04-28 |

| 申请号            | JP2003350951                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-10-09 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 池上富雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 池上 富雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.H G09G3/20.622.C G09G3/20.622.D G09G3/20.624.B G09G3/20.631.V G09G3/20.642.A H05B33/14.A G09G3/20.621.F G09G3/20.642.P G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/KK43 5C080/KK47 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB23 5C380/AB34 5C380/AC07 5C380/AC09 5C380/AC10 5C380/AC11 5C380/AC13 5C380/BB04 5C380/BC02 5C380/BC13 5C380/CA08 5C380/CA13 5C380/CB01 5C380/CB17 5C380/CC12 5C380/CC19 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC63 5C380/CD014 5C380/CF02 5C380/CF13 5C380/DA06 5C380/DA39 5C380/DA40 5C380/EA02 5C380/FA02 5C380/FA21 5C380/FA28 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | <a href="#">JP4572523B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

要解决的问题：为了防止在低灰度显示期间OLED元件的亮度不均匀。

解决方案：在测试周期和显示周期中分别驱动每个像素电路，在测试周期中，以比显示周期慢的水平扫描速度顺序选择扫描线102，并且每个数据线112与要提供的密钥相对应的电流，以及在完成扫描线选择之前的时间，根据数据线112上的测量电压，驱动晶体管位于所选扫描线和测量数据线的相交处。计算晶体管的阈值电压，并将与电流不足相对应的校正数据写入LUT28。另一方面，在显示时段中，依次选择扫描线102，并且位于选择的扫描线中的像素次数增加。通过为像素电路获得的校正数据来校正指定路径的电光元件的亮度的图像数据。对应于校正后的图像数据的电流通过数据线112提供给像素电路。逃走 [选型图]图1