特開2003 - 122306

(P2003 - 122306A)

(43)公開日 平成15年4月25日(2003.4.25)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I          | テ-マコード* (参考)    |

|--------------------------|------|--------------|-----------------|

| G 0 9 G 3/30             |      | G 0 9 G 3/30 | K 3 K 0 0 7     |

| G 0 9 F 9/30             | 338  | G 0 9 F 9/30 | 338 5 C 0 8 0   |

|                          | 365  |              | 365 Z 5 C 0 9 4 |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20 | 611 H           |

|                          | 621  |              | 621 A           |

審査請求 未請求 請求項の数 60 L (全 11数) 最終頁に続く

(21)出願番号 特願2001 - 312322(P2001 - 312322)

(22)出願日 平成13年10月10日(2001.10.10)

(71)出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(72)発明者 湯本 昭

東京都品川区北品川6丁目7番35号 ソニー

株式会社内

(74)代理人 100086298

弁理士 船橋 國則

最終頁に続く

(54)【発明の名称】 アクティブマトリクス型表示装置およびアクティブマトリクス型有機エレクトロルミネッセンス

表示装置

(57)【要約】

【課題】 TFTの特性ばらつきの補償機能を有する画素回路の場合には、電圧書き込み型の基本的な画素回路に比べて素子数が多くなる。

【解決手段】 アクティブマトリクス型有機EL表示装置において、2個のTFT 21, 23および1個のキヤバシタ22からなり、輝度情報に応じた電流を有機EL素子に流す画素回路を、上下に隣り合う2画素の有機EL素子11A, 11Bに対して共通に設け、有機EL素子11A, 11Bを選択用TFT 15A, 15Bで適宜選択することによって当該画素回路を上下に隣り合う2画素間で時分割的に共用するようにし、1画素当たりの画素回路の素子数を削減する。

## 【特許請求の範囲】

【請求項1】 流れる電流によって輝度が変化する電気光学素子を有する画素がマトリクス状に配置されてなるアクティブマトリクス型表示装置であって、複数の画素に対して共通に設けられ、データ線を通して与えられる輝度情報に応じた電流を前記複数の画素の各電気光学素子に流す画素回路と、前記複数の画素の中から前記画素回路の駆動対象となる画素の電気光学素子を選択する選択手段とを備えたことを特徴とするアクティブマトリクス型表示装置。

【請求項2】 前記画素回路は、隣り合う2行の各画素に対して共通に設けられ、奇数行の画素全体への輝度情報の書き込みと、偶数行の画素全体への輝度情報の書き込みとを交互に行うこととする請求項1記載のアクティブマトリクス型表示装置。

【請求項3】 前記画素回路は、隣り合う2行の各画素に対して共通に設けられ、第1のデータ線上の画素において、奇数行の画素全体への輝度情報の書き込みと、偶数行の画素全体への輝度情報の書き込みとを交互に行う一方、前記第1のデータ線上の奇数行の画素に輝度情報の書き込みが行われる間、これに隣接する第2のデータ線上の偶数行の画素に対して輝度情報の書き込みを行い、前記第1のデータ線上の偶数行の画素に輝度情報の書き込みが行われる間、前記第2のデータ線上の奇数行の画素に対して輝度情報の書き込みを行うことを特徴とする請求項1記載のアクティブマトリクス型表示装置。

【請求項4】 第1,第2の電極およびこれら電極間に発光層を含む有機層を有する有機エレクトロルミネッセンス素子を表示素子として有する画素がマトリクス状に配置されてなるアクティブマトリクス型有機エレクトロルミネッセンス表示装置であって、複数の画素に対して共通に設けられ、データ線を通して与えられる輝度情報に応じた電流を前記複数の画素の各有機エレクトロルミネッセンス素子に流す画素回路と、前記複数の画素の中から前記画素回路の駆動対象となる画素の有機エレクトロルミネッセンス素子を選択する選択手段とを備えたことを特徴とするアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項5】 前記画素回路は、隣り合う2行の各画素に対して共通に設けられ、奇数行の画素全体への輝度情報の書き込みと、偶数行の画素全体への輝度情報の書き込みとを交互に行うこととする請求項4記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項6】 前記画素回路は、隣り合う2行の各画素に対して共通に設けられ、第1のデータ線上の画素において、奇数行の画素全体への輝度情報の書き込みと、偶数行の画素全体への輝度情報の書き込みとを交互に行う一方、前記第1のデータ線上の奇数行の画素に輝度情報の書き込みが行われる間、これに隣接する第2のデータ

線上の偶数行の画素に対して輝度情報の書き込みを行い、前記第1のデータ線上の偶数行の画素に輝度情報の書き込みが行われる間、前記第2のデータ線上の奇数行の画素に対して輝度情報の書き込みを行うことを特徴とする請求項4記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、各画素毎に能動素子を有して当該能動素子によって画素単位で表示制御が行われるアクティブマトリクス型表示装置に関し、特に、流れる電流によって輝度が変化する電気光学素子を画素の表示素子として用いるアクティブマトリクス型表示装置および電気光学素子として有機材料のエレクトロルミネッセンス(以下、有機EL(electroluminescence)と記す)素子を用いるアクティブマトリクス型有機EL表示装置に関する。

## 【0002】

【従来の技術】表示装置、例えば画素の表示素子として液晶セルを用いた液晶表示装置などにおいては、多数の画素をマトリクス状に配列し、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像の表示駆動が行われるようになっている。この表示駆動は、画素の表示素子として有機EL素子を用いた有機EL表示装置などでも同様である。

【0003】ただし、有機EL表示装置の場合には、画素の表示素子として発光素子を用いる、いわゆる自発光型の表示装置であるため、液晶表示装置に比べて画像の視認性が高い、バックライトが不要、応答速度が速い等の利点を有する。また、各発光素子の輝度はそれに流れる電流値によって制御される、即ち有機EL素子が電流制御型であるという点で、液晶セルが電圧制御型である液晶表示装置などとは大きく異なる。

【0004】有機EL表示装置においては、液晶表示装置と同様、その駆動方式として、単純(パッシブ)マトリクス方式とアクティブマトリクス方式とを探ることができる。ただし、前者は構造が単純であるものの、大型かつ高精細のディスプレイの実現が難しいなどの問題がある。このため、近年、画素内部の発光素子に流れる電流を、同様に画素内部に設けた能動素子(一般には、薄膜トランジスタ(ThinFilm Transistor; TFT)によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

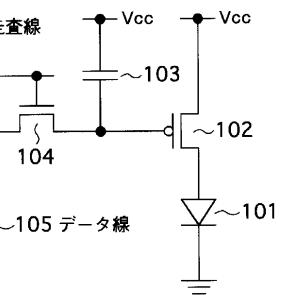

【0005】図8に、アクティブマトリクス型有機EL表示装置における電圧書き込み型の画素回路(単位画素の回路)の回路例を示す(より詳細には、米国特許第5,684,365号公報、特開平8-234683号公報を参照)。

【0006】この回路例に係る画素回路は、図8から明らかなように、カソード(陰極)が接地された有機EL

素子101と、有機EL素子101のアノード（陽極）にドレインが接続され、正電源Vccにソースが接続されたTFT102と、TFT102のゲートと正電源Vccとの間に接続されたキャパシタ103と、TFT102のゲートにドレインが、データ線105にソースがそれぞれ接続されたTFT104とを有し、TFT104のゲートに走査線106を通して走査パルスが与えられる構成となっている。

【0007】ここで、有機EL素子は多くの場合整流性があるため、OLED(Organic Light Emitting Diode)と呼ばれることがある。したがって、図8およびその他の図では、有機EL素子としてダイオードの記号を用いて示している。ただし、以下の説明において、有機EL素子には必ずしも整流性を要求するものではない。

【0008】上記構成の画素回路の動作は次の通りである。先ず、走査線106の電位を選択状態（ここでは、高レベル）とし、データ線105に書き込み電位Vwを印加すると、TFT104が導通してキャパシタ103が充電または放電され、TFT102のゲート電位は書き込み電位Vwとなる。次に、走査線106の電位を非選択状態（ここでは、低レベル）とすると、走査線106とTFT102とは電気的に切り離されるが、TFT102のゲート電位はキャパシタ103によって安定に保持される。

【0009】そして、TFT102および有機EL素子101に流れる電流は、TFT102のゲート・ソース間電圧Vgsに応じた値となり、有機EL素子101はその電流値に応じた輝度で発光し続ける。ここで、走査線106を選択してデータ線105に与えられた輝度情報を画素内部に伝える動作を、以下、「書き込み」と呼ぶこととする。上述のように、図8に示す画素回路では、一度電位Vwの書き込みを行えば、次に書き込みが行われるまでの間、有機EL素子101は一定の輝度で発光を継続する。

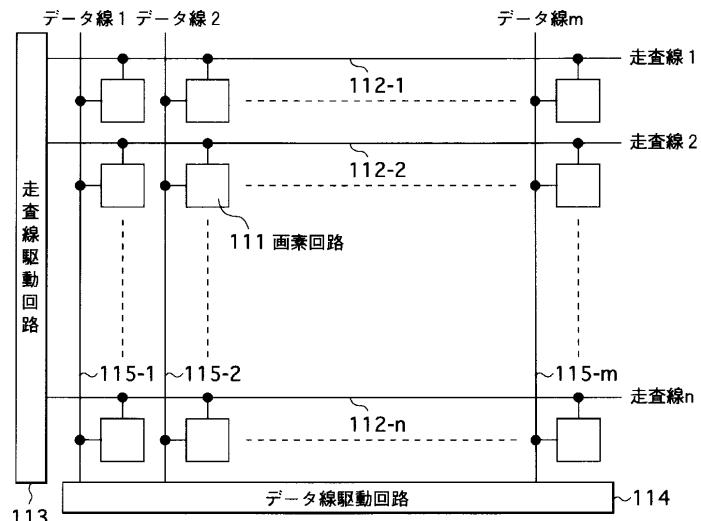

【0010】このような画素回路（以下、単に画素と記す場合もある）111を図9に示すようにマトリクス状に多数並べ、走査線112-1~112nを走査線駆動回路113によって順次選択しながら、電圧駆動型のデータ線駆動回路114からデータ線115-1~115-mを通して書き込みを繰り返すことにより、アクティブマトリクス型表示装置（有機EL表示装置）を構成することができる。ここでは、n行×m列の画素配列を示している。この場合、当然のことながら、走査線がn本、データ線がm本となる。

【0011】単純マトリクス型表示装置では、各発光素子は、選択された瞬間にのみ発光するのに対し、アクティブマトリクス型表示装置では、書き込み終了後も発光素子が発光を継続する。このため、アクティブマトリクス型表示装置は、単純マトリクス型表示装置に比べて発光素子のピーク輝度、ピーク電流を下げられるなどの点

で、とりわけ大型・高精細のディスプレイでは有利となる。

【0012】ところで、アクティブマトリクス型有機EL表示装置においては、能動素子として一般に、ガラス基板上に形成された絶縁ゲート型薄膜電界効果トランジスタ（TFT）が利用される。ところが、このTFTの形成に使用されるアモルファスシリコン（非晶質シリコン）やポリシリコン（多結晶シリコン）は、単結晶シリコンに比べて結晶性が悪く、導電機構の制御性が悪いために、形成されたTFTは特性のばらつきが大きいことが良く知られている。

【0013】特に、比較的大型のガラス基板上にポリシリコンTFTを形成する場合には、ガラス基板の熱変形等の問題を避けるため、通常、アモルファスシリコン膜の形成後、レーザアニール法によって結晶化が行われる。しかしながら、大きなガラス基板に均一にレーザエネルギーを照射することは難しく、ポリシリコンの結晶化の状態が基板内の場所によってばらつきを生ずることが避けられない。この結果、同一基板上に形成したTFTでも、その閾値電圧Vthが画素によって数百mV、場合によっては1V以上ばらつくこともまれではない。

【0014】この場合、例えば異なる画素に対して同じ電位Vwを書き込んでも、画素によってTFTの閾値電圧Vthがばらつくことになる。これにより、有機EL素子に流れる電流Idsは画素毎に大きくばらついて全く所望の値からはずれる結果となり、ディスプレイとして高い画質を期待することはできない。このことは、閾値電圧Vthだけでなく、キャリアの移動度μなどのばらつきについても同様に言える。

【0015】かかる問題を改善するために、従来、以下に説明する2つの画素回路が提案されている。その一つの従来例（以下、従来例1と称す）に係る画素回路の回路例を図10に示す。

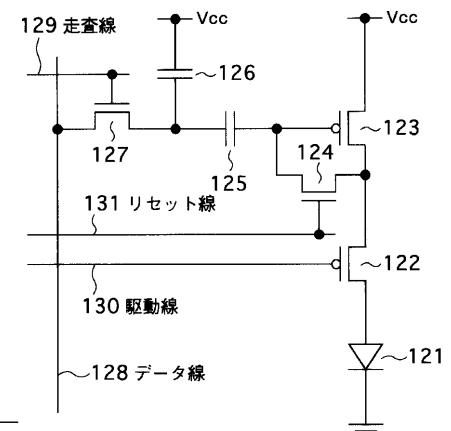

【0016】この従来例1に係る画素回路は、図10から明らかなように、カソードが接地された有機EL素子121と、有機EL素子121のアノードにドレインが接続されたTFT122と、TFT122のソースにドレインが接続され、正電源Vccにソースが接続されたTFT123と、TFT123のゲートとドレインとの間に接続されたTFT124と、TFT123のゲートに一端が接続されたキャパシタ125と、キャパシタ125の他端と正電源Vccとの間に接続されたキャパシタ126と、キャパシタ125の他端にドレインが、データ線128にソースがそれぞれ接続されたTFT127とを有し、TFT127のゲートに走査線129を通して走査パルスが、TFT122のゲートに駆動線130を通して駆動パルスが、TFT124のゲートにリセット線131を通してリセットパルスが与えられる構成となっている。

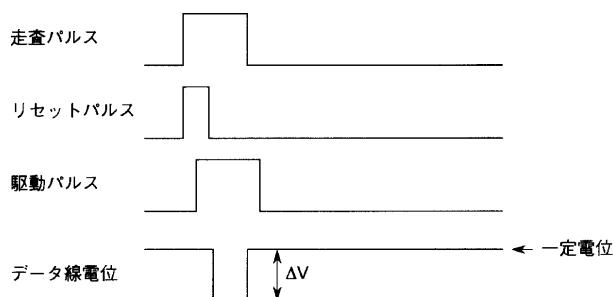

【0017】続いて、上記構成の従来例1に係る画素回

路の回路動作について、図11のタイミングチャートを用いて説明する。

【0018】先ず、データの書き込みに先立って走査線129およびリセット線131を選択状態（共に高レベル）とし、スイッチ用TFT124によって駆動用TFT123のゲート・ドレイン間を短絡する。次に、駆動線130を非選択状態（高レベル）とすると、駆動用TFT123と有機EL素子121との間に介在するスイッチ用TFT122がオフ状態となる。これにより、駆動用TFT123のドレイン電位が上昇する。

【0019】一方、スイッチ用TFT124がオン状態にあり、駆動用TFT123のゲート・ドレイン間が電気的に短絡されているためにそのゲート電位も上昇し、これがVcc-|Vtp|となった時点で安定状態となる（これを以後リセット状態と呼ぶことがある）。ここで、|Vtp|は駆動用TFT123の閾値電圧の絶対値である。リセット動作が完了したら、リセット線131を非選択状態（低レベル）とし、データ線128に輝度情報に応じた電圧を印加する。

$$I_{DS} = \mu C_{ox} \cdot W / L / 2 ( V_{CC} - V_{GS} - | V_{TP} | )^2 \quad \dots \dots (1)$$

ここで、 $\mu$  はキャリアの移動度、 $C_o x$  は単位面積当たりのゲート容量、 $W$  はチャネル幅、 $L$  はチャネル長である。

$$V_g = V_{cc} - |V_{tp}| - V$$

となる。これを(1)式に代入すれば、

$$I_{ds} = \mu C_{ox} \cdot W / L / 2 \cdot V^2$$

が得られる。(3)式は  $V_t p$  を含まないことから、駆動用  $TFT123$  を流れる電流  $I_{ds}$  は、閾値電圧  $V_t p$  のばらつきに影響されないことがわかる。

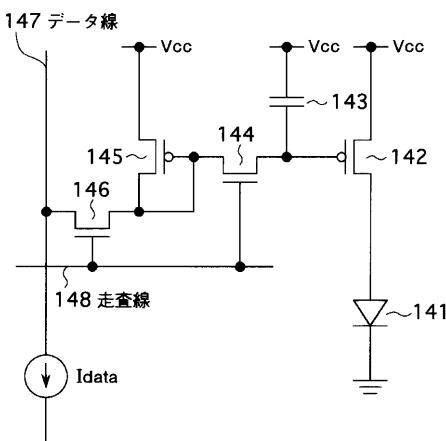

【0023】他の従来例（以下、従来例2と称す）に係る画素回路として、図12に示す電流書き込み型の画素回路が本願発明者によって提案されている（その詳細については、国際公開番号WO01-06484公報参照）。

【0024】この従来例2に係る画素回路は、図12から明らかなように、カソードが接地された有機EL素子141と、有機EL素子141のアノードにドレインが接続され、正電源Vccにソースが接続されたTFT142と、このTFT142のゲートとグランドとの間に接続されたキャパシタ143と、TFT142のゲートにドレインが接続されたTFT144と、TFT144のソースがゲートおよびドレインが接続され、正電源Vccにソースが接続されたTFT145と、TFT145のゲート・ドレインとデータ線147との間に接続されたTFT146とを有し、TFT144, 146の各ゲートに走査線148を通して走査パルスが与えられる構成となっている。

【0025】この従来例2に係る画素回路は、図8および図10の各画素回路では輝度データが電圧の形で与えられるのに対して、輝度データが電流の形で与えられる

\* 【0020】データ線128の電位は、図11に示すように、リセット動作中は一定の基準電位とされており、リセット動作後に電圧Vだけ低下する。その状態で走査線129を非選択状態とすることで、当該画素への書き込み動作が完了する。データ線128と駆動用トランジスタ123のゲートとはキャパシタ125によって容量結合されているため、データ線128の電位は駆動用TFT123のゲートに直接伝わることなく、概ねデータ線128の電位変化分Vが伝達される。その後、駆動線130を選択状態(低レベル)とすると、書き込まれたデータに応じた電流がスイッチ用TFT122を通して有機EL素子121に流れる。これにより、有機EL素子121は、書き込まれたデータに応じた輝度で発光する。

【0021】ところで、駆動用 TFT123 が飽和領域で動作すると仮定すれば、駆動用 TFT123 に流れる電流  $I_{ds}$  は、良く知られた MOS ランジスタの式によって(1)式のように表される。

$$- V g - | V t p | )^2 \quad \dots \dots ($$

【0022】ゲート電位Vgは、前述したリセット動作によって、データ書き込みの直前にはVcc- | Vtp |となっているが、書き込み終了直後には

..... ( 2 )

ことが大きな特徴である。その動作は次の通りである。

【0026】先ず、輝度データの書き込み時には、走査線148を選択状態（高レベル）にし、データ線147に輝度データに応じた書き込み電流Iwを流す。この書き込み電流Iwは、TFT146を通してTFT145に流れる。このとき、TFT144がオン状態にあることから、TFT142とTFT145とはカレントミラー回路を形成する。ここで、両トランジスタ142, 145は小さな画素内部に近接して配置されるためほぼ同一の特性を有している。

【0027】その結果、TFT142には、書き込み電流 $I_w$ に比例した駆動電流 $I_d$ が流れる。駆動電流 $I_d$ と書き込み電流 $I_w$ との比は、TFT142とTFT145とのチャネル幅/チャネル長の比を適宜設定することによって自由に選ぶことができ、TFT142, 145の閾値電圧やキャリアの移動度の値そのものには影響されないので、全画面(全画素領域)に亘って閾値電圧やキャリアの移動度のばらつきによらず、所望の輝度で各画素の有機EL素子141を発光させることができある。

(0028)

【発明が解決しようとする課題】上述したことから明らかなように、TFTの特性ばらつきの補償機能を有する画素回路、即ち図10に示す従来例1に係る画素回路あ

るいは図12に示す従来例2に係る画素回路では、TFTの閾値電圧やキャリアの移動度のばらつきによらず、所望の輝度で各画素の発光素子を発光させることができるという大きな特長を持つのであるが、その反面、図8に示す電圧書き込み型の基本的な画素回路に比べて素子数が増加するという欠点がある。

【0029】すなわち、図8に示す画素回路の場合にはトランジスタ2個で構成されるのに対し、図10および図12に示す各画素回路の場合にはトランジスタが4個必要であり、図10の画素回路ではさらにキャパシタの数も1個多くなる。TFTの特性ばらつきによる画質劣化の対策としては、図10や図12に示す画素回路以外にも種々の回路的工夫がなされた画素回路が提案されているが、いずれも素子数の増加は免れない。このように、1画素当たりの画素回路の素子数が多いと、製造歩留まりの低下を招き易く、さらには画素面積を縮小し難いことから、画素ピッチを大きくとらざるを得なく、高解像度化の妨げとなる。

【0030】本発明は、上記課題に鑑みて為されたものであり、その目的とするところは、1画素当たりの画素回路の素子数を削減することにより、製造歩留まりの向上、さらには画素面積の縮小化、それに伴う高解像度化を可能としたアクティブマトリクス型表示装置およびアクティブマトリクス型有機EL表示装置を提供することにある。

### 【0031】

【課題を解決するための手段】本発明によるアクティブマトリクス型表示装置は、流れる電流によって輝度が変化する電気光学素子を有する画素がマトリクス状に配置されており、複数の画素に対して共通に設けられ、データ線を通して与えられる輝度情報に応じた電流を複数の画素の各電気光学素子に流す画素回路と、複数の画素の中から画素回路の駆動対象となる画素の電気光学素子を選択する選択手段とを備えた構成となっている。また、この表示装置は、電気光学素子として有機EL素子を用いるアクティブマトリクス型有機EL表示装置に適用される。

【0032】上記構成のアクティブマトリクス型表示装置またはアクティブマトリクス型有機EL表示装置において、画素回路は複数の画素に対して共用され、複数の画素の中から選択手段によって駆動回路の駆動対象として時分割的に選択された画素の電気光学素子または有機EL素子に対して、データ線を通して与えられる輝度情報に応じた電流を流す。ここで、画素回路を複数の画素間で共用することで、1画素当たりの画素回路の素子数を削減できる。

### 【0033】

【発明の実施の形態】以下、本発明の実施の形態について図面を参照して詳細に説明する。

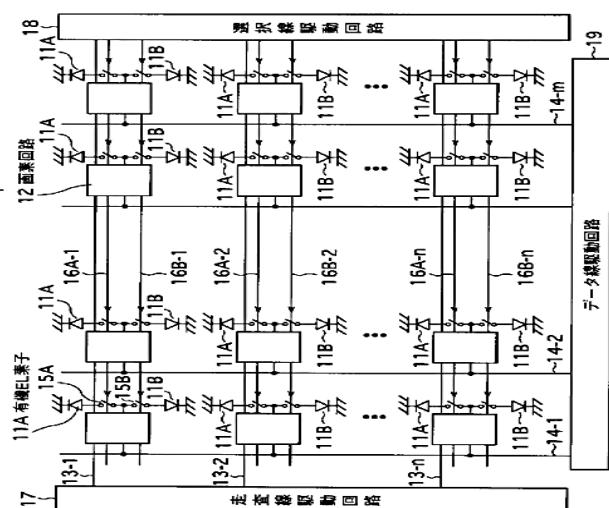

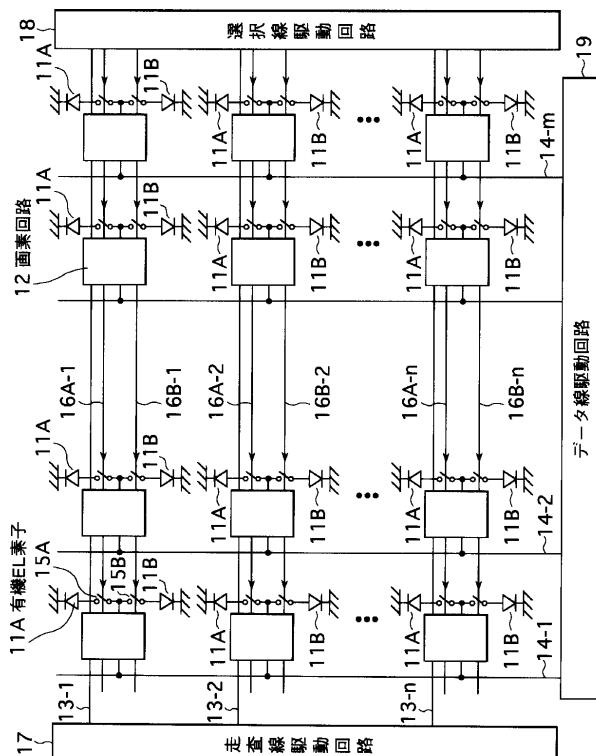

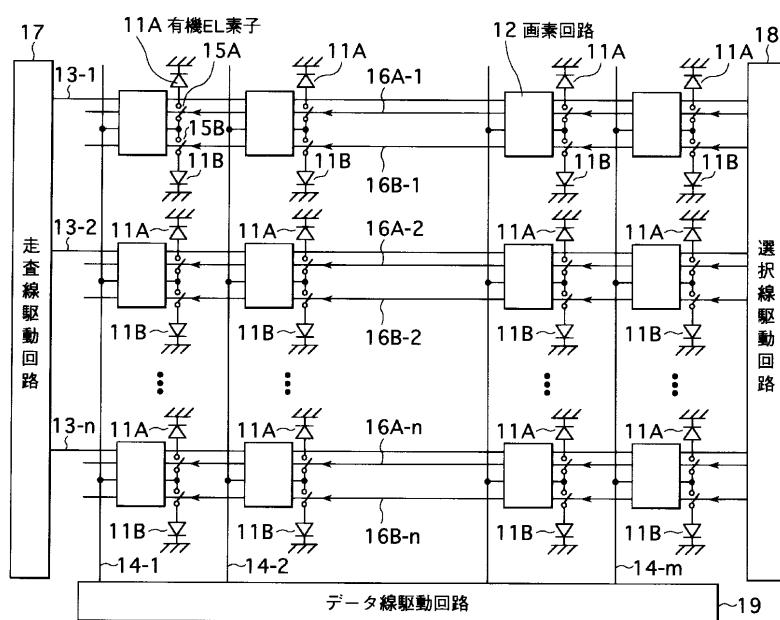

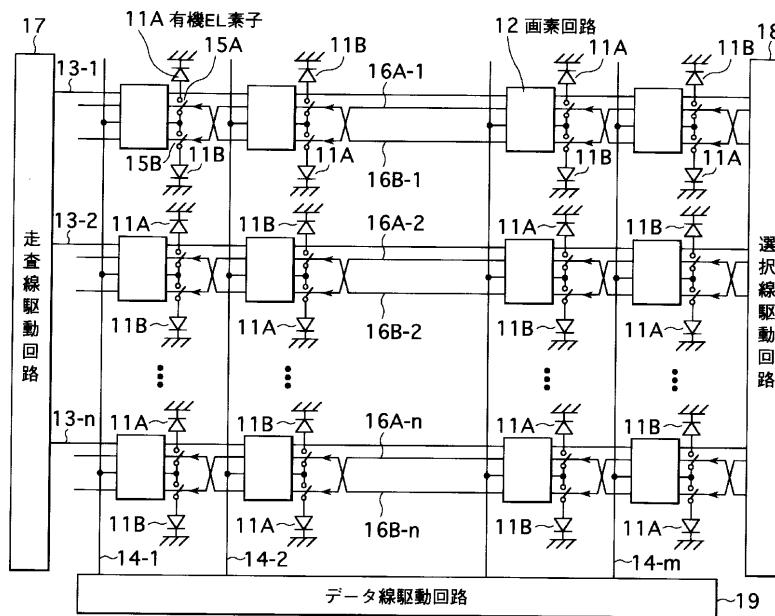

【0034】[第1実施形態]図1は、本発明の第1実

施形態に係るアクティブマトリクス型表示装置の構成を示すブロック図である。図1において、画素毎に設けられる発光素子として、流れる電流によって輝度が変化する電気光学素子、例えば有機EL素子11(11A, 11B)が用いられており、この有機EL素子11が画素単位でマトリクス状(行列状)に配置されている。ここでは、2n行×m列の画素配列を例に採って示している。

【0035】この画素配列において、複数の画素、例えば上下に隣り合う2画素の各有機EL素子11A, 11Bに対して、輝度情報に応じた電流を流す画素回路12が共通に設けられている。すなわち、1つの画素回路12を、上下に隣り合う2画素分の有機EL素子11A, 11Bの駆動に共用する構成となっている。したがって、2n行×m列の画素配列に対して、画素回路12を行単位で選択するn本の走査線13-1~13-nと、各画素回路12に輝度データを供給するm本のデータ線14-1~14-mがマトリクス状に配線されている。

【0036】また、画素の各々には、上下に隣り合う2画素分の有機EL素子11A, 11Bを駆動選択するための一対の選択スイッチ15A, 15Bが2行単位で設けられている。これに伴い、これら選択スイッチ15A, 15Bを行単位で順に時分割的に駆動して、駆動対象の有機EL素子11A/11Bを選択する2系統の選択線16A-1~16A-n, 16B-1~16B-nが2行単位で配線されている。

【0037】有機EL素子11が行列状に配置されてなる画素部に対して、例えば、図の左側にはn本の走査線13-1~13-nを選択駆動する走査線駆動回路17が、図の右側には2系統の選択線16A-1~16A-n, 16B-1~16B-nを選択駆動する選択線駆動回路18が、図の下側にはm本のデータ線14-1~14-mに対して輝度データを供給するデータ線駆動回路19がそれぞれ配置されている。

【0038】走査線駆動回路17は例えばn段の転送段のシフトレジスタからなり、各転送段の出力端に走査線13-1~13-nの各一端が接続されている。選択線駆動回路18は例えば2n段の転送段のシフトレジスタからなり、各転送段の出力端の前半部分に選択線16A-1~16A-nの各一端が、後半部分に選択線16B-1~16B-nの各一端がそれぞれ接続されている。すなわち、選択線駆動回路18による駆動により、先ず、奇数行の選択線16A-1~16A-nが順に選択され、次いで偶数行の選択線16B-1~16B-nが順に選択されるようになっている。

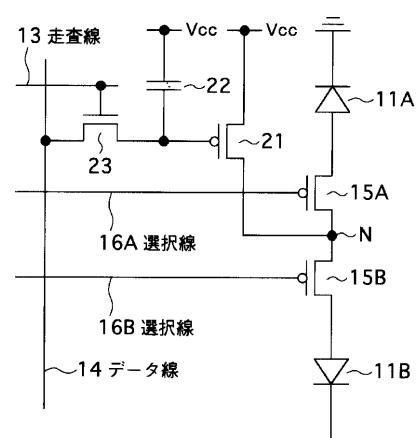

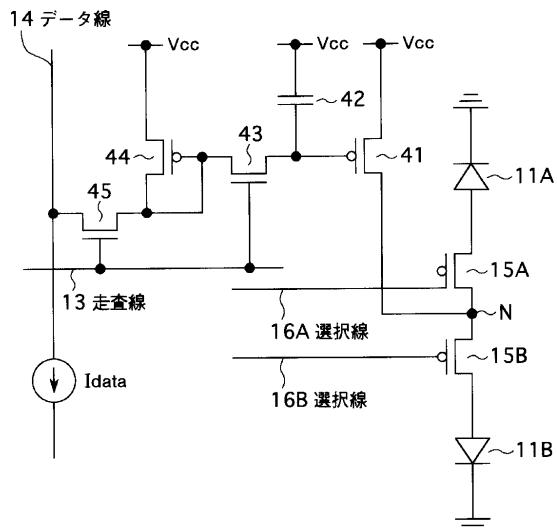

【0039】(第1回路例)次に、画素回路12の具体的な回路構成について説明する。図2は、画素回路12の第1回路例を示す回路図であり、図中、図1と同等部分には同一符号を付して示している。また、図2では、上下に隣り合う2画素分の回路構成を示している。

【0040】図2において、上下に隣り合う2画素分の有機EL素子11A, 11Bは、各カソードが第1の電源、例えばグランドに接続(接地)されている。有機EL素子11A, 11Bの各アノードには、選択スイッチ15A, 15Bの各一端、例えばPchのTFT15A, 15Bの各ドレインが接続されている。これらTFT15A, 15Bは、各ソースがノードNに共通に接続され、各ゲートが選択線16A(16A-1~16A-n), 16B(16B-1~16B-n)にそれぞれ接続されている。

【0041】ノードNには、例えばPchのTFT21のドレインが接続されている。TFT21のソースは、第2の電源、例えば正電源Vccに接続されている。TFT21のゲートには、キャパシタ22の一端が接続され、その他端は正電源Vccに接続されている。TFT21のゲートにはさらに、例えばNchのTFT23のドレインが接続されている。TFT23は、ソースがデータ線14(14-1~14-m)に接続され、ゲートが走査線13(13-1~13-n)に接続されている。

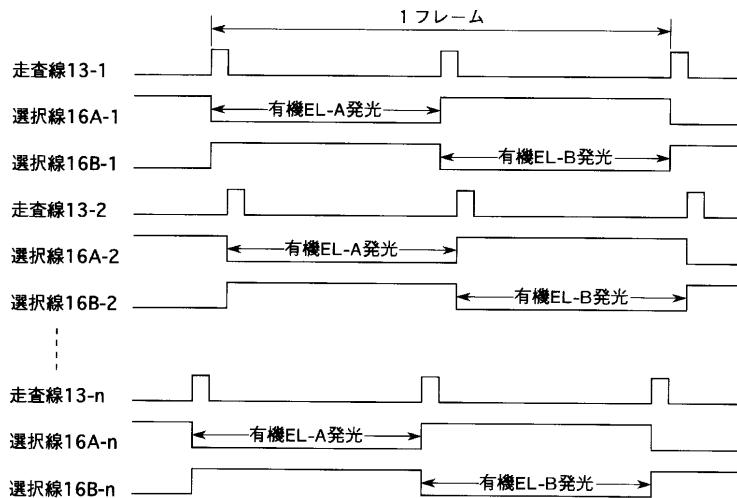

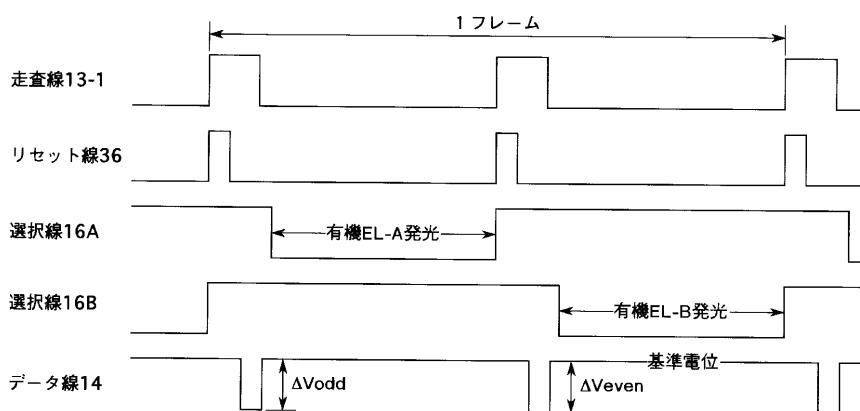

【0042】次に、上記構成の第1実施形態に係るアクティブマトリクス型表示装置、即ちアクティブマトリクス型有機EL表示装置における具体的な動作について、図3のタイミングチャートを用いて説明する。

【0043】先ず、フレームの最初に、走査線駆動回路17による駆動により、先頭の走査線である走査線13-1を選択状態(高レベル)にし、1行目の各画素回路12のTFT23をオン状態とする。これにより、データ線14-1~14-mを通して与えられる輝度データが、TFT23を介してキャパシタ22に書き込まれる。このとき、選択線駆動回路18の駆動により、選択線16A-1が選択状態(低レベル)にあり、選択線16B-1が非選択状態(高レベル)にがあるので、TFT15Aがオン状態、TFT15Bがオフ状態となる。

【0044】この状態において、TFT21は、キャパシタ22に書き込まれた輝度データに応じた電流を、オン状態にあるTFT15Aを通して有機EL素子11Aに流す。その結果、1行目の有機EL素子11Aが発光状態となり、流れる電流に応じた輝度で発光する。一方、TFT15Bがオフ状態にあるため、2行目の有機EL素子11Bには電流が流れず、当該有機EL素子11Bは消灯状態となる。

【0045】次に、走査線駆動回路17による駆動により、走査線13-2を選択する。この走査線13-2の選択時にも、走査線13-1の選択時と同様の画素回路12の回路動作により、3行目の有機EL素子11Aが発光状態となり、4行目の有機EL素子11Bが消灯状態となる。以降、同様にして、走査線13-3, ..., 13-nを選択しながら輝度データの書き込み動作を行うことにより、画面の奇数行の有機EL素子11Aが発光

する。

【0046】かかる後、走査線駆動回路17による駆動により、再び走査線13-1を選択し、1行目の各画素回路12のTFT23を介してキャパシタ22に輝度データを書き込む。このとき、選択線駆動回路18の駆動により、選択線16A-1が非選択状態にあり、選択線16B-1が選択状態にあるため、TFT15Aがオン状態、TFT15Bがオフ状態となる。これにより、キャパシタ22に書き込まれた輝度データに応じた電流が、TFT21およびTFT15Bを通して有機EL素子11Bに流れる。

【0047】その結果、2行目の有機EL素子11Bが発光状態となり、流れる電流に応じた輝度で発光する。一方、TFT15Aがオフ状態にあるため、1行目の有機EL素子11Aには電流が流れず、当該有機EL素子11Aは消灯状態となる。以降、同様にして、走査線13-2, ..., 13-nを選択しながら輝度データの書き込み動作を行うことにより、画面の偶数行の有機EL素子11Bが発光し、1フレーム分の輝度データの書き込みが完了する。

【0048】上述したように、輝度情報に応じた電流を有機EL素子11A, 11Bに流す画素回路12として、2個のTFT21, 23および1個のキャパシタ22からなる画素回路を用い、この画素回路12を例えば上下に隣り合う2画素間で共用するようにしたことにより、選択用のトランジスタ(TFT15A, 15B)が追加されるものの、4個のTFT15A, 15B, 21, 23および1個のキャパシタ22で2画素分の画素回路を構成できる。

【0049】すなわち、当該画素回路12を各画素毎に配した場合には、2画素分で4個のTFTおよび2個のキャパシタが必要となるのに比べて、大きな面積を占有しがちなキャパシタを1個削減できる。したがって、その分だけ製造歩留まりを向上できる。また、キャパシタを1個削減できる分だけ画素面積を縮小できるため、画素ピッチを狭くすることが可能となり、ディスプレイの高解像度化、高精細化が図れる。

【0050】とりわけ、奇数行の画素全体への輝度データの書き込みと、偶数行の画素全体への輝度データの書き込みとを交互に行う駆動方式を探っているため、画像信号がインターレース(飛び越し)走査方式に対応したものである場合には、この画像信号をそのまま用いて表示駆動を行うことが可能であるとともに、なんら表示品位の低下を来すことなく、インターレース走査対応の画像信号の表示に特に有用なものとなる。

【0051】一方、画像信号がプログレッシブ(順次)走査方式に対応したものである場合は、外部に画像メモリを用意しておき、1フレームの前半において例えば偶数行の輝度データを画像メモリに一時的に格納する一方、奇数行の輝度データを先に書き込み、後半に偶数行

の輝度データを画像メモリから読み出して書き込むという駆動方法を探るようにすれば良い。

【0052】あるいは、フレーム周波数が標準的な60Hz程度の値であれば、あるフレームでは偶数行のみ、次のフレームでは奇数行のみというように交互に書き込みを行えばフリッカーを生ずることがないので、実用的な画質を得つつ駆動周波数を半減することができる。この場合、動画の解像度は低下するが、静止画については2n行×m列分の解像度を持った画像を得ることができる。

【0053】[第1実施形態の変形例]図4は、本発明の第1実施形態の変形例に係るアクティブマトリクス型表示装置の構成を示すブロック図であり、図中、図1と同等部分には同一符号を付して示している。

【0054】第1実施形態に係るアクティブマトリクス型表示装置では、2系統(A, B)の有機EL素子11A, 11Bを行毎に交互に配置した画素配列を探っているのに対して、本変形例に係るアクティブマトリクス型表示装置では、2系統の有機EL素子11A, 11Bについて、行毎および列毎に交互に配置したいわゆる市松模様の画素配列を探っている点で相違しており、それ以外の基本的な構成については同じである。市松模様の画素配列を実現するために、2系統の選択線16A(16A-1~16A-n), 16B(16B-1~16B-n)が各行において例えれば1画素毎にクロスする配線構造が採られている。

【0055】これにより、第1のデータ線(奇数列のデータ線14-1, 14-3, ..., 14-m-1)上の画素において、奇数行の画素全体への輝度データの書き込みと、偶数行の画素全体への輝度データの書き込みとが交互に行われる一方、第1のデータ線上の奇数行の画素に輝度データの書き込みが行われる間、これに隣接する第2のデータ線(奇数列のデータ線14-2, 14-4, ..., 14-m)上の偶数行の画素に対して輝度データの書き込みが行われ、第1のデータ線上の偶数行の画素に輝度情報の書き込みが行われる間、第2のデータ線上の奇数行の画素に対して輝度データの書き込みが行われる。

【0056】その結果、選択線駆動回路18から1番目の選択パルスが出力されると、1行目における1列目、3列目、...、m-1列目の有機EL素子11Aと、2行目における2列目、4列目、...、m列目の有機EL素子11Aとが発光し、次いで選択線駆動回路18から2番目の選択パルスが出力されると、2行目における1列目、3列目、...、m-1列目の有機EL素子11Bと、1行目における2列目、4列目、...、m列目の有機EL素子11Bとが発光し、...という具合に、垂直走査に同期して走査線上の左右に隣接する2画素のうちの一方が発光するように駆動が行われる。

【0057】第1実施形態に係るアクティブマトリクス

型表示装置では、先ず全画面の奇数行の画素全体への書き込みを行い、その後偶数行の画素全体への書き込みを行いうインターレース走査方式であり、先述したように、フレーム周波数が60Hz程度であればフリッカーが生じない。しかしながら、60Hzのフレーム周波数で全画素をプログレッシブ走査する場合に比べると、視覚的に走査線が目立ち易いという欠点がある。これは、画素が走査線単位で点灯(発光)および消灯を繰り返していることに起因するものである。

10 【0058】これに対して、本変形例に係るアクティブマトリクス型表示装置では、垂直走査に同期して走査線上の左右に隣接する2画素のうちの一方が発光するよう駆動を行うようとしているため、視覚的に走査線が目立ちにくくなる。なお、図4では簡単のため、単色の表示装置を模しているが、カラー表示装置の場合には、各色毎に図4の構成を探るようにすれば良い。

【0059】なお、上記実施形態およびその変形例では、1つの画素回路12を上下に隣り合う2画素間で共用するとしたが、これに限られるものではなく、3画素以上の画素間で共用するよう拡張することも可能なことは明らかである。ただし、多くの画素で1つの画素回路12を共用するようにした場合は、一つ一つの有機EL素子の発光時間が短くなるので、同じ時間平均輝度をするためには、有機EL素子のピーク輝度を高くする必要がある。

【0060】また、上記実施形態およびその変形例では、画素の表示素子として、有機EL素子を用いたアクティブマトリクス型有機EL表示装置に適用した場合を例に探って説明したが、本発明はこれに限定されるものではなく、流れる電流によって輝度が変化する電気光学素子を表示素子として用いたアクティブマトリクス型表示装置全般に適用し得るものである。

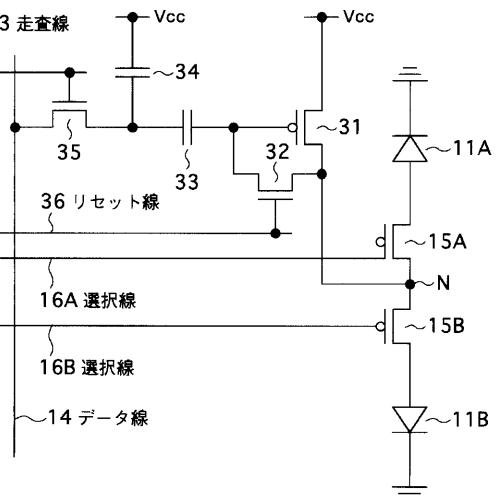

【0061】(第2回路例)図5は、画素回路12の第2回路例を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。また、図5でも、上下に隣り合う2画素分の回路構成を示している。

【0062】図5において、上下に隣り合う2画素分の有機EL素子11A, 11Bは、各カソードが接地されている。有機EL素子11A, 11Bの各アノードには、選択スイッチ15A, 15Bの各一端、例えはPchのTFT15A, 15Bの各ドレインが接続されている。これらTFT15A, 15Bは、各ソースがノードNに共通に接続され、各ゲートが選択線16A(16A-1~16A-n), 16B(16B-1~16B-n)にそれぞれ接続されている。

【0063】ノードNには、例えはPchのTFT31のドレインが接続されている。TFT31のソースは正電源Vccに接続されている。TFT31のゲートとドレインとの間には、例えはNchのTFT32が接続されている。TFT32のゲートは、リセット線36に接

続されている。TFT31のゲートには、キャパシタ3の一端が接続されている。キャパシタ33の他端と正電源Vccとの間にはキャパシタ34が接続されている。キャパシタ33の他端にはさらに、例えばNchのTFT35のドレインが接続されている。TFT35は、ソースがデータ線14(14-1~14-m)に接続され、ゲートが走査線13(13-1~13-n)に接続されている。

【0064】上記構成の第2回路例に係る画素回路は、その基本的な機能については、従来例1として挙げた図10の画素回路と同様であるが、本例では、例えば上下に隣り合う2画素間で共用化されている点が特徴となっている。すなわち、第2回路例に係る画素回路を、第1回路例に係る画素回路と同様に、図1あるいは図4に示す如くマトリクス状に配置すれば、アクティブマトリクス型有機EL表示装置を構成することができる。なお、リセット線36については、走査線13や選択線16A, 16Bと同様に、2行毎に1本ずつ配線されることになる。

【0065】ここで、その具体的な動作について、図6のタイミングチャートを用いて説明する。

【0066】先ず、選択線16Aを非選択状態(高レベル)、選択線16Bを選択状態(低レベル)とした状態において、走査線13およびリセット線36を選択状態(共に高レベル)とし、スイッチ用TFT32によって駆動用TFT31のゲート・ドレイン間を短絡する。次いで、選択線16Bを非選択状態(高レベル)とすると、TFT15Bがオフ状態となることにより、図10の画素回路の場合と同様にリセット動作が行われる。リセット動作が完了したら、リセット線36を非選択状態(低レベル)に戻す。

【0067】続いて、データ線14にVoddの電位変化を与え、しかる後走査線13を非選択状態(低レベル)とすることで、TFT35を通してのキャパシタ34への輝度データの書き込みが完了する。そして、選択線16Aを選択状態(低レベル)とすれば、TFT15Aがオン状態となる。このとき、選択線16Bは非選択状態のままであり、TFT15Bはオフ状態にある。

【0068】この状態において、TFT31は、キャパシタ34に書き込まれた輝度データに応じた電流を、オシロスコープ状態にあるTFT15Aを通して有機EL素子11Aに流す。その結果、有機EL素子11Aが発光状態となり、流れる電流に応じた輝度で発光する。一方、TFT15Bがオフ状態にあるため、有機EL素子11Bには電流が流れず、当該有機EL素子11Bは消灯状態となる。

【0069】その後、走査線13(13-1~13-n)を順次選択しながら輝度データの画素への書き込み動作を行うことにより、画面の奇数行の有機EL素子11Aが発光する。奇数行について輝度データの書き込み

動作が終了したら、再び最初の走査線から偶数行について輝度データの書き込み動作を行うようにすることで、画面の偶数行の有機EL素子11Bが発光し、1フレーム分の輝度データの書き込みが完了する。

【0070】上述したように、第2回路例に係る画素回路を例えれば上下に隣り合う2画素間で共用化することにより、5個のTFT15A, 15B, 31, 32, 35および2個のキャパシタ33, 34で2画素分の画素回路を構成できる。すなわち、図10の画素回路を各画素毎に配した場合は、2画素分で8個のTFTおよび4個のキャパシタが必要となるのに対して、トランジスタ3個とキャパシタ2個を削減できる。したがって、その分だけ製造歩留まりを向上できる。また、信号線についても2本削減でき、しかも大きな面積を占有しがちなキャパシタを2個削減できる分だけ画素面積を大幅に縮小できるため、画素ピッチをさらに狭くすることが可能となり、ディスプレイのさらなる高解像度化、高精細化が図れる。

【0071】(第3回路例)図7は、画素回路12の第3回路例を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。また、図7でも、上下に隣り合う2画素分の回路構成を示している。

【0072】図7において、上下に隣り合う2画素分の有機EL素子11A, 11Bは、各カソードが接地されている。有機EL素子11A, 11Bの各アノードには、選択スイッチ15A, 15Bの各一端、例えばPchのTFT15A, 15Bの各ドレインが接続されている。これらTFT15A, 15Bは、各ソースがノードNに共通に接続され、各ゲートが選択線16A(16A-1~16A-n), 16B(16B-1~16B-n)にそれぞれ接続されている。

【0073】ノードNには、例えばPchのTFT41のドレインが接続されている。TFT41のソースは正電源Vccに接続されている。TFT31のゲートと正電源42との間にはキャパシタ42が接続されている。TFT41のゲートにはさらに、例えばNchのTFT43のドレインが接続されている。TFT43のゲートは、走査線13に接続されている。TFT43のソースには、例えばPchのTFT44のゲートおよびドレインが共通に接続されている。TFT44のソースは正電源Vccに接続されている。TFT44のゲート・ドレインとデータ線14との間にはTFT45が接続されている。TFT45のゲートは走査線13に接続されている。

【0074】上記構成の第3回路例に係る画素回路は、その基本的な機能については、従来例2として挙げた図12の画素回路と同様であるが、本例では、例えば上下に隣り合う2画素間で共用化されている点が特徴となっている。すなわち、第3回路例に係る画素回路を、第1, 第2回路例に係る画素回路と同様に、図1あるいは

図4に示す如くマトリクス状に配置すれば、アクティブマトリクス型有機EL表示装置を構成することができると。

【0075】このように、第3回路例に係る画素回路を例えば上下に隣り合う2画素間で共用化することにより、6個のTFT15A, 15B, 41, 42, 44, 45および1個のキャパシタ42で2画素分の画素回路を構成できる。すなわち、図12の画素回路を各画素毎に配した場合は、2画素分で8個のTFTおよび1個のキャパシタが必要となるのに対して、トランジスタ2個とキャパシタ1個を削減できる。したがって、その分だけ製造歩留まりを向上できる。また、大きな面積を占有しがちなキャパシタを1個削減できる分だけ画素面積を縮小できるため、画素ピッチを狭くすることが可能となり、ディスプレイの高解像度化、高精細化が図れる。

【0076】

【発明の効果】以上説明したように、本発明によれば、画素回路を複数の画素間で時分割的に共用することにより、1画素当たりの画素回路の素子数を削減できる。特に、TFTの特性ばらつきの補償機能を有するために、複雑な回路構成の画素回路を使用するような場合には、当該画素回路を複数の画素間で共用することにより、1画素当たりのトランジスタ数やキャパシタ数を効果的に削減することが可能であるため、製造歩留まりを向上させることが可能であるとともに、高精細のディスプレイの実現が容易になる。

【図面の簡単な説明】

【図1】本発明の第1実施形態に係るアクティブマトリ

クス型表示装置の構成例を示すブロック図である。

【図2】画素回路の第1回路例を示す回路図である。

【図3】第1回路例に係る画素回路の回路動作のタイミングチャートである。

【図4】第1実施形態の変形例に係るアクティブマトリクス型表示装置の構成例を示すブロック図である。

【図5】画素回路の第2回路例を示す回路図である。

【図6】第2回路例に係る画素回路の回路動作のタイミングチャートである。

【図7】画素回路の第3回路例を示す回路図である。

【図8】電圧書き込み型の基本的な画素回路の回路構成を示す回路図である。

【図9】アクティブマトリクス型表示装置の構成例を示すブロック図である。

【図10】従来例1に係る画素回路を示す回路図である。

【図11】従来例1に係る画素回路の回路動作のタイミングチャートである。

【図12】従来例2に係る画素回路を示す回路図である。

【符号の説明】

11A, 11B...有機EL素子、12...画素回路、13, 13-1~13-n...走査線、14, 14-1~14-m...データ線、15A, 15B...選択スイッチ、16A, 16A-1~16A-n, 16B, 16B-1~16B-n...選択線、17...走査線駆動回路、18...選択線駆動回路、19...データ線駆動回路

【図1】

【図2】

【図3】

【図5】

【図4】

【図8】

【図6】

【図10】

【図7】

【図9】

【図11】

【図12】

フロントページの続き

(51) Int.CI.<sup>7</sup> 識別記号

G 0 9 G 3/20 6 2 4

H 0 5 B 33/14 6 4 1

F I

G 0 9 G 3/20

H 0 5 B 33/14

テ-マコ-ド<sup>®</sup> (参考)

6 2 4 B

6 4 1 D

A

F ターム(参考) 3K007 AB02 AB06 AB17 AB18 BA06

BB07 DB03 EB00 GA04

5C080 AA06 BB05 DD05 DD22 DD27

EE28 FF11 JJ02 JJ03 JJ04

5C094 AA05 AA07 AA15 AA43 AA44

AA45 AA51 AA55 BA03 BA27

CA19 DA09 DA13 DB01 DB04

EA04 FB01 FB20 GA10

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵型显示装置和有源矩阵型有机电致发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2003122306A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2003-04-25 |

| 申请号            | JP2001312322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2001-10-10 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 湯本昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 湯本 昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/20 G09G3/30 H01L27/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.K G09F9/30.338 G09F9/30.365.Z G09G3/20.611.H G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09F9/30.365 G09G3/20.641.E G09G3/3241 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB06 3K007/AB17 3K007/AB18 3K007/BA06 3K007/BB07 3K007/DB03 3K007/EB00 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/DD27 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C094/AA05 5C094/AA07 5C094/AA15 5C094/AA43 5C094/AA44 5C094/AA45 5C094/AA51 5C094/AA55 5C094/BA03 5C094/BA27 5C094/CA19 5C094/DA09 5C094/DA13 5C094/DB01 5C094/DB04 5C094/EA04 5C094/FB01 5C094/FB20 5C094/GA10 3K107/AA01 3K107/BB01 3K107/CC35 3K107/CC43 3K107/CC45 3K107/EE03 3K107/HH00 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB31 5C380/AB32 5C380/AB41 5C380/AB45 5C380/BA06 5C380/BA13 5C380/BA14 5C380/BA29 5C380/BA38 5C380/BA39 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CA45 5C380/CA53 5C380/CB01 5C380/CB05 5C380/CB25 5C380/CB26 5C380/CB37 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC07 5C380/CC14 5C380/CC26 5C380/CC33 5C380/CC34 5C380/CC39 5C380/CC54 5C380/CC58 5C380/CC62 5C380/CC64 5C380/CC77 5C380/CD012 5C380/CD016 5C380/CD024 5C380/CF03 5C380/CF26 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA16 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

解决的问题：与基本电压写入型像素电路相比，增加具有补偿TFT特性变化的功能的像素电路中的元件数量。在有源矩阵型有机EL显示装置中，由两个TFT 21和23以及一个电容器22组成并且使与亮度信息相对应的电流流向有机EL元件的像素电路由两个垂直相邻的像素形成。有机EL元件11A和11B共有的，并且通过利用选择TFT 15A和15B适当地选择有机EL元件11A和11B，在垂直相邻的两个像素之间时分共享像素电路。这样，减少了每个像素的像素电路的元件数量。