(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4027614号

(P4027614)

(45) 発行日 平成19年12月26日(2007.12.26)

(24) 登録日 平成19年10月19日(2007.10.19)

(51) Int.C1.

F 1

|             |              |                  |             |             |             |

|-------------|--------------|------------------|-------------|-------------|-------------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b> | <b>J</b>    |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>621M</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>623R</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b> | <b>624B</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b> | <b>680G</b> |

請求項の数 4 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2001-92830(P2001-92830)

(22) 出願日

平成13年3月28日(2001.3.28)

(65) 公開番号

特開2002-287697(P2002-287697A)

(43) 公開日

平成14年10月4日(2002.10.4)

審査請求日

平成15年9月12日(2003.9.12)

審判番号

不服2004-21860(P2004-21860/J1)

審判請求日

平成16年10月21日(2004.10.21)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100093506

弁理士 小野寺 洋二

(72) 発明者 佐藤 敏浩

千葉県茂原市早野3300番地 株式会社

日立製作所 ディスプレイグループ内

(72) 発明者 金子 好之

千葉県茂原市早野3300番地 株式会社

日立製作所 ディスプレイグループ内

(72) 発明者 三上 佳朗

茨城県日立市大みか町七丁目1番1号 株

式会社 日立製作所 日立研究所内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の表示領域内にマトリクス配列された複数の走査線と前記複数の走査線に交差する複数のデータ線の交差部毎に設けられた複数の画素を有し、前記画素に表示のための電流を供給する電流供給線を備え、

前記複数の画素の各々は、前記複数の走査線の一つに供給された前記走査信号でターンオンされて前記複数のデータ線の一つから供給されるデータ信号を取り込む第1のアクティブ素子と、該第1のアクティブ素子で取り込まれた該データ信号を保持するデータ保持素子と、発光素子と、該データ保持素子に保持されたデータ信号に従って前記電流供給線からの電流を前記発光素子に供給して該発光素子を発光させる第2のアクティブ素子とを有する画素回路を備え、

前記発光素子は前記第2のアクティブ素子で駆動される第1の電極層と、前記第1の電極層上に形成された有機発光層と、前記有機発光層上に形成された第2の電極層とを有し、

前記走査線への走査を開始した後、前記データ線にデータが送られる前に前記データ線及び前記データ保持素子を基準電位である初期状態に復帰させるリセット回路を有することを特徴とする表示装置。

## 【請求項 2】

前記リセット回路を前記データ駆動回路の後段、かつ前記データ線の前段に設けたことを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記リセット回路を前記データ線の終端に設けたことを特徴とする請求項1又は2に記載の表示装置。

**【請求項 4】**

前記走査駆動回路と前記データ駆動回路は、前記基板上における前記表示領域の外側で、かつ前記基板の隣接する2辺のそれぞれに配置されていることを特徴とする請求項1乃至3の何れかに記載の表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、アクティブ・マトリクス型表示装置に係り、特に有機半導体膜などの発光層に電流を流すことによって発光させるEL(エレクトロルミネッセンス)素子またはLED(発光ダイオード)素子等の発光素子で構成した画素と、この画素の発光動作を制御する画素回路を備えた表示装置に関する。 10

**【0002】****【従来の技術】**

近年、高度情報化社会の到来に伴い、パソコンコンピュータ、カーナビ、携帯情報端末、情報通信機器あるいはこれらの複合製品の需要が増大している。これらの製品の表示手段には、薄型、軽量、低消費電力のディスプレイデバイスが適しており、液晶表示装置あるいは自発光型のEL素子またはLEDなどの電気光学素子を用いた表示装置が用いられている。 20

**【0003】**

後者の自発光型の電気光学素子を用いた表示装置は、視認性がよいこと、広い視角特性を有すること、高速応答で動画表示に適していることなどの特徴があり、映像表示には特に好適と考えられている。

**【0004】**

特に、近年の有機物を発光層とする有機EL素子(有機LED素子とも言う:以下OLEDと略称する場合もある)を用いたディスプレイは発光効率の急速な向上と映像通信を可能にするネットワーク技術の進展とが相まって、OLEDディスプレイへの期待が高い。 OLEDは有機発光層を2枚の電極で挟んだダイオード構造を有する。 30

**【0005】**

このようなOLED素子を用いて構成したOLEDディスプレイにおける電力効率を高めるためには、後述するように、薄膜トランジスタ(以下、TFTとも称する)を画素のスイッチング素子としたアクティブ・マトリクス駆動が有効である。

**【0006】**

OLEDディスプレイをアクティブ・マトリクス構造で駆動する技術としては、例えば、特開平4-328791号公報、特開平8-241048号公報、あるいは米国特許第5550066号明細書などに記載されており、また、駆動電圧関係については国際特許公報WO98/36407号などに開示されている。

**【0007】**

OLEDディスプレイの典型的な画素構造は、第1と第2のアクティブ素子である2つの薄膜トランジスタTFT(第1のTFTはスイッチングトランジスタ、第2のTFTはドライバトランジスタ)と1つのコンデンサ(蓄積容量:データ信号保持素子)で構成される画素駆動回路(以下、画素回路とも言う)からなり、この画素回路によりOLEDの発光輝度を制御する。画素はデータ信号(または、画像信号)が供給されるM本のデータ線と、走査信号が供給されるN本の走査線(以下、ゲート線とも言う)をN行×M列のマトリクスに配列した各交差部に配置される。 40

**【0008】**

画素の駆動には、m行のゲート線に順次走査信号(ゲート信号)を供給してスイッチングトランジスタを導通状態に(ターンオン)し、1フレーム期間Tf内に垂直方向の走査を 50

1回終えて、再び最初（1行目）のゲート線にターンオン電圧を供給する。

#### 【0009】

この駆動方式では、1本のゲート線にターンオン電圧が供給される時間は  $T_f / N$  以下となる。一般的には、1フレーム期間  $T_f$  の値としては  $1 / 60$  秒程度が用いられる。なお、1フレームを2フィールドで表示する場合は、1フィールド期間は1フレーム期間の  $1 / 2$  となる。

#### 【0010】

あるゲート線にターンオン電圧が供給されている間は、そのデータ線に接続されたスイッチングトランジスタは全て導通状態（オン状態）となり、それに同期してM列のデータ線に同時に、または順次にデータ電圧（画像電圧）が供給される。これはアクティブ・マトリクス液晶装置で一般的に用いられているものである。10

#### 【0011】

データ電圧はゲート線にターンオン電圧（以下、ターンオンを単にオンとも称する。同様に、ターンオフも単にオフとも称する）が供給されている間に蓄積容量（コンデンサ）に蓄えられ（保持され）、1フレーム期間（もしくは、1フィールド期間、以下同様）はほぼそれらの値に保たれる。蓄積容量の電圧値は、ドライバトランジスタのゲート電圧を規定する。

#### 【0012】

したがって、ドライバトランジスタを流れる電流値が制御されてOLEDの発光が制御される。OLEDに電圧が印加されて、その発光が始まるまでの応答時間は  $1 \mu s$  以下であることが通常であり、動きの早い画像（動画像）にも追随できる。ドライバトランジスタに電流を供給するために、電流供給線が設けられており、蓄積容量に保持されたデータ信号に応じた表示用の電流が電流供給線から供給される。20

#### 【0013】

ところで、アクティブ・マトリクス駆動では、1フレーム期間にわたって発光が行われることで高効率を実現している。TFTを設げずに、OLEDのダイオード電極をそれぞれ走査線、データ線に直結して駆動する単純マトリクス駆動と比較すると、その差異は明確である。

#### 【0014】

単純マトリクス駆動では、走査線が選択されている期間にのみOLEDに電流が流れるので、その短い期間の発光のみで1フレーム期間の発光と同等の輝度を得るために、アクティブ・マトリクス駆動に比べて略走査線数倍の発光輝度が必要となる。それには、必然的に駆動電圧、駆動電流を大きくしなければならず、発熱などの消費電力の損失が大きくなつて電力効率が低下する。30

#### 【0015】

このように、アクティブ・マトリクス駆動は、単純マトリクス駆動に比べて消費電力の低減の観点から優位であると考えられる。

#### 【0016】

##### 【発明が解決しようとする課題】

上記した単純マトリクス型の表示装置では、基板上の表示領域に交差配置した走査線とデータ線をそのまま当該表示領域の外部に引き出して駆動回路に接続し、駆動回路を外部回路と接続するための端子パッドを設けている。しかし、このような端子構成をアクティブ・マトリクス型の表示装置にそのまま適用することは困難である。40

#### 【0017】

OLEDのアクティブ・マトリクス駆動では、1フレーム期間にわたって表示を保持するためのコンデンサへの電荷供給を、当該コンデンサの一方の電極をスイッチングトランジスタの出力端子に接続し、他方の電極をコンデンサ用の共通電位線に接続したり、あるいはOLEDに電流を供給する電流供給線に接続している。

#### 【0018】

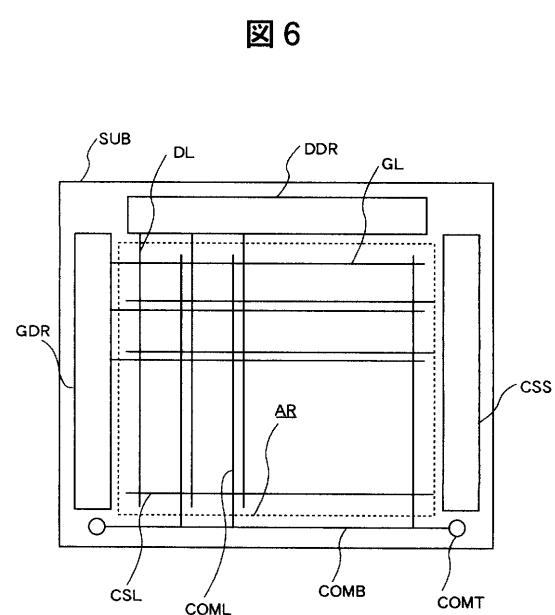

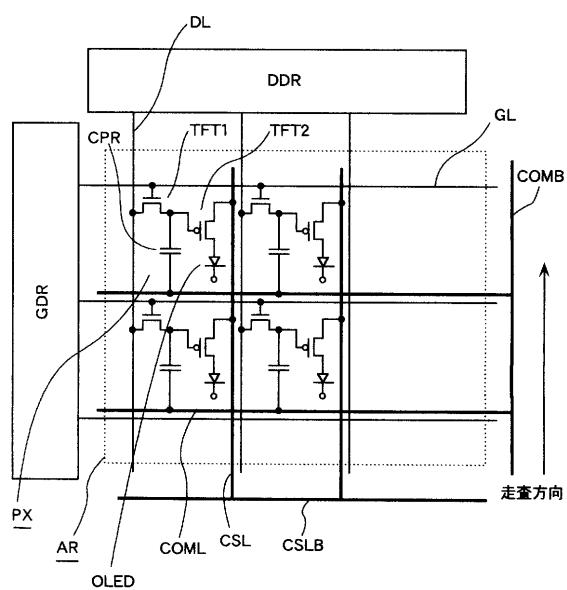

図6はOLEDを用いた従来の表示装置の1構成例を模式的に説明するブロック図、図750

は図 6 における画素構成の説明図である。この表示装置（画像表示装置）は、ガラス等の絶縁材からなる基板 S U B 上に複数のデータ線 D L と複数のゲート線 G L とのマトリクス配列で形成した表示部 A R (図中、点線で囲った内部) の周囲にデータ駆動回路 D D R 、走査駆動回路 G D R 、電流供給回路 C S S を配置して構成されている。

#### 【 0 0 1 9 】

データ駆動回路 D D R は N チャンネル型と P チャンネル型の薄膜トランジスタ T F T による相補型回路、または N チャンネルのみか P チャンネルのみの单チャンネル型の薄膜トランジスタ T F T で構成されるシフトレジスタ回路、レベルシフタ回路、アナログスイッチ回路などからなる。なお、電流供給回路 C S S はバスラインのみとし、外部電源から供給するようにも構成できる。

10

#### 【 0 0 2 0 】

図 6 は表示部 A R にコンデンサ用の共通電位線 C O M L を設けた方式であり、コンデンサの前記他端の電極は、この共通電位線 C O M L に接続される。共通電位線 C O M L は共通電位供給バスライン C O M B の端子 C O M T から外部の共通電位源に引き出されている。なお、共通電位線 C O M L を設けず、コンデンサを電流供給線に接続した方式も既知である。

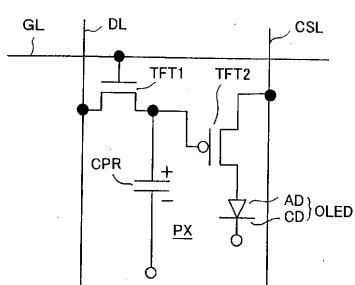

#### 【 0 0 2 1 】

図 7 に示したように、画素 P X はデータ線 D L とゲート線 G L で囲まれた領域に配置されたスイッチングトランジスタである第 1 の薄膜トランジスタ T F T 1 、ドライバトランジスタである第 2 の薄膜トランジスタ T F T 2 、コンデンサ C P R 、および有機発光素子 O L E D で構成される。

20

#### 【 0 0 2 2 】

薄膜トランジスタ T F T 1 のゲートはゲート線 G L に、ドレインはデータ線 D L に接続されている。薄膜トランジスタ T F T 2 のゲートは薄膜トランジスタ T F T 1 のソースに接続され、この接続点にコンデンサ C P R の一方の電極 (+ 極) が接続されている。

#### 【 0 0 2 3 】

図 8 は図 7 の画素構成をもつ図 6 の表示装置の構成をさらに説明するブロック図である。薄膜トランジスタ T F T 2 のドレインは電流供給線 C S L に、ソースは有機発光素子 O L E D の第 1 の電極層（ここでは陽極）A D に接続されている。そして、コンデンサ C P R の他端（- 極）は共通電位線バスライン C O M B から分岐した共通電位線 C O M L に接続されている。

30

#### 【 0 0 2 4 】

データ線 D L はデータ駆動回路 D D R で駆動され、走査線（ゲート線）G L は走査駆動回路 G D R で駆動される。また、電流供給線 C S L は電流供給バスライン C S L B を介して図 8 の電流供給回路 C S S あるいは端子を介して外部電流源に接続している。

#### 【 0 0 2 5 】

図 7 と図 8 において、1 つの画素 P X が走査線 G L で選択されると、データ線 D L から供給される画像信号がコンデンサ C P R に蓄積される。そして、薄膜トランジスタ T F T 1 がターンオフした時点で薄膜トランジスタ T F T 2 がターンオンし、電流供給線 C S L からの電流が有機発光素子 O L E D に流れ、ほぼ 1 フレーム期間にわたってこの電流が持続する。このとき流れる電流はコンデンサ C P R に蓄積されている信号電荷で規定される。

40

#### 【 0 0 2 6 】

コンデンサ C P R の動作レベルは共通電位線 C O M L の電位で規定される。これにより、画素の発光が制御される。有機発光素子 O L E D から流れ出る電流は第 2 の電極層（ここでは陰極）C D から図示しない電流引抜き線に流れる。

#### 【 0 0 2 7 】

この方式では、画素領域の一部を貫通して共通電位線 C O M L を設ける必要があるため、所謂開口率の低下をもたらし、表示装置全体としての明るさ向上を抑制してしまう。

#### 【 0 0 2 8 】

50

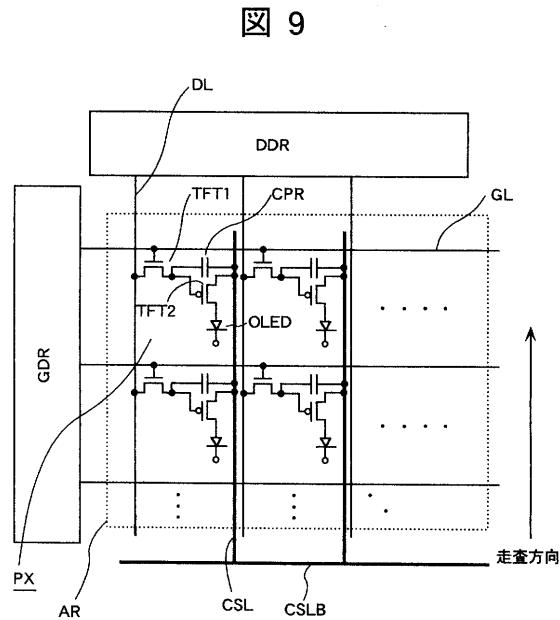

図9はOLEDを用いた従来の表示装置の他の構成例を模式的に説明する図8と同様のブロック図である。この例では、各画素を構成する薄膜トランジスタTFT1、TFT2およびコンデンサCPRの基本配列は図8と同様であるが、コンデンサCPRの他端を電流供給線CSLに接続した点で異なる。

#### 【0029】

すなわち、1つの画素PXが走査線GLで選択されて薄膜トランジスタTFT1がターンオンすると、データ線DLから供給される画像信号がコンデンサCPRに蓄積され、薄膜トランジスタTFT1がターンオフした時点で薄膜トランジスタTFT2がターンオンしたとき、電流供給線CSLからの電流が有機発光素子OLEDに流れ、図8と同様に、ほぼ1フレーム期間（または、1フィールド期間）にわたってこの電流が持続する。このとき流れる電流はコンデンサCPRに蓄積されている信号電荷で規定される。コンデンサCPRの動作レベルは電流供給線CSLの電位で規定される。これにより、画素の発光が制御される。

10

#### 【0030】

図6～図9で説明したこの種の表示装置においては、有機発光素子OLEDの第1の電極層ADとなる薄膜トランジスタTFT2のソース電極はITO（インジウム・チン・オキサイド）等の導電性薄膜で形成され、かつ各画素PXの第1の電極層ADは個別に分離されている。

#### 【0031】

また、発光素子を構成する第2の電極層CDは素子の最上層に位置するため、直接外気に触れて腐食が生じる恐れがある。通常、第2の電極層は全画素について供給のべた膜に形成されているため、外部との接続をとるために下層の配線（第2の電極層接続電極層：電流引出し電極とも言う）に電気的に接続をとる必要がある。この第2の電極層CDへの電流供給のための端子は当該第2の電極層の延長で基板の端子部（端子パッド）に直接引き出されているため、その端子部近傍では外気との接触で腐食の発生が起こり易い。

20

#### 【0032】

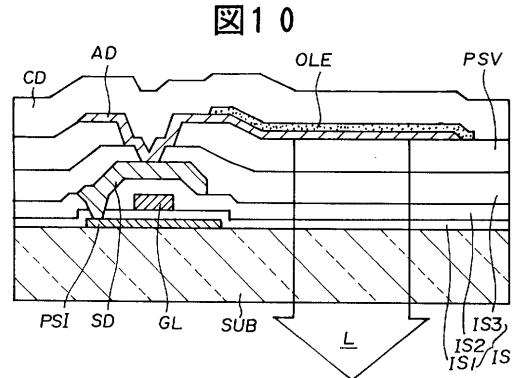

図10は有機発光素子を用いた表示装置の1画素付近の構造を説明する断面図である。この表示装置は、ガラス基板SUBの上に低温ポリシリコンを好適とするポリシリコン半導体層PSI、第1の絶縁層IS1、走査配線であるゲート配線（ゲート電極）GL、第2の絶縁層IS2、アルミニウム配線で形成したソース電極SD、第3の絶縁層IS3、保護膜PSV、第1の電極層AD、有機発光層OLE、第2の電極層CDを積み上げて構成される。

30

#### 【0033】

ポリシリコン半導体層PSIとゲート配線GL、ソース電極SDで構成される薄膜トランジスタ（この薄膜トランジスタはドライバトランジスタ）が選択されると、ソース電極SDに接続した第1の電極層ADと有機発光層OLEおよび第2の電極層CDで形成される有機発光素子が発光し、その光Lが基板SUB側から外部に出射する。

#### 【0034】

この種の表示装置における走査駆動回路は、複数の走査線に順次走査信号を供給し、この走査信号で選択された走査線に接続した画素回路にデータ駆動回路からのデータ信号を書き込む。前記したように、画素回路は2つの薄膜トランジスタとデータ保持素子であるコンデンサおよび有機発光素子を備えている。データ駆動回路からのデータ信号は画素回路を構成する第1の薄膜トランジスタのターンオンでデータ保持素子であるコンデンサに当該データ信号の階調に応じた電荷量として保持される。

40

#### 【0035】

そして、第1の薄膜トランジスタのターンオフでターンオンする第2の薄膜トランジスタを介して電流供給線からの電流をコンデンサに保持されたデータ信号の階調に応じた大きさに従って有機発光素子に流し、これを発光させる。

#### 【0036】

走査駆動回路で選択された走査線の1行分の走査を終えた後、次の行の走査線を選択する

50

。これを繰り返して垂直方向の走査を順に行い、最終行に至ると所定の垂直プランキング期間の後、先頭の走査線（最初の行）に戻り、再び上記の動作を繰り返す。

#### 【0037】

選択された行の走査線に接続した各画素のコンデンサに書き込まれたデータ信号に対応する電荷は、次にその行の走査がなされるまで、その電荷を保持する。しかし、次にデータ信号が書き込まれるまでに当該コンデンサの電荷が残留すると、次に新しいデータ信号が書き込まれる際に、コンデンサに残留している以前のデータ信号の電荷成分が新しいデータ信号に対応する電荷量に影響を及ぼす。その結果、階調が不安定になって、表示品質を劣化させる。

#### 【0038】

また、画素内のコンデンサだけでなく、データ線と第2の電極層との間の容量やデータ線と走査線の間の容量によるデータ線の電荷も影響を及ぼす。

#### 【0039】

このようなデータ信号の書き込みの動作を安定化させるため、駆動能力の大きなバッファ回路を設けることも可能であるが、回路規模が大きくなり、表示装置の素子面積の増大をまねく。決められた基板サイズで、その周辺に駆動回路を搭載するものでは、額縁が広くなつて有効表示領域が狭小となる。

#### 【0040】

本発明の目的は、上記した画素回路のコンデンサに残留する前の（その行を前回走査したときの）データ信号の残留電荷による影響を回避し、高品質の表示を可能とした表示装置を提供することにある。

#### 【0041】

##### 【課題を解決するための手段】

上記目的を達成するため、本発明は、データ駆動回路の出力線であるデータ線に、1つ前の走査線の走査終了後、次の走査線に対応する画素に対するデータが送られる前にその画素回路にデータ信号を供給したデータ線を初期状態に復帰させるリセット回路を設けた。

#### 【0042】

この構成としたことにより、新しく書き込まれるデータ信号が前のデータ信号に影響されることなく、高品質の表示装置が得られる。また、リセット回路は単純なスイッチであることで、基板上の占有面積は極めて少なく、有効表示領域を狭小化することがない。本発明のより具体的な構成例を記述すると以下のとおりである。すなわち、

(1)、基板上の表示領域内にマトリクス配列された複数の走査線GLと前記複数の走査線に交差する複数のデータ線DLの交差部毎に設けられた複数の画素PXを有し、前記画素に表示のための電流を供給する電流供給線CSLを備え、且つ

前記複数の画素PXの各々には、前記複数の走査線の一つGL(n+1)に供給された前記走査信号でターンオンされて前記複数のデータ線の一つDL(m+1)から供給されるデータ信号を取り込む第1のアクティブ素子TFT1と、該第1のアクティブ素子TFT1で取り込まれた該データ信号を保持するデータ保持素子CPRと、発光素子OLEDと、該データ保持素子CPRに保持されたデータ信号に従って前記電流供給線CSLからの電流を前記発光素子OLEDに供給して該発光素子OLEDを発光させる第2のアクティブ素子TFT2とを有する画素回路が備えられ、

前記発光素子OLEDは前記第2のアクティブ素子TFT2で駆動される第1の電極層ADと、前記第1の電極層AD上に形成された有機発光層OLEと、前記有機発光層OLE上に形成された第2の電極層CDとで構成される表示装置において、

前記一つの走査線GL(n+1)の1つ前の前記走査線GL(n)が走査された後、前記データ線DL(m+1)にデータが送られる前に前記データ線DL(m+1)を初期状態に復帰させるリセット回路RSTを設ける。

#### 【0045】

(2)、(1)において、前記リセット回路RSTは、次の前記走査線GL(n+1)への走査を開始した後、前記データ線にDL(m+1)データが送られる前に前記データ保持素子CPRを初期

状態に復帰させる。

【0046】

(3)、(1)及び(2)の何れかにおいて、前記リセット回路RSTは、前記走査線GLへの走査毎に前記初期状態への復帰を行う。

【0047】

(4)、(1)～(3)の何れかにおいて、前記リセット回路RSTを、前記データ駆動回路DDRの後段、かつ前記データ線DLの前段に設けた。

【0048】

(5)、(1)～(3)の何れかにおいて、前記リセット回路RSTを、前記データ線DLの終端に設けた。 10

【0049】

(6)、(1)～(5)の何れかにおいて、前記走査駆動回路GDRと前記データ駆動回路DDRを、前記基板SUB上における前記表示領域ARの外側で、かつ前記基板SUBの隣接する2辺のそれぞれに配置した。

【0050】

上記(1)～(6)の構成としたことにより、新しく書き込まれるデータ信号が前のデータ信号に影響されることなく、高品質の表示装置が得られると共に、有効表示領域の面積を狭小化することのない表示装置を提供できる。

【0051】

なお、本発明は上記の構成および後述する実施例の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変更が可能であることは言うまでもない。本発明の他の目的および構成は後述する実施の形態の記載から明らかになるであろう。 20

【0052】

**【発明の実施の形態】**

以下、本発明の実施の形態につき、実施例の図面を参照して詳細に説明する。図示しないが、以降で説明する各画素に有する有機発光層はほぼ電流値に比例した輝度で、かつその有機材料に依存した色（白色も含む）で発光させてモノクロあるいはカラー表示を行わせるものと、白色発光の有機層に赤、緑、青等のカラーフィルタを組み合わせてカラー表示を行わせるもの等がある。

【0053】

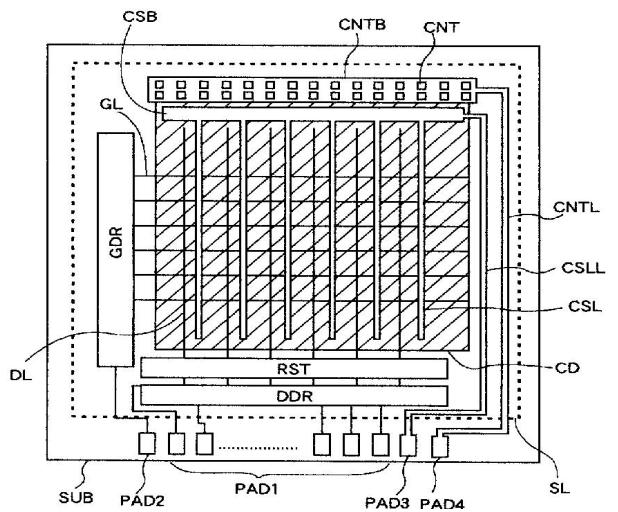

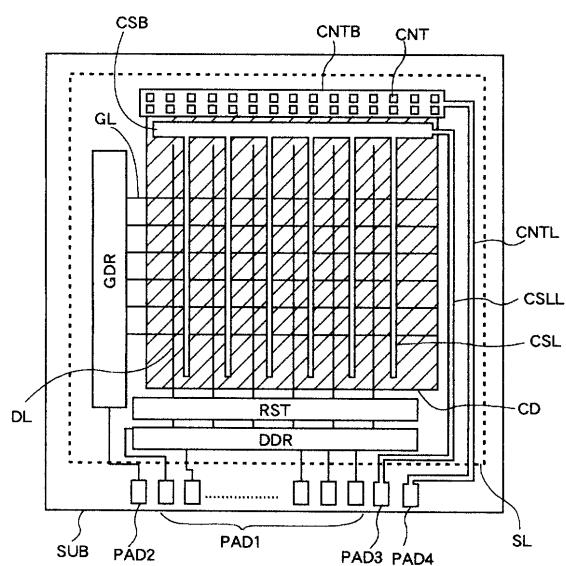

図1は本発明による表示装置の第1実施例の構成を模式的に説明するブロック図である。本実施例の表示装置は、ガラス基板SUB上に走査駆動回路GDRとデータ駆動回路DDRを有する。

【0054】

マトリクスに形成された走査駆動回路GDRで駆動される（走査される）走査線GL、データ駆動回路DDRで駆動されるデータ線GL、所謂陽極配線である電流供給線C<sub>SL</sub>で囲まれた領域に1画素が形成される。また、基板SUBの1の辺には外部回路から走査駆動回路GDR、データ駆動回路DDRへの信号や電圧を供給するための端子パッドPAD1、PAD2が形成されている。 30

【0055】

そして、データ駆動回路DDRの後段でデータ線の前段に、走査線GLの単位走査期間（1行の走査期間）に、1つ前の走査線の走査終了後、次の行へのデータ送出の開始前にデータ線又は前記画素回路内のコンデンサのうち、少なくとも一方を初期状態に復帰させるリセット回路RSTを設けている。先ず、本実施例の画素回路の構成と、その動作について説明する。 40

【0056】

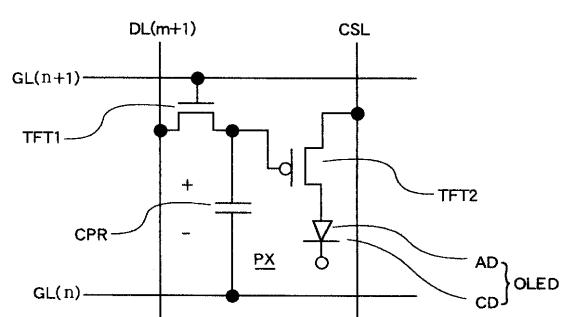

図2は図1における1画素の画素回路の構成図である。本実施例の概略構成は次のとおりである。すなわち、1画素はデータ線DL（ $m + 1$ ）と走査線GL（ $n + 1$ ）、GL（ $n$ ）および電流供給線C<sub>SL</sub>で囲まれた領域に形成される。ここでは、現在走査されている（選択されている）走査線をGL（ $n + 1$ ）として説明する。

## 【0057】

走査線 G L ( n + 1 ) で選択されている複数の画素のうち、画素 P X に着目する。アクティブ素子である第 1 の薄膜トランジスタ T F T 1 はスイッチングトランジスタ、第 2 の薄膜トランジスタ T F T 2 はドライバトランジスタである。第 1 の薄膜トランジスタ T F T 1 のゲートは走査線 G L ( n + 1 ) に接続され、そのドレインはデータ線 D L ( m + 1 ) に、ソースは第 2 薄膜トランジスタ T F T 2 のゲートに接続されている。

## 【0058】

第 2 の薄膜トランジスタ T F T 2 のドレインは図 1 に示した電流供給線バスライン C S B から電流が供給される電流供給線 C S L に接続されている。そして、そのソースは O L E D の第 1 の電極層（ここでは陽極）A D に接続されている。第 1 の薄膜トランジスタ T F T 1 のソースと第 2 の薄膜トランジスタ T F T 2 のゲートの接続点にはデータ信号保持素子としてのコンデンサ C P R の一方の端子が接続され、他方の端子は直前の走査線 G L ( n ) に接続されている。10

## 【0059】

図 2 に示した 1 画素の回路構成において、第 1 の薄膜トランジスタ T F T 1 のソースと第 2 の薄膜トランジスタ T F T 2 のゲートの接続点に接続されるコンデンサ C P R の一方の端子は + 極であり、走査線 G L ( n ) に接続される他方の端子は - 極である。

## 【0060】

また、有機発光素子 O L E D は第 1 の電極層 A D と第 2 の電極層（ここでは陰極）C D の間に有機発光層（図示せず）を挟んだ構成であり、第 1 の電極層 A D は第 2 の薄膜トランジスタ T F T 2 のソース電極に接続し、第 2 の電極層 C D は全画素にわたってべた形成されて図 1 の第 2 電極接続電極層 C N T B に接続している。20

## 【0061】

この第 2 電極接続電極層 C N T B は、所謂電流引抜き配線（電極）であり、基板の下層に前記端子パッド P A D 1、P A D 2 と同層に形成されており、第 2 の電極層 C D をコンタクトホール C N T で接続し、第 2 電極接続電極引回しライン C N T L で前記端子パッド P A D 1、P A D 2 と同層に形成された端子 P A D 4 に接続されている。

## 【0062】

なお、第 1 の電極層の配線である電流供給線 C S L も電流供給線バスライン C S B と電流供給線引回しライン C S L L で前記端子パッド P A D 1、P A D 2 と同層に形成された端子 P A D 3 に接続されている。上記第 2 電極接続電極層 C N T B は電流供給線バスライン C S B よりも基板の外側、かつ点線で示した基板の封止領域 S L の内側に配置されている。30

## 【0063】

このように、第 2 の電極層 C D をコンタクトホール C N T で接続する第 2 電極接続電極層 C N T B を電流供給線バスライン C S B よりも基板 S U B の外側で、かつシール領域 S L の内側に配置したことで、フレキシブルプリント基板を介して 1 辺で外部回路と接続する方式における基板上のレイアウトが容易となる。

## 【0064】

第 1 の薄膜トランジスタ T F T 1 のターンオンでコンデンサ C P R に書き込まれ、電荷量として保持されたデータ信号は第 1 の薄膜トランジスタ T F T 1 のターンオフに伴う第 2 の薄膜トランジスタ T F T 2 のターンオンで電流供給線 C S L からの電流を当該コンデンサ C P R に保持された電荷量（データ信号の階調を示す）で制御された電流量として有機発光素子 O L E D に流す。40

## 【0065】

有機発光素子 O L E D は供給される電流量にほぼ比例した輝度で、かつ当該有機発光素子を構成する有機発光層材料に依存した色で発光する。カラー表示の場合は、通常は赤、緑、青の画素毎に有機発光層材料を変えるか、あるいは白色の有機発光層材料と各色のカラーフィルタの組合せを用いる。

## 【0066】

なお、データ信号の与え方はアナログ量でも、あるいは時分割のデジタル量でもよい。また、階調制御は、赤、緑、青の各画素の面積を分割した面積階調方式を組合せてもよい。

#### 【0067】

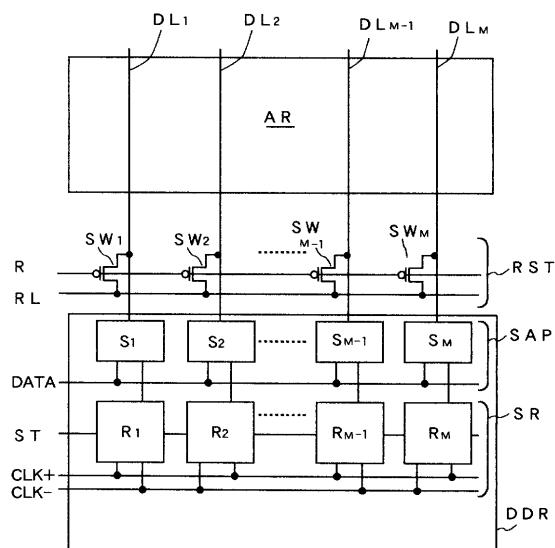

図3は本発明による表示装置の第1実施例の構成の要部を説明するブロック図である。表示領域A Rには前記図2で説明した構成の多数の画素がマトリクス状に配置されている。ここでは、データ駆動回路の部分とデータ線のみを示してある。

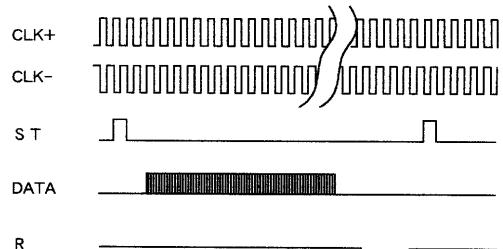

#### 【0068】

また、図4は図3の実施例の動作を説明するタイミング図である。図3と図4における同一参照符号で示した各信号は同じものである。以下、図3の構成と動作を図4のタイミング図を参照して説明する。

10

#### 【0069】

データ駆動回路D D RはシフトレジスタS Rとサンプリング回路S A Pのみを示し、詳細構成は図示を省略した。データ駆動回路D D Rは、スタートパルスS Tと画素クロック信号（以下、単にクロックと言う）C L K +とC L K -を入力し、複数のデータ線に対するデータ信号D A T Aを順次転送する1系統のシフトレジスタS Rと、シフトレジスタS Rからのデータ信号をサンプリングしてデータ線D Lに供給するサンプリング回路S A Pを備えている。

#### 【0070】

このサンプリング回路S A Pの直後で、各データ線D Lの直前にそれぞれ各データ線を所定のリセットレベル（初期電位）R Lに復帰させるためのスイッチ素子S Wを備えたリセット回路R S Tを設けている。

20

#### 【0071】

シフトレジスタS Rはデータ線毎のブロック（レジスタ）R<sub>1</sub>，R<sub>2</sub>，…，R<sub>M-1</sub>，R<sub>M</sub>で構成され、スタートパルスS Tの入力に応じ、クロックC L K +とC L K -に同期した出力を順次サンプリング回路S A Pに出力する。

#### 【0072】

サンプリング回路S A Pはデータ線D L（D L<sub>1</sub>，D L<sub>2</sub>，…，D L<sub>M-1</sub>，D L<sub>M</sub>）毎のサンプリング回路S R（S<sub>1</sub>，S<sub>2</sub>，…，S<sub>M-1</sub>，S<sub>M</sub>）を有し、データ信号D A T AをシフトレジスタS R（R<sub>1</sub>，R<sub>2</sub>，…，R<sub>M-1</sub>，R<sub>M</sub>）からの出力によりサンプリングしてデータ線D Lに供給するスイッチ動作と転送動作を行う。リセット回路R S Tは各1個のp型の薄膜トランジスタで構成したスイッチS W<sub>1</sub>，S W<sub>2</sub>，…，S W<sub>M-1</sub>，S W<sub>M</sub>から構成されている。

30

#### 【0073】

このデータ線へのデータ信号の供給時はリセット回路R S Tの全スイッチS W<sub>1</sub>，S W<sub>2</sub>，…，S W<sub>M-1</sub>，S W<sub>M</sub>はそのリセット端子にハイレベルの信号が印加されていてオフ状態になっている。したがって、サンプリング回路S<sub>1</sub>，S<sub>2</sub>，…，S<sub>M-1</sub>，S<sub>M</sub>からのデータ信号は、そのまま各データ線D L<sub>1</sub>，D L<sub>2</sub>，…，D L<sub>M-1</sub>，D L<sub>M</sub>に転送される。転送されたデータ信号は、それぞれの画素に書き込まれ、そのコンデンサに電荷として保持される。

#### 【0074】

上記した1行（1ライン）分の画素回路にデータ信号の書き込み動作が終了し、その行の走査線の選択が終了した後、リセット回路R S Tの各スイッチS W<sub>1</sub>，S W<sub>2</sub>，…，S W<sub>M-1</sub>，S W<sub>M</sub>に共通にローレベルのリセット信号Rを入力し、これらのスイッチをターンオンする。

40

#### 【0075】

このリセット回路R S Tの各スイッチS W<sub>1</sub>，S W<sub>2</sub>，…，S W<sub>M-1</sub>，S W<sub>M</sub>のターンオンで各データ線D L<sub>1</sub>，D L<sub>2</sub>，…，D L<sub>M-1</sub>，D L<sub>M</sub>は基準電位であるリセットレベルR Lとなる。このリセットは、次の行のデータ信号が送出される前に完了し、データ線およびコンデンサのリセットがなされる。

#### 【0076】

50

したがって、次にデータ信号の書き込み時には、全てのデータ線の書き込みの初期状態が一定となり、前段のデータ信号の大きさやその行の前のデータ信号の大きさに依存することなく、書き込まれるデータ信号に対応するコンデンサの保持電荷にはらつきは生ぜず、均一な画像表示が得られる。

#### 【0077】

尚、次の行の走査線の選択がなされる前にリセットを終える場合は、コンデンサのリセットは行えないので、ゲート線のリセットのみが行われる。この場合でも、前段のデータ信号の大きさに依存することのない書き込みが可能となる。

#### 【0078】

本実施例では、シフトレジスタを1系統としたが、これに代えて複数系統のシフトレジスタを用いたものにも同様に適用できる。また、サンプリング回路についても複数のデータ信号に対応した構成としたものにも同様に適用できる。

10

#### 【0079】

さらに、リセット回路を構成するスイッチ素子であるトランジスタをn型の薄膜トランジスタとした場合は、リセット信号の極性を図4に示したものと反転した信号とすればよい。また、このスイッチ用のトランジスタをn型とp型を組み合わせたトランスマッパーを用いることもできる。

#### 【0080】

本実施例により、画素回路のコンデンサに新しく書き込まれるデータ信号が前のデータ信号に影響されることなく、高品質の表示装置が得られる。

20

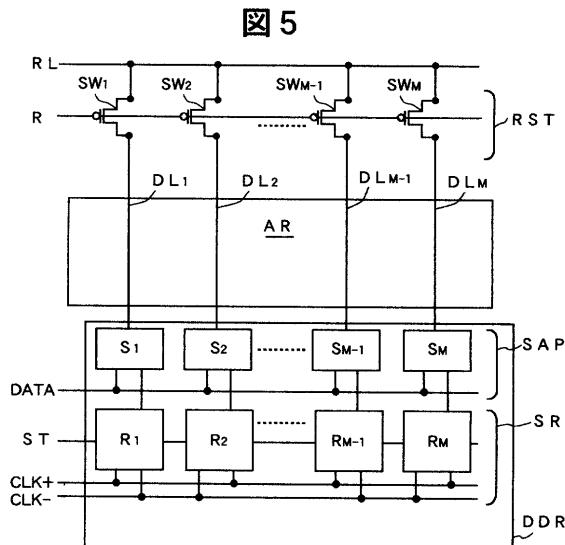

#### 【0081】

図5は本発明による表示装置の第2実施例の構成の要部を説明するブロック図である。図3と同様に表示領域ARには前記図2で説明した構成の多数の画素がマトリクス状に配置されている。また、図5でも、データ駆動回路の部分とデータ線のみを示してある。

#### 【0082】

本実施例は、リセット回路RSTをデータ駆動回路DDRに対して表示領域ARを挟んだ反対側(データ線DLの終端)に配置した点で第1実施例と異なる。シフトレジスタSR、サンプリング回路SAP、リセット回路RSTの回路構成、およびタイミングは第1実施例と同様である。

#### 【0083】

本実施例では、データ駆動回路DDRから遠い位置にリセット回路RSTを設けたことで、基板上の各種配線のレイアウトに起因するノイズの影響を低減できる。また、定められた基板サイズ内にリセット回路を配置する場合に、そのレイアウトが容易になる。

30

#### 【0084】

なお、本発明は上記したOLEDを用いた表示装置に限るものではなく、OLEDと同様の発光動作で表示を行う他の表示装置にも同様に適用できる。

#### 【0085】

また、上記の実施例では、第1の電極層を陽極、第2の電極層を陰極として説明したが、これらと逆の構成、すなわち第1の電極層を陰極、第2の電極層を陽極としたものにも同様に適用できる。また、画素回路を2トランジスタ方式としたものに限らず、4トランジスタ方式としたものにも適用できる。

40

#### 【0086】

#### 【発明の効果】

以上説明したように、本発明によれば、新しく書き込まれるデータ信号が前のデータ信号に影響されることなく、高品質の表示装置が得られる。また、リセット回路は単純なスイッチであることで、基板上の占有面積は極めて少なく、有効表示領域を狭小化することがない表示装置を提供することができる。

#### 【図面の簡単な説明】

【図1】本発明による表示装置の第1実施例の構成を模式的に説明するブロック図である

【図2】図1における1画素の画素回路の構成図である。

【図3】本発明による表示装置の第1実施例の構成の要部を説明するブロック図である。

【図4】図3の実施例の動作を説明するタイミング図である。

【図5】本発明による表示装置の第2実施例の構成の要部を説明するブロック図である。

【図6】有機発光素子を用いた従来の表示装置の1構成例を模式的に説明するブロック図である。

【図7】図6における画素構成の説明図である。

【図8】図7の画素構成をもつ図6の表示装置の構成をさらに説明するブロック図である。

【図9】有機発光素子を用いた従来の表示装置の他の構成例を模式的に説明する図8と同様のブロック図である。 10

【図10】有機発光素子を用いた表示装置の1画素付近の構造を説明する断面図である。

【符号の説明】

S U B 基板

G L ゲート線(走査線)

D L データ線

C S L 電流供給線

C S B 電流供給線バスライン

C S L L 電流供給線引回しライン

C D 第2の電極層

20

C N T B 第2電極接続電極層

C N T L 第2電極接続電極引回しライン

A D 第1の電極層

O L E 有機発光層

O L E D 有機発光素子

G D R 走査駆動回路

D D R データ駆動回路

R S T リセット回路。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

H 05 B 33/14

A

(72)発明者 大内 貴之

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

合議体

審判長 瀧 廣往

審判官 堀部 修平

審判官 小川 浩史

(56)参考文献 特開2000-352941(JP,A)

特開平11-337910(JP,A)

特開2000-47643(JP,A)

特開平3-219288(JP,A)

特開平11-175041(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP4027614B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2007-12-26 |

| 申请号            | JP2001092830                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2001-03-28 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 佐藤敏浩<br>金子好之<br>三上佳朗<br>大内貴之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 佐藤 敏浩<br>金子 好之<br>三上 佳朗<br>大内 貴之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09F9/30 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/3233 G09G3/3291 G09G2300/0842 G09G2300/0876 G09G2310/0248 G09G2310/0251<br>G09G2310/0262                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09G3/20.621.M G09G3/20.623.R G09G3/20.624.B G09G3/20.680.G H05B33/14.A<br>G09G3/20.621.F G09G3/3216 G09G3/3233 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/CA01 3K007/CB01 3K007/DA01 3K007/DB03 3K007/EB00 3K007/<br>/GA02 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC31 3K107/CC43 3K107/EE03 3K107/EE59<br>3K107/HH00 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD08 5C080/DD30 5C080<br>/EE29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AA03 5C380/AB05 5C380/AB06<br>5C380/AB12 5C380/AB15 5C380/AB23 5C380/AB31 5C380/AB34 5C380/AC08 5C380/AC12 5C380<br>/AC13 5C380/BA01 5C380/BA08 5C380/BA11 5C380/BC18 5C380/CA04 5C380/CA05 5C380/CA08<br>5C380/CA26 5C380/CA30 5C380/CB01 5C380/CB26 5C380/CC02 5C380/CC26 5C380/CC30 5C380<br>/CC33 5C380/CC62 5C380/CD012 5C380/CF07 5C380/DA02 5C380/DA06 5C380/DA09 5C380/DA11<br>5C380/DA16 5C380/DA47 |         |            |

| 代理人(译)         | 小野寺杨枝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 助理审查员(译)       | 小川博                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP2002287697A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

**摘要：**通过避免残留在像素电路的电容器中的先前扫描的数据信号的残余电荷的影响来执行高质量显示。水平扫描被提供给多个像素的数据线DL交叉的多个在显示区域AR配置成矩阵状在衬底SUB从扫描线GL的扫描线的扫描线GL桃红的每个交叉点并且通过从电流供给线CSL供给的信号选择的活动元件在用于保持从数据线DL提供的数据信号的数据保持器件，根据导通，并且在数据保持该有源元件的装置中的数据信号包括像素电路具有发光元件OLED配置成以电流时，数据线DL，前一扫描线的扫描结束后的像素之前发光，对应于所述下一个扫描线的像素数据被发送提供用于将电路的电容器CPR或数据线DL中的至少一个返回到初始状态的复位电路RST。