(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-163633

(P2012-163633A)

(43) 公開日 平成24年8月30日(2012.8.30)

| (51) Int.Cl.                | F 1            | テーマコード (参考) |

|-----------------------------|----------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J    | 3K107       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 641D | 5C080       |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 624B | 5C380       |

|                             | G09G 3/20 622C |             |

|                             | G09G 3/20 611H |             |

審査請求 未請求 請求項の数 12 O L (全 28 頁) 最終頁に続く

|           |                            |          |                                                                                                           |

|-----------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2011-22155 (P2011-22155) | (71) 出願人 | 000005821<br>パナソニック株式会社<br>大阪府門真市大字門真1006番地                                                               |

| (22) 出願日  | 平成23年2月3日(2011.2.3)        | (74) 代理人 | 100109210<br>弁理士 新居 広守                                                                                    |

|           |                            | (72) 発明者 | 新井 康弘<br>大阪府門真市大字門真1006番地 パナ<br>ソニック株式会社内                                                                 |

|           |                            |          | F ターム(参考) 3K107 AA01 BB01 CC14 CC33 EE03<br>HH04 HH05<br>5C080 AA06 BB05 DD22 DD26 JJ02<br>JJ03 JJ04 JJ05 |

|           |                            |          |                                                                                                           |

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】2値駆動方式において定電流源を用いることなく発光電流のばらつきを抑制しつつ低損失な表示装置及びその駆動方法を提供する。

【解決手段】複数の画素が配列された画素部10を備える表示装置1であって、画素10Aは、入力された映像信号に基づき、導通状態及び非導通状態を切り換える薄膜トランジスタスイッチ11Aと、薄膜トランジスタスイッチ11Aが導通状態の場合に、正電圧パルス及び負電圧パルスが交互に印加されることにより発生する双方向電流を整流し、当該整流された電流を薄膜トランジスタスイッチ11Aに単方向に流し、当該整流された電流が流れることにより発光する有機EL素子101～104とを備える。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

複数の発光画素が配列された表示部を備える表示装置であって、

前記複数の発光画素のそれぞれは、

入力された映像信号に基づき、導通状態及び非導通状態を切り換えるスイッチ部と、

前記スイッチ部が導通状態の場合に、基準電位よりも高電位の電圧パルス及び低電位の電圧パルスが交互に印加されることにより発生する双方向電流を整流し、当該整流された電流を前記スイッチ部に単方向に流し、前記整流された電流が流れることにより発光する発光整流部とを備える

表示装置。

10

**【請求項 2】**

前記複数の発光画素のそれぞれは、さらに、

前記発光整流部と基準電極との間に直列挿入され、前記発光整流部から前記基準電極へ流れる電流により充電され、当該電流と逆方向に流れる電流により放電する反転コンデンサを備える

請求項 1 に記載の表示装置。

**【請求項 3】**

前記スイッチ部は、ゲート電極、ソース電極及びドレイン電極を有するスイッチ素子を備え、

前記発光整流部は、

20

第 1 ~ 第 4 の整流素子を備え、前記第 1 ~ 第 4 の整流素子のうち少なくとも 1 つは前記整流された電流が流れることにより発光し、

前記第 1 の整流素子のアノード電極は、前記第 3 の整流素子のカソード電極及び前記反転コンデンサの一方の端子に接続され、

前記第 2 の整流素子のアノード電極は、前記第 4 の整流素子のカソード電極に接続され、前記第 2 の整流素子のアノード電極と前記第 4 の整流素子のカソード電極との接続点に前記高電位の電圧パルス及び前記低電位の電圧パルスが印加され、

前記第 1 の整流素子のカソード電極及び前記第 2 の整流素子のカソード電極は、前記スイッチ素子のドレイン電極に接続され、

前記第 3 の整流素子のアノード電極及び前記第 4 の整流素子のアノード電極は、前記スイッチ素子のソース電極に接続される

30

請求項 2 に記載の表示装置。

**【請求項 4】**

前記表示装置は、さらに、

発光画素行ごとに配置された走査線と、

発光画素列ごとに配置されたデータ線と、

発光画素行を選択するための走査信号を、前記走査線を介して前記表示部に出力する走査線制御回路と、

前記走査線制御回路から出力される前記走査信号に同期して、前記スイッチ部の導通及び非導通を切り換えるための、前記映像信号に対応したデータ信号を、前記データ線を介して前記スイッチ部に出力するデータ線制御回路と、

前記高電位の電圧パルス及び前記低電位の電圧パルスを交互に発生して前記接続点に印加するパルス発生部とを備え、

前記発光整流部は、前記スイッチ部が導通状態である場合に、前記接続点と前記反転コンデンサとの電位差により発生する前記整流された電流に応じて発光する

40

請求項 3 に記載の表示装置。

**【請求項 5】**

前記スイッチ部は、さらに、

前記スイッチ素子のソース電極及びゲート電極に接続されたコンデンサと、

カソード電極が前記スイッチ素子のゲート電極に接続されアノード電極が前記データ線

50

に接続された第 5 の整流素子とを備え、

前記スイッチ素子のソース電極は、発光画素行ごとに配置された前記走査線に接続され、

前記データ信号により前記スイッチ部が導通状態となった発光画素は、前記パルス発生部が前記高電位の電圧パルス及び前記低電位の電圧パルスを全画素の前記接続点に一斉に印加することにより一斉に発光する

請求項 4 に記載の表示装置。

**【請求項 6】**

前記スイッチ部は、さらに、

前記スイッチ素子のソース電極及びゲート電極に接続されたコンデンサと、

10

カソード電極が前記スイッチ素子のゲート電極に接続されアノード電極が前記データ線に接続された第 5 の整流素子とを備え、

前記接続点は、発光画素行ごとに配置された前記走査線に接続され、

前記走査線制御回路は、前記パルス発生部を含み、前記高電位の電圧パルス及び前記低電位の電圧パルスを常に前記接続点に出力し、また、前記走査信号を行順次に前記接続点に出力し、

前記データ信号により前記スイッチ部が行順次に導通状態となった発光画素は、行順次に発光する

請求項 4 に記載の表示装置。

**【請求項 7】**

前記表示装置は、さらに、

20

消去線と、

前記コンデンサに保持された、前記データ信号に対応した電圧を消去するための消去信号を、前記消去線を介して前記スイッチ素子のゲート電極に出力する消去線制御回路とを備え、

前記スイッチ部は、さらに、

アノード電極が前記スイッチ素子のゲート電極に接続されカソード電極が前記消去線に接続された第 6 の整流素子を備え、

前記発光整流部が発光している発光画素は、前記消去線制御回路から前記消去信号が印加されることにより消灯する

30

請求項 5 または 6 に記載の表示装置。

**【請求項 8】**

前記第 1 ~ 第 4 の整流素子のうち少なくとも 1 つは、有機 E L 素子である

請求項 3 ~ 7 のうちいずれか 1 項に記載の表示装置。

**【請求項 9】**

前記第 1 ~ 第 4 の整流素子のうち少なくとも 1 つは、無機 E L 素子である

請求項 3 ~ 7 のうちいずれか 1 項に記載の表示装置。

**【請求項 10】**

複数の発光画素が配列された表示部を備える表示装置の駆動方法であって、

40

入力された映像信号に基づき、各発光画素の有するスイッチ部の導通状態及び非導通状態を切り換える第 1 ステップと、

双方向電流を整流し、当該整流された電流を前記スイッチ部に単方向に流し、前記整流された電流が流れることにより発光する、各発光画素の有する発光整流部に、基準電位よりも高電位の電圧パルス及び低電位の電圧パルスを交互に印加する第 2 ステップとを含む表示装置の駆動方法。

**【請求項 11】**

前記複数の発光画素のそれぞれは、さらに、

前記発光整流部と基準電極との間に直列挿入され、前記発光整流部から前記基準電極へ流れる電流により充電され、当該電流と逆方向に流れる電流により放電する反転コンデンサを備え、

50

前記スイッチ部は、ゲート電極、ソース電極及びドレイン電極を有するスイッチ素子を備え、

前記発光整流部は、

第1～第4の整流素子を備え、前記第1～第4の整流素子のうち少なくとも1つは前記整流された電流が流れることにより発光し、前記第1の整流素子のアノード電極が、前記第3の整流素子のカソード電極及び前記反転コンデンサの一方の端子に接続され、前記第2の整流素子のアノード電極が、前記第4の整流素子のカソード電極に接続され、前記第2の整流素子のアノード電極と前記第4の整流素子のカソード電極との接続点に前記高電位の電圧パルス及び前記低電位の電圧パルスが印加され、前記第1の整流素子のカソード電極及び前記第2の整流素子のカソード電極は、前記スイッチ素子のドレイン電極に接続され、前記第3の整流素子のアノード電極及び前記第4の整流素子のアノード電極は、前記スイッチ素子のソース電極に接続され、

前記スイッチ素子のソース電極は、発光画素行ごとに配置された前記走査線に接続され、

前記第1ステップは、

発光画素行を選択するための走査信号を、発光画素行ごとに配置された走査線を介して前記スイッチ素子のソース電極に出力する走査信号出力ステップと、

前記走査信号出力ステップで出力された前記走査信号に同期して、前記スイッチ部の導通及び非導通を切り換えるためのデータ信号を、発光画素列ごとに配置されたデータ線を介して前記スイッチ素子のゲート電極に出力するデータ信号出力ステップとを含み、

前記第2ステップでは、

前記データ信号出力ステップで出力された前記データ信号により前記スイッチ部が導通状態となった発光画素が一斉に発光するよう、前記高電位の電圧パルス及び前記低電位の電圧パルスの交流電圧を全発光画素の前記接続点に一斉に印加する

請求項10に記載の表示装置の駆動方法。

#### 【請求項12】

前記複数の発光画素のそれぞれは、さらに、

前記発光整流部と基準電極との間に直列挿入され、前記発光整流部から前記基準電極へ流れる電流により充電され、当該電流と逆方向に流れる電流により放電する反転コンデンサを備え、

前記スイッチ部は、ゲート電極、ソース電極及びドレイン電極を有するスイッチ素子を備え、

前記発光整流部は、

第1～第4の整流素子を備え、前記第1～第4の整流素子のうち少なくとも1つは前記整流された電流が流れることにより発光し、前記第1の整流素子のアノード電極が、前記第3の整流素子のカソード電極及び前記反転コンデンサの一方の端子に接続され、前記第2の整流素子のアノード電極が、前記第4の整流素子のカソード電極に接続され、前記第2の整流素子のアノード電極と前記第4の整流素子のカソード電極との接続点に前記高電位の電圧パルス及び前記低電位の電圧パルスが印加され、前記第1の整流素子のカソード電極及び前記第2の整流素子のカソード電極は、前記スイッチ素子のドレイン電極に接続され、前記第3の整流素子のアノード電極及び前記第4の整流素子のアノード電極は、前記スイッチ素子のソース電極に接続され、

前記接続点は、発光画素行ごとに配置された前記走査線に接続され、

前記第1ステップは、

発光画素行を選択するための走査信号を、発光画素行ごとに配置された走査線を介して前記スイッチ素子の前記接続点に出力する走査信号出力ステップと、

前記走査信号出力ステップで出力された前記走査信号に同期して、前記スイッチ部の導通及び非導通を切り換えるためのデータ信号を、発光画素列ごとに配置されたデータ線を介して前記スイッチ素子のゲート電極に出力するデータ信号出力ステップとを含み、

前記第2ステップでは、

10

20

30

40

50

前記データ信号出力ステップで出力された前記データ信号により前記スイッチ部が行順次に導通状態となった発光画素が行順次に発光するよう、前記高電位の電圧パルス及び前記低電位の電圧パルスを常に前記接続点に出力する

請求項 10 に記載の表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその駆動方法に関し、特に、画素毎にトランジスタが設けられ、画素の発光を制御するアクティブマトリクス型表示装置及びその駆動方法に関する。

10

【背景技術】

【0002】

有機及び無機EL( Electro Luminescence)、又はLED( Light Emitting Diode)等のような発光素子をアレイ状に組み合わせ、ドットマトリクスにより文字表示を行うディスプレイは、テレビ、携帯端末等に広く利用されている。特に、自発光素子を用いたこれらのディスプレイは、液晶を用いたディスプレイと異なり、照明のためのバックライトを必要としない、視野角が広い、応答速度が速い等の特徴を有し、注目を集めている。中でも、低温ポリシリコン等による薄膜トランジスタとこれらの発光素子とを組み合わせたアクティブマトリクス型と呼ばれるディスプレイは、単純マトリクス駆動のディスプレイと比較して、低消費電力、高輝度、高コントラスト、高精細等の優位性を持っており近年注目されている。

20

【0003】

一般的にコンピュータの端末、パソコンのモニタ、テレビ等の動画表示を行うためには、各画素の輝度が変化する階調表示が出来ることが必要不可欠である。従来から用いられている階調表示方法としては、大きくアナログ階調制御方式及びデジタル階調制御方式に分けられる。

【0004】

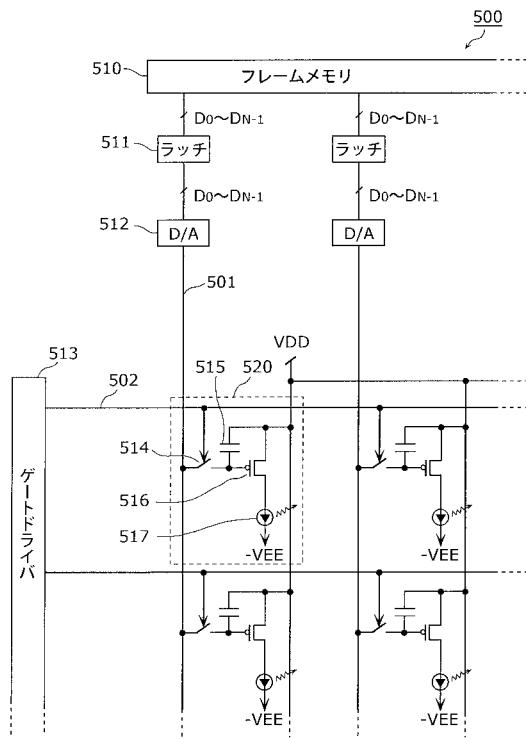

図12は、アナログ階調制御方式による従来の電流駆動型表示パネルの構成の一例を示す回路ブロック図である。同図に記載された電流駆動型表示パネル500は、マトリクス状に配置された複数の画素520と、画素列ごとに配置された複数の信号線501と、画素列ごとに配置された複数のラッチ511及びD/Aコンバータ512と、画素行ごとに配置された複数の走査線502と、ラッチ511及びD/Aコンバータ512を介して信号線501に接続されたフレームメモリ510と、走査線502に接続されたゲートドライバ513とを備える。画素520は、信号電圧の画素520への書き込みを制御するスイッチ514と、保持容量515と、信号電圧を発光電流に変換するPチャネル薄膜トランジスタ516と、発光素子517とを有する。

30

【0005】

フレームメモリ510からのNビットのデジタル階調データ $D_0 \sim D_{N-1}$ は、一旦ラッチ511に保持された後、D/Aコンバータ512によりアナログ電圧値に変換され、信号線501に伝達される。選択期間では、ゲートドライバ513によりスイッチ514がONとなり、信号線501のアナログ電圧値はPチャネル薄膜トランジスタ516のゲートに印加される。これにより、Pチャネル薄膜トランジスタ516のゲート-ソース間には、(アナログ電圧値 - 電源電圧(VDD))の電圧がかかる。その結果、信号線501のアナログ電圧値はPチャネル薄膜トランジスタ516により電圧電流変換され、発光素子517には当該アナログ電圧値に応じた一定の電流値が流れ、発光素子517が発光する。また非選択期間では、スイッチ514がOFFとなるが、保持容量515により信号線501のアナログ電圧値が保持されているので、Pチャネル薄膜トランジスタ516のゲート-ソース間には上記電圧が印加され続け、非選択期間においても発光素子517には一定の電流が流れ続け、発光は持続される。

40

【0006】

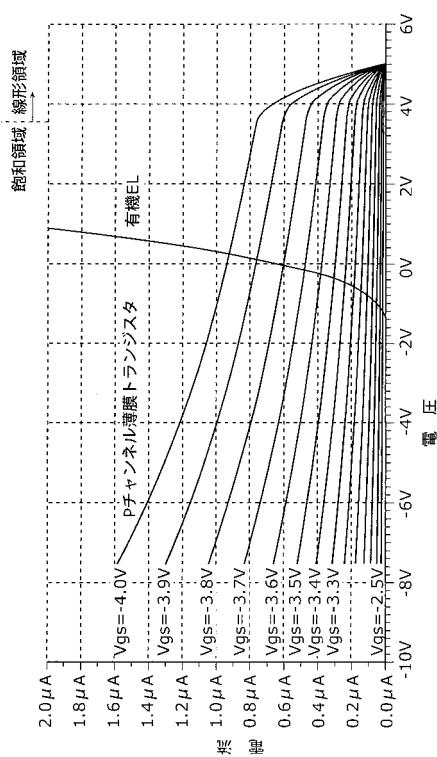

図13は、画素のPチャネル薄膜トランジスタと有機EL素子との動特性のシミュレー

50

ション結果を示すグラフである。電源電圧( VDD )を5V、対向電圧( -VEE )を-7.5Vと仮定し、パラメータとして、Pチャネル薄膜トランジスタのゲート-ソース間電圧 $V_{gs}$ をとっている。横軸は、Pチャネル薄膜トランジスタのソース-ドレイン間電圧 $V_{ds}$ または有機EL素子のアノード-カソード間電圧 $V_{el}$ を表し、縦軸はPチャネル薄膜トランジスタのドレイン電流 $I_d$ または有機EL素子に流れる電流 $I_e$ を表している。グラフにおいて、Pチャネル薄膜トランジスタと有機EL素子との動作曲線の交点が動作点であり、当該動作点が有機EL素子に流れる電流値 $I_e$ を表している。

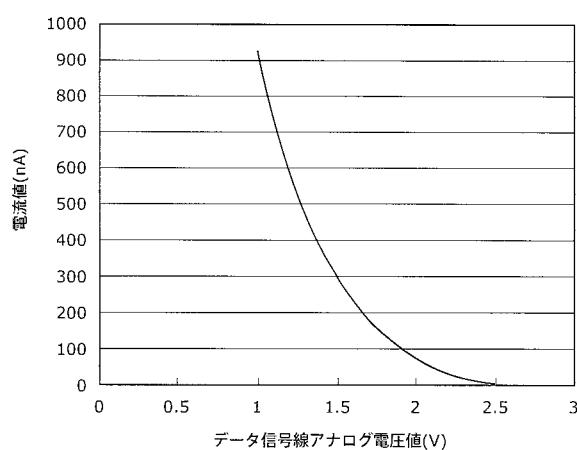

#### 【0007】

図14は、Pチャネル薄膜トランジスタと有機EL素子との動作曲線の交点をプロットしたグラフである。同図に表されたグラフのように、これらの動作点をプロットしていくと、信号線のアナログ信号電圧と有機EL素子に流れる電流値との関係が得られる。一般に、有機EL素子等の発光素子では、流れる電流値と輝度は比例するので、図14のグラフは信号電圧-輝度特性と考えてもよい。図14より、アナログ信号電圧と輝度とは比例しているのではなく、ガンマ特性がかかったような特性を示しているので、ディジタルの階調データをそのままアナログ信号に変換するだけで、ガンマ特性のかかった階調表示が実現できることがわかる。

#### 【0008】

ただし、図14に示された特性以外のガンマ特性を実現する場合には、ディジタルの階調データをそのままアナログ信号に変換するのではなく、別途D/Aコンバータに工夫を凝らす必要がある。

#### 【0009】

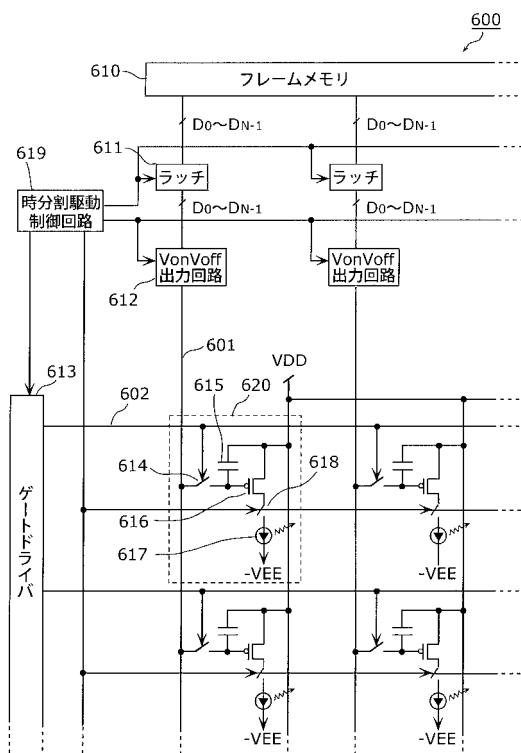

一方、図15は、ディジタル階調制御方式による従来の電流駆動型表示パネルの構成の一例を示す回路ブロック図である。同図に記載された電流駆動型表示パネル600は、マトリクス状に配置された複数の画素620と、画素列ごとに配置された複数の信号線601と、画素列ごとに配置された複数のラッチ611及び $V_{ON}V_{OFF}$ 出力回路612と、画素行ごとに配置された複数の走査線602と、ラッチ611及び $V_{ON}V_{OFF}$ 出力回路612を介して信号線601に接続されたフレームメモリ610と、走査線602に接続されたゲートドライバ613と、時分割駆動制御回路619とを備える。画素620は、信号電圧の画素620への書き込みを制御するスイッチ614と、保持容量615と、信号電圧を発光電流に変換するPチャネル薄膜トランジスタ616と、発光素子617と、発光素子617の発光を制御するスイッチ618とを有する。ディジタル階調制御方式としては、面積階調方式や時分割駆動方式等があるが、ここでは時分割駆動方式を説明する。

#### 【0010】

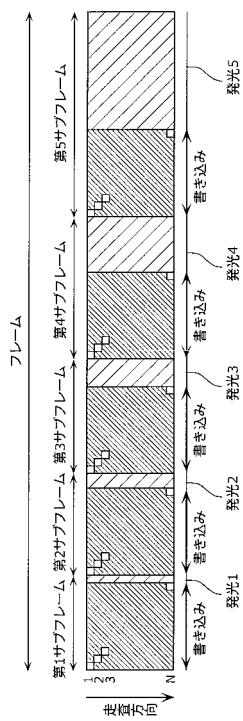

図16は、時分割駆動方式によるディジタル階調制御方式を説明する図である。同図に示すように、時分割駆動方式は、1フレームを、重み付けされたいつかのサブフレームに分割し、ディジタルの階調データにあわせて対応するサブフレームをONまたはOFFさせることにより階調表示を行う方式である。

#### 【0011】

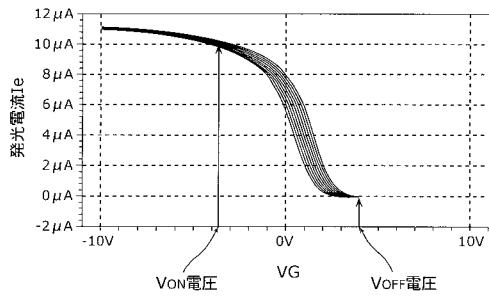

以下、時分割駆動方式によるディジタル階調制御方式を詳細に説明する。図15に示された時分割駆動制御回路619により、フレームメモリ610からのNビットのディジタル階調データ $D_0 \sim D_{N-1}$ は一旦ラッチ611に保持された後、 $V_{ON}V_{OFF}$ 出力回路612に入力される。 $V_{ON}V_{OFF}$ 出力回路612は、時分割駆動制御回路619により、ディジタル階調データの $D_0 \sim D_{N-1}$ のビットに対応したサブフレームに応じて出力信号が選択される。すなわち、第1サブフレームでは $D_0$ 、第2サブフレームでは $D_1$ 、…、第Nサブフレームでは $D_{N-1}$ が選択される。そして、 $V_{ON}V_{OFF}$ 出力回路612は、ディジタル階調データの選択ビットが1のときはON出力電圧 $V_{ON}$ を、0のときはOFF出力電圧 $V_{OFF}$ を信号線601に出力する。ON出力電圧 $V_{ON}$ 及びOFF出力電圧 $V_{OFF}$ は、図17Bに示す特性から決められる。

#### 【0012】

10

20

30

40

50

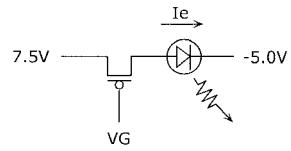

図17Aは、デジタル階調制御方式における薄膜トランジスタ及び発光素子の回路構成の一例を示す図であり、図17Bは、デジタル階調制御方式におけるON出力電圧及びOFF出力電圧を説明するグラフである。図17Bに表されたグラフの横軸は、図17Aの回路構成におけるゲート電圧VGを示しており、図17Bに表されたグラフの縦軸は、図17Aの回路構成における発光電流Ieを示している。図17Bに表されたように、画素の有する駆動用の薄膜トランジスタは、閾値電圧にはらつきを有するため、印加されるゲート電圧VGがアナログ値をもって変化する場合には、有機EL素子を流れる発光電流Ieがばらついてしまう。デジタル階調制御方式では、発光電流Ieのばらつきの大きいゲート電圧範囲を使用せず、V<sub>ON</sub>電圧及びV<sub>OFF</sub>電圧の2値が使用される。

## 【0013】

図15に示されるように、V<sub>ON</sub> V<sub>OFF</sub>出力回路612から信号線601に出力された信号電圧は、ゲートドライバ613により順次、スイッチ614がONされて保持容量615に書き込まれていく。ただし、この期間ではスイッチ618はOFFになっているので、発光素子617には電流が流れず発光はしない。ゲートドライバ613により、走査線が順次選択され画面全体の保持容量615にONまたはOFFの信号電圧が書き込まれると、時分割駆動制御回路619により、スイッチ618が一斉にONされて発光する。

## 【0014】

重み付けされたサブフレームの期間、発光素子617が発光すると、時分割駆動制御回路619によりスイッチ618はOFFされ、再びゲートドライバ613により走査が始まる。以上、図16に示されるように、書き込み期間と発光期間とが繰り返されることにより、階調データに応じた階調表示が行われる。

## 【0015】

このように、時分割駆動によるデジタル階調制御方式では、基本的にONまたはOFFの2値駆動であり、入力電圧としては図17Bに示すV<sub>ON</sub>電圧及びV<sub>OFF</sub>電圧だけであるので、アナログ階調制御方式と比べてD/Aコンバータがない。その分、時分割駆動によるデジタル階調制御方式は、制御が簡単で回路規模が小さいというメリットを有する(特許文献1)。

## 【0016】

さらに、薄膜トランジスタの閾値電圧ばらつきにより、前述した2値駆動方式においても、依然として発光素子の輝度を一定に制御することは困難な場合があるので、当該閾値電圧のばらつきを抑制するためにカレントミラー回路を用いた補正方法が提案されている(特許文献2)。

## 【先行技術文献】

## 【特許文献】

## 【0017】

【特許文献1】特開2003-99000号公報

【特許文献2】特開2008-181159号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0018】

前述したデジタル階調制御方式における2値駆動方式では、図15に記載されたPチャネル薄膜トランジスタ616のゲートにV<sub>ON</sub>電圧が印加された場合に流れる発光電流のばらつきを抑制するために、定電流源が用いられる。この定電流源は、Pチャネル薄膜トランジスタ616のドレイン-ソース間電圧V<sub>ds</sub>がゲート-ソース間電圧V<sub>gs</sub>よりも大きい領域である飽和領域を利用することにより実現されている。図13に表された薄膜トランジスタのV<sub>ds</sub>-I<sub>d</sub>特性において、飽和領域ではV<sub>ds</sub>の変化に対してI<sub>d</sub>の変化が小さいので、薄膜トランジスタが定電流源化できることが解る。

## 【0019】

しかしながら、飽和領域での薄膜トランジスタを定電流源として利用した場合、薄膜ト

10

20

30

40

50

ランジスタのオン抵抗が大きいため、ドレイン - ソース間における電圧降下を要因とする電力損失が発生するという課題がある。

【0020】

本発明は、上記課題に鑑みてなされたものであり、2値駆動方式において定電流源を用いることなく発光電流のばらつきを抑制しつつ低損失な表示装置及びその駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0021】

上記課題を解決するために、本発明の一態様に係る表示装置は、複数の発光画素が配列された表示部を備える表示装置であって、前記複数の発光画素のそれぞれは、入力された映像信号に基づき、導通状態及び非導通状態を切り換えるスイッチ部と、前記スイッチ部が導通状態の場合に、基準電位よりも高電位の電圧パルス及び低電位の電圧パルスが交互に印加されることにより発生する双方向電流を整流し、当該整流された電流を前記スイッチ部に単方向に流し、前記整流された電流が流れることにより発光する発光整流部とを備えることを特徴とする。

10

【0022】

このような構成によれば、発光画素の有するスイッチ部は、定電流源である必要はなく、発光画素に流れる発光電流の開閉状態を切り換えるスイッチ機能を有していればよい。また、表示部の階調制御に必要となるのは、外部交流電圧の供給及びその印加時間制御、ならびに発光画素毎に設けられたスイッチ部のオンオフ動作であるため、従来の定電流源で発生していた電圧降下が原理的にゼロとなる。よって、スイッチ部に発光電流が流れるときの、スイッチ部での電圧降下を低減でき、表示パネルの電力損失を大幅に低減することができる。

20

【0023】

また、前記複数の発光画素のそれぞれは、さらに、前記発光整流部と基準電極との間に直列挿入され、前記発光整流部から前記基準電極へ流れる電流により充電され、当該電流と逆方向に流れる電流により放電する反転コンデンサを備えることが好ましい。

【0024】

これにより、正負の交流電圧パルス印加端子と反転コンデンサとの間に発光整流部が配置されることとなり、上記印加端子と反転コンデンサとの間で発生する双方向電流により反転コンデンサの充放電が繰り返される。この反転コンデンサの充放電により、発光整流部を流れる双方向電流は所定の期間において安定した電流値を有することとなる。よって、定電流源を用いることなく発光電流のばらつきを抑制しつつ低損失なディジタル階調制御が可能となる。

30

【0025】

また、前記スイッチ部は、ゲート電極、ソース電極及びドレイン電極を有するスイッチ素子を備え、前記発光整流部は、第1～第4の整流素子を備え、前記第1～第4の整流素子のうち少なくとも1つは前記整流された電流が流れることにより発光し、前記第1の整流素子のアノード電極は、前記第3の整流素子のカソード電極及び前記反転コンデンサの一方の端子に接続され、前記第2の整流素子のアノード電極は、前記第4の整流素子のカソード電極に接続され、前記第2の整流素子のアノード電極と前記第4の整流素子のカソード電極との接続点に前記高電位の電圧パルス及び前記低電位の電圧パルスが印加され、前記第1の整流素子のカソード電極及び前記第2の整流素子のカソード電極は、前記スイッチ素子のドレイン電極に接続され、前記第3の整流素子のアノード電極及び前記第4の整流素子のアノード電極は、前記スイッチ素子のソース電極に接続されることが好ましい。

40

【0026】

この構成によれば、スイッチ素子が導通状態で上記高電位の電圧パルスが上記接続点に印加されたときには、発光電流は、上記接続点 第3の整流素子 スイッチ素子 第2の整流素子 反転コンデンサを通過し、反転コンデンサは充電され、第3の整流素子及び第

50

2の整流素子が発光し得る。一方、スイッチ素子が導通状態で上記低電位の電圧パルスが上記接続点に印加されたときには、発光電流は、反転コンデンサ 第1の整流素子 スイッチ素子 第4の整流素子 上記接続点を通過し、反転コンデンサは放電され、第1の整流素子及び第4の整流素子が発光し得る。

## 【0027】

また、前記表示装置は、さらに、発光画素行ごとに配置された走査線と、発光画素列ごとに配置されたデータ線と、発光画素行を選択するための走査信号を、前記走査線を介して前記表示部に出力する走査線制御回路と、前記走査線制御回路から出力される前記走査信号に同期して、前記スイッチ部の導通及び非導通を切り換えるための、前記映像信号に対応したデータ信号を、前記データ線を介して前記スイッチ部に出力するデータ線制御回路と、前記高電位の電圧パルス及び前記低電位の電圧パルスを交互に発生して前記接続点に印加するパルス発生部とを備え、前記発光整流部は、前記スイッチ部が導通状態である場合に、前記接続点と前記反転コンデンサとの電位差により発生する前記整流された電流に応じて発光してもよい。

10

## 【0028】

この構成によれば、表示装置が、発光画素選択及び交流電圧パルス発生の機能を有する。

## 【0029】

また、前記スイッチ部は、さらに、前記スイッチ素子のソース電極及びゲート電極に接続されたコンデンサと、カソード電極が前記スイッチ素子のゲート電極に接続されアノード電極が前記データ線に接続された第5の整流素子とを備え、前記スイッチ素子のソース電極は、発光画素行ごとに配置された前記走査線に接続され、前記データ信号により前記スイッチ部が導通状態となった発光画素は、前記パルス発生部が前記高電位の電圧パルス及び前記低電位の電圧パルスを全画素の前記接続点に一斉に印加することにより一斉に発光してもよい。

20

## 【0030】

これによれば、全発光画素で一斉に発光動作をさせることが可能となる。

## 【0031】

また、前記スイッチ部は、さらに、前記スイッチ素子のソース電極及びゲート電極に接続されたコンデンサと、カソード電極が前記スイッチ素子のゲート電極に接続されアノード電極が前記データ線に接続された第5の整流素子とを備え、前記接続点は、発光画素行ごとに配置された前記走査線に接続され、前記走査線制御回路は、前記パルス発生部を含み、前記高電位の電圧パルス及び前記低電位の電圧パルスを常に前記接続点に出力し、また、前記走査信号を行順次に前記接続点に出力し、前記データ信号により前記スイッチ部が行順次に導通状態となった発光画素は、行順次に発光してもよい。

30

## 【0032】

これにより、走査線制御回路が上記走査電圧パルスを発光動作のための正負パルスに重畠して出力するので、走査線制御回路が上記走査電圧パルスを出力し電源線制御回路が発光動作のための正負パルスを出力する場合と比較して、各画素に結線される配線の数を少なくすることが可能である。

40

## 【0033】

また、前記表示装置は、さらに、消去線と、前記コンデンサに保持された、前記データ信号に対応した電圧を消去するための消去信号を、前記消去線を介して前記スイッチ素子のゲート電極に出力する消去線制御回路とを備え、前記スイッチ部は、さらに、アノード電極が前記スイッチ素子のゲート電極に接続されカソード電極が前記消去線に接続された第6の整流素子を備え、前記発光整流部が発光している発光画素は、前記消去線制御回路から前記消去信号が印加されることにより消灯してもよい。

## 【0034】

これにより、発光動作していた発光画素を消灯することが可能となる。

## 【0035】

50

また、前記第1～第4の整流素子のうち少なくとも1つは、有機EL素子であってよい。

**【0036】**

また、前記第1～第4の整流素子のうち少なくとも1つは、無機EL素子であってよい。

**【0037】**

また、本発明は、このような特徴的な手段を備える表示装置として実現することができるだけでなく、表示装置に含まれる特徴的な手段をステップとする表示装置の駆動方法として実現することができる。

**【発明の効果】**

**【0038】**

本発明の表示装置及びその駆動方法によれば、表示部の階調制御に必要となるのは、外部交流電圧の供給及びその印加時間制御、ならびに発光画素毎に設けられたスイッチ部のオンオフ動作であるため、従来の定電流源で発生していた電圧降下が原理的にゼロとなる。よって、ディスプレイの消費電力を大幅に低減することができる。

**【図面の簡単な説明】**

**【0039】**

【図1】本発明の実施の形態1に係る表示装置の機能ブロック図である。

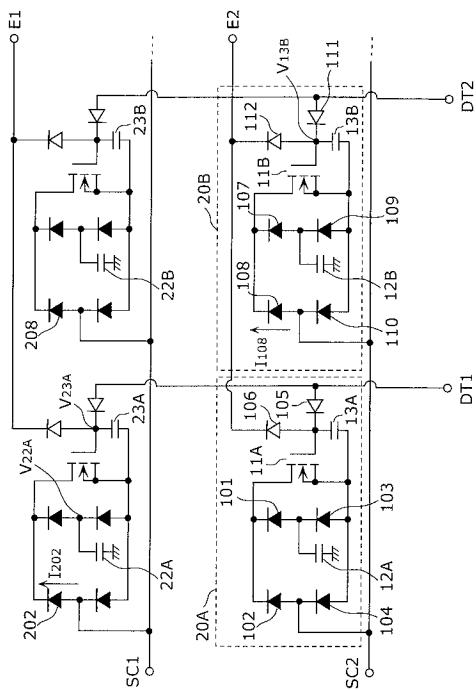

【図2】本発明の実施の形態1に係る表示装置が有する画素部の回路構成図である。

【図3】本発明の実施の形態1に係る表示装置が有する走査線制御回路の内部回路図である。

20

【図4】本発明の表示装置が有する消去線制御回路の内部回路図である。

【図5】本発明の表示装置が有する電源線制御回路の内部回路図である。

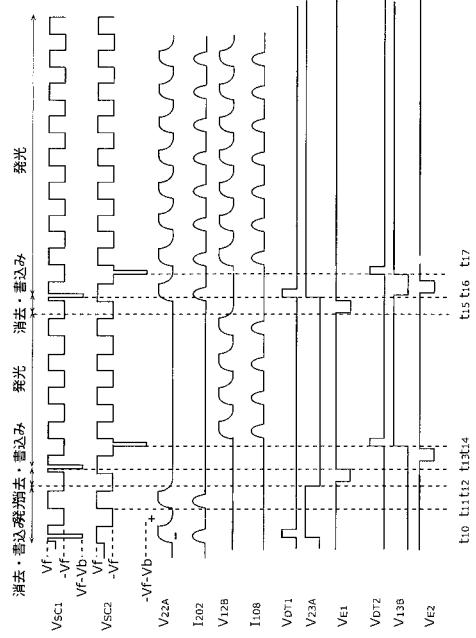

【図6】本発明の実施の形態1に係る表示装置の駆動タイミングチャートである。

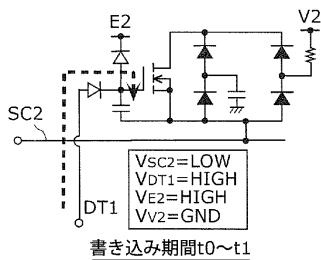

【図7A】本発明の表示装置が有する画素への書き込み動作を説明する状態遷移図である。

。

【図7B】本発明の表示装置が有する画素への第1の発光動作を説明する状態遷移図である。

【図7C】本発明の表示装置が有する画素への第2の発光動作を説明する状態遷移図である。

30

【図7D】本発明の表示装置が有する画素への消去動作を説明する状態遷移図である。

【図8】本発明の実施の形態2に係る表示装置が有する画素部の回路構成図である。

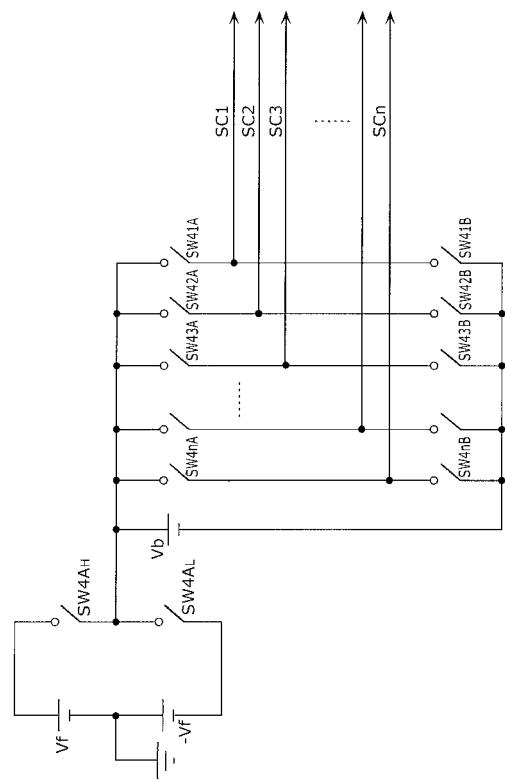

【図9】本発明の実施の形態2に係る表示装置が有する走査線制御回路の内部回路図である。

。

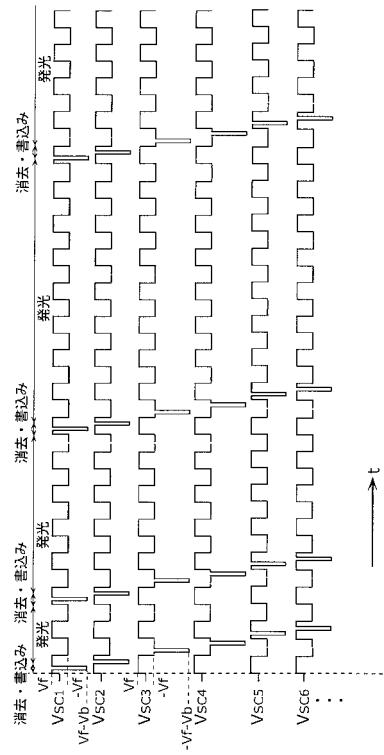

【図10】本発明の実施の形態2に係る走査線制御回路の駆動タイミングチャートである。

。

【図11】本発明の実施の形態2に係る表示装置の動作タイミングチャートである。

【図12】アナログ階調制御方式による従来の電流駆動型表示パネルの構成の一例を示す回路ブロック図である。

【図13】画素部のPチャネル薄膜トランジスタと有機EL素子との動特性のシミュレーション結果を示すグラフである。

40

【図14】Pチャネル薄膜トランジスタと有機EL素子との動作曲線の交点をプロットしたグラフである。

【図15】ディジタル階調制御方式による従来の電流駆動型表示パネルの構成の一例を示す回路ブロック図である。

【図16】時分割駆動方式によるディジタル階調制御方式を説明する図である。

【図17A】ディジタル階調制御方式における薄膜トランジスタ及び発光素子の回路構成の一例を示す図である。

【図17B】ディジタル階調制御方式におけるON出力電圧及びOFF出力電圧を説明するグラフである。

50

## 【発明を実施するための形態】

## 【0040】

以下、本発明を実施するための形態について、図面を参照しながら説明する。

## 【0041】

(実施の形態1)

<表示装置の構成>

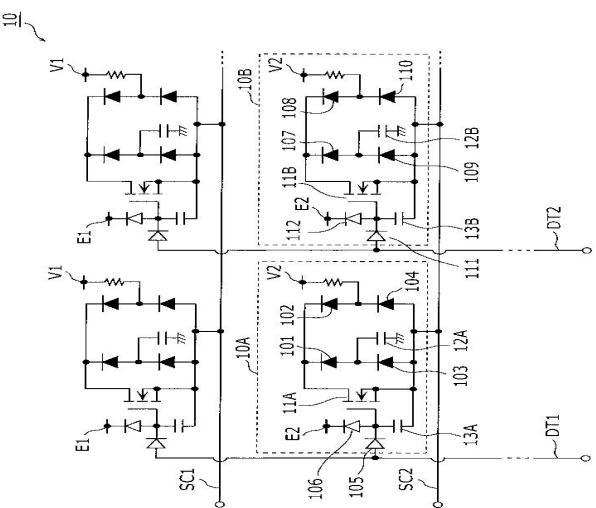

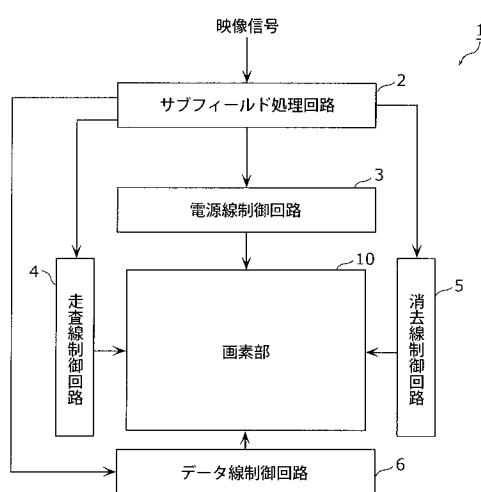

図1は、本発明の実施の形態1に係る表示装置の機能ブロック図である。同図に記載された表示装置1は、サブフィールド処理回路2と、電源線制御回路3と、走査線制御回路4と、消去線制御回路5と、データ線制御回路6と、画素部10とを備える。

## 【0042】

10

サブフィールド処理回路2は、入力された映像信号に応じて、画素部10の画素ごとに発光させるサブフレームを割り当て、電源線制御回路3、走査線制御回路4、消去線制御回路5及びデータ線制御回路6に制御信号を出力する。

## 【0043】

走査線制御回路4は画素部10に走査電圧を印加し、データ線制御回路6は画素部10に信号電圧を印加し、消去線制御回路5は画素部10に消去電圧を印加し、電源線制御回路3は画素部10に電源電圧を印加する。以下、上述した表示装置1の構成要素について詳細に説明する。

## 【0044】

20

図2は、本発明の実施の形態1に係る表示装置が有する画素部の回路構成図である。画素部10は、ディスプレイの解像度( $m \times n$ )に応じたマトリクス状に配置された複数の発光画素が配置された表示部であるが、図2には、画素部10の一部である、隣接する4発光画素が記載されている。図2に記載された画素部10は、隣接する4つの発光画素と、画素列ごとに配置されたデータ線DT1及びDT2と、画素行ごとに配置された走査線SC1及びSC2と、電源線V1及びV2と、消去線E1及びE2とを備える。

## 【0045】

また、表示部である画素部10が有する複数の発光画素は、全て同じ回路構成となっており、例えば、図2に記載された画素10Aは、薄膜トランジスタスイッチ11Aと、有機EL素子101～104と、ダイオード105及び106と、コンデンサ12A及び13Aとを備える発光画素である。また、画素10Bは、薄膜トランジスタスイッチ11Bと、有機EL素子107～110と、ダイオード111及び112と、コンデンサ12B及び13Bとを備える発光画素である。ここで、画素10Aの各構成要素及びそれらの接続状態を説明する。

30

## 【0046】

電源線V2は、2行目の画素行に配置され、直列接続された有機EL素子102及び104の接続点に接続され、電源線制御回路3から供給された正負の電圧パルスを当該接続点に印加する。これにより、有機EL素子101～104には、正負の双方向電流が供給される。

## 【0047】

40

なお、本実施の形態では、n行ごとに配置された電源線V1～Vnは、同じパルス電圧が同じタイミングで印加されるので、全ての電源線が接続された共通線となっていてよい。これにより、電源線制御回路3の駆動負荷が低減される。

## 【0048】

有機EL素子101～104は、電流駆動型の発光素子であり、ブリッジ接続されている。

## 【0049】

薄膜トランジスタスイッチ11Aは、例えば、nチャネルのMOSFETであり、入力された映像信号に基づいてゲート-ソース間に閾値電圧以上の電圧が印加されることにより、ドレイン-ソース間を導通状態とするスイッチ素子である。

## 【0050】

50

コンデンサ 12 A は、電源線 V 2 から供給された電流を、上記ダイオードブリッジを介して充電し、また、充電された電荷を、上記ダイオードブリッジを介して電源線 V 2 へ放電する反転コンデンサである。

#### 【0051】

コンデンサ 13 A は、データ線 D T 1 から供給されたデータ電圧に対応した電荷を、ダイオード 105 を介して蓄積し、また、蓄積された電荷を、ダイオード 106 を介して消去線 E 2 へ放電する。

#### 【0052】

消去線 E 2 は、2 行目の画素行に配置され、消去電圧が印加されることにより、コンデンサ 13 A に蓄積された電荷を放電する。

10

#### 【0053】

なお、本実施の形態では、n 行ごとに配置された消去線 E 1 ~ E n は、同じ消去電圧が同じタイミングで印加されるので、全ての消去線が接続された共通線となっていてもよい。これにより、消去線制御回路 5 の駆動負荷が低減される。

#### 【0054】

第 3 の整流素子である有機 E L 素子 103 のカソードと第 1 の整流素子である有機 E L 素子 101 のアノードとの接続点にコンデンサ 12 A の一方の電極である第 1 電極が接続され、コンデンサ 12 A の他方の電極である第 2 電極は基準電極である G N D 電極に接続されている。また、第 4 の整流素子である有機 E L 素子 104 のカソードと第 2 の整流素子である有機 E L 素子 102 のアノードとの接続点に電源線 V 2 が接続されている。また、有機 E L 素子 101 のカソード及び有機 E L 素子 102 のカソードには、薄膜トランジスタスイッチ 11 A のドレインが接続され、有機 E L 素子 103 のアノード及び有機 E L 素子 104 のアノードには、薄膜トランジスタスイッチ 11 A のソース及び走査線 S C 2 が接続されている。また、薄膜トランジスタスイッチ 11 A のゲート - ソース端子間には、コンデンサ 13 A が接続されている。また、薄膜トランジスタスイッチ 11 A のゲートには、ダイオード 105 のカソード及びダイオード 106 のアノードが接続されている。また、第 5 の整流素子であるダイオード 105 のアノードは、データ線 D T 1 に接続され、第 6 の整流素子であるダイオード 106 のカソードには、消去線 E 2 が接続されている。薄膜トランジスタスイッチ 11 A と、コンデンサ 13 A と、ダイオード 105 と、ダイオード 106 とは、スイッチ部を構成する。

20

#### 【0055】

上記回路構成により、薄膜トランジスタスイッチ 11 A のゲート - ソース間に、閾値電圧よりも十分大きいデータ電圧がデータ線 D T 1 及びダイオード 105 を介して印加されることにより、薄膜トランジスタスイッチ 11 A のドレイン - ソース間はオン抵抗の低い導通状態となる。そして、電源線 V 2 から供給される正負の電流に対して、上記ダイオードブリッジにより薄膜トランジスタスイッチ 11 A に流れる電流は单方向となるため、单一のスイッチで有機 E L 素子 101 ~ 104 のオンオフ制御が可能となる。

30

#### 【0056】

つまり、有機 E L 素子 101 ~ 104 で構成された上記ダイオードブリッジは、薄膜トランジスタスイッチ 11 A が導通状態の場合に、正の電圧パルス及び負の電圧パルスが交互に印加されることにより発生する双方向電流を整流し、当該整流された電流を薄膜トランジスタスイッチ 11 A に单方向に流し、当該整流された電流が流れることにより発光する発光整流部を構成している。

40

#### 【0057】

なお、本実施の形態において、ダイオードブリッジの構成要素を、全て発光素子である有機 E L 素子としているが、4 つの素子のうち少なくとも一素子を発光素子とすればよく、その他を非発光のダイオードで構成することも可能である。

#### 【0058】

また、本実施の形態では、発光素子として有機 E L 素子を用いているが、当該発光素子は電流駆動型の発光素子であればよく、例えば、無機 E L 素子であってもよい。

50

## 【0059】

次に、走査線制御回路4について説明する。走査線制御回路4は、サブフィールド処理回路2からの制御信号により、書き込み期間において発光画素行を選択するための走査信号を、走査線を介して画素部に出力する。

## 【0060】

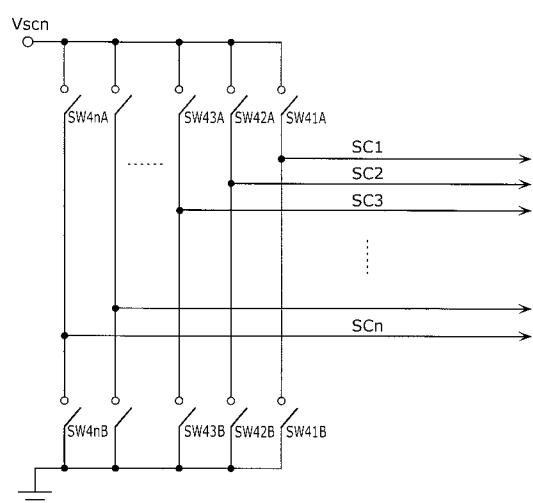

図3は、本発明の実施の形態1に係る表示装置が有する走査線制御回路の内部回路図である。走査線制御回路4は、出力ラインである走査線SC1～SCnに、それぞれ非選択電圧Vscnまたは走査信号であるGND電圧を供給するための2つのスイッチをライン毎に配置した回路構成となっている。画素行数がnである場合には、走査線制御回路4は、n本の走査線SC1～SCnを介して画素部10に接続されている。各走査線には、走査線制御回路4の信号に応じて、任意の順序で1ライン毎に走査線SC1～SCnに非選択電圧VscnまたはGND電圧を供給することが可能である。もちろん、走査線SC1、SC2、…SCnという様に、行順次に走査電圧を印加することも可能であり、あるいは、全ての走査線に対し同時に非選択電圧VscnまたはGND電圧を供給することも可能である。非選択電圧パルスまたはGND電圧パルスを印加するタイミングについては、後述する。

10

## 【0061】

図3に記載された回路において、例えば、走査線SC1にGND電圧を印加し、他の走査線に非選択電圧Vscnを印加する場合には、走査線制御回路4は、スイッチSW41B及びスイッチSW42A、SW43A、…SW4nAをON状態とし、スイッチSW41A及びスイッチSW42B、SW43B、…SW4nBをOFF状態とする。

20

## 【0062】

次に、消去線制御回路5について説明する。消去線制御回路5は、サブフィールド処理回路2からの制御信号により、コンデンサS13Aに保持された、データ信号に対応した電圧を消去するための消去信号を、消去線を介して薄膜トランジスタスイッチのゲートに出力する。

20

## 【0063】

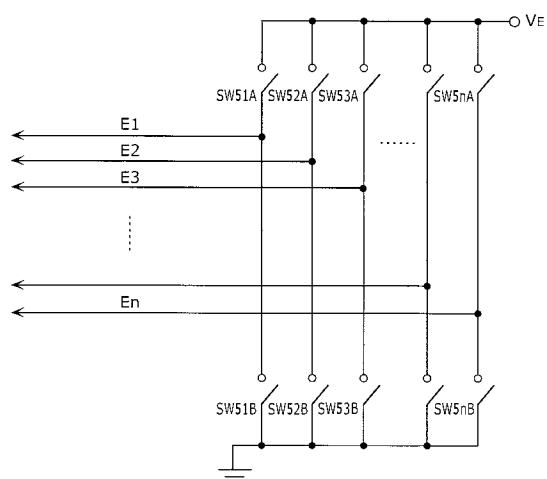

図4は、本発明の表示装置が有する消去線制御回路の内部回路図である。消去線制御回路5は、発光画素行ごとに配置された消去線E1～Enに、それぞれ消去電圧VEもしくはGND電圧を供給するための2つのスイッチをライン毎に配置した回路構成となっている。画素行数がnである場合は、消去線制御回路5は、n本の消去線E1～Enを介して画素部10に接続されている。各消去線には、消去線制御回路5の信号に応じて、任意の消去線に消去電圧VEまたはGND電圧を供給することが可能である。勿論、消去線E1、E2、…Enという様に、行順次に消去電圧を印加することも可能であり、あるいは、全ての消去線に対しを同時に消去電圧VEやGND電圧を供給することも可能である。消去電圧パルスを印加するタイミングについては、後述する。

30

## 【0064】

図4に記載された回路において、例えば、消去線E1に消去電圧VEを印加し、他の走査線にGND電圧を印加する場合には、消去線制御回路5は、スイッチSW51A及びスイッチSW52B、SW53B、…SW5nBをON状態とし、スイッチSW51B及びスイッチSW52A、SW53A、…SW5nAをOFF状態とする。

40

## 【0065】

次に、電源線制御回路3について説明する。電源線制御回路3は、サブフィールド処理回路2からの制御信号により、正負の電圧パルスを交互に発生して各電源線に印加するパルス発生部である。

## 【0066】

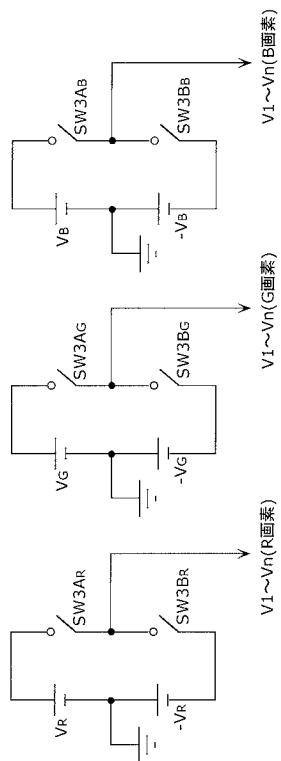

図5は、本発明の表示装置が有する電源線制御回路の内部回路図である。同図に記載された電源線制御回路3は、各画素がR(赤色)画素、G(緑色)画素、B(青色)画素のいずれかの画素であって各発光素子の閾値電圧が異なる場合に、色毎に異なる電源電圧を

50

印加できる回路構成となっている。例えば、赤色に対しては  $V_R$  が、緑色に対しては  $V_G$  が、青色に対しては  $V_B$  が印加されるため、それぞれ所望の振幅に応じた正パルス用のスイッチ及び負パルスの用スイッチが配置され、R画素、G画素、B画素独立にパルス電源電圧を印加することが可能となっている。なお、これら3つのパルス電源電圧は同一であってもよい。その場合には、一対の正パルス用のスイッチ及び負パルス用のスイッチのみで回路構成が可能となる。

#### 【0067】

電源線制御回路3は、画素部10の電源線に正負の電源電圧を印加するために、例えば、R画素の電源線には、任意の正の直流電圧  $V_R$  及び任意の負の直流電圧 -  $V_R$  が直列に接続され、その中点を GND 電位とし、直列接続されていない方の端子に、それぞれ、スイッチ SW3A<sub>R</sub> 及び SW3B<sub>R</sub> が接続されている。例えば、R画素に正の電圧  $V_R$  を供給する場合には、スイッチ SW3A<sub>R</sub> を ON 状態にする。また負の電圧 -  $V_R$  を供給する場合には、スイッチ SW3B<sub>R</sub> を ON 状態にする。ここで、正負の電圧振幅は同一でも異なっても良い(図5では、電圧振幅を同じとしている)。

10

#### 【0068】

次に、データ線制御回路6について説明する。データ線制御回路6は、サブフィールド処理回路2からの制御信号により、書き込み期間において走査線制御回路4から出力される走査信号に同期して、薄膜トランジスタスイッチの導通及び非導通を切り換えるための、映像信号に対応したデータ信号を、データ線を介して薄膜トランジスタスイッチに出力する。データ線制御回路6も走査線制御回路4とほぼ同様の回路構成であるため、図示を省略するが、映像信号に応じた駆動信号により、画素部10の解像度に応じた画素列数m本のデータ線を同時に制御可能とするためのメモリ機能を有している。

20

#### 【0069】

##### <表示装置の動作>

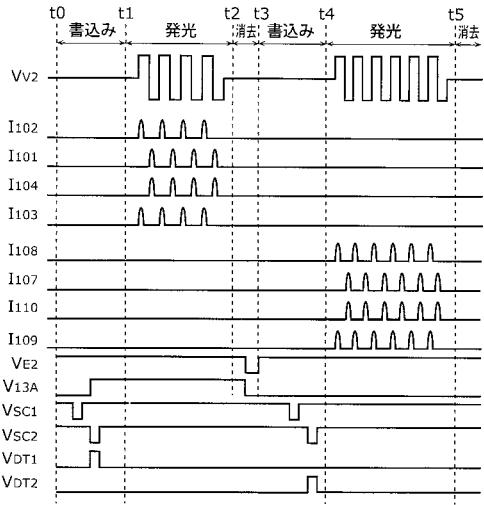

以下、図2、図6及び図7A～図7Dを用いて、表示装置1の動作について述べる。図6は、本発明の実施の形態1に係る表示装置の駆動タイミングチャートである。

#### 【0070】

##### [書き込み期間]

書き込み期間における動作は、入力された映像信号に基づき、各画素の有する薄膜トランジスタスイッチの導通状態及び非導通状態を切り換える第1ステップである。このため、走査線制御回路4は、走査線ごとに、非選択電圧  $V_{scn}$  または、選択電圧である GND 電圧を印加する。これにより、選択された走査線が接続された画素行に属する画素に対して、対応するデータ線からのデータ電圧が印加され、薄膜トランジスタスイッチのゲート電圧が制御される。

30

#### 【0071】

図6の駆動タイミングチャートは、例として、走査線 SC1 より行順次に走査した場合の、走査線 SC2 に接続された画素行に属する画素 10A 及び 10B についての動作を表している。また、サブフィールド処理回路2による処理により、図6におけるサブフィールド期間  $t_0 \sim t_2$  では、画素 10A が発光状態で画素 10B が非発光状態であり、図6におけるサブフィールド期間  $t_3 \sim t_5$  では、画素 10A が非発光状態で画素 10B が発光状態であるものと仮定している。

40

#### 【0072】

時刻  $t_0 \sim$  時刻  $t_1$  及び時刻  $t_3 \sim$  時刻  $t_4$  では、走査線制御回路4は、各走査線に対し行順次に走査信号である GND 電圧を供給し、それ以外の非選択の走査線に非選択電圧  $V_{scn}$  を供給する。

#### 【0073】

時刻  $t_0 \sim$  時刻  $t_1$  の期間において、まず、走査線制御回路4は、走査線 SC1 に対し GND 電圧を供給し、それ以外の走査線に非選択電圧  $V_{scn}$  を供給する。このとき、データ線 DT1 の電圧  $V_{DT1}$  が GND 電圧であるので、走査線 SC1 及びデータ線 DT1 に接続された画素に対して、書き込みは発生せず、当該画素はオフ状態となる。次に、走

50

査線制御回路4は、走査線SC2にGND電圧を供給し、その他の走査線には、非選択電圧Vscnを供給する。このとき、データ線DT1の電圧V<sub>DT1</sub>がVdataであるので、書き込みが発生し、走査線SC2及びデータ線DT1が接続された画素10Aの薄膜トランジスタスイッチ11Aはオン状態となる。

#### 【0074】

上述した時刻t0～時刻t1の期間における走査線制御回路4の動作は、発光画素行を選択するための走査信号を、発光画素行ごとに配置された走査線を介して薄膜トランジスタスイッチのソース電極に出力する走査信号出力ステップに相当する。また、上述した時刻t0～時刻t1の期間におけるデータ線制御回路6の動作は、走査信号出力ステップで出力された走査信号に同期して、薄膜トランジスタスイッチの導通及び非導通を切り換えるためのデータ信号を、発光画素列ごとに配置されたデータ線を介して薄膜トランジスタスイッチのゲート電極に出力するデータ信号出力ステップに相当する。

10

#### 【0075】

図7Aは、本発明の表示装置が有する画素への書き込み動作を説明する状態遷移図である。すなわち、データ線DT1にVdataが印加された場合、図7Aに示されるように、データ線DT1 ダイオード105 コンデンサ13A 走査線SC2の順に電流が流れ、コンデンサ13Aが充電される。

#### 【0076】

このとき、コンデンサ13Aの充電電圧は(Vdata - V<sub>GND</sub>)となり、画素10Aの薄膜トランジスタスイッチ11Aのゲート-ソース間に保持される。この保持電圧が薄膜トランジスタスイッチ11Aの閾値電圧以上となった場合に、薄膜トランジスタスイッチ11Aがオン状態となり、走査線SC2の書き込み動作が終了する。

20

#### 【0077】

なお、非選択電圧Vscnは、信号電圧Vdata以上であることが望ましい。これにより、非選択の走査線にはVdata以上の非選択電圧Vscnが印加されているので、画素10Aで発生したコンデンサ13Aへの充電動作は起こらず、選択した走査線が接続された画素行のみに対して、コンデンサへの充電動作が起こる。

#### 【0078】

その後、走査線SC2の電圧をVdata以上に保持することで、コンデンサ13Aに書き込まれた保持電圧は、データ線DT1の電圧V<sub>DT1</sub>がVdataであってもGNDであっても、ダイオード105が逆バイアス状態となるため変動しない。

30

#### 【0079】

時刻t0～時刻t1の期間の次フィールドである時刻t3～時刻t4の期間においては、書き込み動作の対象となる画素が、図2に記載された画素10Bとなっている。走査線制御回路4は、時刻t0～時刻t1の期間において画素10Aに対して実行した書き込み動作と同様の動作を、画素10Bに対して実行する。

#### 【0080】

以上のように、所望の画素に対し走査線毎に書き込み動作を行うことで、サブフィールド毎に全画素に対して書き込み制御を行うことが可能となる。

#### 【0081】

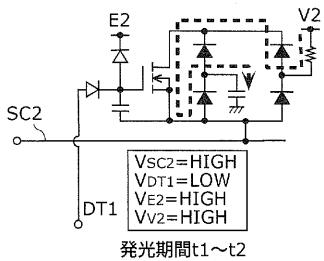

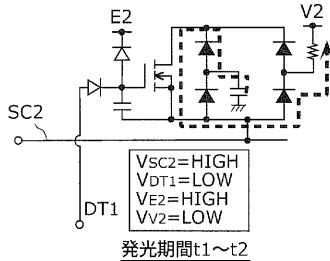

##### [発光期間]

発光期間では、各画素に接続された電源線に正負のパルス電圧を供給し、書き込み期間においてオン状態にされた画素に対して発光動作を行う。この発光動作は第2ステップに相当する。

40

#### 【0082】

時刻t1～時刻t2の期間において、電源線制御回路3は、まず、電源線V2の電圧V<sub>V2</sub>を有機EL素子102及び103の閾値電圧以上の正の電圧に保持する。

#### 【0083】

図7Bは、本発明の表示装置が有する画素への第1の発光動作を説明する状態遷移図である。同図に示されたように、電源線V2の電圧V<sub>V2</sub>をHIGHレベルとすることによ

50

り、書き込み期間  $t_0 \sim t_1$ において、薄膜トランジスタスイッチ 11A がオン状態となっている画素 10A に、電源線 V<sub>2</sub> 有機 EL 素子 102 薄膜トランジスタスイッチ 11A 有機 EL 素子 103 コンデンサ 12A の経路で発光電流が流れる。なお、図 6 には、上記発光電流を、有機 EL 素子 102 に流れる発光電流  $I_{102}$  及び有機 EL 素子 103 に流れる発光電流  $I_{103}$  として表している。その後、この発光電流により、コンデンサ 12A の電位が上昇し、電圧 V<sub>v2</sub> と有機 EL 素子 102 及び 103 の閾値電圧とがバランスした時に上記発光電流は停止する。

#### 【0084】

時刻  $t_1 \sim t_2$  に期間において、電源線制御回路 3 は、次に、電源線 V<sub>2</sub> の電圧 V<sub>v2</sub> を、その絶対値が有機 EL 素子 101 及び 104 の閾値電圧以上となる負の電圧に保持する。

10

#### 【0085】

図 7C は、本発明の表示装置が有する画素への第 2 の発光動作を説明する状態遷移図である。同図に示されたように、電源線 V<sub>2</sub> の電圧 V<sub>v2</sub> を LOW レベル（負電圧）とすることにより、書き込み期間  $t_0 \sim t_1$  において薄膜トランジスタスイッチ 11A がオン状態となっている画素 10A に、コンデンサ 12A 有機 EL 素子 101 薄膜トランジスタスイッチ 11A 有機 EL 素子 104 電源線 V<sub>2</sub> の経路で発光電流が流れる。なお、図 6 には、上記発光電流を、有機 EL 素子 101 に流れる発光電流  $I_{101}$  及び有機 EL 素子 104 に流れる発光電流  $I_{104}$  として表している。その後、この発光電流により、コンデンサ 12A の電位が下降し、電圧 V<sub>v2</sub> と有機 EL 素子 101 及び 104 の閾値電圧とがバランスした時に上記発光電流は停止する。

20

#### 【0086】

図 7B 及び図 7C に示されたように、コンデンサ 12A は、有機 EL 素子 101 ~ 104 で構成されたダイオードブリッジら GND 電極へ流れる電流により充電され、当該電流と逆方向に流れる電流により放電する。これにより、画素 10A のダイオードブリッジは、薄膜トランジスタスイッチ 11A が導通状態である場合に、有機 EL 素子 102 及び 104 の接続点とコンデンサ 12A との電位差により発生する充電電流及び放電電流に応じて、双方向において発光する。

#### 【0087】

また、薄膜トランジスタスイッチが導通状態となった画素は、電源線制御回路 3 が正負の交流電圧パルスを全画素の上記接続点に一斉に印加することにより一斉に発光する。

30

#### 【0088】

また、書き込み期間  $t_0 \sim t_1$  においてオフ状態となっている画素 10B には、発光電流は流れない。

#### 【0089】

上述した発光期間における画素の発光電流の積算値は、電圧 V<sub>v2</sub> をパルス状に正負に印加する回数に比例するため、発光期間における電源線の電圧パルス数と書き込み期間における薄膜トランジスタスイッチのオンオフ制御により、各画素の発光輝度を制御することが可能となる。

#### 【0090】

時刻  $t_1 \sim t_2$  の期間の次フィールドである時刻  $t_4 \sim t_5$  の期間においては、発光動作の対象となる画素が、図 2 に記載された画素 10B となっている。電源線制御回路 3 は、時刻  $t_1 \sim t_2$  の期間において画素 10A に対して実行した書き込み動作と同様の動作を、画素 10B に対して実行する。

40

#### 【0091】

以上のように、事前に書き込み動作を行った画素に対して、サブフィールド毎に一斉に発光動作を行うことが可能となる。

#### 【0092】

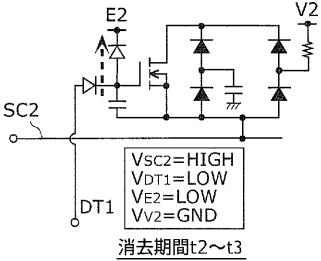

##### [消去期間]

消去期間では、書き込み動作によりオン状態となった薄膜トランジスタスイッチのゲー

ト電圧を再びゼロにするための消去電圧を印加し、画素を消灯させる消去動作を行う。

【0093】

時刻  $t_2$  ~ 時刻  $t_3$  に期間において、電源線制御回路3は電圧  $V_{v_2}$  をGND電圧にし、走査線制御回路4は走査線SC2を非選択電位である非選択電圧  $V_{scn}$  に保持する。この状態で、消去線制御回路5は消去線E2をGND電圧とする。

【0094】

図7Dは、本発明の表示装置が有する画素への消去動作を説明する状態遷移図である。同図に示されるように、消去線E2の電圧  $V_{E_2}$  をLOWレベル(GND電圧)とすることにより、書き込み期間  $t_0$  ~  $t_1$  に薄膜トランジスタスイッチ11Aのゲート-ソース間に保持された保持電圧をゼロにするよう、コンデンサ13A ダイオード106 消去線E2の経路で放電電流が流れる。

10

【0095】

つまり、ダイオードブリッジが発光している発光画素は、消去線制御回路5から消去信号が印加されることにより消灯する。

【0096】

この消去動作以降では、再び電源線V2に正負のパルス電圧を印加しても、画素回路に発光電流は流れない。

【0097】

時刻  $t_5$  以降の期間においては、消去動作の対象となる画素が、図2に記載された画素10Bとなっている。消去線制御回路5は、時刻  $t_2$  ~ 時刻  $t_3$  の期間において画素10Aに対して実行した消去動作と同様の動作を、画素10Bに対して実行する。

20

【0098】

以上説明した表示装置1の動作は、書き込み動作、発光動作及び消去動作という一連の単位を1サブフィールドとし、当該サブフィールドを繰り返し実行する。

【0099】

本実施の形態においては、書き込み動作における走査線電圧制御は順次に走査線を走査することにより実行され、発光動作における電源線電圧制御及び消去動作における消去線電圧制御は、全画素一斉に実行される。

【0100】

本実施の形態によれば、画素の有する薄膜トランジスタスイッチは、定電流源である必要はなく、画素回路のオンオフ状態を切り換えるスイッチ機能を有していればよい。よって、例えば、薄膜トランジスタスイッチに印加する信号電圧、つまり、ゲート-ソース間電圧を、ドレイン-ソース間電圧  $V_{ds}$  に対して十分大きく設定しておくことにより、薄膜トランジスタの線形領域を利用することができるので、ドレイン電流  $I_d$  のオン抵抗を限りなく0にすることが可能となる。よって、薄膜トランジスタスイッチのドレイン-ソース間に発光電流が流れるときの電圧降下を低減でき、表示パネルの電力損失を大幅に低減することができる。つまり、画素回路の発光電流は、薄膜トランジスタの飽和領域を利用した定電流源により生成されるのではなく、電源線制御回路3から供給される正負のパルス信号及び画素部毎に設けられた薄膜トランジスタスイッチのオンオフ動作により実現される。これにより、定電流源を用いることなく発光電流のばらつきを抑制しつつ低損失なディジタル階調制御が可能となる。

30

40

【0101】

また、本発明の表示装置により、損失発生要因となるカレントミラー回路が不要となり、損失を低減可能となる。

【0102】

(実施の形態2)

実施の形態1では、書き込み期間と発光期間とを複数の画素行でまとめて時間的に分割して動作させているが、各画素行において書き込み動作終了から発光動作開始までの待ち時間が生ずるため、全体の駆動時間が長くなる。本実施の形態では、例えば、走査線SC1が接続された画素行の書き込み動作が終了した際に、走査線SC2が接続された画素行の書

込み動作が終了するのを待たずに、直ちに発光動作に移行する場合の表示装置について説明する。

#### 【0103】

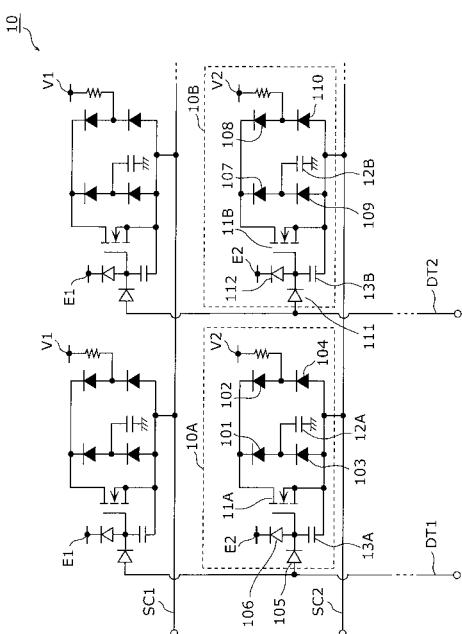

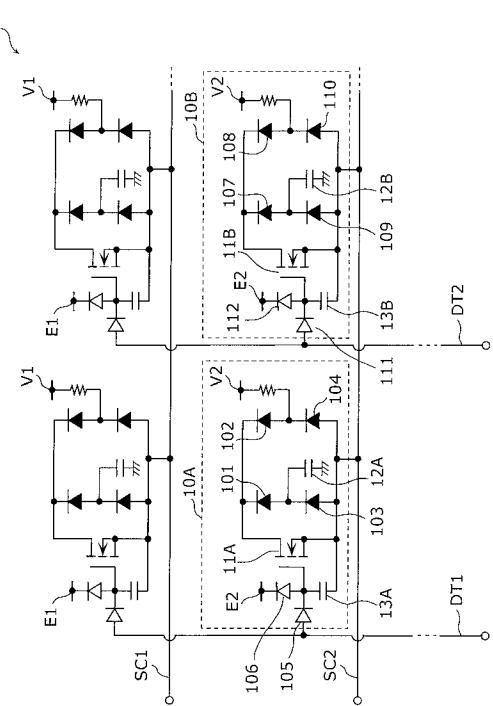

図8は、本発明の実施の形態2に係る表示装置が有する画素部の回路構成図である。本実施の形態に係る表示装置が有する画素部20には、実際にはディスプレイの解像度( $m \times n$ )に応じたマトリクス状に配置された複数の画素が配置されているが、図8には、画素部20の一部である、隣接する4画素が記載されている。図8に記載された画素部20は、隣接する4つの画素と、画素列ごとに配置された信号線DT1及びDT2と、画素行ごとに配置された走査線SC1及びSC2と、消去線E1及びE2とを備える。

#### 【0104】

また、画素部20の有する複数の画素は、全て同じ回路構成となっており、例えば、図8に記載された画素20Aは、薄膜トランジスタスイッチ11Aと、有機EL素子101～104と、ダイオード105及び106と、コンデンサ12A及び13Aとを備える。また、画素10Bは、薄膜トランジスタスイッチ11Bと、有機EL素子107～110と、ダイオード111及び112と、コンデンサ12B及び13Bとを備える。ここで、画素10Aの各構成要素及びそれらの接続状態を説明する。図8に記載された画素部20の回路構成は、図2に記載された画素部10の回路構成と比較して、電源線V1及びV2がなく、電源線V1及びV2の代わりに、走査線SC1及びSC2が有機EL素子の直列接続点に接続されている点が異なる。以下、図2に記載された画素部10と同じ点は説明を省略し、画素20Aの各構成要素及びそれらの接続状態について異なる点のみ説明する。

10

#### 【0105】

有機EL素子104のカソードと有機EL素子102のアノードとの接続点に走査線SC2が接続されている。

#### 【0106】

走査線SC2は、2行目の画素行に配置され、上記接続点に接続され、走査線制御回路4から供給された正負の電圧パルスを当該接続点に印加する。これにより、有機EL素子101～104には、正負の電流が供給される。つまり、走査線SC2は、画素行の選択及び非選択を行うための走査電圧を画素に印加する機能と、発光電流を生成するための正負の電圧パルスを画素に印加する機能とを兼用している。

20

#### 【0107】

コンデンサ12Aは、走査線SC2から供給された電流を、4つの有機EL素子からなるダイオードブリッジを介して充電し、また、充電された電荷を、上記ダイオードブリッジを介して走査線SC2へ放電する。

#### 【0108】

上記回路構成により、薄膜トランジスタスイッチ11Aのゲート-ソース間に、薄膜トランジスタスイッチ11Aの閾値電圧よりも十分大きい信号電圧をデータ線DT1及びダイオード105を介して印加することにより、薄膜トランジスタスイッチ11Aのドレイン-ソース間はオン抵抗の低い導通状態となる。そして、走査線SC2から供給される正負の電流に対して、上記ダイオードブリッジにより薄膜トランジスタスイッチ11Aに流れる電流は単方向となるため、单一のスイッチで有機EL素子101～104のオンオフ制御が可能となる。

30

#### 【0109】

次に、走査線制御回路4について説明する。走査線制御回路4は、サブフィールド処理回路2からの制御信号により、書き込み期間において各走査線に走査電圧を印加する。

#### 【0110】

図9は、本発明の実施の形態2に係る表示装置が有する走査線制御回路の内部回路図である。同図に記載された走査線制御回路は2つの機能を持ち、1つは画素部20に正負のパルス電圧を印加する機能であり、もう1つは、正負のパルス電圧にバイアス電圧-Vbを重畠させた走査電圧を画素行毎に印加する機能である。走査線制御回路は、走査線SC

40

10

20

30

40

50

1 ~ S C n に、それぞれ、正パルス電圧 V f 、負パルス電圧 - V f 、走査電圧 ( V f - V b ) 及び走査電圧 ( - V f - V b ) を供給するためのパルス発生用スイッチ SW 4 A H 及び SW 4 A L と、走査線に対応して配置されたスイッチ SW 4 1 A ~ SW 4 n A 及び SW 4 1 B ~ SW 4 n B とを備える。画素行数が n である場合には、走査線制御回路は、n 本の走査線 S C 1 ~ S C n を介して画素部 2 0 に接続されている。各走査線には、走査線制御回路の信号に応じて、任意の順序で 1 画素行毎に走査線 S C 1 ~ S C n に走査電圧を供給することが可能である。もちろん、走査線 S C 1 、 S C 2 、 ··· 、 S C n という様に、行順次に走査電圧を印加することも可能であり、あるいは、全ての走査線に対し同時に走査電圧を供給することも可能である。走査電圧パルスを印加するタイミングについては、後述する。

10

#### 【 0 1 1 1 】

図 9 に記載された回路において、画素部 2 0 の走査線に正負のパルス電圧を印加するために、例えば、全画素に正のパルス電圧 V f を供給する場合には、パルス発生用スイッチ SW 4 A H を ON 状態、 SW 4 A L を OFF 状態、スイッチ SW 4 1 A 、 SW 4 2 A 、 ··· 、 SW 4 n A を ON 状態、スイッチ SW 4 1 B 、 SW 4 2 B 、 ··· 、 SW 4 n B を OFF 状態とする。また、全画素に負のパルス電圧 ( - V f ) を供給する場合には、パルス発生用スイッチ SW 4 A L を ON 状態、パルス発生用スイッチ SW 4 A H を OFF 状態、スイッチ SW 4 1 A 、 SW 4 2 A 、 ··· 、 SW 4 n A を ON 状態、スイッチ SW 4 1 B 、 SW 4 2 B 、 ··· 、 SW 4 n B を OFF 状態にする。

20

#### 【 0 1 1 2 】

また、図 9 に記載された回路において、例えば、走査線 S C 1 に走査電圧 ( V f - V b ) を印加し、その他の走査線に正のパルス電圧を印加する場合には、走査線制御回路は、パルス発生用スイッチ SW 4 A H を ON 状態、 SW 4 A L を OFF 状態、スイッチ SW 4 1 B 及びスイッチ SW 4 2 A 、 SW 4 3 A 、 ··· 、 SW 4 n A を ON 状態、スイッチ SW 4 1 A 及びスイッチ SW 4 2 B 、 SW 4 3 B 、 ··· 、 SW 4 n B を OFF 状態とする。

20

#### 【 0 1 1 3 】

また、図 9 に記載された回路において、例えば、走査線 S C 1 に走査電圧 ( - V f - V b ) を印加し、その他の走査線に負のパルス電圧を印加する場合には、走査線制御回路は、パルス発生用スイッチ SW 4 A L を ON 状態、 SW 4 A H を OFF 状態、スイッチ SW 4 1 B 及びスイッチ SW 4 2 A 、 SW 4 3 A 、 ··· 、 SW 4 n A を ON 状態、スイッチ SW 4 1 A 及びスイッチ SW 4 2 B 、 SW 4 3 B 、 ··· 、 SW 4 n B を OFF 状態とする。

30

#### 【 0 1 1 4 】

##### < 表示装置の動作 >

以下、図 8 、図 10 及び図 11 を用いて、表示装置の動作について述べる。図 10 は、本発明の実施の形態 2 に係る走査線制御回路の駆動タイミングチャートであり、図 11 は、本発明の実施の形態 2 に係る表示装置の動作タイミングチャートである。本実施の形態において、実施の形態 1 と動作面で異なる点は、図 10 に表された走査線制御回路が、常に正負のパルス電圧を全画素行に印加していることと、各画素行の選択（書き込み）を行う走査信号である走査電圧が発光動作のための上記正負パルスに重畠された電圧となっていることである。なお、図 10 の上部には、1 行目の走査線 S C 1 における期間（消去・書き込み、発光）を明示している。

40

#### 【 0 1 1 5 】

上記走査電圧パルスを発光動作のための正負パルスに重畠することにより、各画素に結線される配線の数を、実施の形態 1 に比べて少なくすることが可能である。さらに、書き込み動作終了後の待ち時間が存在しないため、全体の駆動時間を大幅に短縮することが可能である。最も短くすることが可能となるのは、上記走査信号を全画素行の書き込みに必要な時間のみで駆動した場合である。この場合、発光時間は、他のラインの書き込み動作を行っている時間を充当することとなる。

50

## 【0116】

以下、動作面において実施の形態1と大きく異なる、書き込み動作と発光動作を中心 に説明する。

## 【0117】

図10に示されるように、走査線制御回路4は、常に、全ての走査線に対して同じタイミングで正負のパルス電圧を交互に各走査線へ出力している。このとき、上記正負のパルス電圧は、整流された発光電流となり、発光整流部である有機EL素子のダイオードブリッジ回路を流れる。よって、有機EL素子の閾値電圧をVe1と定義した場合、Ve1よりも高い正のパルス電圧Vfもしくは、(-Ve1)よりも低い負のパルス電圧(-Vf)が供給されている。

10

## 【0118】

上記正負のパルス電圧が、常に、各発光画素へ供給されている状態で、書き込み動作において、各画素の有する薄膜トランジスタスイッチのオンオフ状態を制御する。この場合、書き込み動作時の走査電圧は、重畠元となる正負のパルス電圧に依存し、(Vf-Vb)、または(-Vf-Vb)となっている。この走査電圧は書き込みを行うタイミングにより交互に変化しているため、どちらの走査電圧の場合でも正しく書き込みを行えるようなデータ電圧Vdataが必要となる。このとき、パルス電圧Vfよりも十分振幅が大きなバイアス電圧Vbを設定することで、より書き込み動作を正確に行うことが出来る。例えば、図10において、走査線SC1及びSC2は、書き込み動作のための走査電圧は(Vf-Vb)であるのに対し、走査線SC3及びSC4は、書き込み動作のための走査電圧は(-Vf-Vb)となっている。

20

## 【0119】

また、データ電圧Vdataは、走査電圧として最小値となる値(つまり-Vf-Vb)を、書き込み電圧のオフ状態の電圧とし、書き込み電圧のオン電圧を各画素の薄膜トランジスタスイッチのゲート-ソース間の閾値電圧以上となる値に設定する。これにより、例えば、図8の画素20Aでは、データ線DT1 ダイオード105 コンデンサ13A ダイオード104 走査線SC2(-Vf-Vb)の順に電流が流れ、コンデンサ13Aを充電する。このコンデンサ13Aの電圧が薄膜トランジスタスイッチ11Aの閾値電圧以上となった場合に薄膜トランジスタスイッチ11Aがオン状態となり、走査線SC2による2行目の画素行の書き込み動作が終了する。

30

## 【0120】

次に、書き込まれた画素は、消去動作が行われるまでの間、正負のパルス電圧により、直ちに発光動作を行う。この発光動作は、実施の形態1で述べた発光動作と同様である。図11のタイミングチャートでは、時刻t10~t13のサブフィールド期間では1行目の画素(図8の左上部の画素)が発光し、時刻t14~t17のサブフィールド期間では2行目の画素20Bが発光し、時刻t16及びt17以降のサブフィールド期間では上記両方の画素が発光する例を表している。例えば、画素20Bでは、時刻t14で書き込み動作が行われ、時刻t14~t15の期間において、有機EL素子107~110で構成されるダイオードブリッジが、走査線制御回路4から有機EL素子108及び110の接続点に供給された正負のパルス電圧により発生する双方向電流を整流し、当該整流された電流を薄膜トランジスタスイッチ11Bに単方向に流し、当該整流された電流が流れることにより発光する。

40

## 【0121】

これにより、走査線制御回路4は、正負の交流電圧パルスを常に上記接続点に出力し、また、走査信号である走査電圧(Vf-Vb)または(-Vf-Vb)を行順次に上記接続点に出力し、データ信号により薄膜トランジスタスイッチが行順次に導通状態となつた発光画素は、行順次に発光する。

## 【0122】

一方、書き込まれなかった画素は、上記正負のパルス電圧を印加されても、薄膜トランジスタスイッチがオフ状態であるため発光しない。

50

**【 0 1 2 3 】**

次に、消去線制御回路 5 は、画素行ごとに配置された消去線  $E_1 \sim E_n$  に対して、行順次に消去電圧  $V_E$  を供給する。これにより、発光動作していた画素は、行順次に消灯する。

**【 0 1 2 4 】**

上記で説明した書き込み動作、発光動作及び消灯動作が、他の画素行についても順次実行されるが、このとき、非選択画素に対するデータ電圧  $V_{data}$  の干渉の有無が重要となる。

**【 0 1 2 5 】**

実施の形態 1 では、書き込み動作と発光動作とが時間的に分離されていたため、発光動作中にデータ線の電位が変動することが無かった。これに対し、本実施の形態においては、書き込み動作が終わったラインに対し、直ちに発光動作に移行するため、発光動作中にデータ線電位が変動することになる。このとき、データ線電位は、正負のパルス電圧振幅に対して十分低い電圧 ( $-V_b$ ) を基準とした電位であるため、例えば、画素 20A のダイオード 105 のカソードが  $-V_f$  近傍であることに対し、ダイオード 105 のアノードの電位であるデータ線電位は十分低い電位となるため、ダイオード 105 は常に逆バイアス状態となるので、発光期間において、データ線電位を変動させても、既に書き込まれたラインに対する動作に影響は無い。

10

**【 0 1 2 6 】**

本実施の形態によれば、実施の形態 1 と同様に、画素の有する薄膜トランジスタスイッチは、定電流源である必要はなく、画素回路のオンオフ状態を切り換えるスイッチ機能を有していればよい。よって、例えば、薄膜トランジスタスイッチに印加する信号電圧、つまり、ゲート - ソース間電圧を、ドレイン - ソース間電圧  $V_{ds}$  に対して十分大きく設定しておくことにより、薄膜トランジスタの線形領域を利用することができるので、ドレン電流  $I_d$  のオン抵抗を限りなく 0 にすることが可能となる。よって、薄膜トランジスタスイッチのドレン - ソース間に発光電流が流れるとときの電圧降下を低減でき、表示パネルの電力損失を大幅に低減することができる。また、本発明の表示装置により、損失発生要因となるカレントミラー回路が不要となり、損失を低減可能となる。

20

**【 0 1 2 7 】**

さらに、本実施の形態では、書き込み期間と発光期間とを重畠させて駆動することができるため、総駆動時間を短縮することができ、高精細な画素部でも高階調な表示を実現することができる。

30

**【 0 1 2 8 】**

以上、本発明に係る表示装置及びその駆動方法について実施に形態 1 及び 2 に基づき説明したが、本発明に係る表示装置及びその駆動方法は、上述した実施の形態 1 及び 2 に限定されるものではない。実施の形態 1 及び 2 に対して、本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る表示装置を内蔵した各種機器も本発明に含まれる。

**【 産業上の利用可能性】****【 0 1 2 9 】**

本発明の表示装置及びその駆動方法は、特に、デジタル階調制御方式で輝度を変動させるアクティブ型ディスプレイに有用である。

40

**【 符号の説明】****【 0 1 3 0 】**

- 1 表示装置

- 2 サブフィールド処理回路

- 3 電源線制御回路

- 4 走査線制御回路

- 5 消去線制御回路

- 6 データ線制御回路

50

|                                                                                                                                                                                                                                                                                                        |                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|

| 1 0 、 2 0                                                                                                                                                                                                                                                                                              | 画素部                |    |

| 1 0 A 、 1 0 B 、 2 0 A 、 2 0 B                                                                                                                                                                                                                                                                          | 画素                 |    |

| 1 1 A 、 1 1 B                                                                                                                                                                                                                                                                                          | 薄膜トランジスタスイッチ       |    |

| 1 0 1 、 1 0 2 、 1 0 3 、 1 0 4 、 1 0 7 、 1 0 8 、 1 0 9 、 1 1 0 、 2 0 2 、 2 0 8                                                                                                                                                                                                                          |                    |    |

| 有機 E L 素子                                                                                                                                                                                                                                                                                              |                    |    |

| 1 0 5 、 1 0 6 、 1 1 1 、 1 1 2                                                                                                                                                                                                                                                                          | ダイオード              |    |

| 1 2 A 、 1 2 B 、 1 3 A 、 1 3 B 、 2 2 A 、 2 2 B 、 2 3 A 、 2 3 B                                                                                                                                                                                                                                          | コンデンサ              |    |

| 5 0 0 、 6 0 0                                                                                                                                                                                                                                                                                          | 電流駆動型表示パネル         |    |

| 5 0 1 、 6 0 1                                                                                                                                                                                                                                                                                          | 信号線                |    |

| 5 0 2 、 6 0 2 、 S C 1 、 S C 2 、 S C n                                                                                                                                                                                                                                                                  | 走査線                | 10 |

| 5 1 0 、 6 1 0                                                                                                                                                                                                                                                                                          | フレームメモリ            |    |

| 5 1 1 、 6 1 1                                                                                                                                                                                                                                                                                          | ラッチ                |    |

| 5 1 2                                                                                                                                                                                                                                                                                                  | D / A コンバータ        |    |

| 5 1 3 、 6 1 3                                                                                                                                                                                                                                                                                          | ゲートドライバ            |    |

| 5 1 4 、 6 1 4 、 6 1 8 、 S W 3 A B 、 S W 3 B B 、 S W 3 A G 、 S W 3 B G 、 S W 3<br>A R 、 S W 3 B R 、 S W 4 1 A 、 S W 4 1 B 、 S W 4 2 A 、 S W 4 2 B 、 S W 4 3 A 、 S<br>W 4 3 B 、 S W 4 n A 、 S W 4 n B 、 S W 5 1 A 、 S W 5 1 B 、 S W 5 2 A 、 S W 5 2 B<br>、 S W 5 3 A 、 S W 5 3 B 、 S W 5 n A 、 S W 5 n B | スイッチ               |    |

| 5 1 5 、 6 1 5                                                                                                                                                                                                                                                                                          | 保持容量               |    |

| 5 1 6 、 6 1 6                                                                                                                                                                                                                                                                                          | P チャネル薄膜トランジスタ     | 20 |

| 5 1 7 、 6 1 7                                                                                                                                                                                                                                                                                          | 発光素子               |    |

| 5 2 0 、 6 2 0                                                                                                                                                                                                                                                                                          | 画素                 |    |

| 6 1 2                                                                                                                                                                                                                                                                                                  | V O N V O F F 出力回路 |    |

| 6 1 9                                                                                                                                                                                                                                                                                                  | 時分割駆動制御回路          |    |

| D T 1 、 D T 2                                                                                                                                                                                                                                                                                          | データ線               |    |

| E 1 、 E 2 、 E n                                                                                                                                                                                                                                                                                        | 消去線                |    |

| S W 4 A H 、 S W 4 A L                                                                                                                                                                                                                                                                                  | パルス発生用スイッチ         |    |

| V 1 、 V 2 、 V n                                                                                                                                                                                                                                                                                        | 電源線                |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7 A】

【図7 B】

【図7 D】

【図7 C】

【図 8】

【図 9】

【図 10】

【図 11】

【 図 1 2 】

【 図 1 3 】

【 14 】

【 15 】

【図 1 6】

【図 1 7 A】

【図 1 7 B】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 1 1 A

G 0 9 G 3/20 6 4 1 E

G 0 9 G 3/20 6 2 3 D

H 0 5 B 33/14 A

F ターム(参考) 5C380 AA01 AA03 AB06 AB15 AB24 AC07 AC08 BA01 BA24 BA39

CA08 CA12 CA14 CA32 CA53 CB01 CB31 CC02 CC26 CC27

CC29 CC30 CC33 CC39 CC41 CC51 CC62 CC77 CC80 CD012

CD021 CF51 DA01 DA02 DA06 DA09 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2012163633A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2012-08-30 |

| 申请号            | JP2011022155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2011-02-03 |

| [标]申请(专利权)人(译) | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 新井 康弘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 新井 康弘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09G3/30.J G09G3/20.641.D G09G3/20.624.B G09G3/20.622.C G09G3/20.611.H G09G3/20.611.A<br>G09G3/20.641.E G09G3/20.623.D H05B33/14.A G09G3/3233 G09G3/3258 G09G3/3266 G09G3/3275<br>G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC14 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080<br>/AA06 5C080/BB05 5C080/DD22 5C080/DD26 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05<br>5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB15 5C380/AB24 5C380/AC07 5C380/AC08 5C380<br>/BA01 5C380/BA24 5C380/BA39 5C380/CA08 5C380/CA12 5C380/CA14 5C380/CA32 5C380/CA53<br>5C380/CB01 5C380/CB31 5C380/CC02 5C380/CC26 5C380/CC27 5C380/CC29 5C380/CC30 5C380<br>/CC33 5C380/CC39 5C380/CC41 5C380/CC51 5C380/CC62 5C380/CC77 5C380/CC80 5C380/CD012<br>5C380/CD021 5C380/CF51 5C380/DA01 5C380/DA02 5C380/DA06 5C380/DA09 5C380/DA47 |         |            |

| 代理人(译)         | 新居 広守                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

解决的问题：提供一种显示装置及其驱动方法，该显示装置在不使用恒定电流源的情况下抑制发光电流的变化并且使用低损耗。显示装置

(1) 包括：像素部(10)，其中布置有多个像素，其中，像素(10A)基于输入视频信号来切换导通状态和非导通状态；以及薄膜晶体管开关(11A)。当11A处于导通状态时，通过交替施加正电压脉冲和负电压脉冲而产生的双向电流被整流，并且整流后的电流被单向传递至薄膜晶体管开关11A，并且整流后的电流被整流。并且有机EL元件101至104在电流流动时发光。[选择图]图2