(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-8907

(P2010-8907A)

(43) 公開日 平成22年1月14日(2010.1.14)

| (51) Int. Cl.               | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30  | J 3K107     |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 | A 5C080     |

| <b>H05B 33/12</b> (2006.01) | H05B 33/12 | C 5C094     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 624B        |

| <b>G09F 9/30</b> (2006.01)  | G09G 3/20  | 623D        |

審査請求 未請求 請求項の数 6 O L (全 24 頁) 最終頁に続く

|           |                              |          |                                            |

|-----------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号 | 特願2008-170687 (P2008-170687) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成20年6月30日 (2008.6.30)       | (74) 代理人 | 100090538<br>弁理士 西山 恵三                     |

|           |                              | (74) 代理人 | 100096965<br>弁理士 内尾 裕一                     |

|           |                              | (72) 発明者 | 川野 藤雄<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

|           |                              | (72) 発明者 | 井関 正己<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】アクティブマトリックス型表示装置及びその駆動方法

## (57) 【要約】

【課題】積層構造のEL素子をトランジスタを用いて駆動するアクティブマトリックス型表示装置の駆動に適した回路構成を提供する。

【解決手段】複数の走査線と、複数のデータ線と、複数の画素を備え、

画素は、共通端子に接続された、流れる電流の方向が異なる2つの発光素子と、複数の駆動回路とを含み、複数の駆動回路は、

第1容量と、第1容量の電圧に応じて共通端子から発光素子に向かう方向の電流を発生するP型駆動トランジスタとを備えた第1駆動回路と、

第2容量と、第2容量の電圧に応じて発光素子から共通端子に向かう方向の電流を発生するN型駆動トランジスタとを備えた第2駆動回路とを含み、

走査線の走査信号によって制御されて、データ線の映像信号が第1と第2容量にそれぞれ保持され、第1容量の保持信号に基いて第1駆動回路が一方の発光素子に電流を供給し、第2容量の保持信号に基いて第2駆動回路が他方の発光素子に電流を供給する。

## 【特許請求の範囲】

## 【請求項 1】

複数の走査線と、前記走査線に交差する複数のデータ線と、前記走査線と前記データ線の交差する位置に配置された複数の画素を備え、

前記画素は、共通端子に接続された、流れる電流の方向が異なる2つの発光素子と、前記共通端子に接続された複数の駆動回路とを含んで構成されたアクティブマトリックス型表示装置であって、

前記複数の駆動回路は、

第1の容量と、前記第1の容量の電圧に応じて前記共通端子から前記発光素子に向かう方向の電流を発生するP型の駆動トランジスタとを備えた第1の駆動回路と、

第2の容量と、前記第2の容量の電圧に応じて前記発光素子から前記共通端子に向かう方向の電流を発生するN型の駆動トランジスタとを備えた第2の駆動回路とを含み、

前記走査線の走査信号によって制御されて、前記データ線の映像信号が前記第1と第2の容量にそれぞれ保持され、前記第1の容量に保持された映像信号に基いて前記第1の駆動回路が前記2つの発光素子の一方に電流を供給し、前記第2の容量に保持された映像信号に基いて前記第2の駆動回路が前記2つの発光素子の他方に電流を供給することを特徴とするアクティブマトリックス型表示装置。

## 【請求項 2】

同一画素行の隣接する二つの画素で、一の画素の第1の発光素子と他の画素の第2の発光素子とが同色の光を発光し、前記第1の発光素子を駆動する駆動回路と前記第2の発光素子を駆動する駆動回路とが共有された駆動回路で構成されていることを特徴とする請求項1に記載のアクティブマトリックス型表示装置。

## 【請求項 3】

前記複数の発光素子は積層されて構成されていることを特徴とする請求項1又は2に記載のアクティブマトリックス型表示装置。

## 【請求項 4】

前記複数の駆動回路の各々が、前記P型または前記N型トランジスタと前記共通端子の間にスイッチを備えており、前記スイッチの開閉により、前記P型の駆動トランジスタにより駆動される発光素子と、前記N型の駆動トランジスタにより駆動される発光素子とが、異なる期間に発光することを特徴とする請求項1から3のいずれか1項に記載のアクティブマトリックス型表示装置。

## 【請求項 5】

並列接続された前記複数の発光素子の他方の共通端子は電源線に接続され、前記P型の駆動トランジスタにより駆動される発光素子の発光期間と、前記N型の駆動トランジスタにより駆動される発光素子の発光期間とにおいて、前記電源線の電位が異なることを特徴とする請求項1から4のいずれ1項に記載のアクティブマトリックス型表示装置。

## 【請求項 6】

マトリックス状に配置された複数の画素を備え、

各画素は、共通端子に並列に接続された、流れる電流の方向が異なる2つの発光素子と、前記共通端子に接続され、前記複数の発光素子をそれぞれ駆動する複数の駆動回路とを有し、

前記複数の駆動回路は前記複数の画素の画素行ごとに走査され、

前記複数の駆動回路は前記発光素子を駆動する複数の駆動トランジスタを有し、前記複数の駆動トランジスタは、一方向に電流が流れる発光素子を駆動するP型の駆動トランジスタと、逆方向に電流が流れる発光素子を駆動するN型の駆動トランジスタとを含み、

前記複数の駆動回路は、前記複数の駆動トランジスタの制御電極にそれぞれに接続される複数の容量を有してなるアクティブマトリックス型表示装置の駆動方法において、

前記P型の駆動トランジスタにより駆動される第1の発光素子が発光する第1発光期間と、

前記N型の駆動トランジスタにより駆動される第2の発光素子が発光する第2発光期間

10

20

30

40

50

と、

前記第1及び前記第2発光期間の前に、前記P型の駆動トランジスタの制御電極に接続される前記容量と、前記N型の駆動トランジスタの制御電極に接続される前記容量とに、前記第1及び第2発光期間内に発光素子に流れる電流を規定する制御電位を保持するプログラム期間と、

を有することを特徴とするアクティブマトリックス型表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電流を注入して発光するエレクトロルミネッセンス素子(以後EL素子と言10う)を画像表示に使用したアクティブマトリックス型表示装置に関するものである。

【背景技術】

【0002】

EL素子を駆動するアクティブマトリックス型の表示装置について、個別に駆動できる少なくとも2つのEL素子を基板上に積層させ発光させる構成の表示装置がある。

【0003】

特許文献1には、1画素を並列に配置した複数のサブピクセルで構成し、複数のサブピクセルは各々が異なる色の有機層を複数積層させて構成している。具体的には、1画素PXを第1サブピクセルP1と第2サブピクセルP2とで構成する。特許文献1の図1に示すように、第1サブピクセルP1は、第1の色に発光する第1発光層を含む第1有機層(R有機層)11と、第2の色に発光する第2発光層を含む第2有機層(B有機層)13とが積層されて構成する。第2サブピクセルP2は、第3の色に発光する第3発光層を含む第3有機層(G有機層)12と、第2有機層(B有機層)13とが積層されて構成されている。そして各共通電極に対し、交流信号を印加することにより、複数のEL素子を発光-消灯を交互に繰り返すことで所望の色の光を得ている。こうすることで、寿命の短い第2有機層(B有機層)の面積を2倍として、第2有機層の輝度を半分にして寿命を延ばすことを可能としている。

【特許文献1】特開2005-174639号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来提案されている積層されたEL素子の駆動方法は、各層の電極間に輝度信号に応じた電圧を与えて駆動する電圧駆動方式である。電圧駆動方式の駆動回路は、従来の駆動回路を直列につないで積層する電極にそのまま接続すればよい。

【0005】

しかし、EL素子電極間の電圧を制御して駆動する方式では、EL素子の電圧電流特性のばらつきや経時的な劣化による電流変化があると、同じ輝度信号でもEL素子には異なる電流が流れ、輝度が精確にコントロールできない。

【0006】

これに対し、EL素子に流れる電流をコントロールする電流駆動方式は、輝度信号に応じてEL素子に流す電流が決まるので、EL素子の電圧電流特性のばらつきや経時的な劣化による電流変化があっても、電流と輝度の関係が一定している限り、輝度には影響がない。積層されていない通常のEL素子の電流駆動回路は、EL素子に流す電流方向が決まっているので、一方向の電流発生回路があればよい。

【0007】

しかし、積層されたEL素子では、上下の2つのEL素子の間に位置する電極には、上下のEL素子の輝度に応じて異なる向きに電流を供給しなければならず、従来の一方向の電流発生回路をそのまま用いることは困難であった。本発明の目的は、積層構造のEL素子をトランジスタを用いて駆動するアクティブマトリックス型表示装置の電流駆動に適した駆動回路と駆動方法を提供することにある。

10

20

30

40

50

## 【課題を解決するための手段】

## 【0008】

本発明のアクティブマトリックス型表示装置は、複数の走査線と、前記走査線に交差する複数のデータ線と、前記走査線と前記データ線の交差する位置に配置された複数の画素を備え、

前記画素は、共通端子に接続された、流れる電流の方向が異なる2つの発光素子と、前記共通端子に接続された複数の駆動回路とを含んで構成されたアクティブマトリックス型表示装置であって、

前記複数の駆動回路は、

第1の容量と、前記第1の容量の電圧に応じて前記共通端子から前記発光素子に向かう方向の電流を発生するP型の駆動トランジスタとを備えた第1の駆動回路と、

第2の容量と、前記第2の容量の電圧に応じて前記発光素子から前記共通端子に向かう方向の電流を発生するN型の駆動トランジスタとを備えた第2の駆動回路とを含み、

前記走査線の走査信号によって制御されて、前記データ線の映像信号が前記第1と第2の容量にそれぞれ保持され、前記第1の容量に保持された映像信号に基いて前記第1の駆動回路が前記2つの発光素子の一方に電流を供給し、前記第2の容量に保持された映像信号に基いて前記第2の駆動回路が前記2つの発光素子の他方に電流を供給することを特徴とする。

## 【0009】

また本発明のアクティブマトリックス型表示装置の駆動方法は、マトリックス状に配置された複数の画素を備え、

各画素は、共通端子に並列に接続された、流れる電流の方向が異なる2つの発光素子と、前記共通端子に接続され、前記複数の発光素子をそれぞれ駆動する複数の駆動回路とを有し、

前記複数の駆動回路は前記複数の画素の画素行ごとに走査され、

前記複数の駆動回路は前記発光素子を駆動する複数の駆動トランジスタを有し、前記複数の駆動トランジスタは、一方向に電流が流れる発光素子を駆動するP型の駆動トランジスタと、逆方向に電流が流れる発光素子を駆動するN型の駆動トランジスタとを含み、

前記複数の駆動回路は、前記複数の駆動トランジスタの制御電極にそれぞれに接続される複数の容量を有してなるアクティブマトリックス型表示装置の駆動方法において、

前記P型の駆動トランジスタにより駆動される第1の発光素子が発光する第1発光期間と、

前記N型の駆動トランジスタにより駆動される第2の発光素子が発光する第2発光期間と、

前記第1及び前記第2発光期間の前に、前記P型の駆動トランジスタの制御電極に接続される前記容量と、前記N型の駆動トランジスタの制御電極に接続される前記容量とに、前記第1及び第2発光期間内に発光素子に流れる電流を規定する制御電位を保持するプログラム期間と、

を有することを特徴とする。

## 【発明の効果】

## 【0010】

本発明によれば、積層構造のEL素子を駆動するアクティブマトリックス方式に関し、プログラミング動作、発光動作に至るまで品質の高い駆動を行うことが出来る。

## 【0011】

また、複数のEL素子を時分割で発光させる駆動方式では、発光期間前のプログラミング期間を時分割するとメモリを多く使用することになるが、本発明ではプログラミングを同一期間内で行うことでメモリの数を削減できる。

## 【発明を実施するための最良の形態】

## 【0012】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

10

20

30

30

40

50

## 【0013】

(第1の実施形態)

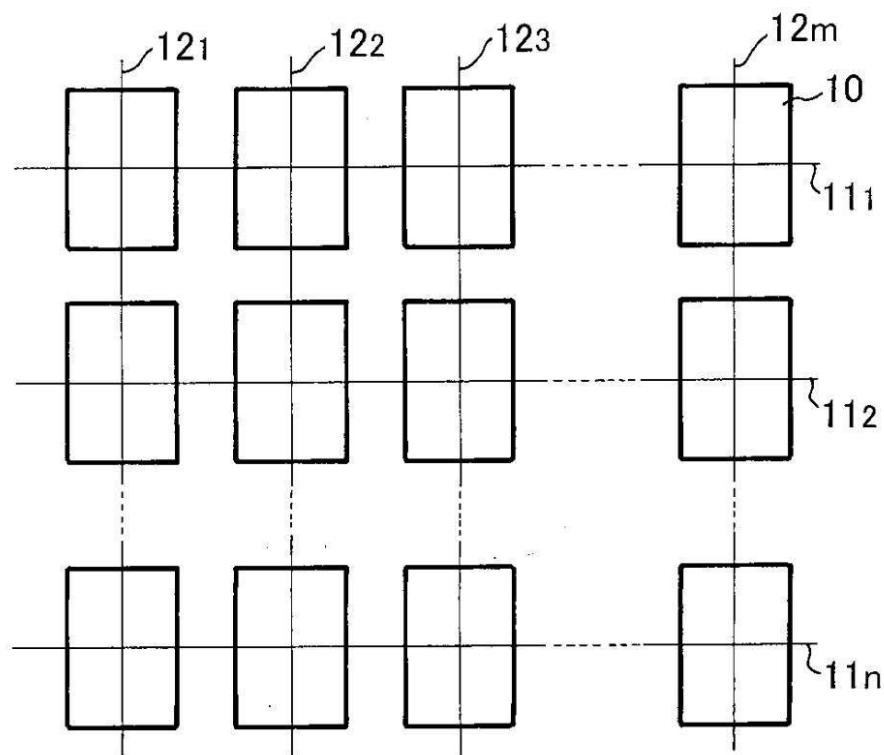

本実施形態のEL素子を用いたアクティブマトリックス型の表示装置の構成例を図12に示す。

## 【0014】

m列n行(m、nは自然数を示す)のマトリックス状に配置された画素10には、EL素子とそれを駆動する画素回路が配置されている。行方向に共通な走査線11<sub>1</sub>~11<sub>n</sub>及び、列方向に共通なデータ線12<sub>1</sub>~12<sub>m</sub>が各画素に接続されている。各画素は走査線とデータ線の交差する位置に配置される。走査線11<sub>1</sub>~11<sub>n</sub>の走査により、データ線12<sub>1</sub>~12<sub>m</sub>の表示情報=映像信号が行ごとに画素回路に順次取り込まれ、画素回路は取り込んだ表示情報に応じた電流によりELを駆動し発光させる。

10

## 【0015】

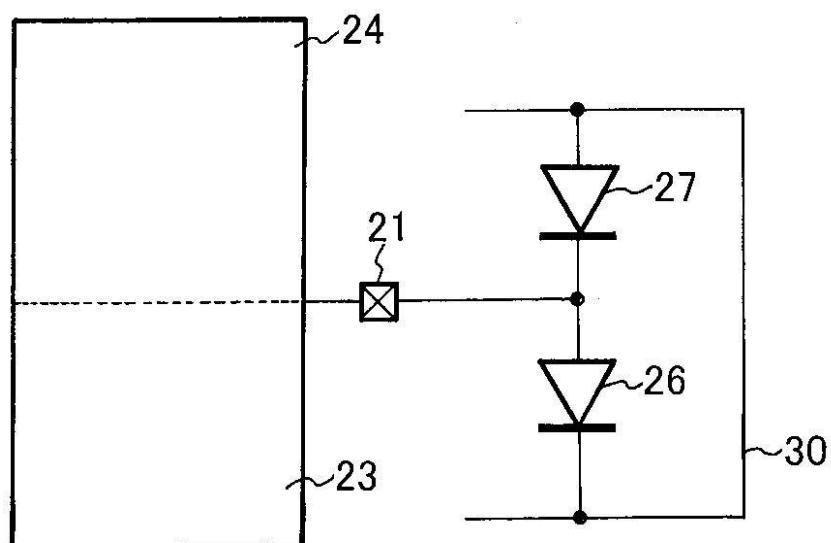

図13は本実施形態における積層したEL素子の模式的断面図を示したものである。

## 【0016】

EL素子26とEL素子27の2層を積層し、これを、上、中央、下の3電極で挟んだ構造にしている。上電極(EL素子27のアノード電極)及び下電極(EL素子26のカソード電極)をともに電源線30Vcに接続し、中央電極(EL素子27のカソード電極及びEL素子26のアノード電極)を共通端子となるタップ21に接続し、2つの駆動回路23, 24に接続している。EL素子26に流れる電流とEL素子27に流れる電流はともに積層方向に対して下向きであって、電源線30と共に端子となるタップ21の間の電流としては逆方向になる。本実施形態では、積層されたEL素子26とEL素子27、駆動回路23, 24とが一つの画素を構成する。以下、1つの画素の2つの駆動回路23、24をまとめて画素回路という。なお、駆動回路23は第1の駆動回路、駆動回路24は第2の駆動回路に対応する。容量C1Rは第1の容量、容量C1Bは第2の容量に対応する。

20

## 【0017】

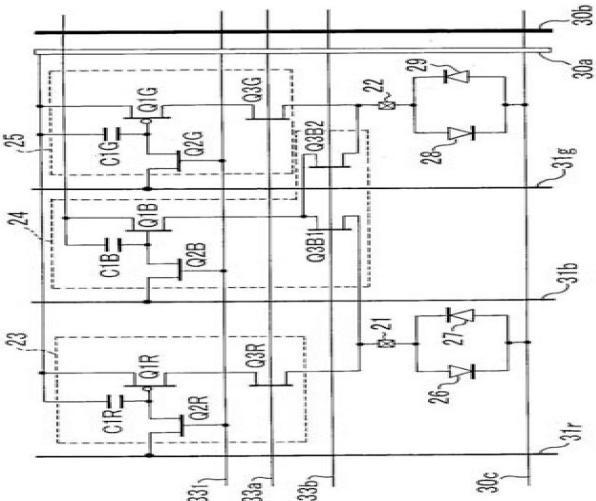

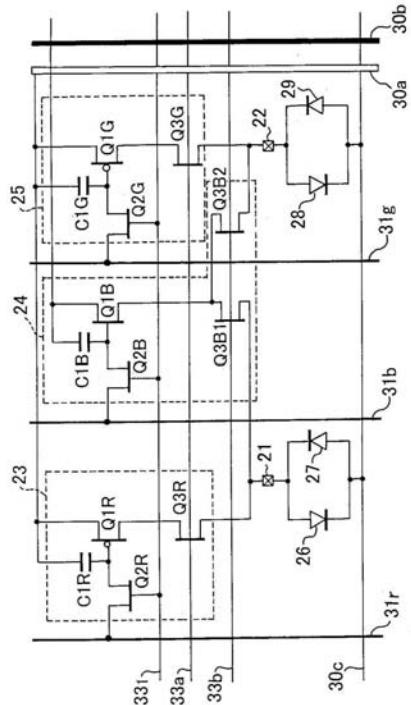

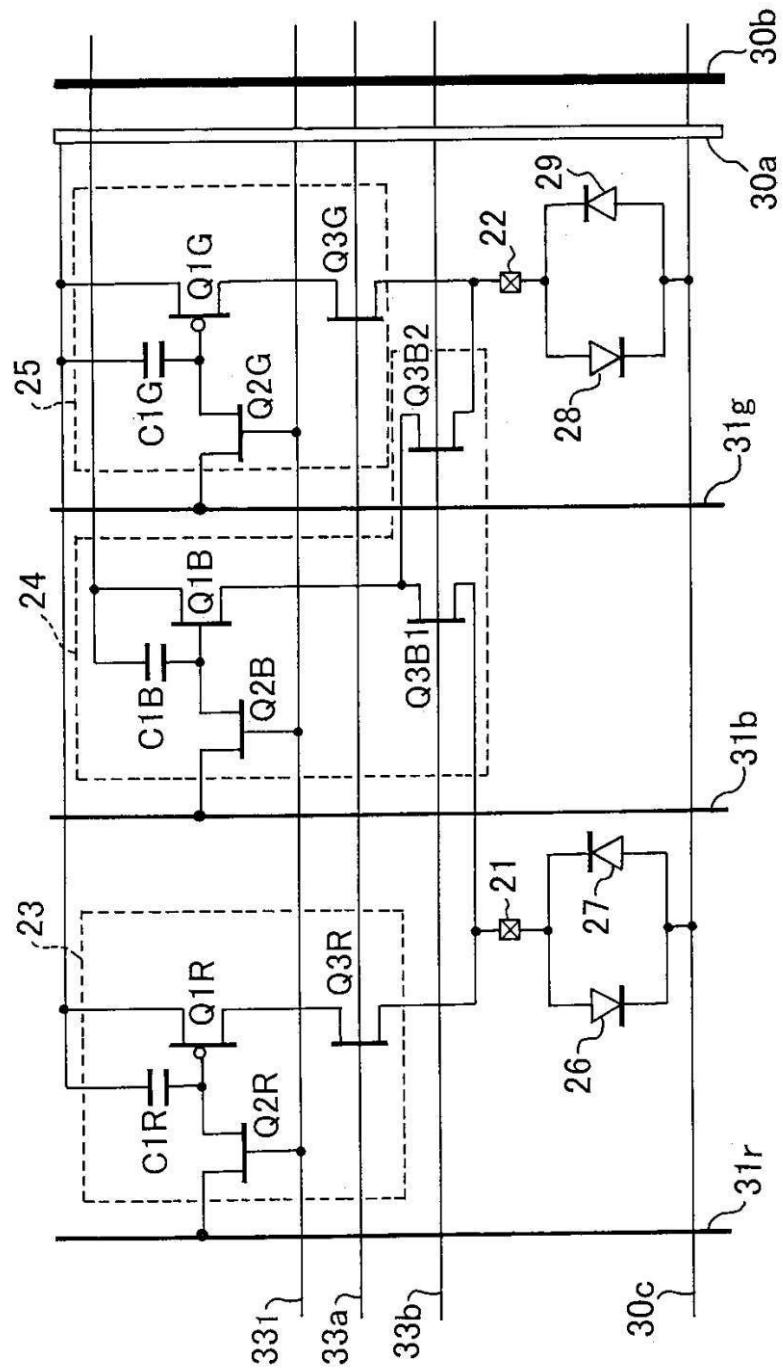

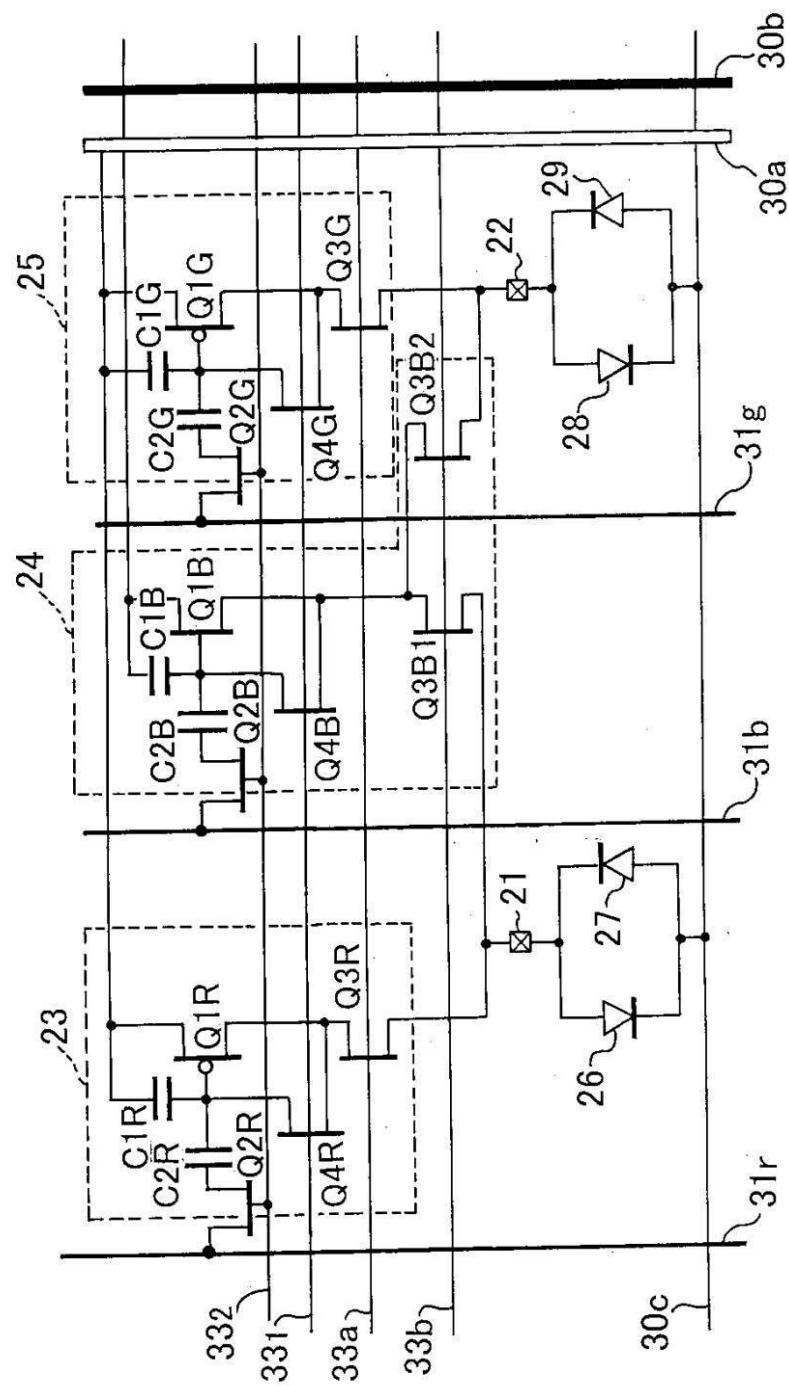

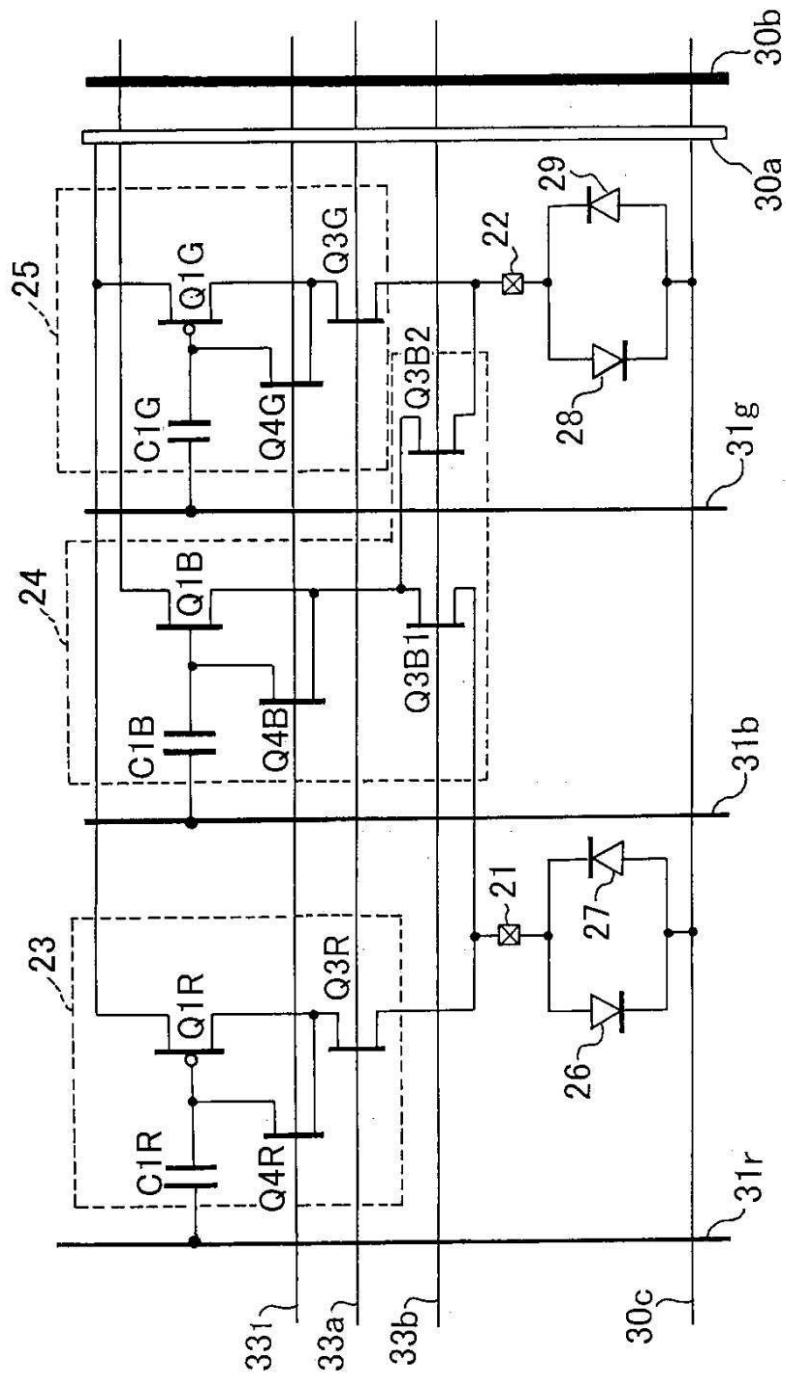

図1は本発明によるアクティブマトリックス型表示装置の第1の実施形態の画素の回路構成図である。

## 【0018】

図1におけるEL素子26, 27および28, 29は、図13の断面図で示した積層EL素子を2つ並べたものである。以下、EL素子26は赤色の光を発光し、EL素子28は緑色の光を発光し、EL素子27, 29は同色の青色の光を発光するものとして説明する。しかし、各層の発光色はこれに限らず、4つの発光素子でRGBの3原色を出すように構成されていれば、どのような配置であってもよい。

30

## 【0019】

EL素子26, 27は共通端子となるタップ21を通して画素回路23, 24のスイッチQ3R、Q3B1と接続されている。同様に、EL素子28, 29はもう1つの共通端子となるタップ22を通して画素回路24, 25のスイッチQ3B2、Q3Gと接続されている。

40

## 【0020】

EL素子26, 27と、画素回路23, 24とは一つの画素を構成する。また、EL素子28, 29と、画素回路24, 25とは、隣接する他の画素を構成する。

## 【0021】

本実施形態では、隣接する画素が駆動回路24を共有している。駆動回路24は共有化され、発光素子27, 29に電流を流すように駆動トランジスタQ1Bが駆動する。各発光素子27, 29には駆動トランジスタQ1Bを流れる電流のほぼ半分の電流がそれぞれ流れる。なお、駆動回路を共有せず、発光素子27, 29ごとに別の駆動回路を設けてよい。またEL素子26, 27、EL素子28, 29は、それぞれ共通端子21と22に並列に接続され、発光のための電流方向が逆の2つのEL素子であればよく、必ずしも積層構造でなくともよい。

50

## 【0022】

駆動回路23は、スイッチQ3R、一方の主電極がスイッチQ3Rと接続される駆動トランジスタQ1R、駆動トランジスタQ1Rの制御電極と接続される、容量C1RとスイッチQ2Rを備えている。容量C1Rの第1の端子は駆動トランジスタQ1Rの制御電極と接続され、第2の端子は電源線30a(第1の電位線となる)と接続される。

## 【0023】

駆動回路24は、2つのスイッチQ3B1、Q3B2、一方の主電極がスイッチQ3B1、Q3B2と接続される駆動トランジスタQ1B、駆動トランジスタQ1Bの制御電極と接続される、容量C1BとスイッチQ2Bを備えている。容量C1Bの第1の端子は駆動トランジスタQ1Bの制御電極と接続され、第2の端子は電源線30b(第2の電位線となる)と接続される。

10

## 【0024】

駆動回路25は、スイッチQ3G、一方の主電極がスイッチQ3Gと接続される駆動トランジスタQ1G、駆動トランジスタQ1Gの制御電極と接続される、容量C1GとスイッチQ2Gを備えている。容量C1Gの第1の端子は駆動トランジスタQ1Gの制御電極と接続され、第2端子は電源線30aと接続される。

## 【0025】

駆動回路23、24、25において、駆動トランジスタQ1BはN型のMOSトランジスタ、駆動トランジスタQ1R、Q1GはP型のMOSトランジスタである。スイッチQ3R、Q2R、Q3B1及びスイッチQ3B2、Q2B、Q3G、Q2GはN型のMOSトランジスタで構成される。各駆動トランジスタ及び各スイッチは例えば薄膜トランジスタ(TFT)で構成する。各駆動トランジスタ及び各スイッチがMOSトランジスタで構成された場合、MOSトランジスタの制御電極はゲートとなり、2つの主電極はソース、ドレインとなる。

20

## 【0026】

制御線33<sub>1</sub>はスイッチQ2R、Q2B、Q2Gのゲートと接続され、制御線33<sub>a</sub>はスイッチQ3R、Q3Gのゲートと接続され、制御線33<sub>b</sub>はスイッチQ3B1、Q3B2のゲートと接続される。図12の走査線11<sub>1</sub>～11<sub>n</sub>の各走査線は、制御線33<sub>1</sub>、33<sub>a</sub>、33<sub>b</sub>から構成される。

30

## 【0027】

データ線31<sub>r</sub>はスイッチQ2Rの一方の主電極と接続され、データ線31<sub>b</sub>はスイッチQ2Bの一方の主電極と接続され、データ線31<sub>g</sub>はスイッチQ2Gの一方の主電極と接続される。図12のデータ線12<sub>1</sub>～12<sub>m</sub>の各データ線は、データ線31<sub>r</sub>、31<sub>b</sub>、31<sub>g</sub>から構成される。30<sub>a</sub>、30<sub>b</sub>、30<sub>c</sub>はそれぞれ電源線を示す。電源線30<sub>c</sub>には、EL素子26、27、EL素子28、29の他方の共通端子が接続される。

30

## 【0028】

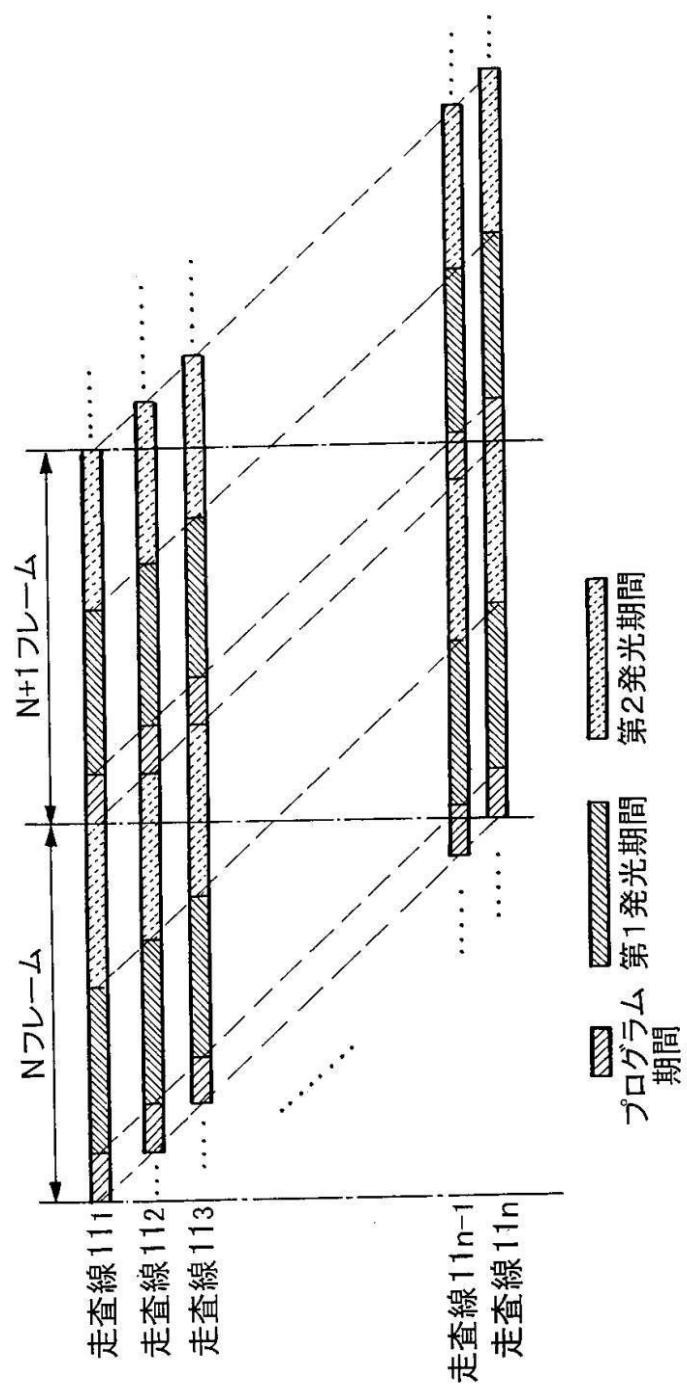

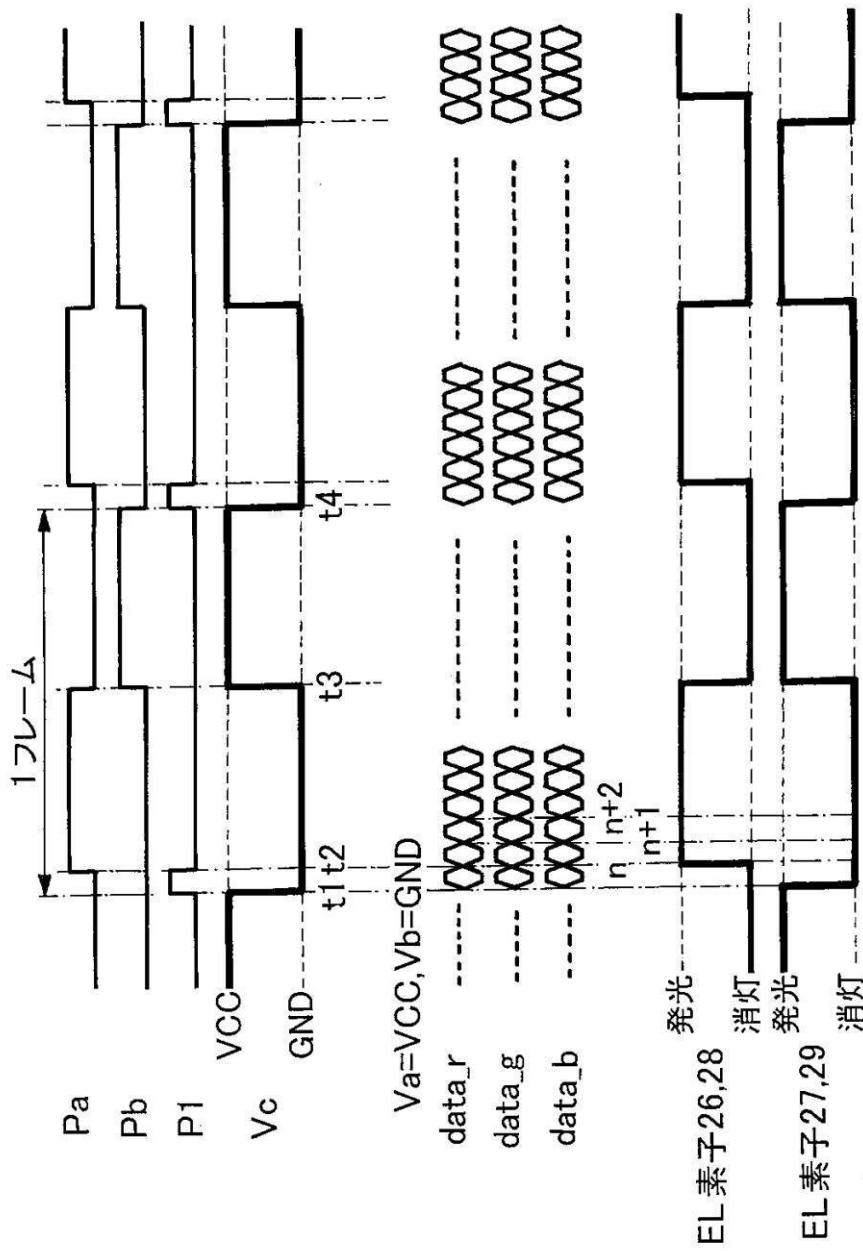

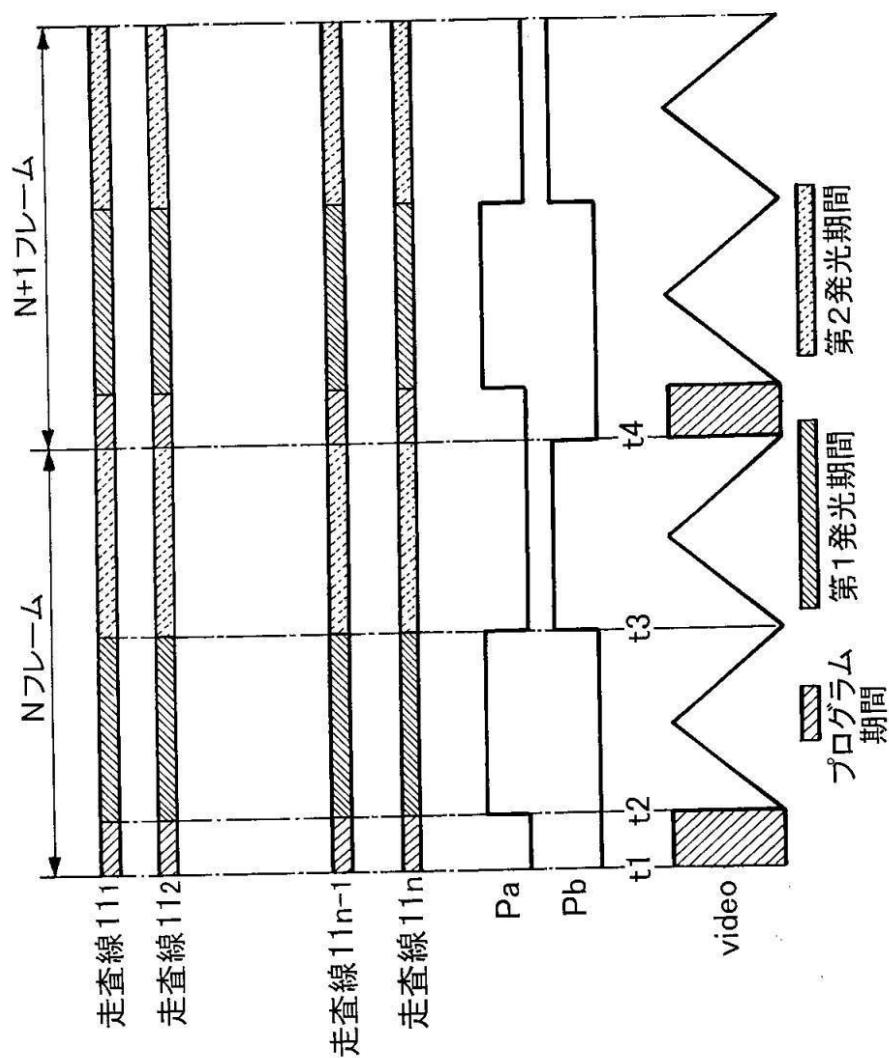

図2は図1の回路を駆動するシーケンスを示す図である。

## 【0029】

1フレームの駆動シーケンスは走査線11<sub>1</sub>～11<sub>n</sub>の各々に接続される画素の画素回路にプログラムされるプログラム期間と、各行プログラム期間終了後の第1発光期間、第2発光期間からなる。プログラム期間、各行プログラム期間終了後の第1発光期間、第2発光期間は同一画素行の同じフレーム(同じ走査期間)内で行われる。同一画素行の発光素子が異なる発光期間(第1発光期間と第2発光期間)に分かれて発光することになる。プログラム期間、第1発光期間、第2発光期間の順に動作が行われ、このシーケンスをフレーム単位で繰り返す。図3では第1発光期間、第2発光期間の発光単位が1回ずつとなっているが、次のプログラム期間まで第1発光期間と第2発光期間の発光期間の長さを短くして交互に繰り返しても良い。

40

## 【0030】

なお、複数のEL素子を時分割で発光させる駆動方式では、発光期間前のプログラミング期間を時分割するとメモリを多く使用することになるが、本実施形態ではプログラミン

50

グを同一期間内で行うことでメモリの数を削減できる。

【0031】

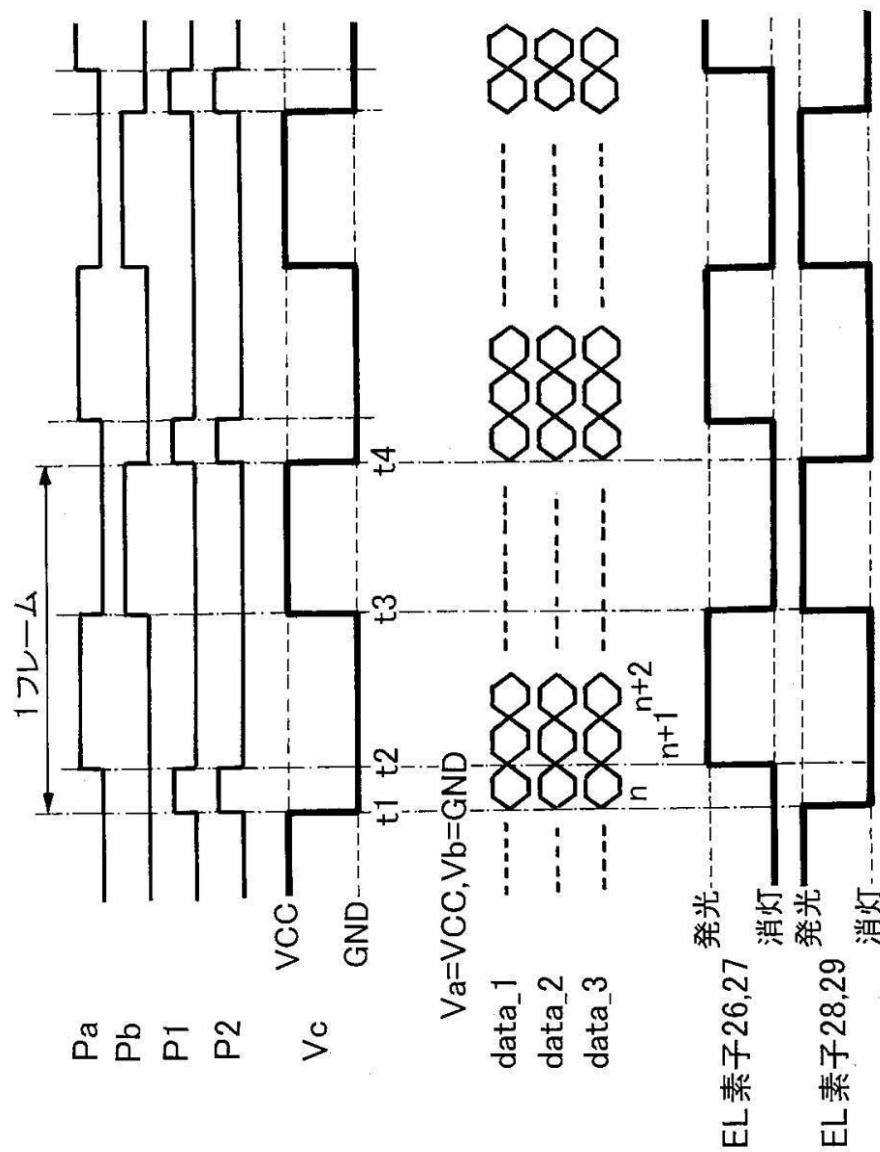

図3は画素回路の動作を示すタイミングチャートである。図3における $P_a$ 、 $P_b$ 、 $P_1$ は図1の制御線 $33_a$ 、 $33_b$ 、 $33_1$ に加えられる走査信号、 $V_c$ は図1の電源線 $30_c$ に加えられる電圧信号を示す。また、 $V_a$ は電源線 $30_a$ に加えられる電圧で、ここでは電圧 $V_{cc}$ である。 $V_b$ は電源線 $30_b$ に加えられる電圧で、ここではグランドGNDである。

【0032】

時刻 $t_1$ から時刻 $t_2$ の期間 $T_1$ （図2におけるプログラム期間）において、制御線 $33_1$ に加えられる走査信号 $P_1$ がハイレベルとなって、各駆動回路 $23$ 、 $24$ 、 $25$ のスイッチ $Q2R$ 、 $Q2B$ 、 $Q2G$ がONになる。この結果、データ線 $31_r$ 、 $31_b$ 、 $31_g$ にそれぞれ供給される映像信号（画像信号） $data_r$ 、 $data_b$ 、 $data_g$ が容量 $C1R$ 、 $C1B$ 、 $C1G$ にチャージされる。こうして、第1及び第2発光期間内にEL素子に流れる電位を規定する制御電位（ゲート電位）が容量 $C1R$ 、 $C1B$ 、 $C1G$ に保持される。このプログラミング動作は画素行ごとに行われ、1つの画素行のプログラミングが終了すると、次の画素行のプログラミングが行われる。データ線 $31_r$ 、 $31_b$ 、 $31_g$ には、1つの画素行にプログラミングするために期間 $T_1$ （図3の時刻 $t_1$ から時刻 $t_2$ の期間）にその画素行の映像信号（画像信号）が印加される。その後、次の画素行にプログラミングするために、当該次の画素行の映像信号が期間 $T_1$ と同一期間印加される。

【0033】

時刻 $t_2$ から時刻 $t_3$ の期間 $T_2$ （図2における第1発光期間）では、制御線 $33_a$ に加えられる走査信号 $P_a$ によりスイッチ $Q3R$ 、 $Q3G$ がONし、駆動トランジスタ $Q1R$ 、 $Q1G$ から信号電流が、EL素子 $26$ 、 $28$ に流れる。また、時刻 $t_1$ から時刻 $t_3$ の期間（ $T_1 + T_2$ ）は電圧 $V_a$ が電圧 $V_{cc}$ 、電圧 $V_c$ がグランドの電位にあるため各EL素子 $26$ 、 $28$ は発光状態になる。

【0034】

時刻 $t_3$ から時刻 $t_4$ の期間 $T_3$ （図2における第2発光期間）では、制御線 $33_b$ に加えられる走査信号 $P_b$ によりスイッチ $Q3B1$ 、 $Q3B2$ がONし、駆動トランジスタ $Q1B$ から信号電流が、EL素子 $27$ 、 $29$ に流れる。また、期間 $T_3$ は $V_a$ がグランドの電位、 $V_c$ が電圧 $V_{cc}$ にあるため各EL素子 $27$ 、 $29$ （同じ色の光を発光する第1の発光素子及び第2の発光素子となる）は発光状態になる。

【0035】

このように、それぞれの駆動回路が、データ線から映像信号を取り込んで容量に保持し、保持された信号に基く電流を発生するので、各駆動回路の発生した電流は2つの発光素子にそれぞれの駆動電流として供給され、各発光素子の輝度が制御される。

【0036】

駆動回路の各々が、P型またはN型トランジスタと共に通端子の間に備えられたスイッチの開閉により、発光素子に流れる電流が制御され、2つの並列接続された発光素子が異なる期間に発光するようになっている。

【0037】

（第2の実施形態）

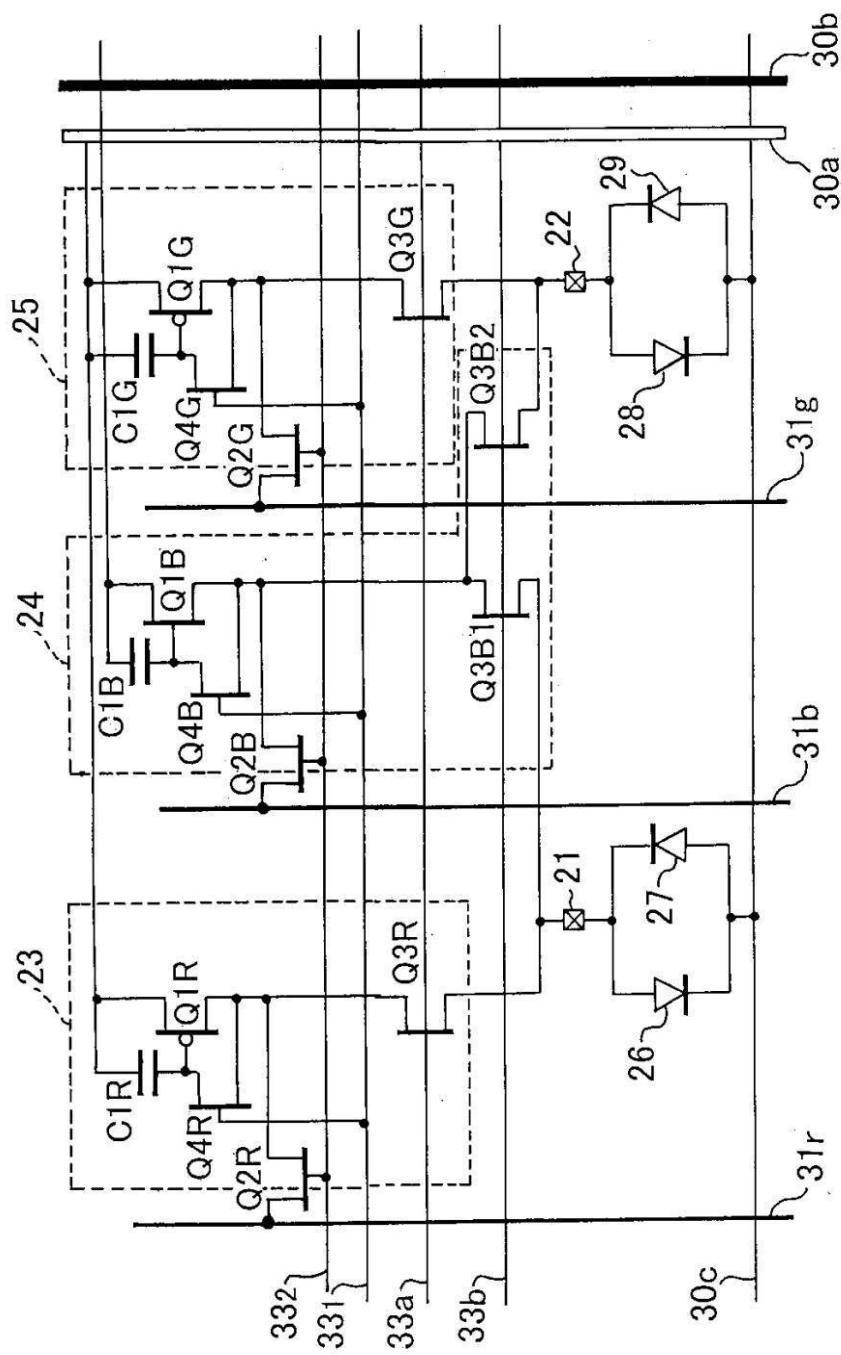

図4は本発明によるアクティブマトリックス型表示装置の第2の実施形態の画素の回路構成図である。

【0038】

図4に示す回路構成において、積層構造のEL素子との接続関係については図1に示した回路構成と同じであり、全体の駆動シーケンスも図2のタイミングと同一である。したがって、本実施形態の説明は図1との差異に関して述べるにとどめる。

【0039】

駆動回路 $23$ 、 $24$ 、 $25$ の駆動トランジスタ $Q1R$ 、 $Q1B$ 、 $Q1G$ のゲート-ドレン間にそれぞれ、スイッチ $Q4R$ 、 $Q4B$ 、 $Q4G$ を設けている。そして、スイッチ $Q$

10

20

30

40

50

4 R、Q 4 B、Q 4 Gのゲートは制御線 3 3<sub>1</sub> と接続され、スイッチ Q 2 R、Q 2 B、Q 2 Gのゲートは制御線 3 3<sub>2</sub> と接続される。

【0040】

さらにスイッチ Q 2 R、Q 2 B、Q 2 G と駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲート間にそれぞれ、容量 C 2 R、C 2 B、C 2 G を設けている。

【0041】

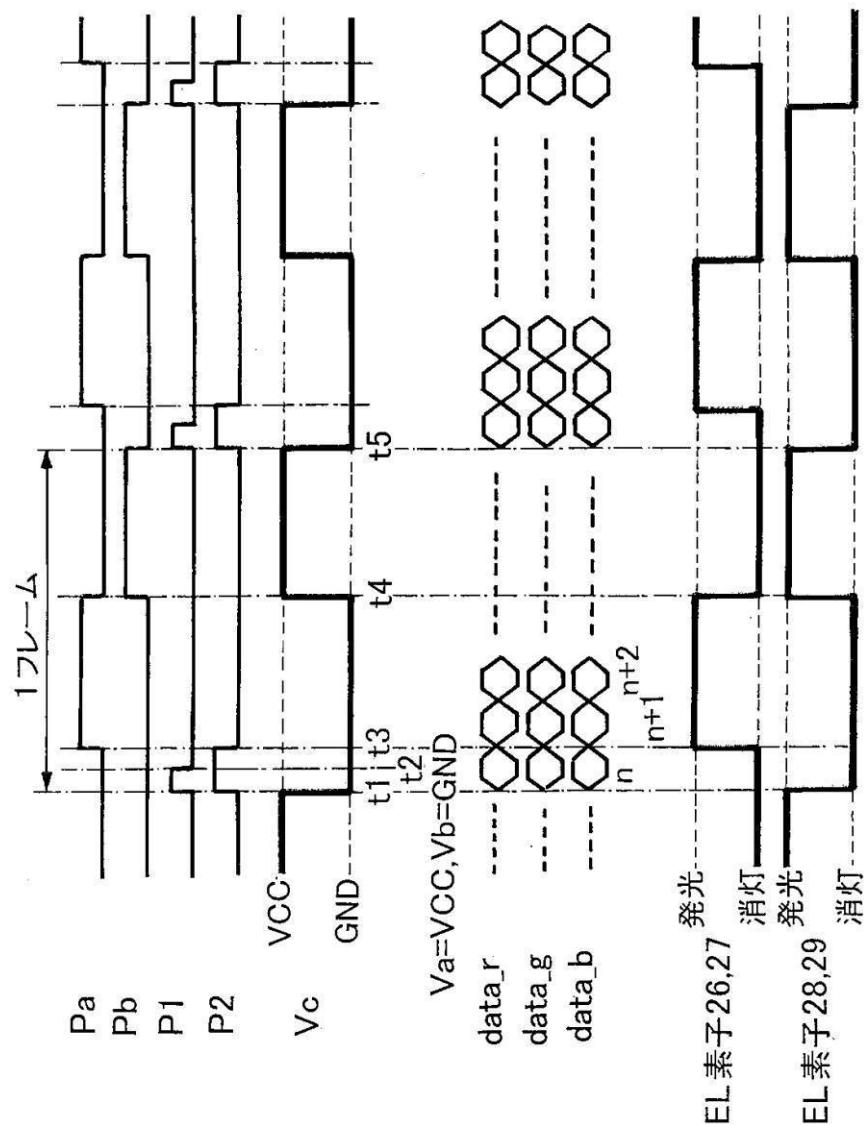

画素回路の動作をタイミングチャートを図 5 により説明する。図 5 における P<sub>a</sub>、P<sub>b</sub>、P<sub>1</sub>、P<sub>2</sub> は図 4 の制御線 3 3<sub>a</sub>、3 3<sub>b</sub>、3 3<sub>1</sub>、3 3<sub>2</sub> に加えられる走査信号、V<sub>c</sub> は図 4 の電源線 3 0<sub>c</sub> に加えられる電圧信号を示す。また、電圧 V<sub>a</sub> は電源線 3 0<sub>a</sub> に加えられる電圧で、ここでは電圧 V<sub>c c</sub>、V<sub>b</sub> は電源線 3 0<sub>b</sub> に加えられる電圧で、ここ 10 ではグランド GND である。

【0042】

時刻 t<sub>1</sub> から時刻 t<sub>2</sub> の期間 T<sub>1</sub> において、制御線 3 3<sub>1</sub> に加えられる走査信号 P<sub>1</sub> がハイレベルとなって、スイッチ Q 4 R、Q 4 B、Q 4 G が ON し、駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲート - ドレイン間にショートされる。この状態において、駆動トランジスタ Q 1 R、Q 1 B、Q 1 G はダイオード接続となり、各々駆動トランジスタのゲート - ソース間電位は閾値電圧 V<sub>t h</sub> に収束する。またこの間、制御線 3 3<sub>2</sub> に加えられる走査信号 P<sub>2</sub> がハイレベルにあり、スイッチ Q 2 R、Q 2 B、Q 2 G も ON し、データ線 3 1<sub>r</sub>、3 1<sub>b</sub>、3 1<sub>g</sub> にそれぞれ加えられる映像信号 data<sub>r</sub>、data<sub>b</sub>、data<sub>g</sub> の電圧はそれぞれ C 2 R、C 2 B、C 2 G の一端に伝達される。データ線 3 1<sub>r</sub>、3 1<sub>b</sub>、3 1<sub>g</sub> の電位 (図 6 の data) は図 6 に示す時刻 t<sub>1</sub> から時刻 t<sub>2</sub> の間、基準電位 v<sub>b 1</sub> 20 になっており、容量 C 2 R、C 2 B、C 2 G の電位差は各駆動トランジスタの閾値電圧との差分で保持される。

【0043】

時刻 t<sub>2</sub> から時刻 t<sub>3</sub> の期間 T<sub>2</sub> では、データ線 3 1<sub>r</sub>、3 1<sub>b</sub>、3 1<sub>g</sub> の電位は図 6 に示すように基準電位 v<sub>b 1</sub> から v<sub>ide o</sub> 電位に移行する。この期間、制御線 3 3<sub>1</sub> に加えられる走査信号 P<sub>1</sub> はロウレベルとなって、スイッチ Q 4 R、Q 4 B、Q 4 G は OFF し、駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲート電位は閾値電圧 V<sub>t h</sub> から v<sub>b 1</sub> - v<sub>ide o</sub> 電位分下がる。このシーケンスにより、駆動トランジスタ Q 1 R、Q 1 B、Q 1 G は閾値のばらつきに左右されない駆動電流を得ることができる。 30

【0044】

時刻 t<sub>3</sub> から時刻 t<sub>4</sub> の期間、時刻 t<sub>4</sub> から時刻 t<sub>5</sub> に関しては、図 3 に示した、時刻 t<sub>2</sub> から時刻 t<sub>3</sub> の期間、時刻 t<sub>3</sub> から時刻 t<sub>4</sub> の間とそれぞれ同じシーケンスであり説明を省略する。

【0045】

(第3の実施形態)

図 7 は本発明によるアクティブマトリックス型表示装置の第3の実施形態の画素の回路構成図である。

【0046】

図 7 に示す回路構成において、積層構造の EL 素子との接続関係については図 1 に示した回路構成と同じである。したがって、本実施形態の説明は図 1 との差異に関して述べるにとどめる。

【0047】

駆動回路 2 3、2 4、2 5 の駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲート - ドレイン間にそれぞれ、スイッチ Q 4 R、Q 4 B、Q 4 G を設けている。スイッチ Q 4 R、Q 4 B、Q 4 G のゲートは制御線 3 3<sub>1</sub> と接続される。さらにデータ線 3 1<sub>r</sub>、3 1<sub>b</sub>、3 1<sub>g</sub> と駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲートとの間に容量 C 1 R、C 1 B、C 1 G を設けている。図 1 のスイッチ Q 2 R、Q 2 B、Q 2 G は設けられていない。

【0048】

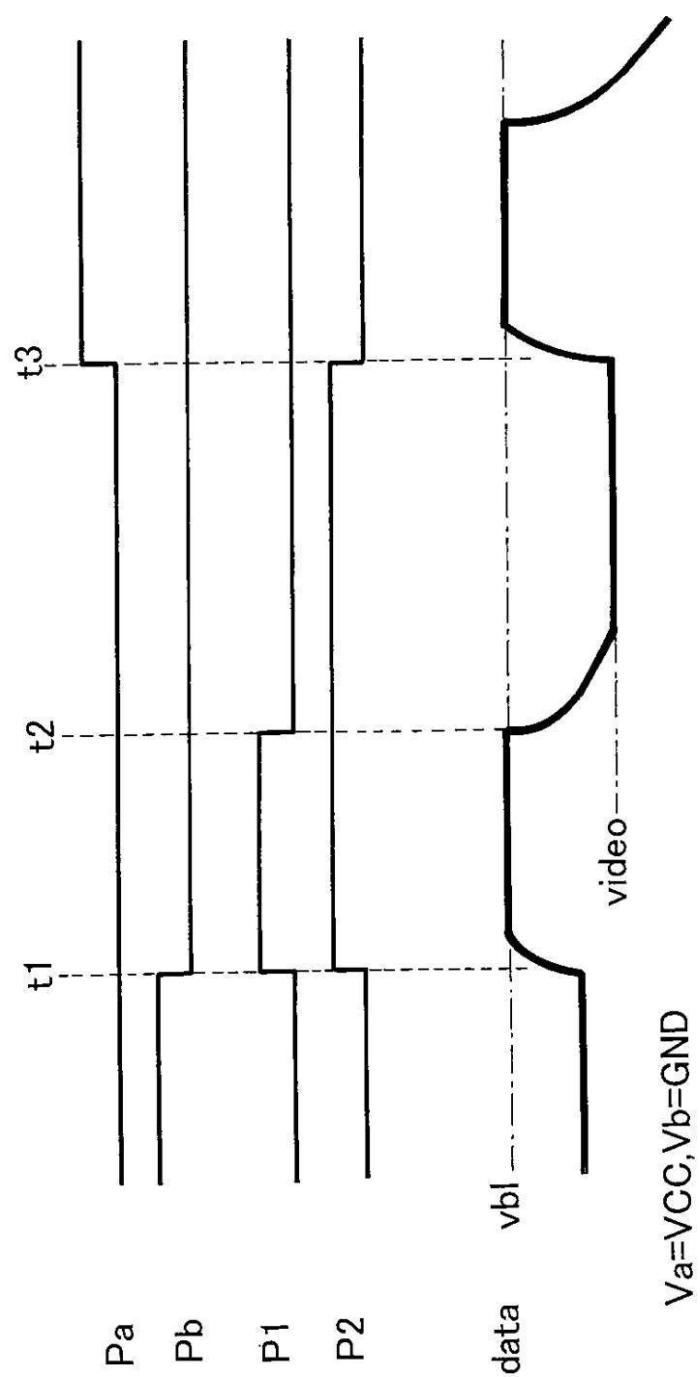

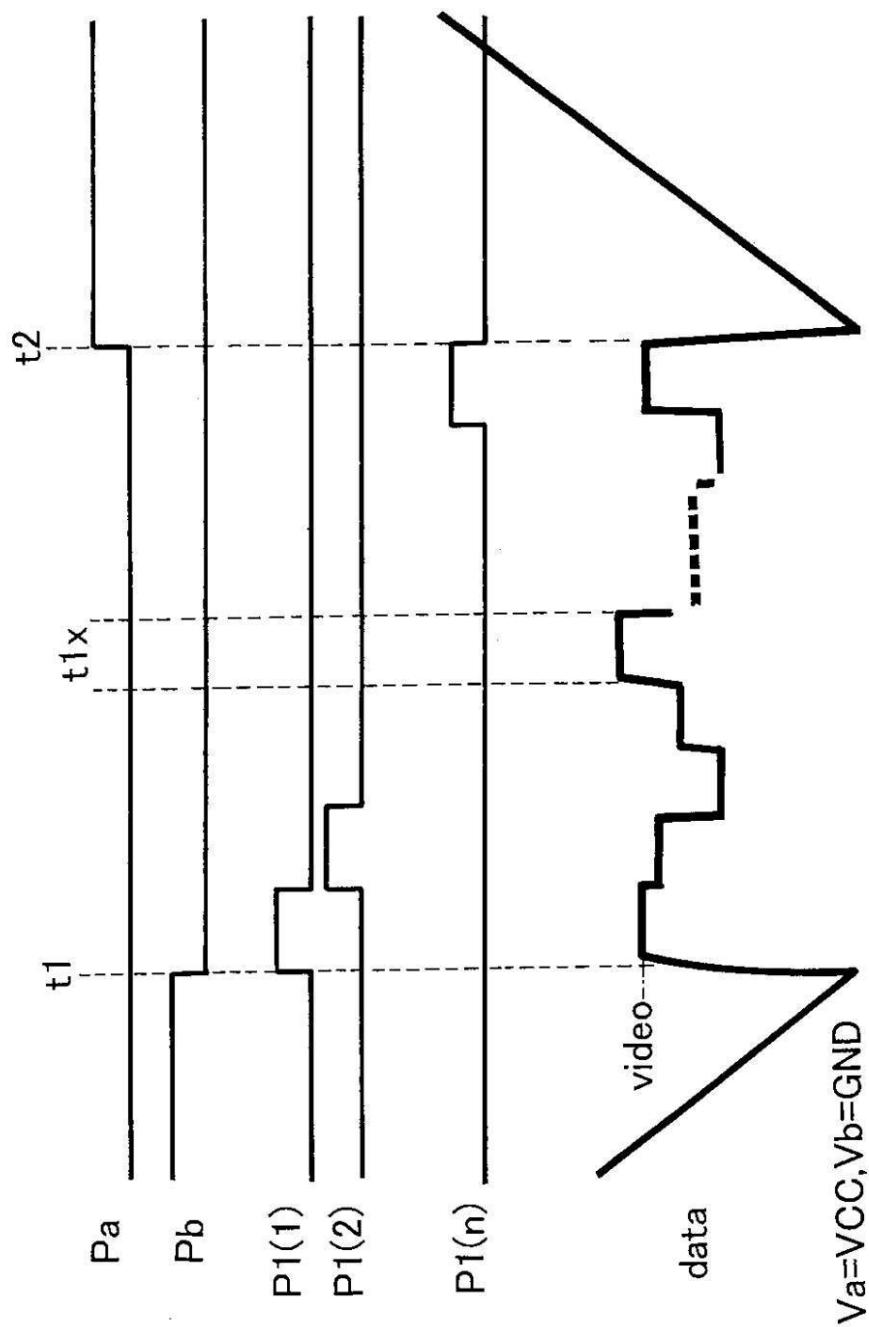

画素回路の動作をタイミングチャート図 8 及び図 9 により説明する。図 8 及び図 9 にお 50

ける  $P_a$ 、 $P_b$ 、 $P_1(1) \sim P_1(n)$  は図 7 の制御線  $33_a$ 、 $33_b$ 、 $33_1$  に加えられる走査信号、 $V_c$  は図 7 の電源線  $30_c$  に加えられる電圧信号を示す。なお、 $P_1(1) \sim P_1(n)$  は走査線  $11_1 \sim 11_n$  の制御線  $33_1$  に加えられる走査専号である。また、電圧  $V_a$  は電源線  $30_a$  に加えられる電圧で、ここでは電圧  $V_{cc}$ 、 $V_b$  は電源線  $30_b$  に加えられる電圧で、ここではグランド GND である。

#### 【0049】

時刻  $t_1$  から時刻  $t_2$  の期間  $T_1$  において、走査線  $11_1 \sim 11_n$  の全行の画素がプログラム期間となる。図 9 は期間  $T_1$  のプログラムのタイミングをより詳細に示したタイミングチャートである。

#### 【0050】

$P_1(1) \sim P_1(n)$  は第 1 の画素行から第  $n$  の画素行にそれぞれ印加される走査信号であり、期間  $T_1$  を  $n$  等分した期間、それぞれハイレベル状態になり、期間  $T_1$  内で順次、第 1 の画素行から第  $n$  の画素行へと各画素行の制御線  $33_1$  がハイレベルとなるようにシフトする。

#### 【0051】

走査信号  $P_1(x)$  ( $x$  は  $1 \sim n$  までの自然数) により、ある画素行における画素内のスイッチ  $Q4R$ 、 $Q4B$ 、 $Q4G$  が ON し、駆動トランジスタ  $Q1R$ 、 $Q1B$ 、 $Q1G$  のゲート - ドレイン間がショートされる。この状態において、駆動トランジスタ  $Q1R$ 、 $Q1B$ 、 $Q1G$  はダイオード接続となり、各駆動トランジスタのゲート - ソース間電位は閾値電圧  $V_{th}$  に収束する。この間、各データ線  $31_r$ 、 $31_b$ 、 $31_g$  にそれぞれ加えられる映像信号  $data_r$ 、 $data_b$ 、 $data_g$  の電圧は、図 9 に示す期間  $t_1 \sim t_2$  に  $video$  の電位となり、それぞれ容量  $C1R$ 、 $C1B$ 、 $C1G$  の一端に伝達される。期間  $t_1 \sim t_2$  で、容量  $C1R$ 、 $C1B$ 、 $C1G$  の電位差は各駆動トランジスタの閾値電圧との差分で保持される。

#### 【0052】

時刻  $t_2$  から時刻  $t_3$  の期間  $T_2$  (第 1 発光期間) では、データ線  $31_r$ 、 $31_b$ 、 $31_g$  に図 8 に示す三角波信号が印加される。この三角波信号電位と  $video$  電圧によりプログラミングされた電位差を保持したまま、各駆動トランジスタ  $Q1R$ 、 $Q1B$ 、 $Q1G$  のゲート電圧は変動し、閾値電圧  $V_{th}$  を超えた時、駆動電流が発生する。制御線  $33_a$  に加えられる走査信号  $P_a$  により、スイッチ  $Q3R$ 、 $Q3G$  が ON し、駆動トランジスタ  $Q1R$ 、 $Q1G$  から信号電流が、EL 素子 26、28 に流れ、発光状態になる。

#### 【0053】

時刻  $t_3$  から時刻  $t_4$  の期間  $T_3$  (図 2 における第 2 発光期間) では、時刻  $t_2$  から時刻  $t_3$  の期間  $T_2$  と同様に三角波が発生する。この三角波信号電位と  $video$  電圧によりプログラミングされた電位差を保持したまま、各駆動トランジスタ  $Q1R$ 、 $Q1B$ 、 $Q1G$  のゲート電圧は変動し、閾値電圧  $V_{th}$  を超えた時、駆動電流が発生する。制御線  $33_b$  に加えられる走査信号  $P_b$  により、スイッチ  $Q3B1$ 、 $Q3B2$  が ON し、駆動トランジスタ  $Q1B$  から信号電流が、EL 素子 27、29 に信号電流が流れ、発光状態になる。

#### 【0054】

なお、発光期間に発生するデータ線の信号は三角波でなく矩形波でもよい。

#### 【0055】

(第 4 の実施形態)

図 10 は本発明によるアクティブマトリックス型表示装置の第 4 の実施形態の画素の回路構成図である。

#### 【0056】

図 10 に示す回路構成において、積層構造の EL 素子との接続関係については図 1 に示した回路構成と同じであり、全体の駆動シーケンスも図 2 のタイミングと同一である。したがって、本実施形態の説明は図 1 との差異に関して述べるにとどめる。

#### 【0057】

駆動回路 23、24、25 の駆動トランジスタ  $Q1R$ 、 $Q1B$ 、 $Q1G$  のゲート - ドレ

10

20

30

40

50

イン間にそれぞれ、スイッチ Q 4 R、Q 4 B、Q 4 Gを設けている。そして、スイッチ Q 4 R、Q 4 B、Q 4 Gのゲートは制御線 3 3<sub>1</sub>と接続される。さらに各データ線 3 1 r、3 1 b、3 1 gと駆動トランジスタ Q 1 R、Q 1 B、Q 1 Gのドレインと間にはスイッチ Q 2 R、Q 2 B、Q 2 Gを設けている。スイッチ Q 2 R、Q 2 B、Q 2 Gのゲートは制御線 3 3<sub>2</sub>と接続される。

【0058】

画素回路の動作をタイミングチャート図 1 1により説明する。図 1 1における P a、P b、P 1、P 2は図 1 0の制御線 3 3<sub>a</sub>、3 3<sub>b</sub>、3 3<sub>1</sub>、3 3<sub>2</sub>に加えられる走査信号、V c は図 1 0の電源線 3 0<sub>c</sub>に加えられる電圧信号を示す。また、電圧 V a は電源線 3 0 a に加えられる電圧で、ここでは電圧 V c c、V b は電源線 3 0 b に加えられる電圧で、ここではグランド G N D である。

10

【0059】

時刻 t 1 から時刻 t 2 の期間 T<sub>1</sub>において、制御線 3 3<sub>1</sub>、3 3<sub>2</sub>に加えられる走査信号 P 1、P 2 がハイレベルとなって、スイッチ Q 4 R、Q 4 B、Q 4 G およびスイッチ Q 2 R、Q 2 B、Q 2 G がONする。すると、駆動トランジスタ Q 1 R、Q 1 B、Q 1 G のゲート - ドレイン間がショートされ、各データ線 3 1 r、3 1 b、3 1 g に接続される。データ線 3 1 r、3 1 b、3 1 g は外部の駆動回路の電流源と接続されており、その駆動電流に相当する電流値が駆動トランジスタ Q 1 R、Q 1 B、Q 1 G の駆動電流と等しくなるように、ゲート - ソース間電位が決定される。そして容量 C 1 R、C 1 B、C 1 G にその電位が保持される。

20

【0060】

時刻 t 2 から時刻 t 3 の期間、時刻 t 3 から時刻 t 4 に関しては、第 1 の実施形態と同じシーケンスであり説明を省略する。

【0061】

なお、第 1 ~ 第 4 の実施形態において、EL 素子 2 6, 2 8 の発光期間（第 3 の実施形態では第 1 発光期間）と、EL 素子 2 7, 2 9 の発光期間（第 3 の実施形態では第 2 発光期間）の比率は、EL 素子の効率を考慮し比率を変えても良い。また発光素子 2 6, 2 7, 2 8, 2 9 に対する色の組み合わせは上述に限定されるものではなく自由である。並列接続される EL 素子は、他の色と比べ劣化特性の劣る EL 素子にしてもよい。

30

【産業上の利用可能性】

【0062】

本発明は、画像表示に使用したアクティブマトリックス型表示装置に適用され、特に表示素子に EL 素子を用いたアクティブマトリックス型表示装置に適用される。

【図面の簡単な説明】

【0063】

【図 1】本発明によるアクティブマトリックス型表示装置の第 1 の実施形態の画素の回路構成図である。

40

【図 2】図 1 の回路を駆動するシーケンスを示す図である。

【図 3】図 1 の画素回路の動作を示すタイミングチャートである。

【図 4】本発明によるアクティブマトリックス型表示装置の第 2 の実施形態の画素の回路構成図である。

【図 5】図 4 の画素回路の動作をタイミングチャートである。

【図 6】図 4 の画素回路の動作をタイミングチャートである。

【図 7】本発明によるアクティブマトリックス型表示装置の第 3 の実施形態の画素の回路構成図である。

【図 8】図 7 の画素回路の動作を説明するタイミングチャートである。

【図 9】図 7 の画素回路の動作を説明するタイミングチャートである。

【図 10】本発明によるアクティブマトリックス型表示装置の第 4 の実施形態の画素の回路構成図である。

【図 11】図 1 0 の画素回路の動作を説明するタイミングチャートである。

50

【図12】EL素子を用いたアクティブマトリックス型の表示装置の構成例を示す平面図である。

【図13】EL素子を積層した場合のデバイスの模式的断面図である。

【符号の説明】

【0064】

21, 22 共通電極のタップ

23, 24, 25 駆動回路

30a, 30b 電源線

31r, 31g, 31b データ線

331, 332 走査線

33a, 33b 制御線

C1R, C1G, C1B 容量

Q1B N型トランジスタ

Q1R, Q1G P型トランジスタ

Q2R, Q3R, Q4R N型トランジスタ

Q2B, Q3B, Q4B N型トランジスタ

Q2G, Q3G, Q4G N型トランジスタ

26, 27, 28, 29 EL素子

10 画素

【図 1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図7】

【図 8】

【 囮 9 】

【図 10】

【図 11】

【図 1 2】

【図 1 3】

## フロントページの続き

|                        |                  |            |

|------------------------|------------------|------------|

| (51) Int.Cl.           | F I              | テーマコード(参考) |

| H 01 L 27/32 (2006.01) | G 09 G 3/20 623B |            |

|                        | G 09 G 3/20 680F |            |

|                        | G 09 F 9/30 338  |            |

|                        | G 09 F 9/30 365Z |            |

(72)発明者 永山 耕平

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 佐藤 信彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 三村 敏彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 EE07 HH04 HH05

5C080 AA06 BB05 CC03 DD30 EE28 FF09 FF11 HH09 JJ02 JJ03

JJ04 JJ05

5C094 AA37 AA53 BA03 BA27 CA19 DA13 DA15 DB04 EA04

【要約の続き】

【選択図】図1

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2010008907A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2010-01-14 |

| 申请号            | JP2008170687                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2008-06-30 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 川野藤雄<br>井関正己<br>永山耕平<br>佐藤信彦<br>三村敏彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 川野 藤雄<br>井関 正己<br>永山 耕平<br>佐藤 信彦<br>三村 敏彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 H01L51/50 H05B33/12 G09G3/20 G09F9/30 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F1分类号          | G09G3/30.J H05B33/14.A H05B33/12.C G09G3/20.624.B G09G3/20.623.D G09G3/20.623.B G09G3/20.680.F G09F9/30.338 G09F9/30.365.Z G09F9/30.365 G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/EE07 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD30 5C080/EE28 5C080/FF09 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C094/AA37 5C094/AA53 5C094/BA03 5C094/BA27 5C094/CA19 5C094/DA13 5C094/DA15 5C094/DB04 5C094/EA04 5C380/AA01 5C380/AB06 5C380/AB15 5C380/BA15 5C380/CA08 5C380/CA12 5C380/CA14 5C380/CB01 5C380/CB17 5C380/CC04 5C380/CC21 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC45 5C380/CC63 5C380/CC64 5C380/CC65 5C380/CD013 5C380/CD014 5C380/CD015 5C380/CD024 5C380/CD025 5C380/DA06 5C380/DA09 5C380/DA30 |         |            |

| 代理人(译)         | 雄一Uchio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

要解决的问题：提供适合于驱动有源矩阵型显示装置的电路配置，该有源矩阵型显示装置通过晶体管驱动层叠结构EL元件。解决方案：有源矩阵型显示装置包括多条扫描线，多条数据线和多个像素。每个像素包括：两个发光元件，连接到公共端子并且在电流的流动方向上彼此不同；和多个驱动电路。所述多个驱动电路包括：第一驱动电路，具有第一电容器和p型驱动晶体管，所述p型驱动晶体管根据所述第一电容的电压产生从所述公共端子流到所述发光元件的电流；具有第二电容的第二驱动电路和N型驱动晶体管，该N型驱动晶体管根据第二电容的电压产生从发光元件流到公共端的电流；并且由扫描线的扫描信号控制，从而数据线的图像信号分别保持在第一和第二容量中。因此，基于以第一容量保持的信号，第一驱动电路向一个发光元件提供电流，并且基于保持在第二电容中的信号，第二驱动电路向另一个发光元件提供电流。元件。乙