(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-184985

(P2004-184985A)

(43) 公開日 平成16年7月2日(2004.7.2)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611A

5C080

G09G 3/20

621F

G09G 3/20

621L

G09G 3/20

622B

審査請求有 請求項の数 12 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2003-346901(P2003-346901)

(22) 出願日

平成15年10月6日(2003.10.6)

(31) 優先権主張番号

2002-075470

(32) 優先日

平成14年11月29日(2002.11.29)

(33) 優先権主張国

韓国(KR)

(71) 出願人

503031422

ハナ・マイクロン・インコーポレイテッド

HANA MICRON INC.

大韓民国336-864チュンチョンナム

ド、アサンーシティ、ウムボンミョン、ソ

ドンリ、ナンバー10-9番

(74) 代理人

100084146

弁理士 山崎 宏

(74) 代理人

100100170

弁理士 前田 厚司

(72) 発明者

シン・ホンジエ

大韓民国139-764ソウル、ノウォン

ク、サンゲ9ドン、ジュゴン・アパートメ

ント1421-402

最終頁に続く

(54) 【発明の名称】有機電界発光ディスプレイ駆動装置及びその駆動方法

## (57) 【要約】

【課題】 OLEDパネル駆動装置の消費電力を小さくし、動作速度を高める。

【解決手段】 手動マトリックス方式のOLEDディスプレイパネル駆動装置において、スキャン駆動回路が3状態出力を有するように構成し、スキャン駆動回路がスキャン動作をする際に、選択されたカソードラインは接地を維持してデータが印加されたOLEDが発光をし、高電圧状態にスイッチングしてピクセルの電荷を初期化するリフレッシュ動作をした後、高インピーダンス状態を維持する動作をして非選択共通カソードラインを高インピーダンス状態にして寄生キャパシタンス成分を除去することによってOLEDのアノードラインに連結されたデータ駆動回路の負荷として作用するキャパシタンス成分を下げて、電圧源を使用して速い時間内にアノードラインを一定電圧以上に維持させた後、プリチャージ方法を使用せずに、OLED発光に必要な電流だけでアノードラインを短時間内に充電する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

格子状に配置された多数の共通アノードラインと多数の共通カソードラインの各交差点に画素を構成するOLEDが配置されてなされたOLEDパネル駆動装置において、

前記多数の共通アノードラインに連結され、前記共通アノードラインの夫々を所定の定電流源又は高インピーダンス端(HIZ)に選択的に連結する多数のデータ出力部を有するデータ駆動回路及び

前記多数の共通カソードラインに連結され、前記共通カソードラインの夫々を少なくとも高インピーダンス端(HIZ)又は接地端に選択的に連結する多数のスキャン出力部を有するスキャン駆動回路を含んでなされたことを特徴とするOLEDパネル駆動装置。 10

**【請求項 2】**

前記スキャン出力部は、高電圧端をさらに備えて、前記共通カソードラインの夫々を前記高電圧端、前記高インピーダンス端(HIZ)又は接地端に選択的に連結することを特徴とする請求項1に記載のOLEDパネル駆動装置。

**【請求項 3】**

水平同期信号、垂直同期信号及びディスプレイされるデータ信号を含む各種信号を発生させるOLED制御回路をさらに備えたことを特徴とする請求項2に記載のOLEDパネル駆動装置。 20

**【請求項 4】**

前記スキャン駆動回路は、

前記スキャン出力部；

前記共通カソードラインに対するスキャン制御信号(CSCAN)を発生させるシフトレジスタ部；及び

前記シフトレジスタ部で提供される前記スキャン制御信号(CSCAN)を論理的に処理して高インピーダンス制御信号(CHIZ)を発生させた後に前記スキャン出力部に提供する制御ロジック部；を含んでなされることを特徴とする請求項3に記載のOLEDパネル駆動装置。 30

**【請求項 5】**

前記スキャン出力部は、

入力端が前記高インピーダンス制御信号端(CHIZ)に連結されたインバータゲート；

一側入力端に前記スキャン制御信号端(CSCAN)が連結され、他の一側入力端には前記高インピーダンス制御信号端(CHIZ)が連結されたノアゲート；

一側入力端に前記スキャン制御信号端(CSCAN)が連結され、他の一側入力端には前記インバータゲートの出力端が連結された NANDゲート；

前記 NANDゲートの出力端に連結されて論理レベルを前記高電圧レベルに変換させる第1レベルシフタ；

前記ノアゲートの出力端に連結されて論理レベルを前記高電圧レベルに変換させる第2レベルシフタ；

前記第1レベルシフタにゲートが連結されソースは前記高電圧端に連結された第1PMOSFET；及び

前記第2レベルシフタにゲートが連結され、ドレンは前記第1PMOSFETのドレンに連結され、ソースは接地されたNMOSFET；を含んでなされ、前記共通カソードラインは前記第1PMOSFETと前記第1NMOSFETのドレンに連結されたことを特徴とする請求項4に記載のOLEDパネル駆動装置。 40

**【請求項 6】**

前記シフトレジスタ部は、前記共通カソードラインの個数だけのシフトレジスタが連結されてなされ、

前記シフトレジスタのうち第1列のシフトレジスタのデータ入力端には前記垂直同期信号が提供され、

前記シフトレジスタ全てのクロック端には前記水平同期信号が提供され、 50

前記シフトレジスタの任意列の出力は前記スキャン出力部の該当列のスキャン制御信号端（C SCAN）に連結されると同時に差列のシフトレジスタのデータ入力端に連結されたことを特徴とする請求項4に記載のOLEDパネル駆動装置。

#### 【請求項7】

前記制御ロジック部は、前記共通カソードラインの個数だけの2入力XNORゲートを含んでなされ、

前記XNORゲートの夫々の一側入力端は該当列の前記シフトレジスタの出力端に連結され、夫々の他側入力端は差列の前記シフトレジスタの出力端に連結され、出力端は前記スキャン出力部の該当列の前記高インピーダンス制御信号端（CHIZ）に連結されたことを特徴とする請求項6に記載のOLEDパネル駆動装置。 10

#### 【請求項8】

前記データ駆動回路は、

前記データ出力部；

前記OLED制御回路からの制御信号に従って前記共通アノードラインに印加されるデータを順次的にシフトさせて貯蔵するシフトレジスタ／ラッチ部；及び

前記シフトレジスタ／ラッチ部で提供されるデータを前記データの階調レベルに応じて異なる時間幅を有する制御信号（PWM）に変換した後に前記データ出力部に提供するPWM発生部；を含んでなされたことを特徴とする請求項3に記載のOLEDパネル駆動装置。 20

#### 【請求項9】

データ出力部は、

電流ミラー回路を構成する第2及び第3のPMOSFET；

前記PWM発生部から提供される前記制御信号（PWM）の論理レベルを前記高電圧レベルに変換する第3レベルシフタ；及び

前記第3レベルシフタによってオン／オフされて前記共通アノードラインを前記定電流源及び前記高インピーダンス端（HIZ）に選択的に連結する第4PMOSFET；を含んでなされたことを特徴とする請求項8に記載のOLEDパネル駆動装置。 30

#### 【請求項10】

前記第4PMOSFETがオフにされた状態で外部制御信号（Reset）によってオンにされて前記共通アノードラインを接地させる第2NMOSFETを含んでなされたことを特徴とする請求項9に記載のOLEDパネル駆動装置。 40

#### 【請求項11】

格子状に配置された多数の共通アノードラインと多数の共通カソードラインの各交差点に画素を構成するOLEDが配置されてなされたOLEDパネルの駆動方法において、

前記共通カソードラインを接地レベル（GND）に転換して順次的にスキャンする間にディスプレイされる画素データの階調レベルに応じて異なる時間幅を有する制御信号（PWM）によって前記共通アノードラインに定電流を印加する過程において、現在スキャンされる列を除外した残りの列の共通カソードラインは高インピーダンス状態に維持されることを特徴とするOLEDパネルの駆動方法。 50

#### 【請求項12】

前記現在スキャンされる列のすぐ前列を高電圧端に連結させることを特徴とする請求項11に記載のOLEDパネルの駆動方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、有機電界発光デバイスディスプレイ駆動装置及びその駆動方法に関する。特に、手動マトリックス方式のOLEDディスプレイ駆動装置において、スキャン駆動回路が3状態出力を有するように構成して、駆動装置の消費電力を下げ、動作速度を増加させることができるようにした有機電界デバイスディスプレイ駆動装置及びその駆動方法に関する（以下、簡単にOLEDパネル駆動装置及びその駆動方法という）。 50

## 【背景技術】

## 【0002】

TV、コンピュータ又は携帯電話の映像表示装置に液晶ディスプレイが広く使用されているところ、このような液晶ディスプレイはバックライトを必要とするため重いだけでなく厚く、応答速度が遅いという短所がある。このようなディスプレイを代替する次世代映像表示装置として注目を集めるものに有機電界発光ダイオード(Organic Light Emitting Diode)ディスプレイパネル(以下、略称して‘OLED・パネル’という)がある。OLEDパネルは $0.1\text{ }\mu\text{m}$ 以下の極めて薄い有機薄膜を含んでいる。このような有機薄膜に電流を流すとその電子輸送層(Electron Transport Layer)と正孔輸送層(Hole Transport Layer)の界面近辺で電子・正孔が再結合されて発光するが、この発光は数百[ns]以下の極めて速い応答時間を持つ。このように、OLEDは無機発光ダイオードと同じようにアノードとカソードの2極構造に成されているが、パネルを構成する個別OLEDの電圧-電流特性の差異によって電流駆動をすることになる。

## 【0003】

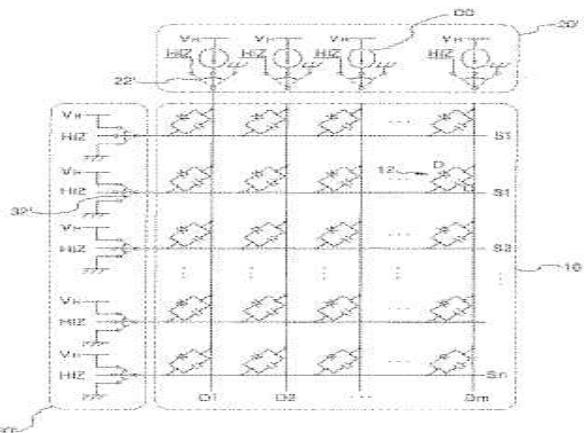

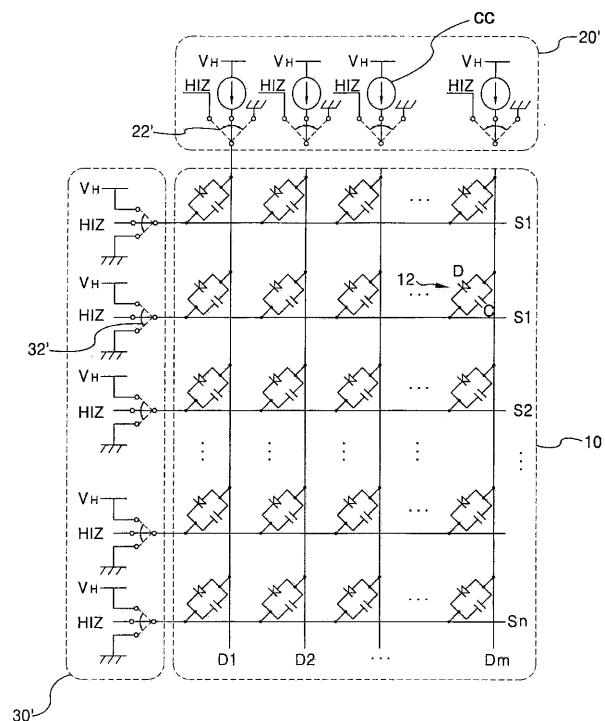

図1は、従来のプリチャージ方式のOLEDパネル駆動装置の概略ブロック構成図である。図1に示したように、OLEDパネル10は多数の共通アノードライン(D1、…Dm)と多数の共通カソードライン(S1、…、Sn)が格子状に配置され、このような格子の各交差点に画素(実際には1対のR/G/Bを1個の画素として構成している)を構成するOLED12が配置されてなされる。また、共通アノードライン(D1、…Dm)にはデータ駆動回路20が連結され、共通カソードライン(S1、…、Sn)にはスキャン駆動回路30が連結されている。

## 【0004】

スキャン駆動回路30は、機能的に図示しない制御部の制御に応じて、共通カソードライン(S1、…、Sn)を、高電圧(例えば15[V])端(VH)と接地端に、予め決められたパターンで選択的に連結するスキャン出力部32を含んでいる。図2は、図1において1個の共通カソードラインに対するスキャン出力部を示した詳細回路図である。図2に図示したとおり、スキャン出力部32は、図示しない外部制御部(未図示)からの制御信号(CSCAN)の論理レベルに応じて、共通カソードライン(Sy)を、高電圧端(VH)又は接地端(GND)に選択的に連結する。

## 【0005】

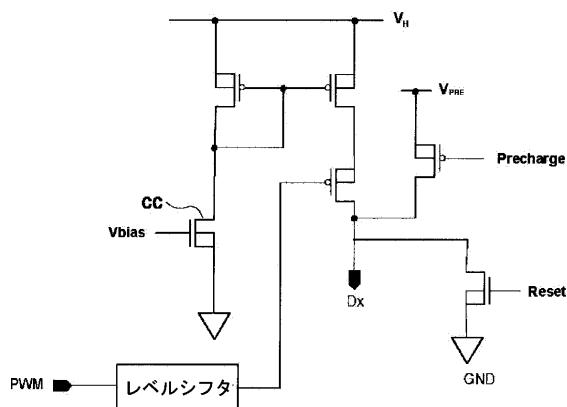

図3は、図1において1個の共通アノードラインに対するデータ出力部を示した詳細回路図である。図3に図示したように、データ出力部22も機能的に図示しない制御部の制御に応じて、個々の共通アノードライン(D1、…Dm)を、定電流源(CC)又は接地端(GND)に選択的に連結する。

## 【0006】

前述した構成において、スキャン出力部32が順次的にオン/オフにされつつ第1列(S1)から第n列(Sn)までの共通カソードラインを選択すると、データ出力部22は、これに同期して、該当画素、即ちOLED12に対する階調(Gray Scale)に従ってPWM(Pulse Width Modulation)方式によって異なって決められる時間幅の間、共通アノードライン(D1、…Dm)を定電流源(CC)側に連結して該当OLED12に電流を印加することによって1個の画面フレームを形成することになる。

## 【0007】

一方、OLED12は有機薄膜でなされているためダイオード(D)のアノードとカソードの両端に寄生キャパシタ(C)が存在するが、このような寄生キャパシタ(C)により低い階調処理を行うことができないという問題があるため、従来は共通アノードライン(D1、…Dm)にPWM電流を印加する前にダイオード(D)がターンオンされ得る程度の電圧を印加して寄生キャパシタCを予め充電(Precharging)させることになる。そして、このためにデータ出力部22には所定電圧、例えば4~6[V]程度のプリチャージ電圧端(VPRE)がさらに備えられる。

## 【0008】

10

20

30

40

50

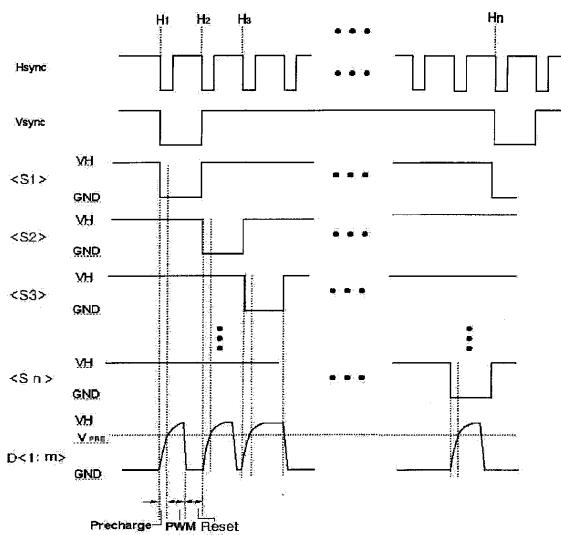

図4は、従来のプリチャージ方式のOLEDパネル駆動装置において、画面1フレームに対するスキャン出力タイミングと各スキャン出力区間におけるプリチャージ区間及びデータ出力区間との関係を示したタイミングチャートである。図4に図示したように、垂直同期信号(V sync)は画面の1フレーム毎に発生するが、このような垂直同期信号(V sync)間の垂直走査区間に共通カソードラインの個数(n)だけの水平同期信号(H sync)が発生し、水平同期信号(H sync)間の水平走査区間に全ての共通アノードライン(D1、...Dm)に同時にデータが印加される。即ち、各水平同期信号(H sync)の下降エッジに同期して発生する外部制御信号(C SCAN)に従ってスキャン出力部32が第1列の共通カソードライン(S1)を高電圧端(VH)で接地端(GND)に連結させると、これに同期した外部制御信号(Precharge)の制御に応じてデータ出力部22は予め決められた時間の間、全ての共通アノードライン(D1、...Dm)をプリチャージ電圧端(VPRE)に連結させてOLED12の寄生キャパシタ(C)を充電させる。それから、外部制御信号(PWM)の制御に応じてデータ出力部22が夫々の共通アノードライン(D1、...Dm)をここに連結されたOLED12の画素階調に応じて決められたPWM時間の間、定電流源(CC)に連結されることによってOLED12を発光させる。その後に再度データ出力部22が外部制御信号(Reset)の制御に応じて共通アノードライン(D1、...Dm)を接地端(GND)に連結されることによって寄生キャパシタ(C)に充電された電圧を放電させる。そして、このような方式で第n列までの共通カソードライン(Sn)に対する動作を遂行して画面1フレームが構成される。

10

20

30

40

50

## 【0009】

しかし、前述したような従来のプリチャージ方式のOLEDパネル駆動装置によれば、データ出力部22が共通アノードライン(D1、...Dm)を動作させる過程においてここに並列に連結された全ての寄生キャパシタ(C)が反復的に充電及び放電(結果的にOLED両端電圧の極性が反転)されるため、OLEDパネル10に大きな値の電流が流れることになるが、これに伴なう消費電力は次の数式1の通りである。

## 【数1】

$$P_d = n * m * C * V_H^2 * f_{clk}$$

## 【0010】

上記の数式1においてnは共通カソードラインの数を、mは共通アノードラインの数を、Cは寄生キャパシタンスを、VHはアノードに印加される高電圧を、fclkはスキャン駆動回路30の動作周波数を夫々表す。数式1において分かるように、従来のOLEDパネル駆動装置においては寄生キャパシタの充電・放電時に大きい値の電流が必要であるため消費電力が上昇し、データ駆動回路の動作速度も低下するという問題点がある。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0011】

本発明は、前述した問題点を解決するために案出されたものであって、手動マトリックス方式のOLEDパネル駆動装置において、スキャン駆動回路が少なくともスキャン状態及び高インピーダンス状態の2状態出力を有するように構成し、非選択共通カソードラインを高インピーダンス状態にして寄生キャパシタンス成分を除去することによって消費電力を下げ、動作速度を増加させることができるようにしたOLEDパネル駆動装置及びその駆動方法を提供することにその目的がある。

## 【0012】

本発明の他の目的は、前記スキャン駆動回路が高電圧状態、スキャン状態及び高インピーダンス状態の3状態出力を有するように構成し、非選択共通カソードラインを高インピーダンス状態にする前にまず高電圧状態にして寄生キャパシタンスの極性を反転させることによってOLEDの両端が同じ極性を維持し続けることによる劣化を防ぐことができるようにしたOLEDパネル駆動装置及びその駆動方法を提供するところにある。

## 【課題を解決するための手段】

## 【0013】

前述した目的を達成するための本発明のOLEDパネル駆動装置は、格子状に配置された多数の共通アノードラインと多数の共通カソードラインの各交差点に画素を構成するOLEDが配置されてなされたOLEDパネル駆動装置において、前記多数の共通アノードラインに連結され、前記共通アノードラインの夫々を所定の定電流源又は高インピーダンス端(HIZ)に選択的に連結する多数のデータ出力部を有するデータ駆動回路、及び前記多数の共通カソードラインに連結され、前記共通カソードラインの夫々を少なくとも高インピーダンス端(HIZ)又は接地端に選択的に連結する多数のスキャン出力部を有するスキャン駆動回路を含んでなされたことを特徴とする。前述した構成において、前記スキャン出力部は高電圧端をさらに備えて前記共通カソードラインの夫々を前記高電圧端、前記高インピーダンス端(HIZ)又は接地端に選択的に連結するようによくすることが望ましい。10

## 【0014】

また、接地端に選択的に連結する多数のデータ出力部を有するデータ駆動回路を含んでなされたことを特徴とする。前述した構成において、前記装置は、水平同期信号、垂直同期信号及びディスプレイされるデータ信号を含む各種信号を発生させるOLED制御回路をさらに備えてなされる。

## 【0015】

一方、前記スキャン駆動回路は、前記スキャン出力部；前記共通カソードラインに対するスキャン制御信号(CSCAN)を発生させるシフトレジスタ部；及び前記シフトレジスタ部で提供される前記スキャン制御信号(CSCAN)を論理的に処理して高インピーダンス制御信号(CSCAN)を発生させた後に前記スキャン出力部に提供する制御ロジック部；を含んでなされ得る。20

## 【0016】

前記スキャン出力部は、入力端が前記高インピーダンス制御信号端(CHIZ)に連結されたインバータゲート；一側入力端に前記スキャン制御信号端(CSCAN)が連結され、他の一側入力端には前記高インピーダンス制御信号端(CHIZ)が連結されたノアゲート；一側入力端に前記スキャン制御信号端(CSCAN)が連結され、他の一側入力端には前記インバータゲートの出力端が連結された NAND ゲート；前記 NAND ゲートの出力端に連結されて論理レベルを前記高電圧レベルに返還させる第1レベルシフタ；前記ノアゲートの出力端に連結されて論理レベルを前記高電圧レベルに返還させる第2レベルシフタ；前記第1レベルシフタにゲートが連結され、ソースは前記高電圧端に連結された第1PMOSFET；及び前記第2レベルシフタにゲートが連結され、ドレインは前記第1PMOSFETのドレインに連結され、ソースは接地されたNMOSFET；を含んでなされ、前記共通カソードラインは前記第1PMOSFETと前記第1NMOSFETのドレインに連結される。30

## 【0017】

また、前記シフトレジスタ部は、前記共通カソードラインの個数ほどのシフトレジスタが連結されてなされ、前記シフトレジスタのうち第1列のシフトレジスタのデータ入力端には前記垂直同期信号が提供され、前記シフトレジスタ全てのクロック端には前記水平同期信号が提供され、前記シフトレジスタの任意列の出力は前記スキャン出力部の該当列のスキャン制御信号端(CSCAN)に連結されると同時に差列のシフトレジスタのデータ入力端に連結される。40

## 【0018】

また、前記制御ロジック部は前記共通カソードラインの個数ほどの2入力XNORゲートを含んでなされ、前記XNORゲートの夫々の一側入力端は該当列の前記シフトレジスタの出力端に連結され、夫々の他側入力端は差列の前記シフトレジスタの出力端に連結され、出力端は前記スキャン出力部の該当列の前記高インピーダンス制御信号端(CHIZ)に連結される。

## 【0019】

また、前記データ駆動回路は、前記データ出力部；前記OLED制御回路からの制御信号に応じて前記共通アノードラインに印加されるデータを順次的にシフトさせて貯蔵するシフトレジスタ／ラッチ部；及び前記シフトレジスタ／ラッチ部において提供されるデータを前記データの階調レベルに応じて異なる時間幅を有する制御信号（PWM）に変換した後に前記データ出力部に提供するPWM発生部；を含んでなされ得る。

#### 【0020】

また、データ出力部は、電流ミラー回路を構成する第2及び第3のPMOSFET；前記PWM発生部から提供される前記制御信号（PWM）の論理レベルを前記高電圧レベルに返還する第3レベルシフタ；及び前記第3レベルシフタによってオン／オフされて前記共通アノードラインを前記定電流源及び前記高インピーダンス端（HIZ）に選択的に連結する第4PMOSFET；を含んでなされ得る。

#### 【0021】

また、前記第4PMOSFETがオフにされた状態において外部制御信号（Reset）によってオンにされて前記共通アノードラインを接地させる第2NMOSFETをさらに含ませることもできる。

#### 【0022】

本発明の他の特徴によるOLEDパネル駆動方法は格子状に配置された多数の共通アノードラインと多数の共通カソードラインの各交差点に画素を構成するOLEDが配置されてなされたOLEDパネルの駆動方法において、前記共通カソードラインを接地レベル（GND）に転換して順次的にスキャンする間ディスプレイされる画素データの階調レベルに応じて異なる時間幅を有する制御信号（PWM）によって前記共通アノードラインに定電流を印加する過程において、現在スキャンされる列を除外した残る列の共通カソードラインは高インピーダンス状態に維持させることを特徴とする。

#### 【0023】

前述した方法において、前記現在スキャンされる列のすぐ前の列を高電圧端に連結させると寄生キャパシタンスの極性を反転させることができOLEDの劣化を防ぐことができる。

#### 【発明の効果】

#### 【0024】

以上において説明したような本発明のパネルOLED駆動装置及びその駆動方法によれば、プリチャージ方式を使用しなくてもPWMデータ電流量のみでも低い階調処理が可能なようにしてプリチャージ時に発生する消費電力を減らし、高速動作を可能にする効果がある。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下には、添付した図面を参照して、本発明の望ましい実施例によるOLEDパネルの駆動装置及びその駆動方法を説明する。

#### 【0026】

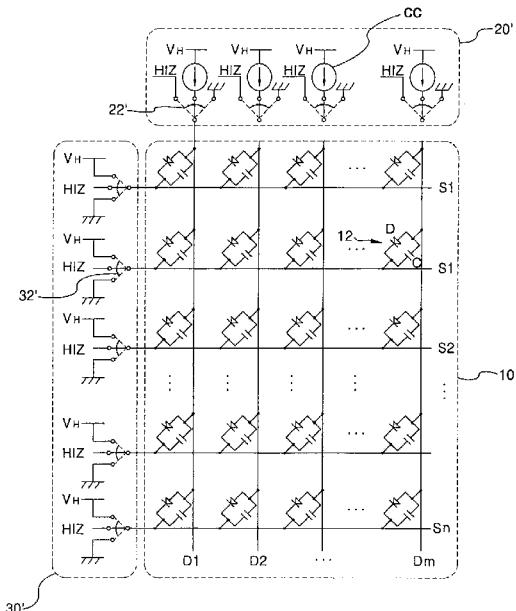

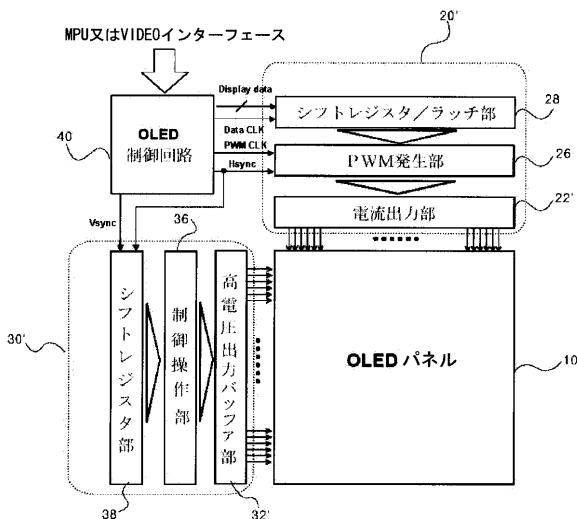

図5は本発明のOLEDパネル駆動装置の概略ブロック構成図である。図5に図示したように、OLEDパネル10は多数の共通アノードライン（D1, ..., Dm）と多数の共通カソードライン（S1, ..., Sn）が格子状に配置され、このような格子の各交差点に画素を構成するOLED12が配置されてなされる。共通アノードライン（D1, ..., Dm）にはデータ駆動回路20'が連結され、共通カソードライン（S1, ..., Sn）にはスキャン駆動回路30'が連結されている。

#### 【0027】

スキャン駆動回路30'は機能的に図示しない制御部の制御に応じて共通カソードライン（S1, ..., Sn）を高電圧（例えば15[V]）端（VH）、高インピーダンス端（HIZ）及び接地端（GND）に予め決められたパターンに選択的に連結するスキャン出力部32'を含んでなされる。ここで、高電圧端（VH）は寄生キャパシタの極性、即ちOLED12両端電圧の極性を反転させることによってOLED12の両端が同じ極性に維持

10

20

30

40

50

され続けるのに従って O L E D 1 2 が劣化するのを防ぐために与えられるところ、その動作に対しても後述する。

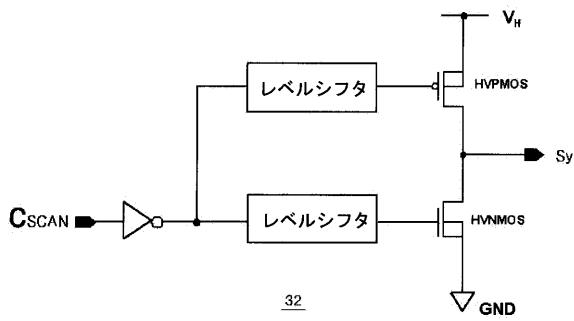

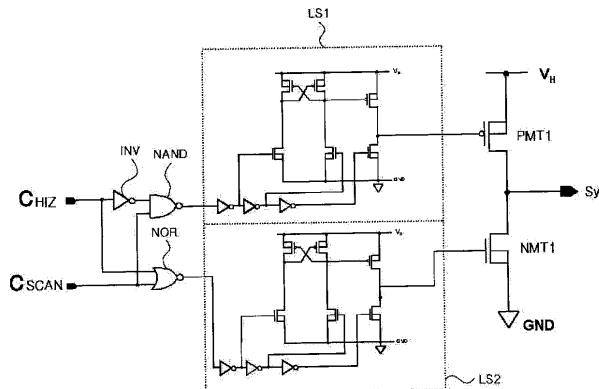

#### 【 0 0 2 8 】

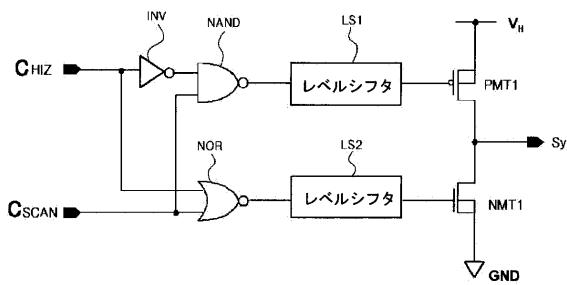

図 6 は、図 5 において 1 個の共通カソードラインに対するスキャン出力部を示したブロック図である。図 6 に図示したように、夫々のスキャン出力部 3 2 ' は入力端が高インピーダンス制御信号端 ( C H I Z ) に連結されたインバータゲート ( I N V ) 、一側入力端にスキャン制御信号端 ( C S C A N ) が連結され、他の一側入力端には高インピーダンス制御信号端 ( C H I Z ) が連結されたノアゲート ( N O R ) 、一側入力端にスキャン制御信号端 ( C S C A N ) が連結され、他の一側入力端にはインバータゲート ( I N V ) の出力端が連結された NAND ゲート ( N A N D ) 、 NAND ゲート ( N A N D ) の出力端に連結されてその論理レベル ( V c c ) を高電圧レベル ( V H ) に変換させる第 1 レベルシフタ ( L S 1 ) 、ノアゲート ( N O R ) の出力端に連結されてその論理レベル ( V c c ) を高電圧レベル ( V H ) に変換させる第 2 レベルシフタ ( L S 2 ) 、第 1 レベルシフタ ( L S 1 ) にゲートが連結されソースは高電圧端 ( V H ) に連結された P M O S F E T ( P M T 1 ) 及び第 2 レベルシフタ ( L S 2 ) にゲートが連結され、ドレインは P M O S F E T ( P M T 1 ) のドレインに連結され、ソースは接地された N M O S F E T ( N M T 1 ) を含んでなされ、共通カソードライン ( S y ) は P M O S F E T ( P M T 1 ) と N M O S F E T ( N M T 1 ) のドレインに連結されている。

10

#### 【 0 0 2 9 】

前述した構成において、外部の制御部 ( 未図示 ) においてスキャン制御信号端 ( C S C A N ) と高インピーダンス制御信号端 ( C H I Z ) に夫々論理 “ 0 ” の信号を出力すると NAND ゲート ( N A N D ) とノアゲート ( N O R ) においては夫々論理 “ 1 ” の信号が出力され、このような論理 “ 1 ” 信号は第 1 レベルシフタ ( L S 1 ) と第 2 レベルシフタ ( L S 2 ) において高電圧レベル ( V H ) に変換され、これによって P M O S F E T ( P M T 1 ) はオフにされる反面、 N M O S F E T ( N M T 1 ) はオンにされて共通カソードライン ( S y ) は接地端 ( G N D ) に連結されることとなる。

20

#### 【 0 0 3 0 】

そして、スキャン制御信号端 ( C S C A N ) に論理 “ 1 ” の信号が出力され、高インピーダンス制御信号端 ( C H I Z ) に論理 “ 0 ” の信号が出力されると、 NAND ゲート ( N A N D ) とノアゲート ( N O R ) では夫々論理 “ 0 ” の信号が出力され、このような論理 “ 0 ” の信号は第 1 レベルシフタ ( L S 1 ) と第 2 レベルシフタ ( L S 2 ) において低電圧レベルに変換され、これに伴なって P M O S F E T ( P M T 1 ) はオンにされる反面、 N M O S F E T ( N M T 1 ) はオフにされて共通カソードライン ( S y ) は高電圧端 ( V H ) に連結される。

30

#### 【 0 0 3 1 】

一方、高インピーダンス制御信号端 ( C H I Z ) に論理 “ 1 ” の信号が出力されるとスキャン制御信号端 ( C S C A N ) に入力される論理信号のレベルに関係なく NAND ゲート ( N A N D ) においては論理 “ 1 ” の信号が出力される反面、ノアゲート ( N O R ) では論理 “ 0 ” の信号が出力される。これに応じて P M O S F E T ( P M T 1 ) と N M O S F E T ( N M T 1 ) が全てオフにされて共通カソードライン ( S y ) は機能的に高インピーダンス端 ( H I Z ) に連結された状態、即ちフローティング ( floating ) 状態になる。これを真理表に表すと次の表 1 の通りである。

40

#### 【 0 0 3 2 】

【表1】

| C SCAN | C HIZ | V NAND | V NOR | PMOSFET | NMOSFET | S <sub>y</sub> |

|--------|-------|--------|-------|---------|---------|----------------|

| 0      | 0     | 1      | 1     | Off     | On      | GND            |

| 1      | 0     | 0      | 0     | On      | Off     | V <sub>H</sub> |

| 0      | 1     | 1      | 0     | Off     | Off     | HIZ            |

| 1      | 1     | 1      | 0     | Off     | Off     | HIZ            |

10

## 【0033】

図7は、図6に図示したスキャン出力部の詳細回路図である。

## 【0034】

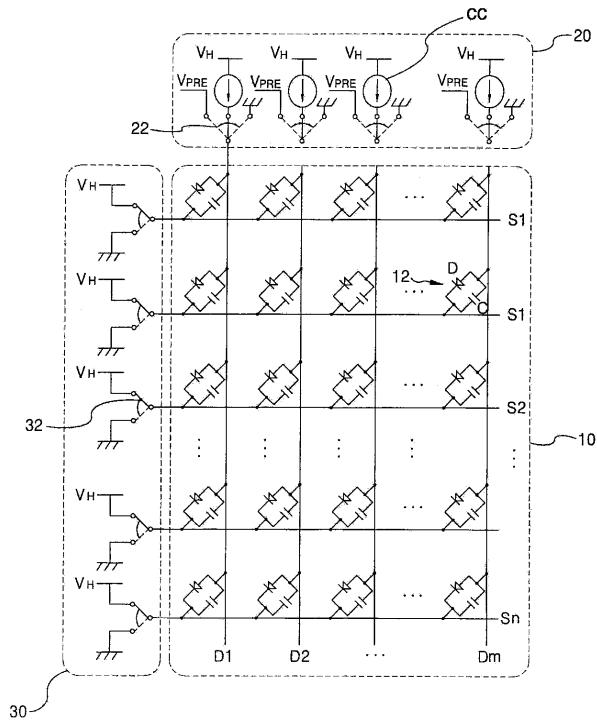

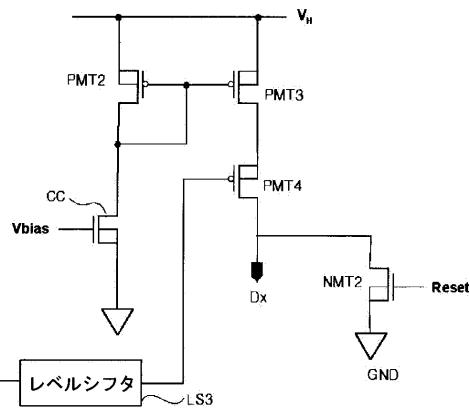

一方、データ出力部22'も機能的に図示しない制御部の制御に応じて個々の共通アノードライン(D1、...Dm)を定電流源(CC)と高インピーダンス端(HIZ)に選択的に連結させる。図8は、図5において1個の共通カソードラインに対するデータ出力部を示した詳細回路図である。図8に図示したように、データ出力部22'は、電流ミラー回路を構成する2個のPMOSFET(PMT2)、(PMT3)、電流ミラー回路に連結された定電流源(CC)、外部制御信号(PWM)の論理レベルを高電圧レベル(VH)に変換する第3レベルシフタ(LS3)及び第3レベルシフタ(LS3)によってオン/オフされて共通アノードライン(DX)に定電流を印加するPMOSFET(PMT4)を含んでなされる。本図において、参照符号NMT2は、PMOSFET(PMT4)がオフにされた状態で必要時に外部制御信号(Reset)によってオンにされて共通アノードライン(DX)を接地させるNMOSFETを示す。

20

## 【0035】

図9は、本発明のOLEDパネル駆動装置の詳細ブロック構成図である。図9に図示したように、本発明のOLEDパネル駆動装置は、大きくスキャン駆動回路30'、データ駆動回路20'及びスキャン駆動回路30'データ駆動回路20'に各種クロック信号(PWM CLK, DataCLK等)とデータ(Display Data等)及び制御信号(Vsync, Hsync等)を出力するOLED制御回路40を含んでなされ得る。

30

## 【0036】

前述した構成において、データ駆動回路20'は、前述したデータ出力部22'(当業界での通常的な表現に従って本図面においてはこれを“電流出力部”と記載する)、OLED制御回路40で提供されるデータクロック信号(data CLK)に同期して同じくOLED制御回路40で提供されるR、G、B画面データ(Display Data)、即ち究極的に共通アノードライン(D1、...Dm)に印加されるデータを順次的にシフトさせて貯蔵するシフトレジスタ/ラッチ部28及びシフトレジスタ/ラッチ部28で提供されるデータをその階調レベルに応じて異なる時間幅を有する信号に変換した後にデータ出力部22'に提供するPWM発生部26を含んでなされ得る。OLED制御回路40ではこのためにPWM発生部26にPWMクロック信号(PWM CLK)を提供している。

40

## 【0037】

一方、スキャン駆動回路30'は前述したスキャン出力部32'(当業界での通常的な表現に従って本図面では“高電圧出力バッファ部”と記載している)、OLED制御回路40において提供される水平同期信号(Hsync)に応じて選択される共通カソードライン(S1、...Sn)に対するスキャン制御信号(CSCAN)を発生させるシフトレジスタ部38及びシフトレジスタ部38で提供されるスキャン制御信号(CSCAN)を論理的に処理してスキャン制御信号(CSCAN)と高インピーダンス制御信号(CHIZ)を発生させてスキャン出力部22'に提供する制御ロジック部36を含んでなされ得る。

## 【0038】

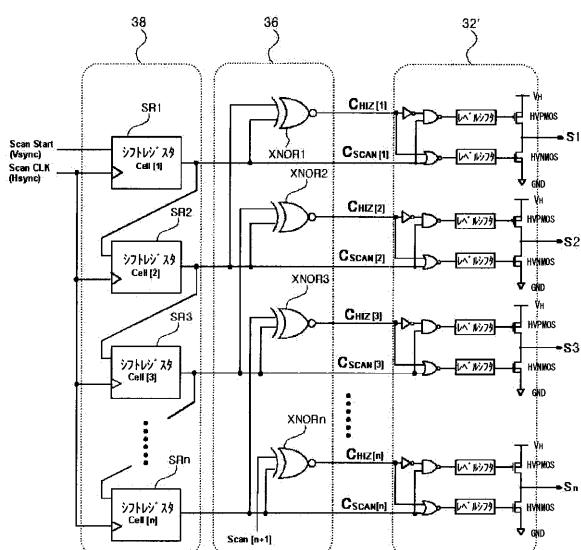

図10は、図9においてスキャン駆動回路の一実施例による詳細回路図である。図10

50

に図示したように、シフトレジスタ部 38 は、共通カソードラインの数 n だけの単位シフトレジスタ (SR1, ..., SRn) が直列に連結されてなされるが、全てのシフトレジスタ (SR1, ..., SRn) のクロック端には、水平同期信号 (Hsync) が提供される。そして、第 1 列のシフトレジスタ (SR1) のデータ入力端には OLED 制御回路 40 で出力された垂直同期信号 (Vsync) が提供され、残りのシフトレジスタ (SR1, ..., SRn) においては任意列のシフトレジスタ (S Ry) の出力は、スキャン出力部 32' の該当スキャン制御信号端 (CSCAN) に直結されると同時に差列のシフトレジスタ (S Ry+1) のデータ入力端に連結される。シフトレジスタ (SR1, ..., SRn) は負論理回路で構成、即ちデータ信号とクロック信号の下降エッジで動作するように構成されている。

## 【0039】

10

制御ロジック部 36 は 2 入力を有し、やはり共通カソードラインの数 (n) だけの単位 XNOR ゲート (XNOR1, ..., XNORn) でなされるが、各列の XNOR ゲート (XNORy) の一側入力端は該当列のシフトレジスタ (S Ry) の出力端に連結され、他側入力端は差列のシフトレジスタ (S Ry+1) の出力端に連結され、その出力端はスキャン出力部 32' の該当高インピーダンス制御信号端 (CHIZ) に連結される。

## 【0040】

以下には、本発明の OLED パネル駆動装置の動作をその方法と共に詳細に説明する。

## 【0041】

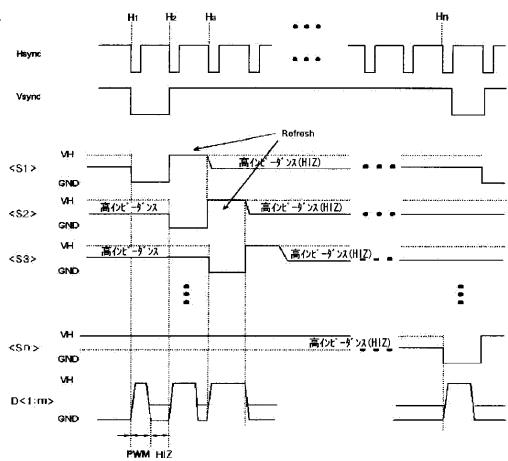

図 11 は、本発明の OLED パネル駆動方法を説明するためのスキャン駆動回路とデータ駆動回路の動作タイミング図である。図 11 に図示したように、垂直同期信号 (Vsync) は画面の 1 フレーム毎に発生するが、このような垂直同期信号 (Vsync) 間の垂直走査区間に共通カソードラインの個数 (n) だけの水平同期信号 (Hsync) が発生し、水平同期信号 (Hsync) 間の水平走査区間にすべての共通アノードライン (D1, ..., Dm) に同時にデータが印加される。これをより詳細に説明すると、OLED 制御回路 40 で発生された垂直同期信号 (Vsync) がスキャン駆動回路 30' の第 1 列のシフトレジスタ (SR1) のデータ入力端に提供され、これと同時に水平同期信号 (Hsync) がそのクロック端に提供されると、第 1 列のシフトレジスタ (SR1) は垂直同期信号 (Vsync) と水平同期信号 (Hsync) の下降エッジで動作してその出力端、即ちスキャン制御信号端 (CSCAN) に論理 “0” の信号を出力する。

20

## 【0042】

30

そして、このように出力された信号はスキャン出力部 32' の第 1 列のスキャン制御信号端 (CSCAN) に提供されると同時に第 1 列の XNOR ゲート (XNOR1) の一側入力端に提供されるが、第 1 列の XNOR ゲート (XNOR1) の他側入力端が第 2 列のシフトレジスタ (SR2) の出力端に連結されているため第 1 列の XNOR ゲート (XNOR1) の出力端、即ち高インピーダンス制御信号端 (CHIZ) に論理 “0” の信号が出力される。そして、この時点で第 2 列以下のシフトレジスタ (SR2, ..., SRn) 及び XNOR ゲート (XNOR2, ..., XNORn) の出力端ではすべての論理 “1” の信号が出力されることになる。

## 【0043】

40

このようなスキャン制御信号 (CSCAN) と高インピーダンス制御信号 (CHIZ) の状態に応じてスキャン出力部 32' が表 1 の真理表のように動作して第 1 列の共通カソードライン (S1) を高インピーダンス状態 (HIZ)、即ちフロー・テイキング状態で接地端 (GND) に連結させる。そして、このような第 1 列に対する水平走査区間に水平同期信号 (H1) に同期して PWM 発生部 26 から発生される外部制御信号 (PWM) の制御に応じてデータ出力部 22' の PMOSFET (PMT4) がオンにされて夫々の共通アノードライン (D1, ..., Dm) をここに連結された OLED12 の画素階調に応じて決められた PWM 時間の間、定電流源 (CC) に連結されることによって OLED12 を発光させ、その後は PMOSFET (PMT4) がオフにされて共通アノードライン (D1, ..., Dm) が高インピーダンス状態 (HIZ) を維持する。

## 【0044】

50

一方、第1列の共通カソードライン( S<sub>1</sub> )が選択された間には第2列以下の共通カソードライン( S<sub>2</sub> 、... S<sub>n</sub> )は高インピーダンス状態( HIZ )を維持するが、これを真理表に示すと次の表2の通りである。また、表2、後述する表3及び表4でイタリック体で標記された部分は現在選択された列を示す。

【 0 0 4 5 】

【表2】

|       | SR出力<br>( C <sub>SCAN</sub> ) | XNOR入力1 | XNOR入力2 | XNOR出力<br>( C <sub>HIZ</sub> ) | S <sub>y</sub> |

|-------|-------------------------------|---------|---------|--------------------------------|----------------|

| 第1列   | 0                             | 0       | 1       | 0                              | GND            |

| 第2列以下 | 1                             | 1       | 1       | 1                              | HIZ            |

【 0 0 4 6 】

次に、前述した方式で第2列の共通カソードライン S<sub>2</sub> が高インピーダンス状態( HIZ )、即ちフロー ティング状態で接地端( GND )に連結されてここに連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> が発光することになるが、この期間の間、高インピーダンス制御信号( C<sub>HIZ</sub> )とスキャン制御信号( C<sub>SCAN</sub> )に応じてスキャン出力部 3<sub>2</sub>' が第1列の共通カソードライン S<sub>1</sub> を高電圧端( VH )に連結させることによってここに連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> の寄生キャパシタ C の極性を反転させることによって O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> の劣化を防止( refresh )する。この動作を真理表に示すと次の表3の通りである。

【 0 0 4 7 】

【表3】

|       | SR出力<br>( C <sub>SCAN</sub> ) | XNOR入力1 | XNOR入力2 | XNOR出力<br>( C <sub>HIZ</sub> ) | S <sub>y</sub> |

|-------|-------------------------------|---------|---------|--------------------------------|----------------|

| 第1列   | 1                             | 1       | 0       | 0                              | VH             |

| 第2列   | 0                             | 0       | 1       | 1                              | GND            |

| 第3列以下 | 1                             | 1       | 1       | 1                              | HIZ            |

【 0 0 4 8 】

次に、第3列の共通カソードライン S<sub>3</sub> が接地端( GND )連結されてそこに連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> が発光される間に第2列の共通カソードライン S<sub>2</sub> は高電圧端( VH )に連結されてそこに連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> の寄生キャパシタ( C )が放電され、この時点以後から最後の列の共通カソードライン( S<sub>n</sub> )に連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> が順次的に発光される間に第1列の共通カソードライン S<sub>1</sub> に連結された O<sub>L</sub>E<sub>D</sub>1<sub>2</sub> は外部制御信号( C<sub>HIZ</sub> )によって高インピーダンス状態( HIZ )を維持する。この動作を真理表に示すと次の表4の通りである。

【 0 0 4 9 】

10

20

30

40

【表4】

|       | SR出力<br>(C <sub>SCAN</sub> ) | XNOR入力1 | XNOR入力2 | XNOR出力<br>(C <sub>HIZ</sub> ) | S <sub>y</sub> |

|-------|------------------------------|---------|---------|-------------------------------|----------------|

| 第1列   | 1                            | 1       | 1       | 1                             | HIZ            |

| 第2列   | 1                            | 1       | 0       | 0                             | V <sub>H</sub> |

| 第3列   | 0                            | 0       | 1       | 0                             | GND            |

| 第4列以下 | 1                            | 1       | 1       | 1                             | HIZ            |

10

## 【0050】

このように、本発明のOLEDパネル駆動方法においては任意の共通カソードライン(Sy)を高インピーダンス状態(HIZ)から接地レベル(GND)へ順次にスキャンするが、次列の共通カソードライン(Sy+1)が選択(スキャン)される間にその列の共通カソードライン(Sy)を高電圧端(VH)に連結させてそこに連結されたOLED12の寄生キャパシタ(C)の極性を反転させ、その後次次列の共通カソードライン(Sy+2)が選択(スキャン)された時点以後からはその列の共通カソードライン(Sy)を高インピーダンス状態(HIZ)に維持させる。結果的に、本発明のOLEDパネル駆動方法によれば、OLED12のアノードとカソード間に寄生キャパシタ(C)が形成される区間は共通カソードライン(Sy)が高電圧端(VH)又は接地端(GND)に連結された状態であるだけで、高インピーダンス端(HIZ)に連結された状態においては寄生キャパシタンス成分は存在しない。

20

## 【0051】

従って、本発明のOLED駆動方法においては接地端(GND)に連結された1個の共通カソードラインに連結されたOLEDと高電圧端(VH)に連結された1個の共通カソードラインに連結されたOLEDにのみ寄生キャパシタンス成分が存在するため、従来のようにプリチャージを行わなくても所望の階調を表現することができ、またその消費電力も従来に比べて2/n倍に下げることができる。これを数式2で表すと次の通りである。

30

## 【数2】

$$P_d = 2 * m * C * V_H^2 * f_{clk}$$

## 【0052】

上記数式2において、CはOLED12に存在する寄生キャパシタを、mは共通アノードライン数を、VHはアノードに印加される高電圧を、f<sub>clk</sub>はスキャン駆動回路30'の動作周波数を夫々示す。例えば128×160の解像度を有するOLEDパネル駆動装置の場合にOLEDのカソードラインの数(n)が160であるため、消費電力を1/80倍に減らすことができる。

40

## 【0053】

本発明のOLEDパネル駆動装置及びその駆動方法は前述した実施例に局限されず、本発明の技術思想が許容する範囲内において、多様に変形して実施することができる。

## 【図面の簡単な説明】

## 【0054】

【図1】従来のプリチャージ方式のOLEDパネル駆動装置の概略ブロック構成図。

【図2】図1において1個の共通カソードラインに対するスキャン出力部を示した詳細回路図。

【図3】図1において1個の共通アノードラインに対するデータ出力部を示した詳細回路図。

【図4】従来のプリチャージ方式のOLEDパネル駆動装置で画面1フレームに対するス

50

キャン出力タイミングと各スキャン出力区間におけるプリチャージ区間及びデータ出力区間との関係を示したタイミングチャート。

【図5】本発明のOLEDパネル駆動装置の概略ブロック構成図。

【図6】図5において1個の共通カソードラインに対するスキャン出力部を示したブロック構成図。

【図7】図6の詳細回路図。

【図8】図5において1個の共通アノードラインに対するデータ出力部を示したブロック構成図。

【図9】本発明のOLEDパネル駆動装置の全体ブロック構成図。

【図10】図9においてスキャン駆動回路の一実施例による詳細回路図。 10

【図11】本発明のOLEDパネル駆動方法を説明するためのスキャン駆動回路とデータ駆動回路の動作タイミング図。

【符号の説明】

【0055】

10 : OLEDディスプレイパネル

12 : OLED

20、20' : データ駆動回路

22、22' : データ出力部

26 : PWM発生部

28 : シフトレジスタ / ラッチ部

30、30' : スキャン駆動回路

32、32' : スキャン出力部

36 : 制御ロジック部

38 : シフトレジスタ部

40 : OLED制御回路

D : ダイオード

C : 寄生キャパシタ

PMT1 - PMT4 : PMOSFET

NMT1、NMT2 : NMOSFET

LS1 LS3 : レベルシフタ

CC : 定電流源

VH : 高電圧端

VPRE : プリチャージ電圧端

S1、...、Sn : 共通カソードライン

D1、...、Dm : 共通アノードライン

Sy : 任意の共通カソードライン

Dx : 任意の共通アノードライン

SR1、...、SRn : シフトレジスタ

XNOR1、... XNORN : XNORゲート

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

| F I           | テーマコード(参考) |

|---------------|------------|

| G 0 9 G 3/20  | 6 2 2 C    |

| G 0 9 G 3/20  | 6 2 2 E    |

| G 0 9 G 3/20  | 6 2 2 G    |

| G 0 9 G 3/20  | 6 2 3 B    |

| G 0 9 G 3/20  | 6 2 3 G    |

| G 0 9 G 3/20  | 6 2 3 H    |

| G 0 9 G 3/20  | 6 4 1 A    |

| G 0 9 G 3/20  | 6 7 0 K    |

| H 0 5 B 33/14 | A          |

(72)発明者 クワック・ケダル

大韓民国 110-804ソウル、ジョンロク、グキドン 154-3番、ジョンドク・ビラ・ビー-

201

F ターム(参考) 3K007 AB03 AB11 BA06 DB03 GA00

5C080 AA06 BB05 DD08 DD26 DD29 EE29 FF12 HH09 JJ02 JJ03

JJ04

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 有机电致发光器件显示器驱动装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号     | <a href="#">JP2004184985A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2004-07-02 |

| 申请号         | JP2003346901                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2003-10-06 |

| 申请(专利权)人(译) | 哈纳美光公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人      | シンホンジエ<br>クワックケダル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人         | シン・ホンジエ<br>クワック・ケダル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号      | H01L51/50 G09G3/10 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号      | G09G3/3216 G09G3/3266 G09G2320/0252 G09G2330/021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号       | G09G3/30.J G09G3/20.611.A G09G3/20.621.F G09G3/20.621.L G09G3/20.622.B G09G3/20.622.C<br>G09G3/20.622.E G09G3/20.622.G G09G3/20.623.B G09G3/20.623.G G09G3/20.623.H G09G3/20.641.<br>A G09G3/20.670.K H05B33/14.A G09G3/3216 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号   | 3K007/AB03 3K007/AB11 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080<br>/DD08 5C080/DD26 5C080/DD29 5C080/EE29 5C080/FF12 5C080/HH09 5C080/JJ02 5C080/JJ03<br>5C080/JJ04 3K107/AA01 3K107/BB01 3K107/CC14 3K107/EE02 3K107/HH00 3K107/HH04 5C380<br>/AA01 5C380/AB05 5C380/AB34 5C380/BA01 5C380/BA40 5C380/BC20 5C380/BD08 5C380/BD09<br>5C380/CA08 5C380/CA14 5C380/CA16 5C380/CA17 5C380/CA26 5C380/CA39 5C380/CA54 5C380<br>/CB01 5C380/CB12 5C380/CB14 5C380/CB31 5C380/CE04 5C380/CE19 5C380/CF07 5C380/CF09<br>5C380/CF22 5C380/CF23 5C380/CF24 5C380/CF26 5C380/CF32 5C380/CF33 5C380/CF34 5C380<br>/CF51 5C380/DA01 5C380/DA07 |         |            |

| 代理人(译)      | 山崎 宏                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 优先权         | 1020020075470 2002-11-29 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

减少OLED面板驱动装置的功耗并提高运行速度。在手动矩阵型OLED显示面板驱动装置中，扫描驱动电路被配置为具有三态输出，并且当扫描驱动电路执行扫描操作时，选择的阴极线保持接地。应用了数据的OLED发光，并且在切换到高电压状态并执行刷新操作以初始化像素的电荷之后，执行维持高阻抗状态的操作，并且未选择的公共阴极线设置为高阻抗状态。通过降低寄生电容分量，用作连接到OLED的阳极线的数据驱动电路的负载的电容分量被降低，并且通过使用电压源，在短时间内阳极线的电压被升高到特定电压或更高。维持后，无需使用预充电方法即可发射OLED所需的电流。在只收取短时间内阳极线。[选择图]图5