(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-4797

(P2004-4797A)

(43) 公開日 平成16年1月8日(2004.1.8)

(51) Int.Cl.<sup>7</sup>

G09F 9/30

H05B 33/14

H05B 33/26

F 1

G09F 9/30

G09F 9/30

H05B 33/14

H05B 33/26

テーマコード(参考)

3K007

5C094

審査請求 未請求 請求項の数 6 O L (全 13 頁)

(21) 出願番号 特願2003-118085 (P2003-118085)

(22) 出願日 平成15年4月23日 (2003.4.23)

(31) 優先権主張番号 特願2002-122149 (P2002-122149)

(32) 優先日 平成14年4月24日 (2002.4.24)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(74) 代理人 100091605

弁理士 岡田 敏

(72) 発明者 松本 昭一郎

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 安齋 勝矢

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

F ターム(参考) 3K007 AB02 AB03 BA06 CC00 DB03

FA01 GA00

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】有機EL表示装置において、開口率を低下させることなく、信号線や電源線を増設する。

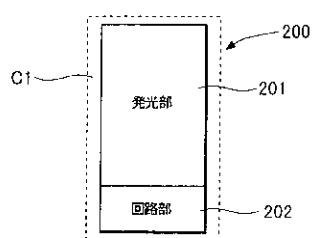

【解決手段】画素部200は、有機EL素子を含む発光部201、画素選択用 TFTや駆動用 TFTを含む回路部202から構成されている。そして、カソード層C1は、発光部201上に配置され、有機EL素子のカソードのみに用いられている。配線層C2はカソード層C1と同一の層(すなわち、同一の配線材料)から成り、カソード層C1から電気的に絶縁されるように分割されており、回路部202上に配置されている。カソード層C1と配線層C2の分割位置は、開口率低下に影響しないように回路部202の上部である。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

複数の画素部を有し、各画素部は、アノード層とカソード層との間に発光層を有するエレクトロルミネッセンス素子を含む発光部と、前記エレクトロルミネッセンス素子を駆動する駆動トランジスタを含む回路部とを備えた表示装置であって、

前記カソード層と同一の層で形成され、かつ前記カソード層から電気的に絶縁され、前記カソード層以外の配線に用いられる配線層を有することを特徴とする表示装置。

## 【請求項 2】

前記カソード層を前記発光部上に配置し、前記配線層を前記カソード層に隣接して配置したことを特徴とする請求項 1 記載の表示装置。

10

## 【請求項 3】

前記配線層を電源配線層または信号配線層に用いたことを特徴とする請求項 1 記載の表示装置。

## 【請求項 4】

前記配線層を前記エレクトロルミネッセンス素子に駆動電圧を供給する配線に用いたことを特徴とする請求項 1 記載の表示装置。

## 【請求項 5】

複数の画素部と、前記複数の画素部を駆動する周辺駆動回路部とを有し、各画素部は、アノード層とカソード層との間に発光層を有するエレクトロルミネッセンス素子を含む発光部と、前記エレクトロルミネッセンス素子を駆動する駆動トランジスタを含む回路部とを備えた表示装置であって、

20

前記カソード層と同一の層で形成され、かつ前記カソード層から電気的に絶縁され、前記周辺駆動回路部の配線に用いられる配線層を有することを特徴とする表示装置。

## 【請求項 6】

前記配線層を前記周辺駆動回路部の電源配線層または信号配線層に用いたことを特徴とする請求項 5 記載の表示装置。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は表示装置に関し、特にエレクトロルミネッセンス表示装置に関する。

30

## 【0002】

## 【従来の技術】

近年、エレクトロルミネッセンス (Electro Luminescence: 以下、「EL」と称する。) 素子を用いた EL 表示装置が、CRT や LCD に代わる表示装置として注目されており、例えば、その EL 素子を駆動させるスイッチング素子として薄膜トランジスタ (Thin Film Transistor: 以下、「TFT」と称する。) を備えた EL 表示装置の研究開発も進められている。

## 【0003】

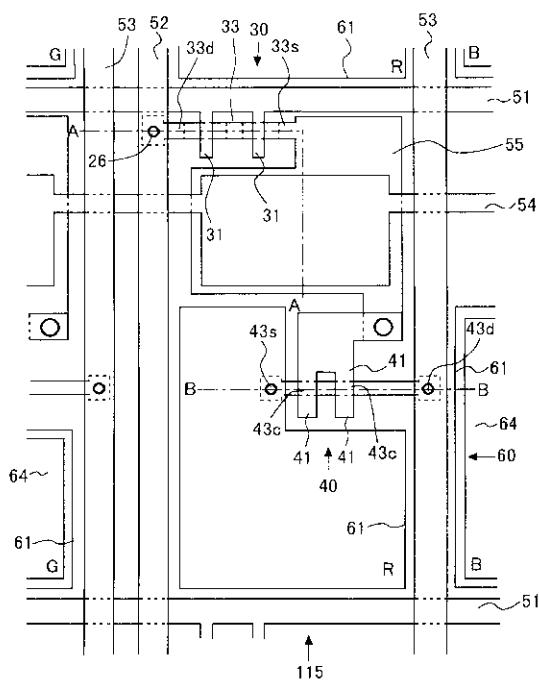

図 9 に有機 EL 表示装置の画素部を示す平面図を示し、図 10 (a) に図 9 中の A - A 線に沿った断面図を示し、図 10 (b) に図 9 中の B - B 線に沿った断面図を示す。

40

## 【0004】

図 9 及び図 10 に示すように、ゲート信号線 51 とドレイン信号線 52 とに囲まれた領域に画素部 115 が形成されており、マトリクス状に配置されている。

## 【0005】

この画素部 115 には、自発光素子である有機 EL 素子 60 と、この有機 EL 素子 60 に電流を供給するタイミングを制御するスイッチング用 TFT 30 と、有機 EL 素子 60 に電流を供給する駆動用 TFT 40 と、保持容量とが配置されている。なお、有機 EL 素子 60 は、アノード (陽極) 層 61 と発光材料からなる発光素子層と、カソード (陰極) 層 65 とから成っている。

## 【0006】

50

即ち、両信号線 5 1 , 5 2 の交点付近には、スイッチング用 TFT である第 1 の TFT 3 0 が備えられており、その TFT 3 0 のソース 3 3 s は保持容量電極線 5 4 との間で容量をなす容量電極 5 5 を兼ねるとともに、EL 素子駆動用 TFT である第 2 の TFT 4 0 のゲート 4 1 に接続されており、第 2 の TFT のソース 4 3 s は有機 EL 素子 6 0 のアノード層 6 1 に接続され、他方のドレイン 4 3 d は有機 EL 素子 6 0 に供給される電流源である駆動電源線 5 3 に接続されている。

【 0 0 0 7 】

また、ゲート信号線 5 1 と並行に保持容量電極線 5 4 が配置されている。この保持容量電極線 5 4 はクロム等から成っており、ゲート絶縁膜 1 2 を介して TFT のソース 3 3 s と接続された容量電極 5 5 との間で電荷を蓄積して容量を成している。この保持容量 5 6 は、第 2 の TFT 4 0 のゲート電極 4 1 に印加される電圧を保持するために設けられている。

【 0 0 0 8 】

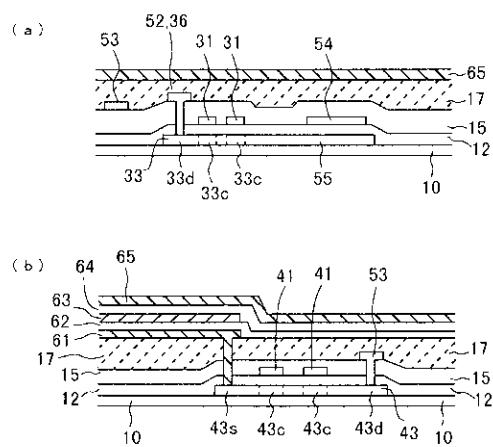

図 1 0 に示すように、有機 EL 表示装置は、ガラスや合成樹脂などから成る基板又は導電性を有する基板あるいは半導体基板等の基板 1 0 上に、TFT 及び有機 EL 素子を順に積層形成して成る。ただし、基板 1 0 として導電性を有する基板及び半導体基板を用いる場合には、これらの基板 1 0 上に SiO<sub>2</sub> や SiN などの絶縁膜を形成した上に第 1 、第 2 の TFT 及び有機 EL 素子を形成する。いずれの TFT ともに、ゲート電極がゲート絶縁膜を介して能動層の上方にあるいはわゆるトップゲート構造である。

【 0 0 0 9 】

まず、スイッチング用 TFT である第 1 の TFT 3 0 について説明する。

【 0 0 1 0 】

図 1 0 ( a ) に示すように、石英ガラス、無アルカリガラス等からなる絶縁性基板 1 0 上に、非晶質シリコン膜 ( 以下、「a - Si 膜」と称する。 ) を CVD 法等にて成膜し、その a - Si 膜にレーザ光を照射して溶融再結晶化させて多結晶シリコン膜 ( 以下、「p - Si 膜」と称する。 ) とし、これを能動層 3 3 とする。その上に、SiO<sub>2</sub> 膜、SiN 膜の単層あるいは積層体をゲート絶縁膜 1 2 として形成する。更にその上に、Cr、Mo などの高融点金属からなるゲート電極 3 1 を兼ねたゲート信号線 5 1 及び A 1 から成るドレイン信号線 5 2 を備えており、有機 EL 素子の駆動電源であり A 1 から成る駆動電源線 5 3 が配置されている。

【 0 0 1 1 】

そして、ゲート絶縁膜 1 2 及び能動層 3 3 上の全面には、SiO<sub>2</sub> 膜、SiN 膜及び SiO<sub>2</sub> 膜の順に積層された層間絶縁膜 1 5 が形成されており、ドレイン 3 3 d に対応して設けたコンタクトホールに A 1 等の金属を充填したドレイン電極 3 6 が設けられ、更に全面に有機樹脂から成り表面を平坦にする平坦化絶縁膜 1 7 が形成されている。

【 0 0 1 2 】

次に、有機 EL 素子の駆動用 TFT である第 2 の TFT 4 0 について説明する。図 1 0 ( b ) に示すように、石英ガラス、無アルカリガラス等からなる絶縁性基板 1 0 上に、a - Si 膜にレーザ光を照射して多結晶化してなる能動層 4 3 、ゲート絶縁膜 1 2 、及び Cr 、 Mo などの高融点金属からなるゲート電極 4 1 が順に形成されており、その能動層 4 3 には、チャネル 4 3 c と、このチャネル 4 3 c の両側にソース 4 3 s 及びドレイン 4 3 d が設けられている。そして、ゲート絶縁膜 1 2 及び能動層 4 3 上の全面に、SiO<sub>2</sub> 膜、SiN 膜及び SiO<sub>2</sub> 膜の順に積層された層間絶縁膜 1 5 を形成し、ドレイン 4 3 d に対応して設けたコンタクトホールに A 1 等の金属を充填して駆動電源に接続された駆動電源線 5 3 が配置されている。更に全面に例えれば有機樹脂から成り表面を平坦にする平坦化絶縁膜 1 7 を備えている。そして、その平坦化絶縁膜 1 7 のソース 4 3 s に対応した位置にコンタクトホールを形成し、このコンタクトホールを介してソース 4 3 s とコンタクトしたITO から成る透明電極、即ち有機 EL 素子のアノード層 6 1 を平坦化絶縁膜 1 7 上に設けている。このアノード層 6 1 は各画素部ごとに島状に分離形成されている。

【 0 0 1 3 】

10

20

30

40

50

有機 E L 素子 6 0 は、一般的な構造であり、 I T O ( I n d i u m T i n O x i d e ) 等

の透明電極から成るアノード層 6 1 、 M T D A T A

( 4 , 4 - b i s ( 3 - m e t h y l p h e n y l p h e n y l a m i n o ) b i p h e n y l ) から成る第 1 ホール輸送層、 T P D ( 4 , 4 , 4 - t r i s ( 3 - m e t h y l p h e n y l p h e n y l a m i n o ) t r i p h e n y l a n i n e ) からなる第 2 ホール輸送層から成るホール輸送層 6 2 、キナクリドン ( Q u i n a c r i d o n e ) 誘導体を含む B e b q 2 ( 1 0 - ベンゾ [ h ] キノリノール - ベリリウム錯体 ) から成る発光層 6 3 、及び B e b q 2 から成る電子輸送層 6 4 、マグネシウム・インジウム合金もしくはアルミニウム、もしくはアルミニウム合金から成るカソード層 6 5 が、この順番で積層形成された構造である。

【 0 0 1 4 】

有機 E L 素子 6 0 は、アノード層 6 1 から注入されたホールと、カソード層 6 5 から注入された電子とが発光層の内部で再結合し、発光層を形成する有機分子を励起して励起子が生じる。この励起子が放射失活する過程で発光層から光が放たれ、この光が透明なアノード層 6 1 から透明絶縁基板を介して外部へ放出されて発光する。なお、上述した技術は、例えは特開平 1 1 - 2 8 3 1 8 2 号公報に記載されている。

【 0 0 1 5 】

上述した有機 E L 表示装置においては、カソード層 6 5 は画素部 1 1 5 の全体を覆うように配置されていた。図 1 1 は、有機 E L 素子装置のレイアウトを示す図である。画素部 2 0 0 は、有機 E L 素子を含む発光部 2 0 1 、 T F T を含む回路部 2 0 2 から構成されている。そして、有機 E L 素子のカソード層 C 1 は、画素部 2 0 0 の全体に配置されている。

【 0 0 1 6 】

【 発明が解決しようとする課題 】

上述したように従来の有機 E L 表示装置では、カソード層に用いられていたアルミニウム等の配線材料は、カソード層としてのみ用いられており、他の配線には使用されていなかった。

【 0 0 1 7 】

このため、画素部に新しく信号線や電源線を配線しようとすると、開口率が低下し、有機 E L 表示装置の輝度の低下を招いていた。また、周辺駆動回路部において新たな信号線や電源線を配線しようとすると、占有面積が増加するという問題があった。

【 0 0 1 8 】

【 課題を解決するための手段 】

そこで、本発明は、カソード層をパターン的に分割して他の配線層に用いることにより、有機 E L 表示装置の輝度低下や周辺駆動回路部の占有面積の低下を招くことなく、信号線や電源線を増設することを可能とするものである。

【 0 0 1 9 】

すなわち、本発明の特徴構成は、複数の画素部を有し、各画素部は、アノード層とのカソード層との間に発光層を有するエレクトロルミネッセンス素子を含む発光部と、前記エレクトロルミネッセンス素子を駆動する駆動トランジスタを含む回路部とを備えた表示装置であって、前記カソード層と同一の層で形成され、かつ前記カソード層から電気的に絶縁され、前記カソード層以外の配線に用いられる配線層を有するものである。

【 0 0 2 0 】

また、本発明の他の特徴構成は、複数の画素部と前記複数の画素部を駆動する周辺駆動回路部とを有し、各画素部は、アノード層とカソード層との間に発光層を有するエレクトロルミネッセンス素子を含む発光部と、前記エレクトロルミネッセンス素子を駆動する駆動トランジスタを含む回路部とを備えた表示装置において、前記カソード層と同一の層で形成され、かつ前記カソード層から電気的に絶縁され、前記周辺駆動回路部の配線に用いられる配線層を有するものである。

【 0 0 2 1 】

10

20

30

40

50

### 【発明の実施の形態】

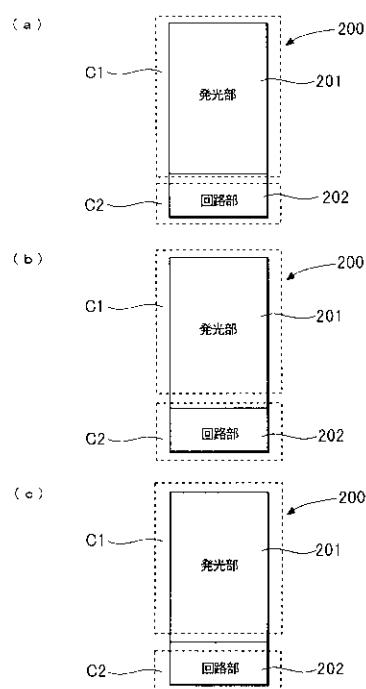

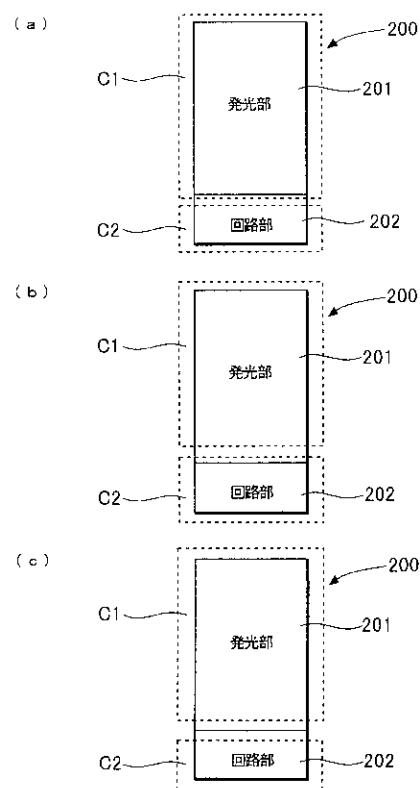

図1は本発明の実施形態に係る有機EL表示装置のレイアウト例を示す概略図である。図1(a)に示すように、画素部200は、有機EL素子を含む発光部201、画素選択用TFTや駆動用TFTを含む回路部202から構成されている。実際の有機EL表示装置では、このような画素部200がマトリクス状に複数個配置されて構成されている。

### 【0022】

そして、カソード層C1は、発光部201上に配置され、有機EL素子のカソード層のみに用いられている。配線層C2はカソード層C1と同一の層(すなわち、同一の配線材料)から成り、カソード層C1から電気的に絶縁されるように分割され、回路部202上に隣接して配置されている。カソード層C1と配線層C2の分割位置は、開口率低下に影響しないようにするために、回路部202の上部とすることが好ましい。

### 【0023】

しかし、カソード層C1と配線層C2との配置関係は、図1(a)の構成に限定されない。例えば、図1(b)に示すように、カソード層C1と配線層C2の分割位置は発光部201上でもあっても良い。また、図1(c)に示すように、カソード層C1と配線層C2の分割位置は、発光部201と回路部202との境界でもあっても良い。すなわち、カソード層C1は、必ずしも、そのすべての部分が発光部201上にあることは必要ではない。同様に、配線層C2は、そのすべての部分が回路部202上にある必要はない。

### 【0024】

配線層C2は、カソード層C1とは別の用途、例えば電源配線層や信号配線層として用いられる。

### 【0025】

次に、有機EL素子装置の具体的なレイアウトについて、図面を参照しながら詳細に説明する。

### 【0026】

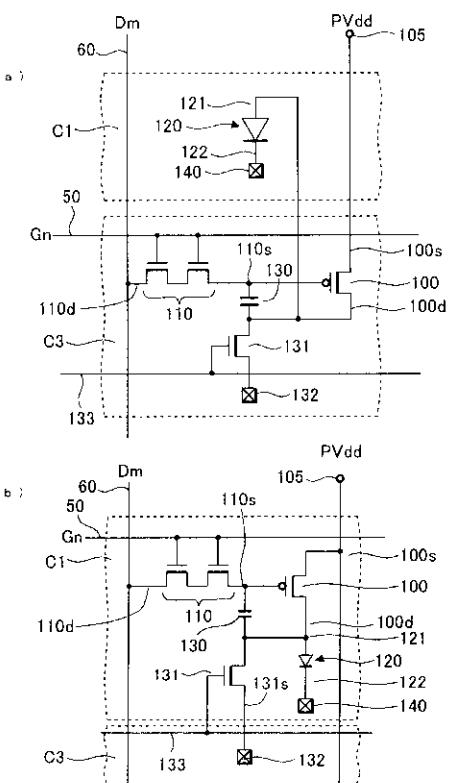

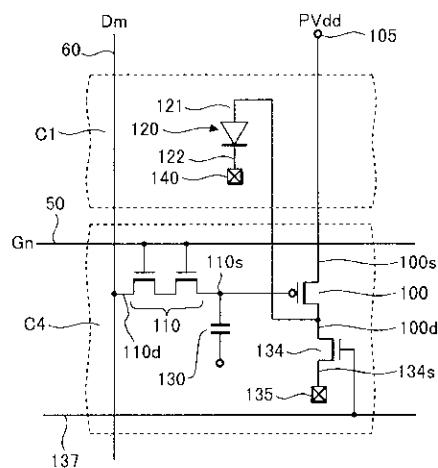

図2の(a)、(b)はそれぞれ有機EL表示装置の一画素部のレイアウト回路図である。この例では、カソード層C1から分割された配線層は、有機EL素子120に逆バイアスを印加するための電源配線層C3として用いられている。

### 【0027】

図2(a)、(b)において、画素選択用TFT110、有機EL素子駆動用TFT100、及び有機EL素子120を含む、第n行のゲート信号線50と第m列のドレイン信号線60の交差点付近に形成された画素部を示している。実際には係る画素部が複数個マトリクス状に配置されている。

### 【0028】

ゲート信号Gnを供給するゲート信号線50と、ドレイン信号、すなわち、ビデオ信号Dmを供給するドレイン信号線60とが互いに交差している。それらの両信号線の交差点付近には、有機EL素子120及びこの有機EL素子120を駆動する有機EL素子駆動用TFT100、この画素部を選択するための画素選択用TFT110が配置されている。TFT100はPチャネル型、TFT110はNチャネル型である。

### 【0029】

有機EL素子駆動用のTFT100のソース100sには駆動電源105が接続され、この駆動電源105から正の駆動電圧PVddが供給されている。また、そのドレイン100dは、有機EL素子120のアノード121に接続されている。

### 【0030】

また、画素選択用のTFT110のゲートにはゲート信号線50が接続されることにより、画素選択用のTFT110を介して画素に、ゲート信号Gnが供給され、ドレイン110dにはドレイン信号線60が接続されることにより、ビデオ信号Dmが供給される。TFT110のソース110sは、TFT100のゲートに接続されている。ここで、ゲート信号Gnは不図示のゲートドライバ回路から出力される。ビデオ信号Dmは不図示のドレインドライバ回路から出力される。

## 【0031】

また、有機EL素子120は、アノード121、カソード122、このアノード121とカソード122の間に形成された、不図示の発光素子層から成る。カソード122は、カソード層C1と一体化され、不図示の負電源に接続されている。

## 【0032】

また、TFT100のゲートには保持容量130が接続されている。すなわち保持容量130の一方の電極はゲートに接続され、他方の電極は、TFT131に接続されている。保持容量130はビデオ信号Dmに応じた電荷を保持することにより、1フィールド期間、画素部のビデオ信号Dmを保持するために設けられている。

## 【0033】

TFT131は、有機EL素子120に逆バイアスを印加して、その輝度特性を復帰させるためのTFTであり、有機EL素子120のアノード121と負電源配線層C3との間に接続されている。TFT131のソース131sは、コンタクト132を介して、負電源配線層C3に接続されている。TFT131のゲートは、スイッチング制御用の信号線133に接続されている。負電源配線層C3は、カソード層C1に隣接し、かつカソード層C1とは電気的に絶縁されている。

## 【0034】

なお、図2(a)において、カソード層C1は有機EL素子120上に形成され、負電源配線層C3は、画素の回路部分を構成する素子、TFT100、TFT110、TFT131、保持容量130上に配置されている。一方、図2(b)においては、カソード層C1は有機EL素子120、画素の回路部分を構成する素子、TFT100、TFT110、TFT131、保持容量130上に配置され、負電源配線層C3はそのカソード層C1に隣接して配置され、その下に回路部分を構成するTFT等の素子は形成されていない。

## 【0035】

上述した構成の有機EL表示装置の動作を説明すると以下の通りである。ゲート信号Gnが一水平期間、ハイレベルになると、TFT110がオンする。すると、ドレイン信号線60からビデオ信号DmがTFT110を通して、TFT100のゲートに印加される。ゲートに供給されたビデオ信号Dmに応じて、TFT100のコンダクタンスが変化し、それに応じた駆動電流が駆動電源105、TFT100、有機EL素子120、カソード層C1という経路で流れる。これにより、有機EL素子120が発光する。

## 【0036】

また、有機EL素子120の輝度は経時変化により劣化するが、逆バイアス用のTFT131をオンさせることにより、負電源配線層C3から有機EL素子120に逆バイアスを印加することにより、輝度特性を復帰させている。有機EL素子120に逆バイアスを印加するために、負電源配線層C3の電位はカソード層C1よりも低電位である。有機EL素子120は一種のダイオードであり、カソード122の電位をアノード121より低い電位にすることで逆バイアス状態となる。

## 【0037】

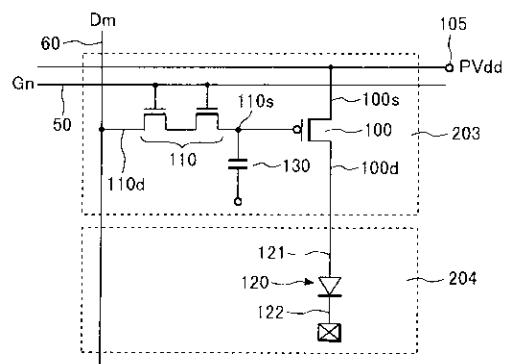

図3は、有機EL表示装置の一画素部の他のレイアウト回路図である。この例では、カソード層C1から分割された配線層は、放電用の電源配線層C4として用いられている。図において、有機EL素子120のアノード121と放電用の電源配線層C4との間には放電用のTFT134が設けられている。

## 【0038】

TFT134のソース134sは、コンタクト135を介して放電用の電源配線層C4に接続される。TFT134ゲートにはスイッチング制御用の信号線137に接続されている。放電用の電源配線層C4は、カソード層C1に隣接し、かつカソード層C1とは電気的に絶縁されている。他の構成は、図2に示した有機EL表示装置の構成と同様である。

## 【0039】

有機EL素子120にアノード121に電荷が残留していると、有機EL表示装置の残像となって現れてしまう。そこで、その電荷を放電させるために、放電用のTFT134、

10

20

30

40

50

電源配線層 C 4 を設けている。電源配線層 C 4 の電位は、カソード層 C 1 の電位と同電位でも異電位でもよい。

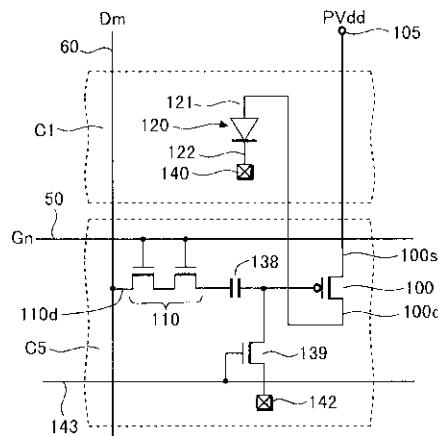

【 0 0 4 0 】

図 4 は、有機 E L 表示装置の一画素部の他のレイアウト回路図である。この例では、カソード層 C 1 から分割された配線層は、リセット用の電源配線層 C 5 として用いられている。図 4 において、画素選択用の T F T 1 1 0 と有機 E L 素子駆動用の T F T 1 0 0 の間に、カップリング容量 1 3 8 が設けられ、このカップリング容量 1 3 8 を介してビデオ信号 D m を有機 E L 素子駆動用の T F T 1 0 0 のゲートに供給している。

【 0 0 4 1 】

そして、有機 E L 素子駆動用の T F T 1 0 0 のゲートとリセット用の電源配線層 C 5 との間にリセット用の T F T 1 3 9 が接続されている。T F T 1 3 9 のソース 1 3 9 s はコンタクト 1 4 2 を介して、リセット用の電源配線層 C 5 に接続される。

【 0 0 4 2 】

リセット用 T F T 1 3 9 のゲートにはスイッチング制御用の信号線 1 4 3 が接続されている。リセット用の電源配線層 C 5 は、カソード層 C 1 に隣接し、かつカソード層 C 1 とは電気的に絶縁されている。

【 0 0 4 3 】

リセット用の T F T 1 3 9 、電源配線層 C 5 を設けている理由は以下の通りである。有機 E L 駆動用 T F T 1 0 0 のしきい値 V t 及び有機 E L 素子 1 2 0 のしきい値 V F t には製造上のばらつきがあるため、同じビデオ信号 D m を印加しても、有機 E L 駆動用 T F T 1 0 0 に流れる電流にはばらつきが生じてしまう。

【 0 0 4 4 】

そこで、ビデオ信号 D m を印加する前のタイミングで、有機 E L 駆動用 T F T 1 2 0 のゲート電位を、( V t + V F t ) にリセットすることにより、同一のビデオ信号 D m に対して常に同じ電流が流れるようしている。( V t + V F t ) の値は、あらかじめ、モニタリングすることにより知られているものとする。したがって、電源配線層 C 5 の電位は V t + V F t に設定される。

【 0 0 4 5 】

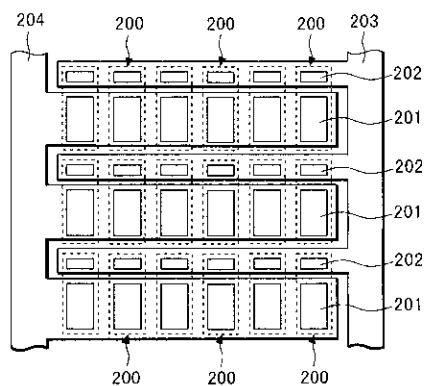

図 5 は、有機 E L 表示装置の複数の画素部を示す他のレイアウト図である。また、図 6 は、図 5 における各画素部 2 0 0 の等価回路図である。なお、図 5 、図 6 において、図 1 、図 2 と同一の構成部分については同一符号を付している。

【 0 0 4 6 】

この例では、有機 E L 素子 1 2 0 のカソード層 2 0 4 から分割された配線層は、有機 E L 素子 1 2 0 に正の駆動電圧 P V d d を供給する P V d d 線 2 0 3 として用いられている。すなわち、 P V d d 線 2 0 3 は、カソード層 2 0 4 の材料（例えばアルミニウム）を兼用して配線されている。

【 0 0 4 7 】

図 5 に示すように、画素部 2 0 0 はマトリクス状に配置されて、表示領域を構成している。そして、カソード層 2 0 4 は列方向に配置された複数の画素部 2 0 0 の発光部 2 0 1 上に延在しており、図において左端部で連結され、全体としては、くし型形状を呈している。なお、発光部 2 0 1 は、有機 E L 素子 1 2 0 の形成されている部分である。

【 0 0 4 8 】

また、 P V d d 線 2 0 3 は、列方向に配置された複数の画素部 2 0 0 の回路部 2 0 2 上に延在しており、図において右端部で連結され、全体としては同様に、くし型形状を呈している。なお、回路部 2 0 2 は有機 E L 駆動用 T F T 1 0 0 、画素選択用 T F T 1 1 0 、保持容量 1 3 0 の形成されている部分である。そして上記のくし型形状のカソード層 2 0 4 と P V d d 線 2 0 3 とは、上記表示領域上で互いに噛み合うように隣接して配置されている。

【 0 0 4 9 】

かかる構成によれば、画素部 2 0 0 の開口率を低下させることなく、有機 E L 素子 1 2 0

10

20

30

40

50

に電源を供給するための P V d d 線 2 0 3 を高密度に配線することが可能である。

【 0 0 5 0 】

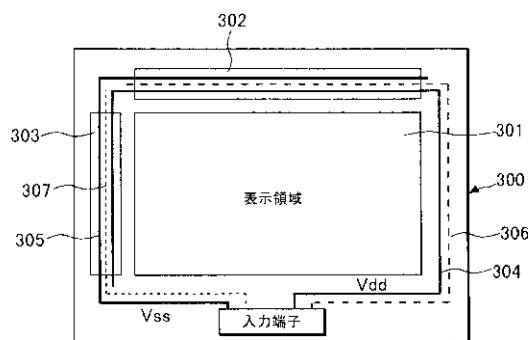

また、図 7 に示すように、有機 E L 表示装置 3 0 0 において、複数の画素部から成る表示領域 3 0 1 の周辺には、各画素部にデータ信号 D m を供給するドレインドライバ回路 3 0 2 や、各画素部にゲート信号 G n を供給するゲートドライバ回路 3 0 3 が配置されている。これらの周辺駆動回路部の信号線や電源線についても、図 1 のカソード層 C 1 と同一の層で形成することができる。例えば、ドレインドライバ回路 3 0 2 及びゲートドライバ回路 3 0 3 に電源を供給するための電源線 3 0 4 、 3 0 5 に適用できる。また、ドレインドライバ回路 3 0 2 にドレイン駆動信号を供給するためのドレイン駆動信号線 3 0 6 、ゲートドライバ回路 3 0 3 にゲート駆動信号を供給するためのゲート駆動信号線 3 0 7 等に適用できる。

【 0 0 5 1 】

これにより、図 7 に示すように、ドレインドライバ回路 3 0 2 やゲートドライバ回路 3 0 3 上に重畠させてこれらの配線を設けることができる、周辺駆動回路部の占有面積を増加させることなく、信号線や電源線を増設することが可能になる。

【 0 0 5 2 】

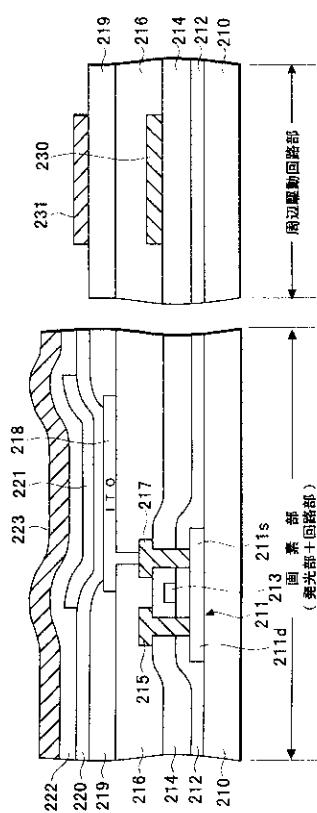

図 8 は、画素部と周辺駆動回路部の部分断面図である。画素部においては、有機 E L 素子及び駆動用 T F T を示し、周辺駆動回路部においては配線を示している。画素部において、石英ガラス、無アルカリガラス等から成る石英ガラス、無アルカリガラス等からなる絶縁性基板 2 1 0 上に、 a - S i 膜にレーザ光を照射して多結晶化してなる能動層 2 1 1 、ゲート絶縁膜 2 1 2 、及び C r 、 M o などの高融点金属からなるゲート電極 2 1 3 が順に形成されており、その能動層 2 1 1 には、チャネルと、このチャネルの両側にソース 2 1 1 s 及びドレイン 2 1 1 d が設けられている。

【 0 0 5 3 】

そして、ゲート絶縁膜 2 1 2 及び能動層 2 1 1 上の全面に、 S i O <sub>2</sub> 膜、 S i N 、膜及び S i O <sub>2</sub> 膜の順に積層された層間絶縁膜 2 1 4 が形成されている。また、ドレイン 2 1 1 d に対応して設けたコンタクトホールに A 1 等の金属を充填して駆動電源 P V d d に接続された駆動用の電源線 2 1 5 (ドレイン電極) が配置されている。更に全面に例えれば有機樹脂から成り表面を平坦にする第 1 平坦化絶縁膜 2 1 6 を備えている。そして、その第 1 平坦化絶縁膜 2 1 6 のソース 2 1 1 s に対応した位置にコンタクトホールを形成し、このコンタクトホールを介してソース電極 2 1 7 とコンタクトした I T O から成る透明電極、即ち有機 E L 素子のアノード層 2 1 8 を第 1 平坦化絶縁膜 2 1 6 上に設けている。このアノード層 2 1 8 は各画素部ごとに島状に分離形成されている。

【 0 0 5 4 】

さらに第 2 平坦化絶縁膜 2 1 9 が形成され、アノード層 2 1 8 上については、第 2 平坦化絶縁膜 2 1 9 が除去されている。有機 E L 素子はアノード層 2 1 8 、ホール輸送層 2 2 0 、発光層 2 2 1 、電子輸送層 2 2 2 、カソード層 2 2 3 が、この順番で積層形成されている。

【 0 0 5 5 】

一方、周辺駆動回路部において、層間絶縁膜 2 1 4 上に第 1 配線層 2 3 0 が形成されている。この第 1 配線層 2 3 0 は、画素部の電源線 2 1 5 、ソース電極 2 1 7 と同一層である。第 1 配線層 2 3 0 の下層には、層間絶縁膜 2 1 4 、ゲート絶縁膜 2 1 2 が存在しているが、これらの膜は配線領域には必要ではなく、これらの膜は除去されてもよい。

【 0 0 5 6 】

また、第 2 平坦化膜 2 1 9 上に第 2 配線層 2 3 1 が形成されている。この第 2 配線層 2 3 1 は、画素部のカソード層 2 2 3 と同一層である。第 2 配線層 2 3 1 は、上述したように、ドレインドライバ回路 3 0 2 及びゲートドライバ回路 3 0 3 に電源を供給するための電源線 3 0 4 、 3 0 5 や、ドレインドライバ回路 3 0 2 にドレイン駆動信号を供給するためのドレイン駆動信号線 3 0 6 、ゲートドライバ回路 3 0 3 にゲート駆動信号を供給するためのゲート駆動信号線 3 0 7 等に利用することができる。

10

20

30

40

50

## 【0057】

第2配線層231は、その下層に第1平坦化絶縁膜216及び第2平坦化絶縁膜219があるので、その寄生容量は、下層の第1配線層230の有する寄生容量に比して小さい。そのため、高速化や低消費電力化を図ることことができる。

## 【0058】

## 【発明の効果】

本発明の表示装置によれば、画素部のカソード層を分割して配線材料として、信号線や電源線に用いることにより、開口率を低下させることなく、信号線や電源線を増設すること可能になる。

## 【0059】

また、周辺駆動回路部についても、カソード層を分割して配線材料として、信号線や電源線に用いることにより、その占有面積を増やすことなく、信号線や電源線を増設することが可能になる。また、そのような信号線や電源線における寄生容量を小さくすることができる、高速化や低消費電力化を図ることが可能になる。

## 【図面の簡単な説明】

【図1】本発明の実施形態に係る有機EL素子装置の一画素部のレイアウトを示す概略図である。

【図2】本発明の実施形態に係る有機EL表示装置の一画素部のレイアウト回路図である。

【図3】本発明の実施形態に係る有機EL表示装置の一画素部の他のレイアウト回路図である。 20

【図4】本発明の実施形態に係る有機EL表示装置の一画素部の他のレイアウト回路図である。

【図5】本発明の実施形態に係る有機EL表示装置の他のレイアウト図である。

【図6】本発明の実施形態に係る有機EL表示装置の画素部に等価回路図である。

【図7】本発明の実施形態に係る有機EL表示装置の全体レイアウト図である。

【図8】本発明の実施形態に係る有機EL表示装置の画素部と周辺駆動回路部の部分断面図である。

【図9】有機EL表示装置の画素部を示す平面図である。

【図10】有機EL表示装置の画素部を示す断面図である。 30

【図11】従来の有機EL素子装置の一画素部のレイアウトを示す図である。

## 【符号の説明】

|     |               |     |           |     |              |

|-----|---------------|-----|-----------|-----|--------------|

| 50  | ゲート信号線        | 60  | ドレイン信号線   | 105 | 駆動電源         |

| 100 | 有機EL素子駆動用 TFT | 110 | 画素選択用 TFT |     |              |

| 120 | 有機EL素子        | 130 | 保持容量      |     |              |

| 131 | 逆バイアス用 TFT    | 134 | 放電用の TFT  |     |              |

| 139 | リセット用の TFT    | 200 | 画素部       |     |              |

| 201 | 発光部           | 202 | 回路部       |     |              |

| C1  | カソード層         | C2  | 配線層       | C3  | 逆バイアス用の電源配線層 |

| C4  | 放電用の電源配線層     |     |           | C5  | リセット用の電源配線層  |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【圖 7】

【 四 9 】

【図10】

【図11】

---

フロントページの続き

F ターム(参考) 5C094 AA10 BA03 BA27 CA19 DA09 DA13 DB01 EA04 EA07 FB01

FB12 FB16

|                |                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2004004797A</a>                                                                                                                                                                                                                                                        | 公开(公告)日 | 2004-01-08 |

| 申请号            | JP2003118085                                                                                                                                                                                                                                                                         | 申请日     | 2003-04-23 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 松本昭一郎<br>安齋勝矢                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 松本昭一郎<br>安齋勝矢                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/00 G09G3/30 G09G3/32 H01J1/54 H01L27/32 H05B33/00 H05B33/14 H05B33/26                                                                                                                                                                                       |         |            |

| CPC分类号         | H01L27/3276 G09G3/3233 G09G2300/0417 G09G2300/0426 G09G2300/0465 G09G2300/0814 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2310/0256 G09G2320/043 H01L27/3297                                                                                                                      |         |            |

| FI分类号          | G09F9/30.330.Z G09F9/30.365.Z H05B33/14.A H05B33/26.Z G09F9/30.330 G09F9/30.365 H01L27/32                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB03 3K007/BA06 3K007/CC00 3K007/DB03 3K007/FA01 3K007/GA00 5C094 /AA10 5C094/BA03 5C094/BA27 5C094/CA19 5C094/DA09 5C094/DA13 5C094/DB01 5C094/EA04 5C094/EA07 5C094/FB01 5C094/FB12 5C094/FB16 3K107/AA01 3K107/BB01 3K107/CC02 3K107 /CC36 3K107/DD39 3K107/EE03 |         |            |

| 代理人(译)         | 须藤克彦<br>冈田敬                                                                                                                                                                                                                                                                          |         |            |

| 优先权            | 2002122149 2002-04-24 JP                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

要解决的问题：在不降低有机EL（电致发光）显示装置中的开口率的情况下扩展信号线或电源线。解决方案：像素部分200由包含有机EL元件的发光部分201和包含用于像素选择的TFT（薄膜晶体管）和用于驱动的TFT的电路部分202组成。阴极层C1放置在发光部分201上，并且仅用于有机EL元件的阴极。布线层C2由与阴极层C1相同的层（即，相同的布线材料）构成，并且从用于电绝缘的阴极层C1分开，并且布置在电路部分202上。阴极层的分割位置C1和布线层C2位于电路部分202的上部，以不降低开口率。 ž