(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4890917号

(P4890917)

(45) 発行日 平成24年3月7日(2012.3.7)

(24) 登録日 平成23年12月22日(2011.12.22)

(51) Int.Cl.

F 1

G09G 3/30 (2006.01)

G09G 3/30

J

G09G 3/20 (2006.01)

G09G 3/20

611H

G09G 3/20

642A

G09G 3/20

623G

G09G 3/20

623F

請求項の数 25 (全 28 頁) 最終頁に続く

(21) 出願番号

特願2006-105041 (P2006-105041)

(22) 出願日

平成18年4月6日(2006.4.6)

(65) 公開番号

特開2007-41523 (P2007-41523A)

(43) 公開日

平成19年2月15日(2007.2.15)

審査請求日

平成18年4月6日(2006.4.6)

(31) 優先権主張番号

10-2005-0070439

(32) 優先日

平成17年8月1日(2005.8.1)

(33) 優先権主張国

韓国(KR)

前置審査

(73) 特許権者 308040351

三星モバイルディスプレイ株式會社

Samsung Mobile Display Co., Ltd.

大韓民国京畿道龍仁市器興区農書洞山24

San #24 Nongseo-Dong,

Giheung-Gu, Yongin-

City, Gyeonggi-Do 4

46-711 Republic of

KOREA

(73) 特許権者 506118135

漢陽大学校産学協力団

大韓民国ソウル特別市城東区杏堂洞17

(74) 代理人 110000671

八田國際特許業務法人

最終頁に続く

(54) 【発明の名称】データ駆動回路とこれを用いた有機発光表示装置

(57) 【特許請求の範囲】

【請求項 1】

外部から供給される k (k は自然数) ビットの第 1 データを二進数の加重値を持つよう

に変更して p (p は自然数) ビットの第 2 データを生成する少なくとも一つのデコーダと、

前記第 1 データ及び第 2 データを保存するラッチ部と、

複数の階調電圧を生成するガンマ電圧部と、

前記第 1 データを利用して前記階調電圧の中からいずれか一つの電圧を選択してデータ

信号として出力する少なくとも一つのデジタル - アナログ変換器と、

水平期間の第 1 期間の間画素から所定の電流の供給を受けて補償電圧を出力する少なく

とも一つの電流シンク器と、

前記第 2 データに応じて前記電流シンク器からの前記補償電圧を利用して前記データ信

号の電圧値を増減する少なくとも一つの電圧制御器と、

前記水平期間中前記第 1 期間を除いた第 2 期間の間前記電圧値が制御された前記データ

信号を前記画素に供給する少なくとも一つのスイッチ手段と、

前記デジタル - アナログ変換器と前記スイッチ手段の間に設置されて前記第 1 期間の中

で一部期間の間ターンオンされて前記データ信号を前記スイッチ手段に伝達する第 1 トランジスターと、

前記第 1 トランジスターと前記スイッチ手段の間に接続される第 1 バッファーと、を備

え、

10

20

前記ガンマ電圧部は、

基準電源と第1電源の電圧値を分圧して前記階調電圧を生成する複数の分圧抵抗と、

前記第1電源からの電圧を前記電圧制御器に供給する第2バッファーと、を備え、

前記電圧制御器は、

前記第1トランジスターと前記第1バッファーの間に接続されるp個のキャパシタと、

前記キャパシタと前記第2バッファーの間に接続される第2トランジスターと、

前記キャパシタと前記電流シンク器の間に接続されて前記第2トランジスターと違う導電型に設定される第3トランジスターと、

10

前記第2トランジスターと前記第3トランジスターと同じ導電型に設定される第4トランジスターと、

前記第2データを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給して前記第2トランジスターと同じ導電型に設定される第5トランジスターと、

を備えることを特徴とするデータ駆動回路。

#### 【請求項2】

前記第4トランジスターは、

前記第2トランジスターがターンオンされるように前記第1期間の間ターンオンされて前記所定電圧源の電圧を前記第2トランジスターのゲート電極に供給することを特徴とする請求項1に記載のデータ駆動回路。

20

#### 【請求項3】

前記所定電圧源は、

基底電圧源に設定されることを特徴とする請求項2に記載のデータ駆動回路。

#### 【請求項4】

前記第1期間の間前記第2トランジスターがターンオンされて前記キャパシタの他側端子が前記第1電源の電圧に設定されることを特徴とする請求項2に記載のデータ駆動回路。

#### 【請求項5】

前記第5トランジスターは、

30

前記第2データのビット数に対応してp個設置され、前記第5トランジスターそれぞれは第2データの互いに違うビットを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給することを特徴とする請求項1に記載のデータ駆動回路。

#### 【請求項6】

前記第3トランジスターの中「1」のビットの供給を受ける第3トランジスターがターンオンされて前記補償電圧を前記キャパシタの他側端子に供給することを特徴とする請求項5に記載のデータ駆動回路。

#### 【請求項7】

前記キャパシタの容量は、

$2^0$ 、 $2^1$ 、 $2^2$ 、 $2^3$ 、 $2^4$ ...のように二進数加重値形態に設定されることを特徴とする請求項1に記載のデータ駆動回路。

40

#### 【請求項8】

前記電流シンク器は、

前記所定の電流の供給を受ける電流源と、

前記画素と接続されたデータ線と前記電圧制御器の間に設置されて前記第1期間の間ターンオンされる第6トランジスターと、

前記データ線と前記電流源の間に設置されて前記第1期間の間ターンオンされる第7トランジスターと、

前記補償電圧を充電するキャパシタと、

前記第6トランジスターと前記電圧制御器の間に設置されて前記補償電圧を前記電圧制

50

御器に伝達する第3バッファーと、を備えることを特徴とする請求項1に記載のデータ駆動回路。

**【請求項9】**

前記所定の電流の電流値は、

前記画素が最大輝度に発光される時流れる電流と同じに設定されることを特徴とする請求項8に記載のデータ駆動回路。

**【請求項10】**

前記スイッチ手段は、

前記第2期間の間ターンオンされる少なくとも一つのトランジスターを備えることを特徴とする請求項1に記載のデータ駆動回路。

10

**【請求項11】**

前記スイッチ手段は、

2個のトランジスターを具備して前記2個のトランジスターはトランスミッショングート形態に接続されることを特徴とする請求項1\_0に記載のデータ駆動回路。

**【請求項12】**

順次サンプリング信号を生成して、生成したサンプリング信号を前記ラッチ部に供給する少なくとも一つのシフトレジスターを含むシフトレジスター部をさらに備えることを特徴とする請求項1に記載のデータ駆動回路。

**【請求項13】**

前記ラッチ部は、

20

前記サンプリング信号に応答して前記第1データ及び第2データをラッチする少なくとも一つのサンプリングラッチを含むサンプリングラッチ部と、

前記サンプリングラッチ部に保存された第1データ及び第2データの供給を受けて保存し、かつ、自分が保存している第1データを前記デジタル-アナログ変換器に供給すると共に自分が保存している第2データを電圧制御器に供給する少なくとも一つのホルディングラッチを含むホルディングラッチ部を備えることを特徴とする請求項1\_2に記載のデータ駆動回路。

**【請求項14】**

前記サンプリングラッチ及びホルディングラッチそれぞれは、

$k + p$ ビットの大きさに設定されることを特徴とする請求項1\_3に記載のデータ駆動回路。

30

**【請求項15】**

前記ホルディングラッチに保存された前記第1データ及び第2データの電圧レベルを上昇させて前記デジタル-アナログ変換器及び前記電圧制御器に供給するレベルシフターをさらに備えることを特徴とする請求項1\_3に記載のデータ駆動回路。

**【請求項16】**

走査線、データ線及び発光制御線と接続されるように位置される複数の画素を含む画素部と、

前記走査線に走査信号を順次供給し、前記発光制御線に発光制御信号を順次供給する走査駆動部と、

40

前記データ線にデータ信号を供給する少なくとも一つのデータ駆動回路を持つデータ駆動部を具備し、

前記データ駆動回路は、

外部から供給される $k$ ( $k$ は自然数)ビットの第1データを二進数の加重値を持つよう

に変更して $p$ ( $p$ は自然数)ビットの第2データを生成する少なくとも一つのデコーダと、

、

前記第1データ及び第2データを保存するラッチ部と、

複数の階調電圧を生成するガンマ電圧部と、

前記第1データを利用して前記複数の階調電圧の中からいずれか一つの電圧を選択して前記データ信号として出力する少なくとも一つのデジタル-アナログ変換器と、

50

水平期間の第1期間の間前記画素から所定の電流の供給を受けて補償電圧を出力する少なくとも一つの電流シンク器と、

前記第2データに応じて前記電流シンク器からの前記補償電圧を利用して前記データ信号の電圧値を増減する少なくとも一つの電圧制御器と、

前記水平期間中前記第1期間を除いた第2期間の間前記電圧値が制御された前記データ信号を前記画素に供給する少なくとも一つのスイッチ手段と、

前記デジタル・アナログ変換器と前記スイッチ手段の間に設置されて前記第1期間中一部期間の間ターンオンされて前記データ信号を前記スイッチ手段に伝達する第1トランジスターと、

前記第1トランジスターと前記スイッチ手段の間に接続される第1バッファーと、を備え、10

前記ガンマ電圧部は、

基準電源と第1電源の電圧値を分圧して前記階調電圧を生成する複数の分圧抵抗と、

前記第1電源を前記電圧制御器に供給する第2バッファーと、を備え、

前記電圧制御器は、

前記第1トランジスターと前記第1バッファーの間のラインに一側端子が接続されるp個のキャパシタと、

前記キャパシタそれぞれの他側端子と前記第2バッファーの間に接続される第2トランジスターと、20

前記キャパシタそれぞれの他側端子と前記電流シンク器の間に接続されて前記第2トランジスターと違う導電型に設定される第3トランジスターと、

前記第2トランジスターのそれぞれのゲート電極と所定電圧源の間に接続されて前記第3トランジスターと同じ導電型に設定される第4トランジスターと、

前記第2データを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給して前記第2トランジスターと同じ導電型に設定される第5トランジスターと、

を備えることを特徴とする有機発光表示装置。

#### 【請求項17】

前記第4トランジスターは、

前記第2トランジスターがターンオンされるように前記第1期間の間ターンオンされて前記所定電圧源の電圧を前記第2トランジスターのゲート電極に供給することを特徴とする請求項16に記載の有機発光表示装置。30

#### 【請求項18】

前記第1期間の間前記第2トランジスターがターンオンされて前記キャパシタの他側端子が前記第1電源の電圧に設定されることを特徴とする請求項17に記載の有機発光表示装置。

#### 【請求項19】

前記第5トランジスターは、

前記第2データのビット数に対応してp個設置され、前記第5トランジスターそれぞれは第2データの互いに違うビットを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給することを特徴とする請求項16に記載の有機発光表示装置。40

#### 【請求項20】

前記第3トランジスターの中「1」のビットの供給を受ける第3トランジスターがターンオンされて前記補償電圧を前記キャパシタの他側端子に供給することを特徴とする請求項16に記載の有機発光表示装置。

#### 【請求項21】

前記キャパシタの容量は、

$2^0$ 、 $2^1$ 、 $2^2$ 、 $2^3$ 、 $2^4$ ...のように二進数加重値形態に設定されることを特徴とする請求項16に記載の有機発光表示装置。50

**【請求項 2 2】**

順次サンプリング信号を生成して、前記生成したサンプリング信号を前記ラッチ部に供給する少なくとも一つのシフトレジスターを含むシフトレジスター部をさらに備えることを特徴とする請求項 1 6 に記載の有機発光表示装置。

**【請求項 2 3】**

前記ラッチ部は、

前記サンプリング信号に応答して前記第 1 データ及び第 2 データの供給を受ける少なくとも一つのサンプリングラッチを含むサンプリングラッチ部と、

前記サンプリングラッチ部に保存された第 1 データ及び第 2 データの供給を受け保存し、かつ、自分が保存している第 1 データを前記デジタル - アナログ変換器に供給すると共に自分が保存している第 2 データを電圧制御器に供給する少なくとも一つのホルディングラッチを含むホルディングラッチ部を備えることを特徴とする請求項 2 2 に記載の有機発光表示装置。10

**【請求項 2 4】**

前記サンプリングラッチ及びホルディングラッチそれぞれは、

$k + p$  ビットの大きさに設定されることを特徴とする請求項 2 3 に記載の有機発光表示装置。

**【請求項 2 5】**

前記画素それぞれは、

第 2 電源と、20

前記第 2 電源から電流の供給を受ける有機発光ダイオードと、

前記第 2 電源にその一側端子が接続される第 1 キャパシタと、

前記第 1 キャパシタの他側端子とその一側端子が接続される第 2 キャパシタと、

第 1 電極が前記データ線に接続され、第 2 電極が前記第 1 キャパシタの他側端子及び前記第 2 キャパシタの一側端子に接続され、ゲート電極が現在走査線に接続されて、前記現在走査線の走査信号が供給される時ターンオンされる第 8 トランジスターと、

第 1 電極が前記データ線に接続され、ゲート電極が前記現在走査線に接続されて、前記現在走査線の走査信号が供給される時ターンオンされる第 9 トランジスターと、

前記第 8 トランジスターの前記第 2 電極と基準電源の間に接続されて以前走査線の走査信号がゲート電極に供給される時ターンオンされる第 10 トランジスターと、30

前記第 2 電源と前記有機発光ダイオードの間で、第 1 電極が前記第 2 電源に接続され、第 2 電極が前記第 9 トランジスターの第 2 電極に接続され、ゲート電極が前記第 2 キャパシタの他側端子に接続されて、前記有機発光ダイオードに供給される電流量を制御する第 11 トランジスターと、

前記第 11 トランジスターのゲート電極と前記第 11 トランジスターの第 2 電極の間に位置し、第 1 電極が前記第 11 トランジスターのゲート電極及び第 2 キャパシタの他側端子に接続されて前記以前走査線の走査信号がゲート電極に供給される時ターンオンされて前記第 11 トランジスターをダイオード形態で接続させる第 12 トランジスターと、

前記第 11 トランジスターの第 2 電極と前記有機発光ダイオードの間に位置し、第 1 電極が前記第 11 トランジスターの第 2 電極及び前記第 9 トランジスターの第 2 電極に接続されて、前記発光制御信号がゲート電極に供給される時ターンオフされて、それ以外の期間の間ターンオンされる第 13 トランジスターと、40

を備えることを特徴とする請求項 1 6 に記載の有機発光表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明はデータ駆動回路とこれを利用した有機発光表示装置に関し、より詳細には、均一な輝度の映像を表示できるようにしたデータ駆動回路とこれを利用した発光表示装置に関する。

**【背景技術】****【0002】**

近年、陰極線管 (Cathode Ray Tube) の短所である重さと嵩を減らすことができる各種平板表示装置が開発されている。平板表示装置では液晶表示装置 (Liquid Crystal Display)、電界放出表示装置 (Field Emission Display)、プラズマ表示パネル (Plasma Display Panel) 及び発光表示装置 (Light Emitting Display) などがある。

**【0003】**

平板表示装置の中で発光表示装置は、電子と正孔の再結合によって光を発生する発光素子を利用して映像を表示する。このような発光表示装置は、早い応答速度を持つと同時に低い消費電力で駆動されるという長所がある。10

**【0004】**

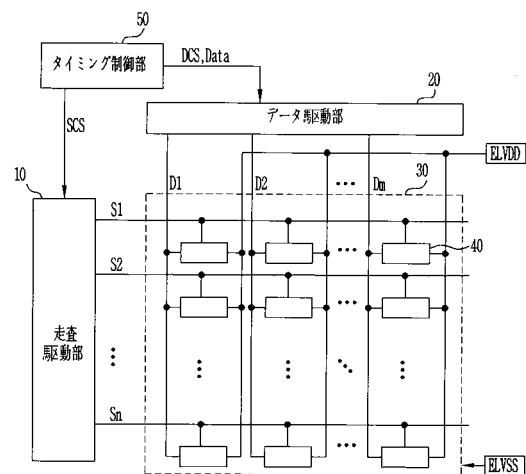

図1は従来の発光表示装置を表す図面である。

**【0005】**

図1を参照すれば、従来の発光表示装置は走査線 S1ないしSn及びデータ線 D1ないしDmに接続された複数の画素40を含む画素部30と、走査線 S1ないしSnを駆動する走査駆動部10と、データ線 D1ないしDmを駆動するデータ駆動部20と、走査駆動部10及びデータ駆動部20を制御するタイミング制御部50を備える。

**【0006】**

タイミング制御部50は、外部から供給される同期信号に対応してデータ駆動制御信号DCS及び走査駆動制御信号SCSを生成する。タイミング制御部50から生成されたデータ駆動制御信号DCSはデータ駆動部20に供給され、走査駆動制御信号SCSは走査駆動部10に供給される。そして、タイミング制御部50は外部から供給されるデータをデータ駆動部20に供給する。20

**【0007】**

走査駆動部10は、タイミング制御部50から走査駆動制御信号SCSの供給を受ける。走査駆動制御信号SCSの供給を受けた走査駆動部10は走査信号を生成し、生成された走査信号を走査線 S1ないしSnに順次供給する。

**【0008】**

データ駆動部20は、タイミング制御部50からデータ駆動制御信号DCSの供給を受ける。データ駆動制御信号DCSの供給を受けたデータ駆動部20は、データ信号を生成し、生成されたデータ信号を走査信号と同期されるようにデータ線 D1ないしDmに供給する。30

**【0009】**

画素部30は、外部から第1電源ELVDD及び第2電源ELVSSの供給を受けてそれぞれの画素40に供給する。第1電源ELVDD及び第2電源ELVSSの供給を受けた画素40それぞれは、データ信号に対応して第1電源ELVDDから発光素子を経由して第2電源ELVSSに流れる電流を制御することでデータ信号に対応される光を生成する。40

**【0010】**

すなわち、従来の発光表示装置で画素40それぞれは、データ信号に対応されて所定輝度の光を生成する。しかし、従来には画素40それぞれに含まれるトランジスターの閾値電圧のバラつき及び電子移動度 (electron mobility) の偏差によって所望の輝度の映像を表示することができないという問題点がある。

**【0011】**

実際に、画素40それぞれに含まれるトランジスターの閾値電圧は、画素40に含まれる画素回路の構造を制御することで、ある程度補償することができるが、電子移動度の偏差は補償されるない。したがって、電子移動度の偏差と無関係に均一な画像を表示することができる発光表示装置が要求されている。50

**【0012】**

このような従来のデータ駆動回路とこれを利用した発光表示装置に関する技術を記載した文献としては、例えば、下記特許文献1等がある。

**【特許文献1】特開2003-186457号公報**

**【発明の開示】****【発明が解決しようとする課題】****【0013】**

したがって、本発明の目的は均一な輝度の映像を表示するようにしたデータ駆動回路とこれを利用した有機発光表示装置を提供することである。

**【課題を解決するための手段】****【0014】**

前記目的を達成するための本発明は、外部から供給される $k$  ( $k$  は自然数) ビットの第1データを二進数の加重値を持つように変更して $p$  ( $p$  は自然数) ビットの第2データを生成する少なくとも一つのデコーダと、前記第1データ及び第2データを保存するラッチ部と、複数の階調電圧を生成するガンマ電圧部と、前記第1データを利用して前記階調電圧の中からいざれか一つの電圧を選択してデータ信号として出力する少なくとも一つのデジタル - アナログ変換器と、水平期間の第1期間の間画素から所定の電流の供給を受けて補償電圧を出力する少なくとも一つの電流シンク器と、前記第2データに応じて前記電流シンク器からの前記補償電圧の電圧値を加減して、当該加減した補償電圧の電圧値により前記データ信号の電圧値を増減する少なくとも一つの電圧制御器と、前記水平期間中前記第1期間を除いた第2期間の間前記電圧値が制御された前記データ信号を前記画素に供給する少なくとも一つのスイッチ手段と、前記デジタル - アナログ変換器と前記スイッチ手段の間に設置されて前記第1期間の中で一部期間の間ターンオンされて前記データ信号を前記スイッチ手段に伝達する第1トランジスターと、前記第1トランジスターと前記スイッチ手段の間に接続される第1バッファーと、を備え、前記ガンマ電圧部は、基準電源と第1電源の電圧値を分圧して前記階調電圧を生成する複数の分圧抵抗と、前記第1電源からの電圧を前記電圧制御器に供給する第2バッファーと、を備え、前記電圧制御器は、前記第1トランジスターと前記第1バッファーの間のラインに一側端子が接続される $p$  個のキャパシタと、前記キャパシタそれぞれの他側端子と前記第2バッファーの間に接続される第2トランジスターと、前記キャパシタそれぞれの他側端子と前記電流シンク器の間に接続されて前記第2トランジスターと違う導電型に設定される第3トランジスターと、前記第2トランジスターのそれぞれのゲート電極と所定電圧源の間に接続されて前記第3トランジスターと同じ導電型に設定される第4トランジスターと、前記第2データを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給して前記第2トランジスターと同じ導電型に設定される第5トランジスターと、を備えることを特徴とするデータ駆動回路である。

**【0016】**

前記デコーダは前記第1データを二進数の加重値 (Binary Weighted) を持つように変更して前記第2データを生成する。前記ガンマ電圧部は基準電源と第1電源の電圧値を分圧して前記階調電圧を生成する複数の分圧抵抗と、前記第1電源を前記電圧制御器に供給する第2バッファーと、を備える。

**【0018】**

また、前記目的を達成するための本発明は、走査線、データ線及び発光制御線と接続されるように位置される複数の画素を含む画素部と、前記走査線に走査信号を順次供給し、前記発光制御線に発光制御信号を順次供給する走査駆動部と、前記データ線にデータ信号を供給する少なくとも一つのデータ駆動回路を持つデータ駆動部を具備し、前記データ駆動回路は、外部から供給される $k$  ( $k$  は自然数) ビットの第1データを二進数の加重値を持つように変更して $p$  ( $p$  は自然数) ビットの第2データを生成する少なくとも一つのデコーダと、前記第1データ及び第2データを保存するラッチ部と、複数の階調電圧を生成するガンマ電圧部と、前記第1データを利用して前記複数の階調電圧の中からいざれか一

10

20

30

40

50

つの電圧を選択して前記データ信号として出力する少なくとも一つのデジタル - アナログ変換器と、水平期間の第1期間の間前記画素から所定の電流の供給を受けて補償電圧を出力する少なくとも一つの電流シンク器と、前記第2データに応じて前記電流シンク器からの前記補償電圧を利用して前記データ信号の電圧値を増減する少なくとも一つの電圧制御器と、前記水平期間中前記第1期間を除いた第2期間の間前記電圧値が制御された前記データ信号を前記画素に供給する少なくとも一つのスイッチ手段と、前記デジタル - アナログ変換器と前記スイッチ手段の間に設置されて前記第1期間中一部期間の間ターンオンされ前記データ信号を前記スイッチ手段に伝達する第1トランジスターと、前記第1トランジスターと前記スイッチ手段の間に接続される第1バッファーと、を備え、前記ガンマ電圧部は、基準電源と第1電源の電圧値を分圧して前記階調電圧を生成する複数の分圧抵抗と、前記第1電源を前記電圧制御器に供給する第2バッファーと、を備え、前記電圧制御器は、前記第1トランジスターと前記第1バッファーの間のラインに一側端子が接続されるp個のキャパシタと、前記キャパシタそれぞれの他側端子と前記第2バッファーの間に接続される第2トランジスターと、前記キャパシタそれぞれの他側端子と前記電流シンク器の間に接続されて前記第2トランジスターと違う導電型に設定される第3トランジスターと、前記第2トランジスターのそれぞれのゲート電極と所定電圧源の間に接続されて前記第3トランジスターと同じ導電型に設定される第4トランジスターと、前記第2データを前記第2トランジスター及び前記第3トランジスターのそれぞれのゲート電極に供給して前記第2トランジスターと同じ導電型に設定される第5トランジスターと、を備えることを特徴とする有機発光表示装置。

10

#### 【発明の効果】

#### 【0021】

上述したように、本発明によるデータ駆動回路とこれを利用した有機発光表示装置によれば、画素から電流をシンクする時発生される補償電圧を利用してデータ信号の電圧値を再設定するので、トランジスターの移動度と無関係に均一な画像を表示することができる。

20

#### 【発明を実施するための最良の形態】

#### 【0022】

以下、本発明の望ましい実施形態を添付された図2乃至図12を参照して詳しく説明する。

30

#### 【0023】

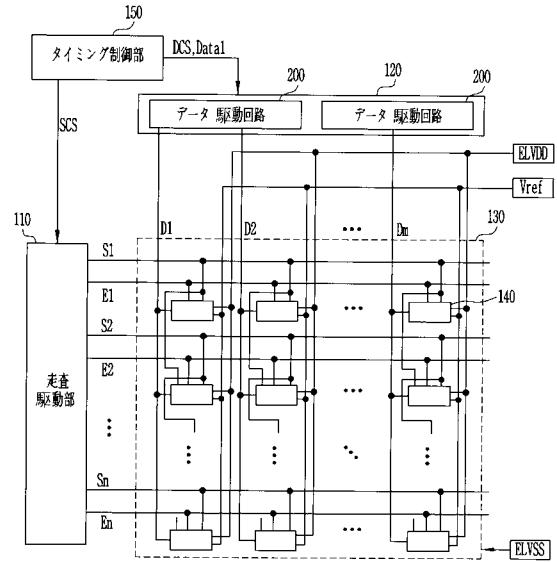

図2は、本発明の実施形態による有機発光表示装置を表す図面である。

#### 【0024】

図2を参照すれば、本発明の実施形態による発光表示装置は、走査線S1乃至Sn、発光制御線E1乃至En、及びデータ線D1乃至Dmに接続される複数の画素140を含む画素部130と、走査線S1乃至Sn及び発光制御線E1乃至Enを駆動する走査駆動部110と、データ線D1乃至Dmを駆動するデータ駆動部120と、走査駆動部110及びデータ駆動部120を制御するタイミング制御部150を備える。

#### 【0025】

画素部130は、走査線S1乃至Sn、発光制御線E1乃至En、及びデータ線D1乃至Dmによって区画された領域に形成される画素140を備える。画素140は外部から第1電源ELVDD、第2電源ELVSS、及び基準電源Vrefから電力の供給を受ける。基準電源Vrefからの電力供給を受けた画素140それぞれは基準電源Vrefと第1電源ELVDDの電圧差の値を利用して第1電源ELVDDの電圧降下を補償する。

40

#### 【0026】

そして、画素140それぞれは、データ信号に対応して第1電源ELVDDからの電流を発光素子(図示せず)を経由して第2電源ELVSSに流すことになる。このために、画素140それぞれは図3または図5のように構成することができる。したがって、本実施形態では第2電源ELVSSは実質的にアースである。なお、図3または図5に図示された画素140の詳細な構造は後述する。

50

## 【0027】

タイミング制御部150は外部から供給される同期信号に対応してデータ駆動制御信号DCS及び走査駆動制御信号SCSを生成する。タイミング制御部150から生成されたデータ駆動制御信号DCSはデータ駆動部120に供給され、走査駆動制御信号SCSは走査駆動部110に供給される。そして、タイミング制御部150は外部から供給されるデータをデータ駆動部120に供給する。

## 【0028】

走査駆動部110は走査駆動制御信号SCSの供給を受ける。走査駆動制御信号SCSの供給を受けた走査駆動部110は、走査線S1乃至Snに走査信号を順次供給する。そして、走査駆動制御信号SCSの供給を受けた走査駆動部110は発光制御線E1乃至Enに発光制御信号を順次供給する。ここで、発光制御信号は2個の走査信号と重畠されるように供給される。このために、発光制御信号の幅は走査信号の幅と同じかまたは広く設定される。

10

## 【0029】

データ駆動部120はタイミング制御部150からデータ駆動制御信号DCSの供給を受ける。データ駆動制御信号DCSの供給を受けたデータ駆動部120はデータ信号を生成し、生成されたデータ信号をデータ線D1乃至Dmに供給する。ここで、データ駆動部120は1水平期間1H中第1期間の間データ線D1乃至Dmに所定の電流を供給し、1水平期間1H中第1期間を除いた第2期間の間データ線D1乃至Dmに所定の電圧を供給する。このために、データ駆動部120は少なくとも一つのデータ駆動回路200を備える。以後、説明の便宜性のために第2期間の間データ線D1乃至Dmに供給される電圧をデータ信号と言う。

20

## 【0030】

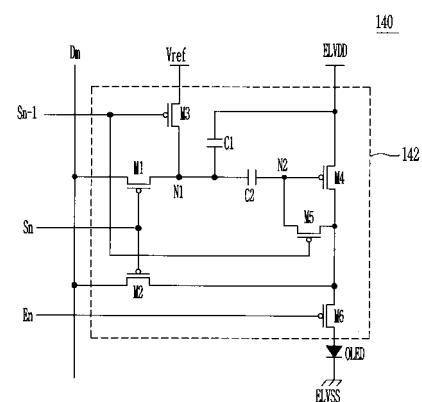

図3は図2に図示された画素の一例を表す図面である。図3では説明の便宜性のために第mデータ線Dm、第n-1及び第n走査線Sn-1、Sn及び第n発光制御線Enに接続された画素を図示する。

## 【0031】

図3を参照すれば、本発明の画素140は有機発光素子OLED、有機発光素子OLEDに電流を供給する画素回路142を備える。

30

## 【0032】

有機発光素子OLEDは画素回路142から供給される電流に対応して所定色の光を生成する。

## 【0033】

画素回路142は第n-1走査線Sn-1(以前走査線)に走査信号が供給される時第1電源ELVDDの電圧降下と第4トランジスターM4の閾値電圧を補償し、第n走査線Sn(現在走査線)に走査信号が供給される時データ信号に対応される電圧を充電する。このために、画素回路142は第1乃至第6トランジスターM1乃至M6と、第1キャパシタC1及び第2キャパシタC2を備える。

## 【0034】

第1トランジスターM1の第1電極はデータ線Dmに接続されて、第2電極は第1ノードN1に接続される。そして、第1トランジスターM1のゲート電極は第n走査線Snに接続される。このような第1トランジスターM1は第n走査線Snに走査信号が供給される時ターンオンされてデータ線Dmと第1ノードN1を電気的に接続させる。

40

## 【0035】

第2トランジスターM2の第1電極はデータ線Dmに接続されて、第2電極は第4トランジスターM4の第2電極に接続される。そして、第2トランジスターM2のゲート電極は第n走査線Snに接続される。このような第2トランジスターM2は第n走査線Snに走査信号が供給される時ターンオンされてデータ線Dmと第4トランジスターM4の第2電極を電気的に接続させる。

## 【0036】

50

第3トランジスターM3の第1電極は基準電源Vrefに接続されて、第2電極は第1ノードN1に接続される。そして、第3トランジスターM3のゲート電極は第n-1走査線Sn-1に接続される。このような第3トランジスターM3は第n-1走査線Sn-1に走査信号が供給される時ターンオンされて基準電源Vrefと第1ノードN1を電気的に接続させる。

#### 【0037】

第4トランジスターM4の第1電極は第1電源ELVDDに接続されて、第2電極は第6トランジスターM6の第1電極に接続される。そして、第4トランジスターM4のゲート電極は第2ノードN2に接続される。このような第4トランジスターM4は第2ノードN2に印加される電圧、すなわち、第1キャパシタC1及び第2キャパシタC2に充電された電圧に対応される電流を第6トランジスターM6の第1電極に供給する。10

#### 【0038】

第5トランジスターM5の第2電極は第2ノードN2に接続されて、第1電極は第4トランジスターM4の第2電極に接続される。そして、第5トランジスターM5のゲート電極は第n-1走査線Sn-1に接続される。このような第5トランジスターM5は第n-1走査線Sn-1に走査信号が供給される時ターンオンされて第4トランジスターM4をダイオード形態で接続させる。

#### 【0039】

第6トランジスターM6の第1電極は第4トランジスターM4の第2電極に接続されて、第2電極は発光素子OLEDのアノード電極に接続される。そして、第6トランジスターM6のゲート電極は第n発光制御線Enに接続される。このような第6トランジスターM6は第n発光制御線Enに発光制御信号が供給される時ターンオフされて、発光制御信号が供給されない時ターンオンされる。20

#### 【0040】

ここで、第n発光制御線Enに供給される発光制御信号は第n-1走査線Sn-1及び第n走査線Snに供給される走査信号と重畠されるように供給される。したがって、第6トランジスターM6は第n-1走査線Sn-1及び第n走査線Snに走査信号が供給されて第1キャパシタC1及び第2キャパシタC2に所定の電圧が充電される時ターンオフされて、それ以外の場合にターンオンされて第4トランジスターM4と発光素子OLEDを電気的に接続させる。30

#### 【0041】

一方、図3では説明の便宜性のためにトランジスターM1乃至M6をPMOSタイプに図示したが、本発明はこれに限定されない。

#### 【0042】

そして、図3に図示された画素で基準電源Vrefは、発光素子OLEDに電流を供給しない。すなわち、基準電源Vrefは画素140に電流を供給しないため、電圧降下が発生されず、これによって画素140の位置と無関係に同じ電圧値を維持することができる。ここで、基準電源Vrefの電圧値は第1電源ELVDDと同じく設定されるか、または違うように設定することができる。

#### 【0043】

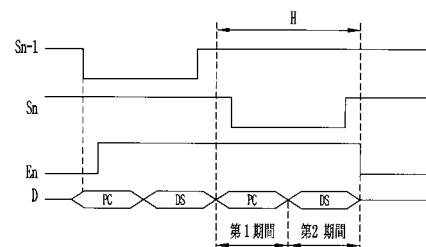

図4は、図3に図示された画素の駆動方法を表す波形図である。図4において、1水平期間1Hは第1期間及び第2期間に分けて駆動される。第1期間の間データ線D1乃至Dmには所定の電流(PC:Pre determined Current)が流れ、第2期間の間データ信号DSが供給される。40

#### 【0044】

実際に、第1期間の間には画素140からデータ駆動回路200に所定の電流PCが供給される(Current Sink)。そして、第2期間の間にはデータ駆動回路200から画素140にデータ信号DSが供給される。

#### 【0045】

図3及び図4を結び付けて動作過程を詳しく説明すれば、まず、第n-1走査線Sn-1

10

20

30

40

50

に走査信号が供給される。第  $n - 1$  走査線  $S_{n-1}$  に走査信号が供給されれば第 3 トランジスター  $M_3$  及び第 5 トランジスター  $M_5$  がターンオンされる。

【0046】

第 5 トランジスター  $M_5$  がターンオンされれば第 4 トランジスター  $M_4$  がダイオード形態に接続される。第 4 トランジスター  $M_4$  がダイオード形態に接続されれば第 2 ノード  $N_2$  には第 1 電源  $E_{LVD}\text{DD}$  から第 4 トランジスター  $M_4$  の閾値電圧を差し引いた電圧値が印加される。

【0047】

そして、第 3 トランジスター  $M_3$  がターンオンされれば基準電源  $V_{ref}$  の電圧が第 1 ノード  $N_1$  に印加される。この時、第 2 キャパシタ  $C_2$  は第 1 ノード  $N_1$  と第 2 ノード  $N_2$  の差に対応される電圧を充電する。この場合、基準電源  $V_{ref}$  と第 1 電源  $E_{LVD}\text{DD}$  の電圧値が同じだと仮定すれば第 2 キャパシタ  $C_2$  には第 4 トランジスター  $M_4$  の閾値電圧に対応される電圧が充電される。そして、第 1 電源  $E_{LVD}\text{DD}$  で所定の電圧降下が発生されれば第 2 キャパシタ  $C_2$  には第 4 トランジスター  $M_4$  の閾値電圧及び第 1 電源  $E_{LVD}\text{DD}$  の電圧降下電圧が充電される。

【0048】

すなわち、本発明では第  $n - 1$  走査線  $S_{n-1}$  に走査信号が供給される期間の間第 1 電源  $E_{LVD}\text{DD}$  の電圧降下電圧及び第 4 トランジスター  $M_4$  の閾値電圧が第 2 キャパシタ  $C_2$  に充電されて、これによって第 1 電源  $E_{LVD}\text{DD}$  の電圧降下を補償することができる。

【0049】

第 2 キャパシタ  $C_2$  に所定の電圧が充電された後、第  $n$  走査線  $S_n$  に走査信号が供給される。第  $n$  走査線  $S_n$  に走査信号が供給されれば第 1 トランジスター  $M_1$  及び第 2 トランジスター  $M_2$  がターンオンされる。第 2 トランジスター  $M_2$  がターンオンされれば 1 水平期間の第 1 期間の間所定の電流  $P_C$  が画素 140 からデータ線  $D_m$  を経由してデータ駆動回路 200 に供給される。

【0050】

実際に、所定の電流  $P_C$  は第 1 電源  $E_{LVD}\text{DD}$ 、第 4 トランジスター  $M_4$ 、第 2 トランジスター  $M_2$  及びデータ線  $D_m$  を経由してデータ駆動回路 200 に供給される。

【0051】

データ駆動回路 200 は、所定の電流  $P_C$  がシンクされる時発生される所定の電圧値（以後「補償電圧」という）を利用してデータ信号  $D_S$  の電圧を再設定し、再設定されたデータ信号  $D_S$  の電圧を水平期間の第 2 期間の間第 1 トランジスター  $M_1$  を経由して第 1 ノード  $N_1$  に供給する。すると、第 1 キャパシタ  $C_1$  にはデータ信号  $D_S$  と第 1 電源  $E_{LVD}\text{DD}$  の差値に対応する電圧が充電される。この時、第 2 ノード  $N_2$  はフローティング状態に設定されるから第 2 キャパシタ  $C_2$  は以前に充電された電圧を維持する。

【0052】

すなわち、本発明では以前走査線に走査信号が供給される期間の間第 2 キャパシタ  $C_2$  に第 4 トランジスター  $M_4$  の閾値電圧及び第 1 電源  $E_{LVD}\text{DD}$  の電圧降下に対応する電圧を充電することで、第 1 電源  $E_{LVD}\text{DD}$  の電圧降下及び第 4 トランジスター  $M_4$  の閾値電圧を補償することができる。

【0053】

そして、本発明では現在走査線に走査信号が供給される期間の間画素 140 に含まれたトランジスターの移動度などが補償されるようにデータ信号  $D_S$  の電圧値を再設定し、電圧値が再設定されたデータ信号  $D_S$  を画素 140 に供給する。したがって、本発明ではトランジスターの閾値電圧、移動度などのバラつきを補償して均一な画像を表示することができる。

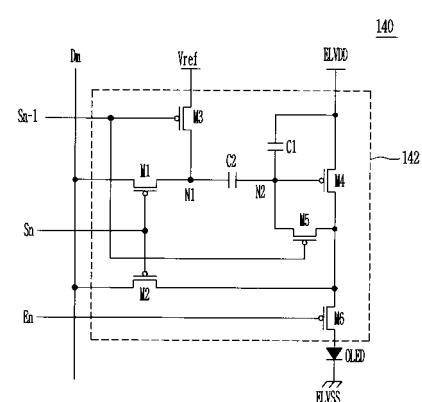

【0054】

図 5 は、図 2 に図示された画素の他の例を表す図面である。図 5 は第 1 キャパシタ  $C_1$  が第 2 ノード  $N_2$  と第 1 電源  $E_{LVD}\text{DD}$  の間に設置されることを除き、図 3 と同じ構成で設定される。

10

20

30

40

50

**【 0 0 5 5 】**

図4及び図5を参照して動作過程を詳しく説明すれば、まず、第n-1走査線S<sub>n-1</sub>に走査信号が供給される。第n-1走査線S<sub>n-1</sub>に走査信号が供給されれば第3トランジスターM3及び第5トランジスターM5がターンオンされる。第5トランジスターM5がターンオンされれば第4トランジスターM4がダイオード形態に接続される。第4トランジスターM4がダイオード形態に接続されれば第2ノードN2には第1電源E<sub>LVD</sub>Dから第4トランジスターM4の閾値電圧を差し引いた電圧値が印加される。したがって、第1キャパシタC1には第4トランジスターM4の閾値電圧に対応される電圧が充電される。

**【 0 0 5 6 】**

そして、第3トランジスターM3がターンオンされれば基準電源V<sub>ref</sub>の電圧が第1ノードN1に印加される。すると、第2キャパシタC2は第1ノードN1と第2ノードN2の差に対応される電圧が充電される。ここで、第n-1走査線S<sub>n-1</sub>に走査信号が供給される期間の間第1トランジスターM1及び第2トランジスターM2がターンオフされるからデータ信号D<sub>S</sub>は画素140に供給されない。

**【 0 0 5 7 】**

以後、第n走査線S<sub>n</sub>に走査信号が供給されて第1トランジスターM1及び第2トランジスターM2がターンオンされる。第2トランジスターM2がターンオンされれば1水平期間の第1期間の間所定の電流P<sub>C</sub>が画素140からデータ線D<sub>m</sub>を経由してデータ駆動回路200に供給される。

10

20

**【 0 0 5 8 】**

実際に、所定の電流P<sub>C</sub>は第1電源E<sub>LVD</sub>D、第4トランジスターM4、第2トランジスターM2及びデータ線D<sub>m</sub>を経由してデータ駆動回路200に供給される。

**【 0 0 5 9 】**

データ駆動回路200は、所定の電流P<sub>C</sub>がシンクされるとき発生される補償電圧を利用してデータ信号D<sub>S</sub>の電圧を再設定し、電圧が再設定されたデータ信号D<sub>S</sub>を水平期間の第2期間の間第1トランジスターM1を経由して第1ノードN1に供給する。すると、第1キャパシタC1及び第2キャパシタC2にはデータ信号D<sub>S</sub>に対応して所定の電圧が充電される。

**【 0 0 6 0 】**

30

実際に、データ信号D<sub>S</sub>が供給されれば第1ノードN1の電圧が下降する。第2ノードN2がフローティングされているから第1ノードN1の電圧下降量に対応して第2ノードN2の電圧値も下降する。この場合、第2ノードN2で下降する電圧値は、第1キャパシタC1及び第2キャパシタC2の容量によって決まる。

**【 0 0 6 1 】**

第2ノードN2の電圧が下降すると第1キャパシタC1には、第2ノードN2の電圧値に対応して所定の電圧が充電される。ここで、第1ノードN1の下降電圧は、データ信号D<sub>S</sub>によって決まり、これによって第1キャパシタC1に充電される電圧もデータ信号D<sub>S</sub>によって決まる。そして、本発明では画素140に含まれたトランジスターの移動度などが補償されるようにデータ信号D<sub>S</sub>の電圧を再設定するからトランジスターの移動度などのバラつきを補償して画像を表示することができる。

40

**【 0 0 6 2 】**

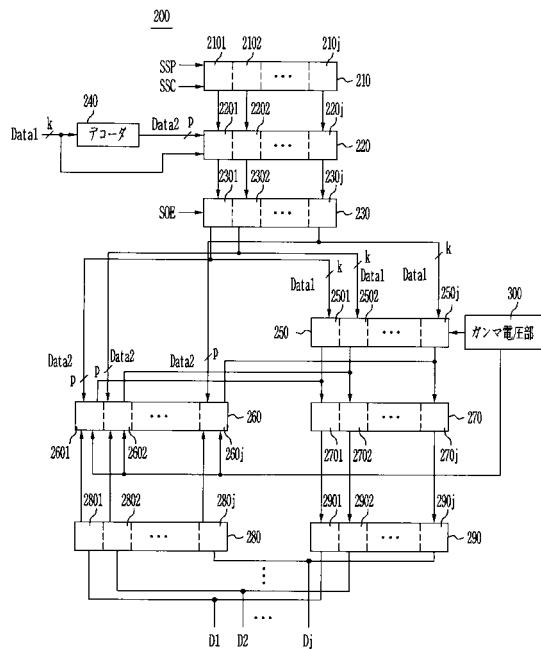

図6は図2に図示されたデータ駆動回路の一例を表すブロック図である。図6では説明の便宜性のためにデータ駆動回路200がj(jは2以上の自然数)個のチャンネルを持つと仮定する。

**【 0 0 6 3 】**

図6を参照すれば、本発明のデータ駆動回路200は、シフトレジスター部210、サンプリングラッチ部220、ホールディングラッチ部230、デコーダ240、デジタル-アナログ変換部(以下「DAC部」とする)250、電圧制御部260、第1バッファ部270、電流供給部280、選択部290、及びガンマ電圧部300を備える。ここで

50

サンプリングラッチ部 220 及びホルディングラッチ部 230 が本発明におけるラッチ部を構成することになる。

【0064】

シフトレジスター部 210 はタイミング制御部 150 からソースシフトクロック S S C 及びソーススタートパルス S S P の供給を受ける。タイミング制御部 150 からソースシフトクロック S S C 及びソーススタートパルス S S P の供給を受けたシフトレジスター部 210 は、ソースシフトクロック S S C の 1 周期ごとにソーススタートパルス S S P をシフトさせながら順次  $j$  個のサンプリング信号を生成する。このために、シフトレジスター部 210 は  $j$  個のシフトレジスター 2101 乃至 210j を備える。

【0065】

デコーダ 240 はタイミング制御部 150 から供給される  $k$  ( $k$  は自然数) ビットの第 1 データ Data1 を  $p$  ( $p$  は自然数) ビットの第 2 データ Data2 に変換する。

【0066】

ここで、デコーダ 240 は二進数の加重値を持つように第 2 データ Data2 を生成する。二進数の加重値は、第 2 データの各ビットが二進数の加重値で増加することを意味する。例えば、第 2 データが「10101」だとすれば、下位ビットから上位ビットに行くほど  $2^0$ 、 $2^1$ 、 $2^2$ 、 $2^3$ 、 $2^4$ 、. . . の加重値を持つようになる。

【0067】

つまり、ガンマ電圧部 300 から生成される階調電圧の中でいずれか一つを選択するためにビット値が設定された  $k$  ビットの第 1 データ Data1 を二進数の加重値を持つように変換して  $p$  ビットの第 2 データ Data2 を生成する。例えば、デコーダ 240 は 8 ビットの第 1 データ Data1 を利用して 5 ビットの第 2 データ Data2 を生成する。

【0068】

このようなデコーダ 240 はサンプリングラッチ部 220 と接続されるように少なくとも一つ以上設置される。例えば、タイミング制御部 150 から第 1 データ Data1 が順次供給されれば、サンプリングラッチ部 220 と接続されるように一つのデコーダ 240 が設置される。そして、タイミング制御部 150 から赤、緑、及び青に対応する第 1 データ Data1 が同時に入力される場合、サンプリングラッチ部 220 と接続されるように三つのデコーダ 240 が設置される。

【0069】

サンプリングラッチ部 220 はシフトレジスター部 210 から順次供給されるサンプリング信号に応答して第 1 データ Data1 及び第 2 データ Data2 を順次保存する。このために、サンプリングラッチ部 220 は  $j$  個の第 1 データ Data1 及び  $j$  個の第 2 データ Data2 を保存するために  $j$  個のサンプリングラッチ 2201 乃至 220j を備える。

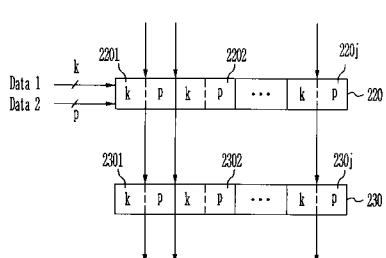

【0070】

ここで、それぞれのサンプリングラッチ 2201 乃至 220j は図 7 に図示されたところのように  $k$  ビットの第 1 データ Data1 及び  $p$  ビットの第 2 データ Data2 を保存できるように  $k + p$  ビットの大きさに設定される。

【0071】

ホルディングラッチ部 230 はソース出力イネーブル S O E 信号が入力された時にサンプリングラッチ部 220 から第 1 データ Data1 及び第 2 データ Data2 の入力を受けて保存する。そして、ホルディングラッチ部 230 はソース出力イネーブル S O E 信号が入力された時に、自分に保存されている第 1 データ Data1 を D A C 部 250 に供給すると共に、同じく自分に保存されている第 2 データ Data2 を電圧制御部 260 に供給する。

【0072】

このために、ホルディングラッチ部 230 は  $j$  個の第 1 データ Data1 及び  $j$  個の第 2 データ Data2 を保存するために  $j$  個のホルディングラッチ 2301 乃至 230j を備える。ここで、それぞれのホルディングラッチ 2301 乃至 230j は図 7 に図示され

10

20

30

40

50

たように k ビットの第 1 データ Data1 及び p ビットの第 2 データ Data2 を保存できるように k + p ビットの大きさに設定される。

#### 【0073】

電流供給部 280 は、1 水平期間の第 1 期間の間データ線 D1 乃至 Dj に接続された画素 140 から所定の電流 P C を吸い込む（シンクする）。実際に、電流供給部 280 はそれぞれの画素 140 に流すことができる最大電流、すなわち、画素 140 を最大輝度に発光される時に有機発光ダイオード O L E D に供給すべき電流をシンクする。そして、電流供給部 280 は電流がシンクされる時発生される所定の補償電圧を比較部 260 に供給する。このために、電流供給部 280 は j 個の電流シンク器 2801 乃至 280j を備える。

10

#### 【0074】

ガンマ電圧部 300 は、k ビットの第 1 データに対応して所定の階調電圧を生成する。実際に、ガンマ電圧部 300 は図 9 に図示されたように、複数の分圧抵抗 R1 乃至 R1 で構成されて 2k 個の階調電圧を生成する。ガンマ電圧部 300 から生成された階調電圧は、D A C 2501 乃至 250j に供給される。

#### 【0075】

D A C 部 250 は、j 個の D A C 2501 乃至 250j を備える。D A C 2501 乃至 250j それぞれは、ホルディングラッチ部 2301 乃至 230j から供給される第 1 データ Data1 のビット値に対応してガンマ電圧部 300 から供給される階調電圧の中でいずれか一つを選択する。選択された電圧はデータ信号 DS として D A C 部 250 から出力される。

20

#### 【0076】

電圧制御部 260 は、j 個の電圧制御器 2601 乃至 260j を備える。それぞれの電圧制御器 2601 乃至 260j は、補償電圧、第 2 データ Data2、及び第 3 電源 V S S の供給を受ける。ここで、第 3 電源 V S S は、ガンマ電圧部 300 の一側端子に供給される電圧である。補償電圧、第 2 データ Data2 及び第 3 電源 V S S の供給を受けた電圧制御器 2601 乃至 260j は、画素 140 に含まれたトランジスターの移動度などが補償されるように、D A C 部 250 から出力されたデータ信号 DS の電圧値を制御する。

#### 【0077】

第 1 バッファーパート 270 は、電圧制御部 260 によって電圧が制御されたデータ信号 DS を選択部 290 に供給する。このために、第 1 バッファーパート 270 は、j 個の第 1 バッファー 2701 乃至 270j を備える。

30

#### 【0078】

選択部 290 はデータ線 D1 乃至 Dj と第 1 バッファー 2701 乃至 270j の電気的連結を制御する。実際に、選択部 290 は 1 水平期間の第 2 期間の間にデータ線 D1 乃至 Dj と第 1 バッファー 2701 乃至 270j を電気的に接続させ、それ以外にはデータ線 D1 乃至 Dj と第 1 バッファー 2701 乃至 270j を接続させない。このために、選択部 290 は j 個のスイッチ手段 2901 乃至 290j を備える。

#### 【0079】

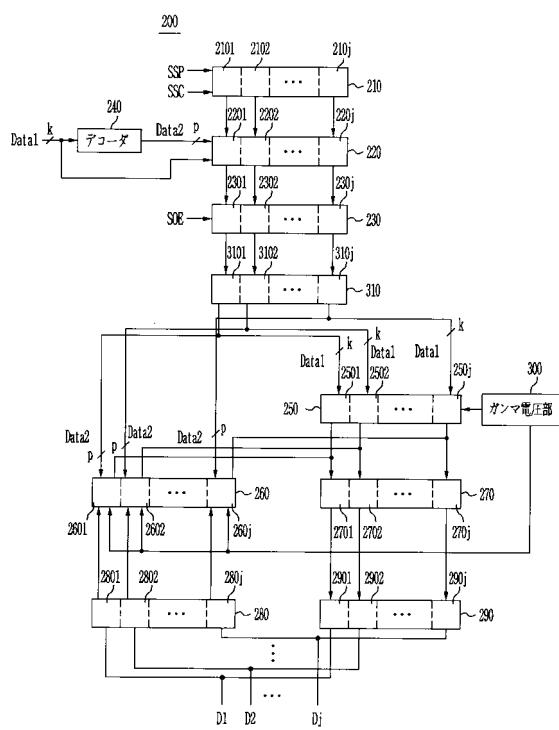

ここで、データ駆動回路の他の形態について説明する。

40

#### 【0080】

図 8 は、本発明のデータ駆動回路の他の形態を示す図面である。このデータ駆動回路 200 は、ホルディングラッチ部 230 の次の段にレベルシフター部 310 をさらに配置したものである（第 2 実施形態）。そのほかの構成は、図 6 を用いて説明したデータ駆動回路と同様である。

#### 【0081】

レベルシフター部 310 は、ホルディングラッチ部 230 から供給される第 1 データ Data1 および第 2 データ Data2 の電圧レベルを上昇させて D A C 部 250 及び電圧制御部 260 に供給する。

#### 【0082】

50

外部システムからデータ駆動回路 200 に高い電圧レベルを持つ第 1 データ Data 1 が供給されれば電圧レベルに対応させて高い耐圧を持つ回路部品が設置されなければならないから製造コストが増加される。このため、データ駆動回路 200 の外部では低い電圧レベルを持つ第 1 データ Data 1 を供給できるようにする一方、この低い電圧レベルを持つ第 1 データ Data 1 をレベルシフター部 310 で高い電圧レベルに昇圧させるようにしたものである。

#### 【0083】

図 9 は図 6 に図示されたガンマ電圧部、DAC、電圧制御器、スイッチ手段、電流シンク器及び画素の連結関係を表す図面である。図 9 では説明の便宜性のために j 番目チャンネルを図示して、データ線 D<sub>j</sub> が図 3 に図示された画素 140 と接続されると仮定する。

10

#### 【0084】

図 9 を参照すれば、ガンマ電圧部 300 は複数の分圧抵抗 R<sub>1</sub> 乃至 R<sub>1</sub> を備える。分圧抵抗 R<sub>1</sub> 乃至 R<sub>1</sub> は基準電源 V<sub>ref</sub> と第 3 電源 V<sub>SS</sub> の間に位置されて電圧を分圧する。実際に、分圧抵抗 R<sub>1</sub> 乃至 R<sub>1</sub> は基準電源 V<sub>ref</sub> と第 3 電源 V<sub>SS</sub> の間の電圧を分圧して複数の階調電圧 V<sub>0</sub> 乃至 V<sub>2<sup>K-1</sup></sub> を生成し、生成された階調電圧 V<sub>0</sub> 乃至 V<sub>2<sup>K-1</sup></sub> を DAC 250j に供給する。

#### 【0085】

そして、ガンマ電圧部 300 は第 3 電源 V<sub>SS</sub> の電圧を第 3 バッファー 301 を経由して電圧制御器 260j に供給する。

20

#### 【0086】

DAC 250j は、第 1 データ Data 1 のビット値に対応して階調電圧 V<sub>0</sub> 乃至 V<sub>2<sup>K-1</sup></sub> の中でいずれか一つの電圧を選択して、データ信号 DS として出力される。出力されたデータ信号 DS は第 1 バッファー 270j に供給される。

#### 【0087】

ここで、DAC 250j と第 1 バッファー 270j の間には第 3 制御信号 CS 3 ( 図 10 参照 ) によって制御される第 41 トランジスター M41 が設置されている。

#### 【0088】

すなわち、第 41 トランジスター M41 は水平期間の第 1 期間中、一部期間の間ターンオンされて DAC 250j から供給されるデータ信号 DS を第 1 バッファー 270j に供給する。実際に、第 3 制御信号 CS 3 は第 2 制御信号 CS 2 より遅く上昇し、第 2 制御信号 CS 2 と同一時点で下降される。

30

#### 【0089】

電流シンク器 280j は、第 2 制御信号 CS 2 によって制御される第 12 トランジスター M12 及び第 13 トランジスター M13 と、第 13 トランジスター M13 の第 1 電極に接続される電流源 I<sub>max</sub> と、第 3 ノード N3 と基底電圧源 GND の間に接続される第 3 キャパシタ C3 と、第 3 ノード N3 と電圧制御器 260j の間に接続される第 2 バッファー 281 を備える。

#### 【0090】

第 12 トランジスター M12 のゲート電極は、第 13 トランジスター M13 のゲート電極に接続され、第 2 電極は第 13 トランジスター M13 の第 2 電極とデータ線 D<sub>j</sub> に接続される。そして、第 12 トランジスター M12 の第 1 電極は第 2 バッファー 281 に接続される。このような第 12 トランジスター M12 は第 2 制御信号 CS 2 によって 1 水平期間 1H の第 1 期間の間ターンオンされて第 2 期間の間ターンオフされる。

40

#### 【0091】

第 13 トランジスター M13 のゲート電極は、第 12 トランジスター M12 のゲート電極に接続され、第 2 電極はデータ線 D<sub>j</sub> に接続される。そして、第 13 トランジスター M13 の第 1 電極は電流源 I<sub>max</sub> に接続される。このような第 13 トランジスター M13 は第 2 制御信号 CS 2 によって 1 水平期間 1H の第 1 期間の間ターンオンされて第 2 期間の間ターンオフされる。

#### 【0092】

50

電流源  $I_{max}$  は、画素 140 が最大輝度に発光される時、有機発光ダイオード OLE D に供給されるべき電流を第 12 トランジスター M12 及び第 13 トランジスター M13 がターンオンされる第 1 期間の間画素 140 から供給を受ける (Current Sink)。つまり、電流源  $I_{max}$  から電流をシンク (Sink、吸い込むとき) することになれば、電流は第 13 トランジスターを経由して  $I_{max}$  に供給される。ここで、第 12 トランジスターがターンオンため、シンクされる電流に対応して第 3 ノードに所定の補償電圧が印加される。すなわち、シンクされる電流に対応される電圧が第 3 ノードに印加されることになる。

#### 【0093】

第 3 キャパシタ C3 は、電流源  $I_{max}$  によって画素 140 から電流がシンクされる時、第 3 ノード N3 に印加される補償電圧を保存する。つまり、第 3 キャパシタ C3 は第 1 期間の間第 3 ノード N3 に印加される補償電圧を充電し、第 12 トランジスター M12 及び第 13 トランジスター M13 がターンオフされると、第 3 キャパシタ C3 は放電して、第 3 ノード N3 の電圧を一定に維持する。このように一定に維持された電圧 (N3 に現れている電圧) を補償電圧と称している。10

#### 【0094】

補償電圧は第 2 バッファー 281 に供給されてそこから第 3 ノード N3 に印加された補償電圧が電圧制御器 260j に供給される。したがって、電圧制御器 260j へは、第 12 トランジスター M12 及び第 13 トランジスター M13 のオン / オフにかかわらず常に補償電圧が供給されることになる。20

#### 【0095】

電圧制御器 260j は、補償電圧、第 2 データ Data2 及び第 3 電源 VSS の電圧の供給を受けてデータ信号 DS の電圧値を制御する。以後、説明の便宜性のために第 2 データ Data2 が 5 ビット (すなわち、 $p = 5$ ) に設定されると仮定する。

#### 【0096】

電圧制御器 260j は第 41 トランジスター M41 と第 1 バッファー 270j の間のラインと接続される 5 個 (すなわち、 $p$  個) の第 4 キャパシタ C、2C、4C、8C、16C と、第 4 キャパシタ C、2C、4C、8C、16C と第 3 バッファー 301 の間に接続される第 31 トランジスター M31、第 32 トランジスター M32、第 33 トランジスター M33、第 34 トランジスター M34 及び第 35 トランジスター M35 と、第 4 キャパシタ C、2C、4C、8C、16C と第 2 バッファー 281 の間に接続される第 21 トランジスター M21、第 22 トランジスター M22、第 23 トランジスター M23、第 24 トランジスター M24 及び第 25 トランジスター M25 を備える。30

#### 【0097】

そして、電圧制御器 260j は第 31 乃至第 35 トランジスター M31 乃至 M35 のゲート端子及び第 21 乃至第 25 トランジスター M21 乃至 M25 のゲート端子と基底電圧源 GND の間に接続される第 51 トランジスター M51、第 52 トランジスター M52、第 53 トランジスター M53、第 54 トランジスター M54 及び第 55 トランジスター M55 と、第 2 データ Data2 のビット数に対応して設置されて第 2 データ Data2 のビット値を第 21 トランジスター M21、第 22 トランジスター M22、第 23 トランジスター M23、第 24 トランジスター M24 及び第 25 トランジスター M25 のゲート端子に供給する第 61 トランジスター M61、第 62 トランジスター M62、第 63 トランジスター M63、第 64 トランジスター M64 及び第 65 トランジスター M65 を備える。40

#### 【0098】

第 4 キャパシタ C、2C、4C、8C、16C それぞれは互いに違う容量値に設定される。実際に、第 4 キャパシタ C、2C、4C、8C、16C 容量は、 $2^0$ 、 $2^1$ 、 $2^2$ 、 $2^3$ 、 $2^4$  のように二進数の加重値形態に増加される。すなわち、第 4 キャパシタ C、2C、4C、8C、16C は第 2 データ Data2 の加重値に対応して設定される。

#### 【0099】

10

20

30

40

50

第51トランジスターM51は第21トランジスターM21及び第35トランジスターM35のゲート端子に接続される。第52トランジスターM52は第22トランジスターM22及び第34トランジスターM34のゲート端子に接続される。第53トランジスターM53は第23トランジスターM23及び第33トランジスターM33のゲート端子に接続される。第54トランジスターM54は第24トランジスターM24及び第32トランジスターM32のゲート端子に接続される。第55トランジスターM55は第25トランジスターM25及び第31トランジスターM31のゲート端子に接続される。

#### 【0100】

このような第51乃至55トランジスターM51乃至M55は図10に図示された第4制御信号CS4によって水平期間の第1期間の間ターンオンされ、第2期間の間ターンオフされる。このために、第51乃至55トランジスターM51乃至M55はNMOSで形成される。10

#### 【0101】

第31乃至第35トランジスターM31乃至M35それぞれは第4キャパシタC、2C、4C、8C、16Cの中でいずれか一つと第3バッファー301の間に設置される。このような第31乃至第35トランジスターM31乃至M35は、第51乃至55トランジスターM51乃至M55がターンオンされる第1期間の間ターンオンされて第3電源VSSの電圧を第4キャパシタC、2C、4C、8C、16Cの一側端子に供給する。このために、第31乃至第35トランジスターM31乃至M35は第51乃至55トランジスターM51乃至M55と違う導電型であるPMOSで形成される。20

#### 【0102】

第61トランジスターM61は第2データData2の一番低い加重値を持つビットの供給を受けて第25トランジスターM25に供給する。この時、一番低い加重値を持つビットが「1」の値を持つ場合、第25トランジスターM25がターンオンされ、「0」の値を持つ場合第25トランジスターM25はターンオフされる。第62トランジスターM62は第2データData2で二番目に低い加重値を持つビットの供給を受けて第24トランジスターM24に供給する。第63トランジスターM63は第2データData2で三番目に低い加重値を持つビットの供給を受けて第23トランジスターM23に供給する。第64トランジスターM64は第2データData2で四番目に低い加重値を持つビットの供給を受けて第22トランジスターM22に供給する。第65トランジスターM65は第2データData2で一番高い加重値を持つビットの供給を受けて第21トランジスターM21に供給する。30

#### 【0103】

このような第61乃至第65トランジスターM61乃至M65は、PMOSで形成されて第4制御信号CS4によって制御される。すなわち、第61乃至第65トランジスターM61乃至M65は第1期間の間ターンオフされて、第2期間の間ターンオンされる。

#### 【0104】

第21乃至第25トランジスターM21乃至M25それぞれは、第4キャパシタC、2C、4C、8C、16Cの中でいずれか一つと第2バッファー281の間にNMOS導電型で設置される。このような第21乃至第25トランジスターM21乃至M25それぞれは、自分に「1」に対応されるビットが供給される時ターンオンされて第4キャパシタC、2C、4C、8C、16Cの一側端子で補償電圧を供給する。40

#### 【0105】

一方、第4キャパシタC、2C、4C、8C、16Cの中少なくとも一つの一側端子に補償電圧が印加されれば第41トランジスターM41と第1バッファー270jの間のラインに印加されたデータ信号DSの電圧値が増加または減少される（実際に、データ信号DSの電圧値の増加または減少は補償電圧の電圧値によって決まる）。ここで、データ信号DSの電圧値が補償電圧によって制御されるから画素140に含まれたトランジスターの移動度が補償されるようにデータ信号DSの電圧値が制御され、これによって画素部130で均一な画像を表示することができる。つまり、本発明のデータ駆動回路200は移50

動度などによって決まった補償電圧を利用してデータ信号 D S の電圧値を制御するからトランジスターの移動度のバラつき現象を補償することができる。

#### 【0106】

第 1 バッファー 270j は第 4 1 トランジスター M 4 1 と第 1 バッファー 270j の間のラインに印加されたデータ信号 D S をスイッチ手段 290j に伝達する。スイッチ手段 290j は第 1 1 トランジスター M 1 1 を備える。このような第 1 1 トランジスター M 1 1 は図 10 に図示された第 1 制御信号 C S 1 によって制御される。すなわち、第 1 1 トランジスター M 1 1 は 1 水平期間 1 H の第 2 期間の間ターンオンされて第 1 期間の間ターンオフされる。したがって、データ信号 D S は 1 水平期間 1 H 中第 2 期間の間データ線 D j に供給され、それ以外の期間の間には供給されない。

10

#### 【0107】

図 10 は、図 9 に図示されたスイッチ手段、電流シンク器、第 4 1 トランジスターおよび電圧制御器 260j に供給される駆動波形を表す図面である。

#### 【0108】

図 9 及び図 10 を結付して画素 140 に供給されるデータ信号 D S の電圧制御過程を詳しく説明する。

#### 【0109】

まず、第 n - 1 走査線 S n - 1 に走査信号が供給される。第 n - 1 走査線 S n - 1 に走査信号が供給されれば、第 3 トランジスター M 3 及び第 5 トランジスター M 5 がターンオンされる。すると、第 2 ノード N 2 には第 1 電源 E L V D D から第 4 トランジスター M 4 の閾値電圧を差し引いた電圧値が印加され、第 1 ノード N 1 には基準電源 V ref の電圧が印加される。この時、第 2 キャパシタ C 2 には第 1 電源 E L V D D の電圧降下電圧及び第 4 トランジスター M 4 の閾値電圧に対応さ

20

実際に、第 1 ノード N 1 及び第 2 ノード N 2 それぞれに印加される電圧は、下記(数 1)式のように表現することができる。

#### 【0110】

#### 【数 1】

$$V_{N1} = V_{ref} \quad V_{N2} = ELVDD - |V_{thM4}|$$

30

#### 【0111】

(数 1) 式で、V N 1 は第 1 ノード N 1 に印加される電圧、V N 2 は第 2 ノード N 2 に印加される電圧、V th M 4 は第 4 トランジスター M 4 の閾値電圧を表す。

#### 【0112】

一方、第 n - 1 走査線 S n - 1 に供給される走査信号がオフされる時点と第 n 走査線 S n に走査信号が供給される時点の間の期間の間第 1 ノード N 1 及び第 2 ノード N 2 は、フローティング状態に設定される。したがって、第 2 キャパシタ C 2 に充電される電圧値は変化されない。

#### 【0113】

以後、第 n 走査線 S n に走査信号が供給されて第 1 トランジスター M 1 及び第 2 トランジスター M 2 がターンオンされる。そして、第 n 走査線 S n に走査信号が供給される期間中第 1 期間の間第 1 2 トランジスター M 1 2 及び第 1 3 トランジスター M 1 3 がターンオンされる。第 1 2 トランジスター M 1 2 及び第 1 3 トランジスター M 1 3 がターンオンされれば第 1 電源 E L V D D 、第 4 トランジスター M 4 、第 2 トランジスター M 2 、データ線 D j 及び第 1 3 トランジスター M 1 3 を経由して電流源 I max に対応される電流がシンクされる。

40

#### 【0114】

この時、第 4 トランジスター M 4 には電流源 I max の電流が流れるから(数 2)式のように表現することができる。

#### 【0115】

50

【数2】

$$Imax = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2$$

【0116】

(数2)式で、 $\mu$ は移動度を表し、 $C_{ox}$ は酸化層の容量、 $W$ はチャンネルの幅、 $L$ はチャンネルの長さを表す。

【0117】

(数2)式のような電流が第4トランジスターM4に流れる時第2ノードN2に印加される電圧は(数3)式のように表現することができる。 10

【0118】

【数3】

$$V_{N2} = ELVDD - \sqrt{\frac{2Imax}{\mu_p C_{ox}} \frac{L}{W} - |V_{thM4}|}$$

【0119】

そして、第2キャパシタC2のカップリングによって第1ノードN1に印加される電圧は、(数4)式のように表現することができる。 20

【0120】

【数4】

$$V_{N1} = Vref - \sqrt{\frac{2Imax}{\mu_p C_{ox}} \frac{L}{W}} = V_{N3}$$

【0121】

ここで、第1ノードN1に印加される電圧VN1は、理想的に第3ノードN3に印加される電圧VN3及び第4ノードN4に印加される電圧VN3と同じく設定される。すなわち、電流源Imaxによって電流がシンクされる時第4ノードN4には(数4)のような電圧が印加される。 30

【0122】

一方、(数4)式に図示されたように第3ノードN3及び第4ノードN4に印加される電圧は、現在電流がシンクされる画素140に含まれたトランジスターの移動度などの影響を受けるようになる。したがって、電流源Imaxによって電流がシンクされる時第3ノードN3に印加される電圧値は、それぞれの画素140ごとに相異なるよう決まる(移動度が相異なる場合)。 40

【0123】

一方、水平期間の第1期間中DAC250jでは、第1データData1に対応してf(fは自然数)個の階調電圧の中、h(hはf以下の自然数)番目階調電圧を選択する。そして、DAC250jは第41トランジスターM41がターンオンされる期間の間選択された階調電圧をデータ信号DSとして第41トランジスターM41と第1バッファー270jの間のラインに供給する。

【0124】

ここで、第41トランジスターM41と第1バッファー270jの間のラインの間の電圧VLは、(数5)式のように表現することができる。

【0125】

【数5】

$$V_L = V_{ref} - \frac{h}{f} (V_{ref} - VSS)$$

【0126】

一方、第4制御信号CS4によって水平期間の第1期間の間第51トランジスターM51乃至第55トランジスターM55がターンオンされて基底電圧源GNDの電圧が第31トランジスターM31乃至第35トランジスターM35のゲート電極に供給される。すると、第31トランジスターM31乃至第35トランジスターM35がターンオンされて第4キャパシタC、2C、4C、8C、16Cの一側端子が第3電源VSSの電圧値に設定される。10

【0127】

一方、第51トランジスターM51乃至第55トランジスターM55は基底電圧源GNDのみならずPMOSである31トランジスターM31乃至第35トランジスターM35がターンオンされる電圧と接続されうる。

【0128】

そして、第3電源VSSの電圧値は基準電源Vrefの電圧値より低い電圧、例えば、画素部130に含まれた画素140から生成される補償電圧の平均電圧に設定されうる。

【0129】

第4キャパシタC、2C、4C、8C、16Cの一側端子が第3電源VSSの電圧値に設定された後、水平期間の第2期間の間第61トランジスターM61乃至第65トランジスターM65がターンオンされる。第61トランジスターM61乃至第65トランジスターM65がターンオンされると第2データData2の各ビットが第21トランジスターM21、第22トランジスターM22、第23トランジスターM23、第24トランジスターM24及び第25トランジスターM25に供給される。20

【0130】

例えば、第2データData2のビットが「00011」に設定されると第61トランジスターM61乃至第65トランジスターM65がターンオンされる第2期間の間第24トランジスター及び第25トランジスターM25がターンオンされる。すると、一番目第4キャパシタC及び二番目第4キャパシタ2Cの一側端子に補償電圧が印加される。この場合、一番目第4キャパシタC及び二番目第4キャパシタ2Cの一側端子に補償電圧が印加されるので(数6)式のように表現することができる。30

【0131】

【数6】

$$\frac{C+2C}{C+2C+4C+8C+16C} \equiv \frac{h}{f}$$

【0132】

ここで、第2データData2は、第1データData1の加重値を変更して生成されるから(数6)式の値はおおよそh/fに表現することができる。40

【0133】

一方、数式第4キャパシタC、2C、4C、8C、16Cの中、少なくとも一つに補償電圧が印加されれば、第41トランジスターM41と第1バッファ-270の間のラインの間の電圧VLは(数7)式のように表現することができる。

【0134】

【数7】

$$V_L = V_{ref} - \frac{h}{f} (V_{ref} - VSS) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - VSS)$$

$$= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3})$$

$$= V_{ref} - \frac{h}{f} \sqrt{\frac{2Imax}{\mu_p C_{OX}}} \frac{L}{W}$$

10

【0135】

(数7)式のような電圧は、第1バッファー270jを経由して第11トランジスターM11に供給される。ここで、第2期間の間第11トランジスターM11がターンオンされるため、第1バッファー270jに供給された電圧は、第11トランジスターM11、データ線Dj及び第1トランジスターM1を経由して第1ノードN1に供給される。

【0136】

すなわち、第1ノードN1には数式7のような電圧が供給される。そして、第2キャパシタC2のカップリングによって第2ノードN2に印加される電圧は(数8)式のように表現することができる。

20

【0137】

【数8】

$$V_{N2} = ELVDD - \frac{h}{f} \sqrt{\frac{2Imax}{\mu_p C_{OX}}} \frac{L}{W} - |V_{thM4}|$$

30

【0138】

この時、第4トランジスターM4を経由して流れる電流は、(数9)式のように表すことができる。

【0139】

【数9】

$$I_{N4} = \frac{1}{2} \mu_p C_{OX} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2$$

$$= \frac{1}{2} \mu_p C_{OX} \frac{W}{L} \left( ELVDD - \left( ELVDD - \frac{h}{f} \sqrt{\frac{2Imax}{\mu_p C_{OX}}} \frac{L}{W} - |V_{thM4}| \right) - |V_{thM4}| \right)^2$$

40

$$= \left( \frac{h}{f} \right)^2 Imax$$

【0140】

(数9)式を参照すれば、本発明で第4トランジスターM4に流れる電流は、データ信号DSによって決まる。すなわち、本発明では第4トランジスターM4の閾値電圧、移動度などと無関係にデータ信号DSによって決まった電流が第4トランジスターM4に流れることができ、これによって均一な画像を表示することができる。

50

## 【0141】

一方、本発明でスイッチ手段 290j の構成は多様に設定することができる。例えば、スイッチ手段 290j は、図 11 のように第 11 トランジスター M11 及び第 14 トランジスター M14 をトランスマッシュゲート (Transmission Gate) 形態で接続することができる。PMOS タイプに形成された第 14 トランジスター M14 は、第 2 制御信号 CS2 の供給を受け、NMOS タイプに形成された第 11 トランジスター M11 は、第 1 制御信号 CS1 の供給を受ける。ここで、第 1 制御信号 CS1 及び第 2 制御信号 CS2 は、互いに反対の極性を持つから第 11 トランジスター M11 及び第 14 トランジスター M14 は同じ時間にターンオン及びターンオフされる。

## 【0142】

10

一方、第 11 トランジスター M11 及び第 14 トランジスター M14 がトランスマッシュゲート形態で接続されれば、電圧 - 電流特性曲線がおよそ直線形態に設定されるからスイッチングエラーを最小化することができる。

## 【0143】

図 12 は、図 6 に図示されたガンマ電圧部、DAC、デコーダ、電圧制御器、スイッチ手段、電流シンク器及び画素連結関係の他の例を表す図面である。図 12 では説明の便宜性のために j 番目チャンネルを図示し、データ線 D<sub>j</sub> が図 5 に図示された画素 140 と接続されると仮定する。

## 【0144】

20

図 10 及び図 12 を参照して動作過程を説明すれば、まず、第 n - 1 走査線 S<sub>n - 1</sub> で走査信号が供給される時第 1 ノード N1 及び第 2 ノード N2 には数式 1 に記載された電圧が印加される。

## 【0145】

そして、第 n 走査線 S<sub>n</sub> に走査信号が供給され、第 12 トランジスター M12 及び第 13 トランジスター M13 がターンオンされる第 1 期間の間第 4 トランジスター M4 に流れる電流は、(数 2) 式のように表現され、第 2 ノード N2 に印加される電圧は(数 3) 式のように表現される。

## 【0146】

そして、第 2 キャパシタ C2 のカップリングによって第 1 ノード N1 に印加される電圧は(数 10)式のように表現することができる。

30

## 【0147】

## 【数 10】

$$V_{M1} = V_{ref} \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2I_{max}}{\mu_p C_{ox}}} \frac{L}{W} = V_{N3}$$

## 【0148】

一方、水平期間の第 1 期間中 DAC250j では、第 1 データ Data1 に対応して f (f は自然数) 個の階調電圧の中、h (h は f 以下の自然数) 番目階調電圧を選択する。そして、DAC250j は第 41 トランジスター M41 がターンオンされる期間の間選択された階調電圧をデータ信号 DS として第 41 トランジスター M41 と第 1 バッファ 270 の間のラインに(数 5)式のような電圧を印加する。

40

## 【0149】

一方、水平期間の第 1 期間の間には第 51 乃至第 55 トランジスター M51 乃至 M55 がターンオンされ、これによって第 31 乃至第 35 トランジスター M31 乃至 M35 がターンオンされる。すると、第 1 期間の間第 4 キャパシタ C2C、4C、8C、16C の一側端子には第 3 電源 VSS の電圧が印加される。

## 【0150】

そして、水平期間の第 2 期間の間第 61 乃至第 65 トランジスター M61 乃至 M65 が

50

ターンオンされる。第61乃至第65トランジスターM61乃至M65がターンオンされると第2データData2のビット値に対応して第21トランジスターM21、第22トランジスターM22、第23トランジスターM23、第24トランジスターM24及び第25トランジスターM25がターンオンまたはターンオフされる。この時、第41トランジスターM41と第1バッファ-270の間のラインの間の電圧VLは(数11)式のように表現することができる。

【0151】

【数11】

$$V_L = V_{ref} - \frac{h}{f} (V_{ref} - V_{SS}) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - V_{SS}) \quad 10$$

$$= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3})$$

$$= V_{ref} - \frac{h}{f} \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W}$$

20

【0152】

(数11)式のような電圧は、第1バッファ-270jを経由して第11トランジスターM11に供給される。ここで、第2期間の間第11トランジスターM11がターンオンされるため、第1バッファ-270jに供給された電圧は、第11トランジスターM11、データ線Dj及び第1トランジスターM1を経由して第1ノードN1に供給される。すなわち、第1ノードN1には(数11)式のような電圧が供給される。

【0153】

そして、第2キャパシタC2のカップリングによって第2ノードN2に印加される電圧は(数8)式のように表現することができる。したがって、第4トランジスターM4を経由して流れる電流は(数9)式のように表すことができる。すなわち、本発明で第4トランジスターM4を経由して発光素子OLEDに供給される電流は、第4トランジスターM4の閾値電圧、移動度などと無関係にデータ信号DSによって決まるから均一な画像を表示することができる。

30

【0154】

一方、図5に図示されたような画素140は、第1ノードN1の電圧が大きく変わっても第2ノードN2の電圧が鈍感に変化される(すなわち、C1+C2/C2)。したがって、図5に図示された画素140が適用されれば、図3に図示された画素140が適用される場合よりガンマ電圧部300の電圧範囲を広く設定することができる。このように、ガンマ電圧部300の電圧範囲が広く設定されれば第11トランジスターM11及び第1トランジスターM1などのスイッチングエラーによる影響を減らすことができるという長所がある。

40

【0155】

本発明は添付された図面に図示された実施形態を参照して説明されたが、これは例示的なものに過ぎず、当該技術分野における通常の知識を有する者であれば、多様な変形及び均等な他の実施形態が可能であるということを理解することができる。

【図面の簡単な説明】

【0156】

【図1】従来の発光表示装置を表す図面である。

【図2】本発明の実施形態による発光表示装置を表す図面である。

【図3】図2に図示された画素の一例を表す回路図である。

50

【図4】図3に図示された画素の駆動方法を表す波形図である。

【図5】図2に図示された画素の他の例を表す回路図である。

【図6】図2に図示されたデータ駆動回路の第1実施形態を表すブロック図である。

【図7】図2に図示されたデータ駆動回路の第2実施形態を表すブロック図である。

【図8】図2に図示されたデータ駆動回路の第2実施形態を表すブロック図である。

【図9】図6に図示されたガンマ電圧部、デジタル-アナログ変換器、スイッチ手段、電圧制御器、電流シンク器及び画素の連結関係を表す図面である。

【図10】図9に図示された制御信号の駆動波形を表す波形図である。

【図11】図9に図示されたスイッチ手段の他の例を表す図面である。

【図12】図6に図示されたガンマ電圧部、デジタル-アナログ変換器、スイッチ手段、電圧制御器、電流シンク器及び画素連結関係の他の例を表す図面である。 10

【符号の説明】

【0157】

110 … 走査駆動部、

120 … データ駆動部、

130 … 画素部、

140 … 画素、

142 … 画素回路、

150 … タイミング制御部、

200 … データ駆動回路、

210 … シフトレジスター部、

220 … サンプリングラッチ部、

230 … ホルディングラッチ部、

240 … デコーダ、

250 … デジタル-アナログ変換部、

260 … 電圧制御部、

270 … バッファー部、

280 … 電流供給部、

290 … 選択部、

300 … ガンマ電圧部、

310 … レベルシフター部。 30

20

30

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

---

フロントページの続き

(51)Int.Cl.

F I

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 4 1 Q |

| G 09 G | 3/20 | 6 2 3 R |

| G 09 G | 3/20 | 6 2 3 H |

| G 09 G | 3/20 | 6 2 3 L |

(72)発明者 鄭 寶 容

大韓民国ソウル特別市松坡区可樂2洞173-19

(72)発明者 柳 道 享

大韓民国京畿道水原市八達区靈通洞1028-2, 303

(72)発明者 権 五 敬

大韓民国ソウル特別市松坡区7新川洞 薔薇アパート14-1102

審査官 福村 拓

(56)参考文献 特開2004-004675 (JP, A)

特開2003-058106 (JP, A)

特開2004-192000 (JP, A)

特表2007-536585 (JP, A)

特開2003-043993 (JP, A)

特開2003-140613 (JP, A)

特開2004-125852 (JP, A)

特開2004-287345 (JP, A)

特開2003-295828 (JP, A)

特開2004-145197 (JP, A)

特開2002-311898 (JP, A)

特開平10-254410 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3 0

G 09 G 3 / 2 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 数据驱动电路和使用其的有机发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP4890917B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2012-03-07 |

| 申请号            | JP2006105041                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2006-04-06 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社<br>学校法人汉阳大学产学合作局                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 三星移动显示的股票会社<br>汉阳大学校产学协力团                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 鄭寶容<br>柳道享<br>權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 鄭寶容<br>柳道享<br>權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3233 G09G3/3291 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0251<br>G09G2310/0262 G09G2310/027 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.623.G G09G3/20.623.F G09G3/20.641.Q<br>G09G3/20.623.R G09G3/20.623.H G09G3/20.623.L G09G3/20.642.P G09G3/3233 G09G3/3266<br>G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-Term分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380<br>/AA01 5C380/AB06 5C380/AB34 5C380/BA05 5C380/BA20 5C380/BA24 5C380/BA28 5C380/BA32<br>5C380/BA38 5C380/BA39 5C380/BB03 5C380/BC03 5C380/BC14 5C380/CA04 5C380/CA08 5C380<br>/CA12 5C380/CA13 5C380/CA16 5C380/CA17 5C380/CA22 5C380/CA26 5C380/CA33 5C380/CA49<br>5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CC03 5C380/CC05 5C380<br>/CC08 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC55 5C380/CC61 5C380/CC64<br>5C380/CD026 5C380/CE05 5C380/CE07 5C380/CF07 5C380/CF09 5C380/CF22 5C380/CF24 5C380<br>/CF41 5C380/CF43 5C380/CF48 5C380/CF64 5C380/DA02 5C380/DA06 5C380/EA01 |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 优先权            | 1020050070439 2005-08-01 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | JP2007041523A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

提供了一种能够显示具有均匀亮度的图像的数据驱动电路和使用该数据驱动电路的发光显示装置。解决方案：半导体存储器件包括至少一个解码器240，用于使用外部提供的k ( k是自然数 ) 位的第一数据产生p ( p是自然数 ) 位的第二数据，用于存储两个数据的锁存单元220和230，用于产生多个灰度电压的伽马电压单元300，用于使用第一数据选择灰度电压之一的至少一个电压选择单元使用补偿电压和对应于在水平周期的第一周期期间从像素提供的预定电流产生的第二数据来控制数字 - 模拟转换单元250和数据信号的电压值。电压控制单元260和选择单元290，用于向像素提供数据信号，该数据信号的电压值在除水平周期期间的第一周期之外的第二周期期间被控制。点域6

$$V_{\text{M}} = V^{\text{ref}} \quad V_{\text{M}} = E_{\text{LVD}} \cdot |V_{\text{M}}|$$