(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-9185

(P2016-9185A)

(43) 公開日 平成28年1月18日(2016.1.18)

|                  |                  |                             |

|------------------|------------------|-----------------------------|

| (51) Int.Cl.     | F 1              | テーマコード (参考)                 |

| <b>G09G 3/30</b> | <b>(2006.01)</b> | <b>G09G 3/30</b> J 5C080    |

| <b>G09G 3/20</b> | <b>(2006.01)</b> | <b>G09G 3/20</b> 611H 5C380 |

|                  |                  | <b>G09G 3/20</b> 642A       |

|                  |                  | <b>G09G 3/20</b> 624B       |

|                  |                  | <b>G09G 3/20</b> 623C       |

審査請求 有 請求項の数 6 O L (全 19 頁) 最終頁に続く

(21) 出願番号 特願2014-256831 (P2014-256831)

(22) 出願日 平成26年12月19日 (2014.12.19)

(31) 優先権主張番号 10-2014-0079255

(32) 優先日 平成26年6月26日 (2014.6.26)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー ディスプレイカンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

ウィーテロ 128

(74) 代理人 100109726

弁理士 園田 吉隆

(74) 代理人 100101199

弁理士 小林 義教

(72) 発明者 キム、テガン

大韓民国 413-837, キョンギド

, パジュシ, ヤダンドン, ハンビット

マウル 2 ダンジ ヒューマンビル

レイク パレス アパートメント, 2

01-2304

最終頁に続く

(54) 【発明の名称】駆動素子の電気的特性の偏差を補償することができる有機発光表示装置

## (57) 【要約】

【課題】駆動素子の電気的特性の偏差をセンシングするあたり、センシング時間を削減し、センシングの精度を向上させるようにした、有機発光表示装置を提供する。

【解決手段】本発明に係る有機発光表示装置は、画素が備えた表示パネルと、センシング駆動時、1ラインセンシングオンタイムに対応するセンシング用ゲートパルスを生成した後、行順次方式で、ゲートラインに順次供給するゲート駆動回路と、前記センシング駆動時、前記1ラインセンシングオンタイム内で、センシングラインを介して入力される前記画素のそれぞれの、駆動TFTのソースドレイン間の電流を積分する複数の電流積分器と、前記電流積分器の出力を順次デジタル処理して、デジタルセンシング値を出力するADCを含むデータ駆動回路と、前記ゲート駆動回路と、前記データ駆動回路の動作を制御するタイミングコントローラとを備える。

【選択図】図6

**【特許請求の範囲】**

**【請求項 1】**

OLED、当該OLEDの発光量を制御する駆動TFT、をそれぞれ含み、

データラインの内のいずれか一つ、ゲートラインの内のいずれか一つ、及びセンシングラインの内のいずれか一つ、にそれぞれ接続された複数の画素が形成された表示パネルと、

センシング駆動時、1ラインセンシングオンタイムに対応するセンシング用ゲートパルスを生成した後、行順次方式で前記ゲートラインに順次供給するゲート駆動回路と、

前記センシング駆動時、前記1ラインセンシングオンタイム内で、センシング用のデータ電圧を生成して、前記データラインに供給する複数のDACと、前記センシングラインを介して入力される前記画素のそれぞれの駆動TFTのソースドレイン間の電流を積分する複数の電流積分器と、前記電流積分器の出力を順次デジタル処理してデジタルセンシング値を出力するADCを含むデータ駆動回路と、

前記ゲート駆動回路と、前記データ駆動回路の動作を制御して、前記1ラインセンシングオンタイム内で、第1レベルの前記センシング用データ電圧による第1ソースドレイン電流値を積分した後、第2レベルの前記センシング用データ電圧による第2ソースードレイン電流値を積分するタイミングコントローラを備えることを特徴とする有機発光表示装置。

**【請求項 2】**

前記第1レベルは、全体の階調区間ににおいて、所定範囲の低階調電流値と所定範囲の高階調電流値のいずれか1つに対応する電圧の大きさで入力され、

前記第2レベルは、前記全体の階調区間ににおいて、前記所定範囲の低階調電流値と前記所定範囲の高階調電流値の残りの一つに対応する電圧の大きさで入力されることを特徴とする、請求項1に記載の有機発光表示装置。

**【請求項 3】**

前記タイミングコントローラは、前記ゲート駆動回路の動作を制御して、前記センシング用ゲートパルスのオンパルス区間が、前記1ラインセンシングオンタイム内に2つ以上含まれるように、前記センシング用ゲートパルスをマルチパルスの形で生成することを特徴とする、請求項1に記載の有機発光表示装置。

**【請求項 4】**

前記タイミングコントローラは、前記センシング用データ電圧の大きさに応じて、前記第1及び第2センシング&サンプリング期間でのセンシング期間を互いに異なるように制御し、前記センシング期間は、前記センシング用データ電圧の大きさに反比例するように調整されることを特徴とする、請求項1に記載の有機発光表示装置。

**【請求項 5】**

前記電流積分器に含まれる積分キャパシターの静電容量を調整するための静電容量制御部をさらに含み、

前記積分キャパシターは、アンプの反転入力端に並列接続された複数のキャパシターを含み、前記キャパシターのそれぞれの他端は、互いに異なる静電容量調整用スイッチを介して、前記アンプの出力端に接続され、

前記タイミングコントローラは、前記ADCから入力される前記デジタルセンシング値に対する分析結果に基づいて、前記静電容量制御部の動作を制御して、前記静電容量調整用スイッチをオン/オフさせるためのスイッチング制御信号を生成することを特徴とする、請求項1に記載の有機発光表示装置。

**【請求項 6】**

前記ADCの入力電圧範囲を決定する、ADCの基準電圧を調整するためのプログラマブル電圧調整ICをさらに含み、

前記タイミングコントローラは、前記デジタルセンシング値に対する分析結果に基づいて、前記プログラマブル電圧調整ICの動作を制御して、前記ADCの基準電圧を調整することを特徴とする、請求項1に記載の有機発光表示装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、有機発光表示装置に関し、特に、駆動素子の電気的特性の偏差を補償することができる有機発光表示装置に関する。

**【背景技術】****【0002】**

アクティブマトリクス型の有機発光表示装置は、自ら発光する有機発光ダイオード(Or-

ganic Light Emitting Diode: 以下、「OLED」という)を含み、応答速度が速く、発

光効率、輝度、及び視野角が大きいという利点がある。

10

**【0003】**

自発光素子であるOLEDは、アノード電極及びカソード電極と、これらの間に形成された有機化合物層(HIL、HTL、EML、ETL、EIL)を含む。有機化合物層は、正孔注入層(Hole Injection layer、HIL)、正孔輸送層(Hole transport layer、HTL)、発光層(Emission layer、EML)、電子輸送層(Electron transport layer、ETL)及び電子注入層(Electron Injection layer、EIL)からなる。アノード電極とカソード電極に駆動電圧が印加されると、正孔輸送層(HTL)を通過した正孔と電子輸送層(ETL)を通過した電子が発光層(EML)に移動して励起子を形成し、その結果、発光層(EML)が可視光を発生する。

**【0004】**

有機発光表示装置は、OLEDをそれぞれ含む画素をマトリックス形態に配列し、ビデオデータの階調に応じて画素の輝度を調節する。画素それぞれは、自身のゲート電極とソース電極との間にかかる電圧(Vgs)に応じて、OLEDに流れる駆動電流を制御する駆動素子、すなわち、駆動TFT(Thin Film Transistor)を含む。しきい値電圧、移動度などの駆動TFTの電気的特性は、駆動時間の経過に応じて劣化して、画素ごとに偏差が生じことがある。駆動TFTの電気的特性が画素ごとに変われば、同じビデオデータに対して画素間の輝度が変化するため、所望する画像実現が難しい。

20

**【0005】**

駆動TFTの電気的特性の偏差を補償するために、内部補償方式と外部補償方式が知られている。内部補償方式は、駆動TFT間のしきい値電圧偏差を画素回路内部で自動的に補償する。内部補償のためにはOLEDに流れる駆動電流が、駆動TFTのしきい値電圧に関係なく決定されるようにしなければならぬので、画素回路の構成が非常に複雑である。さらに、内部補償方式は、駆動TFT間の移動度偏差を補償するには不適合である。

30

**【0006】**

外部補償方式は、駆動TFTの電気的特性(しきい値電圧、移動度)に対応するセンシング電圧を測定し、このセンシング電圧に基づいて、外部回路でビデオデータを変調することにより、電気的特性の偏差を補償する。最近では、このような外部補償方式の研究が盛んに行われている。

**【0007】**

従来の外部補償方式において、データ駆動回路は、センシングラインを介して各画素からセンシング電圧を直接入力し、このセンシング電圧をデジタルセンシング値に変換した後、タイミングコントローラに伝送する。タイミングコントローラは、デジタルセンシング値に基づいて、デジタルビデオデータを変調して、駆動TFTの電気的特性の偏差を補償する。

40

**【0008】**

駆動TFTは電流素子であるため、その電気的特性は、一定のゲートソース間電圧(Vgs)に応じて、ドレインソース間に流れる電流(IdS)の大きさに代弁される。ところが、従来の外部補償方式のデータ駆動回路は、駆動TFTの電気的特性をセンシングするために、駆動TFTに流れる電流(IdS)を直接センシングするのではなく、その電流(IdS)に対応する電圧値をセンシングする。

50

## 【0009】

例えば、本願出願人により出願された出願番号第10-2013-0134256号、第10-2013-0149395号などにより提案された外部補償方式では、駆動TFTをソースフォロワー(Source Follower)方式で動作させた後、センシングラインのキャパシター(寄生キャパシター)に貯蔵される電圧(駆動TFTのソース電圧)をデータ駆動回路でセンシングする。この外部補償方式は、駆動TFTのしきい値電圧偏差を補償するために、ソースフォロワー(Source Follower)方式で動作される駆動TFT(DT)のソース電極電位がセチュレーション(saturation state)されるとき、(つまり、駆動TFT(DT)の電流( $I_{ds}$ )がゼロになる時)のソース電圧をセンシングする。そして、この外部補償方式は、駆動TFTの移動度の偏差を補償するために、ソースフォロワー(Source Follower)方式で動作される駆動TFT(DT)のソース電極電位がセチュレーション状態に到達する前の線形状態の値をセンシングする。

10

## 【0010】

このような従来の外部補償方式には、以下のような問題がある。

## 【0011】

第一に、従来の外部補償方式は、駆動TFTに流れる電流をセンシングラインの寄生キャパシターを用いて、ソース電圧に変更して記憶した後、このソース電圧をセンシングする。このとき、センシングラインの寄生容量は相対的に大きく、さらに表示パネルの表示負荷に応じて、寄生容量の大きさが変動することがある。このように電流が蓄積される寄生容量の大きさがセンシングラインの間に変わると、正確なセンシング値の獲得が難しい。

20

## 【0012】

第二に、従来の外部補償方式は、電圧センシング方式をとるので、駆動TFTのソース電圧がセチュレーションされるまでに多くの時間がかかるなど、センシング値取得にかかる時間が非常に長い。特に、センシングラインの寄生容量が大きい場合は、センシング可能な電圧レベルに電流を流すために多くの時間がかかり、このような問題は、低階調センシングにおいてさらに悪化する。

20

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0013】

したがって、本発明の目的は、駆動素子の電気的特性の偏差をセンシングするにあたり、センシング時間を削減し、センシングの精度を向上させる、有機発光表示装置を提供することにある。

30

## 【課題を解決するための手段】

## 【0014】

前記目的を達成するために、本発明の実施の形態に係る有機発光表示装置は、OLED、当該OLEDの発光量を制御する駆動TFTをそれぞれ含み、データラインのいずれか一つと、ゲートラインのいずれか一つ、及びセンシングラインのいずれか一つに、それぞれ接続された複数の画素が形成された表示パネルと、センシング駆動時、1ラインセンシングオンタイムに対応するセンシング用ゲートパルスを生成した後、行順次方式で、前記ゲートラインに順次供給するゲート駆動回路と、前記センシング駆動時、前記1ラインセンシングオンタイム内で、センシング用データ電圧を生成して、前記データラインに供給する複数のDACと、前記センシングラインを介して入力される、前記画素のそれぞれの駆動TFTのソースードライン間の電流を積分する複数の電流積分器と、前記電流積分器の出力を順次デジタル処理して、デジタルセンシング値を出力するADCを含むデータ駆動回路と、前記ゲート駆動回路と前記データ駆動回路の動作を制御して、前記1ラインセンシングオンタイム内で、第1レベルの前記センシング用データ電圧による第1ソースードライン電流値を積分した後、第2レベルの前記センシング用データ電圧による第2ソースードライン電流値を積分するタイミングコントローラを備える。

40

## 【0015】

50

前記第1レベルは、全体の階調区間で所定範囲の低階調電流値と所定範囲の高階調電流値のいずれか1つに対応する電圧の大きさで入力され、前記第2レベルは、前記すべての階調区間で前記所定範囲の低階調電流値と前記所定範囲の高階調電流値の残りの一つに対応する電圧の大きさで入力される。

#### 【0016】

前記タイミングコントローラは、前記ゲート駆動回路の動作を制御して、前記センシング用ゲートパルスのオンパルス区間が、前記1ラインセンシングオンタイム内に2つ以上含まれるように、前記センシング用ゲートパルスをマルチパルスの形で生成する。

前記タイミングコントローラは、前記センシング用データ電圧の大きさに応じて、前記第1及び第2センシング&サンプリング期間でのセンシング期間を互いに異なるように制御し、前記センシング期間は、前記センシング用データ電圧の大きさに反比例するように調整される。

10

#### 【0017】

前記電流積分器に含まれた積分キャパシターの静電容量(capacitance)を調整するための静電容量制御部をさらに含み、前記積分キャパシターは、アンプの反転入力端に並列接続された複数のキャパシターを含み、前記キャパシターのそれぞれの他端は、互いに異なる容量調整用スイッチを介して前記アンプの出力端子に接続され、前記タイミングコントローラは、前記ADCから入力される前記デジタルセンシング値に対する分析結果に基づいて、前記静電容量制御部の動作を制御して、前記静電容量調整用スイッチをオン/オフさせるためのスイッチング制御信号を生成する。

20

#### 【0018】

前記ADCの入力電圧範囲を決定する、ADCの基準電圧を調整するためのプログラマブル電圧調整ICをさらに含み、前記タイミングコントローラは、前記デジタルセンシング値に対する分析結果に基づいて、前記プログラマブル電圧調整ICの動作を制御して、前記ADCの基準電圧を調整する。

#### 【発明の効果】

#### 【0019】

本発明は、駆動素子の電気的特性の偏差をセンシングするにあたり、電流積分器を用いた電流センシング方式を介して、低電流及び高速センシングを実現して、センシング時間を大幅に減らすことができる。さらに、本発明は、1ラインセンシングオンタイム内で、画素のそれについて、マルチタイムセンシングを実行して、センシングの精度を大幅に向かせることができる。

30

#### 【図面の簡単な説明】

#### 【0020】

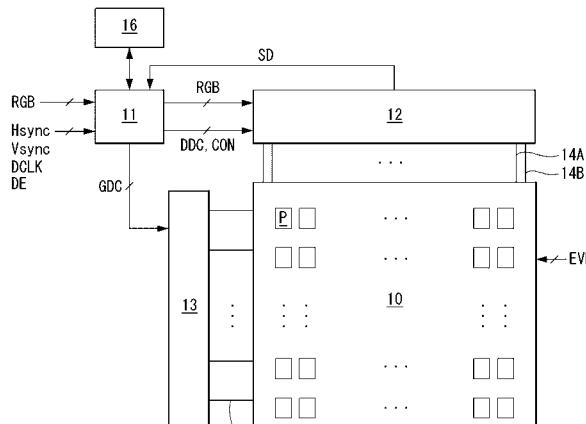

【図1】本発明の実施の形態に係る有機発光表示装置を示す図である。

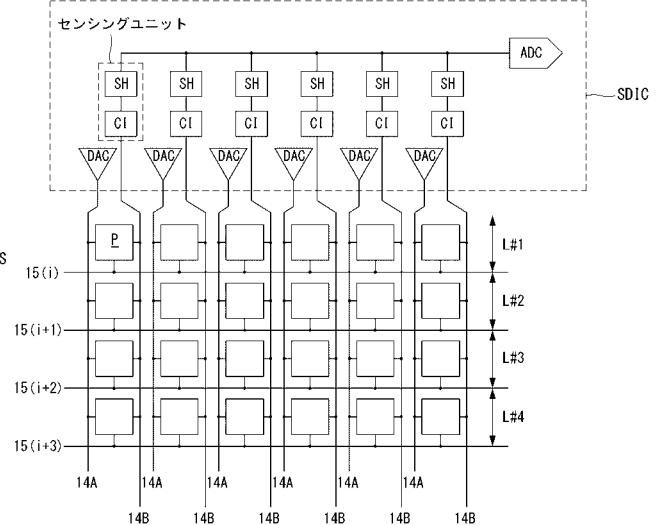

【図2】図1の表示パネルに形成された画素アレイと、電流センシング方式を実現するためのデータドライバICの構成を示す図である。

30

【図3】本発明の電流センシング方式が適用される画素とセンシングユニットの接続構造、及びセンシング原理を示す図である。

40

【図4】本発明の電流センシング方式が適用される画素とセンシングユニットの接続構造、及びセンシング原理を示す図である。

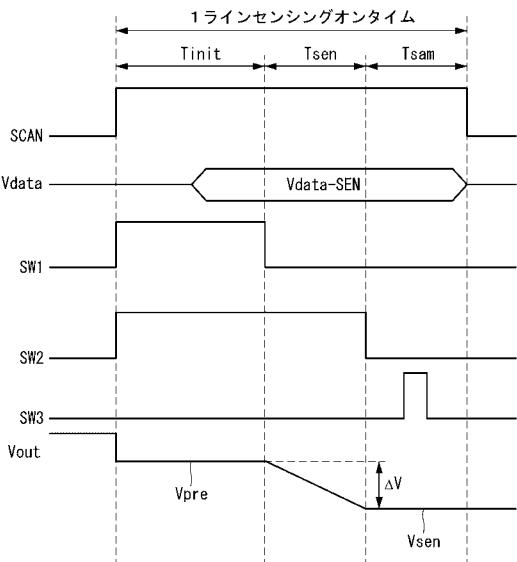

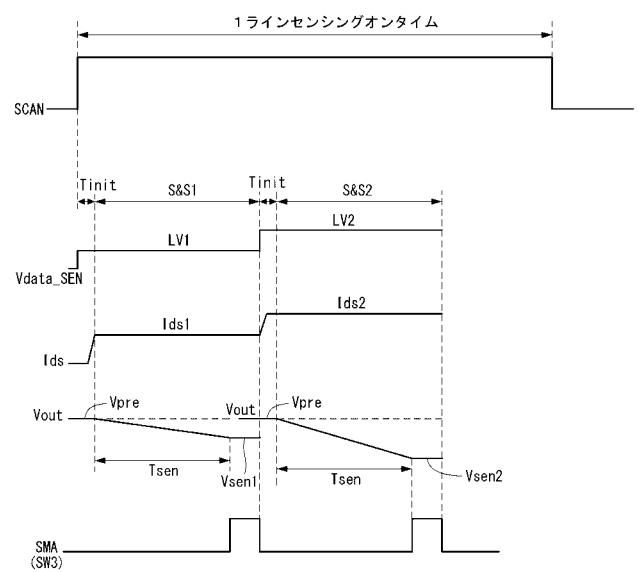

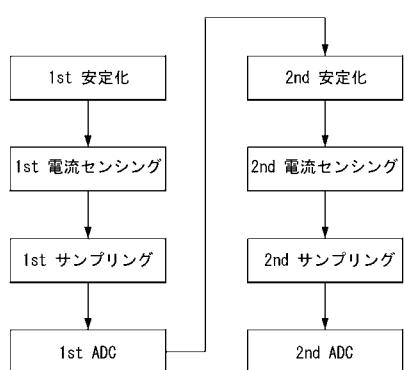

【図5】センシング性能向上のために、本発明で提案するマルチタイム電流センシング方式の一駆動波形及び駆動手順を示す図である。

【図6】センシング性能向上のために、本発明で提案するマルチタイム電流センシング方式の一駆動波形及び駆動手順を示す図である。

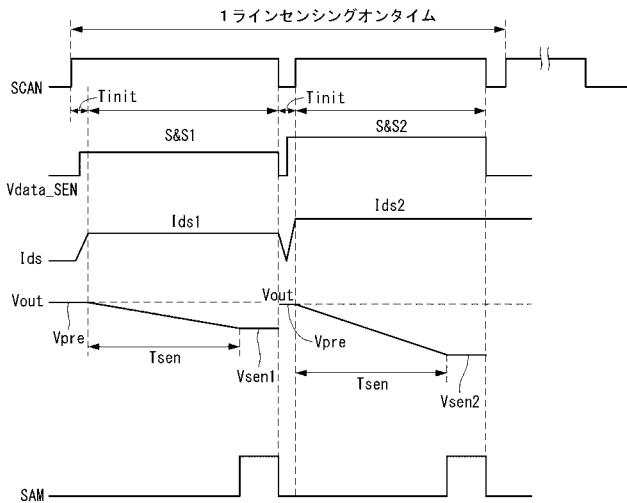

【図7】本発明において提案するマルチタイム電流センシング方式の他の駆動波形を示す図である。

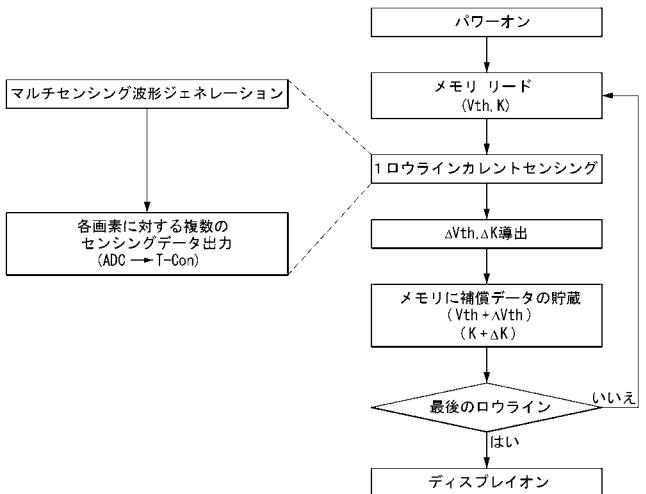

【図8】パワーオン時の補償フローを示す図である。

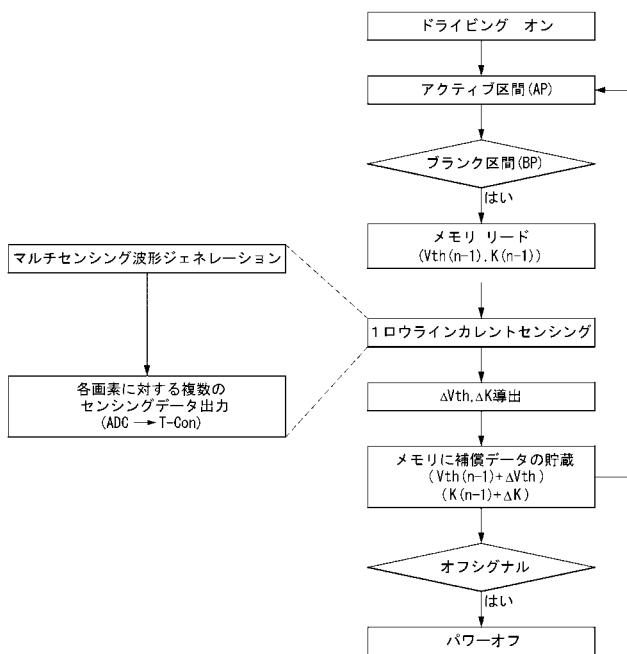

【図9】リアルタイム駆動時の補償フローを示す図である。

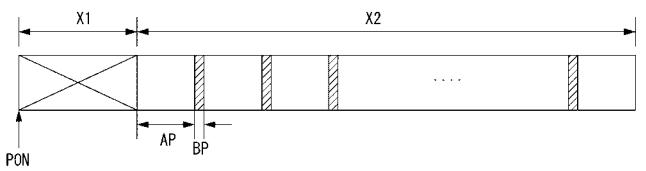

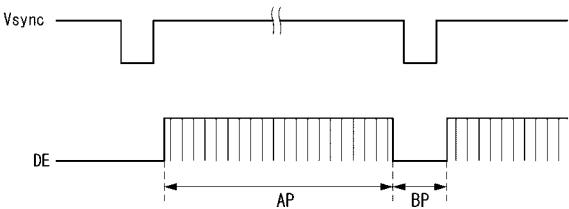

【図10A】パワーオン時の所定の初期非表示期間、有効表示期間、垂直プランク期間な

50

どを示す図である。

【図10B】パワーオン時の所定の初期非表示期間、有効表示期間、垂直プランク期間などを示す図である。

【図11】本発明のマルチタイム電流センシング方式において表示されることができるADCのオーバーレンジ(over range)の状況を示す図である。

【図12】ADCのオーバーレンジ(over range)現象を防止することができる方法を示す図である。

【図13】ADCのオーバーレンジ(over range)現象を防止することができる他の方法を示す図である。

【図14】ADCのオーバーレンジ(over range)現象を防止することができる他の方法を示す図である。 10

【図15】ADCのオーバーレンジ(over range)現象を防止することができる他の方法を示す図である。

【図16】ルックアップテーブルを用いた補償方式の一例を示す図である。

【発明を実施するための形態】

【0021】

以下、図1～図16を参照して本発明の好適な実施の形態について説明する。

【0022】

図1は、本発明の実施の形態に係る有機発光表示装置を示し、図2は図1の表示パネルに形成された画素アレイを示す。 20

【0023】

図1及び図2を参照すると、本発明の実施の形態に係る有機発光表示装置は、表示パネル10、タイミングコントローラ11、データ駆動回路12、ゲート駆動回路13、及びメモリ16を備える。

【0024】

表示パネル10には、複数のデータラインとセンシングライン(14A、14B)と、複数のゲートライン15が交差され、この交差領域ごとに画素(P)がマトリックス形態に配置される。

【0025】

各画素(P)は、データライン14Aのいずれか1つ、センシングラインの14Bのいずれか1つ、そしてゲートライン15のいずれか1つ、に接続される。各画素(P)は、ゲートライン15を介して入力されるゲートパルスに応答して、データ電圧供給ライン14Aと電気的に接続され、データ電圧供給ライン14Aからデータ電圧の入力を受け、センシングライン14Bを介してセンシング信号を出力する。 30

【0026】

画素(P)のそれぞれは、図示しない電源生成部から、高電位駆動電圧(EVDD)と低電位駆動電圧(EVSS)の供給を受ける。本発明の画素(P)は、外部補償のためにOLED、駆動TFT、第1及び第2スイッチTFT、及びストレージキャパシタを含むことができる。画素(P)を構成するTFTはp型で実現される、または、n型で実現されることができる。また、画素(P)を構成するTFTの半導体層は、アモルファスシリコンまたは、ポリシリコンまたは、酸化物を含むことができる。 40

【0027】

画素(P)のそれぞれは、画像を実現するためのノーマル駆動時と、センシング値獲得のためのセンシング駆動時に、互いに異なるように動作することができる。センシング駆動はノーマル駆動に先立って、所定時間の間実行される、または、ノーマル駆動中の垂直プランク期間において実行されることがある。

【0028】

ノーマル駆動は、タイミングコントローラ11の制御下で、データ駆動回路12と、ゲート駆動回路13のノーマル動作から行うことができる。センシング駆動は、タイミングコントローラ11の制御下で、データ駆動回路12と、ゲート駆動回路13のセンシング 50

動作からなることができる。そして、センシング結果に基づいて、偏差補償のための補償データを導出する動作と、補償データを用いて、デジタルビデオデータを変調する動作は、タイミングコントローラ 11 で実行される。

#### 【0029】

データ駆動回路 12 は、少なくとも一つ以上のデータドライバ I C ( Intergrated Circuit ) ( S D I C ) を含む。データドライバ I C ( S D I C ) には、各データライン 14 A に接続された複数のデジタル アナログコンバータ ( 以下、D A C ) と、各センシングライン 14 B に接続された複数のセンシングユニットと、センシングユニットの出力端に共通に接続された A D C が含まれている。

#### 【0030】

データドライバ I C ( S D I C ) の D A C は、ノーマル駆動時のタイミングコントローラ 11 から印加されるデータタイミング制御信号 ( D D C ) に基づいて、デジタルビデオデータ ( R G B ) を画像実現用のデータ電圧に変換してデータライン 14 A に供給する。一方、データドライバ I C ( S D I C ) の D A C は、センシング駆動時のタイミングコントローラ 11 から印加されるデータタイミング制御信号 ( D D C ) に基づいて、センシング用のデータ電圧を生成してデータライン 14 A に供給する。

#### 【0031】

データドライバ I C ( S D I C ) の各センシングユニットは、センシングライン 14 B を介して入力される画素 ( P ) のセンシング信号、すなわち、駆動 T F T のソース ドライン間の電流を積分する電流積分器 ( C I ) と、電流積分器 ( C I ) の出力をサンプリング及びホールディングするサンプリング部 ( S H ) を含む。データドライバ I C ( S D I C ) の A D C は、サンプリング部 ( S H ) の出力を順次にデジタル処理してタイミングコントローラ 11 に伝送する。

#### 【0032】

ゲート駆動回路 13 は、ノーマル駆動時、ゲート制御信号 ( G D C ) に基づいて画像表示用のゲートパルスを生成した後、行順次方式 ( L # 1, L # 2, ... ) でゲートライン 15 に順次供給する。ゲート駆動回路 13 は、センシング駆動時、ゲート制御信号 ( G D C ) に基づいて、センシング用ゲートパルスを生成した後、行順次方式 ( L # 1, L # 2, ... ) にゲートラインに 15 に順次供給する。センシング用ゲートパルスは、画像表示用のゲートパルスに比べてオンパルス区間が広いことがある。センシング用ゲートパルスのオンパルス区間は 1 ラインセンシングオンタイム内に、一個 ( 図 6 参照 ) 、または複数 ( 図 7 参照 ) 含めることができる。ここで、1 ラインセンシングオンタイムとは、1 行の画素ライン ( L # 1, L # 2, ... ) の画素を同時にセンシングするために割くスキヤン時間を意味する。

#### 【0033】

タイミングコントローラ 11 は、垂直同期信号 ( V s y n c ) 、水平同期信号 ( H s y n c ) 、ドットクロック信号 ( D C L K ) と、データタイネーブル信号 ( D E ) などのタイミング信号に基づいて、データ駆動回路 12 の動作タイミングを制御するためのデータ制御信号 ( D D C ) と、ゲート駆動回路 13 の動作タイミングを制御するためのゲート制御信号 ( G D C ) を生成する。タイミングコントローラ 11 は、所定の参照信号 ( 駆動電源イネーブル信号、垂直同期信号、データタイネーブル信号 ) に基づいて、ノーマル駆動とセンシング駆動を区別し、それぞれの駆動に合わせて、データ制御信号 ( D D C ) とゲート制御信号 ( G D C ) を生成する。さらに、タイミングコントローラ 11 は、センシング駆動に必要な追加の制御信号 ( 図 3 の R S T, S A M, H O L D など ) を生成することができる。

#### 【0034】

タイミングコントローラ 11 は、センシング駆動時、センシング用データ電圧に対応するデジタルデータをデータ駆動回路 12 に伝送することができる。タイミングコントローラ 11 は、センシング駆動時、データ駆動回路 12 から伝送されるデジタルセンシング値 ( S D ) を、あらかじめ記憶された補償アルゴリズムに適用して、しきい値電圧偏差 (

10

20

30

40

50

$V_{th}$ ) と移動度偏差 ( $K$ ) を導出した後、その偏差を補償することができる補償データをメモリ 16 に記憶する。

【0035】

タイミングコントローラ 11 は、ノーマル駆動時の、メモリ 16 に記憶された補償データを参照して、画像を実現するためのデジタルビデオデータ (RGB) を変調した後、データ駆動回路 12 に伝送する。

【0036】

図 3 及び図 4 は、本発明の電流センシング方式が適用される、画素 (P) とセンシングユニットの接続構造、及びセンシング原理を示す。

【0037】

図 3 及び図 4 は、電流センシング方式の駆動理解を助けるための一例に過ぎない。本発明の電流センシングが適用される画素構造及びその駆動タイミングは、さまざまな変形が可能であるため、本発明の技術的思想は、この実施の形態に限定されない。

【0038】

図 3 を参照すると、本発明の画素 (PIX) は、OLED、駆動 TFT (Thin Film Transistor) (DT)、ストレージキャパシタ (Cst)、第 1 スイッチ TFT (ST1)、及び第 2 スイッチ TFT (ST2) を備えることができる。

【0039】

OLED は、第 2 ノード (N2) に接続されたアノード電極と、低電位駆動電圧 (EVSS) の入力端に接続されたカソード電極と、アノード電極とカソード電極との間に位置する有機化合物層を含む。駆動 TFT (DT) は、ゲート - ソース間電圧 (Vgs) に応じて、OLED に入力される電流量を制御する。駆動 TFT (DT) は、第 1 ノード (N1) に接続されたゲート電極、高電位駆動電圧 (EVDD) の入力端に接続されたドレイン電極、及び第 2 ノード (N2) に接続されたソース電極とを備える。ストレージキャパシタ (Cst) は、第 1 ノード (N1) と第 2 ノード (N2) との間に接続される。第 1 スイッチ TFT (ST1) は、ゲートパルス (SCAN) に応答してデータ電圧供給ライン 14A 上のデータ電圧 (Vdata) を第 1 ノード (N1) に印加する。第 1 スイッチ TFT (ST1) は、ゲートライン 15 に接続されたゲート電極、データ電圧供給ライン 14A に接続されたドレイン電極、及び第 1 ノード (N1) に接続されたソース電極とを備える。第 2 スイッチ TFT (ST2) は、ゲートパルス (SCAN) に応答して、第 2 ノード (N2) とセンシングライン (14B) との間の電流の流れをスイッチングする。第 2 スイッチ TFT (ST2) は、第 2 ゲートライン (15D) に接続されたゲート電極、センシングライン (14B) に接続されたドレイン電極、及び第 2 ノード (N2) に接続されたソース電極とを備える。

【0040】

本発明のセンシングユニットに属する電流積分器 (CI) は、センシングライン (14B) に接続されて、センシングライン (14B) から駆動 TFT のソース - ドレイン間電流 (IdS) の入力を受ける反転入力端子 (-)、基準電圧 (Vpre) の入力を受ける非反転入力端子 (+)、積分値 (Vsen) を出力する出力端子を含むアンプ (AMP) と、アンプ (AMP) の反転入力端子 (-) と出力端子との間に接続された積分キャパシタ - (Cfb) と、積分キャパシタ - (Cfb) の両端に接続された第 1 スイッチ (SW1) を含む。

【0041】

そして、本発明のセンシングユニットに属するサンプリング部 (SH) は、サンプリング信号 (SAM) の信号に応じてスイッチングされる第 2 スイッチ (SW2)、ホールディング信号 (HOLD) 信号に応じてスイッチングされる第 3 スイッチ (SW3)、及び第 2 スイッチ (SW2) と第 3 スイッチ (SW3) との間に一端が接続され、他端が基底電圧源 (GND) に接続されたホールディングキャパシタ - (Ch) を含む。

【0042】

図 4 には、同じ行に配置された画素をセンシングするために、センシング用ゲートパル

ス( S C A N )のオンパルス区間で定義される1ラインセンシングオンタイム内で、画素のそれぞれに1回センシング波形が示されている。図4を参照すると、センシング駆動は、初期化期間( T i n i t )、センシング期間( T s e n )、及びサンプリング期間( T s a m )を含む。

#### 【 0 0 4 3 】

初期化期間( T i n i t )において、第1スイッチ( S W 1 )のターンオンにより、アンプ( A M P )は、利得が1であるユニットゲインバッファとして動作する。初期化期間( T i n i t )において、アンプ( A M P )の入力端子( +、- )と出力端子、センシングライン( 1 4 B )、及び第2ノード( N 2 )は、すべて基準電圧( V p r e )に初期化される。

10

#### 【 0 0 4 4 】

初期化期間( T i n i t )中に、データドライバI C( S D I C )のD A Cを介してセンシング用データ電圧( V d a t a - S E N )が第1ノード( N 1 )に印加される。それに応じて、駆動T F T( D T )には、第1ノード( N 1 )と第2ノード( N 2 )の電位差{ ( V d a t a - S E N - V p r e ) }に対応するソース-ドレイン間電流( I d s )が流れ、安定化される。しかし、初期化期間( T i n i t )中にアンプ( A M P )は、継続してユニットゲインバッファとして動作するので、出力端子の電位は基準電圧( V p r e )に維持される。

#### 【 0 0 4 5 】

センシング期間( T s e n )において、第1スイッチ( S W 1 )のターンオフにより、アンプ( A M P )は、電流積分器( C I )で動作して、駆動T F T( D T )に流れるソース-ドレイン間電流( I d s )を積分する。センシング期間( T s e n )において、アンプ( A M P )の反転入力端子( - )に流入される電流( I d s )によって積分キャパシター( C f b )の両端の電位差は、センシング時間が経過すればするほど、つまり蓄積される電流値( I d s )が増加するほど大きくなる。ところが、アンプ( A M P )の特性上、反転入力端子( - )と非反転入力端子( + )は、仮想接地( Virtual Ground )を介してショートされ、互いに電位差が0なので、センシング期間( T s e n )で、反転入力端子( - )の電位は、積分キャパシター( C f b )の電位差の増加にかかわらず、基準電圧( V p r e )に維持される。その代わりに、積分キャパシター( C f b )の両端の電位差に対応してアンプ( A M P )の出力端子の電位が低くなる。このような原理で、センシング期間( T s e n )で、センシングライン( 1 4 B )を介して流される電流( I d s )は、積分キャパシター( C f b )を介して電圧値の積分値( V s e n )に生成される。電流積分器出力値( V o u t )の立ち上がりの傾きは、センシングライン( 1 4 B )を介して流される電流量( I d s )が大きいほど増加するので、積分値( V s e n )の大きさは、前記電流量( I d s )が大きいほど、むしろ小さくなる。センシング期間( T s e n )において、積分値( V s e n )は、第2スイッチ( S W 2 )を経由してホールディングキャパシター( C h )に貯蔵される。

20

30

#### 【 0 0 4 6 】

サンプリング期間( T s a m )において、第3スイッチ( S W 3 )がターンオンされると、ホールディングキャパシタ( C h )に貯蔵された積分値( V s e n )が、第3スイッチ( S W 3 )を経由して、A D Cに入力される。積分値( V s e n )は、A D Cからのデジタルセンシング値( S D )に変換された後、タイミングコントローラ1 1に伝送される。デジタルセンシング値( S D )は、タイミングコントローラ1 1で駆動T F Tのしきい値電圧偏差( V t h )と移動度偏差( K )を導出するために使用される。タイミングコントローラ1 1には、積分キャパシター( C f b )の静電容量、基準電圧値( V p r e )、センシング時間値( T s e n )が予めデジタルコードで記憶されている。したがって、タイミングコントローラ1 1は、積分値( V s e n )のデジタルコードのデジタルセンシング値( S D )から駆動T F T( D T )に流れるソース-ドレイン間の電流( I d s = C f b \* V / t 、ここで、 V = V p r e - V s e n 、 t = T s e n )を計算することができる。

40

50

タイミングコントローラ 11 は、駆動 TFT (DT) に流れるソース - ドレイン間電流 ( $I_{ds}$ ) を補償アルゴリズムに適用して、偏差値 (しきい値電圧偏差 ( $V_{th}$ ) と移動度偏差 ( $K$ )) と偏差補償のための補償データ ( $V_{th} + V_{th}$ ,  $K + K$ ) を導出する。補償アルゴリズムは、ルックアップテーブルまたは、計算ロジックで実現することができる。

#### 【0047】

このような本発明の電流積分器 (CI) に含まれる積分キャパシター (Cfb) の静電容量は、センシングラインに存在する寄生容量に比べて数百分の 1 ほどと小さく、本発明の電流センシング方式は、センシング可能な積分値 ( $V_{sen}$ ) まで電流 ( $I_{ds}$ ) を流すためにかかる時間が、従来の電圧センシング方式に比べて大幅に短くなる。さらに、従来の電圧センシング方式では、しきい値電圧センシング時の駆動 TFT のソース電圧がセチュレーションされた後に、その電圧をセンシング電圧でサンプリングしたため、センシング時間が非常に長くなつたが、本発明の電流センシング方式では、しきい値電圧及び移動度センシング時の電流センシングを介して短い時間内に駆動 TFT のソース - ドレイン電流を積分し、その積分値をサンプリングすることができ、センシング時間を大幅に短縮することができる。

#### 【0048】

また、本発明の電流積分器 (CI) に含まれる積分キャパシター (Cfb) は、センシングラインの寄生キャパシターとは異なり、表示負荷に応じて貯蔵値が変動せず、キャリブレーションが容易で、正確なセンシング値の獲得が可能である。

#### 【0049】

このように、本発明の電流センシング方式は、従来の電圧センシング方式に比べて、低電流センシングが可能であり、また、高速センシングが可能という利点がある。低電流及び高速センシングが可能であるため、本発明の電流センシング方式は、センシング性能を向上するために、1 ラインセンシングオンタイム内で、画素のそれぞれについて、複数回センシングすることも可能である。

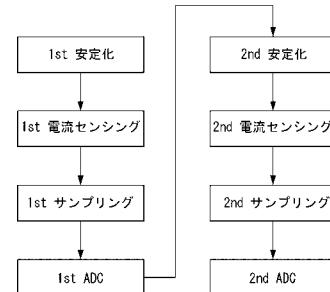

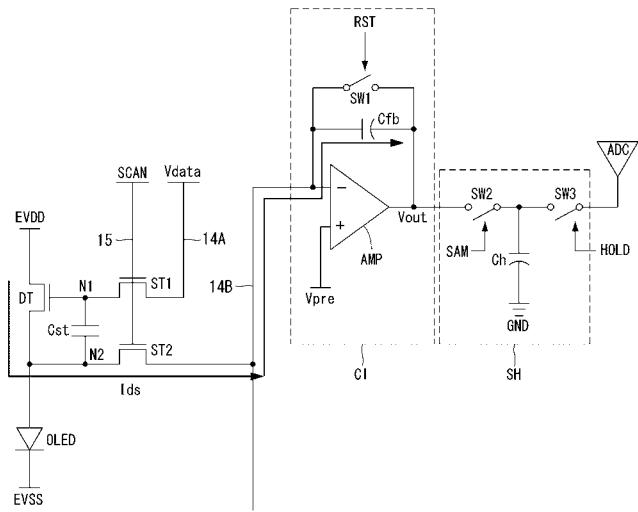

図 5 及び図 6 は、センシング性能向上のために、本発明で提案するマルチタイム電流センシング方式の一駆動波形と駆動手順を示す。図 7 は、本発明で提案するマルチタイム電流センシング方式の他の駆動波形を示す。図 5 ~ 図 7 において、本発明のマルチタイム電流センシングは、2 回の電流センシングが例示されているが、本発明の技術的思想は、3 回以上の電流センシングにも適用することができる。

#### 【0050】

図 5 及び図 6 を参照すると、センシング用ゲートパルス (SCAN) のオンパルス区間の 1 つに対応する 1 ラインセンシングオンタイム内で、同じ画素を対象に、センシング及びサンプリング動作を、2 回行うことができる。このため、タイミングコントローラ 11 は、駆動回路 12、13 の動作を制御して、1 ラインセンシングオンタイム内に、第 1 レベル (LV1) のセンシング用データ電圧 ( $V_{data-SEN}$ ) による第 1 ソース - ドレイン電流値 ( $I_{ds1}$ ) を積分する、第 1 センシング & サンプリング期間 ( $S \& S_1$ ) と、第 2 レベル (LV2) のセンシング用データ電圧 ( $V_{data-SEN}$ ) による第 2 ソース - ドレイン電流値 ( $I_{ds2}$ ) を積分する、第 2 センシング & サンプリング期間 ( $S \& S_2$ ) を含むことができる。そして、タイミングコントローラ 11 は、第 1 及び第 2 センシング & サンプリング期間 ( $S \& S_1$ ,  $S \& S_2$ ) の前に、それぞれ初期化期間 ( $T_{init}$ ) を設けることができる。

#### 【0051】

第 1 レベル (LV1) と第 2 レベル (LV2) のセンシング用データ電圧 ( $V_{data-SEN}$ ) は、互いに同じ電圧とすることができますが、異なる電圧とすることが、センシング性能を向上させるために好適である。第 1 レベル (LV1) は、全体の階調区間で所定範囲の低階調電流値 ( $I_{ds1}$ ) に対応する電圧であり、第 2 レベル (LV2) は、前記全体階調区間で所定範囲の高階調電流値 ( $I_{ds2}$ ) に対応する電圧とすることができます、これと反対とすることもできる。

10

20

30

40

50

すなわち、前記第1レベル（LV1）は、全体の階調区間で所定範囲の低階調電流値と所定範囲の高階調電流値の内いずれか1つに対応する電圧の大きさとすることができます、前記第2レベル（LV2）は、前記全体階調区間で、前記所定範囲の低階調電流値と前記所定範囲の高階調電流値の内、残りの一つに対応する電圧とすることができます。

#### 【0052】

1次初期化期間（T<sub>init</sub>）において、図4の初期化期間（T<sub>init</sub>）と同じ動作、つまり初期化動作及びソース・ドレイン間の電流（I<sub>ds</sub>）安定化動作が、1回実行される。

#### 【0053】

第1センシング&サンプリング期間（S&S1）では、図4のセンシング期間（T<sub>sen</sub>）とサンプリング期間（T<sub>sam</sub>）のような動作、第1ソース・ドレイン電流値（I<sub>ds1</sub>）をセンシングして、1次積分し、1次積分値（V<sub>sen1</sub>）をサンプリングして、1回ADC処理した後、第1デジタルセンシング値を内部ラッチに記憶する。10

#### 【0054】

2次初期化期間（T<sub>init</sub>）は、図4の初期化期間（T<sub>init</sub>）と同じ動作、つまり初期化動作及びソース・ドレイン間の電流（I<sub>ds</sub>）の安定化動作が2回実行される。

#### 【0055】

第2センシング&サンプリング期間（S&S2）では、図4のセンシング期間（T<sub>sen</sub>）とサンプリング期間（T<sub>sam</sub>）のような動作、第2ソース・ドレイン電流値（I<sub>ds2</sub>）をセンシングして、2次積分し、2次積分値（V<sub>sen2</sub>）をサンプリングして、2次ADC処理した後、第2デジタルセンシング値を内部ラッチに記憶する。20

#### 【0056】

ここで、第1及び第2センシング&サンプリング期間（S&S1、S&S2）にそれぞれ含まれるセンシング期間（T<sub>sen</sub>）の長さは、互いに同一である。

#### 【0057】

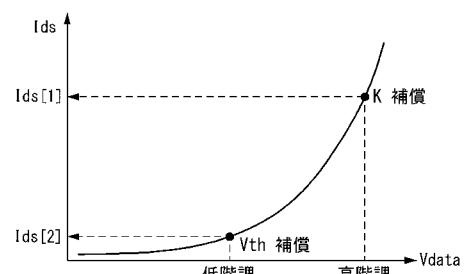

タイミングコントローラ11は、第1及び第2デジタルセンシング値に基づいて、第1及び第2ソース・ドレイン電流値（I<sub>ds1</sub>、I<sub>ds2</sub>）を計算し、計算ロジックまたはルックアップテーブルを用いて、所望する偏差値（V<sub>th</sub>、K）を導出することができる。

#### 【0058】

計算ロジックを用いる時、タイミングコントローラ11は、計算された第1及び第2ソース・ドレイン電流値（I<sub>ds1</sub>、I<sub>ds2</sub>）を、それぞれLED電流を数式（I<sub>ds</sub> = K(V<sub>gs</sub> - V<sub>th</sub>)<sup>2</sup>）に適用して、2つの電流の数式（I<sub>ds1</sub> = K(V<sub>gs1</sub> - V<sub>th</sub>)<sup>2</sup>、I<sub>ds2</sub> = K(V<sub>gs2</sub> - V<sub>th</sub>)<sup>2</sup>）を得、この数式を演算して、当該画素のしきい値電圧（V<sub>th</sub>）を先に計算した後、その値を前記LED電流の数式のいずれか1つに代入して、移動度（K）を計算することができる。そして、計算されたしきい値電圧（V<sub>th</sub>）と移動度（K）を、あらかじめ記憶された基準値と比較して、所望する偏差値（V<sub>th</sub>、K）を導出することができる。30

#### 【0059】

ルックアップテーブルを用いる時、タイミングコントローラ11は、計算された第1及び第2ソース・ドレイン電流値（I<sub>ds1</sub>、I<sub>ds2</sub>）を、予め記憶された基準電流値と比較して、第1及び第2電流偏差値を計算し、第1及び第2電流偏差値をそれぞれリードアドレスにして、しきい値電圧の偏差値（V<sub>th</sub>）と移動度偏差値（K）を導出することができる。通常、駆動TFTのソース・ドレイン電流が低階調区間では、しきい値電圧の変化に多く影響を受け、高階調区間では、移動度の変化に多く影響を受けることが知られている。したがって、タイミングコントローラ11は、図16に示すように、相対的に小さな第1ソース・ドレイン電流値（I<sub>ds1</sub>）に基づいて、しきい値電圧の偏差値（V<sub>th</sub>）を導出することができ、相対的に大きな第2ソース・ドレイン電流値（I<sub>ds2</sub>）に基づいて移動度の偏差値（K）を導出することができる。40

#### 【0060】

10

20

30

40

50

一方、タイミングコントローラ 11 は、第 1 及び第 2 センシング & サンプリング期間 (S & S1, S & S2) に対し、同じ安定化条件を付与するために、ゲート駆動回路 13 の動作を制御し、図 7 のように、センシング用ゲートパルス (SCAN) のオンパルス区間が、1 ラインセンシングオンタイム内に 2 つ以上含まれるように、センシング用ゲートパルス (SCAN) をマルチパルスの形で生成することができる。前記安定化条件には、ゲート遅延、データの充電ディレイなどを含むことができる。

#### 【0061】

図 8 は、パワーオン時の補償フローを示し、図 9 は、リアルタイム駆動時の補償フローを示す。図 10A 及び図 10B は、パワーオン時の所定の初期非表示期間、有効表示期間、垂直ブランク期間などを示す。10

#### 【0062】

図 8 の補償フローは、ノーマル駆動に先立つ、所定の初期非表示期間 (X1) 中のすべての画素に対して実行されるセンシング駆動を含む。図 9 の補償フローは、ノーマル駆動中の垂直ブランク期間 (BP) において、1 画素の行に対して実行されるセンシング駆動を含む。20

#### 【0063】

ここで、初期の非表示期間 (X1) は、図 10A に示すように、駆動電源イネーブル信号 (PON) の印加時点から数十～数百フレーム経過するまでの非表示期間として定義することができる。そして、垂直ブランク期間 (BP) は、図 10A 及び図 10B に示すように、画像が表示される有効表示期間 (AP) との間の非表示期間として定義することができる。初期非表示期間 (X1) と垂直ブランク期間 (BP) においては、データイネーブル信号 (DE) が発生されず、それに応じて、画像表示用のデータ電圧は垂直ブランク期間 (BP) から画素に供給されない。20

#### 【0064】

図 8 を参照して、初期非表示期間 (X1) 中の補償フローを再度概略的に説明すると、本発明は、パワーオン時に、以前の補償時記憶されたしきい値電圧 (Vth) と移動度 (K) をメモリから読み出す。続いて、本発明は、各画素の行に対して、行順次方式の前述したマルチタイムの電流センシング方式を適用して、複数のデジタルセンシング値を獲得し、このデジタルセンシング値にもとづいて、現在のしきい値電圧 (Vth) と移動度 (K) を導出する。続いて、本発明は、導出された現在のしきい値電圧 (Vth) と移動度 (K) を、メモリから読み出されるしきい値電圧 (Vth) 及び移動度 (K) とそれぞれ比較して、しきい値電圧偏差値 (ΔVth) と移動度偏差値 (ΔK) を導出した後、偏差値を補償することができる補償データ (Vth + ΔVth, K + ΔK) をメモリに記憶する。30

#### 【0065】

図 9 を参照して、ノーマル駆動中の垂直ブランク期間 (BP) において、1 画素行ずつ実行される補償フローを再度概略的に説明すると、本発明は、垂直ブランク期間 (BP) から、直前の補償時に記憶されたしきい値電圧 (Vth(n-1)) と移動度 (K(n-1)) をメモリから読み出す。続いて、本発明は、各画素の行に対して、行順次方式の前述したマルチタイム電流センシング方式を適用して、複数のデジタルセンシング値を獲得し、このデジタルセンシング値に基づいて、現在のしきい値電圧 (Vth) と移動度 (K) を導出する。続いて、本発明は、導出された現在のしきい値電圧 (Vth) と移動度 (K) を、メモリから読み出されるしきい値電圧 (Vth(n-1)) と移動度 (K(n-1)) とそれぞれ比較して、しきい値電圧偏差値 (ΔVth) と移動度偏差値 (ΔK) を導出した後、偏差値を補償することができる補償データ (Vth + ΔVth, K + ΔK) をメモリに記憶する。40

#### 【0066】

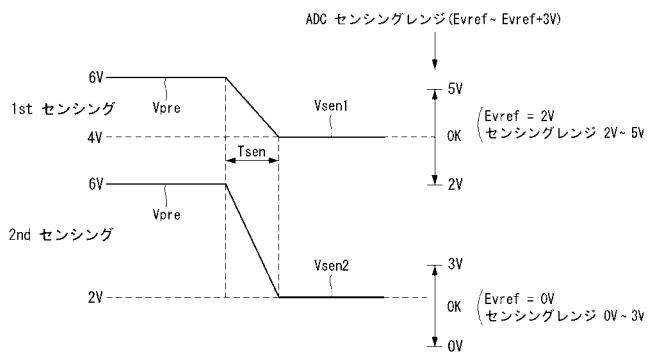

図 11 は、本発明のマルチタイム電流センシング方式で表示されることができる ADC のオーバーレンジ (over range) の状況を示す。

#### 【0067】

10

20

30

40

50

A D C は、アナログ信号をデジタル信号形式のデータに変換する特殊な符号器である。A D C はその入力電圧範囲、すなわち、センシングレンジが決まっている。A D C の電圧範囲は、A D 变換の分解能に応じて異なるが、通常、 $E_{vref}$  (A D C 基準電圧) ~  $E_{vref} + 3V$  に設定することができる。ここで、A D 变換の分解能とは、アナログ入力電圧をデジタル値に変換することができるビットの値を指示する。A D C に入力されるアナログ信号がA D C の入力範囲を超える場合、A D C の出力値は、入力電圧範囲の下限値にアンダーフロー (underflow) したり、または、入力電圧範囲の上限値にオーバーフロー (overflow) したりすることがある。

#### 【0068】

本発明は、マルチタイム電流センシング方式に基づいて、各画素ごとに少なくとも2回以上のセンシング過程を介して、互いに異なる大きさのアナログ積分値 ( $V_{sen}$ ) を生成する。前述したように、電流積分器 (C I) に流される電流値 ( $I_{ds}$ ) が大きい場合には、出力される積分値 ( $V_{sen}$ ) の大きさは小さくなり、逆に電流積分器 (C I) に流される電流値 ( $I_{ds}$ ) が小さい場合には、出力される積分値 ( $V_{sen}$ ) の大きさは大きくなる。したがって、さまざまな大きさの積分値 ( $V_{sen}$ ) の中の一部がA D C の入力範囲を超えることがある。

#### 【0069】

図11を用いてさらに説明すると、A D C の入力範囲が2V ~ 5Vのとき、第1電流値 ( $I_{ds1}$ ) による1次積分値 ( $V_{sen1}$ ) が4V、第1電流値 ( $I_{ds1}$ ) より大きい第2電流値 ( $I_{ds2}$ ) に基づく2次積分値 ( $V_{sen2}$ ) が1.5Vである場合を仮定する。

#### 【0070】

1次積分値 ( $V_{sen1}$ ) である4Vは、A D C の入力範囲 (2V ~ 5V) に属するので、正常に出力することができるのでに対し、2次積分値 ( $V_{sen2}$ ) である1.5VはA D C の入力範囲 (2V ~ 5V) 外となるので、それに近い入力電圧範囲 (2V ~ 5V) の下限値 (2V) にアンダーフローされて出力される。

#### 【0071】

このようにA D C のオーバーレンジ (over range) 現象が発生する場合、センシングの精度が落ちる。したがって、A D C のオーバーレンジ (over range) 現象を防止する追加の方法が要求される。

#### 【0072】

図12は、A D C のオーバーレンジ (over range) 現象を防止する一方法を示している。

#### 【0073】

本発明は、マルチタイム電流センシング方式において、図12に示すように、電流積分器 (C I) 出力値 ( $V_{out}$ ) の立ち下がりの傾きが相対的に大きい第1センシング&サンプリング期間 ( $S \& S_1$ ) では、電流積分器 (C I) 出力値 ( $V_{out}$ ) の立ち下がりの傾きが相対的に小さい第2センシング&サンプリング期間 ( $S \& S_2$ ) に比べ、1次積分値 ( $V_{sen1}$ ) がアンダーフローする可能性が高い。

#### 【0074】

この場合、本発明は、第1センシング&サンプリング期間 ( $S \& S_1$ ) でのセンシング期間 ( $T_{sen1}$ ) を、第2センシング&サンプリング期間 ( $S \& S_2$ ) でのセンシング期間 ( $T_{sen2}$ ) に比べて減らすことで、1次積分値 ( $V_{sen1}$ ) を2Vから3.5Vへと上向きに調整して、1次積分値 ( $V_{sen1}$ ) がA D C の入力電圧範囲 (2V ~ 5V) を満足するように補正することができる。

#### 【0075】

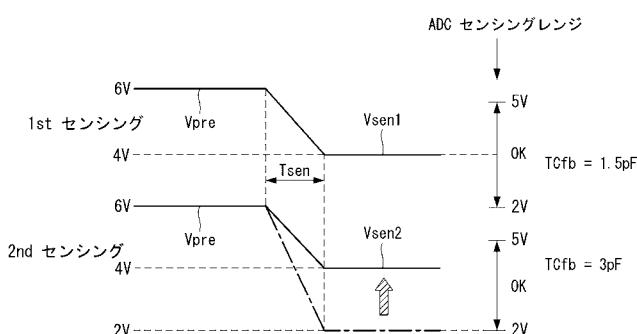

図13～図15は、A D C のオーバーレンジ (over range) 現象を防止する他の方法を示す。

#### 【0076】

図13を参照すると、本発明は、タイミングコントローラ11の制御下で、電流積分器

10

20

30

40

50

(C I)に含まれる積分キャパシター(C f b)の静電容量を調整するための容量制御部22をさらに含む。積分キャパシター(C f b)は、アンプ(AMP)の反転入力端子(-)に並列接続された複数のキャパシター(C f b 1、C f b 2、C f b 3)を含むが、キャパシター(C f b 1、C f b 2、C f b 3)それぞれの他端は、互いに異なる容量調整用スイッチ(S 1、S 2、S 3)を介して、アンプ(AMP)の出力端に接続することができる。積分キャパシター(C f b)の合成静電容量は、オンされる静電容量調整用スイッチ(S 1、S 2、S 3)の数に応じて決定される。

#### 【0077】

タイミングコントローラ11は、デジタルセンシング値(SD)を分析して、ADCの下限値及び上限値と同じデジタルセンシング値(SD)の比率に応じて、静電容量制御部22の動作を制御して適切なスイッチング制御信号を生成する。静電容量調整用スイッチ(S 1、S 2、S 3)は、静電容量制御部22から入力されるスイッチング制御信号に応じてオン/オフされる。積分キャパシター(C f b)の合成静電容量が大きいほど、電流積分器ユニット(C I)の出力値(Vout)の立ち下がりの傾きは小さくなり、逆に、積分キャパシター(C f b)の合成静電容量が小さいほど、電流積分器ユニット(C I)の出力値(Vout)の立ち下がりの傾きは大きくなる。

#### 【0078】

したがって、タイミングコントローラ11は、静電容量制御部22を介して、ターン・オンされる静電容量調整用スイッチ(S 1、S 2、S 3)の数を制御することにより、ADCの出力値が入力電圧範囲の下限値でアンダーフロー(underflow)する場合には、積分キャパシター(C f b)の合成静電容量を増加させ、逆にADCの出力値が入力電圧範囲の上限値でオーバーフロー(overflow)する場合には、積分キャパシター(C f b)の合成静電容量を減少させることができる。

#### 【0079】

積分キャパシター(C f b)の合成静電容量を制御することにより、ADCのオーバーレンジ状況が防止される一例が図14に示されている。本発明のマルチタイム電流センシング方式において、図14に示すように、電流積分器(C I)の出力値(Vout)の立ち下がりの傾きが相対的に大きい第2センシング&サンプリング期間では、電流積分器(C I)の出力値(Vout)の立ち下がりの傾きが相対的に小さい第1センシング&サンプリング期間に比べて、2次積分値(Vsen2)がアンダーフローする可能性が高い。

#### 【0080】

この場合、本発明は、第2センシング&サンプリング期間中に動作する積分キャパシター(C f b)の合成静電容量(3 pF)を、第1センシング&サンプリング期間中に動作する積分キャパシター(C f b)の合成静電容量(1.5 pF)に比べて2倍増やすことで、1次積分値(Vsen1)を2Vから4Vに上向きに調整し、2次積分値(Vsen2)がADCの入力電圧範囲(2V~5V)を満足するように補正することができる。

#### 【0081】

一方、図13を参照すると、本発明は、タイミングコントローラ11の制御下に、ADC基準電圧(Evref)を調整するためのプログラマブル電圧調整IC24をさらに含むことができる。

#### 【0082】

タイミングコントローラ11は、デジタルセンシング値(SD)を分析して、ADCの下限値及び上限値と同じデジタルセンシング値(SD)の比率に応じて、プログラマブル電圧調整IC24の動作を制御して、ADC基準電圧(Evref)を調整することができる。

#### 【0083】

ADC基準電圧(Evref)を調整することにより、ADCのオーバーレンジ状況が防止される一例が、図15に示されている。本発明のマルチタイム電流センシング方式において、図15に示すように、電流積分器(C I)の出力値(Vout)の立ち下がりの傾きが相対的に大きい第2センシング&サンプリング期間では、電流積分器(C I)の出

10

20

30

40

50

力値 ( $V_{out}$ ) の立ち下がりの傾きが相対的に小さい第1センシング&サンプリング期間に比べて、2次積分値 ( $V_{sen2}$ ) がアンダーフローする可能性が高い。

#### 【0084】

この場合、本発明は、1次積分値 ( $V_{sen1}$ ) である4Vをデジタル処理する際のADC基準電圧 ( $E_{ref}$ ) は、元の2Vを保持し、2次積分値 ( $V_{sen2}$ ) である2Vをデジタル処理する際のADC基準電圧 ( $E_{ref}$ ) は、元の2Vから0Vに下向きに調整する。このような下向き調整により、2次積分値 ( $V_{sen2}$ ) 2VはADCの入力電圧範囲 (0V ~ 3V) を十分に満足することになる。

#### 【0085】

前述したように、本発明は、駆動素子の電気的特性の偏差をセンシングするにあたり、電流積分器を用いた電流センシング方式を介して、低電流及び高速センシングを実現して、センシング時間を大幅に減らすことができる。さらに、本発明は、1ラインセンシングオンタイム内で、画素のそれぞれについて、マルチタイムセンシングを実行して、センシングの精度を大幅に向上させることができる。10

#### 【0086】

以上説明した内容を介して、当業者であれば、本発明の技術思想を逸脱しない範囲で、多様な変更及び修正が可能であることを分かるであろう。したがって、本発明の技術的範囲は、明細書の詳細な説明に記載された内容に限定されるものではなく、特許請求の範囲の記載によって定められるべきである。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10A】

【図10B】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 5】

【図 1 4】

【図 1 6】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 2 3 D |

|             | G 0 9 G | 3/20 6 2 2 D |

|             | G 0 9 G | 3/20 6 2 4 Z |

|             | G 0 9 G | 3/20 6 1 2 E |

|             | G 0 9 G | 3/20 6 2 1 F |

(72)発明者 キム， ジュンヒョン

大韓民国 156-827, ソウル, ドンジャクク, サダン 1ドン, ナムブスンワンロ

263ギル, サンヨン ハッピールーム, 402

(72)発明者 ユン， ジンハン

大韓民国 621-190, キョンサンナム-ド, キメシ, サムバンドン 659-14

F ターム(参考) 5C080 AA06 BB05 DD05 DD08 EE29 FF03 FF11 JJ02 JJ03 JJ04

JJ05 JJ07

|       |      |      |      |      |      |      |      |      |       |      |

|-------|------|------|------|------|------|------|------|------|-------|------|

| 5C380 | AA01 | AB06 | AB21 | AB22 | AB23 | BA19 | BA38 | BA39 | BB04  | BC01 |

| BC20  | CA12 | CA32 | CA53 | CA54 | CB01 | CC26 | CC27 | CC33 | CD013 |      |

| CE08  | CE20 | CF13 | CF20 | CF27 | CF44 | CF48 | CF49 | CF51 | DA02  |      |

| DA39  | DA47 | DA49 | EA02 | EA05 | FA03 | FA21 | FA28 |      |       |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种有机发光显示装置，能够补偿驱动元件的电特性的偏差                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2016009185A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2016-01-18 |

| 申请号            | JP2014256831                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2014-12-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | キムテガン<br>キムジュンヒョン<br>ユンジンハン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | キム, テガン<br>キム, ジュンヒョン<br>ウン, ジンハン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/006 G09G3/3225 G09G3/3233 G09G3/3275 G09G2310/027 G09G2310/0291 G09G2310/08<br>G09G2320/0285 G09G2320/029 G09G2320/045 G09G2330/12 G09G3/3258 G09G3/3291 G09G2300<br>/0819 G09G2300/0828 G09G2320/0223                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.624.B G09G3/20.623.C G09G3/20.623.D<br>G09G3/20.622.D G09G3/20.624.Z G09G3/20.612.E G09G3/20.621.F G09G3/3233 G09G3/3266<br>G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD08 5C080/EE29 5C080/FF03 5C080/FF11 5C080<br>/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ07 5C380/AA01 5C380/AB06 5C380/AB21 5C380<br>/AB22 5C380/AB23 5C380/BA19 5C380/BA38 5C380/BA39 5C380/BB04 5C380/BC01 5C380/BC20<br>5C380/CA12 5C380/CA32 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CC26 5C380/CC27 5C380<br>/CC33 5C380/CD013 5C380/CE08 5C380/CE20 5C380/CF13 5C380/CF20 5C380/CF27 5C380/CF44<br>5C380/CF48 5C380/CF49 5C380/CF51 5C380/DA02 5C380/DA39 5C380/DA47 5C380/DA49 5C380<br>/EA02 5C380/EA05 5C380/FA03 5C380/FA21 5C380/FA28 |         |            |

| 优先权            | 1020140079255 2014-06-26 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | <a href="#">JP6144250B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

解决的问题：提供一种有机发光显示装置，该有机发光显示装置能够在感测驱动元件的电特性的偏差时减少感测时间并提高感测精度。根据本发明的有机发光显示装置包括具有像素的显示面板，与在感测驱动期间的一条线感测导通时间相对应的感测栅极脉冲以及行顺序栅极线产生方法。并且，在感测驱动期间，在单线感测导通时间内，顺序地提供驱动TFT的多个栅极驱动电路，以及对通过感测线输入的每个像素的驱动TFT的源极-漏极电流进行积分。电流积分器，数据驱动电路，包括栅极驱动电路和控制数据驱动电路的操作的时序控制器，该数据驱动电路依次对电流积分器的输出进行数字化处理并输出数字感测值。用。[选择图]图

|             |                              |         |                                                                                                               |

|-------------|------------------------------|---------|---------------------------------------------------------------------------------------------------------------|

| (21)出願番号    | 特願2014-256831 (P2014-256831) | (71)出願人 | 501426046<br>エルジー ディスプレイ カンパニー リ<br>ミテッド                                                                      |

| (22)出願日     | 平成26年12月19日 (2014.12.19)     | (72)発明者 | 大韓民国 ソウル、ヨンドゥンポーク、ヨ<br>ウーテロ 128                                                                               |

| (31)優先権主張番号 | 10-2014-0079255              | (74)代理人 | 100109726<br>弁理士 園田 吉隆                                                                                        |

| (32)優先日     | 平成26年6月26日 (2014.6.26)       | (74)代理人 | 100101199<br>弁理士 小林 義教                                                                                        |

| (33)優先権主張国  | 韓国 (KR)                      | (72)発明者 | キム, テガン<br>大韓民国 413-837, キョンギド<br>, バジュシ, ヤダンドン, ハンビック<br>トマウル 2 ダンジ ヒューマンビル<br>レイク パレス アパートメント, 2<br>01-2304 |