(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-242369

(P2008-242369A)

(43) 公開日 平成20年10月9日(2008.10.9)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30  | J 3K107     |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 | A 5C080     |

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30  | 338 5C094   |

| <b>H01L 27/32</b> (2006.01) | G09F 9/30  | 365Z        |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 624B        |

審査請求 未請求 請求項の数 4 O L (全 36 頁) 最終頁に続く

|           |                            |            |                                                                                                                              |

|-----------|----------------------------|------------|------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2007-86677 (P2007-86677) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                                                       |

| (22) 出願日  | 平成19年3月29日 (2007.3.29)     | (74) 代理人   | 100094363<br>弁理士 山本 孝久                                                                                                       |

|           |                            | (72) 発明者   | 山本 哲郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                                             |

|           |                            | (72) 発明者   | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                                             |

|           |                            | F ターム (参考) | 3K107 AA01 BB01 CC31 EE03 HH04<br>HH05<br>5C080 AA06 BB05 DD01 DD05 FF11<br>JJ02 JJ03 JJ04 JJ06<br>5C094 AA53 BA03 BA27 DB01 |

(54) 【発明の名称】有機エレクトロルミネッセンス素子及び有機エレクトロルミネッセンス表示装置

## (57) 【要約】

【課題】発光制御トランジスタ制御回路からの位置の遠近に依存すること無く、移動度補正処理の時間長を一定とし得る構成、構造を有する有機EL素子を提供する。

【解決手段】有機EL素子は、駆動回路と発光部ELPとを備え、駆動回路は、駆動トランジスタT<sub>Drv</sub>、映像信号書き込みトランジスタT<sub>Sig</sub>、発光制御トランジスタT<sub>EL\_C</sub>、コンデンサ部C<sub>1</sub>から構成されており、駆動回路は、更に、固定電源部に一方の電極が接続され、発光制御トランジスタT<sub>EL\_C</sub>の他方のソース／ドレイン領域に他方の電極が接続された補助容量部C<sub>Sub</sub>を備えている。

【選択図】 図1

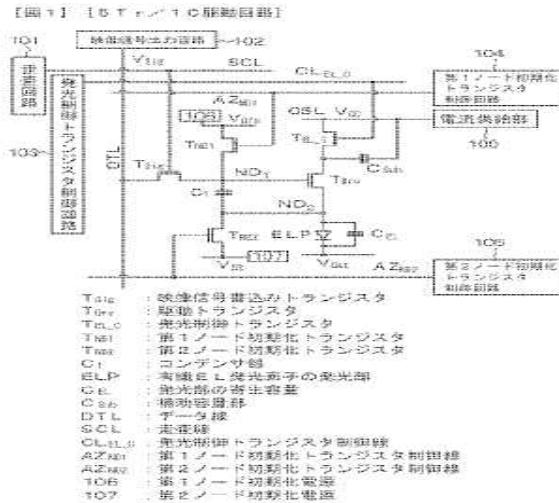

【図1】 [5 Tr / 1 C 駆動回路]

【特許請求の範囲】

【請求項 1】

駆動回路と、該駆動回路に接続された有機エレクトロルミネッセンス発光部とを備えた有機エレクトロルミネッセンス素子であって、

該駆動回路は、

(A) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた駆動トランジスタ、

(B) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた映像信号書き込みトランジスタ、

(C) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた発光制御トランジスタ、並びに、

(D) 一対の電極を備えたコンデンサ部、

から構成されており、

駆動トランジスタにおいては、

(A-1) 他方のソース／ドレイン領域は、有機エレクトロルミネッセンス発光部に備えられたアノード電極に接続され、且つ、コンデンサ部の一方の電極に接続されており、第2ノードを構成し、

(A-2) ゲート電極は、映像信号書き込みトランジスタの他方のソース／ドレイン領域に接続され、且つ、コンデンサ部の他方の電極に接続されており、第1ノードを構成し、

映像信号書き込みトランジスタにおいては、

(B-1) 一方のソース／ドレイン領域は、データ線に接続されており、

(B-2) ゲート電極は、走査線に接続されており、

発光制御トランジスタにおいては、

(C-1) 一方のソース／ドレイン領域は、電流供給部に接続されており、

(C-2) 他方のソース／ドレイン領域は、駆動トランジスタの一方のソース／ドレイン領域に接続されており、

(C-3) ゲート電極は、発光制御トランジスタ制御回路に接続されており、

該駆動回路は、更に、

(E) 固定電源部に一方の電極が接続され、発光制御トランジスタの他方のソース／ドレイン領域に他方の電極が接続された補助容量部、

を備えていることを特徴とする有機エレクトロルミネッセンス素子。

【請求項 2】

前記駆動回路は、

(F) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第2ノード初期化トランジスタ、

を更に備え、

第2ノード初期化トランジスタにおいては、

(F-1) 一方のソース／ドレイン領域は、第2ノードの電位を初期化するための電源に接続されており、

(F-2) 他方のソース／ドレイン領域は、第2ノードに接続されており、

(F-3) ゲート電極は、第2ノード初期化トランジスタ制御回路に接続されている、ことを特徴とする請求項1に記載の有機エレクトロルミネッセンス素子。

【請求項 3】

前記駆動回路は、

(G) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第1ノード初期化トランジスタ、

を更に備え、

第1ノード初期化トランジスタにおいては、

(G-1) 一方のソース／ドレイン領域は、第1ノードの電位を初期化するための電源に接続されており、

10

20

30

40

50

(G-2) 他方のソース／ドレイン領域は、第1ノードに接続されており、

(G-3) ゲート電極は、第1ノード初期化トランジスタ制御回路に接続されている、

ことを特徴とする請求項2に記載の有機エレクトロルミネッセンス素子。

**【請求項4】**

(a) 電流供給部、

(b) 走査回路、

(c) 映像信号出力回路、

(d) 発光制御トランジスタ制御回路、

(e) 第1の方向にN個、第1の方向とは異なる第2の方向にM個、合計N×M個の、

2次元マトリクス状に配列された有機エレクトロルミネッセンス素子、

(f) 走査回路に接続され、第1の方向に延びるM本の走査線、並びに、

(g) 映像信号出力回路に接続され、第2の方向に延びるN本のデータ線、

を備え、

各有機エレクトロルミネッセンス素子は、駆動回路、及び、該駆動回路に接続された有機エレクトロルミネッセンス発光部を備えており、

該駆動回路は、

(A) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた駆動トランジスタ、

(B) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた映像信号書き込みトランジスタ、

(C) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた発光制御トランジスタ、並びに、

(D) 一対の電極を備えたコンデンサ部、

から構成されており、

駆動トランジスタにおいては、

(A-1) 他方のソース／ドレイン領域は、有機エレクトロルミネッセンス発光部に備えられたアノード電極に接続され、且つ、コンデンサ部の一方の電極に接続されており、第2ノードを構成し、

(A-2) ゲート電極は、映像信号書き込みトランジスタの他方のソース／ドレイン領域に接続され、且つ、コンデンサ部の他方の電極に接続されており、第1ノードを構成し、

映像信号書き込みトランジスタにおいては、

(B-1) 一方のソース／ドレイン領域は、データ線に接続されており、

(B-2) ゲート電極は、走査線に接続されており、

発光制御トランジスタにおいては、

(C-1) 一方のソース／ドレイン領域は、電流供給部に接続されており、

(C-2) 他方のソース／ドレイン領域は、駆動トランジスタの一方のソース／ドレイン領域に接続されており、

(C-3) ゲート電極は、発光制御トランジスタ制御回路に接続されており、

該駆動回路は、更に、

(E) 固定電源部に一方の電極が接続され、発光制御トランジスタの他方のソース／ドレイン領域に他方の電極が接続された補助容量部、

を備えていることを特徴とする有機エレクトロルミネッセンス表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、有機エレクトロルミネッセンス素子、及び、係る有機エレクトロルミネッセンス素子から構成された有機エレクトロルミネッセンス表示装置に関する。

**【背景技術】**

**【0002】**

有機エレクトロルミネッセンス素子（以下、単に、有機EL素子と略称する）を発光素

10

20

30

40

50

子として用いた有機エレクトロルミネッセンス表示装置（以下、単に、有機EL表示装置と略称する）において、有機EL素子の輝度は、有機EL素子を流れる電流値によって制御される。そして、液晶表示装置と同様に、有機EL表示装置においても、駆動方式として、単純マトリクス方式、及び、アクティブマトリクス方式が周知である。アクティブマトリクス方式は、単純マトリクス方式に比べて構造が複雑となるといった欠点はあるが、画像の輝度を高いものとすることができる等、種々の利点を有する。

#### 【0003】

有機EL素子を構成する有機エレクトロルミネッセンス発光部（以下、単に、発光部と略称する）を駆動するための回路として、5つのトランジスタと1つのコンデンサ部から構成された駆動回路（5Tr / 1C駆動回路と呼ぶ）が、例えば、特開2006-215213から周知である。この従来の5Tr / 1C駆動回路は、図17に示すように、映像信号書き込みトランジスタT<sub>Sig</sub>、駆動トランジスタT<sub>Drv</sub>、発光制御トランジスタT<sub>EL\_C</sub>、第1ノード初期化トランジスタT<sub>ND1</sub>、第2ノード初期化トランジスタT<sub>ND2</sub>の5つのトランジスタから構成され、更には、1つのコンデンサ部C<sub>1</sub>から構成されている。ここで、駆動トランジスタT<sub>Drv</sub>の他方のソース／ドレイン領域は第2ノードND<sub>2</sub>を構成し、駆動トランジスタT<sub>Drv</sub>のゲート電極は第1ノードND<sub>1</sub>を構成する。

10

#### 【0004】

尚、これらのトランジスタ及びコンデンサ部については、後に詳しく説明するが、トランジスタをnチャネル型としている。

20

#### 【0005】

そして、図3にタイミングチャートを示すように、[期間 - TP(5)<sub>1</sub>]において、閾値電圧キャンセル処理を行うための前処理が実行される。即ち、第1ノード初期化トランジスタT<sub>ND1</sub>及び第2ノード初期化トランジスタT<sub>ND2</sub>をオン状態とすることで、第1ノードND<sub>1</sub>の電位は、V<sub>Off</sub>（例えば、0ボルト）となる。一方、第2ノードND<sub>2</sub>の電位は、V<sub>SS</sub>（例えば、-10ボルト）となる。そして、これによって、駆動トランジスタT<sub>Drv</sub>のゲート電極と他方のソース／ドレイン領域（以下、便宜上、ソース領域と呼ぶ）との間の電位差がV<sub>th</sub>以上となり、駆動トランジスタT<sub>Drv</sub>はオン状態となる。

#### 【0006】

次いで、[期間 - TP(5)<sub>2</sub>]において、閾値電圧キャンセル処理が行われる。即ち、第1ノード初期化トランジスタT<sub>ND1</sub>のオン状態を維持したまま、発光制御トランジスタT<sub>EL\_C</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位から駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>を減じた電位に向かって、第2ノードND<sub>2</sub>の電位は変化する。即ち、浮遊状態の第2ノードND<sub>2</sub>の電位は上昇する。そして、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>th</sub>に達すると、駆動トランジスタT<sub>Drv</sub>がオフ状態となる。この状態にあっては、第2ノードの電位は、概ね（V<sub>Off</sub> - V<sub>th</sub>）である。その後、[期間 - TP(5)<sub>3</sub>]において、第1ノード初期化トランジスタT<sub>ND1</sub>のオン状態を維持したまま、発光制御トランジスタT<sub>EL\_C</sub>をオフ状態とする。次に、[期間 - TP(5)<sub>4</sub>]において、第1ノード初期化トランジスタT<sub>ND1</sub>をオフ状態とする。

30

#### 【0007】

次いで、[期間 - TP(5)<sub>5</sub>]において、駆動トランジスタT<sub>Drv</sub>に対する一種の書き込み処理を実行する。具体的には、第1ノード初期化トランジスタT<sub>ND1</sub>、第2ノード初期化トランジスタT<sub>ND2</sub>、及び、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、データ線DTLの電位を映像信号に相当する電圧〔発光部ELPにおける輝度を制御するための映像信号（駆動信号、輝度信号）V<sub>Sig</sub>〕とし、次いで、走査線SCLをハイレベルとすることによって映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>Sig</sub>へと上昇する。第1ノードND<sub>1</sub>の電位の変化分に基づく電荷は、コンデンサ部C<sub>1</sub>、発光部ELPの寄生容量C<sub>EL</sub>、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の寄生容量に振り分けられる。従って、第1ノードND<sub>1</sub>の電位が変化すると、第2ノードND<sub>2</sub>の電位も変化する。しかしながら、発光部ELPの寄生容量C<sub>EL</sub>の容量値が大きな値である程、第2ノードND<sub>2</sub>の電位の変化は小さくなる

40

50

。そして、一般に、発光部 E L P の寄生容量  $C_{EL}$  の容量値は、コンデンサ部  $C_1$  の容量値及び駆動トランジスタ  $T_{DRV}$  の寄生容量の値よりも大きい。そこで、第 2 ノード  $N D_2$  の電位は殆ど変化しないとすれば、駆動トランジスタ  $T_{DRV}$  のゲート電極と他方のソース / ドレイン領域との間の電位差  $V_{gs}$  は、以下の式 (A) のとおりとなる。

【0008】

$$V_{gs} = V_{Sig} - (V_{Off} - V_{th}) \quad (A)$$

【0009】

その後、[期間 - TP(5)<sub>6</sub>]において駆動トランジスタ  $T_{DRV}$  の移動度  $\mu$  の大小に基づく駆動トランジスタ  $T_{DRV}$  のソース領域（第 2 ノード  $N D_2$ ）の電位の補正（移動度補正処理）を行う。具体的には、駆動トランジスタ  $T_{DRV}$  のオン状態を維持したまま、発光制御トランジスタ  $T_{EL\_C}$  をオン状態とし、次いで、所定の時間 ( $t_0$ ) が経過した後、映像信号書き込みトランジスタ  $T_{Sig}$  をオフ状態とし、第 1 ノード  $N D_1$ （駆動トランジスタ  $T_{DRV}$  のゲート電極）を浮遊状態とする。その結果、駆動トランジスタ  $T_{DRV}$  の移動度  $\mu$  の値が大きい場合、駆動トランジスタ  $T_{DRV}$  のソース領域における電位の上昇量  $V$ （電位補正值）は大きくなり、駆動トランジスタ  $T_{DRV}$  の移動度  $\mu$  の値が小さい場合、駆動トランジスタ  $T_{DRV}$  のソース領域における電位の上昇量  $V$ （電位補正值）は小さくなる。ここで、駆動トランジスタ  $T_{DRV}$  のゲート電極とソース領域との間の電位差  $V_{gs}$  は、式 (A) から以下の式 (B) のように変形される。尚、移動度補正処理を実行するための所定の時間 ([期間 - TP(5)<sub>6</sub>] の全時間 ( $t_0$ )) は、有機 E L 表示装置の設計の際、設計値として予め決定しておけばよい。

10

20

30

40

【0010】

$$V_{gs} = V_{Sig} - (V_{Off} - V_{th}) - V \quad (B)$$

【0011】

以上の操作によって、閾値電圧キャンセル処理、書き込み処理、移動度補正処理が完了する。そして、その後の [期間 - TP(5)<sub>7</sub>]においては、映像信号書き込みトランジスタ  $T_{Sig}$  がオフ状態となり、第 1 ノード  $N D_1$ 、即ち、駆動トランジスタ  $T_{DRV}$  のゲート電極は浮遊状態となる一方、発光制御トランジスタ  $T_{EL\_C}$  はオン状態を維持しており、発光制御トランジスタ  $T_{EL\_C}$  の一方のソース / ドレイン領域（以下、便宜上、ドレイン領域と呼ぶ）は、発光部 E L P の発光を制御するための電流供給部（電圧  $V_{CC}$ 、例えば 20 ボルト）に接続された状態にある。従って、以上の結果として、第 2 ノード  $N D_2$  の電位が上昇し、所謂ブートストラップ回路におけると同様の現象が駆動トランジスタ  $T_{DRV}$  のゲート電極に生じ、第 1 ノード  $N D_1$  の電位も上昇する。その結果、駆動トランジスタ  $T_{DRV}$  のゲート電極とソース領域との間の電位差  $V_{gs}$  は、式 (B) の値を保持する。また、発光部 E L P を流れる電流は、駆動トランジスタ  $T_{DRV}$  の一方のソース / ドレイン領域（以下、便宜上、ドレイン領域と呼ぶ）からソース領域へと流れるドレイン電流  $I_{ds}$  であるので、式 (C) で表すことができる。

【0012】

$$\begin{aligned} I_{ds} &= k \cdot \mu \cdot (V_{gs} - V_{th})^2 \\ &= k \cdot \mu \cdot (V_{Sig} - V_{Off} - V)^2 \quad (C) \end{aligned}$$

【0013】

以上に概要を説明した 5 T r / 1 C 駆動回路の駆動等についても、後に詳しく説明する。

【0014】

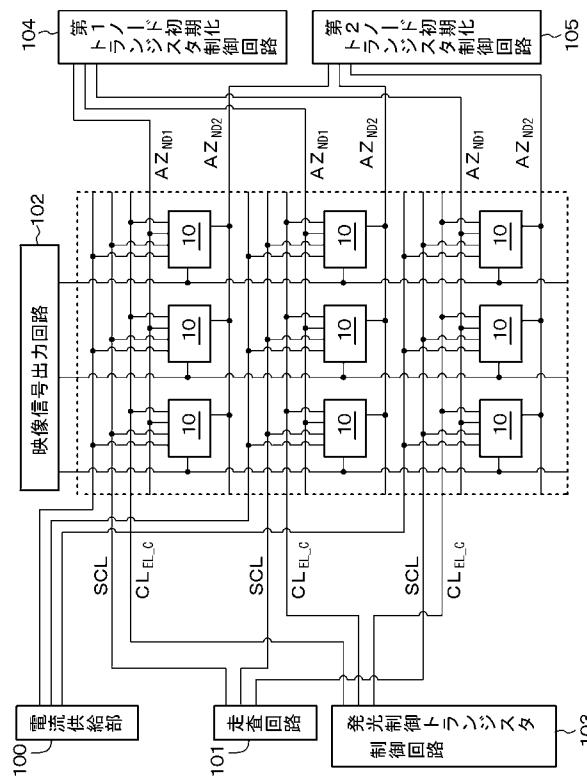

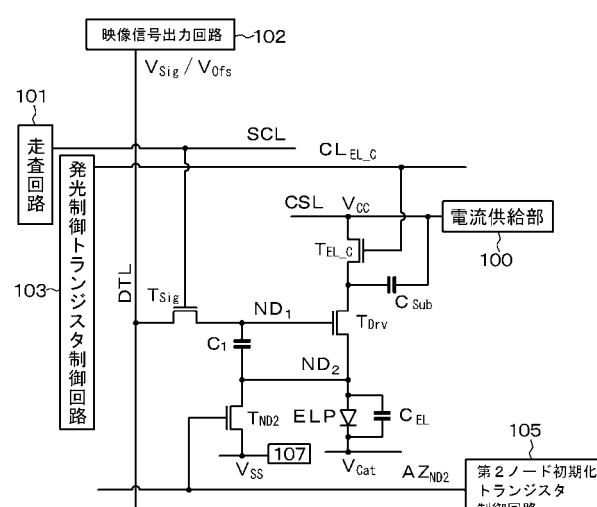

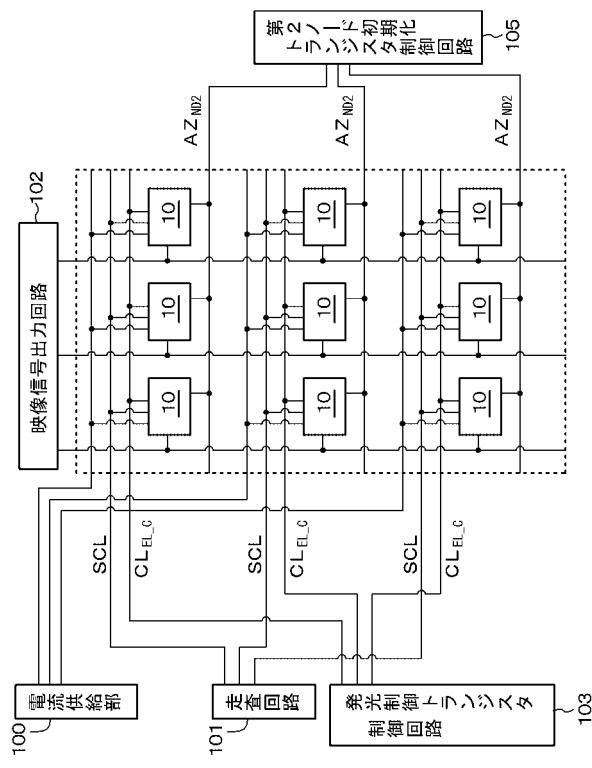

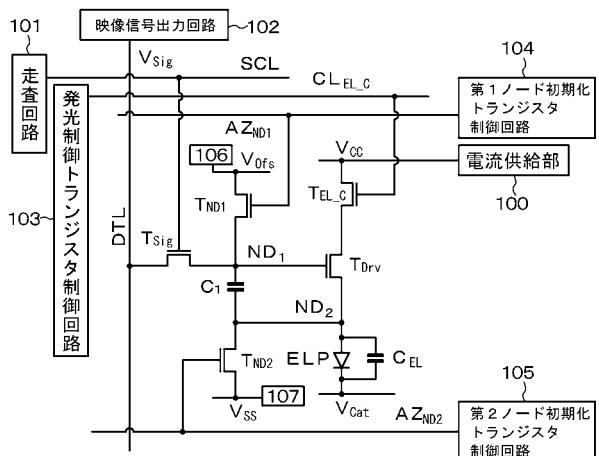

ところで、従来の有機 E L 表示装置は、図 17 及び図 2 に回路の概念図を示すように、

(イ) 電流供給部 100、

(ロ) 走査回路 101、

(ハ) 映像信号出力回路 102、

(ニ) 発光制御トランジスタ制御回路 103、

(ホ) 第 1 ノード初期化トランジスタ制御回路 104、

(ヘ) 第 2 ノード初期化トランジスタ制御回路 105、

50

(ト) 第1ノード初期化電源 106、

(チ) 第2ノード初期化電源 107、

(リ) 第1の方向にN個、第1の方向とは異なる第2の方向(具体的には、第1の方向に直交する方向)にM個、合計 $N \times M$ 個の、2次元マトリクス状に配列された有機EL素子10、

(ヌ) 走査回路101に接続され、第1の方向に延びるM本の走査線SCL、並びに、

(ル) 映像信号出力回路102に接続され、第2の方向に延びるN本のデータ線DTLを備えている。

### 【0015】

ここで、各有機EL素子10は、上述したとおり、5Tr/1C駆動回路、及び、発光部ELPを備えている。また、映像信号書き込みトランジスタ $T_{sig}$ の動作は、走査回路101に接続された走査線SCLに印加される電位(映像信号書き込みトランジスタ制御信号と呼ぶ)によって規定される。そして、上述した移動度補正処理の始点は、より具体的には、映像信号書き込みトランジスタ $T_{sig}$ がオン状態となり、データ線DTLから映像信号書き込みトランジスタ $T_{sig}$ を経由して駆動トランジスタ $T_{Drv}$ のゲート電極に映像信号に相当する電圧 $V_{sig}$ が印加され、発光制御トランジスタ制御回路103から発光制御トランジスタ制御線 $C_{L_{EL\_C}}$ を介して入力された発光制御トランジスタ制御信号によって発光制御トランジスタ $T_{EL\_C}$ がオン状態となり、その結果、駆動トランジスタ $T_{Drv}$ が発光制御トランジスタ $T_{EL\_C}$ を介して電流供給部100と接続されることによって第2ノードND<sub>2</sub>の電位が上昇し始めた時点である。一方、移動度補正処理の終点は、映像信号書き込みトランジスタ $T_{sig}$ がオフ状態となった時点、即ち、走査線SCLがローレベルとなり、映像信号書き込みトランジスタ $T_{sig}$ のゲート電極に低い電圧が印加された時点である。そして、移動度補正処理の時間長は、例えば、2~4マイクロ秒と、非常に短い時間である。

### 【0016】

【特許文献1】特開2006-215213

### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0017】

ところで、[期間-TP(5)<sub>5</sub>]の開始直前にあっては、発光制御トランジスタ $T_{EL\_C}$ はオフ状態であり、且つ、駆動トランジスタ $T_{Drv}$ もオフ状態にあるので、駆動トランジスタ $T_{Drv}$ のドレイン領域の電位とソース領域の電位は等しい。また、[期間-TP(5)<sub>5</sub>]にあっても、発光制御トランジスタ $T_{EL\_C}$ はオフ状態であるが故に、駆動トランジスタ $T_{Drv}$ がオン状態になっても、駆動トランジスタ $T_{Drv}$ のドレイン領域の電位とソース領域の電位は等しく、しかも、殆ど変化しない。

### 【0018】

次いで、移動度補正処理の開始時、発光制御トランジスタ $T_{EL\_C}$ はオン状態となる。このとき、駆動トランジスタ $T_{Drv}$ のドレイン領域の電位は、電流供給部の電圧 $V_{CC}$ へと上昇する。そして、この際、これらの電位の下降及び上昇といった現象の重ね合わせに基づき、駆動トランジスタ $T_{Drv}$ のドレイン領域、即ち、発光制御トランジスタ $T_{EL\_C}$ の他方のソース/ドレイン領域(以下、便宜上、ソース領域と呼ぶ)と、ゲート電極との間のカップリングによって、発光制御トランジスタ $T_{EL\_C}$ のゲート電極の電位変化に変動が生じる。

### 【0019】

ここで、第1の方向にN個、配列された有機EL素子10にあっては、各有機EL素子10を構成する駆動回路における発光制御トランジスタ $T_{EL\_C}$ のゲート電極は、発光制御トランジスタ制御線 $C_{L_{EL\_C}}$ を介して発光制御トランジスタ制御回路103に接続されている。従って、発光制御トランジスタ制御回路103の近くに位置する有機EL素子10における発光制御トランジスタ $T_{EL\_C}$ のゲート電極に印加される発光制御トランジスタ制御信号の波形の立上り部(変化開始部分)と、発光制御トランジスタ制御回路103から遠くに位置する有機EL素子10における発光制御トランジスタ $T_{EL\_C}$ のゲート電極に印

10

20

30

40

50

加される発光制御トランジスタ制御信号の波形の立上り部（変化開始部分）との間には、差異が生じる。一般に、発光制御トランジスタ制御回路 103 の近くに位置する有機 EL 素子 10 における発光制御トランジスタ  $T_{EL\_C}$  のゲート電極に印加される発光制御トランジスタ制御信号の波形の立上り部（変化開始部分）はシャープであり、発光制御トランジスタ制御回路 103 から遠くに位置する有機 EL 素子 10 における発光制御トランジスタ  $T_{EL\_C}$  のゲート電極に印加される発光制御トランジスタ制御信号の波形の立上り部（変化開始部分）は鈍っている。尚、発光制御トランジスタ  $T_{EL\_C}$  を  $n$  チャネル型としているので、発光制御トランジスタ  $T_{EL\_C}$  のゲート電極に印加される発光制御トランジスタ制御信号の波形の立上り部は、ローレベルの状態からハイレベルの状態に変化する部分である。一方、発光制御トランジスタ  $T_{EL\_C}$  を  $p$  チャネル型とする場合には、発光制御トランジスタ  $T_{EL\_C}$  のゲート電極に印加される発光制御トランジスタ制御信号の波形の立上り部は、ハイレベルの状態からローレベルの状態に変化する部分である。

10

## 【0020】

そして、このような発光制御トランジスタ制御信号の波形の立上り部（変化開始部分）に差異が生じ、しかも、上述したように、発光制御トランジスタ  $T_{EL\_C}$  のソース領域とゲート電極との間のカップリングに起因して発光制御トランジスタ  $T_{EL\_C}$  のゲート電極の電位変化に変動が生じると、これらの相乗効果によって、移動度補正処理の時間長に大きな変動が生じてしまう。即ち、各有機 EL 素子 10 に同じ電圧  $V_{sig}$  が印加されたときであっても、一般に、発光制御トランジスタ制御回路 103 と有機 EL 素子 10 との位置関係が、「近い」、「中程度」、「遠い」という関係にある場合、移動度補正処理の時間長の変動、更には、駆動トランジスタ  $T_{Drv}$  のソース領域における電位の上昇量  $\Delta V$ （電位補正值）は、発光制御トランジスタ  $T_{EL\_C}$  が  $n$  チャネル型である場合には、以下のとおりとなる。

20

## 【0021】

| 位置関係 | 移動度補正処理の時間長 | $\Delta V$ |

|------|-------------|------------|

| 近い   | 短い          | 小          |

| 中程度  | 中程度         | 中          |

| 遠い   | 長い          | 大          |

## 【0022】

ここで、移動度補正処理の時間長に生じる変動は、全期間  $t_0$  の 10% ~ 20% となることもあり、決して、無視できない変動である。そして、このように移動度補正処理の時間長  $t$  に変動  $\Delta t$  が生じる結果、発光制御トランジスタ制御回路 103 の近くに位置する有機 EL 素子 10 においては、第 2 ノード  $ND_2$  の電位上昇量（電位補正值）が  $\Delta V$  であったものが、発光制御トランジスタ制御回路 103 から遠くに位置する有機 EL 素子 10 においては、第 2 ノード  $ND_2$  の電位上昇量（電位補正值）が  $\Delta V' (> \Delta V)$  となってしまい、電位補正值に差異が生じる。その結果、同じ電圧  $V_{sig}$  が入力されたとしても、発光制御トランジスタ制御回路 103 の近くに位置する有機 EL 素子 10 と、発光制御トランジスタ制御回路 103 から遠くに位置する有機 EL 素子 10 とでは、上述した式（C）から、輝度に差異が生じてしまい、輝度差によってシェーディング（グラデーション）が発生する原因となる。

30

## 【0023】

従って、本発明の目的は、発光制御トランジスタ制御回路の近くに位置する有機 EL 素子と発光制御トランジスタ制御回路から遠くに位置する有機 EL 素子との間で、移動度補正処理の時間長に相違が生じ難い構成、構造、即ち、発光制御トランジスタ制御回路からの位置の遠近に依存すること無く、移動度補正処理の時間長を一定とし得る構成、構造を有する有機エレクトロルミネッセンス素子、及び、係る有機エレクトロルミネッセンス素子から構成された有機エレクトロルミネッセンス表示装置を提供することにある。

40

## 【課題を解決するための手段】

## 【0024】

上記の目的を達成するための本発明の有機エレクトロルミネッセンス素子（以下、有機

50

E L 素子と呼ぶ)は、駆動回路と、この駆動回路に接続された有機エレクトロルミネッセンス発光部とを備えた有機E L 素子である。

【0025】

また、上記の目的を達成するための本発明の有機エレクトロルミネッセンス表示装置(以下、有機E L 表示装置と呼ぶ)は、

- (a) 電流供給部、

- (b) 走査回路、

- (c) 映像信号出力回路、

- (d) 発光制御トランジスタ制御回路、

- (e) 第1の方向にN個、第1の方向とは異なる第2の方向にM個、合計 $N \times M$ 個の、

2次元マトリクス状に配列された有機エレクトロルミネッセンス素子、

- (f) 走査回路に接続され、第1の方向に延びるM本の走査線、並びに、

- (g) 映像信号出力回路に接続され、第2の方向に延びるN本のデータ線、

- を備えた有機E L 表示装置であり、

各有機エレクトロルミネッセンス素子は、駆動回路、及び、この駆動回路に接続された有機エレクトロルミネッセンス発光部を備えている。

【0026】

そして、本発明の有機E L 素子あるいは有機E L 表示装置において、駆動回路は、

- (A) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた駆動トランジスタ、

(B) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた映像信号書き込みトランジスタ、

(C) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた発光制御トランジスタ、並びに、

(D) 一対の電極を備えたコンデンサ部、

から構成されており、

駆動トランジスタにおいては、

(A-1) 他方のソース／ドレイン領域は、有機エレクトロルミネッセンス発光部に備えられたアノード電極に接続され、且つ、コンデンサ部の一方の電極に接続されており、第2ノードを構成し、

(A-2) ゲート電極は、映像信号書き込みトランジスタの他方のソース／ドレイン領域に接続され、且つ、コンデンサ部の他方の電極に接続されており、第1ノードを構成し、

映像信号書き込みトランジスタにおいては、

(B-1) 一方のソース／ドレイン領域は、データ線に接続されており、

(B-2) ゲート電極は、走査線に接続されており、

発光制御トランジスタにおいては、

(C-1) 一方のソース／ドレイン領域は、電流供給部に接続されており、

(C-2) 他方のソース／ドレイン領域は、駆動トランジスタの一方のソース／ドレン領域に接続されており、

(C-3) ゲート電極は、発光制御トランジスタ制御回路に接続されており、

駆動回路は、更に、

(E) 固定電源部に一方の電極が接続され、発光制御トランジスタの他方のソース／ドレン領域に他方の電極が接続された補助容量部、

を備えていることを特徴とする。

【0027】

本発明の有機E L 素子あるいは有機E L 表示装置にあっては、前記駆動回路は、

(F) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第2ノード初期化トランジスタ、

を更に備え、

第2ノード初期化トランジスタにおいては、

10

20

30

40

50

(F-1) 一方のソース／ドレイン領域は、第2ノードの電位を初期化するための電源（第2ノード初期化電源）に接続されており、

(F-2) 他方のソース／ドレイン領域は、第2ノードに接続されており、

(F-3) ゲート電極は、第2ノード初期化トランジスタ制御回路に接続されている、構成とすることができる。

#### 【0028】

更には、本発明の有機EL素子あるいは有機EL表示装置の上述した好ましい構成にあっては、前記駆動回路は、

(G) ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第1ノード初期化トランジスタ、

を更に備え、

第1ノード初期化トランジスタにおいては、

(G-1) 一方のソース／ドレイン領域は、第1ノードの電位を初期化するための電源（第1ノード初期化電源）に接続されており、

(G-2) 他方のソース／ドレイン領域は、第1ノードに接続されており、

(G-3) ゲート電極は、第1ノード初期化トランジスタ制御回路に接続されている、構成とすることができる。

#### 【0029】

以上に説明した好ましい構成を含む本発明の有機EL素子あるいは有機EL表示装置（以下、これらを総称して、単に、本発明と呼ぶ場合がある）において、電流供給部、走査回路、映像信号出力回路、発光制御トランジスタ制御回路、第1ノードの電位を初期化するための電源（第1ノード初期化電源）、第2ノードの電位を初期化するための電源（第2ノード初期化電源）、走査線、データ線、発光制御トランジスタ制御線、第1ノード初期化トランジスタ制御線、第2ノード初期化トランジスタ制御線、有機エレクトロルミネッセンス発光部（以下、単に、発光部と呼ぶ場合がある）の構成、構造は、周知の構成、構造とすることができる。具体的には、発光部は、例えば、アノード電極、正孔輸送層、発光層、電子輸送層、カソード電極等から構成することができる。

#### 【0030】

駆動回路の詳細は後述するが、上述したとおり、5つのトランジスタと1つのコンデンサ部から構成された駆動回路（5Tr/1C駆動回路）、4つのトランジスタと1つのコンデンサ部から構成された駆動回路（4Tr/1C駆動回路と呼ぶ）、あるいは又、3つのトランジスタと1つのコンデンサ部から構成された駆動回路（3Tr/1C駆動回路と呼ぶ）から構成することができる。

#### 【0031】

駆動回路を構成するトランジスタとして、nチャネル型の薄膜トランジスタ（TFT）を挙げることができるが、場合によっては、例えば、映像信号書き込みトランジスタや発光制御トランジスタ、第1ノード初期化トランジスタ、第2ノード初期化トランジスタにpチャネル型の薄膜トランジスタを用いることもできる。更には、シリコン半導体基板に形成された電界効果トランジスタ（例えば、MOSトランジスタ）から構成することもできる。補助容量部（コンデンサ）は、一方の電極、他方の電極、及び、これらの電極に挟まれた誘電体層（絶縁層）から構成することができる。コンデンサ部も、一方の電極、他方の電極、及び、これらの電極に挟まれた誘電体層（絶縁層）から構成することができる。駆動回路を構成するトランジスタ、コンデンサ部及び補助容量部は、或る平面内に形成され（例えば、支持体上に形成され）、発光部は、例えば、層間絶縁層を介して、駆動回路を構成するトランジスタ、コンデンサ部及び補助容量部の上方に形成されている。また、駆動トランジスタの他方のソース／ドレイン領域は、発光部に備えられたアノード電極に、例えば、コンタクトホールを介して接続されている。補助容量部の一方の電極は、例えば、コンタクトホールを介して電流供給部から延びる配線（電流供給線）あるいは電流供給線の延長部に接続すればよいし、あるいは又、電流供給線の延長部それ自体から構成することもできる。また、補助容量部の他方の電極は、例えば、駆動トランジスタの一方の

ソース／ドレイン領域と発光制御トランジスタの他方のソース／ドレイン領域との共通領域に接続され、あるいは又、係る共通領域の延在部に接続され、あるいは又、係る共通領域の延在部それ自体から構成されている形態とすることができる。

### 【0032】

補助容量部の容量値  $c_{sub}$  を異ならせた有機EL表示装置を各種試作して、発光制御トランジスタ制御回路の近くに位置する有機EL素子と発光制御トランジスタ制御回路から遠くに位置する有機EL素子との間で、移動度補正処理の時間長に相違が生じる状態を評価することで、最適な補助容量部の容量値  $c_{sub}$  を決定すればよい。容量値  $c_{sub}$  として、限定するものではないが、例えば、5fF乃至10fFを挙げることができる。

### 【発明の効果】

### 【0033】

本発明においては、例えば、固定電源部としての電流供給部に一方の電極が接続され、発光制御トランジスタの他方のソース／ドレイン領域に他方の電極が接続された補助容量部を備えている場合を想定すると、発光制御トランジスタの他方のソース／ドレイン領域とゲート電極との間のカップリングに起因した発光制御トランジスタのゲート電極の電位変化の変動を遅らせることができる。即ち、発光制御トランジスタ制御信号が発光制御トランジスタのゲート電極に入力されることによって発光制御トランジスタのゲート電極の電位に変化が生じ始めるが、補助容量部を備えているが故に、この発光制御トランジスタ制御信号の入力によって生じる発光制御トランジスタのゲート電極の電位の変化の方が、発光制御トランジスタの他方のソース／ドレイン領域とゲート電極との間のカップリングに起因した発光制御トランジスタのゲート電極の電位変化よりも十分に早く、係るカップリングに起因した発光制御トランジスタのゲート電極の電位変化を無視することができる。その結果、移動度補正処理の時間長に、発光制御トランジスタの他方のソース／ドレイン領域とゲート電極との間のカップリングに起因して大きな変動が生じてしまうといった現象の発生を確実に抑制することができる。それ故、輝度に差が生じ難く、シェーディング（グラデーション）が発生し難い、高い表示品質を有する有機エレクトロルミネッセンス表示装置を提供することができる。

### 【発明を実施するための最良の形態】

### 【0034】

以下、図面を参照して、実施例に基づき本発明を説明する。

### 【実施例1】

### 【0035】

実施例1は、本発明の有機EL素子及び有機EL表示装置に関する。実施例1における3トランジスタ／1コンデンサ部から基本的に構成された駆動回路の等価回路図を図11に示し、3トランジスタ／1コンデンサ部から基本的に構成された駆動回路の概念図を図12に示す。

### 【0036】

実施例1の有機EL表示装置は、

- (a) 電流供給部 100、

- (b) 走査回路 101、

- (c) 映像信号出力回路 102、

- (d) 発光制御トランジスタ制御回路 103、

(e) 第1の方向にN個、第1の方向とは異なる第2の方向（具体的には、第1の方向に直交する方向）にM個、合計 $N \times M$ 個の、2次元マトリクス状に配列された有機EL素子 10、

- (f) 走査回路 101に接続され、第1の方向に延びるM本の走査線 SCL、並びに、

- (g) 映像信号出力回路 102に接続され、第2の方向に延びるN本のデータ線 DTL

、を備えている。尚、図12、あるいは、後述する図2、図7においては、 $3 \times 3$ 個の有機EL素子 10を図示しているが、これは、あくまでも例示に過ぎない。

10

20

30

40

50

## 【0037】

各有機EL素子10は、駆動回路、及び、この駆動回路に接続された有機エレクトロルミネッセンス発光部（発光部ELP）を備えている。ここで、発光部ELPは、例えば、アノード電極、正孔輸送層、発光層、電子輸送層、カソード電極等の周知の構成、構造を有する。また、走査線SCLの一端に走査回路101が設けられており、電流供給線CSLの一端に電流供給部100が設けられている。電流供給部100、走査回路101、映像信号出力回路102、発光制御トランジスタ制御回路103、走査線SCL、データ線DTL、電流供給線CSLの構成、構造は、周知の構成、構造とすることができます。

## 【0038】

実施例1にあっては、駆動回路は、上述したとおり、3つのトランジスタと1つのコンデンサ部C<sub>1</sub>から構成された駆動回路（3Tr/1C駆動回路）から構成されている。即ち、実施例1の駆動回路は、図11に示すように、駆動トランジスタT<sub>Drv</sub>、映像信号書き込みトランジスタT<sub>Sig</sub>、発光制御トランジスタT<sub>EL\_C</sub>、及び、一対の電極を備えたコンデンサ部C<sub>1</sub>から構成されている。駆動トランジスタT<sub>Drv</sub>は、ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた、nチャネル型のTFTから成る。また、映像信号書き込みトランジスタT<sub>Sig</sub>も、ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた、nチャネル型のTFTから成る。更には、発光制御トランジスタT<sub>EL\_C</sub>も、ソース／ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた、nチャネル型のTFTから成る。尚、映像信号書き込みトランジスタT<sub>Sig</sub>、発光制御トランジスタT<sub>EL\_C</sub>は必ずしもnチャネル型のTFTである必要はなく、pチャネル型のTFTであってもよい。

10

20

## 【0039】

ここで、駆動トランジスタT<sub>Drv</sub>においては、

(A-1)他方のソース／ドレイン領域（便宜上、ソース領域と呼ぶ）は、発光部ELPに備えられたアノード電極に接続され、且つ、コンデンサ部C<sub>1</sub>の一方の電極に接続されており、第2ノードND<sub>2</sub>を構成し、

(A-2)ゲート電極は、映像信号書き込みトランジスタT<sub>Sig</sub>の他方のソース／ドレイン領域に接続され、且つ、コンデンサ部C<sub>1</sub>の他方の電極に接続されており、第1ノードND<sub>1</sub>を構成する。

30

## 【0040】

また、映像信号書き込みトランジスタT<sub>Sig</sub>においては、

(B-1)一方のソース／ドレイン領域は、データ線DTLに接続されており、

(B-2)ゲート電極は、走査線SCLに接続されている。

40

## 【0041】

更には、発光制御トランジスタT<sub>EL\_C</sub>においては、

(C-1)一方のソース／ドレイン領域（便宜上、ドレイン領域と呼ぶ）は、電流供給部100に電流供給線CSLを介して接続されており、

(C-2)他方のソース／ドレイン領域（便宜上、ソース領域と呼ぶ）は、駆動トランジスタT<sub>Drv</sub>の一方のソース／ドレイン領域（便宜上、ドレイン領域と呼ぶ）に接続されており、

(C-3)ゲート電極は、発光制御トランジスタ制御回路103に発光制御トランジスタ制御線CL<sub>EL\_C</sub>を介して接続されている。

## 【0042】

そして、駆動回路は、更に、

(E)固定電源部（具体的には、例えば電流供給部100）に一方の電極が接続され、発光制御トランジスタT<sub>EL\_C</sub>のソース領域に他方の電極が接続された補助容量部C<sub>Sub</sub>、を備えている。尚、電流供給部100と別個に固定電源部を設けてもよい。

50

## 【0043】

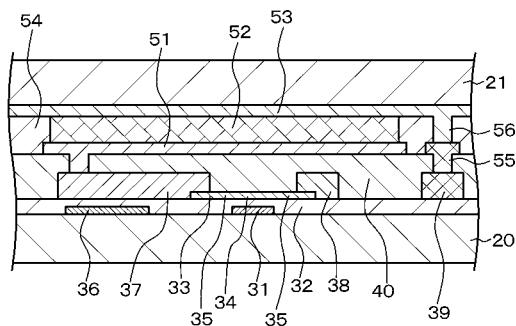

より具体的には、図16に一部分の模式的な一部断面図を示すように、駆動回路を構成するトランジスタT<sub>Sig</sub>、T<sub>Drv</sub>、T<sub>EL\_C</sub>及びコンデンサ部C<sub>1</sub>、補助容量部C<sub>Sub</sub>は支持体

上に形成され、発光部 E L P は、例えば、層間絶縁層 4 0 を介して、駆動回路を構成するトランジスタ  $T_{sig}$ ,  $T_{Drv}$ ,  $T_{EL\_C}$  及びコンデンサ部  $C_1$ 、補助容量部  $C_{Sub}$  の上方に形成されている。また、駆動トランジスタ  $T_{Drv}$  の他方のソース / ドレイン領域は、発光部 E L P に備えられたアノード電極に、コンタクトホールを介して接続されている。尚、図 16においては、駆動トランジスタ  $T_{Drv}$  のみを図示する。映像信号書き込みトランジスタ  $T_{sig}$ ,  $T_{EL\_C}$  及び補助容量部  $C_{Sub}$ 、あるいは、後述するその他の駆動回路における種々のトランジスタは隠れて見えない。

#### 【 0 0 4 4 】

より具体的には、駆動トランジスタ  $T_{Drv}$  は、ゲート電極 3 1、ゲート絶縁層 3 2、半導体層 3 3、半導体層 3 3 に設けられたソース / ドレイン領域 3 5、及び、ソース / ドレイン領域 3 5 の間の半導体層 3 3 の部分が該当するチャネル形成領域 3 4 から構成されている。一方、コンデンサ部  $C_1$  は、他方の電極 3 6、ゲート絶縁層 3 2 の延在部から構成された誘電体層、及び、一方の電極 3 7 ( 第 2 ノード  $N D_2$  に相当する ) から成る。ゲート電極 3 1、ゲート絶縁層 3 2 の一部、及びコンデンサ部  $C_1$  を構成する他方の電極 3 6 は、支持体 2 0 上に形成されている。駆動トランジスタ  $T_{Drv}$  の一方のソース / ドレイン領域 3 5 は配線 3 8 に接続され、他方のソース / ドレイン領域 3 5 は一方の電極 3 7 ( 第 2 ノード  $N D_2$  に相当する ) に接続されている。駆動トランジスタ  $T_{Drv}$  及びコンデンサ部  $C_1$  等は、層間絶縁層 4 0 で覆われており、層間絶縁層 4 0 上に、アノード電極 5 1、正孔輸送層、発光層、電子輸送層、及び、カソード電極 5 3 から成る発光部 E L P が設けられている。尚、図面においては、正孔輸送層、発光層、及び、電子輸送層を 1 層 5 2 で表した。発光部 E L P が設けられていない層間絶縁層 4 0 の部分の上には、第 2 層間絶縁層 5 4 が設けられ、第 2 層間絶縁層 5 4 及びカソード電極 5 3 上には透明な基板 2 1 が配置されており、発光層にて発光した光は、基板 2 1 を通過して、外部に出射される。尚、一方の電極 3 7 ( 第 2 ノード  $N D_2$  ) とアノード電極 5 1 とは、層間絶縁層 4 0 に設けられたコンタクトホールによって接続されている。また、カソード電極 5 3 は、第 2 層間絶縁層 5 4、層間絶縁層 4 0 に設けられたコンタクトホール 5 6, 5 5 を介して、ゲート絶縁層 3 2 の延在部上に設けられた配線 3 9 に接続されている。

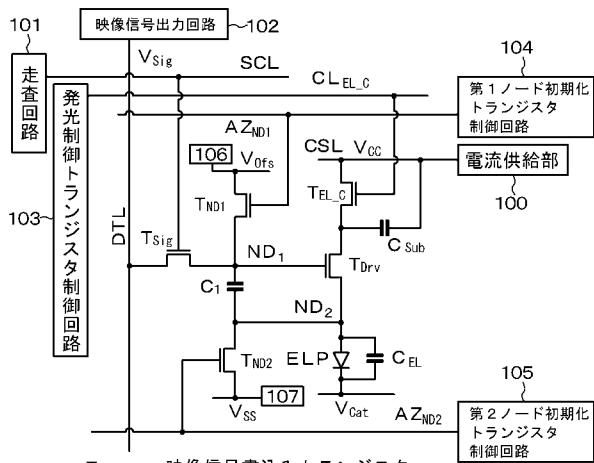

#### 【 0 0 4 5 】

尚、駆動回路を、4つのトランジスタと1つのコンデンサ部  $C_1$  から構成された駆動回路 ( 4 T r / 1 C 駆動回路 ) から構成することもできる。4 T r / 1 C 駆動回路の等価回路図を図 6 に示し、4 T r / 1 C 駆動回路の概念図を図 7 に示す。この 4 T r / 1 C 駆動回路を備えた有機 E L 表示装置は、更に、第 2 ノード初期化トランジスタ制御回路 1 0 5 及び、第 2 ノード初期化電源 1 0 7 を備えている。そして、この 4 T r / 1 C 駆動回路は、上述した 3 T r / 1 C 駆動回路の構成要件に加えて、ソース / ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第 2 ノード初期化トランジスタ  $T_{ND_2}$  を更に備えている。ここで、この第 2 ノード初期化トランジスタ  $T_{ND_2}$  においては、一方のソース / ドレイン領域は、第 2 ノードの電位を初期化するための電源 ( 第 2 ノード初期化電源 1 0 7 ) に接続されており、他方のソース / ドレイン領域は第 2 ノード  $N D_2$  に接続されており、ゲート電極は、第 2 ノード初期化トランジスタ制御線  $A Z_{ND_2}$  を介して第 2 ノード初期化トランジスタ制御回路 1 0 5 に接続されている。

#### 【 0 0 4 6 】

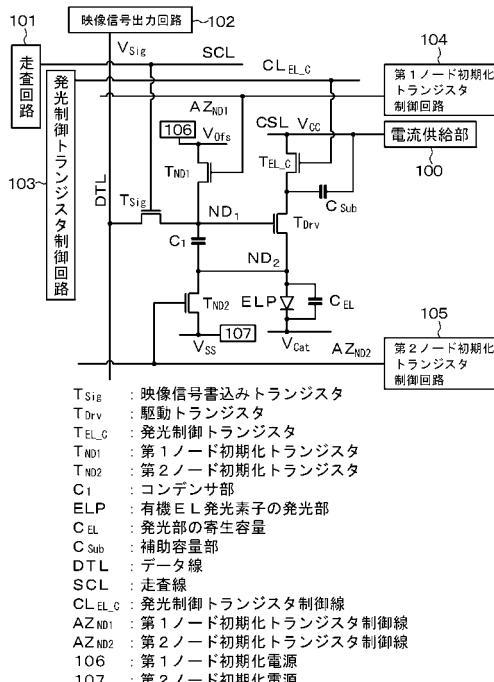

あるいは又、駆動回路を、5つのトランジスタと1つのコンデンサ部  $C_1$  から構成された駆動回路 ( 5 T r / 1 C 駆動回路 ) から構成することもできる。5 T r / 1 C 駆動回路の等価回路図を図 1 に示し、5 T r / 1 C 駆動回路の概念図を図 2 に示す。この 5 T r / 1 C 駆動回路を備えた有機 E L 表示装置は、更に、第 1 ノード初期化トランジスタ制御回路 1 0 4 及び、第 1 ノード初期化電源 1 0 6 を備えている。そして、この 5 T r / 1 C 駆動回路は、上述した 4 T r / 1 C 駆動回路の構成要件に加えて、ソース / ドレイン領域、チャネル形成領域、及び、ゲート電極を備えた第 1 ノード初期化トランジスタ  $T_{ND_1}$  を更に備えている。ここで、この第 1 ノード初期化トランジスタ  $T_{ND_1}$  においては、一方のソース / ドレイン領域は、第 1 ノードの電位を初期化するための電源 ( 第 1 ノード初期化

10

20

30

40

50

電源 106) に接続されており、他方のソース / ドレイン領域は第 1 ノード ND<sub>1</sub> に接続されており、ゲート電極は、第 1 ノード初期化トランジスタ制御線 AZ<sub>ND1</sub> を介して第 1 ノード初期化トランジスタ制御回路 104 に接続されている。

#### 【0047】

以上に説明した変形例を含む実施例 1 にあっては、固定電源部の一例としての電流供給部 100 に電流供給線 CSL を介して一方の電極が接続され、発光制御トランジスタ T<sub>EL\_C</sub> のソース領域（駆動トランジスタ T<sub>Drv</sub> のドレイン領域と共通の領域である）に他方の電極が接続された補助容量部 C<sub>Sub</sub> を備えている。そして、発光制御トランジスタ制御信号が発光制御トランジスタ T<sub>EL\_C</sub> のゲート電極に入力されることによって発光制御トランジスタ T<sub>EL\_C</sub> のゲート電極の電位に変化が生じ始める。然るに、補助容量部 C<sub>Sub</sub> を備えているが故に、この発光制御トランジスタ制御信号の入力によって生じる発光制御トランジスタ T<sub>EL\_C</sub> のゲート電極の電位の変化の方が、発光制御トランジスタ T<sub>EL\_C</sub> のソース領域とゲート電極との間のカップリングに起因した発光制御トランジスタ T<sub>EL\_C</sub> のゲート電極の電位変化よりも十分に早く、係るカップリングに起因した発光制御トランジスタ T<sub>EL\_C</sub> のゲート電極の電位変化を無視することができる。その結果、移動度補正処理の時間長に、発光制御トランジスタ T<sub>EL\_C</sub> のソース領域とゲート電極との間のカップリングに起因して大きな変動が生じてしまうといった現象の発生を確実に抑制することができる。10

#### 【0048】

以下、5Tr / 1C 駆動回路、4Tr / 1C 駆動回路、3Tr / 1C 駆動回路、及び、これらの駆動回路を用いた発光部 ELP の駆動方法を説明する。尚、以下の説明においては、補助容量部 C<sub>Sub</sub> に関する記述、即ち、これらの駆動回路には補助容量部 C<sub>Sub</sub> が備えられ、あるいは又、設けられているが、その旨の記載は省略した。20

#### 【0049】

有機 EL 表示装置は、(N / 3) × M 個の 2 次元マトリクス状に配列された画素から構成されているが、以下の説明において、1つの画素は、3つの副画素（赤色を発光する赤色発光副画素、緑色を発光する緑色発光副画素、青色を発光する青色発光副画素）から構成されているとする。また、各画素を構成する有機 EL 素子 10 は、線順次駆動されるとし、表示フレームレートを FR (回 / 秒) とする。即ち、第 m 行目（但し、m = 1, 2, 3, ..., M）に配列された (N / 3) 個の画素 (N 個の副画素) のそれぞれを構成する有機 EL 素子 10 が同時に駆動される。換言すれば、1つの行を構成する各有機 EL 素子 10 にあっては、その発光 / 非発光のタイミングは、それらが属する行単位で制御される。尚、1つの行を構成する各画素について映像信号を書き込む処理は、全ての画素について同時に映像信号を書き込む処理（以下、単に、同時書き込み処理と呼ぶ場合がある）であってもよいし、各画素毎に順次映像信号を書き込む処理（以下、単に、順次書き込み処理と呼ぶ場合がある）であってもよい。いずれの書き込み処理とするかは、駆動回路の構成に応じて適宜選択すればよい。30

#### 【0050】

ここで、原則として、第 m 行目、第 n 列（但し、n = 1, 2, 3, ..., N）に位置する画素における 1 つの副画素を構成する有機 EL 素子 10 に関する駆動、動作を説明するが、係る副画素あるいは有機 EL 素子 10 を、以下、第 (n, m) 番目の副画素あるいは第 (n, m) 番目の有機 EL 素子 10 と呼ぶ。そして、第 m 行目に配列された各有機 EL 素子 10 の水平走査期間（第 m 番目の水平走査期間）が終了するまでに、各種の処理（後述する閾値電圧キャセル処理、書き込み処理、移動度補正処理）が行われる。尚、書き込み処理は、第 m 番目の水平走査期間内に行われる必要がある。一方、駆動回路の種類によっては、閾値電圧キャセル処理や移動度補正処理、これに伴う前処理を第 m 番目の水平走査期間より先行して行うことができる。40

#### 【0051】

そして、上述した各種の処理が全て終了した後、第 m 行目に配列された各有機 EL 素子 10 を構成する発光部を発光させる。尚、上述した各種の処理が全て終了した後、直ちに発光部を発光させてもよいし、所定の期間（例えば、所定の行数分の水平走査期間）が経50

過した後に発光部を発光させてもよい。この所定の期間は、有機EL表示装置の仕様や駆動回路の構成等に応じて、適宜設定することができる。尚、以下の説明においては、説明の便宜のため、各種の処理終了後、直ちに発光部を発光させるものとする。そして、第m行目に配列された各有機EL素子10を構成する発光部の発光は、第(m+m')行目に配列された各有機EL素子10の水平走査期間の開始直前まで継続される。ここで、「m'」は、有機EL表示装置の設計仕様によって決定される。即ち、或る表示フレームの第m行目に配列された各有機EL素子10を構成する発光部の発光は、第(m+m'-1)番目の水平走査期間まで継続される。一方、第(m+m')番目の水平走査期間の始期から、次の表示フレームにおける第m番目の水平走査期間内において書き込み処理や移動度補正処理が完了するまで、第m行目に配列された各有機EL素子10を構成する発光部は、原則として、非発光状態を維持する。上述した非発光状態の期間（以下、単に、非発光期間と呼ぶ場合がある）を設けることにより、アクティブマトリクス駆動に伴う残像ボケが低減され、動画品位をより優れたものとすることができます。但し、各副画素（有機EL素子10）の発光状態／非発光状態は、以上に説明した状態に限定するものではない。また、水平走査期間の時間長は、(1/FR) × (1/M) 秒未満の時間長である。(m+m')の値がMを越える場合、越えた分の水平走査期間は、次の表示フレームにおいて処理される。

10

## 【0052】

1つのトランジスタの有する2つのソース／ドレイン領域において、「一方のソース／ドレイン領域」という用語を、電源部に接続された側のソース／ドレイン領域といった意味において使用する場合がある。また、トランジスタがオン状態にあるとは、ソース／ドレイン領域間にチャネルが形成されている状態を意味する。係るトランジスタの一方のソース／ドレイン領域から他方のソース／ドレイン領域に電流が流れているか否かは問わない。一方、トランジスタがオフ状態にあるとは、ソース／ドレイン領域間にチャネルが形成されていない状態を意味する。また、或るトランジスタのソース／ドレイン領域が他のトランジスタのソース／ドレイン領域に接続されているとは、或るトランジスタのソース／ドレイン領域と他のトランジスタのソース／ドレイン領域とが同じ領域を占めている形態を包含する。更には、ソース／ドレイン領域は、不純物を含有したポリシリコンやアモルファスシリコン等の導電性物質から構成することができるだけでなく、金属、合金、導電性粒子、これらの積層構造、有機材料（導電性高分子）から成る層から構成することができる。また、以下の説明で用いるタイミングチャートにおいて、各期間を示す横軸の長さ（時間長）は模式的なものであり、各期間の時間長の割合を示すものではない。

20

## 【0053】

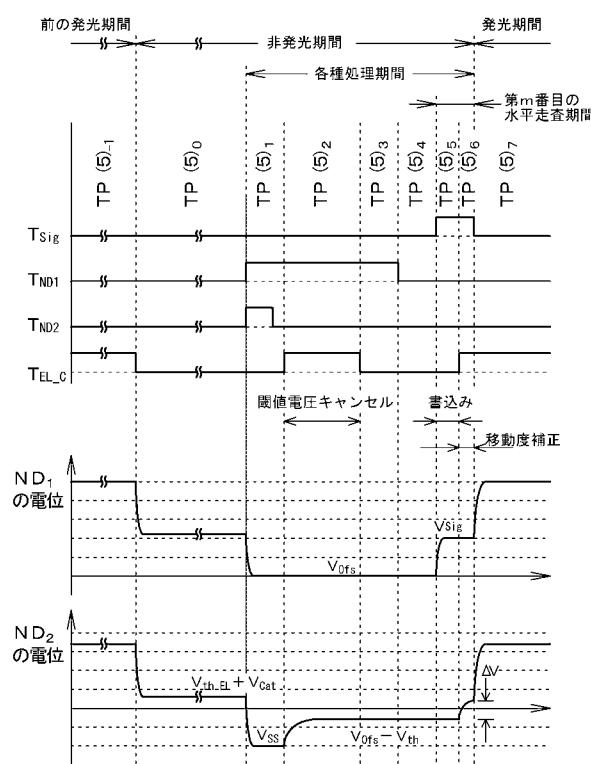

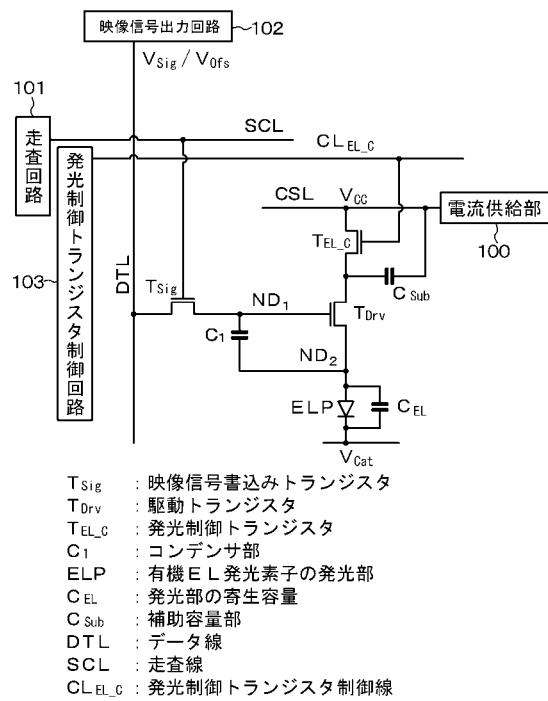

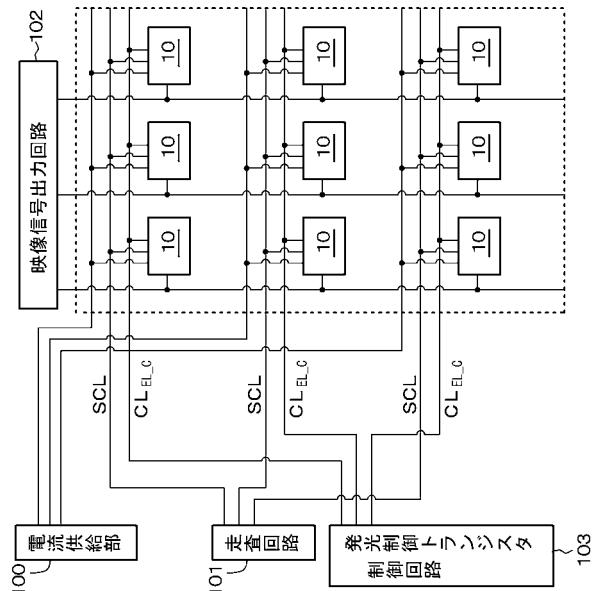

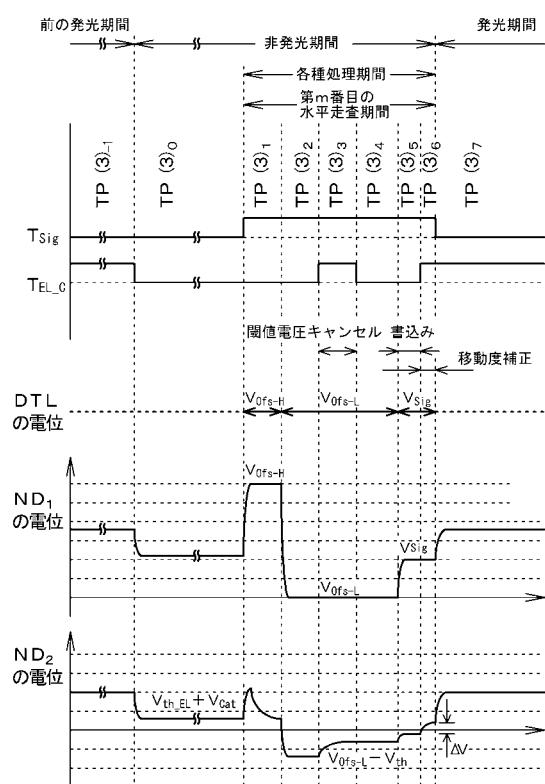

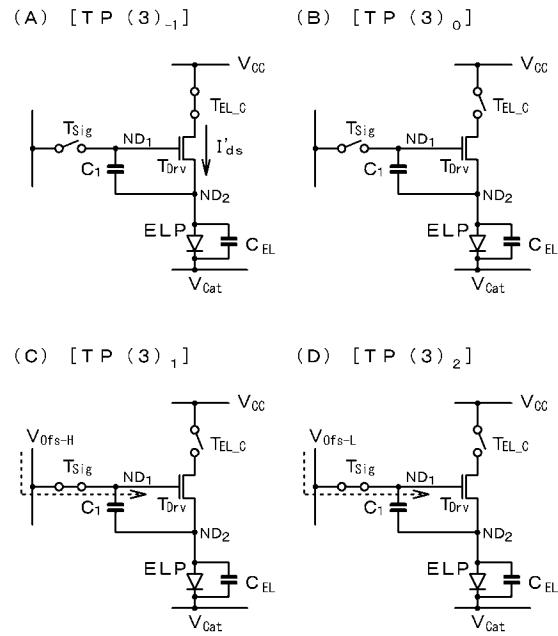

## [5Tr/1C駆動回路]

5Tr/1C駆動回路の等価回路図を図1に示し、概念図を図2を示し、駆動のタイミングチャートを模式的に図3に示し、各トランジスタのオン／オフ状態等を模式的に図4の(A)～(D)及び図5の(A)～(E)に示す。尚、駆動の状態を模式的に示す図4、図5、図9、図10、図14、図15において、補助容量部C<sub>Sub</sub>の図示を省略した。また、図2においては第1ノード初期化電源106、第2ノード初期化電源107の図示を省略し、図7においては第2ノード初期化電源107の図示を省略した。

30

## 【0054】

この5Tr/1C駆動回路は、上述したとおり、映像信号書き込みトランジスタT<sub>Sig</sub>、駆動トランジスタT<sub>Drv</sub>、発光制御トランジスタT<sub>EL\_C</sub>、第1ノード初期化トランジスタT<sub>ND1</sub>、第2ノード初期化トランジスタT<sub>ND2</sub>の5つのトランジスタから構成され、更には、1つのコンデンサ部C<sub>1</sub>から構成されている。

40

## 【0055】

[発光制御トランジスタT<sub>EL\_C</sub>]

発光制御トランジスタT<sub>EL\_C</sub>の一方のソース／ドレイン領域は、電流供給部100（電圧V<sub>CC</sub>）に電流供給線C<sub>SL</sub>を介して接続され、発光制御トランジスタT<sub>EL\_C</sub>の他方のソース／ドレイン領域は、駆動トランジスタT<sub>Drv</sub>の一方のソース／ドレイン領域に接続さ

50

れている。また、発光制御トランジスタ  $T_{EL\_C}$  のオン / オフ動作は、発光制御トランジスタ  $T_{EL\_C}$  のゲート電極に接続された発光制御トランジスタ制御線  $C_{L_{EL\_C}}$  によって制御される。尚、電流供給部 100 は、有機 EL 素子 10 の発光部 ELP に電流を供給し、発光部 ELP の発光を制御するために設けられている。また、発光制御トランジスタ制御線  $C_{L_{EL\_C}}$  は、発光制御トランジスタ制御回路 103 に接続されている。

#### 【0056】

##### [ 駆動トランジスタ $T_{Drv}$ ]

駆動トランジスタ  $T_{Drv}$  の一方のソース / ドレイン領域は、上述のとおり、発光制御トランジスタ  $T_{EL\_C}$  の他方のソース / ドレイン領域に接続されている。即ち、駆動トランジスタ  $T_{Drv}$  の一方のソース / ドレイン領域は、発光制御トランジスタ  $T_{EL\_C}$  を介して、電流供給部 100 に接続されている。一方、駆動トランジスタ  $T_{Drv}$  の他方のソース / ドレイン領域は、

(1) 発光部 ELP のアノード電極、

(2) 第 2 ノード初期化トランジスタ  $T_{ND2}$  の他方のソース / ドレイン領域、及び、

(3) コンデンサ部  $C_1$  の一方の電極、

に接続されており、第 2 ノード  $ND_2$  を構成する。また、駆動トランジスタ  $T_{Drv}$  のゲート電極は、

(1) 映像信号書き込みトランジスタ  $T_{Sig}$  の他方のソース / ドレイン領域、

(2) 第 1 ノード初期化トランジスタ  $T_{ND1}$  の他方のソース / ドレイン領域、及び、

(3) コンデンサ部  $C_1$  の他方の電極、

に接続されており、第 1 ノード  $ND_1$  を構成する。

#### 【0057】

ここで、駆動トランジスタ  $T_{Drv}$  は、有機 EL 素子 10 の発光状態においては、以下の式 (1) に従ってドレイン電流  $I_{ds}$  を流すように駆動される。有機 EL 素子 10 の発光状態においては、駆動トランジスタ  $T_{Drv}$  の一方のソース / ドレイン領域はドレイン領域として働き、他方のソース / ドレイン領域はソース領域として働く。説明の便宜のため、以下の説明において、駆動トランジスタ  $T_{Drv}$  の一方のソース / ドレイン領域を単にドレイン領域と呼び、他方のソース / ドレイン領域を単にソース領域と呼ぶ場合がある。尚、

$\mu$  : 実効的な移動度

$L$  : チャネル長

$W$  : チャネル幅

$V_{gs}$  : ゲート電極とソース領域との間の電位差

$V_{th}$  : 閾値電圧

$C_{ox}$  : ( ゲート絶縁層の比誘電率 ) × ( 真空の誘電率 ) / ( ゲート絶縁層の厚さ )

$k$  ( 1 / 2 ) · (  $W / L$  ) ·  $C_{ox}$

とする。

#### 【0058】

$$I_{ds} = k \cdot \mu \cdot (V_{gs} - V_{th})^2 \quad (1)$$

#### 【0059】

このドレイン電流  $I_{ds}$  が有機 EL 素子 10 の発光部 ELP を流れることで、有機 EL 素子 10 の発光部 ELP が発光する。更には、このドレイン電流  $I_{ds}$  の値の大小によって、有機 EL 素子 10 の発光部 ELP における発光状態 ( 輝度 ) が制御される。

#### 【0060】

##### [ 映像信号書き込みトランジスタ $T_{Sig}$ ]

映像信号書き込みトランジスタ  $T_{Sig}$  の他方のソース / ドレイン領域は、上述のとおり、駆動トランジスタ  $T_{Drv}$  のゲート電極に接続されている。一方、映像信号書き込みトランジスタ  $T_{Sig}$  の一方のソース / ドレイン領域は、データ線 DTL に接続されている。そして、映像信号出力回路 102 からデータ線 DTL を介して、発光部 ELP における輝度を制御するための映像信号 ( 駆動信号、輝度信号 )  $V_{Sig}$  が、一方のソース / ドレイン領域に供給される。尚、データ線 DTL を介して、 $V_{Sig}$  以外の種々の信号・電圧 ( プリチャーパターン ) が供給される。

10

20

30

40

50

ジ駆動のための信号や各種の基準電圧等)が、一方のソース/ドレイン領域に供給されてもよい。また、映像信号書き込みトランジスタ $T_{Sig}$ のオン/オフ動作は、映像信号書き込みトランジスタ $T_{Sig}$ のゲート電極に接続された走査線SCLによって制御される。

#### 【0061】

##### [第1ノード初期化トランジスタ $T_{ND1}$ ]

第1ノード初期化トランジスタ $T_{ND1}$ の他方のソース/ドレイン領域は、上述のとおり、駆動トランジスタ $T_{Drv}$ のゲート電極に接続されている。一方、第1ノード初期化トランジスタ $T_{ND1}$ の一方のソース/ドレイン領域には、第1ノードND<sub>1</sub>の電位(即ち、駆動トランジスタ $T_{Drv}$ のゲート電極の電位)を初期化するための電圧 $V_{Ofs}$ が第1ノードND<sub>1</sub>の電位を初期化するための電源(第1ノード初期化電源106)から供給される。また、第1ノード初期化トランジスタ $T_{ND1}$ のオン/オフ動作は、第1ノード初期化トランジスタ $T_{ND1}$ のゲート電極に接続された第1ノード初期化トランジスタ制御線AZ<sub>ND1</sub>によって制御される。第1ノード初期化トランジスタ制御線AZ<sub>ND1</sub>は、第1ノード初期化トランジスタ制御回路104に接続されている。

10

#### 【0062】

##### [第2ノード初期化トランジスタ $T_{ND2}$ ]

第2ノード初期化トランジスタ $T_{ND2}$ の他方のソース/ドレイン領域は、上述のとおり、駆動トランジスタ $T_{Drv}$ のソース領域に接続されている。一方、第2ノード初期化トランジスタ $T_{ND2}$ の一方のソース/ドレイン領域には、第2ノードND<sub>2</sub>の電位(即ち、駆動トランジスタ $T_{Drv}$ のソース領域の電位)を初期化するための電圧 $V_{SS}$ が第2ノードND<sub>2</sub>の電位を初期化するための電源(第2ノード初期化電源107)から供給される。また、第2ノード初期化トランジスタ $T_{ND2}$ のオン/オフ動作は、第2ノード初期化トランジスタ $T_{ND2}$ のゲート電極に接続された第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>によって制御される。第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>は、第2ノード初期化トランジスタ制御回路105に接続されている。

20

#### 【0063】

##### [発光部ELP]

発光部ELPのアノード電極は、上述のとおり、駆動トランジスタ $T_{Drv}$ のソース領域に接続されている。一方、発光部ELPのカソード電極には、電圧 $V_{Cat}$ が印加される。発光部ELPの寄生容量を符号 $C_{EL}$ で表す。また、発光部ELPの発光に必要とされる閾値電圧を $V_{th-EL}$ とする。即ち、発光部ELPのアノード電極とカソード電極との間に $V_{th-EL}$ 以上の電圧が印加されると、発光部ELPは発光する。

30

#### 【0064】

以下の説明において、電圧あるいは電位の値を以下のとおりとするが、これは、あくまでも説明のための値であり、これらの値に限定されるものではない。

#### 【0065】

$V_{Sig}$  : 発光部ELPにおける輝度を制御するための映像信号

・・・0ボルト~10ボルト

$V_{CC}$  : 発光部ELPの発光を制御するための電流供給部の電圧

・・・20ボルト

40

$V_{Ofs}$  : 駆動トランジスタ $T_{Drv}$ のゲート電極の電位(第1ノードND<sub>1</sub>の電位)を初期化するための電圧

・・・0ボルト

$V_{SS}$  : 駆動トランジスタ $T_{Drv}$ のソース領域の電位(第2ノードND<sub>2</sub>の電位)を初期化するための電圧

・・・-10ボルト

$V_{th}$  : 駆動トランジスタ $T_{Drv}$ の閾値電圧

・・・3ボルト

$V_{Cat}$  : 発光部ELPのカソード電極に印加される電圧

・・・0ボルト

50

$V_{th-EL}$  : 発光部 E L P の閾値電圧

・・・ 3 ボルト

#### 【0066】

以下、5 Tr / 1 C 駆動回路の動作説明を行う。尚、上述したように、各種の処理（閾値電圧キャンセル処理、書き込み処理、移動度補正処理）が全て完了した後、直ちに発光状態が始まるものとして説明するが、これに限るものではない。後述する4 Tr / 1 C 駆動回路、3 Tr / 1 C 駆動回路の説明においても同様である。

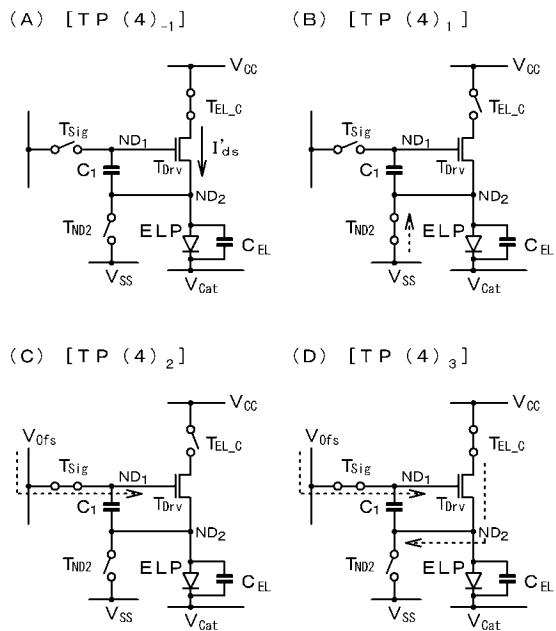

#### 【0067】

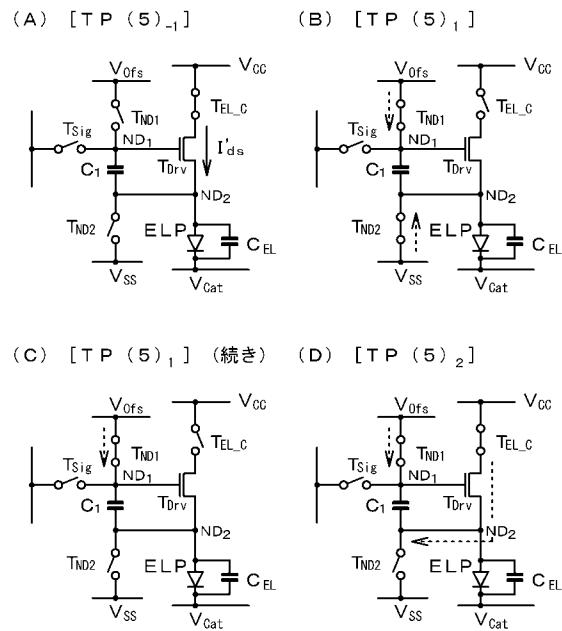

[期間 - TP(5)\_1] (図4の(A)参照)

この[期間 - TP(5)\_1]は、例えば、前の表示フレームにおける動作であり、前回の各種の処理完了後に第(n, m)番目の有機EL素子10が発光状態にある期間である。即ち、第(n, m)番目の副画素を構成する有機EL素子10における発光部E L Pには、後述する式(5)に基づくドレイン電流 $I_{ds}$ が流れしており、第(n, m)番目の副画素を構成する有機EL素子10の輝度は、係るドレイン電流 $I_{ds}$ に対応した値である。ここで、映像信号書き込みトランジスタ $T_{Sig}$ 、第1ノード初期化トランジスタ $T_{ND1}$ 及び第2ノード初期化トランジスタ $T_{ND2}$ はオフ状態であり、発光制御トランジスタ $T_{EL_C}$ 及び駆動トランジスタ $T_{Drv}$ はオン状態である。第(n, m)番目の有機EL素子10の発光状態は、第(m+m')行目に配列された有機EL素子10の水平走査期間の開始直前まで継続される。

#### 【0068】

図3に示す[期間 - TP(5)\_0] ~ [期間 - TP(5)\_4]は、前回の各種の処理完了後の発光状態が終了した後から、次の書き込み処理が行われる直前までの動作期間である。即ち、この[期間 - TP(5)\_0] ~ [期間 - TP(5)\_4]は、例えば、前の表示フレームにおける第(m+m')番目の水平走査期間の始期から、現表示フレームにおける第(m-1)番目の水平走査期間の終期までの或る時間長さの期間である。尚、[期間 - TP(5)\_1] ~ [期間 - TP(5)\_4]を、現表示フレームにおける第m番目の水平走査期間内に含む構成とすることもできる。

#### 【0069】

そして、この[期間 - TP(5)\_0] ~ [期間 - TP(5)\_4]において、第(n, m)番目の有機EL素子10は、原則として、非発光状態にある。即ち、[期間 - TP(5)\_0] ~ [期間 - TP(5)\_1]、[期間 - TP(5)\_3] ~ [期間 - TP(5)\_4]においては、発光制御トランジスタ $T_{EL_C}$ はオフ状態であるので、有機EL素子10は発光しない。尚、[期間 - TP(5)\_2]においては、発光制御トランジスタ $T_{EL_C}$ はオン状態となる。しかし、この期間においては後述する閾値電圧キャンセル処理が行われている。閾値電圧キャンセル処理の説明において詳しく述べるが、後述する式(2)を満たすことを前提とすれば、有機EL素子10が発光することはない。

#### 【0070】

以下、[期間 - TP(5)\_0] ~ [期間 - TP(5)\_4]の各期間について、先ず、説明する。尚、[期間 - TP(5)\_1]の始期や、[期間 - TP(5)\_1] ~ [期間 - TP(5)\_4]の各期間の長さは、有機EL表示装置の設計に応じて適宜設定すればよい。

#### 【0071】

[期間 - TP(5)\_0]

上述したように、この[期間 - TP(5)\_0]において、第(n, m)番目の有機EL素子10は、非発光状態にある。映像信号書き込みトランジスタ $T_{Sig}$ 、第1ノード初期化トランジスタ $T_{ND1}$ 、第2ノード初期化トランジスタ $T_{ND2}$ はオフ状態である。また、[期間 - TP(5)\_1]から[期間 - TP(5)\_0]に移る時点で、発光制御トランジスタ $T_{EL_C}$ がオフ状態となるが故に、第2ノードND<sub>2</sub>(駆動トランジスタ $T_{Drv}$ のソース領域あるいは発光部E L Pのアノード電極)の電位は、( $V_{th-EL} + V_{Cat}$ )まで低下し、発光部E L Pは非発光状態となる。また、第2ノードND<sub>2</sub>の電位低下に倣うように、浮遊状態の第1ノードND<sub>1</sub>(駆動トランジスタ $T_{Drv}$ のゲート電極)の電位も低下する。

10

20

30

40

50

## 【0072】

[期間 - TP(5)<sub>1</sub>] (図4の(B)及び(C)参照)

この[期間 - TP(5)<sub>1</sub>]において、後述する閾値電圧キャンセル処理を行うための前処理が行われる。即ち、[期間 - TP(5)<sub>1</sub>]の開始時、第1ノード初期化トランジスタ制御回路104及び第2ノード初期化トランジスタ制御回路105の動作に基づき第1ノード初期化トランジスタ制御線AZ<sub>ND1</sub>及び第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>をハイレベルとすることによって、第1ノード初期化トランジスタT<sub>ND1</sub>及び第2ノード初期化トランジスタT<sub>ND2</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>ofs</sub>(例えば、0ボルト)となる。一方、第2ノードND<sub>2</sub>の電位は、V<sub>ss</sub>(例えば、-10ボルト)となる。そして、この[期間 - TP(5)<sub>1</sub>]の完了以前において、第2ノード初期化トランジスタ制御回路105の動作に基づき第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>をローレベルとすることによって、第2ノード初期化トランジスタT<sub>ND2</sub>をオフ状態とする。尚、第1ノード初期化トランジスタT<sub>ND1</sub>のオン状態及び第2ノード初期化トランジスタT<sub>ND2</sub>を同時にオン状態としてもよいし、第1ノード初期化トランジスタT<sub>ND1</sub>を先にオン状態としてもよいし、第2ノード初期化トランジスタT<sub>ND2</sub>を先にオン状態としてもよい。

10

## 【0073】

以上の処理により、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>th</sub>以上となり、駆動トランジスタT<sub>Drv</sub>はオン状態となる。

20

## 【0074】

[期間 - TP(5)<sub>2</sub>] (図4の(D)参照)

次に、閾値電圧キャンセル処理が行われる。即ち、第1ノード初期化トランジスタT<sub>ND1</sub>のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線CL<sub>EL\_C</sub>をハイレベルとすることによって、発光制御トランジスタT<sub>EL\_C</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は変化しないが(V<sub>ofs</sub>=0ボルトを維持)、第1ノードND<sub>1</sub>の電位から駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>を減じた電位に向かって、第2ノードND<sub>2</sub>の電位は変化する。即ち、浮遊状態の第2ノードND<sub>2</sub>の電位は上昇する。そして、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>th</sub>に達すると、駆動トランジスタT<sub>Drv</sub>がオフ状態となる。具体的には、浮遊状態の第2ノードND<sub>2</sub>の電位が(V<sub>ofs</sub> - V<sub>th</sub> = -3ボルト > V<sub>ss</sub>)に近づき、最終的に(V<sub>ofs</sub> - V<sub>th</sub>)となる。ここで、以下の式(2)が保証されていれば、云い換えれば、式(2)を満足するように電位を選択、決定しておけば、発光部ELPが発光することはない。尚、定性的には、閾値電圧キャンセル処理において、第1ノードND<sub>1</sub>と第2ノードND<sub>2</sub>との間の電位差(換言すれば、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差)が駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>に近づく程度は、閾値電圧キャンセル処理の時間により左右される。従って、例えば閾値電圧キャンセル処理の時間を充分長く確保した場合には、第1ノードND<sub>1</sub>と第2ノードND<sub>2</sub>との間の電位差は駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>に達し、駆動トランジスタT<sub>Drv</sub>はオフ状態となる。一方、例えば閾値電圧キャンセル処理の時間を短く設定した場合には、第1ノードND<sub>1</sub>と第2ノードND<sub>2</sub>との間の電位差が駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>より大きく、駆動トランジスタT<sub>Drv</sub>はオフ状態とはならない場合がある。即ち、閾値電圧キャンセル処理の結果として、必ずしも駆動トランジスタT<sub>Drv</sub>がオフ状態となることを要しない。

30

## 【0075】

$$(V_{ofs} - V_{th}) < (V_{th-EL} + V_{Cat}) \quad (2)$$

## 【0076】

この[期間 - TP(5)<sub>2</sub>]にあっては、第2ノードND<sub>2</sub>の電位は、例えば、最終的に(V<sub>ofs</sub> - V<sub>th</sub>)となる。即ち、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>、及び、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>ofs</sub>のみに依存して、第2ノードND<sub>2</sub>の電位は決定される。云い換えれば、発光部ELPの閾値電圧V<sub>th-EL</sub>には依存しな

40

50

い。

### 【0077】

[期間 - TP(5)<sub>3</sub>] (図5の(A)参照)

その後、第1ノード初期化トランジスタ $T_{ND1}$ のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線 $CLEL_C$ をローレベルとすることによって、発光制御トランジスタ $T_{EL_C}$ をオフ状態とする。その結果、第1ノード $ND_1$ の電位は変化せず ( $V_{OFS} = 0$ ボルトを維持)、浮遊状態の第2ノード $ND_2$ の電位も変化せず、 ( $V_{OFS} - V_{TH} = -3$ ボルト) を保持する。

### 【0078】

[期間 - TP(5)<sub>4</sub>] (図5の(B)参照)

次いで、第1ノード初期化トランジスタ制御回路104の動作に基づき第1ノード初期化トランジスタ $T_{ND1}$ をオフ状態とすることによって、第1ノード初期化トランジスタ $T_{ND1}$ をオフ状態とする。第1ノード $ND_1$ 及び第2ノード $ND_2$ の電位は、実質上、変化しない（実際には、寄生容量等の静電結合により電位変化が生じ得るが、通常、これらは無視することができる）。

### 【0079】

次いで、[期間 - TP(5)<sub>5</sub>] ~ [期間 - TP(5)<sub>7</sub>] の各期間について説明する。尚、後述するように、[期間 - TP(5)<sub>5</sub>]において書き込み処理が行われ、[期間 - TP(5)<sub>6</sub>]において移動度補正処理が行われる。上述したように、これらの処理は、第m番目の水平走査期間内に行われる必要がある。説明の便宜のため、[期間 - TP(5)<sub>5</sub>] の始期と[期間 - TP(5)<sub>6</sub>] の終期とは、それぞれ、第m番目の水平走査期間の始期と終期とに一致するものとして説明する。

### 【0080】

[期間 - TP(5)<sub>5</sub>] (図5の(C)参照)

その後、駆動トランジスタ $T_{Drv}$ に対する書き込み処理を実行する。具体的には、第1ノード初期化トランジスタ $T_{ND1}$ 、第2ノード初期化トランジスタ $T_{ND2}$ 、及び、発光制御トランジスタ $T_{EL_C}$ のオフ状態を維持したまま、映像信号出力回路102の動作に基づき、データ線 $DTL$ の電位を、発光部 $ELP$ における輝度を制御するための映像信号（駆動信号、輝度信号） $V_{Sig}$ とし、次いで、走査回路101の動作に基づき走査線 $SLC$ をハイレベルとすることによって、映像信号書き込みトランジスタ $T_{Sig}$ をオン状態とする。その結果、第1ノード $ND_1$ の電位は、 $V_{Sig}$ へと上昇する。

### 【0081】

ここで、コンデンサ部 $C_1$ の容量は値 $c_1$ であり、発光部 $ELP$ の寄生容量 $C_{EL}$ の容量は値 $c_{EL}$ である。そして、駆動トランジスタ $T_{Drv}$ のゲート電極とソース領域との間の寄生容量の値を $c_{gs}$ とする。駆動トランジスタ $T_{Drv}$ のゲート電極の電位が $V_{OFS}$ から $V_{Sig}$  ( $> V_{OFS}$ ) に変化したとき、コンデンサ部 $C_1$ の両端の電位（第1ノード $ND_1$ 及び第2ノード $ND_2$ の電位）は、原則として、変化する。即ち、駆動トランジスタ $T_{Drv}$ のゲート電極の電位 (= 第1ノード $ND_1$ の電位) の変化分 ( $V_{Sig} - V_{OFS}$ ) に基づく電荷が、コンデンサ部 $C_1$ 、発光部 $ELP$ の寄生容量 $C_{EL}$ 、駆動トランジスタ $T_{Drv}$ のゲート電極とソース領域との間の寄生容量に振り分けられる。然るに、通常、値 $c_{EL}$ は、値 $c_1$ 及び値 $c_{gs}$ と比較して十分に大きな値である。従って、駆動トランジスタ $T_{Drv}$ のゲート電極の電位の変化分 ( $V_{Sig} - V_{OFS}$ ) に基づく駆動トランジスタ $T_{Drv}$ のソース領域（第2ノード $ND_2$ ）の電位の変化は小さい。そこで、説明の便宜のため、特段の必要がある場合を除き、第1ノード $ND_1$ の電位変化により生ずる第2ノード $ND_2$ の電位変化は考慮せずに説明を行う。他の駆動回路においても同様である。尚、図示した駆動のタイミングチャートも、第1ノード $ND_1$ の電位変化により生ずる第2ノード $ND_2$ の電位変化を考慮せずに示した。駆動トランジスタ $T_{Drv}$ のゲート電極（第1ノード $ND_1$ ）の電位を $V_g$ 、駆動トランジスタ $T_{Drv}$ のソース領域（第2ノード $ND_2$ ）の電位を $V_s$ としたとき、 $V_g$ の値、 $V_s$ の値は以下のとおりとなる。それ故、第1ノード $ND_1$ と第2ノード $ND_2$ の電位差、即ち、駆動トランジスタ $T_{Drv}$ のゲート電極とソース領域との間の電位差 $V_{gs}$ は、以下の式 (3)

10

20

30

40

50

) で表すことができる。

【 0 0 8 2 】

$$\begin{aligned} V_g &= V_{\text{Sig}} \\ V_s &= V_{\text{Ofs}} - V_{\text{th}} \\ V_{gs} &= V_{\text{Sig}} - (V_{\text{Ofs}} - V_{\text{th}}) \end{aligned} \quad (3)$$

【 0 0 8 3 】

即ち、駆動トランジスタ  $T_{\text{Drv}}$  に対する書き込み処理において得られた  $V_{gs}$  は、発光部 ELP における輝度を制御するための映像信号  $V_{\text{Sig}}$ 、駆動トランジスタ  $T_{\text{Drv}}$  の閾値電圧  $V_{\text{th}}$ 、及び、駆動トランジスタ  $T_{\text{Drv}}$  のゲート電極を初期化するための電圧  $V_{\text{Ofs}}$  のみに依存している。そして、発光部 ELP の閾値電圧  $V_{\text{th-EL}}$  とは無関係である。

10

【 0 0 8 4 】

[期間 - TP (5)<sub>6</sub>] (図 5 の (D) 参照)

その後、駆動トランジスタ  $T_{\text{Drv}}$  の移動度  $\mu$  の大小に基づく駆動トランジスタ  $T_{\text{Drv}}$  のソース領域 (第 2 ノード  $N D_2$ ) の電位の補正 (移動度補正処理) を行う。

【 0 0 8 5 】

一般に、駆動トランジスタ  $T_{\text{Drv}}$  をポリシリコン薄膜トランジスタ等から作製した場合、トランジスタ間で移動度  $\mu$  にばらつきが生じることは避け難い。従って、移動度  $\mu$  に差異がある複数の駆動トランジスタ  $T_{\text{Drv}}$  のゲート電極に同じ値の映像信号  $V_{\text{Sig}}$  を印加したとしても、移動度  $\mu$  の大きい駆動トランジスタ  $T_{\text{Drv}}$  を流れるドレイン電流  $I_{ds}$  と、移動度  $\mu$  の小さい駆動トランジスタ  $T_{\text{Drv}}$  を流れるドレイン電流  $I_{ds}$  との間に、差異が生じてしまう。そして、このような差異が生じると、有機 ELP 表示装置の画面の均一的 (ユニフォーミティ) が損なわれてしまう。

20

【 0 0 8 6 】

従って、具体的には、駆動トランジスタ  $T_{\text{Drv}}$  のオン状態を維持したまま、発光制御トランジスタ制御回路 103 の動作に基づき発光制御トランジスタ制御線  $C L_{EL\_C}$  をハイレベルとすることによって、発光制御トランジスタ  $T_{EL\_C}$  をオン状態とし、次いで、所定の時間 ( $t_0$ ) が経過した後、走査回路 101 の動作に基づき走査線  $S CL$  をロー・レベルとすることによって、映像信号書き込みトランジスタ  $T_{\text{Sig}}$  をオフ状態とし、第 1 ノード  $N D_1$  (駆動トランジスタ  $T_{\text{Drv}}$  のゲート電極) を浮遊状態とする。そして、以上の結果、駆動トランジスタ  $T_{\text{Drv}}$  の移動度  $\mu$  の値が大きい場合、駆動トランジスタ  $T_{\text{Drv}}$  のソース領域における電位の上昇量  $V$  (電位補正值) は大きくなり、駆動トランジスタ  $T_{\text{Drv}}$  の移動度  $\mu$  の値が小さい場合、駆動トランジスタ  $T_{\text{Drv}}$  のソース領域における電位の上昇量  $V$  (電位補正值) は小さくなる。ここで、駆動トランジスタ  $T_{\text{Drv}}$  のゲート電極とソース領域との間の電位差  $V_{gs}$  は、式 (3) から以下の式 (4) のように変形される。

30

【 0 0 8 7 】

$$V_{gs} = V_{\text{Sig}} - (V_{\text{Ofs}} - V_{\text{th}}) - V \quad (4)$$

【 0 0 8 8 】

尚、移動度補正処理を実行するための所定の時間 ([期間 - TP (5)<sub>6</sub>] の全時間  $t_0$ ) は、有機 ELP 表示装置の設計の際、設計値として予め決定しておけばよい。また、このときの駆動トランジスタ  $T_{\text{Drv}}$  のソース領域における電位 ( $V_{\text{Ofs}} - V_{\text{th}} + V$ ) が以下の式 (2') を満足するように、[期間 - TP (5)<sub>6</sub>] の全時間  $t_0$  は決定されている。そして、これによって、[期間 - TP (5)<sub>6</sub>]において、発光部 ELP が発光することはない。更には、この移動度補正処理によって、係数  $k$  ((1/2) · (W/L) ·  $C_{ox}$ ) のばらつきの補正も同時に行われる。

40

【 0 0 8 9 】

$$(V_{\text{Ofs}} - V_{\text{th}} + V) < (V_{\text{th-EL}} + V_{\text{Cat}}) \quad (2')$$

【 0 0 9 0 】

[期間 - TP (5)<sub>7</sub>] (図 5 の (E) 参照)

以上の操作によって、閾値電圧キャンセル処理、書き込み処理、移動度補正処理が完了する。ところで、走査回路 101 の動作に基づき走査線  $S CL$  がロー・レベルとなる結果、映

50

像信号書込みトランジスタ  $T_{sig}$  がオフ状態となり、第 1 ノード  $N D_1$ 、即ち、駆動トランジスタ  $T_{Drv}$  のゲート電極は浮遊状態となる。一方、発光制御トランジスタ  $T_{EL\_C}$  はオン状態を維持しており、発光制御トランジスタ  $T_{EL\_C}$  のドレイン領域は、発光部  $ELP$  の発光を制御するための電流供給部 100（電圧  $V_{CC}$ 、例えば 20 ボルト）に接続された状態にある。従って、以上の結果として、第 2 ノード  $N D_2$  の電位は上昇する。

#### 【0091】

ここで、上述したとおり、駆動トランジスタ  $T_{Drv}$  のゲート電極は浮遊状態にあり、しかも、コンデンサ部  $C_1$  が存在するが故に、所謂ブートストラップ回路におけると同様の現象が駆動トランジスタ  $T_{Drv}$  のゲート電極に生じ、第 1 ノード  $N D_1$  の電位も上昇する。その結果、駆動トランジスタ  $T_{Drv}$  のゲート電極とソース領域との間の電位差  $V_{gs}$  は、式(4)の値を保持する。10

#### 【0092】

また、第 2 ノード  $N D_2$  の電位が上昇し、 $(V_{th-EL} + V_{Cat})$  を越えるので、発光部  $ELP$  は発光を開始する。このとき、発光部  $ELP$  を流れる電流は、駆動トランジスタ  $T_{Drv}$  のドレイン領域からソース領域へと流れるドレイン電流  $I_{ds}$  であるので、式(1)で表すことができる。ここで、式(1)と式(4)から、式(1)は、以下の式(5)のように変形することができる。

#### 【0093】

$$I_{ds} = k \cdot \mu \cdot (V_{Sig} - V_{Ofs} - V)^2 \quad (5)$$

#### 【0094】

従って、発光部  $ELP$  を流れる電流  $I_{ds}$  は、例えば、 $V_{Ofs}$  を 0 ボルトに設定したとした場合、発光部  $ELP$  における輝度を制御するための映像信号（駆動信号、輝度信号） $V_{Sig}$  の値から、駆動トランジスタ  $T_{Drv}$  の移動度  $\mu$  に起因した第 2 ノード  $N D_2$ （駆動トランジスタ  $T_{Drv}$  のソース領域）における電位補正值  $V$  の値を減じた値の 2 乗に比例する。云い換えれば、発光部  $ELP$  を流れる電流  $I_{ds}$  は、発光部  $ELP$  の閾値電圧  $V_{th-EL}$  及び、駆動トランジスタ  $T_{Drv}$  の閾値電圧  $V_{th}$  には依存しない。即ち、発光部  $ELP$  の発光量（輝度）は、発光部  $ELP$  の閾値電圧  $V_{th-EL}$  の影響、及び、駆動トランジスタ  $T_{Drv}$  の閾値電圧  $V_{th}$  の影響を受けない。そして、第  $(n, m)$  番目の有機  $EL$  素子 10 の輝度は、係る電流  $I_{ds}$  に対応した値である。20

#### 【0095】

しかも、移動度  $\mu$  の大きな駆動トランジスタ  $T_{Drv}$  ほど、電位補正值  $V$  が大きくなるので、式(4)の左辺の  $V_{gs}$  の値が小さくなる。従って、式(5)において、移動度  $\mu$  の値が大きくとも、 $(V_{Sig} - V_{Ofs} - V)^2$  の値が小さくなる結果、ドレイン電流  $I_{ds}$  を補正することができる。即ち、移動度  $\mu$  の異なる駆動トランジスタ  $T_{Drv}$  においても、映像信号  $V_{Sig}$  の値が同じであれば、ドレイン電流  $I_{ds}$  が略同じとなる結果、発光部  $ELP$  を流れ、発光部  $ELP$  の輝度を制御する電流  $I_{ds}$  が均一化される。即ち、移動度  $\mu$  のばらつき（更には、 $k$  のばらつき）に起因する発光部の輝度のばらつきを補正することができる。30

#### 【0096】

発光部  $ELP$  の発光状態を第  $(m + m' - 1)$  番目の水平走査期間まで継続する。この時点は、[期間 -  $TP(5)_1$ ] の終わりに相当する。40

#### 【0097】

以上によって、有機  $EL$  素子 10 [第  $(n, m)$  番目の副画素（有機  $EL$  素子 10）] の発光の動作が完了する。

#### 【0098】

上述したように、移動度補正処理を実行するための所定の時間（[期間 -  $TP(5)_6$ ] の全時間  $t_0$  は、有機  $EL$  表示装置の設計の際、設計値として予め決定しておけばよい。しかしながら、実施例 1 にて説明したとおり、実際の [期間 -  $TP(5)_6$ ] の時間  $t$  は、発光制御トランジスタ  $T_{EL\_C}$  のソース領域とゲート電極とのカップリングに起因して変動し得る。然るに、実施例 1 にて説明したとおり、補助容量部  $C_{sub}$  を備えることで、50

発光制御トランジスタ  $T_{EL\_C}$  のソース領域とゲート電極とのカップリングに起因した実際の [期間 - TP(5)] の時間  $t$  の変動発生を抑制することができる。そして、その結果、シェーディング（グラデーション）の発生を確実に防止することができる。以下に説明する 4 Tr / 1 C 駆動回路、及び、3 Tr / 1 C 駆動回路においても、同様である。

## 【0099】

次に、4 Tr / 1 C 駆動回路に関する説明を行う。

## 【0100】

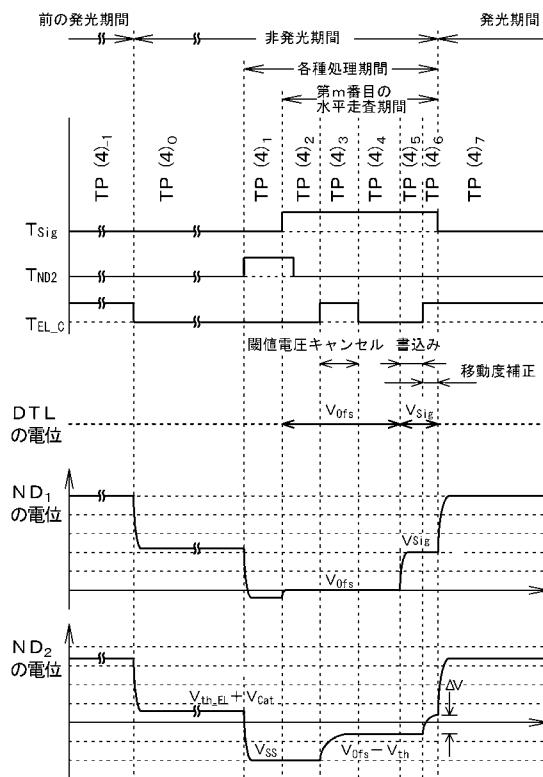

## [4 Tr / 1 C 駆動回路]

4 Tr / 1 C 駆動回路の等価回路図を図6に示し、概念図を図7を示し、駆動のタイミングチャートを模式的に図8に示し、各トランジスタのオン／オフ状態等を模式的に図9の(A)～(D)及び図10の(A)～(D)に示す。

10

## 【0101】

この4 Tr / 1 C 駆動回路においては、前述した5 Tr / 1 C 駆動回路から、第1ノード初期化トランジスタ  $T_{ND1}$  が省略されている。即ち、この4 Tr / 1 C 駆動回路は、映像信号書き込みトランジスタ  $T_{Sig}$ 、駆動トランジスタ  $T_{Drv}$ 、発光制御トランジスタ  $T_{EL\_C}$ 、第2ノード初期化トランジスタ  $T_{ND2}$  の4つのトランジスタから構成され、更には、1つのコンデンサ部  $C_1$  から構成されている。

## 【0102】

[発光制御トランジスタ  $T_{EL\_C}$ ]

発光制御トランジスタ  $T_{EL\_C}$  の構成は、5 Tr / 1 C 駆動回路において説明した発光制御トランジスタ  $T_{EL\_C}$  の構成と同じであるので、詳細な説明は省略する。

20

## 【0103】

[駆動トランジスタ  $T_{Drv}$ ]

駆動トランジスタ  $T_{Drv}$  の構成は、5 Tr / 1 C 駆動回路において説明した駆動トランジスタ  $T_{Drv}$  の構成と同じであるので、詳細な説明は省略する。

## 【0104】

[第2ノード初期化トランジスタ  $T_{ND2}$ ]

第2ノード初期化トランジスタ  $T_{ND2}$  の構成は、5 Tr / 1 C 駆動回路において説明した第2ノード初期化トランジスタ  $T_{ND2}$  の構成と同じであるので、詳細な説明は省略する。

30

## 【0105】

[映像信号書き込みトランジスタ  $T_{Sig}$ ]

映像信号書き込みトランジスタ  $T_{Sig}$  の構成は、5 Tr / 1 C 駆動回路において説明した映像信号書き込みトランジスタ  $T_{Sig}$  の構成と同じであるので、詳細な説明は省略する。但し、映像信号書き込みトランジスタ  $T_{Sig}$  の一方のソース／ドレイン領域は、データ線 DTL に接続されているが、映像信号出力回路 102 から、発光部 ELP における輝度を制御するための映像信号  $V_{Sig}$  だけでなく、駆動トランジスタ  $T_{Drv}$  のゲート電極を初期化するための電圧  $V_{ofs}$  も供給される。この点が、5 Tr / 1 C 駆動回路において説明した映像信号書き込みトランジスタ  $T_{Sig}$  の動作と相違している。尚、映像信号出力回路 102 から、データ線 DTL を介して、 $V_{Sig}$  や  $V_{ofs}$  以外の信号・電圧（例えば、プリチャージ駆動のための信号）が、一方のソース／ドレイン領域に供給されてもよい。

40

## 【0106】

## [発光部 ELP]

発光部 ELP の構成は、5 Tr / 1 C 駆動回路において説明した発光部 ELP の構成と同じであるので、詳細な説明は省略する。

## 【0107】

以下、4 Tr / 1 C 駆動回路の動作説明を行う。

## 【0108】

## [期間 - TP(4)] (図9の(A)参照)

この[期間 - TP(4)]は、例えば、前の表示フレームにおける動作であり、5 Tr

50

$r / 1 C$  駆動回路において説明した [期間 - TP(5)<sub>-1</sub>] と同じ動作である。

#### 【0109】

図8に示す [期間 - TP(4)<sub>0</sub>] ~ [期間 - TP(4)<sub>4</sub>] は、図3に示す [期間 - TP(5)<sub>0</sub>] ~ [期間 - TP(5)<sub>4</sub>] に対応する期間であり、次の書き込み処理が行われる直前までの動作期間である。そして、 $5Tr / 1C$  駆動回路と同様に、[期間 - TP(4)<sub>0</sub>] ~ [期間 - TP(4)<sub>4</sub>]において、第(n, m)番目の有機EL素子10は、原則として、非発光状態にある。但し、 $4Tr / 1C$  駆動回路の動作においては、図8に示す [期間 - TP(4)<sub>5</sub>] ~ [期間 - TP(4)<sub>6</sub>] の他、[期間 - TP(4)<sub>2</sub>] ~ [期間 - TP(4)<sub>4</sub>] も第m番目の水平走査期間に包含される点が、 $5Tr / 1C$  駆動回路の動作とは異なる。尚、説明の便宜のため、[期間 - TP(4)<sub>2</sub>] の始期、及び、[期間 - TP(4)<sub>6</sub>] の終期は、それぞれ、第m番目の水平走査期間の始期、及び、終期に一致するものとして説明する。

10

#### 【0110】

以下、[期間 - TP(4)<sub>0</sub>] ~ [期間 - TP(4)<sub>4</sub>] の各期間について、説明する。尚、 $5Tr / 1C$  駆動回路において説明したと同様に、[期間 - TP(4)<sub>1</sub>] の始期や、[期間 - TP(4)<sub>1</sub>] ~ [期間 - TP(4)<sub>4</sub>] の各期間の長さは、有機EL表示装置の設計に応じて適宜設定すればよい。

20

#### 【0111】

##### [期間 - TP(4)<sub>0</sub>]

この[期間 - TP(4)<sub>0</sub>]は、例えば、前の表示フレームから現表示フレームにおける動作であり、 $5Tr / 1C$  駆動回路において説明した[期間 - TP(5)<sub>0</sub>]と、実質的に同じ動作である。

20

#### 【0112】

##### [期間 - TP(4)<sub>1</sub>] (図9の(B)参照)

この[期間 - TP(4)<sub>1</sub>]は、 $5Tr / 1C$  駆動回路において説明した[期間 - TP(5)<sub>1</sub>]に相当する。この[期間 - TP(4)<sub>1</sub>]において、後述する閾値電圧キャンセル処理を行うための前処理が行われる。[期間 - TP(4)<sub>1</sub>]の開始時、第2ノード初期化トランジスタ制御回路105の動作に基づき第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>をハイレベルとすることによって、第2ノード初期化トランジスタT<sub>ND2</sub>をオン状態とする。その結果、第2ノードND<sub>2</sub>の電位は、V<sub>ss</sub>(例えば、-10ボルト)となる。また、第2ノードND<sub>2</sub>の電位低下に倣うように、浮遊状態の第1ノードND<sub>1</sub>(駆動トランジスタT<sub>Drv</sub>のゲート電極)の電位も低下する。尚、[期間 - TP(4)<sub>1</sub>]における第1ノードND<sub>1</sub>の電位は、[期間 - TP(4)<sub>-1</sub>]における第1ノードND<sub>1</sub>の電位(前フレームのV<sub>Sig</sub>の値に応じて定まる)により左右されるので、一定の値をとるものではない。

30

#### 【0113】

##### [期間 - TP(4)<sub>2</sub>] (図9の(C)参照)

その後、映像信号出力回路102の動作に基づきデータ線DTLの電位をV<sub>ofs</sub>とし、走査回路101の動作に基づき走査線SCLをハイレベルとすることによって、映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>of</sub><sub>s</sub>(例えば、0ボルト)となる。第2ノードND<sub>2</sub>の電位はV<sub>ss</sub>(例えば、-10ボルト)を保持する。その後、第2ノード初期化トランジスタ制御回路105の動作に基づき第2ノード初期化トランジスタ制御線AZ<sub>ND2</sub>をローレベルとすることによって、第2ノード初期化トランジスタT<sub>ND2</sub>をオフ状態とする。

40

#### 【0114】

尚、[期間 - TP(4)<sub>1</sub>]の開始と同時に、あるいは、[期間 - TP(4)<sub>1</sub>]の途中で、映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態としてもよい。

#### 【0115】

以上の処理により、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>th</sub>以上となり、駆動トランジスタT<sub>Drv</sub>はオン状態となる。

50

## 【0116】

[期間 - TP(4)<sub>3</sub>] (図9の(D)参照)

次に、閾値電圧キャンセル処理が行われる。即ち、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線C<sub>LEL\_C</sub>をハイレベルとすることによって、発光制御トランジスタT<sub>EL\_C</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は変化しないが(V<sub>ofs</sub> = 0ボルトを維持)、第1ノードND<sub>1</sub>の電位から駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>を減じた電位に向かって、第2ノードND<sub>2</sub>の電位は変化する。即ち、浮遊状態の第2ノードND<sub>2</sub>の電位は上昇する。そして、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>th</sub>に達すると、駆動トランジスタT<sub>Drv</sub>がオフ状態となる。具体的には、浮遊状態の第2ノードND<sub>2</sub>の電位が(V<sub>ofs</sub> - V<sub>th</sub> = -3ボルト)に近づき、最終的に(V<sub>ofs</sub> - V<sub>th</sub>)となる。ここで、上述した式(2)が保証されていれば、云い換えれば、式(2)を満足するように電位を選択、決定しておけば、発光部ELPが発光することはない。

10

## 【0117】

この[期間 - TP(4)<sub>3</sub>]にあっては、第2ノードND<sub>2</sub>の電位は、例えば、最終的に、(V<sub>ofs</sub> - V<sub>th</sub>)となる。即ち、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>、及び、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>ofs</sub>のみに依存して、第2ノードND<sub>2</sub>の電位は決定される。そして、発光部ELPの閾値電圧V<sub>th-EL</sub>とは無関係である。

20

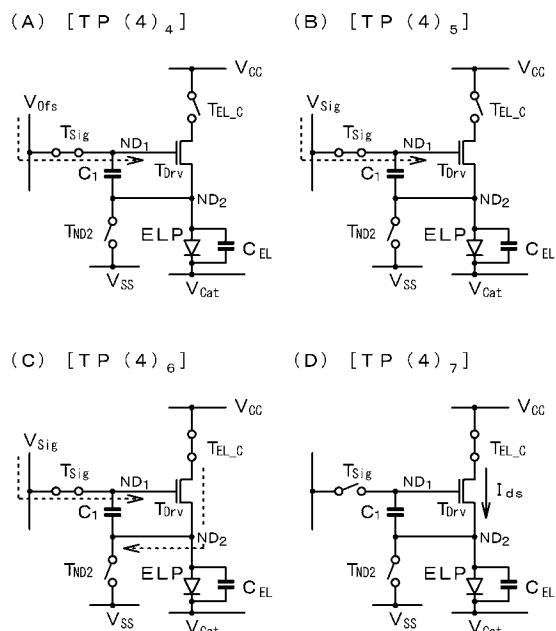

## 【0118】

[期間 - TP(4)<sub>4</sub>] (図10の(A)参照)

その後、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線C<sub>LEL\_C</sub>をローレベルとすることによって、発光制御トランジスタT<sub>EL\_C</sub>をオフ状態とする。その結果、第1ノードND<sub>1</sub>の電位は変化せず(V<sub>ofs</sub> = 0ボルトを維持)、浮遊状態の第2ノードND<sub>2</sub>の電位も、実質上、変化せず(実際には、寄生容量等の静電結合により電位変化が生じ得るが、通常、これらは無視することができる)、(V<sub>ofs</sub> - V<sub>th</sub> = -3ボルト)を保持する。

20

## 【0119】

次いで、[期間 - TP(4)<sub>5</sub>] ~ [期間 - TP(4)<sub>7</sub>] の各期間について説明する。これらの期間は、5Tr / 1C駆動回路において説明した[期間 - TP(5)<sub>5</sub>] ~ [期間 - TP(5)<sub>7</sub>]と、実質的に同じ動作である。

30

## 【0120】

[期間 - TP(4)<sub>5</sub>] (図10の(B)参照)

次に、駆動トランジスタT<sub>Drv</sub>に対する書き込み処理を実行する。具体的には、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持し、第2ノード初期化トランジスタT<sub>ND2</sub>、及び、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、映像信号出力回路102の動作に基づきデータ線DTLの電位を、V<sub>ofs</sub>から、発光部ELPにおける輝度を制御するための映像信号V<sub>Sig</sub>に切り替える。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>Sig</sub>へと上昇する。尚、映像信号書き込みトランジスタT<sub>Sig</sub>を、一旦、オフ状態とし、映像信号書き込みトランジスタT<sub>Sig</sub>、第2ノード初期化トランジスタT<sub>ND2</sub>、及び、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、映像信号出力回路102の動作に基づきデータ線DTLの電位を、発光部ELPにおける輝度を制御するための映像信号V<sub>Sig</sub>に変更し、その後、第2ノード初期化トランジスタT<sub>ND2</sub>、及び、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、走査線SCLをハイレベルとすることによって、映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態としてもよい。

40

## 【0121】

これによって、5Tr / 1C駆動回路において説明したと同様に、第1ノードND<sub>1</sub>と第2ノードND<sub>2</sub>の電位差、即ち、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差V<sub>gs</sub>として、式(3)で説明した値を得ることができる。

50

## 【0122】

即ち、 $4\text{ Tr} / 1\text{ C}$  駆動回路においても、駆動トランジスタ  $T_{Drv}$  に対する書込み処理において得られた  $V_{gs}$  は、発光部  $ELP$  における輝度を制御するための映像信号  $V_{Sig}$ 、駆動トランジスタ  $T_{Drv}$  の閾値電圧  $V_{th}$ 、及び、駆動トランジスタ  $T_{Drv}$  のゲート電極を初期化するための電圧  $V_{ofs}$  のみに依存している。そして、発光部  $ELP$  の閾値電圧  $V_{th-EL}$  とは無関係である。

## 【0123】

[期間 - TP(4)<sub>6</sub>] (図10の(C)参照)

その後、駆動トランジスタ  $T_{Drv}$  の移動度  $\mu$  の大小に基づく駆動トランジスタ  $T_{Drv}$  のソース領域 (第2ノード  $N_{D2}$ ) の電位の補正 (移動度補正処理) を行う。具体的には、 $5\text{ Tr} / 1\text{ C}$  駆動回路において説明した [期間 - TP(5)<sub>6</sub>] と同じ動作を行えばよい。

尚、移動度補正処理を実行するための所定の時間 ([期間 - TP(4)<sub>6</sub>] の全時間  $t_0$ ) は、有機  $EL$  表示装置の設計の際、設計値として予め決定しておけばよい。

10

## 【0124】

[期間 - TP(4)<sub>7</sub>] (図10の(D)参照)

以上の操作によって、閾値電圧キャンセル処理、書込み処理、移動度補正処理が完了する。そして、 $5\text{ Tr} / 1\text{ C}$  駆動回路において説明した [期間 - TP(5)<sub>7</sub>] と同じ処理がなされ、第2ノード  $N_{D2}$  の電位が上昇し、( $V_{th-EL} + V_{Cat}$ ) を越えるので、発光部  $ELP$  は発光を開始する。このとき、発光部  $ELP$  を流れる電流は、前述した式(5)にて得ることができるので、発光部  $ELP$  を流れる電流  $I_{ds}$  は、発光部  $ELP$  の閾値電圧  $V_{th-EL}$ 、及び、駆動トランジスタ  $T_{Drv}$  の閾値電圧  $V_{th}$  には依存しない。即ち、発光部  $ELP$  の発光量 (輝度) は、発光部  $ELP$  の閾値電圧  $V_{th-EL}$  の影響、及び、駆動トランジスタ  $T_{Drv}$  の閾値電圧  $V_{th}$  の影響を受けない。加えて、駆動トランジスタ  $T_{Drv}$  における移動度  $\mu$  のばらつきに起因したドレイン電流  $I_{ds}$  のばらつき発生を抑制することができる。

20

## 【0125】

そして、発光部  $ELP$  の発光状態を第 ( $m + m' - 1$ ) 番目の水平走査期間まで継続する。この時点は、[期間 - TP(4)<sub>.1</sub>] の終わりに相当する。

## 【0126】

以上によって、有機  $EL$  素子 10 [第 ( $n, m$ ) 番目の副画素 (有機  $EL$  素子 10)] の発光の動作が完了する。

30

## 【0127】

次に、 $3\text{ Tr} / 1\text{ C}$  駆動回路に関する説明を行う。

## 【0128】

[ $3\text{ Tr} / 1\text{ C}$  駆動回路]

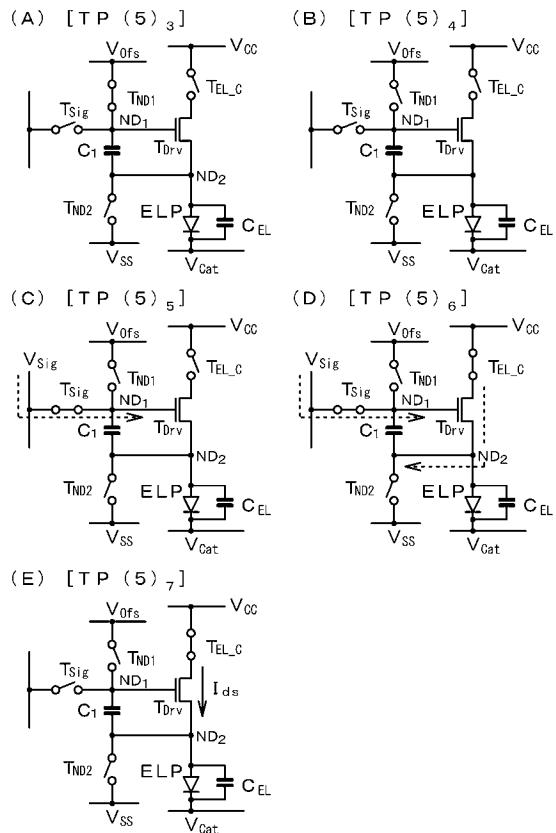

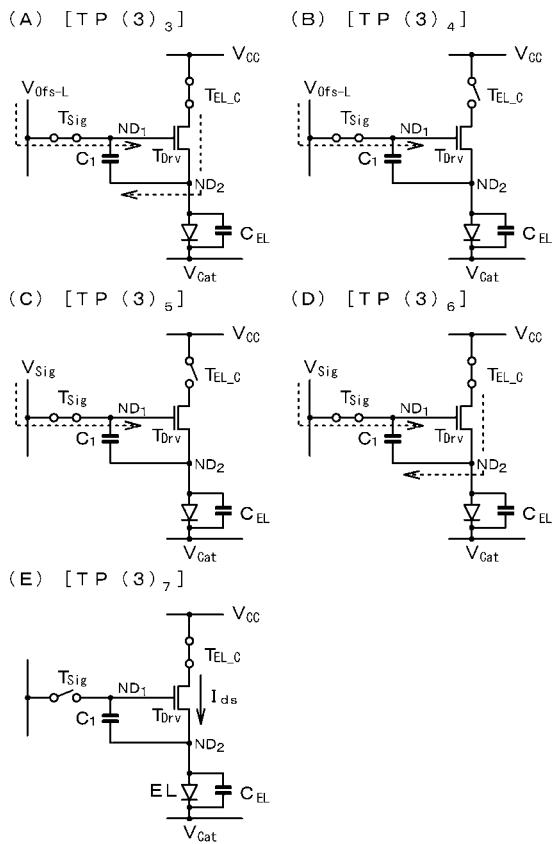

$3\text{ Tr} / 1\text{ C}$  駆動回路の等価回路図を図11に示し、概念図を図12を示し、駆動のタイミングチャートを模式的に図13に示し、各トランジスタのオン／オフ状態等を模式的に図14の(A)～(D) 及び図15の(A)～(E) に示す。

40

## 【0129】

この $3\text{ Tr} / 1\text{ C}$  駆動回路においては、前述した $5\text{ Tr} / 1\text{ C}$  駆動回路から、第1ノード初期化トランジスタ  $T_{ND1}$ 、及び、第2ノード初期化トランジスタ  $T_{ND2}$  の2つのトランジスタが省略されている。即ち、この $3\text{ Tr} / 1\text{ C}$  駆動回路は、映像信号書込みトランジスタ  $T_{Sig}$ 、発光制御トランジスタ  $T_{EL\_C}$ 、及び、駆動トランジスタ  $T_{Drv}$  の3つのトランジスタから構成され、更には、1つのコンデンサ部  $C_1$  から構成されている。

## 【0130】

[発光制御トランジスタ  $T_{EL\_C}$ ]

発光制御トランジスタ  $T_{EL\_C}$  の構成は、 $5\text{ Tr} / 1\text{ C}$  駆動回路において説明した発光制御トランジスタ  $T_{EL\_C}$  の構成と同じであるので、詳細な説明は省略する。

## 【0131】

[駆動トランジスタ  $T_{Drv}$ ]

駆動トランジスタ  $T_{Drv}$  の構成は、 $5\text{ Tr} / 1\text{ C}$  駆動回路において説明した駆動トラン

50

ジスタ  $T_{Drv}$  の構成と同じであるので、詳細な説明は省略する。

【0132】

[ 映像信号書き込みトランジスタ  $T_{Sig}$  ]

映像信号書き込みトランジスタ  $T_{Sig}$  の構成は、5 Tr / 1 C 駆動回路において説明した映像信号書き込みトランジスタ  $T_{Sig}$  の構成と同じであるので、詳細な説明は省略する。但し、映像信号書き込みトランジスタ  $T_{Sig}$  の一方のソース / ドレイン領域は、データ線 DTL に接続されているが、映像信号出力回路 102 から、発光部 ELP における輝度を制御するための映像信号駆（駆動信号、輝度信号） $V_{Sig}$  だけでなく、駆動トランジスタ  $T_{Drv}$  のゲート電極を初期化するための電圧  $V_{Off-H}$  及び電圧  $V_{Off-L}$  も供給される。この点が、5 Tr / 1 C 駆動回路において説明した映像信号書き込みトランジスタ  $T_{Sig}$  の動作と相違している。尚、映像信号出力回路 102 から、データ線 DTL を介して、 $V_{Sig}$  や  $V_{Off-H}$  /  $V_{Off-L}$  以外の信号・電圧（例えば、プリチャージ駆動のための信号）が、一方のソース / ドレイン領域に供給されてもよい。電圧  $V_{Off-H}$  及び電圧  $V_{Off-L}$  の値として、限定するものではないが、例えば、

$V_{Off-H}$  = 約 30 ボルト

$V_{Off-L}$  = 約 0 ボルト

を例示することができる。

【0133】

[  $C_{EL}$  と  $c_1$  の値の関係 ]

後述するように、3 Tr / 1 C 駆動回路においては、データ線 DTL を利用して第 2 ノード ND<sub>2</sub> の電位を変化させる必要がある。上述した 5 Tr / 1 C 駆動回路や 4 Tr / 1 C の駆動回路においては、値  $c_{EL}$  は、値  $c_1$  及び値  $c_{gs}$  と比較して十分に大きな値であるとし、駆動トランジスタ  $T_{Drv}$  のゲート電極の電位の変化分 ( $V_{Sig} - V_{Off}$ ) に基づく駆動トランジスタ  $T_{Drv}$  のソース領域（第 2 ノード ND<sub>2</sub>）の電位の変化を考慮せずに説明を行った。一方、3 Tr / 1 C 駆動回路においては、値  $c_1$  を、設計上、他の駆動回路よりも大きい値（例えば、値  $c_1$  を値  $c_{EL}$  の約 1 / 4 ~ 1 / 3 程度）に設定する。従って、他の駆動回路よりも、第 1 ノード ND<sub>1</sub> の電位変化により生ずる第 2 ノード ND<sub>2</sub> の電位変化の程度は大きい。このため、3 Tr / 1 C の説明においては、第 1 ノード ND<sub>1</sub> の電位変化により生ずる第 2 ノード ND<sub>2</sub> の電位変化を考慮して説明を行う。尚、図示した駆動のタイミングチャートも、第 1 ノード ND<sub>1</sub> の電位変化により生ずる第 2 ノード ND<sub>2</sub> の電位変化を考慮して示した。

【0134】

[ 発光部 ELP ]

発光部 ELP の構成は、5 Tr / 1 C 駆動回路において説明した発光部 ELP の構成と同じであるので、詳細な説明は省略する。

【0135】

以下、3 Tr / 1 C 駆動回路の動作説明を行う。

【0136】

[ 期間 - TP(3)\_1 ] ( 図 14 の (A) 参照 )

この [ 期間 - TP(3)\_1 ] は、例えば、前の表示フレームにおける動作であり、実質的に、5 Tr / 1 C 駆動回路において説明した [ 期間 - TP(5)\_1 ] と同じ動作である。

【0137】

図 13 に示す [ 期間 - TP(3)\_0 ] ~ [ 期間 - TP(3)\_4 ] は、図 3 に示す [ 期間 - TP(5)\_0 ] ~ [ 期間 - TP(5)\_4 ] に対応する期間であり、次の書き込み処理が行われる直前までの動作期間である。そして、5 Tr / 1 C 駆動回路と同様に、[ 期間 - TP(3)\_0 ] ~ [ 期間 - TP(3)\_4 ] において、第 (n, m) 番目の有機 EL 素子 10 は、原則として、非発光状態にある。但し、3 Tr / 1 C 駆動回路の動作においては、図 13 に示すように、[ 期間 - TP(3)\_5 ] ~ [ 期間 - TP(3)\_6 ] の他、[ 期間 - TP(3)\_1 ] ~ [ 期間 - TP(3)\_4 ] も第 m 番目の水平走査期間に包含される点が、5 Tr / 1 C

10

20

30

40

50

駆動回路の動作とは異なる。尚、説明の便宜のため、[期間 - TP(3)<sub>1</sub>]の始期、及び、[期間 - TP(3)<sub>6</sub>]の終期は、それぞれ、第m番目の水平走査期間の始期、及び、終期に一致するものとして説明する。

#### 【0138】

以下、[期間 - TP(3)<sub>0</sub>] ~ [期間 - TP(3)<sub>4</sub>] の各期間について、説明する。尚、5Tr / 1C 駆動回路において説明したと同様に、[期間 - TP(3)<sub>1</sub>] ~ [期間 - TP(3)<sub>4</sub>] の各期間の長さは、有機EL表示装置の設計に応じて適宜設定すればよい。

#### 【0139】

[期間 - TP(3)<sub>0</sub>] (図14の(B)参照)

この[期間 - TP(3)<sub>0</sub>]は、例えば、前の表示フレームから現表示フレームにおける動作であり、5Tr / 1C 駆動回路において説明した[期間 - TP(5)<sub>0</sub>]と、実質的に同じ動作である。

#### 【0140】

[期間 - TP(3)<sub>1</sub>] (図14の(C)参照)

そして、現表示フレームにおける第m行目の水平走査期間が開始する。[期間 - TP(3)<sub>1</sub>]の開始時、映像信号出力回路102の動作に基づきデータ線DTLの電位を、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>Offs-H</sub>とし、次いで、走査回路101の動作に基づき走査線SCLをハイレベルとすることによって、映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>Offs-H</sub>となる。上述したように、コンデンサ部C<sub>1</sub>の値c<sub>1</sub>を、設計上、他の駆動回路よりも大きい値としたので、ソース領域の電位(第2ノードND<sub>2</sub>の電位)は上昇する。そして、発光部ELPの両端の電位差が閾値電圧V<sub>th-EL</sub>を超えるので、電位発光部ELPは導通状態となるが、駆動トランジスタT<sub>Drv</sub>のソース領域の電位は、再び、(V<sub>th-EL</sub> + V<sub>Cat</sub>)まで、直ちに低下する。尚、この過程において、発光部ELPが発光し得るが、発光は一瞬であり、実用上、問題とはならない。一方、駆動トランジスタT<sub>Drv</sub>のゲート電極は電圧V<sub>Offs-H</sub>を保持する。

#### 【0141】

[期間 - TP(3)<sub>2</sub>] (図14の(D)参照)

その後、映像信号出力回路102の動作に基づき、データ線DTLの電位を、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>Offs-H</sub>から電圧V<sub>Offs-L</sub>へと変更することによって、第1ノードND<sub>1</sub>の電位は、V<sub>Offs-L</sub>となる。そして、第1ノードND<sub>1</sub>の電位の低下に伴い、第2ノードND<sub>2</sub>の電位も低下する。即ち、駆動トランジスタT<sub>Drv</sub>のゲート電極の電位の変化分(V<sub>Offs-L</sub> - V<sub>Offs-H</sub>)に基づく電荷が、コンデンサ部C<sub>1</sub>、発光部ELPの寄生容量C<sub>EL</sub>、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の寄生容量に振り分けられる。尚、後述する[期間 - TP(3)<sub>3</sub>]における動作の前提として、[期間 - TP(3)<sub>2</sub>]の終期において、第2ノードND<sub>2</sub>の電位がV<sub>Offs-L</sub> - V<sub>t</sub>よりも低いことが必要となる。V<sub>Offs-H</sub>の値等は、この条件を満たすように設定されている。即ち、以上の処理により、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>t</sub>以上となり、駆動トランジスタT<sub>Drv</sub>はオン状態となる。

#### 【0142】

[期間 - TP(3)<sub>3</sub>] (図15の(A)参照)

次に、閾値電圧キャセル処理が行われる。即ち、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線C<sub>L<sub>EL-C</sub></sub>をハイレベルとすることによって、発光制御トランジスタT<sub>EL-C</sub>をオン状態とする。その結果、第1ノードND<sub>1</sub>の電位は変化しないが(V<sub>Offs-L</sub> = 0ボルトを維持)、第1ノードND<sub>1</sub>の電位から駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>t</sub>を減じた電位に向かって、第2ノードND<sub>2</sub>の電位は変化する。即ち、浮遊状態の第2ノードND<sub>2</sub>の電位は上昇する。そして、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差がV<sub>t</sub>に達すると、駆動トランジスタT<sub>Drv</sub>がオフ状態となる。具体的には

10

20

30

40

50

、浮遊状態の第2ノードND<sub>2</sub>の電位が( $V_{Ofs-L} - V_{th} = -3$ ボルト)に近づき、最終的に( $V_{Ofs-L} - V_{th}$ )となる。ここで、上述した式(2)が保証されていれば、云い換えれば、式(2)を満足するように電位を選択、決定しておけば、発光部ELPが発光することはない。

#### 【0143】

この[期間-TP(3)<sub>3</sub>]にあっては、第2ノードND<sub>2</sub>の電位は、最終的に、( $V_{Ofs-L} - V_{th}$ )となる。即ち、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>、及び、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>Ofs-L</sub>のみに依存して、第2ノードND<sub>2</sub>の電位は決定される。そして、発光部ELPの閾値電圧V<sub>th-EL</sub>とは無関係である。

#### 【0144】

[期間-TP(3)<sub>4</sub>] (図15の(B)参照)

その後、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持したまま、発光制御トランジスタ制御回路103の動作に基づき発光制御トランジスタ制御線C<sub>L\_EL\_C</sub>をローレベルとすることによって、発光制御トランジスタT<sub>EL\_C</sub>をオフ状態とする。その結果、第1ノードND<sub>1</sub>の電位は変化せず( $V_{Ofs-L} = 0$ ボルトを維持)、浮遊状態の第2ノードND<sub>2</sub>の電位も変化せず、( $V_{Ofs-L} - V_{th} = -3$ ボルト)を保持する。

#### 【0145】

次いで、[期間-TP(3)<sub>5</sub>]～[期間-TP(3)<sub>7</sub>]の各期間について説明する。これらは、5Tr/1C駆動回路において説明した[期間-TP(5)<sub>5</sub>]～[期間-TP(5)<sub>7</sub>]と、実質的に同じ動作である。

#### 【0146】

[期間-TP(3)<sub>5</sub>] (図15の(C)参照)

次に、駆動トランジスタT<sub>Drv</sub>に対する書き込み処理を実行する。具体的には、映像信号書き込みトランジスタT<sub>Sig</sub>のオン状態を維持し、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、映像信号出力回路102の動作に基づき、データ線DTLの電位を、発光部ELPにおける輝度を制御するための映像信号V<sub>Sig</sub>とする。その結果、第1ノードND<sub>1</sub>の電位は、V<sub>Sig</sub>へと上昇する。尚、映像信号書き込みトランジスタT<sub>Sig</sub>を、一旦、オフ状態とし、映像信号書き込みトランジスタT<sub>Sig</sub>、及び、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、データ線DTLの電位を、発光部ELPにおける輝度を制御するための映像信号V<sub>Sig</sub>に変更し、その後、発光制御トランジスタT<sub>EL\_C</sub>のオフ状態を維持したまま、走査線SCLをハイレベルとすることによって、映像信号書き込みトランジスタT<sub>Sig</sub>をオン状態としてもよい。

#### 【0147】

[期間-TP(3)<sub>5</sub>]において、第1ノードND<sub>1</sub>の電位が、V<sub>Ofs-L</sub>からV<sub>Sig</sub>へと上昇する。このため、第1ノードND<sub>1</sub>の電位変化により生ずる第2ノードND<sub>2</sub>の電位変化を考慮すると、第2ノードND<sub>1</sub>の電位も、若干、上昇する。即ち、第2ノードND<sub>1</sub>の電位を、 $V_{Ofs-L} - V_{th} + \cdot (V_{Sig} - V_{Ofs-L})$ と表すことができる。但し、 $0 < \cdot < 1$ であり、 $\cdot$ の値はコンデンサ部C<sub>1</sub>、発光部ELPの寄生容量C<sub>EL</sub>の値等により定まる。

#### 【0148】

これによって、5Tr/1C駆動回路において説明したと同様に、第1ノードND<sub>1</sub>と第2ノードND<sub>2</sub>の電位差、即ち、駆動トランジスタT<sub>Drv</sub>のゲート電極とソース領域との間の電位差V<sub>gs</sub>として、以下の式(3')で説明した値を得ることができる。

#### 【0149】

$$V_{gs} = V_{Sig} - (V_{Ofs-L} - V_{th}) - \cdot (V_{Sig} - V_{Ofs-L}) \quad (3')$$

#### 【0150】

即ち、3Tr/1C駆動回路においても、駆動トランジスタT<sub>Drv</sub>に対する書き込み処理において得られたV<sub>gs</sub>は、発光部ELPにおける輝度を制御するための映像信号V<sub>Sig</sub>、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>、及び、駆動トランジスタT<sub>Drv</sub>のゲート電極を初期化するための電圧V<sub>Ofs-L</sub>のみに依存している。そして、発光部ELPの閾値電圧V<sub>th-EL</sub>とは無関係である。

10

20

30

40

50

## 【0151】

[期間 - TP(3)<sub>6</sub>] (図15の(D)参照)

その後、駆動トランジスタT<sub>Drv</sub>の移動度μの大小に基づく駆動トランジスタT<sub>Drv</sub>のソース領域(第2ノードND<sub>2</sub>)の電位の補正(移動度補正処理)を行う。具体的には、5Tr/1C駆動回路において説明した[期間 - TP(5)<sub>6</sub>]と同じ動作を行えばよい。尚、移動度補正処理を実行するための所定の時間([期間 - TP(3)<sub>6</sub>]の全時間t<sub>0</sub>)は、有機EL表示装置の設計の際、設計値として予め決定しておけばよい。

## 【0152】

[期間 - TP(3)<sub>7</sub>] (図15の(E)参照)

以上の操作によって、閾値電圧キャンセル処理、書き込み処理、移動度補正処理が完了する。そして、5Tr/1C駆動回路において説明した[期間 - TP(5)<sub>7</sub>]と同じ処理がなされ、第2ノードND<sub>2</sub>の電位が上昇し、(V<sub>th-EL</sub> + V<sub>Cat</sub>)を越えるので、発光部ELPは発光を開始する。このとき、発光部ELPを流れる電流は、前述した式(5)にて得ることができるので、発光部ELPを流れる電流I<sub>ds</sub>は、発光部ELPの閾値電圧V<sub>th-EL</sub>、及び、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>には依存しない。即ち、発光部ELPの発光量(輝度)は、発光部ELPの閾値電圧V<sub>th-EL</sub>の影響、及び、駆動トランジスタT<sub>Drv</sub>の閾値電圧V<sub>th</sub>の影響を受けない。加えて、駆動トランジスタT<sub>Drv</sub>における移動度μのばらつきに起因したドレイン電流I<sub>ds</sub>のばらつき発生を抑制することができる。

10

## 【0153】

そして、発光部ELPの発光状態を第(m+m'-1)番目の水平走査期間まで継続する。この時点は、[期間 - TP(4)<sub>-1</sub>]の終わりに相当する。

20

## 【0154】

以上によって、有機EL素子10[第(n,m)番目の副画素(有機EL素子10)]の発光の動作が完了する。

## 【0155】

以上、本発明を好ましい実施例に基づき説明したが、本発明はこの実施例に限定されるものではない。実施例において説明した有機EL表示装置を構成する各種の構成要素の構成、構造は例示であり、適宜、変更することができる。

## 【0156】

実施例においては、発光制御トランジスタT<sub>EL\_C</sub>等をnチャネル型としたが、pチャネル型とすることもできる。尚、発光制御トランジスタT<sub>EL\_C</sub>をpチャネル型とする場合、例えば、[期間 - TP(5)<sub>6</sub>]の移動度補正処理の開始時、発光制御トランジスタT<sub>EL\_C</sub>がオン状態となるとき、駆動トランジスタT<sub>Drv</sub>のドレイン領域の電位は、電流供給部の電圧V<sub>cc</sub>へと上昇する。そして、このとき、駆動トランジスタT<sub>Drv</sub>のドレイン領域、即ち、発光制御トランジスタT<sub>EL\_C</sub>の他方のソース/ドレイン領域と、ゲート電極との間のカップリングによって、発光制御トランジスタT<sub>EL\_C</sub>のゲート電極の電位変化に変動が生じる。然るに、駆動回路が補助容量部C<sub>sub</sub>を備えることによって、前述したと同様に、駆動トランジスタT<sub>Drv</sub>のドレイン領域のカップリングに起因した発光制御トランジスタT<sub>EL\_C</sub>の他方のソース/ドレイン領域の変動を遅くすることができる結果、発光制御トランジスタT<sub>EL\_C</sub>の他方のソース/ドレイン領域とゲート電極との間のカップリングに起因した発光制御トランジスタT<sub>EL\_C</sub>のゲート電極の電位変化の変動を遅らせることができる。その結果、移動度補正処理の時間長に、発光制御トランジスタT<sub>EL\_C</sub>の他方のソース/ドレイン領域とゲート電極との間のカップリングに起因して大きな変動が生じてしまうといった現象の発生を確実に抑制することができるので、輝度に差が生じ難く、シェーディング(グラデーション)が発生し難い、高い表示品質を有する有機エレクトロルミネッセンス表示装置を提供することができる。

30

40

## 【図面の簡単な説明】

## 【0157】

【図1】図1は、本発明の5トランジスタ/1コンデンサ部から基本的に構成された駆動回路の等価回路図である。

50

【図2】図2は、5トランジスタ/1コンデンサ部から基本的に構成された駆動回路の概念図である。

【図3】図3は、5トランジスタ/1コンデンサ部から基本的に構成された駆動回路の駆動のタイミングチャートを模式的に示す図である。

【図4】図4の(A)~(D)は、5トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。

【図5】図5の(A)~(E)は、図4の(D)に引き続き、5トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。

【図6】図6は、本発明の4トランジスタ/1コンデンサ部から基本的に構成された駆動回路の等価回路図である。 10

【図7】図7は、4トランジスタ/1コンデンサ部から基本的に構成された駆動回路の概念図である。

【図8】図8は、4トランジスタ/1コンデンサ部から基本的に構成された駆動回路の駆動のタイミングチャートを模式的に示す図である。

【図9】図9の(A)~(D)は、4トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。

【図10】図10の(A)~(D)は、図9の(D)に引き続き、4トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。 20

【図11】図11は、本発明の3トランジスタ/1コンデンサ部から基本的に構成された駆動回路の等価回路図である。

【図12】図12は、3トランジスタ/1コンデンサ部から基本的に構成された駆動回路の概念図である。

【図13】図13は、3トランジスタ/1コンデンサ部から基本的に構成された駆動回路の駆動のタイミングチャートを模式的に示す図である。

【図14】図14の(A)~(D)は、3トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。 30

【図15】図15の(A)~(E)は、図14の(D)に引き続き、3トランジスタ/1コンデンサ部から基本的に構成された駆動回路を構成する各トランジスタのオン/オフ状態等を模式的に示す図である。

【図16】図16は、有機エレクトロルミネッセンス素子の一部分の模式的な一部断面図である。

【図17】図17は、従来の5トランジスタ/1コンデンサ部から基本的に構成された駆動回路の等価回路図である。

#### 【符号の説明】

##### 【0158】

$T_{Sig}$ ・・・映像信号書き込みトランジスタ、 $T_{Drv}$ ・・・駆動トランジスタ、 $T_{EL\_C}$ ・・・発光制御トランジスタ、 $T_{ND1}$ ・・・第1ノード初期化トランジスタ、 $T_{ND2}$ ・・・第2ノード初期化トランジスタ、 $C_1$ ・・・コンデンサー部、ELP・・・有機エレクトロルミネッセンス発光部（発光部）、 $C_{Sub}$ ・・・補助容量部、 $C_{EL}$ ・・・発光部ELPの寄生容量、 $ND_1$ ・・・第1ノード、 $ND_2$ ・・・第2ノード、SCL・・・走査線、DTL・・・データ線、CSL・・・電流供給線、 $CL_{EL\_C}$ ・・・発光制御トランジスタ制御線、 $AZ_{ND1}$ ・・・第1ノード初期化トランジスタ制御線、 $AZ_{ND2}$ ・・・第2ノード初期化トランジスタ制御線、10・・・有機エレクトロルミネッセンス素子、20・・・支持体、21・・・基板、31・・・ゲート電極、32・・・ゲート絶縁層、33・・・半導体層、34・・・チャネル形成領域、35・・・ソース/ドレイン領域、36・・・他方の電極、37・・・一方の電極、38, 39・・・配線、40・・・層間絶縁層、51・・・アノード電極、52・・・正孔輸送層、発光層及び電子輸送層、53・・・カソード電極 40 50

、 5 4 . . . 第 2 層間絶縁層、 5 5 , 5 6 . . . コンタクトホール、 1 0 0 . . . 電流供給部、 1 0 1 . . . 走査回路、 1 0 2 . . . 映像信号出力回路、 1 0 3 . . . 発光制御トランジスタ制御回路、 1 0 4 . . . 第 1 ノード初期化トランジスタ制御回路、 1 0 5 . . . 第 2 ノード初期化トランジスタ制御回路、 1 0 6 . . . 第 1 ノード初期化電源、 1 0 7 . . . 第 2 ノード初期化電源

【図 1】

【図 1】 [5 Tr / 1 C 駆動回路]

- T<sub>Sig</sub> : 映像信号書き込みトランジスタ

- T<sub>Drv</sub> : 駆動トランジスタ

- T<sub>EL\_C</sub> : 発光制御トランジスタ

- T<sub>ND1</sub> : 第 1 ノード初期化トランジスタ

- T<sub>ND2</sub> : 第 2 ノード初期化トランジスタ

- C<sub>1</sub> : コンデンサ部

- ELP : 有機 E L 発光素子の発光部

- C<sub>EL</sub> : 発光部の寄生容量

- C<sub>Sub</sub> : 補助容量部

- DTL : データ線

- SCL : 走査線

- CL<sub>EL\_C</sub> : 発光制御トランジスタ制御線

- AZ<sub>ND1</sub> : 第 1 ノード初期化トランジスタ制御線

- AZ<sub>ND2</sub> : 第 2 ノード初期化トランジスタ制御線

- 106 : 第 1 ノード初期化電源

- 107 : 第 2 ノード初期化電源

【図 2】

【図 2】 [5 Tr / 1 C 駆動回路構成の表示装置]

## 【図3】

【図3】 [5 Tr / 1 C 駆動回路]

## 【図4】

【図4】 [5 Tr / 1 C 駆動回路]

## 【図5】

【図5】 [5 Tr / 1 C 駆動回路]

## 【図6】

【図6】 [4 Tr / 1 C 駆動回路]

T<sub>Sig</sub> : 映像信号書き込みトランジスタT<sub>Drv</sub> : 駆動トランジスタT<sub>EL\_C</sub> : 発光制御トランジスタT<sub>ND2</sub> : 第2ノード初期化トランジスタC<sub>1</sub> : コンデンサ部

ELP : 有機EL発光素子の発光部

C<sub>EL</sub> : 発光部の寄生容量C<sub>Sub</sub> : 助導容量部

DTL : データ線

SCL : 走査線

CL<sub>EL\_C</sub> : 発光制御トランジスタ制御線AZ<sub>S</sub> : 第2ノード初期化トランジスタ制御線

107 : 第2ノード初期化電源

【図7】

【図7】 [4 T r / 1 C 駆動回路構成の表示装置]

【図8】

【図8】 [4 T r / 1 C 駆動回路]

【図9】

【図9】 [4 T r / 1 C 駆動回路]

【図10】

【図10】 [4 T r / 1 C 駆動回路]

【図 1 1】

【図 1 1】 [3 Tr / 1 C 駆動回路]

【図 1 2】

【図 1 2】 [3 Tr / 1 C 駆動回路構成の表示装置]

【図 1 3】

【図 1 3】 [3 Tr / 1 C 駆動回路]

【図 1 4】

【図 1 4】 [3 Tr / 1 C 駆動回路]

## 【図 1 5】

【図 1 5】 [3 Tr r / 1 C 駆動回路]

## 【図 1 6】

【図 1 6】

## 【図 1 7】

【図 1 7】 [従来の 5 Tr r / 1 C 駆動回路]

---

フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 2 1 M |

|             | G 0 9 G | 3/20 6 4 2 A |

|             | G 0 9 G | 3/20 6 1 1 J |

|             | G 0 9 G | 3/20 6 1 2 R |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光器件和有机电致发光显示器件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2008242369A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2008-10-09 |

| 申请号            | JP2007086677                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2007-03-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 山本哲郎<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 山本 哲郎<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/30 H01L51/50 G09F9/30 H01L27/32 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G09G3/30.J H05B33/14.A G09F9/30.338 G09F9/30.365.Z G09G3/20.624.B G09G3/20.621.M G09G3/20.642.A G09G3/20.611.J G09G3/20.612.R G09F9/30.365 G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD01 5C080/DD05 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C094/AA53 5C094/BA03 5C094/BA27 5C094/DB01 5C380/AA01 5C380/AB06 5C380/BA38 5C380/BA39 5C380/BB05 5C380/BE01 5C380/CA08 5C380/CA09 5C380/CA12 5C380/CB01 5C380/CB17 5C380/CC03 5C380/CC04 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC63 5C380/CC64 5C380/CC65 5C380/CD013 5C380/CD014 5C380/CD015 5C380/CD023 5C380/CD024 5C380/CD025 5C380/DA02 5C380/DA06 5C380/DA32 5C380/DA35 |         |            |

| 代理人(译)         | 山本隆久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

解决的问题：提供一种有机EL元件，其结构和结构能够使迁移率校正处理的时间长度恒定而不依赖于与发光控制晶体管控制电路的距离。有机EL元件包括驱动电路和发光单元ELP，并且该驱动电路包括驱动晶体管T<sub>驱动</sub>，视频信号写入晶体管T<sub>信号</sub>，发光控制晶体管T<sub>EL\_C</sub>和电容器单元C。1，并且驱动电路还具有辅助电容，其中一个电极连接到固定电源部分，另一个电极连接到发射控制晶体管T的另一个源/漏区EL\_C。它具有C部分子。**[选型图]**图1