(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6683690号

(P6683690)

(45) 発行日 令和2年4月22日(2020.4.22)

(24) 登録日 令和2年3月30日(2020.3.30)

|                             |              |

|-----------------------------|--------------|

| (51) Int.Cl.                | F 1          |

| <b>H05B 33/02</b> (2006.01) | H05B 33/02   |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 A |

| <b>H05B 33/12</b> (2006.01) | H05B 33/12 B |

| <b>H05B 33/22</b> (2006.01) | H05B 33/22 Z |

| <b>H01L 27/32</b> (2006.01) | H01L 27/32   |

請求項の数 15 (全 16 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2017-514408 (P2017-514408)  |

| (86) (22) 出願日      | 平成26年10月9日(2014.10.9)         |

| (65) 公表番号          | 特表2017-536646 (P2017-536646A) |

| (43) 公表日           | 平成29年12月7日(2017.12.7)         |

| (86) 国際出願番号        | PCT/US2014/059936             |

| (87) 国際公開番号        | W02016/048385                 |

| (87) 国際公開日         | 平成28年3月31日(2016.3.31)         |

| 審査請求日              | 平成29年4月11日(2017.4.11)         |

| (31) 優先権主張番号       | 14/494,931                    |

| (32) 優先日           | 平成26年9月24日(2014.9.24)         |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 503260918<br>アップル インコーポレイテッド<br>Apple Inc.<br>アメリカ合衆国 95014 カリフォルニア州 クパチーノ アップル パーク<br>ウェイ ワン<br>One Apple Park Way,<br>Cupertino, California 95014, U. S. A. |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                                                                                                                                        |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                                                                                                                                        |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                                                                                                                                        |

最終頁に続く

(54) 【発明の名称】シリコン及び半導体酸化物の薄膜トランジスタディスプレイ

## (57) 【特許請求の範囲】

## 【請求項 1】

有機発光ダイオードディスプレイであって、

基板と、

前記基板のアクティブ領域を形成する画素回路のアレイと、

前記基板の非アクティブ領域内の回路と、

複数の誘電体層であって、前記複数の誘電体層は前記アクティブ領域に存在し、前記複数の誘電体層のうちの少なくとも一部は前記非アクティブ領域に存在しない、複数の誘電体層と、

前記アクティブ領域から前記非アクティブ領域まで延在するデータ線であって、前記複数の誘電体層は、前記アクティブ領域から前記非アクティブ領域に移行するときに高さが減少する階段状プロファイルを有し、前記データ線は、前記階段状プロファイルを有する前記複数の誘電体層上に形成される、データ線と、

を備え、各画素回路は、

有機発光ダイオードと、

前記有機発光ダイオードと直列に結合されたシリコントランジスタと、

前記シリコントランジスタに結合された蓄積コンデンサと、

前記蓄積コンデンサに結合された半導体酸化物トランジスタと、

を含み、

前記基板は前記非アクティブ領域で折り曲げられる、有機発光ダイオードディスプレイ

10

20

。

【請求項 2】

各画素回路内の前記シリコントランジスタはシリコンチャネルを含み、前記複数の誘電体層は前記基板と前記シリコンチャネルとの間にバッファ層を含み、前記バッファ層は前記非アクティブ領域に存在しない、請求項 1 に記載の有機発光ダイオードディスプレイ。

【請求項 3】

前記アクティブ領域内に第 1 金属層を更に備え、前記第 1 金属層のうちの一部は、各画素回路内の前記シリコントランジスタのゲートを形成する、請求項 2 に記載の有機発光ダイオードディスプレイ。

【請求項 4】

前記第 1 金属層のうちの一部は、各画素回路内の前記半導体酸化物トランジスタのゲートを、各画素回路内の前記シリコントランジスタの前記ゲートと各画素回路内の前記半導体酸化物トランジスタの前記ゲートとがともに前記第 1 金属層から形成されるように形成する、請求項 3 に記載の有機発光ダイオードディスプレイ。

【請求項 5】

第 2 金属層を更に備え、前記第 2 金属層は、前記シリコントランジスタ及び前記半導体酸化物トランジスタのソース / ドレイン端子を形成するように前記アクティブ領域内でパターン化される、請求項 3 に記載の有機発光ダイオードディスプレイ。

【請求項 6】

前記第 2 金属層は、前記画素回路のアレイと前記非アクティブ領域内の前記回路との間で結合される前記データ線を、前記ソース / ドレイン端子と前記データ線とがともに前記第 2 金属層から形成されるように形成するように前記非アクティブ領域内でパターン化される、請求項 5 に記載の有機発光ダイオードディスプレイ。

【請求項 7】

前記基板は折れ曲がった可撓性基板であり、前記データ線は、前記複数の誘電体層のいずれも前記データ線と前記基板との間に介在しないように折れ曲がり且つ前記基板の表面上に形成される、請求項 6 に記載の有機発光ダイオードディスプレイ。

【請求項 8】

各画素における前記半導体酸化物トランジスタは、半導体酸化物チャネルを含む、請求項 7 に記載の有機発光ダイオードディスプレイ。

【請求項 9】

前記複数の誘電体層は、各画素回路内の前記シリコントランジスタの前記シリコンチャネルと重なり、且つ、各画素回路内の前記半導体酸化物トランジスタの前記半導体酸化物チャネルと重ならない、窒化ケイ素層を含む、請求項 8 に記載の有機発光ダイオードディスプレイ。

【請求項 10】

前記蓄積コンデンサは、前記第 2 金属層から形成された第 1 電極を有し、かつ、第 2 電極を有する、請求項 9 に記載の有機発光ダイオードディスプレイ。

【請求項 11】

前記複数の誘電体層は追加の窒化ケイ素層を含み、前記追加の窒化ケイ素層は、各画素回路内の前記蓄積コンデンサの前記第 1 と第 2 電極との間に介在する、請求項 10 に記載の有機発光ダイオードディスプレイ。

【請求項 12】

シリコン酸化物層を更に備え、前記シリコン酸化物層は、各画素回路の前記半導体酸化物チャネルと重なり、且つ、前記シリコン酸化物層が前記蓄積コンデンサの前記第 1 と第 2 電極との間に介在しないように各画素回路の前記蓄積コンデンサ内で局所的に除去される、請求項 11 に記載の有機発光ダイオードディスプレイ。

【請求項 13】

各画素回路の前記半導体酸化物トランジスタは駆動トランジスタを含み、各画素回路の前記シリコントランジスタはスイッチングトランジスタを含む、請求項 1 に記載の有機發

10

20

30

40

50

光ダイオードディスプレイ。

【請求項 14】

有機発光ダイオードディスプレイであって、

基板と、

前記基板のアクティブ領域を形成する有機発光ダイオードのアレイと、

それぞれが前記有機発光ダイオードのうちの対応する1つに直列に結合されたシリコン駆動トランジスタと、

前記シリコン駆動トランジスタに結合された半導体酸化物スイッチングトランジスタと、

前記半導体酸化物スイッチングトランジスタに結合された蓄積コンデンサと、

前記基板の非アクティブ領域内の回路と、

複数の誘電体層であって、前記複数の誘電体層は前記アクティブ領域に存在し、前記複数の誘電体層のうちの少なくとも一部は前記非アクティブ領域に存在しない、複数の誘電体層と、

前記アクティブ領域から前記非アクティブ領域まで延在するデータ線であって、前記複数の誘電体層は、前記アクティブ領域から前記非アクティブ領域に移行するときに高さが減少する階段状プロファイルを有し、前記データ線は、前記階段状プロファイルを有する前記複数の誘電体層上に形成される、データ線と、

を備える、有機発光ダイオードディスプレイ。

【請求項 15】

有機発光ダイオードディスプレイであって、

可撓性ポリマー基板と、

前記可撓性ポリマー基板上の画素回路のアレイであって、各画素回路は、有機発光ダイオードと、半導体酸化物チャネルをそれぞれ有する少なくとも2つの半導体酸化物トランジスタと、前記有機発光ダイオードと直列に結合された少なくとも1つのシリコントランジスタと、少なくとも1つの蓄積コンデンサと、を含む、画素回路のアレイと、

前記画素回路のアレイから前記画素回路のアレイに隣接する非アクティブ領域に移行するときに高さが減少する階段状プロファイルを有する、前記可撓性ポリマー基板上の複数の誘電体層と、

前記階段状プロファイルに従う前記複数の誘電体層上のデータ線と、を備え、前記複数の誘電体層は、前記シリコントランジスタと重なり且つ前記半導体酸化物チャネルと重ならない誘電体層を含み、

前記可撓性ポリマー基板は前記非アクティブ領域で折り曲げられる、有機発光ダイオードディスプレイ。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、2014年9月24日に出願された米国特許出願第14/494,931号に対して優先権を主張するものであり、この参照により、その全体が本明細書に組み込まれる。

これは、一般に、電子デバイスに関し、より詳細には、薄膜トランジスタを有するディスプレイを備えた電子デバイスに関するものである。

【背景技術】

【0002】

電子デバイスは、ディスプレイを備えることが多い。例えば、携帯電話及びポータブルコンピュータは、ユーザに情報を提供するためのディスプレイを備えている。

【0003】

有機発光ダイオードディスプレイなどのディスプレイは、発光ダイオードに基づく画素のアレイを有する。この種類のディスプレイでは、各画素は、発光ダイオード、及び、発光ダイオードへの信号の印加を制御するための薄膜トランジスタを含んでいる。

10

20

30

40

50

**【0004】**

注意を払わなければ、ディスプレイの薄膜トランジスタ回路は、過剰なトランジスタ漏洩電流、不十分なトランジスタ駆動強度、劣悪な領域効率、ヒステリシス、不均一性、及び他の問題を呈する恐れがある。したがって、改良された電子デバイスディスプレイを提供できることが望ましい。

**【発明の概要】****【0005】**

電子デバイスはディスプレイを備えることができる。ディスプレイは、アクティブ領域を形成する画素を有してもよい。非アクティブ境界領域は、アクティブ領域の縁部に沿って延在することができる。画素は、基板上の画素回路のアレイから形成することができる。基板は、剛性材料から形成してもよく、あるいは、非アクティブ領域内で折れ曲がる可撓性材料から形成してもよい。

10

**【0006】**

各画素回路は、有機発光ダイオードと、その有機発光ダイオードに結合された駆動トランジスタと、を含むことができる。各駆動トランジスタは、それが結合されている有機発光ダイオードにどれだけの電流が流れ、そのダイオードによってどのくらいの光が生成されるかを制御するように調整することができる。各画素回路は、スイッチングトランジスタなどの1つ以上の追加のトランジスタを含んでもよく、蓄積コンデンサを含んでもよい。

**【0007】**

20

画素回路のトランジスタを形成するには、半導体酸化物トランジスタ及びシリコントランジスタを使用することができる。例えば、半導体酸化物トランジスタをスイッチングトランジスタとして使用し、シリコントランジスタを駆動トランジスタとして使用してもよい。画素回路当たり、1つの駆動トランジスタ及び1つ以上の追加のトランジスタがあり得る。

**【0008】**

蓄積コンデンサ及びトランジスタは、金属層、半導体構造、及び誘電体層を用いて形成することができる。複数の誘電体層は、データ線がディスプレイの非アクティブな折れ曲がった縁部領域内に延在するにつれて、画素回路のアレイ内のデータ線が基板の表面に向かって徐々に降下することを可能にする階段状のプロファイルを有することができる。折り曲げを容易にするために、誘電体層の一部又は全部を非アクティブ縁部領域で除去することができる。

30

**【図面の簡単な説明】****【0009】**

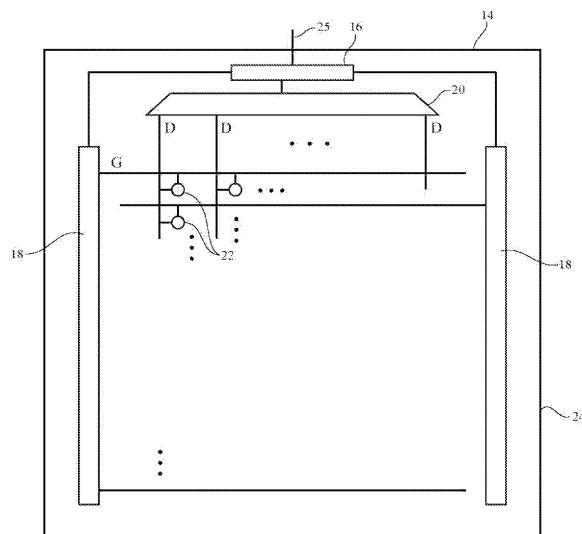

【図1】一実施形態に係る、有機発光ダイオード画素のアレイを有する有機発光ダイオードディスプレイなどの例示的なディスプレイの図である。

**【0010】**

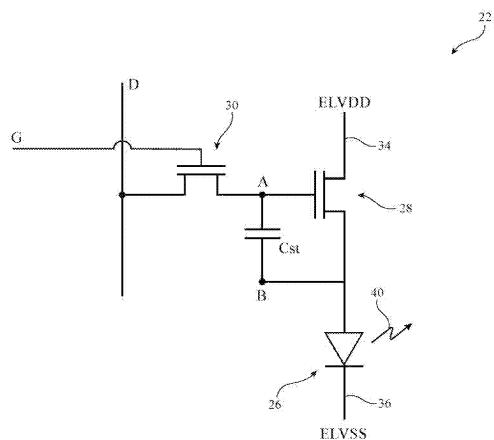

【図2】一実施形態に係る、半導体酸化物薄膜トランジスタ及びシリコン薄膜トランジスタを有する、有機発光ダイオードに使用され得る種類の例示的な有機発光ダイオードディスプレイ画素の図である。

40

**【0011】**

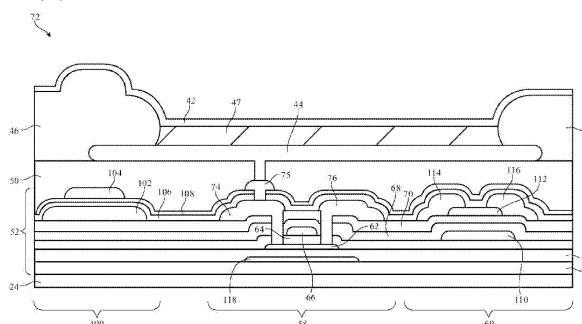

【図3】一実施形態に係る、ボトムゲート構成を用いて半導体酸化物薄膜トランジスタが形成された構成の、表示画素に関する例示的な薄膜トランジスタ構造の断面側面図である。

**【0012】**

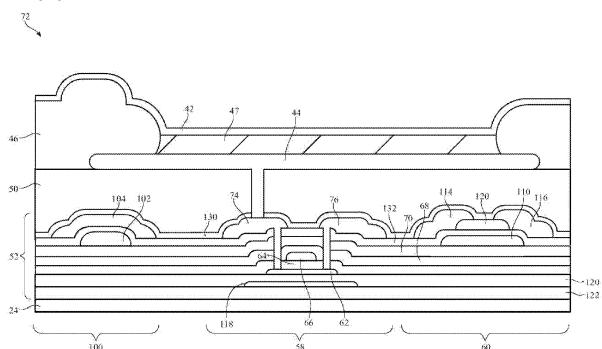

【図4】一実施形態に係る、トップゲート構成を用いて半導体酸化物薄膜トランジスタが形成された構成の、表示画素に関する例示的な薄膜トランジスタ構造の断面側面図である。

**【0013】**

【図5】一実施形態に係る、半導体酸化物薄膜トランジスタがボトムゲート構成を用いて

50

形成され、かつ、蓄積コンデンサが、半導体酸化物薄膜トランジスタのゲートと同じ金属層からパターン化されたた、第1電極と、トランジスタソース／ドレイン電極もまた形成する第2電極と、を含む構成の、表示画素に関する例示的な薄膜トランジスタ構造の断面側面図である。

【0014】

【図6】一実施形態に係る、半導体酸化物薄膜トランジスタがボトムゲート構成を用いて形成され、かつ、シリコントランジスタの薄膜トランジスタゲート金属としてもまた機能する金属層からパターン化された下部電極を使用して蓄積コンデンサが形成される、構成の表示画素に関する例示的な薄膜トランジスタ構造の断面側面図である。

【0015】

10

【図7】一実施形態に係る、半導体酸化物薄膜トランジスタが、そのゲートとそのチャネルとの間に3層の層間絶縁体が介在するボトムゲート構造を用いて形成される構成の、表示画素に関する例示的な薄膜トランジスタ構造の断面側面図である。

【0016】

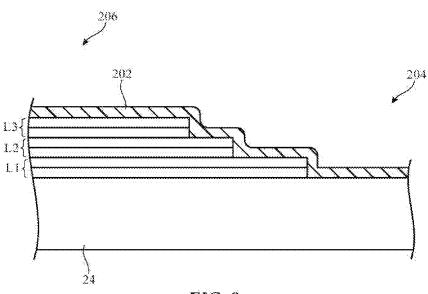

【図8】一実施形態に係る、折れ曲がった縁部を有する例示的なディスプレイの斜視図である。

【0017】

【図9】一実施形態に係る、折れ曲がった縁部を有するディスプレイに関する例示的な複数の階段状誘電体層の断面側面図である。

【0018】

20

【図10】一実施形態に係る、材料の上部層がディスプレイから除去されて、ディスプレイの縁部に沿った非アクティブ領域におけるディスプレイの折り曲げを容易にする構成の、ディスプレイに関する例示的な薄膜トランジスタ構造の断面側面図である。

【0019】

【図11】一実施形態に係る、ディスプレイの縁部に沿った折り曲げ領域におけるディスプレイの折り曲げを容易にするために、材料の上部層がディスプレイから除去され、かつ、半導体酸化物トランジスタ構造が、水素が豊富な窒化ケイ素とは重ならない、構成のディスプレイに関する例示的な薄膜トランジスタ構造の断面側面図である。

【発明を実施するための形態】

【0020】

30

電子デバイスのディスプレイは、画素アレイ上に画像を表示するための駆動回路を備えることができる。例示的なディスプレイを図1に示す。図1に示すように、ディスプレイ14は、基板24などの1つ以上の層を有してもよい。基板24などの層は、ガラス、プラスチック、セラミック、及び／又は他の誘電体などの絶縁材料から形成することができる。基板24は長方形であってもよく、あるいは他の形状を有してもよい。基板24の形成には、硬質基板材料（例えば、ガラス）又は可撓性基板材料（例えば、ポリイミド又は他の材料の層などの可撓性のあるポリマーシート）を使用することができる。

【0021】

ディスプレイ14は、ユーザに対して画像を表示するための画素22のアレイ（画素回路と呼ばれることがある）を有することができる。画素22のアレイは、基板24上の画素構造の行及び列から形成してもよい。画素22のアレイには、任意の好適な数の行及び列（例えば、10以上、100以上、又は1000以上）が存在し得る。

40

【0022】

ディスプレイドライバ集積回路16などのディスプレイドライバ回路は、はんだ又は導電性接着剤を用いて基板24上の金属トレースなどの導電性経路に結合してもよい。ディスプレイドライバ集積回路16（タイミングコントローラチップと呼ばれることがある）は、経路25を通じてシステム制御回路と通信するための通信回路を含むことができる。経路25は、フレキシブルプリント回路又は他のケーブル上のトレースから形成してもよい。この制御回路は、携帯電話、コンピュータ、セットトップボックス、メディアプレーヤ、ポータブル電子デバイス、腕時計型デバイス、タブレットコンピュータ、又はディス

50

プレイ 1 4 が使用される他の電子装置、などの電子デバイスのメインロジックボード上に配置してもよい。動作中に、制御回路は、ディスプレイドライバ集積回路 1 6 に対して、ディスプレイ 1 4 に表示される画像に関する情報を提供することができる。表示画素 2 2 に画像を表示するために、ディスプレイドライバ集積回路 1 6 は、対応する画像データをデータ線 D に供給し、ゲートドライバ回路 1 8 及び逆多重化回路 2 0 などの、補助用の薄膜トランジスタディスプレイドライバ回路に対して、クロック信号及び他の制御信号を発行することができる。

#### 【 0 0 2 3 】

ゲートドライバ回路 1 8 は、基板 2 4 上に（例えば、ディスプレイ 1 4 の左端及び右端に、ディスプレイ 1 4 の单一の端部のみに、又はディスプレイ 1 4 の他の場所に）形成することができる。逆多重化回路 2 0 は、ディスプレイドライバ集積回路 1 6 からのデータ信号を複数の対応するデータ線 D に分離するために使用することができる。図 1 の例示的な構成では、データ線 D はディスプレイ 1 4 に沿って垂直に走る。各データ線 D は、表示画素 2 2 の対応する列に関連付けられている。ゲート線 G はディスプレイ 1 4 に沿って水平に走る。各ゲート線 G は、表示画素 2 2 の対応する行に関連付けられている。ゲートドライバ回路 1 8 は、図 1 に示すように、ディスプレイ 1 4 の左側、ディスプレイ 1 4 の右側、又はディスプレイ 1 4 の左右両側に配置することができる。

#### 【 0 0 2 4 】

ゲートドライバ回路 1 8 は、ディスプレイ 1 4 のゲート線 G 上のゲート信号（走査信号と呼ばれることがある）をアサートすることができる。例えば、ゲートドライバ回路 1 8 は、ディスプレイドライバ集積回路 1 6 からクロック信号及び他の制御信号を受信することができ、受信信号に応じて、表示画素 2 2 の第 1 行のゲート線信号 G から開始して、ゲート線 G 上にゲート信号を順番にアサートすることができる。各ゲート線がアサートされると、ゲート線がアサートされた行の対応する表示画素は、データ線 D に現れる表示データを表示する。

#### 【 0 0 2 5 】

ディスプレイドライバ回路 1 6 は、1 つ以上の集積回路を使用して実装することができる。逆多重化回路 2 0 及びゲートドライバ回路 1 8 などのディスプレイドライバ回路は、基板 2 4 上の1つ以上の集積回路及び／又は薄膜トランジスタ回路を使用して実装することができる。薄膜トランジスタは、表示画素 2 2 に回路を形成するのに使用してもよい。表示性能を向上させるために、漏洩電流、スイッチング速度、駆動強度、均一性などの所望の基準を満たすディスプレイ 1 4 の薄膜トランジスタ構造を使用することができる。ディスプレイ 1 4 の薄膜トランジスタは、一般に、任意の好適な種類の薄膜トランジスタ技術（例えば、シリコン系、半導体酸化物系など）を用いて形成することができる。

#### 【 0 0 2 6 】

本明細書で例として説明されることがある1つの好適な構成によれば、ディスプレイ 1 4 上のいくつかの薄膜トランジスタのチャネル領域（アクティブ領域）は、シリコン（例えば、L T P S 又は低温ポリシリコンと呼ばれることがある低温プロセスを用いて堆積されたポリシリコンなどのシリコン）から形成され、ディスプレイ 1 4 上の他の薄膜トランジスタは、半導体酸化物材料（例えば、I G Z O と呼ばれることがあるアモルファスインジウムガリウム亜鉛酸化物）から形成される。また、所望であれば、アモルファスシリコン、I G Z O 以外の半導電性酸化物などの薄膜トランジスタの形成に、他の種類の半導体を用いてもよい。この種類のハイブリッドディスプレイ構成では、スイッチング速度及び良好な信頼性などの属性が望まれる場合（例えば、画素内の有機発光ダイオードを通る電流を駆動する駆動トランジスタの場合）、シリコントランジスタ（例えば、L T P S トランジスタ）を使用することができる。一方、低漏洩電流が望まれる場合（例えば、可変リフレッシュレート方式を実施するディスプレイ内の表示画素スイッチングトランジスタ又は低漏洩電流が必要な他のシナリオとして）、酸化物トランジスタ（例えば、I G Z O トランジスタ）を使用することができる。他の考慮事項（例えば、電力消費、消費面積、ヒステリシス、トランジスタ均一性などに関する考慮事項）も考慮に入れることができる。

10

20

30

40

50

## 【0027】

IGZO薄膜トランジスタなどの酸化物トランジスタは、一般にnチャネルデバイス（即ち、NMOSトランジスタ）であるが、所望であれば、PMOSデバイスを酸化物トランジスタに使用することができる。シリコントランジスタはまた、pチャネル又はnチャネルの設計（即ち、LTPSデバイスはPMOS又はNMOSのどちらでもよい）を使用して製造することができる。これらの薄膜トランジスタ構造の組み合わせは、有機発光ダイオードディスプレイに最適な性能を提供することができる。

## 【0028】

有機発光ダイオードディスプレイでは、各画素は、対応する有機発光ダイオードを含む。例示的な有機発光ダイオードディスプレイ画素の概略図を図2に示す。図2に示すように、画素22は、発光ダイオード26を含むことができる。正電源端子34に正の電源電圧ELVDDを供給し、接地電源端子36に接地電源電圧ELVSSを供給してもよい。駆動トランジスタ28の状態は、ダイオード26を流れる電流の量、したがって表示画素22から放出される光40の量を制御する。

10

## 【0029】

連続するフレームのデータ間でトランジスタ28が所望の状態に確実に保持されるように、表示画素22は、蓄積コンデンサCstなどの蓄積コンデンサを含んでもよい。蓄積コンデンサCst上の電圧は、トランジスタ28を制御するためにノードAでトランジスタ28のゲートに印加される。データは、スイッチングトランジスタ30などの1つ以上のスイッチングトランジスタを使用して、蓄積コンデンサCstにロードすることができる。スイッチングトランジスタ30がオフのとき、データ線Dは蓄積コンデンサCstから分離され、端子Aのゲート電圧は蓄積コンデンサCstに記憶されたデータ値に等しい（即ち、表示データの前のフレームからのデータ値がディスプレイ14に表示されている）。画素22に関連する行のゲート線G（走査線と呼ばれることがある）がアサートされると、スイッチングトランジスタ30がオンになり、データ線D上の新しいデータ信号が蓄積コンデンサCstにロードされる。コンデンサCst上の新しい信号は、ノードAでトランジスタ28のゲートに印加され、それによってトランジスタ28の状態を調整し、発光ダイオード26によって放出される対応する光40の量を調整する。

20

## 【0030】

図2の例示的な画素回路は、ディスプレイ14内の画素アレイに対して使用され得る回路の単なる一例である。例えば、各画素回路は、任意の好適な数のスイッチングトランジスタ（1つ以上、2つ以上、3つ以上など）を含むことができる。所望であれば、有機発光ダイオード表示画素22は、追加構成要素（例えば、閾値電圧補償などの機能の実現を助けるための駆動トランジスタと直列に結合された1つ又は2つの発光可能トランジスタ）を有することができる。概して、本明細書に記載の薄膜トランジスタ構造は、図2の画素回路と共に、又は他の任意の好適な画素回路と共に使用することができる。一例として、本明細書に記載の薄膜トランジスタ構造は、2つの異なる走査線によって制御される3つのスイッチングトランジスタ、有機発光ダイオードと直列に結合された駆動トランジスタ、及び2つの対応する発光線によって制御され、かつ、駆動トランジスタ及び発光ダイオードと直列に結合されて閾値電圧補償機能を実施する2つの発光イネーブルトランジスタ、を有する6トランジスタ画素回路に使用することができる。ディスプレイ14の画素用の薄膜トランジスタ回路はまた、他の数のスイッチングトランジスタ（例えば、1つ以上、2つ以上、3つ以上、4つ以上など）又は他の数の発光トランジスタ（発光トランジスタなし、1つ以上の発光トランジスタ、2つ以上の発光トランジスタ、3つ以上の発光トランジスタ、4つ以上の発光トランジスタ、など）を含むことができる。各画素回路内のトランジスタは、シリコン及びシリコン酸化物トランジスタの任意の好適な組み合わせ、並びに、NMOS及びPMOSトランジスタの任意の好適な組み合わせ、から形成することができる。図2の画素回路は、単なる例示に過ぎない。

30

## 【0031】

図2の画素22などの有機発光ダイオード画素、又はディスプレイ14用の任意の他の

40

50

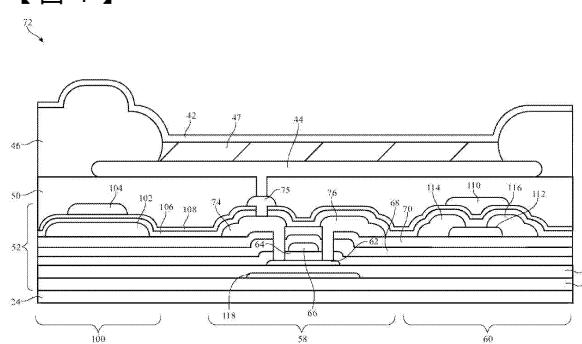

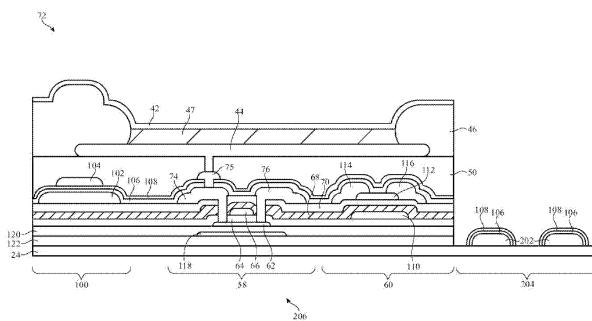

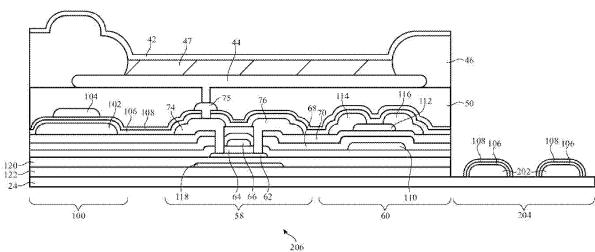

好適な画素回路は、図3に示される種類の薄膜トランジスタ構造を使用することができる。この種類の構造では、2つの異なる種類の半導体が使用される。図3に示すように、画素回路72は、発光ダイオードカソード端子42及び発光ダイオードアノード端子44などの画素構造を含むことができる。有機発光ダイオード発光材料47は、カソード42とアノード44との間に介在し、それによって、図2の発光ダイオード26を形成することができる。誘電体層46は、画素のレイアウトを画定する機能（例えば、アノード44に対する発光材料47の位置合わせ）を果たし、画素画定層と呼ばれることがある。平坦化層50（例えば、ポリマー層）は、薄膜トランジスタ構造52の上部に形成してもよい。薄膜トランジスタ構造52は、基板24上に形成することができる。基板24は、剛性又は可撓性であってもよく、ガラス、セラミック、サファイアなどの結晶質材料、ポリマー（例えば、ポリイミドの可撓性層又は他のポリマー材料の可撓性シート）などから形成してもよい。10

#### 【0032】

薄膜トランジスタ構造52は、シリコントランジスタ58などのシリコントランジスタを含むことができる。トランジスタ58は、「トップゲート」設計を用いて形成されたLT

TPSトランジスタとしてもよく、画素22に任意のトランジスタを形成するために使用してもよい（例えば、トランジスタ58は、図2の画素22内の駆動トランジスタ28などの駆動トランジスタとして機能することができる）。トランジスタ58は、ゲート絶縁層64（例えば、シリコン酸化物層又は他の無機層）によって覆われたポリシリコンチャネル62を有することができる。ゲート66は、パターン化された金属（例えば、一例として、モリブデン）から形成することができる。ゲート66は、層間誘電体の層（例えば、窒化ケイ素層68及びシリコン酸化物層70又は他の無機層又は有機材料）によって覆ってもよい。ソース／ドレインの接点74及び76は、ポリシリコン層62の対向する側面に接触して、シリコン薄膜トランジスタ58を形成してもよい。20

#### 【0033】

ゲート66は金属層GATEから形成することができ、ソース／ドレイン端子74及び76は、金属層SDから形成することができ、追加の金属層M3を使用して金属ピア75を形成して、ソース／ドレイン電極74をアノード44に結合することができる。

#### 【0034】

回路72はまた、コンデンサ構造100（例えば、図2のコンデンサCst）などのコンデンサ構造を含むことができる。コンデンサ構造100は、電極102などの下部電極、及び、電極104などの上部電極を有することができる。下部電極102は、金属層SDのパターン化部分から形成することができる。上部電極104は、金属層M3のパターン化部分から形成することができる。誘電体層は、上部電極104及び下部電極102を分離することができる。誘電体層は、酸化ハフニウム又は酸化アルミニウムなどの高誘電率材料から形成してもよく、あるいは、1つ以上の他の層から形成してもよい。図3の例では、電極102及び104を分離する誘電体層は、2つのパッシベーション層106及び108を含んでいる。層106及び108は、それぞれ、シリコン酸化物及び窒化ケイ素から形成することができる。他の無機層及び／又は有機層は、所望であれば、層106及び108を形成するのに使用することができる（例えば、酸化物層、窒化物層、ポリマー層など）。

#### 【0035】

薄膜トランジスタ構造52は、半導体酸化物トランジスタ60などの半導体酸化物トランジスタを含むことができる。構造60内の薄膜トランジスタは、「ボトムゲート」酸化物トランジスタとしてもよい。トランジスタ60のゲート110は、金属層GATEの一部から形成することができる。トランジスタ60の半導体酸化物チャネル領域（チャネル112）は、IGZOなどの半導体酸化物から形成することができる。層間誘電体（例えば、層68及び70）は、ゲート110と半導体酸化物チャネル112との間に介在し、トランジスタ60のゲート絶縁体層として機能することができる。酸化物トランジスタ60は、金属層SDのパターン化された部分から形成されたソース／ドレイン端子114及30

40

50

び 116 を有することができる。

【0036】

基板 24 上のバッファ層 122 は、ポリイミド又は他の誘電体の層から形成することができる。トランジスタ 58 の下には、バッファ層 122 の電荷からトランジスタ 58 を遮蔽するために、裏面金属層 118 を形成することができる。バッファ層 120 は、シールド層 118 の上に形成することができ、誘電体（例えば、ポリマー層などの有機層、又は他の絶縁層）から形成することができる。

【0037】

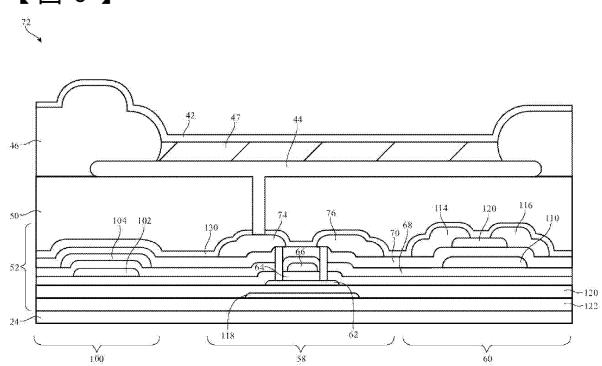

画素回路 22 用の追加の例示的な薄膜トランジスタ回路 72 が図 4 に示されている。図 4 の例では、酸化物トランジスタ 60 は、「トップゲート」構成を用いて形成されている。この手法では、トランジスタ 60 のゲート 110 は、金属層 M3 のパターン化された部分から形成される。金属層 M3 は、コンデンサ 100 の電極 104（一例として）を形成するのに使用することができる。金属層 SD は、電極 102、ソース／ドレイン端子 74 及び 76、並びにソース／ドレイン端子 114 及び 116 を形成するのに使用してもよい。酸化物トランジスタ 60 は、半導体酸化物チャネル 112 を有することができる。チャネル 112 とゲート 110 との間に誘電体（例えば、パッシベーション層 106 及び 108、並びに／又は高誘電率材料又は他の絶縁材料）を介在させることができる。

【0038】

図 5 の例では、回路 72 のトランジスタ 60 はボトムゲート酸化物トランジスタである。コンデンサ 100 の上部電極 104 と下部電極 102 との間に誘電体層 132 を介在させることができます。誘電体層 132 は、無機絶縁体（例えば、シリコン酸化物、窒化ケイ素など）から形成してもよく、あるいは、ポリマー層から形成してもよい。層 132 は、層間誘電体層と呼ばれることがあります。層間誘電体層 68 及び 70 の上に形成してもよい。コンデンサ 100 において、層 132 は、電極 102 及び 104 を互いに分離する。上部電極 104 は、金属層 SD から形成することができる。金属層 SD はまた、シリコントランジスタ 58 のソース／ドレイン電極 74、76、及び酸化物トランジスタ 60 のソース／ドレイン電極 114、116 を形成するのにも使用することができる。下部電極 102 は、ゲート 66 用のゲート金属 GATE と金属層 SD との間に堆積されパターン化された金属層から形成することができる。図 5 の下部電極 102 を形成するのに使用される金属層は、金属層 M2S と呼ばれることがある。コンデンサ 100 の下部電極 102 を形成するために使用されることに加えて、金属層 M2S を用いて、トランジスタ 60 のゲート 110 を形成することができる。

【0039】

図 5 の構成では、金属層 M2S が誘電体層 68 及び 70 の上に形成されている。誘電体層 132 は、ゲート 110 と半導体酸化物チャネル 120 との間に介在し、トランジスタ 60 のゲート絶縁体として機能する。チャネル 120 の半導体酸化物界面を保護するために、誘電体層 130 などのパッシベーション層をチャネル 120 の上に形成してもよい。誘電体層 130 及び誘電体層 132 は、それぞれ、シリコン酸化物、窒化ケイ素、酸化アルミニウム、酸化ハフニウム、単層、複数の副層、又は他の絶縁材料から形成することができる。

【0040】

図 6 は、トランジスタ回路 74 の別の例示的な構成を示す。図 6 の構成では、回路 74 は 3 つの金属層を有する。金属層 GATE は、コンデンサ 100 の下部電極 102 を形成するのに用いられ、シリコントランジスタ 58 のゲート 66 を形成するのに用いられる。金属層 SD は、ソース／ドレイン端子 74、76、114 及び 116 の形成に使用される。金属層 G2 と呼ばれることがある付加的な金属層が、金属層 SD と金属層 GATE との間に介在する。金属層 G2 は、コンデンサ 100 の上部電極 104 を形成するのに使用してもよく、酸化物トランジスタ 60 内にゲート 110 を形成する際に使用することができる。図 6 の酸化物トランジスタ 60 は、ボトムゲートトランジスタである。誘電体層 70 は、トランジスタ 60 のゲート絶縁体として機能し、ゲート 110 と半導体酸化物チャネル 120 との間に介在する。

10

20

30

40

50

ル 120との間に介在する。パッシベーション層 130は、チャネル領域 120を保護することができる。コンデンサ 100において、誘電体層 68は、上部電極 104と下部電極 102との間に介在する。

【0041】

図 7 に示される回路 72 の例示的な構成では、コンデンサ 100 の上部電極 104 は、金属層 SD から形成される。金属層 SD は、シリコントランジスタ 58 のソース - ドレイン電極 74 及び 76、並びに、酸化物トランジスタ 60 のソース / ドレイン電極 114 及び 116 の形成にもまた、使用することができる。酸化物トランジスタ 60 は、ボトムゲート構成を有し得る。酸化物トランジスタ 60 のゲート 110 及びシリコントランジスタ 58 のゲート 66 は、同じ金属層（即ち、金属層 GATE）の各部分から形成することができる。追加の金属層（金属層 M2S）は、金属層 GATE と金属層 SD との間に形成してもよい。金属層 M2S は、コンデンサ 100 の下部電極 102 を形成するのに使用することができる。下部電極 102 と上部電極 104 との間に誘電体層 132 を介在させてもよい。パッシベーション層 130 は、酸化物トランジスタ 60 内の半導体酸化物層 120 の境界面を保護するために使用することができる。

【0042】

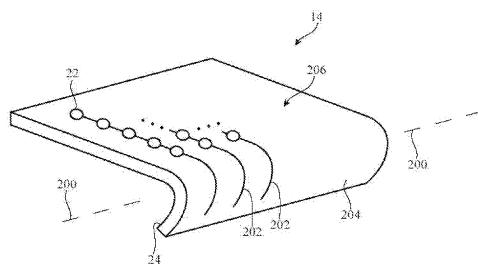

ディスプレイ 14 の非アクティブ境界領域を最小化することが望ましい場合がある。画素 22 は、ユーザに対して画像を表示するので、画素 22 のアレイによって占有されているディスプレイ 14 の部分は、ディスプレイ 14 のアクティブ領域を形成する。アクティブ領域を取り囲むディスプレイ 14 の部分は、ユーザに対して画像を表示しないので、非アクティブである。ユーザに見える非アクティブ領域の量は、基板 24 の一部をアクティブ領域の平面から下方に（例えば、直角又は他の好適な角度で）折り曲げることによって、最小化又は除去することができる。ディスプレイ 14 が折り曲げ中に損傷を受けないようにするために、基板 24 上の構造は、非アクティブ領域の折り曲げられる部分におけるディスプレイ 14 の柔軟性を高めるように構成することができる。例えば、応力に起因するひび割れ又は折り曲げ中の他の損傷（特に金属信号線に対する）を防止するために、非アクティブ領域内で無機誘電体層及びディスプレイ 14 の他の層（例えば、金属層のいくつか）などの絶縁層を部分的又は完全に除去することができる。

【0043】

一例として、図 8 のディスプレイ 14 を考える。図 8 に示すように、非アクティブ縁部領域 204 は、アクティブ領域 206 から曲げ軸 200 の周りに下方に折り曲げられている。線 202（例えば、データ線又はディスプレイ 14 内の他の金属信号トレース）は、軸 200 における曲がり部を横断する。ディスプレイ 14 の構造に対する亀裂の形成及びその他の損傷を防止するために、線 202 以外のディスプレイ 14 の構造の一部又は全部は、非アクティブ領域 204 内で選択的に除去してもよい（一方、図 3、図 4、図 5、図 6 及び図 7 の回路 72 などの薄膜トランジスタ回路 72 を形成するため、アクティブ領域 206 で保持される）。この手法によって、線 202 を形成する金属層は、アクティブ領域 206 内では、非アクティブ領域 204 内よりも、基板 24 の上により遠く離して配置してもよい。

【0044】

アクティブ領域 206 と非アクティブ領域 204 との間の高さの不一致に対応するために、ディスプレイ 14 の複数の誘電体層に一連の段差を設けることができる。この段差によって、複数の誘電体層上に支持された金属トレースの高さは徐々に低下することができ、金属トレースは高さを徐々に変えることができるので、誘電体の高さの急激な不連続による切断は起こらない。

【0045】

金属線 202 がアクティブ領域 206 と非アクティブ領域 204 との間で首尾よく移行できるように階段状のプロファイルを有する例示的な一式の誘電体層が図 9 に示されている。図 9 に示すように、ディスプレイ 14 は、層 L1、L2、及び L3（例えば、図 3、図 4、図 5、及び図 6 の回路 72 の複数の誘電体層を参照）などの複数の誘電体層を有す

10

20

30

40

50

ることができる。層 L 1、L 2、及び L 3 は、ポリマーの副層及び／又は無機層（例えば、シリコン酸化物、窒化ケイ素、酸化ハフニウム、酸化アルミニウムなど）のうちの 1 つ以上から形成してもよい。図 9 の例では、3 つの誘電体層 L 1、L 2、及び L 3 が存在するが、これは単なる例示である。アクティブ領域 206 の図 9 の左側には、全ての誘電体層 L 1、L 2、及び L 3 が存在するので、金属線 202 は基板 24 から最大距離だけ離れて配置される。アクティブ領域 206 から連続的に大きな横方向距離で層 L 3、L 2、及び L 1 を選択的に除去することによって、階段状（段差のある）の誘電体プロファイルが生成される。複数の誘電体層に形成された高さの段差により、金属線 202 は、非アクティブ領域 204 において、その最大高さ（アクティブ領域 206 内の）から最小高さまで滑らかに遷移することが可能になる。線 202 は、例えば、非アクティブ領域 204 内の基板 24 の表面上又はその近傍に置くことができる。10

#### 【 0 0 4 6 】

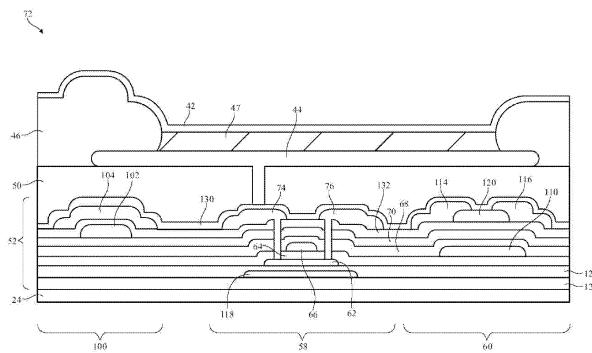

図 10 は、ディスプレイの非アクティブ縁部に沿った折り曲げ領域におけるディスプレイの折り曲げを容易にするために、材料の上部層がディスプレイから除去された構成のディスプレイ 14 用の例示的な薄膜トランジスタ回路 72 の断面側面図である。図 10 の例では、パッシベーション層 106 及び 108 を除く全ての誘電体層が領域 204 の基板 24 から除去されているので、金属線 202（例えば、データ線及び／又はディスプレイ 14 の他の信号線）は基板 24 の表面上に載置される。これによって、領域 204 における基板 24 の折り曲げが容易になる。一般に、任意の好適な薄膜トランジスタ回路 72 は、図 10 の非アクティブ領域材料除去方式（例えば、図 3、図 4、図 5、図 6、図 7、及び図 8 の回路 72 などの回路）と共に、使用することができる。図 10 の回路は、単なる例示に過ぎない。20

#### 【 0 0 4 7 】

図 10 の例示的な構成では、上部コンデンサ電極 104 は、金属層 M3 から形成されている。金属層 M3 はまた、ビア 74 を形成してソース／ドレイン端子 74 をアノード 44 に結合するのに使用することもできる。下部コンデンサ電極 102 は、金属層 SD から形成することができる。金属層 SD はまた、ソース／ドレイン端子 74、76、114、及び 116 を形成するために使用してもよい。パッシベーション層 106 及び 108（例えば、それぞれ窒化ケイ素層及びシリコン酸化物層）又は他の好適な誘電体層（単数又は複数）を、半導体酸化物チャネル 112 の上に形成することができる。コンデンサ 100 では、誘電体の厚さを減少させ、それによってコンデンサ 100 の容量値を高めるために、層 106 及び 108 の 1 つを局所的に除去することができる。例えば、図 10 に示すように、層 106 は電極 104 の下で除去され、その結果、層 106 はコンデンサ 100 と重ならず、誘電体層 108 のみがコンデンサ 100 の上部電極 104 と下部電極 102 との間に介在することになる。誘電体層 108 は、シリコン酸化物の誘電率よりも大きい誘電率を有する窒化ケイ素から形成することができるので、電極 102 と 104 との間の専用絶縁層として誘電体層 108 を使用すれば、コンデンサ 100 の容量向上に役立つことができる。追加のフォトリソグラフィマスクを用いて、シリコン酸化物層 106 を選択的に除去することができる。このマスクは、金属線 202 の誘電体段差（例えば、図 9 の誘電体段差を参照）を形成するのにも使用することができる。金属線 202 は、金属層 SD から形成することができる。ディスプレイ 14 のアクティブ領域 206 において、金属線 202 は、層 122、120、64、68、及び 70 などの複数の誘電体層（即ち、図 9 の例示的な層 L 1、L 2、及び L 3 を形成し得る種類の層）によって支持される金属層 SD の部分から形成してもよい。図 9 の例では 3 つの高さの段があるが、1 段、2 段、3 段、又は 3 段を超える段を形成してもよい。30

#### 【 0 0 4 8 】

図 11 の例示的な構成は、図 10 と同様であるが、局所的に除去された窒化ケイ素パッシベーション層を有する酸化物トランジスタを有する。図 10 のパッシベーション層 106 は、窒化ケイ素層としてよい。窒化ケイ素層 106 は、シリコントランジスタ 58 のポリシリコン層 62 内のダングリングボンドを不活性化するために、高濃度の水素を有す40

ることができる。効果的な不活性化のために、窒化ケイ素層106は、トランジスタ58及びシリコンチャネル62と重なることができる。窒化ケイ素層106からの水素が半導体酸化物チャネル112に達するのを防止することができる。窒化ケイ素層106からの水素が半導体酸化物チャネル112に達するのを防止することができる。これは、トランジスタ60から窒化物層106を除去することによって達成することができる。例えば、窒化ケイ素層106が半導体酸化物112の下に存在しないように（即ち、トランジスタ60と重なる窒化物層106の部分が存在しないように）フォトリソグラフィマスクを用いて窒化ケイ素層106をパターン化することができる。窒化ケイ素がゲート110と酸化物112との間に存在しないようにすることによって、トランジスタ60の性能は、層106からの水素のせいで劣化することはない。

【0049】

10

一実施形態によれば、基板と、基板のアクティブ領域を形成する画素回路のアレイと、基板の非アクティブ領域内の回路と、を備える有機発光ダイオードディスプレイが提示され、各画素回路は、有機発光ダイオードと、この有機発光ダイオードと直列に結合されたシリコントランジスタと、このシリコントランジスタに結合された蓄積コンデンサと、この蓄積コンデンサに結合された半導体酸化物トランジスタと、を含んでいる。

【0050】

別の実施形態によれば、基板は非アクティブ領域内で折り曲げられる。

【0051】

20

別の実施形態によれば、有機発光ダイオードディスプレイは複数の誘電体層を含み、この複数の誘電体層はアクティブ領域に存在し、誘電体層のうちの少なくとも一部は非アクティブ領域には存在しない。

【0052】

別の実施形態によれば、各画素回路内のシリコントランジスタはシリコンチャネルを含み、複数の誘電体層は基板とシリコンチャネルとの間にバッファ層を含み、このバッファ層は非アクティブ領域には存在しない。

【0053】

別の実施形態によれば、有機発光ダイオードディスプレイは、アクティブ領域内に第1金属層を備え、第1金属層のいくつかは、各画素回路内のシリコントランジスタのゲートを形成する。

【0054】

30

別の実施形態によれば、第1金属層の一部は、各画素回路内の半導体酸化物トランジスタのゲートを形成する。

【0055】

別の実施形態によれば、有機発光ダイオードディスプレイは第2金属層を備え、この第2金属層はアクティブ領域内でパターン化されて、シリコントランジスタ及び半導体酸化物トランジスタのソース／ドレイン端子を形成する。

【0056】

別の実施形態によれば、第2金属層は、非アクティブ領域内でパターン化され、画素回路のアレイと非アクティブ領域内の回路との間で結合されるデータ線を形成する。

【0057】

40

別の実施形態によれば、基板は折れ曲がった可撓性基板であり、データ線は折れ曲がって、基板の表面上に形成され、複数の誘電体層のいずれもデータ線と基板との間に介在しない。

【0058】

別の実施形態によれば、各画素における半導体酸化物トランジスタは、半導体酸化物チャネルを含んでいる。

【0059】

別の実施形態によれば、複数の誘電体層は、各画素回路内のシリコントランジスタのシリコンチャネルと重なり、かつ、各画素回路内の半導体酸化物トランジスタの半導体酸化物チャネルと重ならない、窒化ケイ素層を含むものである。

50

**【 0 0 6 0 】**

別の実施形態によれば、蓄積コンデンサは、第2金属層から形成された第1電極を有し、かつ、第2電極を有している。

**【 0 0 6 1 】**

別の実施形態によれば、複数の誘電体層は追加の窒化ケイ素層を含み、この追加の窒化ケイ素層は各画素回路内の蓄積コンデンサの第1電極と第2電極との間に介在する。

**【 0 0 6 2 】**

別の実施形態によれば、有機発光ダイオードディスプレイは、シリコン酸化物層を更に含み、このシリコン酸化物層は、各画素回路の半導体酸化物チャネルと重なり、局的に各画素回路の蓄積コンデンサ内で除去される結果、このシリコン酸化物層は、蓄積コンデンサの第1と第2電極との間には介在しないことになる。

10

**【 0 0 6 3 】**

別の実施形態によれば、有機発光ダイオードディスプレイは、アクティブ領域から非アクティブ領域まで延在するデータ線を備え、当該複数の誘電体層は、アクティブ領域から非アクティブ領域に移行するときに高さが減少する階段状プロファイルを有し、データ線は、階段状のプロファイルを有する複数の誘電体層上に形成される。

**【 0 0 6 4 】**

別の実施形態によれば、各画素回路の半導体酸化物トランジスタは駆動トランジスタを含み、各画素回路のシリコントランジスタはスイッチングトランジスタを含むものである。

20

**【 0 0 6 5 】**

一実施形態によれば、有機発光ダイオードディスプレイが提示され、この有機発光ダイオードディスプレイは、有機発光ダイオードのアレイと、それぞれが有機発光ダイオードのうちの対応する1つに直列に結合されたシリコン駆動トランジスタと、このシリコントランジスタに結合された半導体酸化物スイッチングトランジスタと、を備えている。

**【 0 0 6 6 】**

別の実施形態によれば、半導体酸化物スイッチングトランジスタは、それぞれ半導体酸化物チャネルを有し、有機発光ダイオードディスプレイは、シリコン駆動トランジスタと重なり、かつ、半導体酸化物チャネルとは重ならない、窒化ケイ素層を備えている。

**【 0 0 6 7 】**

30

別の実施形態によれば、有機発光ダイオードディスプレイは、半導体酸化物スイッチングトランジスタに結合された蓄積コンデンサと、半導体酸化物チャネルと重なり、かつ、蓄積コンデンサとは重ならない、シリコン酸化物層と、を備えている。

**【 0 0 6 8 】**

一実施形態によれば、有機発光ダイオードディスプレイが提示され、この有機発光ダイオードディスプレイは、可撓性ポリマー基板と、基板上の画素回路のアレイであって、各画素回路は、有機発光ダイオードと、半導体酸化物チャネルをそれぞれ有する少なくとも2つの半導体酸化物トランジスタと、有機発光ダイオードと直列に結合された少なくとも1つのシリコントランジスタと、少なくとも1つの蓄積コンデンサと、を含む、画素回路のアレイと、画素回路のアレイから画素回路のアレイに隣接する非アクティブ領域に移行するときに高さが減少する階段状プロファイルを有する、可撓性ポリマー基板上の複数の誘電体層と、階段状プロファイルに従う複数の誘電体層上のデータ線と、を備え、この複数の誘電体層は、シリコントランジスタと重なり、かつ、半導体酸化物チャネルとは重ならない、誘電体層を含んでいる。

40

**【 0 0 6 9 】**

上述の内容は単なる例示に過ぎず、説明された実施形態の範囲及び趣旨から逸脱することなく、当業者によってさまざまな修正を行うことができる。前述の実施形態は、個々に又は任意の組み合わせで実装することができる。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図5】

FIG. 5

【図4】

FIG. 4

【図6】

FIG. 6

【図7】

FIG. 7

【 四 8 】

FIG. 8

### 【図 1 1】

FIG. II

【図9】

FIG. 9

【図10】

FIG. 10

## フロントページの続き

| (51)Int.Cl.    |               | F I              |                |                |

|----------------|---------------|------------------|----------------|----------------|

| <b>G 0 9 F</b> | <b>9/30</b>   | <b>(2006.01)</b> | <b>G 0 9 F</b> | <b>9/30</b>    |

| <b>H 0 1 L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>G 0 9 F</b> | <b>9/30</b>    |

| <b>H 0 1 L</b> | <b>21/336</b> | <b>(2006.01)</b> | <b>G 0 9 F</b> | <b>9/30</b>    |

|                |               |                  | <b>H 0 1 L</b> | <b>29/78</b>   |

|                |               |                  | <b>H 0 1 L</b> | <b>29/78</b>   |

|                |               |                  |                | <b>3 6 5</b>   |

|                |               |                  |                | <b>3 3 8</b>   |

|                |               |                  |                | <b>3 0 8 Z</b> |

|                |               |                  |                | <b>6 1 8 B</b> |

|                |               |                  |                | <b>6 1 2 Z</b> |

(74)代理人 100116894

弁理士 木村 秀二

(74)代理人 100130409

弁理士 下山 治

(74)代理人 100134175

弁理士 永川 行光

(72)発明者 ツアイ, ツイン-ティン

台湾 タイペイシティ, シンイ ディストリクト, ナンバー 1 ソンジ ロード, 19エー

ー, メイルストップ 706-アールイー

(72)発明者 グプタ, ヴァスード

アメリカ合衆国 カリフォルニア州 95014, クパチーノ, インフィニット ループ 1

, エム/エス 83-オー

(72)発明者 リン, チン-ウェイ

アメリカ合衆国 カリフォルニア州 95014, クパチーノ, インフィニット ループ 1

, エム/エス 83-オー

審査官 中山 佳美

(56)参考文献 特開2011-141529(JP, A)

特開2011-209405(JP, A)

米国特許出願公開第2014/0232956(US, A1)

特開2014-106539(JP, A)

特開2012-093707(JP, A)

国際公開第2011/125353(WO, A1)

国際公開第2012/046658(WO, A1)

特開2012-186083(JP, A)

特開2013-051423(JP, A)

特開2010-056356(JP, A)

特開2000-284722(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 5 1 / 5 0 - 5 1 / 5 6

H 0 1 L 2 7 / 3 2

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

|                |                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 硅和半导体氧化物薄膜晶体管显示器                                                                                                                                                  |         |            |

| 公开(公告)号        | JP6683690B2                                                                                                                                                       | 公开(公告)日 | 2020-04-22 |

| 申请号            | JP2017514408                                                                                                                                                      | 申请日     | 2014-10-09 |

| [标]申请(专利权)人(译) | 苹果公司                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 苹果公司                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 苹果公司                                                                                                                                                              |         |            |

| [标]发明人         | ツアイツインテイン<br>グプタヴァスース<br>リンチンウェイ                                                                                                                                  |         |            |

| 发明人            | ツアイ, ツイン-テイン<br>グプタ, ヴァスース<br>リン, チン-ウェイ                                                                                                                          |         |            |

| IPC分类号         | H05B33/02 H01L51/50 H05B33/12 H05B33/22 H01L27/32 G09F9/30 H01L29/786 H01L21/336                                                                                  |         |            |

| CPC分类号         | H01L27/1225 H01L27/1251 H01L27/1255 H01L27/3258 H01L27/3262 H01L27/3265 H01L27/3276<br>H01L51/0097 H01L2251/5338 Y02E10/549 H01L29/78651 H01L29/78672 H01L29/7869 |         |            |

| FI分类号          | H05B33/02 H05B33/14.A H05B33/12.B H05B33/22.Z H01L27/32 G09F9/30.365 G09F9/30.338 G09F9<br>/30.308.Z H01L29/78.618.B H01L29/78.612.Z                              |         |            |

| 代理人(译)         | 大冢康弘<br>下山治<br>永川行光                                                                                                                                               |         |            |

| 审查员(译)         | 中山佳美                                                                                                                                                              |         |            |

| 优先权            | 14/494931 2014-09-24 US                                                                                                                                           |         |            |

| 其他公开文献         | JP2017536646A                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                         |         |            |

## 摘要(译)

电子设备显示器可以具有像素电路的阵列。每个像素电路可以包括有机发光二极管和驱动晶体管。可以调节每个驱动晶体管以控制多少电流流过有机发光二极管。每个像素电路可以包括一个或多个附加晶体管，例如开关晶体管和存储电容器。半导体氧化物晶体管和硅晶体管可用于形成像素电路的晶体管。可以使用金属层，半导体结构和电介质层来形成存储电容器和晶体管。可以沿着显示器的边缘去除一些层以促进弯曲。介电层可以具有阶梯状的轮廓，当数据线延伸到无效边缘区域中时，该阶梯状的轮廓允许阵列中的数据线朝着基板的表面向下倾斜。

| (19)日本国特許庁(JP)                         | (12)特許公報(B2)                          | (11)特許番号<br>特許第6683690号<br>(P6683690) |

|----------------------------------------|---------------------------------------|---------------------------------------|

| (45)発行日 令和2年4月22日(2020.4.22)           |                                       | (24)登録日 令和2年3月30日(2020.3.30)          |

| (51)Int.Cl.                            | F I                                   |                                       |

| <b>H05B 33/02</b> (2006.01)            | H05B 33/02                            |                                       |

| <b>H01L 51/50</b> (2006.01)            | H05B 33/14                            | A                                     |

| <b>H05B 33/12</b> (2006.01)            | H05B 33/12                            | B                                     |

| <b>H05B 33/22</b> (2006.01)            | H05B 33/22                            | Z                                     |

| <b>HO1L 27/32</b> (2006.01)            | HO1L 27/32                            |                                       |

|                                        |                                       |                                       |

| (21)出願番号 特願2017-514408 (P2017-514408)  | (73)特許権者 50326918                     | 請求項の数 15 (全 16 頁) 最終頁に続く              |

| (60) (22)出願日 平成26年10月9日 (2014.10.9)    | アップル インコーポレイテッド                       |                                       |

| (65)公表番号 特表2017-536646 (P2017-536646A) | Apple Inc.                            |                                       |

| (43)公表日 平成29年12月7日 (2017.12.7)         | アメリカ合衆国 95014 カリフォル                   |                                       |

| (69)国際出願番号 PCT/US2014/059396           | ニア州 クバチーノ アップル パーク                    |                                       |

| (87)国際公開日 平成28年3月31日 (2016.3.31)       | ウェイ ウン                                |                                       |

| (審査請求日 平成29年4月11日 (2017.4.11))         | One Apple Park Way,                   |                                       |

| (31)優先権番号 14/494,931                   | Cupertino, California 95014, U. S. A. |                                       |

| (32)優先日 平成26年9月24日 (2014.9.24)         | (74)代理人 100076428                     |                                       |

| (33)優先権主張国・地域又は機関 米国(US)               | 弁理士 大塚 康徳                             |                                       |

|                                        | (74)代理人 100115071                     |                                       |

|                                        | 弁理士 大塚 康徳                             |                                       |

|                                        | (74)代理人 100112508                     |                                       |

|                                        | 弁理士 高柳 司郎                             |                                       |

|                                        |                                       | 最終頁に続く                                |

(54)【発明の名称】シリコン及び半導体酸化物の薄膜トランジスタディスプレイ