(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-169090

(P2009-169090A)

(43) 公開日 平成21年7月30日(2009.7.30)

| (51) Int.Cl.                | F 1                  | テーマコード (参考) |

|-----------------------------|----------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K107    |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B 5C080 |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 622G       |             |

|                             | G09G 3/20 611H       |             |

|                             | HO5B 33/14 A         |             |

審査請求 未請求 請求項の数 5 O L (全 31 頁)

|           |                          |          |                                        |

|-----------|--------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2008-6956 (P2008-6956) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成20年1月16日 (2008.1.16)   | (74) 代理人 | 100094053<br>弁理士 佐藤 隆久                 |

|           |                          | (72) 発明者 | 飯田 幸人<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|           |                          | (72) 発明者 | 三並 徹雄<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|           |                          | (72) 発明者 | 谷龜 貴央<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】自発光型表示装置およびその駆動方法

## (57) 【要約】

【課題】補助キャパシタ  $C_{sub}$  が前段の電源走査線  $D S_L$  ( $i - 1$ ) に接続されている場合、その前段の電位変化により画質が低下すること防止する。

【解決手段】画素回路3( $i, j$ )が、一方電極(ソースノード  $N D_s$ )の電位( $V_s$ )によって印加電圧値が変化する発光素子(有機発光ダイオード  $O L E D$ : 容量  $C_{oled}$ )と、制御ノード  $N D_c$ (電位  $V_g$ )を有する駆動トランジスタ  $M_d$ と、サンプリングトランジスタ  $M_s$ と、保持キャパシタ  $C_s$ と、補助キャパシタ  $C_{sub}$ とを含む。駆動回路は、 $C_{sub}$ 、 $C_{oled}$ 、 $V_g$ の範囲、D前記電源走査線の高電位  $V_{cc\_H}$ と低電位  $V_{cc\_L}$ 、および、電源走査線  $D S_L$  ( $i - 1$ ) の電位( $V_{cc\_H}$ ,  $V_{cc\_L}$ )に応じて、 $V_w$  ( $V_{cc\_L} < V_g - (V_{cc\_H} - V_{cc\_L}) C_{sub} / (C_{sub} + C_{oled})$ ) を満たす低電位  $V_w$  ( $V_{cc\_L}$ ) を出力可能に構成されている。

【選択図】図13

## 【特許請求の範囲】

## 【請求項 1】

複数の画素回路が行列状に配置される画素アレイと、

前記画素アレイ内の画素回路を行方向で接続する、複数の書き込み走査線および複数の電源走査線と、

前記画素アレイ内の画素回路を列方向で接続する複数の映像信号線と、

前記複数の書き込み走査線および前記複数の電源走査線の各電位を制御する駆動回路と、を有し、

前記複数の画素回路の各々が、

一方電極の電位によって印加電圧値が変化する発光素子と、

前記電源走査線と前記一方電極との間に接続される駆動トランジスタと、

前記映像信号線と前記駆動トランジスタの制御ノードとの間に接続され、前記書き込み走査線の電位に応じて制御されるサンプリングトランジスタと、

前記制御ノードに結合する保持キャパシタと、

前記一方電極と、列方向の一方側に位置する他の画素回路の電源走査線との間に接続される補助キャパシタと、

を含み、

前記駆動回路は、前記補助キャパシタの値  $C_{sub}$ 、前記発光素子の等価容量  $C_{oled.}$ 、前記電源走査線の高電位  $V_{c c\_H}$  と低電位  $V_{c c\_L}$ 、および、前記映像信号線の電位に対応して前記駆動トランジスタのゲート電位  $V_g$  がとりうる範囲に応じて、以下の式、すなわち、

$$V_{ws\_L} < V_g - (V_{c c\_H} - V_{c c\_L}) C_{sub} / (C_{sub} + C_{oled.})$$

を満たす低電位  $V_{ws\_L}$  を、2 値電位の低い方の電位として前記書き込み走査線に出力するように構成されている

自発光型表示装置。

## 【請求項 2】

前記駆動回路は、複数の画素行の各々に 1 本ずつ対応する前記書き込み走査線と前記電源走査線の組を、列方向で順次選択し、

前記補助キャパシタは、当該補助キャパシタを有する画素回路が属する画素行より、前記駆動回路によって先に選択される他の画素行内で画素回路を接続する電源走査線に接続されている

請求項 1 に記載の自発光型表示装置。

## 【請求項 3】

前記書き込み走査線の前記低電位  $V_{ws\_L}$  は、前記式を満たす値の負電位である

請求項 1 に記載の自発光型表示装置。

## 【請求項 4】

データ基準電位  $V_o$  との電位差が画素の表示輝度に対応して変化するデータ電位をもつデータパルスが所定周期で繰り返す映像信号が前記映像信号線内を伝送され、前記式の右辺が、前記ゲート電位  $V_g$  が前記データ基準電位  $V_o$  のときに最小値をとり、前記駆動回路は、前記最小値より低い値に前記低電位  $V_{ws\_L}$  を制御する

請求項 1 に記載の自発光型表示装置。

## 【請求項 5】

画素アレイ内で行列状に配置される複数の画素回路の各々が、一方電極の電位によって印加電圧値が変化する発光素子と、電源走査線と前記発光素子の一方電極との間に接続される駆動トランジスタと、前記駆動トランジスタの制御ノードと映像信号線との間に接続され、前記書き込み走査線の電位に応じて制御されるサンプリングトランジスタと、前記制御ノードに結合する保持キャパシタと、前記一方電極と、列方向の一方側に位置する他の画素回路の電源走査線との間に接続される補助キャパシタと、を含む自発光型表示装置の駆動方法であって、

前記補助キャパシタの値  $C_{sub}$ 、前記発光素子の等価容量  $C_{oled.}$ 、前記電源走査線の高

10

20

30

40

50

電位  $V_{c c\_H}$  と低電位  $V_{c c\_L}$ 、および、前記映像信号線の電位に対応して前記駆動トランジスタのゲート電位  $V_g$  がとりうる範囲に応じて、以下の式、すなわち、

$$V_{ws\_L} < V_g - (V_{c c\_H} - V_{c c\_L}) C_{sub} / (C_{sub} + C_{oled.})$$

を満たす低電位  $V_{ws\_L}$  が、低い方の電位として定められた前記書込走査線の 2 値電位によって前記サンプリングトランジスタを駆動する

自発光型表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の画素回路と駆動回路を有し、映像信号線と電源走査線と書込走査線が複数の画素回路に対し配線され、各画素回路が、一方電極の電位に応じて印加電圧値が変化する発光素子、駆動トランジスタ、サンプリングトランジスタ、保持キャパシタおよび補助キャパシタを含む自発光型表示装置と、その駆動方法に関する。特定的に本発明は、上記補助キャパシタが、補助キャパシタと同じ画素回路内の上記一方電極と、他の画素行の電源走査線との間に接続されている自発光型表示装置と、その駆動方法に関する。

10

【背景技術】

【0002】

発光素子として有機ELデバイスを用いた自発光型表示装置の開発が近年盛んになっている。有機ELデバイスは有機薄膜を有し、有機薄膜に電界をかけると発光する現象を利用したデバイスである。

20

有機ELデバイスは印加電圧が10[V]以下で駆動するため低消費電力である。有機ELデバイスは自ら光を発する自発光素子であるため、これを有する表示装置は、照明部を必要とせず軽量化及び薄型化が容易である。有機ELデバイスの応答速度は数[μs]程度と非常に高速なので、有機ELデバイスを用いた表示装置は動画表示時の残像が発生しない。

【0003】

有機ELデバイスを自発光素子として用いる自発光型表示装置の中でも、とりわけ駆動素子として薄膜トランジスタを各画素に集積形成したアクティブマトリクス型の表示装置の開発が盛んである。

30

【0004】

自発光素子を有するアクティブマトリクス型の表示装置であって、データ電位に応じた駆動電流が流入する側の自発光素子の一方電極（アノード電極）に対し、補助キャパシタ（追加容量）を接続させた表示装置が知られている（例えば特許文献1参照）。

【0005】

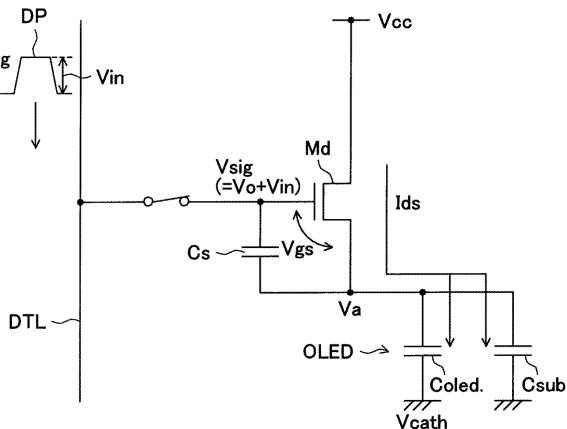

図14に、画素回路の基本構成の等価回路図（特許文献1の図8）を、参照符号を一部変更して転記する。

発光素子は、本例では有機発光ダイオードOLEDであり、図14では、有機発光ダイオードOLEDを、その等価容量  $C_{oled.}$  により示している。また、特許文献1の図8に示す、電源電圧  $V_{dd}$  の供給線と駆動トランジスタの間に接続され（符号Tr4により示す）トランジスタは、画素回路の構成によっては不要であるため、ここでの図示を省略している。

40

【0006】

有機発光ダイオードOLEDの他方電極（カソード）の電位がカソード電位  $V_{cath}$  で固定されているため、一方電極（アノード）の電位（アノード電位）  $V_a$  によって有機発光ダイオードOLEDに印加される電圧が制御される。有機発光ダイオードOLEDのアノードに対し、駆動トランジスタMdを介して電源電圧  $V_{dd}$  の供給線が接続可能となっている。駆動トランジスタMdは、そのゲート（制御ノード）に入力されるデータ電位  $V_{sig}$  に応じてドレイン電流  $I_{ds}$  の大きさが制御され、これによりソース電位、即ち有機発光ダイオードOLEDのアノード電位  $V_a$  が決まる。

【0007】

50

駆動トランジスタM d のゲートとソース間に、データ電位Vsigを保持する目的で保持キャパシタCsが接続されている。駆動トランジスタM d のゲートと映像信号線D T Lの間に、映像信号のデータ電位VsigをサンプリングするサンプリングトランジスタMsが接続されている。

サンプリングトランジスタは、そのゲートに接続される書込走査線（不図示）の電位に応じて制御され、書込走査線が活性化されたときにオンして、ドレインに接続されている映像信号線の電位をサンプリングし、サンプリング後の電位を、ソースに接続されている駆動トランジスタの制御ノードに伝達する。

ここで映像信号は一定の基準電位（以下、データ基準電位V0という）の印加と、データ基準電位V0から任意の電位を持つデータパルスDPの印加とが繰り返された波形を有する。データパルスDPの電位がデータ電位Vsigであり、表示階調を決めるデータ電圧Vinは、データ電位Vsigからデータ基準電位V0を差し引いた上記データパルスDPの波高値に該当する。

駆動トランジスタM d のゲートとソース間に保持キャパシタCsが接続されている。

#### 【0008】

このような構成の画素回路では、駆動トランジスタM d のゲートソース間電圧Vgsが、そのまま保持キャパシタCsの保持電圧となる。言い換えると、駆動トランジスタのソース電位（有機発光ダイオードOLEDのアノード電位Va）を基準として、駆動トランジスタのゲートに与えられる電位“Vsig - Va”的大きさで、保持キャパシタCsの保持電圧値が決められる。

駆動トランジスタM d は、そのゲートソース間電圧Vgsに応じたドレイン電流Idsを流すことから、データ電圧Vin（データパルスDPの波高値）を保持キャパシタCsに正確に入力し、保持させる必要がある。

#### 【0009】

そのためには、データ電圧Vinの入力に先立って、駆動トランジスタM d のソース（発光素子の一方電極、本例ではアノード）の電位（アノード電位Va）を、映像信号のデータ基準電位V0により初期化する。そして、サンプリングトランジスタMsによるデータ電位Vsigのサンプリングによって、駆動トランジスタM d の制御ノードにデータ電位Vsigを入力する。

#### 【0010】

データ電位Vsigの入力によって駆動トランジスタM d の制御ノード（ゲート）の電位が上昇すると、駆動トランジスタM d のソース電位（アノード電位Va）もデータ基準電位V0から上昇する。データ電圧Vinを保持キャパシタCsに100[%]保持させるには、データ電位Vsigを入力する時の駆動トランジスタM d のソース電位（アノード電位Va）の変動量をほぼゼロとする必要がある。

しかしながら、データ電位Vsigの入力によって駆動トランジスタM d が流す電流値が増大し、この電流値の増大によって、駆動トランジスタM d のソース電位（アノード電位Va）が容易に上昇しようとする。

#### 【0011】

そこで、特許文献1に記載されている画素回路では、駆動トランジスタのソースに接続されている容量値を大きくする目的で、有機発光ダイオードOLEDと並列に補助キャパシタCsubが接続されている。

ドレイン電流Idsは、有機発光ダイオードOLEDの容量Coled.と、補助キャパシタCsubと、駆動トランジスタM d 等の寄生容量との合成容量を充電する。ドレイン電流Idsがデータ電位Vsigの入力によって増加し、このとき補助キャパシタCsubがある程度大きいと、ドレイン電流Idsの増加分は上記合成容量を充電するのに費やされ、アノード電位Vaが殆ど上昇しないようにすることできる。この場合、実際に保持キャパシタCsに保持される電圧と、所望のデータ電圧Vinとの比率で定義される“書き込みゲイン”が“1”に近いものとなる。

#### 【0012】

10

20

30

40

50

このように、補助キャパシタ  $C_{sub}$  はデータ電圧  $V_{in}$  を画素回路に書き込む際に、データ書き込みの効率（書き込みゲイン）を上げる作用効果がある。

【特許文献 1】特開 2007-102046 号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

補助キャパシタ  $C_{sub}$  は、一方電極との電位差が大きい電位線に接続すると、より付加容量値を大きくできる。

【0014】

そのような意図で、本発明者は、上記特許文献 1 に記載の補助キャパシタ  $C_{sub}$  を、当該補助キャパシタ  $C_{sub}$  と同じ画素内の一定電位線（カソード電位  $V_{cath}$  の供給線）ではなく、隣接する他の画素回路が有する電源電圧の供給制御線（電源走査線  $D_{SL}$ ）に接続させた画素回路構成を提案している（特願 2006-209327 号）。

10

【0015】

しかしながら、隣接する他の画素回路が有する電源走査線  $D_{SL}$  は、低電位  $V_{ccl}$  から高電位  $V_{chl}$  に制御され、このとき、電源走査線  $D_{SL}$  に接続している補助キャパシタ  $C_{sub}$  が設けられている画素回路が発光可能状態にある場合がある。

そのような場合、隣の画素回路が接続された電源走査線  $D_{SL}$  の電位変動が、サンプリングトランジスタがオフされ発光可能状態にある画素回路内の補助キャパシタ  $C_{sub}$ 、保持キャパシタ  $C_s$  を介して駆動トランジスタ  $M_d$  のゲートの電位を低下させる。この低下の程度が大きいと、発光可能状態ではオフされているはずのサンプリングトランジスタ  $M_s$  が瞬間的にオンし、そのときの映像信号線  $D_{TL}$  の電位を短い時間だけサンプリングし、表示画像の画質が著しく低下する。

20

【0016】

サンプリングトランジスタ  $M_s$  がオンしない場合でも、リーク電流が流れると発光輝度レベルが変化する。この発光輝度レベルの変化はリーク電流に起因しているため目立たない画素もあるが、とりわけ黒表示時にリーク電流が発生すると白っぽい表示となる、いわゆる「黒浮き」が生じコントラストが低下するため画質の低下が目立ってしまう。

【0017】

本発明は、補助キャパシタを他の画素行の画素回路の電源走査線に接続させる構成の自発光型表示装置において、電源走査線の電位変化により画質が低下することを防止するものである。

30

【課題を解決するための手段】

【0018】

本発明の一形態（第 1 形態）に関わる自発光型表示装置は、複数の画素回路が行列状に配置される画素アレイと、前記画素アレイ内の画素回路を行方向で接続する、複数の書き走査線および複数の電源走査線と、前記画素アレイ内の画素回路を列方向で接続する複数の映像信号線と、前記複数の書き走査線および前記複数の電源走査線の各電位を制御する駆動回路と、を有する。

40

前記複数の画素回路の各々が、一方電極の電位によって印加電圧値が変化する発光素子と、前記電源走査線と前記一方電極との間に接続される駆動トランジスタと、前記映像信号線と前記駆動トランジスタの制御ノードとの間に接続され、前記書き走査線の電位に応じて制御されるサンプリングトランジスタと、前記制御ノードに結合する保持キャパシタと、前記一方電極と、列方向の一方側に位置する他の画素回路の電源走査線との間に接続される補助キャパシタと、を含む。

前記駆動回路は、前記補助キャパシタの値  $C_{sub}$ 、前記発光素子の等価容量  $C_{oled.}$ 、前記電源走査線の高電位  $V_{chl}$  と低電位  $V_{ccl}$ 、および、前記映像信号線の電位に対応して前記駆動トランジスタのゲート電位  $V_g$  がとりうる範囲に応じて、以下の式、すなわち、

$$V_{wsL} < V_g - (V_{chl} - V_{ccl}) C_{sub} / (C_{sub} + C_{oled.})$$

50

を満たす低電位  $V_{ws\_L}$  を、2値電位の低い方の電位として前記書込走査線に出力するように構成されている。

【0019】

本発明の他の形態(第2形態)に関わる自発光型表示装置は、上記第1形態において、前記駆動回路は、複数の画素行の各々に1本ずつ対応する前記書込走査線と前記電源走査線の組を、列方向で順次選択し、前記補助キャパシタは、当該補助キャパシタを有する画素回路が属する画素行より、前記駆動回路によって先に選択される他の画素行内で画素回路を接続する電源走査線に接続されている。

【0020】

本発明の他の形態(第3形態)に関わる自発光型表示装置は、上記第1形態において、前記書込走査線の前記低電位  $V_{ws\_L}$  は、前記式を満たす値の負電位である。 10

【0021】

本発明の他の形態(第4形態)に関わる自発光型表示装置は、上記第1形態において、データ基準電位  $V_o$  との電位差が画素の表示輝度に対応して変化するデータ電位をもつデータパルスが所定周期で繰り返す映像信号が前記映像信号線内を伝送され、前記式の右辺が、前記ゲート電位  $V_g$  が前記データ基準電位  $V_o$  のときに最小値をとり、前記駆動回路は、前記最小値より低い値に前記低電位  $V_{ws\_L}$  を制御する。

【0022】

本発明の他の形態(第5形態)に関わる自発光型表示装置の駆動方法は、画素アレイ内で行列状に配置される複数の画素回路の各々が、一方電極の電位によって印加電圧値が変化する発光素子と、電源走査線と前記発光素子の一方電極との間に接続される駆動トランジスタと、前記駆動トランジスタの制御ノードと映像信号線との間に接続され、前記書込走査線の電位に応じて制御されるサンプリングトランジスタと、前記制御ノードに結合する保持キャパシタと、前記一方電極と、列方向の一方側に位置する他の画素回路の電源走査線との間に接続される補助キャパシタと、を含む自発光型表示装置の駆動方法であって、前記補助キャパシタの値  $C_{sub}$ 、前記発光素子の等価容量  $C_{oled.}$ 、前記電源走査線の高電位  $V_{cc\_H}$  と低電位  $V_{cc\_L}$ 、および、前記映像信号線の電位に対応して前記駆動トランジスタのゲート電位  $V_g$  がとりうる範囲に応じて、以下の式、すなわち、

$$V_{ws\_L} < V_g - (V_{cc\_H} - V_{cc\_L}) C_{sub} / (C_{sub} + C_{oled.})$$

を満たす低電位  $V_{ws\_L}$  が、低い方の電位として定められた前記書込走査線の2値電位によって前記サンプリングトランジスタを駆動する。 30

【0023】

ここで、他の画素回路の電源走査線が、例えば、高電位  $V_{cc\_H}$  から電源電位  $V_{cc\_L}$  に変化する場合を例として、作用を説明する。

電源走査線の電位変化は  $(V_{cc\_H} - V_{cc\_L})$  で表され、これが補助キャパシタを介して、当該補助キャパシタが設けられ発光可能状態にある画素回路に入力されるとする。この画素回路は、発光可能状態であるため、サンプリングトランジスタがオフし、駆動トランジスタの制御ノードがフローティング状態となっている。

電位変化  $(V_{cc\_H} - V_{cc\_L})$  が発光素子の一方電極に入力されると、この電位変化が、容量結合比  $g$  ( $= C_{sub} / (C_{sub} + C_{oled.})$ ) に比例した電位変化、即ち、 $(V_{cc\_H} - V_{cc\_L}) C_{sub} / (C_{sub} + C_{oled.})$  となって、保持キャパシタを介して駆動トランジスタの制御ノードの電位を低下させる。上記式の右辺は、電位低下を受けたときに制御ノードで生じる電位変化のボトム値を示す。 40

【0024】

サンプリングトランジスタの制御ノードに書込走査線が接続され、書込走査線は低電位  $V_{ws\_L}$  を低い方の電位とする2値電位により制御される。サンプリングトランジスタは、書込走査線の低電位  $V_{ws\_L}$  でオフが規定される。

【0025】

トランジスタが電界効果型の場合、ソース電位がゲート電位と同じであればリーク電流は発生しないが、ソース電位がゲート電位より低くなるとオンしない場合でもオフリーク

10

20

30

40

50

電流が急激に大きくなる。

よって、上記式は、駆動トランジスタに重畠される電位変化によって制御ノードの電位が一番低くなったときでも、その電位がサンプリングトランジスタの制御ノードの電位より低くならない条件を規定し、この条件が満たされればオン電流およびリーク電流の発生が防止される。

#### 【発明の効果】

#### 【0026】

本発明によれば、サンプリングトランジスタを介して電流が流れないため、電源走査線の電位変化により画質が低下することがない。

10

#### 【発明を実施するための最良の形態】

#### 【0027】

以下、本発明の実施形態を、2T・1C型の画素回路を有する有機ELディスプレイを主な例として、図面を参照して説明する。

#### 【0028】

#### <全体構成>

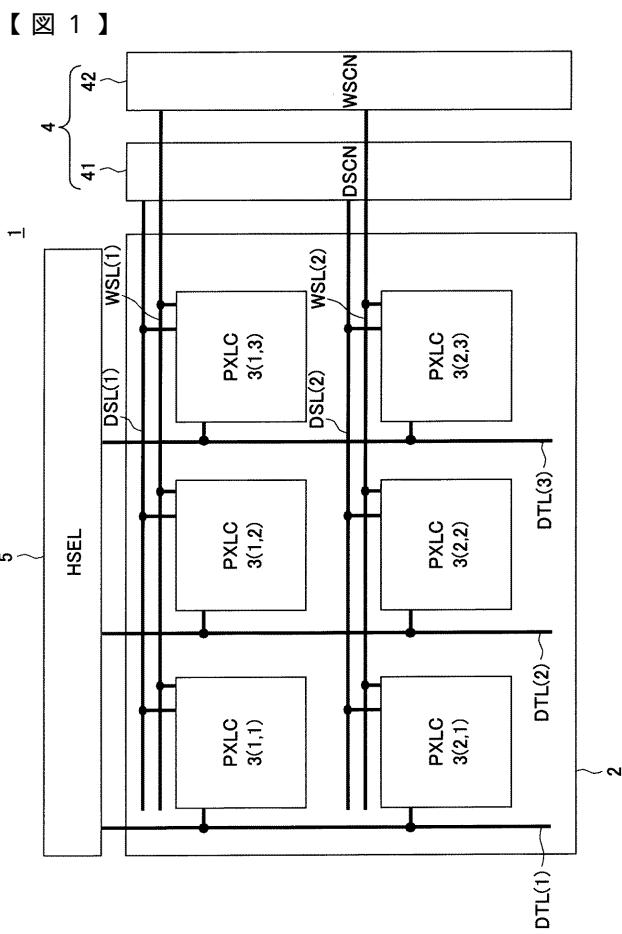

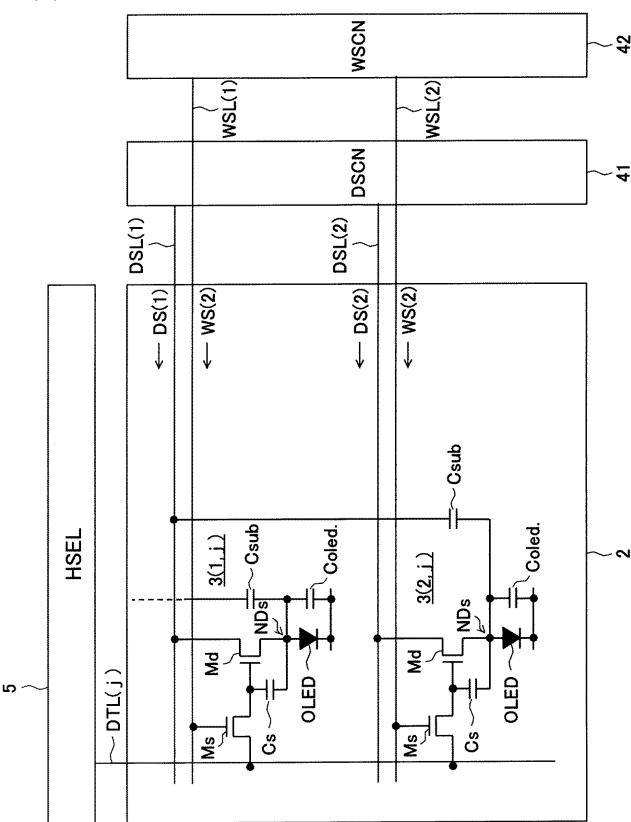

図1に、本発明の実施形態に関わる有機ELディスプレイの主要構成を示す。

図解する有機ELディスプレイ1は、複数の画素回路(PXL<sub>C</sub>)3(i,j)がマトリクス状に配置されている画素アレイ2と、画素アレイ2を駆動する垂直駆動回路(Vスキャナ)4および水平駆動回路(Hセレクタ:HSEL)5とを含む。

20

Vスキャナ4は、画素回路3の構成により複数設けられている。ここではVスキャナ4が、水平画素ライン駆動回路(DSCN)41と、書き込み信号走査回路(WSCN)42とを含んで構成されている。Vスキャナ4およびHセレクタ5は「駆動回路」の一部であり、「駆動回路」は、Vスキャナ4とHセレクタ5の他に、これらにクロック信号を与える回路や制御回路(CPU等)など、不図示の回路も含む。

#### 【0029】

図1に示す画素回路の符号「3(i,j)」は、当該画素回路が垂直方向(縦方向)のアドレスi(i=1,2)と、水平方向(横方向)のアドレスj(j=1,2,3)を持つことを意味する。これらのアドレスiとjは最大値をそれぞれ「n」と「m」とする1以上の整数をとる。ここでは図の簡略化のためn=2、m=3の場合を示す。

このアドレス表記は、以後の説明や図面において画素回路の素子、信号や信号線ならびに電圧等についても同様に適用する。

30

#### 【0030】

画素回路3(1,1)、3(2,1)が垂直方向の映像信号線DTL(1)に接続されている。同様に、画素回路3(1,2)、3(2,2)が垂直方向の映像信号線DTL(2)に接続され、画素回路3(1,3)、3(2,3)が垂直方向の映像信号線DTL(3)に接続されている。映像信号線DTL(1)～DTL(3)は、Hセレクタ5によって駆動される。

第1行の画素回路3(1,1)、3(1,2)および3(1,3)が書き込み走査線WSL(1)に接続されている。同様に、第2行の画素回路3(2,1)、3(2,2)および3(2,3)が書き込み走査線WSL(2)に接続されている。書き込み走査線WSL(1)、WSL(2)は、水平画素ライン駆動回路41によって駆動される。

40

また、第1行の画素回路3(1,1)、3(1,2)および3(1,3)が電源走査線DSL(1)に接続されている。同様に、第2行の画素回路3(2,1)、3(2,2)および3(2,3)が電源走査線DSL(2)に接続されている。電源走査線DSL(1)、DSL(2)は、書き込み信号走査回路42によって駆動される。

#### 【0031】

映像信号線DTL(1)～DTL(3)を含むm本の映像信号線の何れか1本を、以下、符号「DTL(j)またはDTL」により表記する。同様に、書き込み走査線WSL(1)、WSL(2)を含むn本の書き込み走査線の何れか1本を符号「WSL(i)またはWSL」により表記し、電源走査線DSL(1)、DSL(2)を含むn本の電源走査線の何れか1本を符号「DSL(i)またはDSL」により表記する。

50

映像信号線 D T L ( j )に対し、表示画素行（表示ラインともいう）を単位として一齊に映像信号が排出される線順次駆動、あるいは、同一行の映像信号線 D T L ( j )に順次、映像信号が排出される点順次駆動があるが、本実施形態では、そのどの駆動法でもよい。

#### 【 0 0 3 2 】

< 画素回路 >

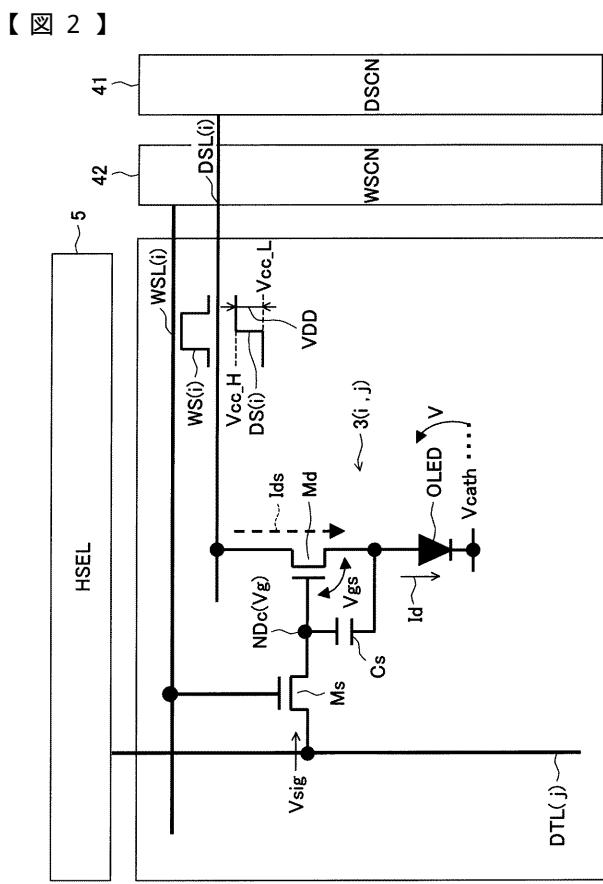

図 2 に、画素回路 3 ( i , j )の一構成例を示す。

図解する画素回路 3 ( i , j )は、有機発光ダイオード O L E D を制御する回路である。画素回路は、有機発光ダイオード O L E D の他に、N M O S タイプの T F T からなる駆動トランジスタ M d およびサンプリングトランジスタ M s と、保持キャパシタ C s とを有する。

10

#### 【 0 0 3 3 】

有機発光ダイオード O L E D は、特に図示しないが、例えば上面発光型の場合、透明ガラス等からなる基板に形成された T F T 構造の上にアノード電極を最初に形成し、その上に、正孔輸送層、発光層、電子輸送層、電子注入層等を順次堆積させて有機多層膜を構成する積層体を形成し、積層体の上に透明電極材料からなるカソード電極を形成した構造を有する。アノード電極が正側の電源に接続され、カソード電極が負側の電源に接続される。

#### 【 0 0 3 4 】

有機発光ダイオード O L E D のアノードとカソードの電極間に所定の電界が得られるバイアス電圧を印加すると、注入された電子と正孔が発光層において再結合する際に有機多層膜が自発光する。有機発光ダイオード O L E D は、有機多層膜を構成する有機材料を適宜選択することで赤( R ), 緑( G ), 青( B )の各色での発光が可能であることから、この有機材料を、例えば各行の画素に R , G , B の発光が可能に配列することで、カラー表示が可能となる。あるいは、白色発光の有機材料を用いて、フィルタの色で R , G , B の区別を行ってもよい。R , G , B の他に W ( ホワイト ) を加えた 4 色構成でもよい。

20

#### 【 0 0 3 5 】

駆動トランジスタ M d は、有機発光ダイオード O L E D に流す電流量を制御して表示階調を規定する電流制御手段として機能する。

駆動トランジスタ M d のドレインが、電源電圧 V D D の供給を制御する電源走査線 D S L ( i )に接続され、ソースが有機発光ダイオード O L E D のアノードに接続されている。有機発光ダイオード O L E D のアノード電極が「一方電極」に該当する。

30

#### 【 0 0 3 6 】

サンプリングトランジスタ M s は、画素階調を決めるデータ電位 V sig の供給線（映像信号線 D T L ( j )）と駆動トランジスタ M d のゲート（制御ノード N D c ）との間に接続されている。サンプリングトランジスタ M s のソースとドレンの一方が駆動トランジスタ M d のゲート（制御ノード N D c ）に接続され、もう片方が映像信号線 D T L ( j )に接続されている。映像信号線 D T L ( j )に、H セレクタ 5 ( 図 1 参照 ) からデータ電位 V sig を持つデータパルスが所定の間隔で供給される。サンプリングトランジスタ M s は、データ電位の供給期間（データパルスの持続時間 duration time ）の適正なタイミングで、当該画素回路で表示すべきレベルのデータをサンプリングする。これは、サンプリングすべき所望のデータ電位 V sig を持つデータパルスの前部または後部における、レベルが不安定な遷移期間の表示映像に与える影響を排除するためである。

40

#### 【 0 0 3 7 】

駆動トランジスタ M d のゲート（制御ノード）とソース（有機発光ダイオード O L E D のアノードをなす一方電極）との間に、保持キャパシタ C s が接続されている。保持キャパシタ C s の役割については、後述の動作説明で明らかにする。

#### 【 0 0 3 8 】

図 2 では、水平画素ライン駆動回路 4 1 により、低電位 V c c \_ L を基準とした高電位 V c c \_ H の波高値が電源電圧 V D D となる電源駆動パルス D S ( i )が駆動トランジスタ M d のドレンに供給され、駆動トランジスタ M d の補正時や有機発光ダイオード O L E

50

D が実際に発光する時の電源供給が行われる。

また、書き込み信号走査回路 4 2 により、比較的短い持続時間の書き込み駆動パルス W S (i) がサンプリングトランジスタ M s のゲートに供給され、サンプリング制御が行われる。

なお、電源供給の制御は、駆動トランジスタ M d のドレインと電源電圧 V D D の供給線との間にトランジスタをもう 1 つ挿入し、そのゲートを水平画素ライン駆動回路 4 1 により制御する構成であってもよい(後述の変形例参照)。

#### 【0039】

図 2 では有機発光ダイオード O L E D の一方電極(アノード)が駆動トランジスタ M d を介して正側の電源から電源電圧 V D D の供給を受ける。有機発光ダイオード O L E D のカソードが、カソード電位 V cath を供給する所定の電圧線(例えば、負側の電源線)に接続されている。

#### 【0040】

通常、画素回路内の全てのトランジスタは T F T で形成されている。T F T のチャネルが形成される薄膜半導体層は、多結晶シリコン(ポリシリコン)または非晶質シリコン(アモルファスシリコン)等の半導体材料からなる。ポリシリコン T F T は移動度を高くとれるが特性ばらつきが大きいため、表示装置の大画面化に適さない。よって、大画面を有する表示装置では、一般に、アモルファスシリコン T F T が用いられる。ただし、アモルファスシリコン T F T では P チャネル型 T F T が形成し難いため、上述した画素回路 3(i,j) のように、すべての T F T を N チャネル型とすることが望ましい。

#### 【0041】

ここで、以上の画素回路 3(i,j) は、本実施形態で適用可能な画素回路の一例、即ち 2 トランジスタ(2 T)・1 キャパシタ(1 C) 型の基本構成例である。よって、本実施形態で用いることができる画素回路は、上記画素回路 3(i,j) を基本構成として、さらにトランジスタやキャパシタを付加した画素回路であってもよい(後述の変形例参照)。また、基本構成において、保持キャパシタ C s を電源電圧 V D D の供給線と駆動トランジスタ M d のゲートとの間に接続するものもある。

具体的に、本実施形態で採用可能な 2 T・1 C 型以外の画素回路として、後述する変形例で幾つかを簡単に述べるが、例えば、4 T・1 C 型、4 T・2 C 型、5 T・1 C 型、3 T・1 C 型などであってもよい。

#### 【0042】

図 2 の構成を基本とする画素回路では、閾値電圧補正時や移動度補正時に有機発光ダイオード O L E D を逆バイアスすると、詳細は後述するが、有機発光ダイオード O L E D の逆バイアス時の等価容量値が保持キャパシタ C s の値より十分大きくできるため、有機発光ダイオード O L E D のアノードが電位的に動き難くなるため、補正精度が向上する。このため、逆バイアス状態で補正を行うことが望ましい。

カソード電位 V cath を接地せずに、カソードを所定の電圧線に接続しているのは、逆バイアスを行うためである。有機発光ダイオード O L E D を逆バイアスするには、例えば、電源駆動パルス D S (i) の基準電位(低電位 V c c \_ L ) より、カソード電位 V cath を小さくする。

#### 【0043】

データの書き込み時に、有機発光ダイオード O L E D のアノード電位を更に動き難くして電位的に固定するには、有機発光ダイオード O L E D のアノードからみた容量値を大きくするとよい。この目的で、有機発光ダイオード O L E D のアノードに補助キャパシタが接続される。この補助キャパシタの有無によって、動作タイミング制御自体が変更されないので、先に動作(表示制御)を説明する。

#### 【0044】

##### < 表示制御 >

図 2 の回路におけるデータ書き込み時の動作を、閾値電圧と移動度の補正動作と併せて説明する。これらの一連の動作を「表示制御」という。

10

20

30

40

50

最初に、補正対象となる駆動トランジスタと有機発光ダイオードOLEDの特性について説明する。

【0045】

図2に示す駆動トランジスタMdの制御ノードNdcには、保持キャパシタCsが結合されている。映像信号線DTL(j)を伝送するデータパルスの有効電位であるデータ電位VsigがサンプリングトランジスタMsでサンプリングされ、これにより得られた電位が制御ノードNdcに印加され、保持キャパシタCsで保持される。駆動トランジスタMdのゲートに所定の電位が印加された時、そのドレイン電流Idsは、印加電位に応じた値を持つゲートソース間電圧Vgsに応じて決まる。

ここで駆動トランジスタMdのソース電位Vsを、上記データパルスの基準電位(データ基準電位Vo)に初期化してから、サンプリングを行うとする。サンプリング後のデータ電位Vsig、より正確には、データ基準電位Voとデータ電位Vsigとの電位差で規定されるデータ電圧Vinの大きさに応じたドレイン電流Idsが駆動トランジスタMdに流れ、これがほぼ、有機発光ダイオードOLEDの駆動電流Idとなる。

よって、駆動トランジスタMdのソース電位Vsがデータ基準電位Voで初期化されている場合、有機発光ダイオードOLEDがデータ電位Vsigに応じた輝度で発光する。

【0046】

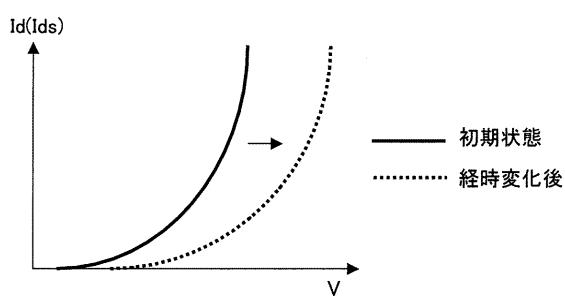

図3に、有機発光ダイオードOLEDのI-V特性のグラフと、駆動トランジスタMdのドレイン電流Ids(OLEDの駆動電流Idにほぼ相当)の一般式を示す。

有機発光ダイオードOLEDは、よく知られているように、経時変化によりI-V特性が図3のように変化する。このとき、図2の画素回路では、駆動トランジスタMdが一定のドレイン電流Idsを流そうとしても、図3に示すグラフから分かるように有機発光ダイオードOLEDの印加電圧が大きくなるため、有機発光ダイオードOLEDのソース電位Vsが上昇する。このとき駆動トランジスタMdのゲートはフローティング状態であるため、ほぼ一定のゲートソース間電圧Vgsが維持されるように、ソース電位と共にゲート電位も上昇し、ドレイン電流Idsはほぼ一定に保たれ、このことが有機発光ダイオードOLEDの発光輝度を変化させないように作用する。

【0047】

しかしながら、画素回路ごとに駆動トランジスタMdの閾値電圧Vth、移動度μが異なっているため、図3の式に応じて、ドレイン電流Idsにバラツキが生じ、表示画面内で与えられているデータ電位Vsigが同じ2つの画素であっても、当該2つの画素間で発光輝度が異なる。

【0048】

なお、図3の式において、符号“Ids”は、飽和領域で動作する駆動トランジスタMdのドレインとソース間に流れる電流を表す。また、当該駆動トランジスタMdにおいて、“Vth”が閾値電圧を、“μ”が移動度を、“W”が実効チャネル幅(実効ゲート幅)を、“L”が実効チャネル長(実効ゲート長)を、それぞれ表す。また、“Cox”が当該駆動トランジスタMdの単位ゲート容量、即ち単位面積当たりのゲート酸化膜容量と、ソースやドレインとゲート間のフリンジング容量との総和を表す。

【0049】

Nチャネル型の駆動トランジスタMdを有する画素回路は、駆動能力が高く製造プロセスを簡略化できる利点があるが、閾値電圧Vthや移動度μのばらつきを抑えるため、それらの補正動作を、発光可能なバイアス設定に先立って行う必要がある。

【0050】

つぎに、図4を用いて具体的な制御の説明に移るが、この図4は、本発明が適用される前の制御を示している。

以下、図4における期間を定義し、制御の全体を図4の時間軸に沿って詳しく説明した上で、図4の制御での不具合(横クロストークの発生)、図4の制御に対する本発明の適用(本実施形態の特徴)とその効果の順で説明する。

【0051】

10

20

30

40

50

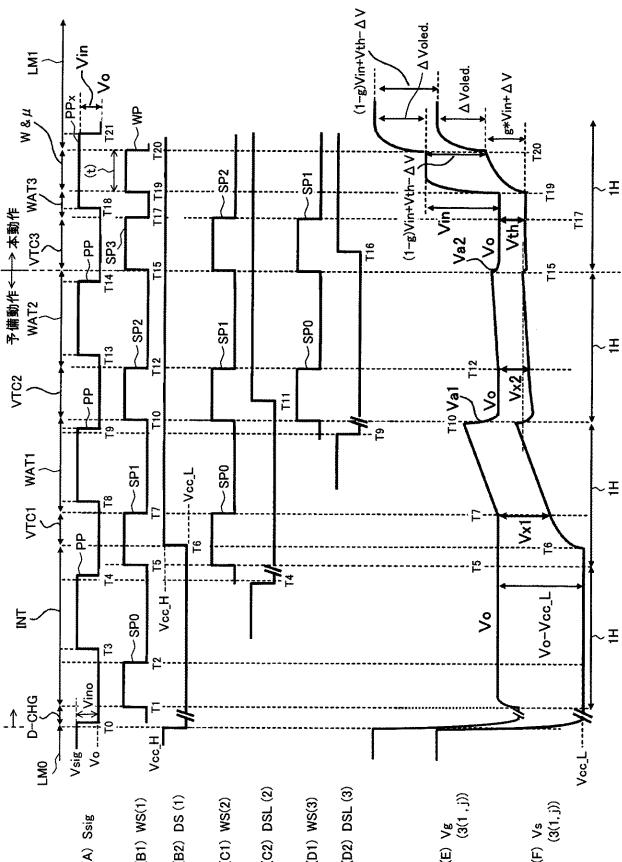

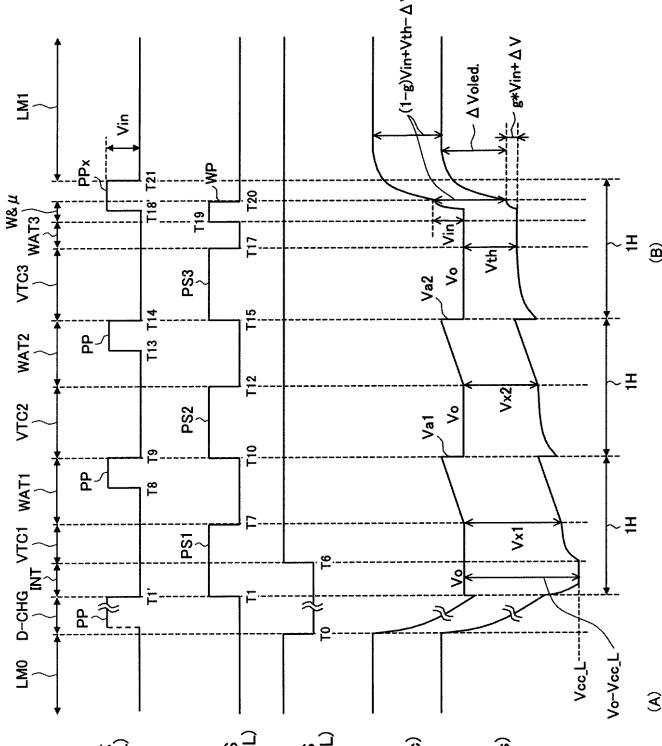

図4(A)～図4(F)は、表示制御における各種信号や電圧の波形を示すタイミングチャートである。ここで表示制御では行単位でデータ書き込みを順次行うものとし、第1行の画素回路3(1,j)が書き込み対象の行(表示行)であり、第2行の画素回路3(2,j)と第3行の画素回路3(3,j)は、図4の時点では書き込み対象でない(非表示行である)。表示行に対し、図4に示し、これから説明する表示制御によってデータが書かれた後は、表示行が第2行に移り同様な表示制御が行われ、同様な表示制御が第3行、第4行、…と繰り返されることによって1画面が表示される。1画面の表示後は、同様にして他の画面表示のための表示制御が、必要な回数繰り返される。

#### 【0052】

図4(A)は、映像信号Ssigの波形図である。

10

図4(B1)と図4(B2)は、書き込み対象の第1行に供給される書き駆動パルスWS(1)と電源駆動パルスDS(1)の波形図である。同様にして、図4(C1)と図4(C2)は、非書き込み対象の第2行に供給される書き駆動パルスWS(2)と電源駆動パルスDS(2)の波形図、図4(D1)と図4(D2)は、非書き込み対象の第3行に供給される書き駆動パルスWS(3)と電源駆動パルスDS(3)の波形図である。

図4(E)は、書き込み対象の第1行の画素回路3(1,j)における駆動トランジスタMdのゲート電位(制御ノードNDCの電位)の波形図である。

図4(F)は、書き込み対象の第1行の画素回路3(1,j)における駆動トランジスタMdのソース電位(有機発光ダイオードOLEDのアノード電位)の波形図である。

#### 【0053】

20

##### [期間の定義]

図4(F)の下部に記載している通り、図4は、NTSC映像信号規格の1水平期間(1H)に対し、その約4倍強のスパンで波形図を表示している。そして、その後の1水平期間(1H)で、最終的な3回目の第3閾値補正(VTC3)と、移動度の補正および実際のデータ書き込み(W&μ)とを連続して実行する(本動作)。その後の1水平期間(1H)に行われる本動作より前の3水平期間((1H)×3)は、専ら、初期化のためと、最終的な閾値補正では時間が短くて補正しきれない場合を考慮して、ある程度まで閾値補正を予め2度行うために費やされる(予備動作)。

図4のような表示制御は、表示画像の高解像度化が進展し、表示パネルの駆動周波数が非常に高くなっている現状では、短い1水平期間(1H)で閾値電圧補正からデータ書き込みまで一挙に行うことができず、とくに閾値補正の時間が不足することに鑑み、閾値補正を数回に分けて行うものである。ただし、駆動周波数が余り高くない小型から中型の表示パネル等で、本動作の時間が1水平期間(1H)で十分なら、初期化のために1水平期間(1H)もあれば予備動作としては十分な場合もある。もちろん、予備動作が2水平期間(2H)であってもよいし、4水平期間(4H)以上であってもよい。

30

ある行に対して本動作を行っているときは、次の行(および、その次以降の行、…、)について予備動作を並列に実行できるため、予備動作時間の長短は全体の表示期間にほとんど影響しない。むしろ、閾値電圧補正を確実に行う意味で、予備動作を十分に行ったほうが望ましい。

#### 【0054】

40

以上は1水平期間(1H)という一定尺度で見た期間の区分であるが、図4(F)に記載した大よそ4水平期間を機能的に把握することも可能である。

具体的に図4(A)の上部に記載しているように、(1フィールドまたは1フレーム)前画面の発光期間(LM0)の後に時系列の順で、放電期間(D-CHG)、初期化期間(INT)、第1閾値補正期間(VTC1)、第1待機期間(WAT1)、第2閾値補正期間(VTC2)、第2待機期間(WAT2)を経て「予備動作」が実行される。また、続いて、第3閾値補正(VTC3)、第3待機期間(WAT3)、書き込み&移動度補正期間(W&μ)を経て、当該第1行の画素回路3(1,j)の発光期間(LM1)に推移することによって「本動作」が実行される。

#### 【0055】

50

### [ 駆動パルスの概略 ]

また、図4では、波形図の適当な箇所に時間表示を符号“T 0”～“T 21”により示している。つぎに、この時間表示を参照して映像信号や駆動パルスの概略を説明する。

第1行に供給される書込駆動パルスWS(1)では、図4(B1)に示すように、“L”レベルで非アクティブ、“H”レベルでアクティブの4つのサンプリングパルス(S P 0～S P 3)が周期的に出現する。このとき4つのサンプリングパルス(S P 0～S P 3)の周期は、予備動作(時間T 0～時間T 15)および本動作(時間T 15以後)を通じて一定である。ただし、本動作における書込駆動パルスWS(1)は、4つ目のサンプリングパルス(S P 3)の後に書き込みパルス(W P)が重畠された波形となる。

### 【 0 0 5 6 】

これに対し、m本(数百～千数百本)の映像信号線DTL(j)(図1および図2参照)に供給される映像信号S sigは、線順次表示ではm本の映像信号線DTL(j)に同時に供給される。そして、映像信号S sigをサンプリング後に得られるデータ電圧を反映した信号振幅(V in)は、図4(A)に示すように、1水平期間(1 H)の前半部分で繰り返し出現するデータ基準電位V oを基準とした、1水平期間(1 H)の後半部分に繰り返し出現する映像信号パルス(P P)の波高値に相当する。以下、信号振幅(V in)をデータ電圧V inと呼ぶ。

図4(A)に示す幾つかの映像信号パルス(P P)のうち、第1行にとって重要な映像信号パルスは、書き込みパルス(W P)と時間的に重なる本動作時の映像信号パルス(P P x)である。本動作時の映像信号パルス(P P x)のデータ基準電位V oからの波高値が、図4で表示させたい(書き込みたい)階調値、即ちデータ電圧V inの大きさに該当する。この階調値(=V in)は、第1行の各画素で同じ場合(単色表示の場合)もあるが、通常、表示画素行の階調値に応じて変化している。図4は、主として、第1行内における1つの画素についての動作を説明するためのものであるが、同一行の他の画素では、この表示階調値が異なることがある以外、制御自体は、図示の画素駆動制御と並列に実行される。

### 【 0 0 5 7 】

駆動トランジスタM dのドレイン(図2参照)に供給される電源駆動パルスDS(1)は、図4(B2)に示すように、時間T 0から最初の第1閾値補正期間(V T C 1)の開始(時間T 6)直前まで非アクティブの低電位V c c \_ Lで保持され、第1閾値補正期間(V T C 1)の開始とほぼ同時に(時間T 6)、アクティブの高電位V c c \_ Hに推移する。高電位V c c \_ Hの保持は、発光期間(L M 1)が終了するまで続く。

### 【 0 0 5 8 】

第2行(の画素回路3(2,j))、第3行(の画素回路3(3,j))については、それぞれ、図4(C1)と図4(C2)、図4(D1)と図4(D2)に示すように、1水平期間(1 H)ずつ各パルスが遅れて印加される。

具体的には、第1行の第1閾値補正期間(V T C 1)に対応する2つ目のサンプリングパルス(S P 1)が印加される時間T 5～T 7の間に、第2行では、初期化期間(I N T)に対応する1つ目のサンプリングパルス(S P 0)が印加される。

このパルス印加の途中、即ち時間T 6で第1行の電源駆動パルスDS(1)がハイレベル(電源電位V c c \_ H)に立ち上がりアクティブとなる。

### 【 0 0 5 9 】

その後、第1行の第2閾値補正期間(V T C 2)に対応する3つ目のサンプリングパルス(S P 2)が印加される時間T 10～T 12の間に、第2行では、第1行から1水平期間(1 H)遅れて上記2つ目のサンプリングパルス(S P 1)が印加され、第3行では、第1行から2水平周期((1 H)×2)遅れて上記1つ目のサンプリングパルス(S P 0)が印加される。

このパルス印加の途中、即ち時間T 11で第2行の電源駆動パルスDS(2)が高電位V c c \_ Hに立ち上がりアクティブとなる。

### 【 0 0 6 0 】

10

20

30

40

50

その後、第1行の第3閾値補正期間（VTC3）に対応する4つ目のサンプリングパルス（SP3）が印加される時間T15～T17の間に、第2行では、第1行から1水平期間（1H）遅れて上記3つ目のサンプリングパルス（SP2）が印加され、第3行では、第1行から2水平周期（（1H）×2）遅れて上記2つ目のサンプリングパルス（SP1）が印加される。

このパルス印加の途中、即ち時間T16で第3行の電源駆動パルスDS(3)が高電位Vcc\_Hに立ち上がりアクティブとなる。

#### 【0061】

以上のようにしてパルス印加のタイミング設計を行うと、ある行の本動作を行っている期間に、その1～数水平期間後に本動作を行う他の数行分の予備動作を並列に実行することから、本動作に限ってみると行単位でシームレスに、その実行がなされる。よって、最初の数水平期間以外は無駄な期間は発生しない。

表示画面は通常、数百～千数百の行を有するため、1画面表示中における1～数水平期間という時間は無視できるほど短い。したがって、閾値電圧補正を数回に分けても時間的な損失は実質的に生じない。

#### 【0062】

つぎに、以上のパルス制御の下における、図4(E)および図4(F)に示す駆動トランジスタMdのソースやゲートの電位変化と、それに伴う動作を、図4(A)に示す期間ごとに説明する。

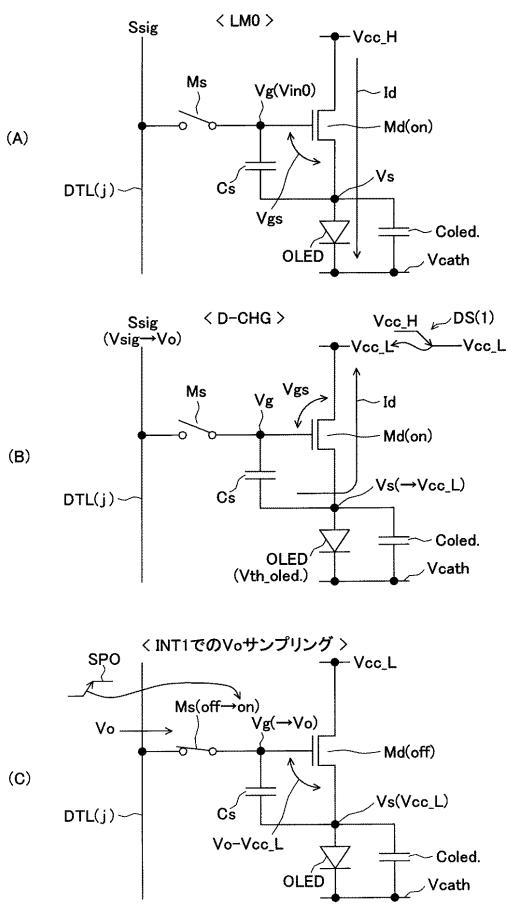

なお、ここでは図5(A)～図7(B)に示す第1行の画素回路3(1,j)の予備動作説明図、図8に示すソース電位Vsの時間推移のグラフ、図9(A)～図9(C)に示す第1行の画素回路3(1,j)の本動作説明図、ならびに、図2等を適宜参照する。

#### 【0063】

##### [前画面の発光期間(LM0)]

第1行の画素回路3(1,j)について、時間T0以前の1フィールドまたは1フレームだけ前の画面（以下、前画面という）についての発光期間（LM0）では、図4(B1)に示すように書込駆動パルスWS(1)が“L”レベルであるため、サンプリングトランジスタMsがオフしている。また、図4(B2)に示すように、電源駆動パルスDS(1)が高電位Vcc\_Hの印加状態にある。

#### 【0064】

このとき、図5(A)に示すように、前画面のデータ書き込み動作によって駆動トランジスタMdのゲートに入力され保持されているデータ電圧Vin0に応じて、有機発光ダイオードOLEDが発光状態にあるとする。駆動トランジスタMdは飽和領域で動作するよう設定されているため、有機発光ダイオードOLEDに流れる駆動電流Id(=Ids)は、保持キャパシタCsに保持されている駆動トランジスタMdのゲートソース間電圧Vgsに応じて、前述した図3に示す式から算出される値をとる。

#### 【0065】

##### [放電期間(D-CHG)]

図4において時間T0から、線順次走査の新しい画面表示に関する処理が開始される。

時間T0になると、水平画素ライン駆動回路41（図2参照）が、図4(B2)に示すように、電源駆動パルスDS(1)を高電位Vcc\_Hから低電位Vcc\_Lに切り替える。駆動トランジスタMdは、今までドレインとして機能していたノードの電位が低電位Vcc\_Lにまで急激に落とされ、ソースとドレインの電位が逆転するため、今までドレインであったノードをソースとし、今までソースであったノードをドレインとして、当該ドレインの電位（ただし、図の表記ではソース電位Vsのまととする）を引き抜くディスチャージ動作が行われる。

したがって、図5(B)に示すように、今までとは逆向きのドレイン電流Id\_sが駆動トランジスタMdに流れる。この駆動トランジスタMdに逆向きの電流が流れる期間を、図4や図5(B)では「放電期間(D-CHG)」と表記している。

#### 【0066】

10

20

30

40

50

放電期間 (D - C H G) が開始されると、図 4 (F) に示すように、時間 T 0 を境に駆動トランジスタ M d のソース電位 V s (現実の動作上はドレイン電位) が急激に放電され、ほぼ低電位 V c c \_ L の近くまで低下する。

このとき、低電位 V c c \_ L が有機発光ダイオード O L E D の発光閾値電圧 V th\_oled. とカソード電位 V cath の和よりも小さいとき、つまり “V c c \_ L < V th\_oled. + V cath” であれば有機発光ダイオード O L E D は消光する。

なお、放電期間 (D - C H G) の終了 (時間 T 1) の前までには、図 4 (A) に示すように、映像信号 S sig の電位が、データ電位 V sig からデータ基準電位 V o にまで下げられている。

#### 【0067】

時間 T 0において、図 5 (B) に示すように、サンプリングトランジスタ M s がオフし、制御ノード N D c がフローティング状態にある。このため、図 4 (E) に示すように、時間 T 0 を境に駆動トランジスタ M d のゲート電圧 V g が低下する。

#### 【0068】

##### [初期化期間 (INT)]

次に、書き込み信号走査回路 4 2 (図 2 参照) が、図 4 (B1) に示すように、時間 T 1 にて書込駆動パルス W S(1)を “L” レベルから “H” レベルに遷移させて 1 つ目のサンプリングパルス (S P 0) を、サンプリングトランジスタ M s のゲートに与える。

この時間 T 1 にて放電期間 (D - C H G) が終了し、ここから初期化期間 (INT) が開始する。

#### 【0069】

時間 T 1 での、サンプリングパルス (S P 0) の印加に応答して、図 5 (C) に示すように、サンプリングトランジスタ M s がオンする。前述したように時間 T 1 までには、映像信号 S sig の電位がデータ基準電位 V o に切り替えられている。したがって、サンプリングトランジスタ M s は、映像信号 S sig のデータ基準電位 V o をサンプリングして、サンプリング後のデータ基準電位 V o を駆動トランジスタ M d のゲートに伝達する。

このサンプリング動作によって、図 4 (E) に示すように、時間 T 0 を境に低下した駆動トランジスタ M d のゲート電圧 V g が、データ基準電位 V o に収束する。

#### 【0070】

図 4 (B1) に示すサンプリングパルス (S P 0) は、時間 T 1 から、この電位収束に十分な時間が経過した時間 T 2 にて終了し、サンプリングトランジスタ M s がオフする。よって、次にサンプリングトランジスタ M s がオンする時間 T 5 までは、駆動トランジスタ M d のゲートが電気的なフローティング状態となる。

この時間 T 5 でサンプリングトランジスタ M s を再度オンさせるタイミングは、最初の 1 水平期間 (1 H) の終了とほぼ同じに制御され、かつ、時間 T 2 ~ T 5 の期間内に、当該 1 水平期間 (1 H) における映像信号パルス (P P) が収まるようにタイミング設計されている (図 4 (A) と図 4 (B1) 参照)。

#### 【0071】

このことをサンプリングパルス (S P 0) から見ると、書込駆動パルス W S(1)を “H” レベルにするサンプリングパルス (S P 0) の持続時間 (時間 T 1 ~ T 2) は、1 水平期間 (1 H) の前半部分である、映像信号 S sig がデータ基準電位 V o をとる期間 (時間 T 0 ~ T 3) 内となっている。

そして、時間 T 2 でサンプリングトランジスタ M s をオフさせた状態で、映像信号パルス (P P) による映像信号線 D T L(j) の電位変動が終了する時間 T 4 の経過を待ち、その後の時間 T 5 で、データ基準電位 V o を再度サンプリングするための 2 つ目のサンプリングパルス (S P 1) を立ち上げる。

この制御の結果、2 つ目のサンプリングパルス (S P 1) を立ち上げた時間 T 5 で、映像信号 S sig のデータ電位 V sig を誤ってサンプリングすることは回避される。

なお、時間 T 5 における 2 度目のサンプリング開始時には、図 4 (E) に示すように、既にゲート電圧 V g がデータ基準電位 V o を保持している。したがって、2 度目のサンプ

10

20

30

40

50

リングによってリーク電流等による微小な損失を補うことがあるにせよ、一般には、ゲート電圧  $V_g$  は殆ど変動しない。

#### 【0072】

時間軸上での説明を若干前に戻すと、時間  $T_1$  で 1 つ目のサンプリングパルス ( S P 0 ) が印加されることによってサンプリングトランジスタ  $M_s$  がオンし、図 4 ( E ) に示すように、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  がデータ基準電位  $V_o$  に収束すると、これに連動して保持キャパシタ  $C_s$  の保持電圧が低下し、“ $V_o - V_{c c \_ L}$ ”となる(図 4 ( F ) )。これは、図 5 ( B ) のディスクチャージによってソース電位  $V_s$  が低電位  $V_{c c \_ L}$  になり、低電位  $V_{c c \_ L}$  を基準にしたゲート電圧  $V_g$  で保持キャパシタ  $C_s$  の保持電圧が規定されるためである。つまり、図 5 ( C ) において、ゲート電圧  $V_g$  がデータ基準電位  $V_o$  に下がると、これに連動して保持キャパシタ  $C_s$  の保持電圧が下がり、当該保持電圧が“ $V_o - V_{c c \_ L}$ ”に収束する。なお、この保持電圧“ $V_o - V_{c c \_ L}$ ”はゲートソース間電圧  $V_{gs}$  そのものであり、ゲートソース間電圧  $V_{gs}$  が駆動トランジスタ  $M_d$  の閾値電圧  $V_{th}$  よりも大きくないと、その後に閾値補正動作を行なうことができないために、“ $V_o - V_{c c \_ L} > V_{th}$ ”とするように電位関係が決められている。

このようにして、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  およびソース電位  $V_s$  を初期化することで、閾値補正動作の準備が完了する。

#### 【0073】

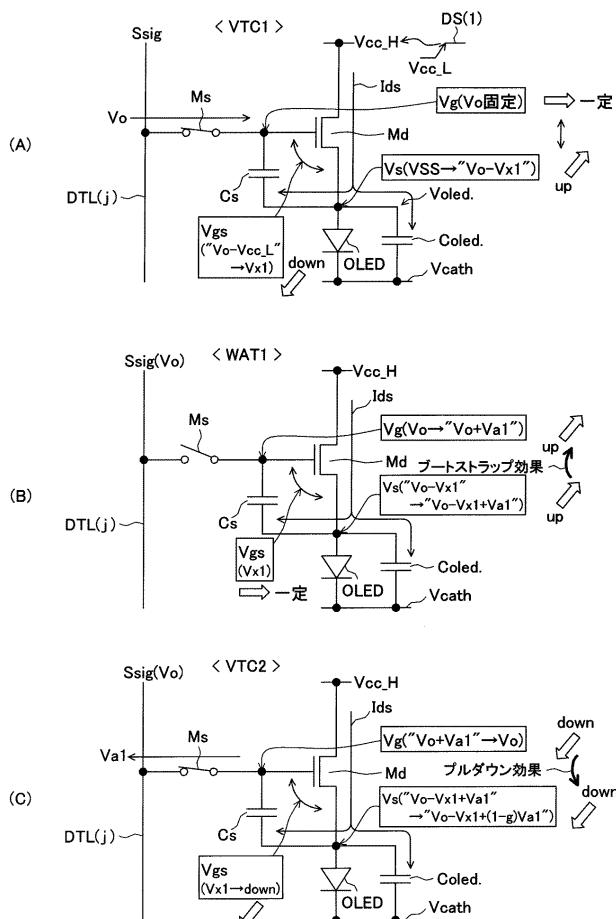

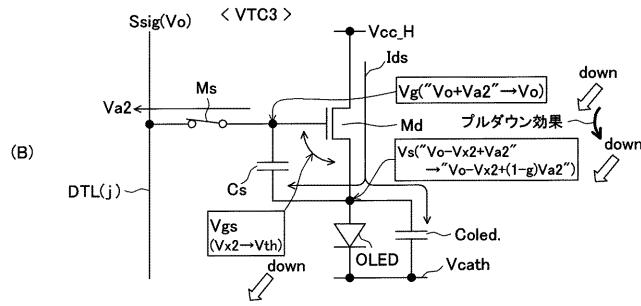

##### [ 第 1 閾値補正期間 ( V T C 1 ) ]

時間  $T_5$  でサンプリングトランジスタ  $M_s$  が 2 度目の  $V_o$  サンプリングを開始した後、図 4 ( B 2 ) に示すように、時間  $T_6$  で電源駆動パルス  $D_S(1)$  が低電位  $V_{c c \_ L}$  から高電位  $V_{c c \_ H}$  に立ち上がると、当該初期化期間 ( I N T ) が終了し、第 1 閾値補正期間 ( V T C 1 ) が開始する。

#### 【0074】

第 1 閾値補正期間 ( V T C 1 ) の開始時 ( 時間  $T_6$  ) の直前において、オン状態のサンプリングトランジスタ  $M_s$  がデータ基準電位  $V_o$  をサンプリング中であるため、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  は、一定のデータ基準電位  $V_o$  で電気的に固定された状態にある。

この状態で時間  $T_6$  にて、水平画素ライン駆動回路 4 1 ( 図 2 参照 ) が、図 4 ( B 2 ) に示すように、電源駆動パルス  $D_S(1)$  を低電位  $V_{c c \_ L}$  から高電位  $V_{c c \_ H}$  に立ち上げる。水平画素ライン駆動回路 4 1 は、時間  $T_6$  以降は、次のフレーム ( あるいはフィールド ) の処理開始まで、駆動トランジスタ  $M_d$  への電源供給線の電位を高電位  $V_{c c \_ H}$  に保持しておく。

#### 【0075】

電源駆動パルス  $D_S(1)$  の立ち上げによって駆動トランジスタ  $M_d$  のソースとドレイン間に“ $V_{c c \_ H} - V_{c c \_ L}$ ”の電源電圧  $V_{DD}$  が印加される。そのため、駆動トランジスタ  $M_d$  に電源からドレイン電流  $I_{ds}$  が流れようになる。

ドレイン電流  $I_{ds}$  によって駆動トランジスタ  $M_d$  のソースが充電され、図 4 ( F ) に示すようにソース電位  $V_s$  が上昇するため、それまで“ $V_o - V_{c c \_ L}$ ”という値をとっていた駆動トランジスタ  $M_d$  のゲートソース間電圧  $V_{gs}$  ( 保持キャパシタ  $C_s$  の保持電圧 ) は、徐々に小さくなっていく ( 図 4 ( E ) および図 4 ( F ) )。

#### 【0076】

このときのドレイン電流  $I_{ds}$  による駆動トランジスタ  $M_d$  のソース充電速度は余り大きくない。その理由を、図 6 ( A ) を参照しつつ述べる。

図 6 ( A ) に示すように、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  に印加されているゲートバイアス電圧がデータ基準電位  $V_o$  で規定され、当該バイアス電圧が余り大きくないため、駆動トランジスタ  $M_d$  は浅いオン状態、すなわち駆動能力が余り大きくない状態でオンする ( 第 1 の理由 )。

また、ドレイン電流  $I_{ds}$  は保持キャパシタ  $C_s$  に流れ込むが、有機発光ダイオード O LED の容量  $C_{oled}$  の充電にもドレイン電流  $I_{ds}$  が消費されるため、ソース電位  $V_s$

10

20

30

40

50

が上がりにくい（第2の理由）。

さらに、サンプリングパルス（S P 1）を、次に映像信号 S sig がデータ電位 V sig に遷移する時間 T 8 より前の時間 T 7 で終了させる必要があるため（図4（B 1）参照）、ソース電位 V s の充電時間が不十分である（第3の理由）。

#### 【0077】

仮に、図4（B 1）に示す2つ目のサンプリングパルス（S P 1）が時間 T 7 を越えて十分長くまで持続可能であるとすると、駆動トランジスタ M d のソース電位 V s（有機発光ダイオード O L E D のアノード電位）は、図8に示すように、時間 T 6 を起点として時間とともに上昇し、“V o - V th”で収束する（図8の破線により示す曲線 C V）。つまり、ゲートソース間電圧 V gs（保持キャパシタ C s の保持電圧）が丁度、駆動トランジスタ M d の閾値電圧 V th となつたところでソース電位 V s の上昇がほぼ終了するはずである。

10

#### 【0078】

##### [第1待機期間（W A T 1）]

しかしながら、現実には、その収束点に達する前に時間 T 7 が来るため、サンプリングパルス（S P 1）の持続時間が終了し、これによって、第1閾値補正期間（V T C 1）が終了し、第1待機期間（W A T 1）が開始する。

具体的には、駆動トランジスタ M d のゲートソース間電圧 V gs が V × 1 (> V th) になったとき、つまり、図8に示すように、駆動トランジスタ M d のソース電位 V s が低電位 V c c \_ L から “V o - V × 1” に上昇した時点（時間 T 7）で、第1閾値補正期間（V T C 1）が終了する。このとき（時間 T 7）では、電圧値 V × 1 が保持キャパシタ C s に保持される。

20

#### 【0079】

第1閾値補正期間（V T C 1）が終了すると、サンプリングトランジスタ M s がオフするため、駆動トランジスタ M d のゲートがデータ基準電位 V o で電気的に固定された状態から、電気的なフローティング状態に推移する。

したがって、時間 T 7 以後は、ソース電位 V s が上昇すると、それに伴って、ソースに容量結合したフローティング状態のゲートの電位（V g）も上昇する（図4（E）と図4（F））。その結果、本例では、第1待機期間（W A T 1）の終了時点（時間 T 10）において、ソース電位 V s が収束目標の “V o - V th” よりも大きくなる（図8参照）一方で、図4（E）および（F）に示すようにゲートソース間電圧 V gs は縮まらない。

30

#### 【0080】

第1待機期間（W A T 1）は、先に説明した初期化期間（I N T）と同様、映像信号パルス（P P）の通過を待つ必要があり、その意味で“待機期間”と称している。しかし、時間 T 7 ~ T 10 といった比較的長い待機期間は、ゲート電圧 V g の上昇を許してしまい、また、上記のようにゲートソース間電圧 V gs の閾値電圧 V th への収束が進まない。

図4（E）では、第1待機期間（W A T 1）中におけるゲート電圧 V g の上昇分を “V a 1” で表している。なお、結合容量（保持キャパシタ C s）を介した、このゲート電圧 V g の上昇をブーストアップ動作により引き起こす原因となるソース電位 V s の上昇分も “V a 1” で同じとする。ソース電位 V s は第1待機期間（W A T 1）の終了時点（時間 T 10）で “V o - V × 1 + V a 1” となる（図6（B）参照）。

40

このため、ゲート電位を、初期化レベルであるデータ基準電位 V o に戻すとともに閾値電圧補正を再度行う必要がある。

#### 【0081】

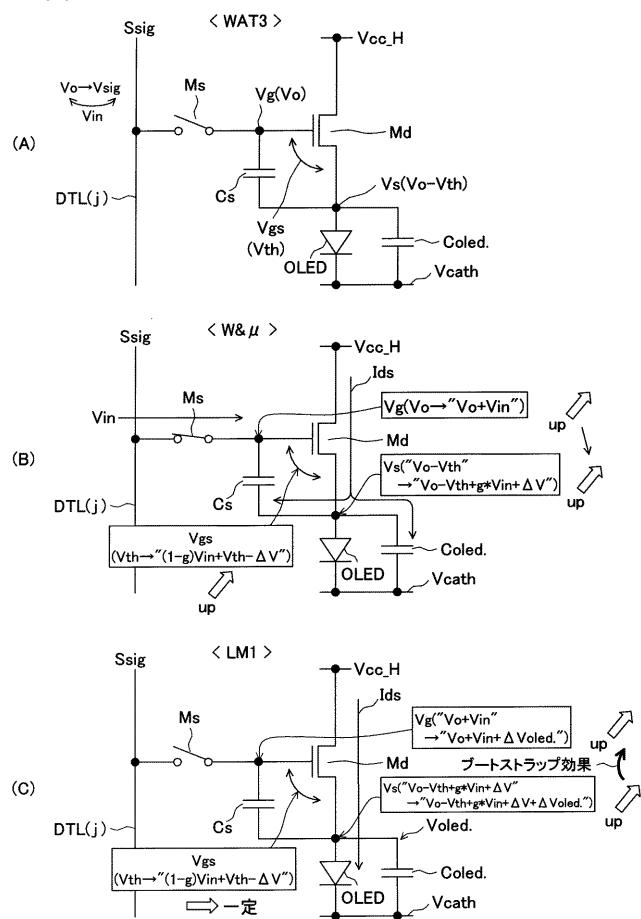

##### [第2閾値補正期間（V T C 2）]

そこで本実施形態の動作例では、次の1水平期間（1 H）（時間 T 10 ~ T 15）において、前の1水平期間（1 H）（時間 T 5 ~ T 10）で行った第1閾値補正期間（V T C 1）と第1待機期間（W A T 1）と同様な処理、即ち、第2閾値補正期間（V T C 2）と第2待機期間（W A T 2）を実行する。

ただし、第1閾値補正期間（V T C 1）が開始された時間 T 5 においてはゲートソース

50

間電圧  $V_{gs}$  (保持キャパシタ  $C_s$  の保持電圧) が “ $V_o - V_{ccc\_L}$ ” と比較的大きい値であったのに対し、第2閾値補正期間 ( $VT_{C2}$ ) が開始される時間  $T_{10}$ において当該保持電圧が、より小さい “ $V_{x1}$ ” に縮まっている。

#### 【0082】

図4(B1)に示すように時間  $T_{10}$ でサンプリングパルス ( $SP_2$ ) が立ち上がり、サンプリングトランジスタ  $M_s$  がオンすると、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  ( $= "V_o + V_{a1}"$ ) がより低い電位 (データ基準電位  $V_o$ ) の映像信号線  $D_{TL}(j)$  に接続される。このため、その差分 ( $V_{a1}$ ) に相当する電流が駆動トランジスタ  $M_d$  のゲートから映像信号線  $D_{TL}(j)$  に流れ、図6(C)に示すようにゲート電圧  $V_g$  がデータ基準電位  $V_o$  にまで強制的に下げられる。

10

この駆動トランジスタ  $M_d$  のゲートにおける電位 ( $V_{a1}$ ) の変動は、保持キャパシタ  $C_s$ 、および、駆動トランジスタ  $M_d$  のゲートソース間寄生容量  $C_{gs}$  を介して駆動トランジスタ  $M_d$  のソースに入力され、ソース電位  $V_s$  がプルダウンされる。

このときのソース電位  $V_s$  のプルダウン量は、容量結合比  $g$  を用いて “ $g * V_{a1}$ ” と表される。ここで容量結合比  $g$  は、上記ゲートソース間寄生容量  $C_{gs}$ 、保持キャパシタ  $C_s$  と同一符号のその容量値 ( $C_s$ )、有機発光ダイオード OLEd の容量  $C_{oled}$  を用いて、 $g = (C_{gs} + C_s) / (C_{gs} + C_s + C_{oled})$  と表される。よって、ソース電位  $V_s$  は、直前の “ $V_o - V_{x1} + V_{a1}$ ” から “ $g * V_{a1}$ ” だけ低下し、“ $V_o - V_{x1} + (1 - g) V_{a1}$ ” となる。

容量結合比  $g$  は定義式から明らかのように 1 より小さい値をとるため、ソース電位  $V_s$  の変化量 “ $g * V_{a1}$ ” は、ゲート電圧  $V_g$  の変化量 ( $V_{a1}$ ) より小さい。

20

#### 【0083】

ここで、駆動トランジスタのゲートソース間電圧  $V_{gs}$  ( $= "V_{x1} - (1 - g) V_{a1}"$ ) が駆動トランジスタ  $M_d$  の閾値電圧  $V_{th}$  よりも大きければ、図6(C)のように、ドレイン電流  $I_{ds}$  が流れる。ドレイン電流  $I_{ds}$  は、駆動トランジスタ  $M_d$  のソース電位  $V_s$  が “ $V_o - V_{th}$ ” となって駆動トランジスタ  $M_d$  がカットオフするまで流れようとする。しかし、本実施形態の動作例では、図4(E)および図4(F)に示すように、ゲートソース間電圧  $V_{gs}$  が “ $V_{x2}$ ” (但し  $V_{x2}$  は、 $V_{x1} > V_{x2} > V_{th}$  を満たす大きさを有する) となった時間  $T_{12}$  でサンプリングパルス ( $SP_2$ ) が終了するため、サンプリングトランジスタ  $M_s$  がオフする。時間  $T_{12}$  における、保持キャパシタ  $C_s$  の保持電圧は “ $V_{x2}$ ” である。

30

#### 【0084】

##### [ 第2待機期間 (WAT2) ]

時間  $T_{12}$  から第2待機期間 (WAT2) が開始する。

第2待機期間 (WAT2) では、前回の第1待機期間 (WAT1) と同様に、サンプリングトランジスタ  $M_s$  がオフしてゲート電圧  $V_g$  が電気的にフローティング状態となるため、ソース電位  $V_s$  の上昇に応じてゲート電圧  $V_g$  も上昇する (図7(A) 参照)。

しかし、ゲート電圧  $V_g$  の電位上昇効果 (ブーストストラップ効果) は、その開始時点のゲートソース間電圧  $V_{gs}$  が制御目標 “ $V_{th}$ ” に近いため余り大きくなく、図4(E)および図4(F)の時間  $T_{12} \sim T_{15}$  に見られるように、ソース電位  $V_s$  およびゲート電圧  $V_g$  の電位上昇幅は僅かである。

40

#### 【0085】

より詳細には、図7(A)の第2待機期間 (WAT2)において、ドレイン電流  $I_{ds}$  が流れることによるソース電位  $V_s$  の上昇分を “ $V_{a2}$ ” とすると、待機期間終了時 (図4の時間  $T_{15}$ ) におけるソース電位  $V_s$  は “ $V_o - V_{x2} + V_{a2}$ ” となる。このソース電位が “ $V_{a2}$ ” だけ上昇することは、ゲートソース間寄生容量  $C_{gs}$  および保持キャパシタ  $C_s$  を介して、フローティング状態のゲートに伝達され、その結果、ゲート電圧  $V_g$  もほぼ同じ電位 “ $V_{a2}$ ” だけ上昇する。ただし、ゲート電圧  $V_g$  の電位上昇分 “ $V_{a2}$ ” は、図4(E)に示すように、第1待機期間 (WAT1) における電位上昇分 “ $V_{a1}$ ” より遥かに小さいものである。

50

## 【0086】

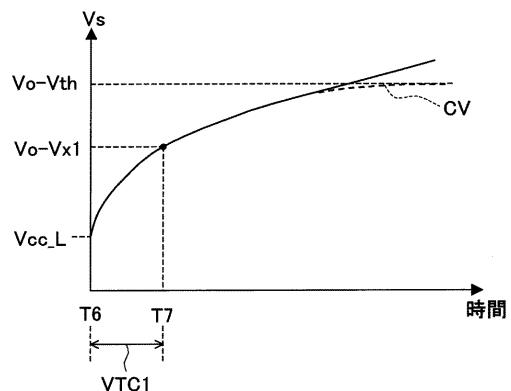

## [第3閾値補正(VTC3)]

時間T15から「本動作」に入り、第3閾値補正(VTC3)が開始する。

第3閾値補正(VTC3)(時間T15～T17)では、第2閾値補正期間(VTC2)と同様な処理を実行する。

ただし、第2閾値補正期間(VTC2)が開始された時間T10においてはゲートソース間電圧Vgs(保持キャパシタCsの保持電圧)が“Vx1”と比較的大きい値であったのに対し、第3閾値補正期間(VTC3)が開始される時間T15においては、さらに小さい“Vx2”に縮まっている。

動作の基本は[第2閾値補正期間(VTC2)]の繰り返しになるので割愛する。[第2閾値補正期間(VTC2)]の説明は、“Va1”を“Va2”に、“Vx1”を“Vx2”に置き換えることによって、当該第3閾値補正(VTC3)に適用できる。このことは図6(C)と図7(B)との対比でも明らかである。10

## 【0087】

ただし、第2閾値補正期間(VTC2)と異なるのは、第3閾値補正(VTC3)が終了する時間T17までには、図4(E)および図4(F)に示すように、駆動トランジスタMdのゲートソース間電圧Vgs(保持キャパシタCsの保持電圧)が、閾値電圧Vthと等しくなることである。このため、駆動トランジスタMdは、ゲートソース間電圧Vgsが閾値電圧Vthと等しくなったところでカットオフし、それ以後、ドレイン電流IdSが流れなくなる。このときの駆動トランジスタMdのソース電位Vsは“Vo-Vth”である。20

## 【0088】

以上のように待機期間を間に挟んだ複数回(本例では3回)に亘る閾値電圧補正によって、保持キャパシタCsの保持電圧は、これが一定となる待機期間を間に挟んでステップ状に収束し、最終的には閾値電圧Vthとなる。

ここで仮に、駆動トランジスタのゲートソース間電圧が“Vin”だけ大きくなつたとすると、ゲートソース間電圧は“Vin+Vth”となる。また、閾値電圧Vthが大きい駆動トランジスタと、これが小さい駆動トランジスタを考える。

前者の閾値電圧Vthが大きい駆動トランジスタは、閾値電圧Vthが大きい分だけゲートソース間電圧が大きく、逆に閾値電圧Vthが小さい駆動トランジスタは、閾値電圧Vthが小さいためゲートソース間電圧が小さくなる。よって、閾値電圧Vthについていえば、閾値電圧補正動作により、そのバラツキをキャンセルして、同じデータ電圧Vinなら同じドレイン電流IdSを駆動トランジスタに流すことができる。30

## 【0089】

なお、3回に亘る閾値補正期間、すなわち、第1閾値補正期間(VTC1)、第2閾値補正期間(VTC2)および第3閾値補正(VTC3)においては、ドレイン電流IdSが専ら保持キャパシタCsの一方電極側、有機発光ダイオードOLEDの容量Coled.の一方電極側に流入することにのみ消費され、有機発光ダイオードOLEDがオンしないようにする必要がある。有機発光ダイオードOLEDのアノード電圧を“Volled.”、その閾値電圧を“Vtholed.”、そのカソード電位を“Vcath”と表記すると、有機発光ダイオードOLEDをオフ状態に維持する条件は、“Volled.-Vcath+Vtholed.”が常に成り立つことである。40

ここで有機発光ダイオードOLEDのカソード電位Vcathを基準電圧VSS(例えば接地電圧GND)で一定とした場合、発光閾値電圧Vtholed.が非常に大きいときは、この式を常に成立させることも可能である。しかし、発光閾値電圧Vtholed.は有機発光ダイオードOLEDの作製条件で決まり、また、低電圧で効率的な発光のためには発光閾値電圧Vtholed.を余り大きくできない。よって、望ましくは、3度の閾値補正期間、および、次に述べる移動度補正期間が終了するまでは、カソード電位Vcathを低電位VccLより小さく設定することによって、有機発光ダイオードOLEDを逆バイアスさせておくとよい。50

## 【0090】

## [第3待機期間(WAT3)]

以上は閾値電圧補正についての説明であるが、本動作例では、続いて“書き込み＆移動度補正”のための待機期間(第3待機期間(WAT3))が開始する。第3待機期間(WAT3)は、今までの閾値電圧補正のための第1待機期間(WAT1)および第2待機期間(WAT2)とは異なり、単に、その後に行う“書き込み＆移動度補正”時に、映像信号Ssigの電位変化の不安定な箇所を誤ってサンプリングしないように待機する短い待機期間である。

## 【0091】

図4(B1)に示すように、時間T17でサンプリングパルス(SP3)が“H”レベルから“L”レベルに遷移すると、ここから第3待機期間(WAT3)が開始する。10

第3待機期間(WAT3)では、その途中の時間T18で、図4(A)に示すように、当該画素回路3(1,j)で表示すべきデータ電位Vsigをもつ映像信号パルス(PPx)が、映像信号Ssigとして映像信号線DTL(j)に供給される(図9(A)参照)。映像信号Ssigにおいて、データ電位Vsigとデータ基準電位Voの差分が、当該画素回路で表示すべき階調値に対応するデータ電圧Vinに相当する。つまり、データ電位Vsigは“Vo + Vin”に等しい。

時間T18で行われた電位変化から時間が経って、映像信号Ssigがデータ電位Vsigで安定した時間T19で、当該第3待機期間(WAT3)が終了する。

## 【0092】

## [書き込み＆移動度補正期間(W&amp;μ)]

時間T19から、書き込み＆移動度補正期間(W&μ)が開始する。

図4(B1)に示すように、本動作時の映像信号パルス(PPx)を印加中の時間T19で、書き込みパルス(WP)がサンプリングトランジスタMsのゲートに供給される。すると、図9(B)に示すように、サンプリングトランジスタMsがオンし、映像信号線DTL(j)のデータ電位Vsig(=Vo + Vin)のうち、ゲート電圧Vg(=Vo)との差分、すなわち、データ電圧Vinが、駆動トランジスタMdのゲートに入力される。この結果、ゲート電圧Vgが“Vo + Vin”となる。

ゲート電圧Vgがデータ電圧Vinだけ上昇すると、これに連動してソース電位Vsも上昇する。このとき、データ電圧Vinがそのままソース電位Vsに伝達される訳ではなく、前述した容量結合比gに応じた比率の変化分、すなわち、“g \* Vin”だけソース電位Vsが上昇する。よって、変化後のソース電位Vsは、“Vo - Vth + g \* Vin”となる。その結果、駆動トランジスタMdのゲートソース間電圧Vgsは、“(1 - g) Vin + Vth”となる。

## 【0093】

ここで、移動度μによるバラツキについて説明する。

今までの3度の閾値電圧補正で、実は、ドレイン電流Idsを流すたびに移動度μによる誤差が含まれていたものの、閾値電圧Vthのバラツキが大きいため移動度μによる誤差成分を厳密に議論しなかった。このとき容量結合比gを用いずに、単に結果だけを示す電圧を新たに“Va1”や“Va2”により表記して説明したのは、移動度のバラツキを説明することによる煩雑さを回避するためである。40

一方、既に説明したことであるが、厳密に閾値電圧補正が行われた後は、そのとき保持キャパシタCsに閾値電圧Vthが保持されているため、その後、駆動トランジスタMdをオンさせると、閾値電圧Vthの大小によってドレイン電流Idsが変動しない。そのため、この閾値電圧補正後の駆動トランジスタMdの導通で、仮に、当該導通時の駆動電流Idによって保持キャパシタCsの保持電圧(ゲートソース間電圧Vgs)の値に変動が生じたとすると、その変動量V(正または負の極性をとることが可能)は、駆動トランジスタMdの移動度μのバラツキ、より厳密には、半導体材料の物性パラメータである純粋な意味での移動度のほかに、トランジスタの構造上あるいは製造プロセス上で電流駆動力に影響を与える要因の総合的なバラツキを反映したものとなる。

10

20

30

40

50

## 【0094】

以上のことと踏まえた上で説明を戻すと、図9(B)において、サンプリングトランジスタM<sub>s</sub>がオンしてゲート電圧V<sub>g</sub>にデータ電圧V<sub>in</sub>が加わったときに、駆動トランジスタM<sub>d</sub>は、そのデータ電圧V<sub>in</sub>(階調値)に応じた大きさのドレイン電流I<sub>ds</sub>をソースドレイン間に流そうとする。このときドレイン電流I<sub>ds</sub>が移動度μに応じてばらつき、その結果、ソース電位V<sub>s</sub>は、“V<sub>o</sub>-V<sub>th</sub>+g\*V<sub>in</sub>”に上記移動度μによる変動量Vを加えた“V<sub>o</sub>-V<sub>th</sub>+g\*V<sub>in</sub>+V”となる。

## 【0095】

このとき有機発光ダイオードOLEDを発光させないためには、“V<sub>s</sub>(=V<sub>o</sub>-V<sub>th</sub>+g\*V<sub>in</sub>+V)<V<sub>tholed.</sub>+V<sub>cath</sub>”が満たされるように、データ電圧V<sub>in</sub>や容量結合比g等に応じたカソード電位V<sub>cath</sub>を予め設定するとよい。10

この設定を予め行っていると、有機発光ダイオードOLEDは逆バイアスされ、ハイインピーダンス状態にあるため発光することではなく、また、ダイオード特性ではなく単純な容量特性を示すようになる。

このとき上記条件式が満たされている限り、ソース電位V<sub>s</sub>が、有機発光ダイオードOLEDの発光閾値電圧V<sub>tholed.</sub>とカソード電位V<sub>cath</sub>との和を越えないため、ドレイン電流I<sub>ds</sub>(駆動電流I<sub>d</sub>)は保持キャパシタC<sub>s</sub>の容量値C<sub>s</sub>と、有機発光ダイオードOLEDの逆バイアス時等価容量値C<sub>oled.</sub>と、駆動トランジスタM<sub>d</sub>のゲートソース間に存在する寄生容量(C<sub>gs</sub>と表記)とを加算した容量“C=C<sub>s</sub>+C<sub>oled.</sub>+C<sub>gs</sub>”を充電するために用いられる。これにより、駆動トランジスタM<sub>d</sub>のソース電位V<sub>s</sub>は上昇していく。このとき、駆動トランジスタM<sub>d</sub>の閾値補正動作は完了しているため、駆動トランジスタM<sub>d</sub>が流すドレイン電流I<sub>ds</sub>は移動度μを反映したものとなる。20

## 【0096】

図4(E)および図4(F)で“(1-g)V<sub>in</sub>+V<sub>th</sub>-V”的式により示しているように、保持キャパシタC<sub>s</sub>に保持されるゲートソース間電圧V<sub>gs</sub>においては、ソース電位V<sub>s</sub>に加わる変動量Vが閾値補正後のゲートソース間電圧V<sub>gs</sub>(=(1-g)V<sub>in</sub>+V<sub>th</sub>)から差し引かれることになるため、負帰還がかかるように当該変動量Vが保持キャパシタC<sub>s</sub>に保持される。よって、以下、変動量Vを「負帰還量」ともいう。

この負帰還量Vは、有機発光ダイオードOLEDに逆バイアスをかけた状態では、“C<sub>oled.</sub>>>C<sub>s</sub>+C<sub>gs</sub>”が成り立つので、V=t\*I<sub>ds</sub>/(C<sub>oled.</sub>+C<sub>s</sub>+C<sub>gs</sub>)という概算式で表すことができる。この概算式から、変動量Vは、ドレイン電流I<sub>ds</sub>の変動に比例して変化するパラメータであることが分かる。30

上記負帰還量Vの概算式から、ソース電位V<sub>s</sub>に付加される負帰還量Vは、ドレイン電流I<sub>ds</sub>の大きさ(この大きさは、データ電圧V<sub>in</sub>の大きさ、即ち階調値と正の相関関係にある)と、ドレイン電流I<sub>ds</sub>が流れる時間、すなわち、図4(B1)に示す、移動度補正に要する時間T19から時間T20までの時間(t)に依存している。つまり、階調値が大きいほど、また、時間(t)を長くとるほど、負帰還量Vが大きくなる。

したがって、移動度補正の時間(t)は必ずしも一定である必要はなく、逆にドレイン電流I<sub>ds</sub>(階調値)に応じて調整することが好ましい場合がある。たとえば、白表示に近くドレイン電流I<sub>ds</sub>が大きい場合、移動度補正の時間(t)は短めにし、逆に、黒表示に近くなりドレイン電流I<sub>ds</sub>が小さくなると、移動度補正の時間(t)を長めに設定するとよい。この階調値に応じた移動度補正時間の自動調整は、その機能を図2に示す書き込み信号走査回路42等に予め設けることにより実現可能である。40

## 【0097】

## [発光期間(LM1)]

時間T20で書き込み&移動度補正期間(W&μ)が終了すると、発光期間(LM1)が開始する。

時間T20で書き込みパルス(WP)が終了するためサンプリングトランジスタM<sub>s</sub>がオフし、駆動トランジスタM<sub>d</sub>のゲートが電気的にフローティング状態となる。

## 【0098】

10

20

30

40

50

ところで、発光期間（LM1）より前の書込み＆移動度補正期間（W & μ）においては、駆動トランジスタM<sub>d</sub>はデータ電圧V<sub>in</sub>に応じたドレイン電流I<sub>ds</sub>を流そうとするが、実際に流せるとは限らない。その理由は、有機発光ダイオードOLEDに流れる電流値（I<sub>d</sub>）が駆動トランジスタM<sub>d</sub>に流れる電流値（I<sub>ds</sub>）に比べて非常に小さいなら、サンプリングトランジスタM<sub>s</sub>がオンしているため、駆動トランジスタM<sub>d</sub>のゲート電圧V<sub>g</sub>が“V<sub>o</sub> + V<sub>in</sub>”に固定され、そこから閾値電圧V<sub>th</sub>分下がった電位（“V<sub>o</sub> + V<sub>in</sub> - V<sub>th</sub>”）にソース電位V<sub>s</sub>が収束しようとするからである。よって、移動度補正の時間（t）を幾ら長くしてもソース電位V<sub>s</sub>は上記収束点を超える電位にはなれない。移動度補正是、その収束までの速さの違いで移動度μの違いをモニタし、補正するものである。このため、最大輝度の白表示のデータ電圧V<sub>in</sub>が入力された場合でも、上記収束になる前に移動度補正の時間（t）の終点が決められる。

10

## 【0099】

発光期間（LM1）が開始して駆動トランジスタM<sub>d</sub>のゲートがフローティングとなると、そのソース電位V<sub>s</sub>は、さらに上昇可能となる。よって、駆動トランジスタM<sub>d</sub>は、入力されたデータ電圧V<sub>in</sub>に応じた駆動電流I<sub>d</sub>を流すように動作する。

その結果、ソース電位V<sub>s</sub>（有機発光ダイオードOLEDのアノード電位）が上昇し、やがて、有機発光ダイオードOLEDの逆バイアス状態が解消され、図9（C）に示すように、ドレイン電流I<sub>ds</sub>が駆動電流I<sub>d</sub>として有機発光ダイオードOLEDに流れ始めるため、有機発光ダイオードOLEDが実際に発光を開始する。発光が開始して暫くすると、駆動トランジスタM<sub>d</sub>は、入力されたデータ電圧V<sub>in</sub>に応じたドレイン電流I<sub>ds</sub>で飽和し、ドレイン電流I<sub>ds</sub>（= I<sub>d</sub>）が一定となると、有機発光ダイオードOLEDがデータ電圧V<sub>in</sub>に応じた輝度の発光状態となる。

20

## 【0100】

発光期間（LM1）の開始から輝度が一定となるまでの間に生じる有機発光ダイオードOLEDのアノード電位の上昇は、駆動トランジスタM<sub>d</sub>のソース電位V<sub>s</sub>の上昇に他ならず、これを、有機発光ダイオードOLEDのアノード電圧V<sub>oled</sub>の上昇量という意味で“V<sub>oled</sub>”とする。駆動トランジスタM<sub>d</sub>のソース電位V<sub>s</sub>は、“V<sub>o</sub> - V<sub>th</sub> + g \* V<sub>in</sub> + V<sub>+</sub> V<sub>oled</sub>”となる（図4（F）参照）。

一方、ゲート電圧V<sub>g</sub>は、図4（E）に示すように、フローティング状態であるためソース電位V<sub>s</sub>に連動して、その上昇量V<sub>oled</sub>と同じだけ上昇し、ドレイン電流I<sub>ds</sub>の飽和に伴ってソース電位V<sub>s</sub>が飽和すると、ゲート電圧V<sub>g</sub>も飽和する。

30

その結果、ゲートソース間電圧V<sub>gs</sub>（保持キャパシタC<sub>s</sub>の保持電圧）について、移動度補正時の値（“(1 - g)V<sub>in</sub> + V<sub>th</sub> - V”）が、発光期間（LM1）中も維持される。

## 【0101】

発光期間（LM1）においては、駆動トランジスタM<sub>d</sub>が定電流源として動作することから、有機発光ダイオードOLEDのI-V特性が経時変化し、これに伴って駆動トランジスタM<sub>d</sub>のソース電位V<sub>s</sub>が変化することがある。

しかしながら、有機発光ダイオードOLEDのI-V特性が経時変化の有無に関係なく、保持キャパシタC<sub>s</sub>の保持電圧が“(1 - g)V<sub>in</sub> + V<sub>th</sub> - V”に保たれる。そして、保持キャパシタC<sub>s</sub>の保持電圧は、駆動トランジスタM<sub>d</sub>の閾値電圧V<sub>th</sub>を補正する成分（+V<sub>th</sub>）と、移動度μによる変動を補正する成分（-V）とを含むことから、閾値電圧V<sub>th</sub>や移動度μが、異なる画素間でばらついても駆動トランジスタM<sub>d</sub>のドレイン電流I<sub>ds</sub>、つまり、有機発光ダイオードOLEDの駆動電流I<sub>d</sub>が一定に保たれる。

40

## 【0102】

具体的には、駆動トランジスタM<sub>d</sub>は、閾値電圧V<sub>th</sub>が大きいほど、上記保持電圧の閾値電圧補正成分（+V<sub>th</sub>）によってソース電位V<sub>s</sub>を下げて、ドレイン電流I<sub>ds</sub>（駆動電流I<sub>d</sub>）をより流すようにソースドレイン間電圧を大きくする。このため閾値電圧V<sub>th</sub>の変動があってもドレイン電流I<sub>ds</sub>は一定となる。

また、駆動トランジスタM<sub>d</sub>は、移動度μが小さくて上記変動量Vが小さい場合は、

50

保持キャパシタ  $C_s$  の保持電圧の移動度補正成分 ( $-V$ ) によって当該保持電圧の低下量も小さくなるため、相対的に、大きなソースドレイン間電圧が確保され、その結果、ドレイン電流  $I_{ds}$  (駆動電流  $I_d$ ) をより流すように動作する。このため移動度  $\mu$  の変動があってもドレイン電流  $I_{ds}$  は一定となる。

#### 【0103】

以上より、画素間で駆動トランジスタ  $M_d$  の閾値電圧  $V_{th}$  や移動度  $\mu$  がばらついても、さらに、駆動トランジスタ  $M_d$  の特性が経時変化しても、データ電圧  $V_{in}$  が同じである限り、有機発光ダイオード  $OLED$  の発光輝度も一定に保たれる。

#### 【0104】

##### <補助キャパシタ>

以上の発光制御の書き込み & 移動度補正期間 ( $W & \mu$ )において、図4(E)および図4(F)に示すように、駆動トランジスタ  $M_d$  のゲート電圧  $V_g$  に書き込まれたデータ電圧  $V_{in}$  がそのまま保持キャパシタ  $C_s$  の保持電圧に追加されるのではなく、データ電圧  $V_{in}$  から  $(g * V_{in})$ だけ下がったデータ電圧 “ $(1 - g) V_{in}$ ” が保持キャパシタ  $C_s$  の保持電圧に追加される。このため容量結合比  $g$  に相当する書き込みゲインのロスが発生し、これが表示画面で所望の明るさが得られない原因となる。

容量結合比  $g$  は “ $g = (C_{gs} + C_s) / (C_{gs} + C_s + C_{oled.})$ ” と表されるが、その分母が大きいほうが書き込みゲインのロスも小さくなり好ましい。そこで、特開2007-102046号公報(特許文献1)では、有機発光ダイオード  $OLED$  と並列に補助キャパシタ  $C_{sub}$  を接続した画素回路構成を提案している。十分大きな補助キャパシタ  $C_{sub}$  を付加すると容量結合比  $g$  は、“ $g = (C_{gs} + C_s) / (C_{gs} + C_s + C_{oled.} + C_{sub})$ ” となってゼロに近づき、その分、書き込みゲインが向上する。

#### 【0105】

ところで、移動度補正で駆動トランジスタ  $M_d$  のソースにおける容量を大きくすると、ソース電位  $V_s$  の充電がゆっくりとなる。駆動トランジスタ  $M_d$  の駆動能力は高く設定されているため、所定の時間 ( $t$ ) 内にソース電位  $V_s$  の充電が早すぎる場合がある。この充電が早すぎると時間 ( $t$ ) 内にソース電位  $V_s$  の上昇カーブが飽和してしまい、移動度補正の精度が低下する。この所定時間内の飽和を防止して移動度補正精度を高くする意味でも、補助キャパシタ  $C_{sub}$  の追加は望ましい。

#### 【0106】

特許文献1では、補助キャパシタ  $C_{sub}$  を、駆動トランジスタ  $M_d$  のソースとカソード電位  $V_{cath}$  の供給線との間に接続している。通常、カソード電位  $V_{cath}$  は有機発光ダイオード  $OLED$  を逆バイアスする程度に低い負電位に設定されるが、補助キャパシタ  $C_{sub}$  の一方電極をカソード電位  $V_{cath}$  で固定するよりも、電源走査線  $D_{SL}(i)$  の高電位  $V_c$  \_H で固定する方が、補助キャパシタ  $C_{sub}$  の実使用時の容量値(電荷蓄積能力)を高くできるため好ましい。しかし、同じ画素回路内の電源走査線  $D_{SL}(i)$  に補助キャパシタ  $C_{sub}$  を接続すると、閾値電圧補正に支障をきたすため、本願発明者は、特願2006-209327号の画素回路構成(以下、単に先願という)を提案している。

#### 【0107】

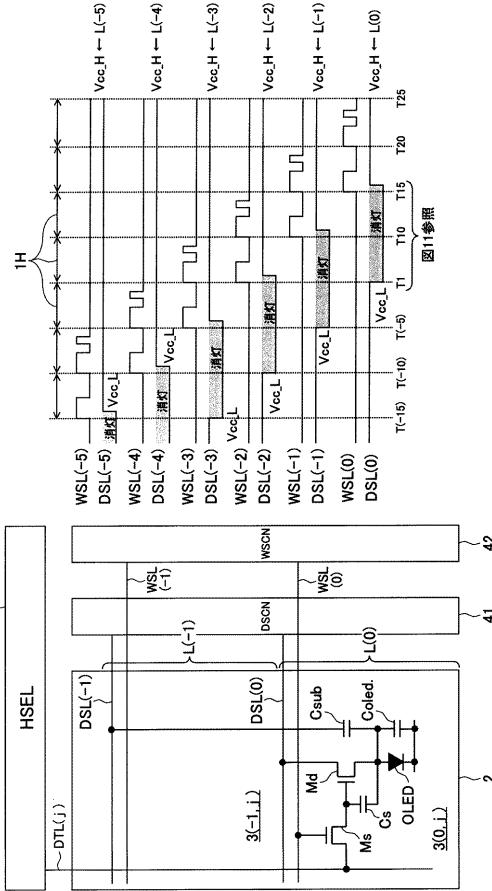

図10に、先願の画素回路を、列方向に隣接する2つの画素において示す。

図10に図解する画素回路  $3(2,j)$  は、図2に示す画素回路  $3(i,j)$  と比較すると、補助キャパシタ  $C_{sub}$  が追加されていることが異なる。補助キャパシタ  $C_{sub}$  は、画素回路  $3(2,j)$  における駆動トランジスタ  $M_d$  のソース(以下、ソースノード  $N_{Ds}$  とも言う)と、隣接する1行前の画素回路  $3(1,j)$  の電源走査線  $D_{SL}(1)$  との間に接続されている。このことは1行前の画素回路  $3(1,j)$  においても同様である。なお、有機発光ダイオード  $OLED$  の容量  $C_{oled.}$  は逆バイアス時のダイオード等価容量であるため回路素子でないが、便器上、当該回路に記載している。

#### 【0108】

##### <他の発光制御例>

以下、図10に示す画素回路構成における不具合を、図11に示す他の発光制御例で説

明する。

図11(A)～図11(D)に示すタイミングチャートでは、図4では示していた他の表示ラインのパルス波形を省略し、また、最初の1水平期間(1H)内に初期化と第1閾値補正を連続して行っているが、この点は本質的なものでなく、図4においても採用可能な制御である。

基本的な制御は図11と図4で共通し、同じ符号を付して表示する。なお、符号“T1'”は、時間T1より若干前であることを意味する。また、図11においては時間軸上の同じ位置で示している2つの時間、すなわちT7とT8、T9とT10、T12とT13、T14とT15、T17とT18は、数字が小さい時間が大きい時間より時間軸上で若干前であることが望ましいことを意味する。

10

#### 【0109】

図11では、最初の1水平期間(1H)内に初期化と第1閾値補正を連続して行っているため、速やかなディスチャージが必要である。よって、電源走査線DSLの低電位Vcc\_Lを、通常、比較的大きな負電位に設定する。高電位Vccc\_Hは書き込み、移動度補正および発光に必要な高い正電位である。よって、図11のような速やかな放電を行う必要がある場合、電源走査線DSLのパルス波高値(Vccc\_H - Vcc\_L)は大きく設定されることがある。

#### 【0110】

< Csubを前段のDSL接続とした場合の不具合 >

図12(A)は、図10の一つの画素について着目した図であり、図12(B)は、発光時間を制御したときのタイミングを着目した画素を含む画素行(表示ライン)から、5段前の表示ラインまで概略的に示す図である。

20

ここで着目した画素を含む表示ラインを、“着目表示ラインL(0)”と表記し、着目表示ラインL(0)より1水平期間(1H)前に表示制御される表示ラインを“表示ラインL(-1)”、2H前に表示制御される表示ラインを“表示ラインL(-2)”、以下同様に、3H, 4H, 5H前に表示制御される表示ラインをそれぞれ“表示ラインL(-3)”、“表示ラインL(-4)”、“表示ラインL(-5)”と表記する。

このように行を示す符号(i)を0以下に拡張し、この符号を用いて電源走査線DSL(i)と書き走査線WSL(i)を表している。

#### 【0111】

図12(B)に示す時間T1, T10, T15は、図11に示す表示制御に対応するため、この間に図4で説明した処理が実行される。

30

図12(B)において、電源走査線DSL(i)(i=0, -1, -2, -3, -4, -5)が低電位Vcc\_Lに遷移している期間が消灯時間、高電位Vccc\_Hの期間が発光(許可)期間である。

また、図12(B)には示していないが、書き走査線WSL(i)は、高電位Vwshと低電位Vws\_Lとの2値電位をとる(図11(B2)参照)。

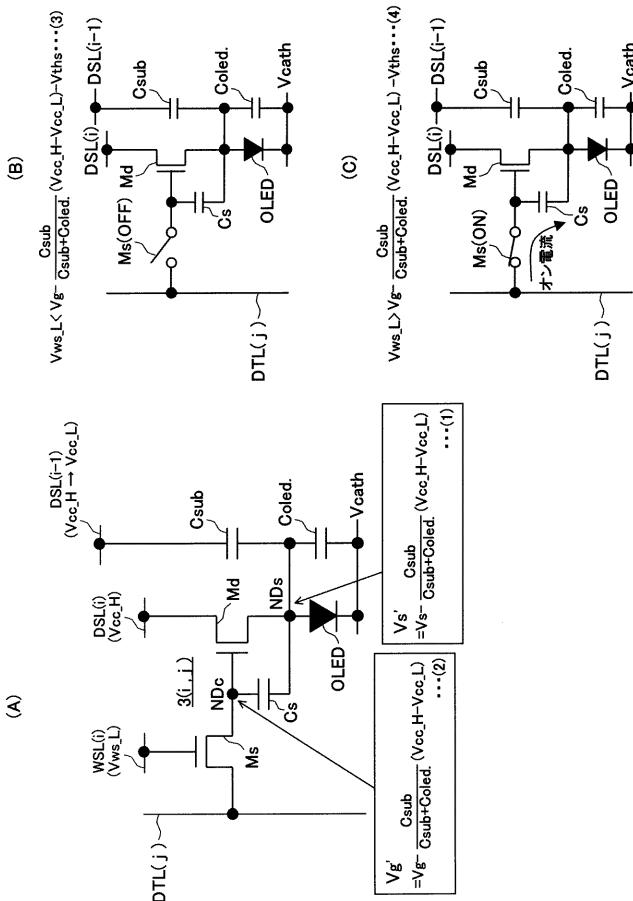

#### 【0112】

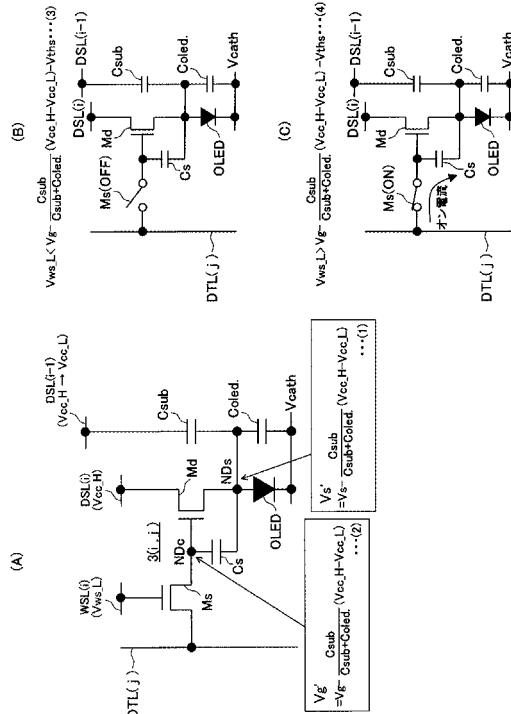

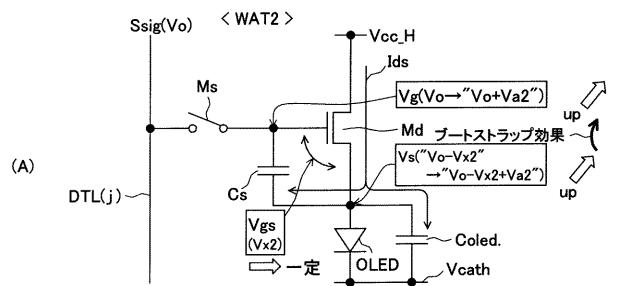

図13(A)には、前段の画素回路3(i-1, j)が消灯しており、かつ、自段の画素回路3(i, j)が発光しているときの画素回路3(i, j)の制御ノードNDcとソースノードNDSの電位を式(1)と式(2)により示している。

40

前段の電源走査線DSL(i-1)電源供給線が高電位Vccc\_Hから低電位Vcc\_Lに遷移したとき、この電位変化に起因した電位変動が、補助キャパシタCsubを介して、駆動トランジスタM\_dのソースノードNDSに入る。このときのノードNDの電位は、図13(A)に示す式(1)から分かるように、元のソース電位Vsから、有機EL容量Cole\_d.と補助容量Csubの容量比により“(Vccc\_H - Vcc\_L)Csub / (Csub + Cole\_d.)”だけ下がったソース電位Vs'にまで変動する。ただし、この式(1)の右辺は電位変動のピークを示し、時間がたつと電位変動が収束して消滅する。

#### 【0113】

発光状態の画素回路3(i, j)においては、サンプリングトランジスタMsのゲートに印

50

加される低電位  $V_{ws\_L}$  によってサンプリングトランジスタ  $M_s$  がオフし、駆動トランジスタ  $M_d$  のゲート（制御ノード  $N_{Dc}$ ）は電気的にフローティング状態となっている。そのため、ソースノード  $N_{Ds}$  に発生した電位変動が保持キャパシタ  $C_s$  等を介して制御ノード  $N_{Dc}$  に伝わり、その電位を揺らす。

制御ノード  $N_{Dc}$  の電位は、入力されるデータ電圧  $V_{in}$  に応じて既に設定されたゲート電圧  $V_g$  から、保持キャパシタ  $C_s$  の保持特性により “ $(V_{cc\_H} - V_{cc\_L}) C_{sub} / (C_{sub} + C_{oled.})$ ” だけ下がったゲート電圧  $V_g'$ （最小値）にまで変動する。この電位変動も時間がたつと収束して消滅する。

#### 【0114】

<  $V_{ws\_L}$  の条件式 >

このようにして電位変動を受けた制御ノード電位（駆動トランジスタ  $M_d$  のゲート電圧  $V_g'$ ）が、サンプリングトランジスタ  $M_s$  のゲート電位（低電位  $V_{ws\_L}$ ）から、サンプリングトランジスタ  $M_s$  の閾値電圧  $V_{ths}$  だけ下がった場合にはサンプリングトランジスタ  $M_s$  がオンする。

このことを図 13 (B) と図 13 (C) の式(3)と式(4)に示す。

#### 【0115】

ただし、サンプリングトランジスタ  $M_s$  のソース電位がゲート電位と同じであればリーク電流は発生しないが、ソース電位がゲート電位より低くなるとオンしない場合でもオフリーク電流が画質に影響する程度まで急激に大きくなる。

よって、式(3)の右辺から、サンプリングトランジスタ  $M_s$  の閾値電圧  $V_{ths}$  の項を削除した、以下の式(5)が満たされれば、画質に影響する比較的大きなリーク電流とオン電流を含む電流が、サンプリングトランジスタ  $M_s$  に流れることはない。

#### 【0116】

$$V_{ws\_L} < V_g - (V_{cc\_H} - V_{cc\_L}) C_{sub} / (C_{sub} + C_{oled.}) \dots (5)$$

#### 【0117】

以上から、上記式(5)を満たすように、書き走査線  $W_{SL}$  の低電位  $V_{ws\_L}$  が決められる。この低電位  $V_{ws\_L}$  および高電位  $V_{ws\_H}$  の値を決めるのは、図 12 等に示す書き込み信号走査回路 42 であり、特に低電位  $V_{ws\_L}$  の値が上記式(5)を満たすことができるように、書き込み信号走査回路 42 が構成されている。

#### 【0118】

より詳細には、式(5)の右辺には、 $V_g$ ,  $V_{cc\_H}$ ,  $V_{cc\_L}$ ,  $C_{sub}$ ,  $C_{oled.}$  といった 5 つのパラメータを含む。

このうち高電位  $V_{cc\_H}$  は限られた時間のデータ書き込みと移動度補正に必要な観点等から値が決められる。

低電位  $V_{cc\_L}$  は限られた時間に有機発光ダイオード  $OLED$  を逆バイアスして速やかな放電を行う等の観点から値に決められる。

有機発光ダイオード  $OLED$  の容量  $C_{oled.}$  は、有機多層膜の開発で高効率、長寿命な作製条件が確定すると、画素における  $OLED$  の面積に依存して決まる値である。

補助キャパシタ  $C_{sub}$  は低電位  $V_{cc\_L}$  のレベルやデータ書き込み時間との兼ね合いにもよるが、主として、必要な書き込みゲインを得るために値に決められる。

ゲート電圧  $V_g$  は、映像信号線  $D_{TL}$  がとり得る電位範囲、即ちデータ基準電位  $V_o$  および黒から白までのデータ電位  $V_{sig}$  を含む範囲に応じて、これをサンプリングした電位範囲が分かるため、その電位範囲を考慮して変化させる。

#### 【0119】

以上のように、ゲート電圧  $V_g$  を除く、式(5)の右辺のパラメータは、プロセスやパターンの改良ごとに、種々の条件で変化するが、変化幅は比較的狭い。そしてプロセスやパターンの改良ごとに、これらのパラメータは、その値がほぼ確定する。

一方、ゲート電圧  $V_g$  については、映像信号線  $D_{TL}$  がとり得る電位範囲から正確に値がとり得る範囲が求まる。

水平画素ライン駆動回路 41 は、プロセスやパターンの改良ごとに、確定したパラメー

10

20

30

40

50

タを用い、かつ、ゲート電圧  $V_g$  が最大限変化しても常に式(5)が成り立つような低電位  $V_{ws\_L}$  を出力可能に設計されている。

なお、ゲート電圧  $V_g$  の最低値は通常、データ基準電位  $V_o$  で0[V]とする場合が多い。よって、この場合、低電位  $V_{ws\_L}$  は負の値をとる。

以上より、サンプリングトランジスタ  $M_s$  がオンすることによる大きな画質低下だけでなく、リーク電流による、例えば黒浮きのような画質低下まで防止できる。

#### 【0120】

本実施形態における変形例を述べる。

#### 【0121】

##### <変形例1>

水平画素ライン駆動回路41は、プロセスやパターンの改良ごとに、確定したパラメータを用い、かつ、ゲート電圧  $V_g$  が最大限変化しても常に、サンプリングトランジスタ  $M_s$  の閾値電圧  $V_{ths}$  を考慮した前記式(3)を満たすように、低電位  $V_{ws\_L}$  を出力可能に構成してもよい。

この場合、サンプリングトランジスタ  $M_s$  がオンしないため大きな画質低下は回避される。

#### 【0122】

##### <変形例2>

画素回路は図2や図10に示すものに限定されない。

図10に示すように補助キャパシタ  $C_{sub}$  を前段の電源走査線  $D_{SL}$  でなく、それより前に表示制御される他の電源走査線  $D_{SL}$  に接続してもよい。

図12(B)に示す場合、着目表示ライン  $L(0)$  が発光可能なときに、表示ライン  $L(-1)$  だけでなく、表示ライン  $L(-2)$  も消灯している期間があるため、この場合、補助キャパシタ  $C_{sub}$  を2段前の表示ライン  $L(-2)$  の電源走査線  $D_{SL}(-2)$  に接続してもよい。

消灯時間は、電源走査線  $D_{SL}$  のデューティ比により任意に決められ、それに応じて補助キャパシタ  $C_{sub}$  が接続可能な段の範囲も決められる。

#### 【0123】

##### <変形例3>

図2の画素回路ではデータ基準電位  $V_o$  は映像信号  $S_{sig}$  のサンプリングにより与えられるが、データ基準電位  $V_o$  を、別のトランジスタを介して駆動トランジスタ  $M_d$  のソースやゲートに与えることもできる。

図2の画素回路ではキャパシタは保持キャパシタ  $C_s$  のみであるが、他の保持キャパシタを、例えば駆動トランジスタ  $M_d$  のゲートと一定電圧線との間にもう1つ設けてよい。発光素子は有機発光ダイオード  $OLED$  に限定されず、他の自発光素子でもよい。

#### 【0124】

##### <変形例4>

画素回路が有機発光ダイオード  $OLED$  の発光と非発光を制御する駆動方法には、画素回路内のトランジスタを走査線により制御する方法と、電源電圧の供給線を駆動回路によりAC駆動する方法(電源AC駆動方法)とがある。

図2や図13の画素回路は、後者の電源AC駆動方法の一例であるが、この方法において有機発光ダイオード  $OLED$  のカソード側をAC駆動して駆動電流を流す、流さないを制御してもよい。

一方、前者の発光制御を走査線により制御する方法では、駆動トランジスタ  $M_d$  のドレン側、または、ソースと有機発光ダイオード  $OLED$  との間に、他のトランジスタを挿入し、そのゲートを電源駆動制御の走査線で駆動する。

#### 【0125】

##### <変形例5>

図4および図11に示す表示制御は、閾値補正期間( $VTC$ )を3回の補正で行っていたが、1回の補正、または、3回以外の複数回の連続した(初期化を間に挟まない)との意

味)処理によって閾値補正を行ってもよい。さらに、移動度補正を行ってからデータの書き込みを行う表示制御でもよい。その場合、データの書き込みに本発明を適用する、移動度補正に本発明を適用する、その両方に本発明を適用する、の何れも可能である。

#### 【0126】

本実施形態およびその変形例によれば、以下の効果がある。

図10のような画素回路構成では、特に黒表示の場合に、駆動トランジスタM<sub>d</sub>のゲート電位がより低いため、リーケを起こしやすい。映像信号線D<sub>T</sub>L(j)には常にデータ基準電位V<sub>o</sub>とデータ電位V<sub>sig</sub>が与えられ、データ電位V<sub>sig</sub>も常に変化している。このため、式(5)や式(3)が満たされないと、駆動トランジスタM<sub>d</sub>のゲートには映像信号線電位が漏れこむ。このとき、駆動トランジスタM<sub>d</sub>のゲートソース間電圧V<sub>gs</sub>は、黒レベル以上の電圧となり、これは黒浮きとして表れ、コントラストの低下となる。

また、サンプリングトランジスタM<sub>s</sub>が完全にオンする場合、その前に保持していたデータ電圧V<sub>in</sub>と、映像信号線D<sub>T</sub>Lのデータ電圧V<sub>in</sub>(=V<sub>o</sub>+V<sub>sig</sub>)が大きく異なると、その表示ラインは筋状の画面ノイズとして見え大きく画質が低下する。

#### 【0127】

本実施形態では、式(5)または式(3)を、ゲート電圧V<sub>g</sub>がどのような場合でも常に満たすように、低電位V<sub>w</sub><sub>s</sub>\_Lが決められているため、黒浮きを防止または抑制し高コントラストの画質を得ることができ、さらに大きな画質低下も防止できる。

#### 【図面の簡単な説明】

#### 【0128】

【図1】本発明の実施形態に関わる有機ELディスプレイの主要構成を示す図である。

【図2】本発明の実施形態に関わる画素回路の基本構成の一例と、その画素回路を制御する駆動回路部分を示す図である。

【図3】有機発光ダイオードの特性を表すグラフと式を示す図である。

【図4】本発明の実施形態に関わり、本発明を適用前の表示制御における各種信号や電圧の波形を示すタイミングチャートである。

【図5】図4の制御におけるV<sub>o</sub>サンプリングまでの動作説明図である。

【図6】図4の制御における第2閾値補正までの動作説明図である。

【図7】図4の制御における第3閾値補正までの動作説明図である。

【図8】本発明の実施形態に関わるソース電位の時間推移のグラフである。

【図9】図4の制御における発光期間までの動作説明図である。

【図10】本発明の実施形態の一例に関わる画素回路の構成と、その画素回路を制御する駆動回路部分を示す図である。

【図11】図10に示す隣接する2つの画素回路の配線配置と、それに対応した等価回路を示す図である。

【図12】本発明の実施形態において、消灯と発光の表示ライン間の推移を説明するための図である。

【図13】本発明の実施形態に関わり、電源走査線の電位変化による画素回路の電位変動を、式を用いて説明するための図である。

【図14】ノード背景技術(特許文献1)に記載された画素回路の等価回路図を、参照符号を一部変更して転記した図である。

#### 【符号の説明】

#### 【0129】

1...有機ELディスプレイ、2...画素アレイ、3...画素回路、4...Vスキャナ、5...Hスキャナ、41...水平画素ライン駆動回路、42...書き込み信号走査回路、OLED...有機発光ダイオード、M1...駆動トランジスタ、Ms...サンプリングトランジスタ、Cs...保持キャパシタ、Coled...有機発光ダイオードの容量、Csub...補助キャパシタ、NDc...制御ノード、NDs...ソースノード、WSL...書き込み走査線、DSL...電源走査線、DTL...映像信号線、Vs...データ電位、Vo...データ基準電位、Vws\_L...書き込み走査線の低電位、Vcc\_H...電源走査線の高電位、Vcc\_L...電源走査線の低電位、Vg...

ゲート電圧

【図3】

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} C_{ox} (V_{gs} - V_{th})^2$$

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(72)発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

F ター&ム(参考) 3K107 AA01 BB01 CC31 CC32 EE03 HH04 HH05

5C080 AA06 BB05 DD01 EE29 FF01 FF11 HH09 JJ02 JJ03 JJ04

JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 自发光显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2009169090A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2009-07-30 |

| 申请号            | JP2008006956                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2008-01-16 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 飯田幸人<br>三並徹雄<br>谷亀貴央<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 飯田幸人<br>三並徹雄<br>谷亀貴央<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.622.G G09G3/20.611.H H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/CC32 3K107/EE03 3K107/HH04 3K107/HH05 5C080 /AA06 5C080/BB05 5C080/DD01 5C080/EE29 5C080/FF01 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB23 5C380 /AB34 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB23 5C380/CA08 5C380/CA12 5C380/CB02 5C380/CB18 5C380/CB20 5C380/CC02 5C380/CC03 5C380/CC05 5C380/CC07 5C380/CC27 5C380 /CC30 5C380/CC33 5C380/CC41 5C380/CC62 5C380/CD012 5C380/CD022 5C380/CD032 5C380 /DA06 5C380/DA32 5C380/DA47 |         |            |

| 代理人(译)         | 佐藤隆久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

要解决的问题：当辅助电容器Csub连接到前一级的电源扫描线DSL ( i-1 ) 时，防止由于前一级的电位变化导致的图像质量下降。像素电路3 ( i, j ) 包括发光元件 ( 有机发光二极管OLED : 电容Coled。 )。其施加电压值根据一个电极 ( 源节点ND ) 的电位 ( Vs ) 和控制节点Ndc而变化。 ( 电位Vg )，采样晶体管Ms，保持电容器Cs和辅助电容器Csub。根据电源扫描线的高电位Vcc\_H和电源扫描线DSL ( i-1 ) 的低电位Vcc\_L和电位 ( Vcc\_H, Vcc\_L ) , Vws\_L并且被配置为能够输出满足<math>Vg - ( Vcc\_H - Vcc\_L ) Csub / ( Csub + Coled。 )</math>的低电位Vws\_L。.The 13