(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-86727

(P2007-86727A)

(43) 公開日 平成19年4月5日(2007.4.5)

| (51) Int.CI.                | F 1                                 | テーマコード (参考) |

|-----------------------------|-------------------------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K107                   |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 622A 5C080                |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 622C                      |             |

|                             | G09G 3/20 622D                      |             |

|                             | G09G 3/20 622G                      |             |

|                             | 審査請求 有 請求項の数 28 O L (全 27 頁) 最終頁に続く |             |

|              |                              |            |                                                                                                 |

|--------------|------------------------------|------------|-------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-108759 (P2006-108759) | (71) 出願人   | 590002817                                                                                       |

| (22) 出願日     | 平成18年4月11日 (2006.4.11)       |            | 三星エスディアイ株式会社                                                                                    |

| (31) 優先権主張番号 | 10-2005-0087425              |            | 大韓民国京畿道水原市靈通区▲しん▼洞5                                                                             |

| (32) 優先日     | 平成17年9月20日 (2005.9.20)       |            | 75番地                                                                                            |

| (33) 優先権主張国  | 韓国 (KR)                      | (74) 代理人   | 100095957                                                                                       |

|              |                              |            | 弁理士 龟谷 美明                                                                                       |

|              |                              | (74) 代理人   | 100096389                                                                                       |

|              |                              |            | 弁理士 金本 哲男                                                                                       |

|              |                              | (72) 発明者   | 申 東蓉                                                                                            |

|              |                              |            | 大韓民国ソウル市冠岳区奉天1洞969-37                                                                           |

|              |                              | F ターム (参考) | 3K107 AA01 BB01 CC04 CC14 CC21<br>EE03 HH02 HH05<br>5C080 AA06 BB05 DD09 DD26 JJ02<br>JJ03 JJ04 |

(54) 【発明の名称】走査駆動回路、および走査駆動回路を利用した有機電界発光表示装置

(57) 【要約】 (修正有)

【課題】有機電界発光表示装置に利用される走査駆動回路を提供する。

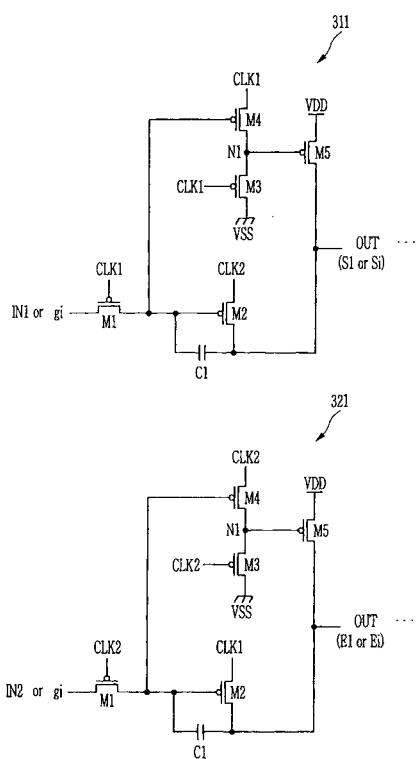

【解決手段】走査駆動回路の各々ステージは、第1クロック端子にゲート端子が接続され、最初入力信号 (IN1 または IN2) または一つ前のステージからの出力信号 (gi) が入力される第1トランジスタ (M1) と、第1トランジスタの出力端にゲート端子が接続され、第2クロック端子および出力線に接続される第2トランジスタ (M2) と、第1クロック端子にゲート端子が接続され、第2電源 (VSS) と第1ノード (N1) との間に接続される第3トランジスタ (M3) と、第1トランジスタの出力端にゲート端子が接続され、第1クロック端子と第1ノードとの間に接続される第4トランジスタ (M4) と、第1ノードにゲート端子が接続され、第1電源 (VDD) と出力線との間に接続される第5トランジスタ (M5) を含む。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

連続して接続される複数のステージを具備して、各々前記ステージを通じて順次選択信号を出力する第1走査駆動部と；

連続して接続される複数のステージを具備して、各々前記ステージを通じて順次発光信号を出力する第2走査駆動部と；

を含む走査駆動回路において，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，

第1クロック端子にゲート端子が接続され，最初入力信号または一つ前の前記ステージからの出力信号が入力される第1トランジスタと；

前記第1トランジスタの出力端にゲート端子が接続され，第2クロック端子および出力線に接続される第2トランジスタと；

前記第1クロック端子にゲート端子が接続され，第2電源と第1ノードとの間に接続される第3トランジスタと；

前記第1トランジスタの出力端にゲート端子が接続され，前記第1クロック端子と前記第1ノードとの間に接続される第4トランジスタと；

前記第1ノードにゲート端子が接続され，第1電源と前記出力線との間に接続される第5トランジスタと；

を含んで構成されることを特徴とする，走査駆動回路。

**【請求項 2】**

前記第1トランジスタの出力端と前記出力線との間に接続される第1キャパシタがさらに含まれて構成されることを特徴とする，請求項1に記載の走査駆動回路。

**【請求項 3】**

前記第1走査駆動部の前記ステージが奇数番目の場合には，前記第1クロック端子に第1クロック信号が供給され，前記第2クロック端子に第2クロック信号が供給され，

前記第1走査駆動部の前記ステージが偶数番目の場合には，前記第1クロック端子に第2クロック信号が供給され，前記第2クロック端子に第1クロック信号が供給されることを特徴とする，請求項1または2に記載の走査駆動回路。

**【請求項 4】**

前記第2走査駆動部の前記ステージが奇数番目の場合には，前記第1クロック端子に第2クロック信号が供給され，前記第2クロック端子に第1クロック信号が供給され，

前記第2走査駆動部の前記ステージが偶数番目の場合には，前記第1クロック端子に第1クロック信号が供給され，前記第2クロック端子に第2クロック信号が供給されることを特徴とする，請求項1～3のいずれかに記載の走査駆動回路。

**【請求項 5】**

前記第1クロック信号および前記第2クロック信号は，ローレベルおよびハイレベルの信号を繰り返し，互いに相反する位相を備え，各々一つのハイレベルおよびローレベルの信号を出力する期間を1周期とすることを特徴とする，請求項3または4に記載の走査駆動回路。

**【請求項 6】**

前記第1走査駆動部の各々の前記ステージにおいて，

前記最初入力信号または前記一つ前のステージからの出力信号が入力されるフリーチャージと；

前記フリーチャージによって入力される前記最初入力信号または前記一つ前のステージからの出力信号のレベルに相当する信号を出力する評価遂行と；

が行われ，

前記第1走査駆動部の前記ステージが奇数番目の場合では，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで

10

20

30

40

50

入力される期間に，前記評価遂行が行われ，

前記第1走査駆動部の前記ステージが偶数番目の場合は，

前記第2クロック信号がローレベルで入力され，前記第1クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第2クロック信号がハイレベルで入力され，前記第1クロック信号がローレベルで入力される期間に，前記評価遂行が行われ，

前記第1走査駆動部の奇数番目の前記ステージで前記評価遂行される時，前記第1走査駆動部の偶数番目の前記ステージは，前記第1走査駆動部の奇数番目の前記ステージから出力される信号を入力する前記フリーチャージを行うことを特徴とする，請求項3～5のいずれかに記載の走査駆動回路。

10

#### 【請求項7】

前記第2走査駆動部の各々の前記ステージにおいて，

前記最初入力信号または前記一つ前のステージからの出力信号が入力されるフリーチャージと；

前記フリーチャージによって入力される前記最初入力信号または前記一つ前のステージからの出力信号のレベルに相当する信号を出力する評価遂行と；

が行われ，

前記第2走査駆動部の前記ステージが奇数番目の場合は，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記評価遂行が行われ，

前記第2走査駆動部の前記ステージが偶数番目の場合は，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで入力される期間に，前記評価遂行が行われ，

前記第2走査駆動部の奇数番目の前記ステージで前記評価遂行される時，前記第2走査駆動部の偶数番目の前記ステージは，前記第2走査駆動部の奇数番目の前記ステージから出力される信号を入力する前記フリーチャージを行うことを特徴とする，請求項4～6のいずれかに記載の走査駆動回路。

20

30

#### 【請求項8】

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージにおいて，

前記フリーチャージされる期間には，前記第1電源の電圧に相当するハイレベルの信号が output され，

前記評価遂行される期間には，前記フリーチャージされる期間に入力される前記最初入力信号または前記一つ前のステージからの出力信号に相当するレベルの信号が output されて，

前記最初入力信号または前記一つ前のステージからの出力信号がローレベルで入力される場合，前記評価遂行される期間で，ローレベルの信号を出力し，

前記一つ前のステージからローレベルの出力信号が順次入力されることによって，前記一つ前のステージに比べて，前記第1クロック信号または前記第2クロック信号の前記1周期の半分だけシフトされる前記ローレベルの信号が順次出力されることを特徴とする，請求項6または7に記載の走査駆動回路。

40

#### 【請求項9】

前記第1走査駆動部の偶数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号は，前記第2走査駆動部の奇数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号と同一であることを特徴とする，請求項4～8のいずれかに記載の走査駆動回路。

50

**【請求項 10】**

前記第1走査駆動部の奇数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号は，前記第2走査駆動部の偶数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号と同一であることを特徴とする，請求項4～9のいずれかに記載の走査駆動回路。

**【請求項 11】**

前記第2走査駆動部に入力される前記最初入力信号は，前記第1クロック信号または前記第2クロック信号の複数の前記周期に相当する所定の期間，ローレベルに提供されることを特徴とする，請求項5～10のいずれかに記載の走査駆動回路。 10

**【請求項 12】**

前記所定の期間は，前記第1走査駆動部および前記第2走査駆動部に各々の前記最初入力信号が入力され，前記選択信号および前記発光信号が出力される1データフレーム内の一定期間であることを特徴とする，請求項11に記載の走査駆動回路。

**【請求項 13】**

前記第2走査駆動部に入力される前記最初入力信号によって，前記第2走査駆動部の各々前記ステージは，前記所定の期間に対応して，少なくとも一度以上，順次ローレベル信号およびハイレベル信号に変換される信号を出力することを特徴とする，請求項11または12に記載の走査駆動回路。 20

**【請求項 14】**

選択信号を出力する第1走査駆動部と；

発光信号を出力する第2走査駆動部と；

を含む走査駆動回路において，

前記第1走査駆動部および前記第2走査駆動部は，連続して接続されるn個のステージを各々具備し，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，入力信号線または一つ前の前記ステージの出力線に従属接続され，第1クロック信号入力線および第2クロック信号入力線に接続され，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージにおいて，

入力される第1クロック信号および第2クロック信号の1周期は，各々一つのハイレベルおよびローレベルの信号を出力する期間に相当し，前記1周期は，ハイレベルまたはローレベルの信号を出力する期間に相当する第1期間および第2期間に分けられ， 30

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，

前記1期間には，ハイレベルの信号を出力するフリーチャージを遂行し，

前記2期間には，前記1期間に入力される信号のレベルに相当する信号を出力する評価遂行を行うことを特徴とする，走査駆動回路。

**【請求項 15】**

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，

第1クロック端子にゲート端子が接続され，一つ前の前記ステージの前記出力線からの出力信号または前記入力信号線からの最初入力信号が入力される第1トランジスタと； 40

前記第1トランジスタの出力端にゲート端子が接続され，第2クロック端子および出力線に接続される第2トランジスタと；

前記第1クロック端子にゲート端子が接続され，第2電源と第1ノードとの間に接続される第3トランジスタと；

前記第1トランジスタの出力端にゲート端子が接続され，前記第1クロック端子と前記第1ノードとの間に接続される第4トランジスタと；

前記第1ノードにゲート端子が接続され，第1電源と前記出力線との間に接続される第5トランジスタと；

を含んで構成されることを特徴とする，請求項14に記載の走査駆動回路。

**【請求項 16】**

10

20

30

40

50

前記第1トランジスタの出力端と前記出力線との間に接続される第1キャパシタがさらに含まれることを特徴とする，請求項15に記載の走査駆動回路。

**【請求項17】**

前記第1クロック信号および前記第2クロック信号は，ローレベルおよびハイレベルの信号を繰り返し，互いに相反する位相を備えることを特徴とする，請求項14～16のいずれかに記載の走査駆動回路。

**【請求項18】**

前記第1走査駆動部の前記ステージが奇数番目の場合には，前記第1クロック端子に前記第1クロック信号が供給され，前記第2クロック端子に前記第2クロック信号が供給され，

前記第1走査駆動部の前記ステージが偶数番目の場合には，前記第1クロック端子に前記第2クロック信号が供給され，前記第2クロック端子に前記第1クロック信号が供給されることを特徴とする，請求項15～17のいずれかに記載の走査駆動回路。

**【請求項19】**

前記第1走査駆動部の各々の前記ステージにおいて，

前記最初入力信号または前記一つ前のステージからの出力信号が入力される前記フリーチャージと；

前記フリーチャージによって入力される前記最初入力信号または前記一つ前のステージからの出力信号のレベルに相当する信号を出力する前記評価遂行と；

が行われ，

前記第1走査駆動部の前記ステージが奇数番目の場合には，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで入力される期間に，前記評価遂行が行われ，

前記第1走査駆動部の前記ステージが偶数番目の場合には，

前記第2クロック信号がローレベルで入力され，前記第1クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第2クロック信号がハイレベルで入力され，前記第1クロック信号がローレベルで入力される期間に，前記評価遂行が行われ，

前記第1走査駆動部の奇数番目の前記ステージで前記評価遂行される時，前記第1走査駆動部の偶数番目の前記ステージは，前記第1走査駆動部の奇数番目の前記ステージから出力される信号を入力する前記フリーチャージを行うことを特徴とする，請求項15～18のいずれかに記載の走査駆動回路。

**【請求項20】**

前記第2走査駆動部の前記ステージが奇数番目の場合には，前記第1クロック端子に前記第2クロック信号が供給され，前記第2クロック端子に前記第1クロック信号が供給され，

前記第2走査駆動部の前記ステージが偶数番目の場合には，前記第1クロック端子に前記第1クロック信号が供給され，前記第2クロック端子に前記第2クロック信号が供給されることを特徴とする，請求項15～19のいずれかに記載の走査駆動回路。

**【請求項21】**

前記第2走査駆動部の各々の前記ステージにおいて，

前記最初入力信号または前記一つ前のステージからの出力信号が入力される前記フリーチャージと；

前記フリーチャージによって入力される前記最初入力信号または前記一つ前のステージからの出力信号のレベルに相当する信号を出力する前記評価遂行と；

が行われ，

前記第2走査駆動部の前記ステージが奇数番目の場合には，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで

10

20

30

40

50

入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記評価遂行が行われ，

前記第2走査駆動部の前記ステージが偶数番目の場合では，

前記第1クロック信号がローレベルで入力され，前記第2クロック信号がハイレベルで入力される期間に，前記フリーチャージが遂行され，

前記第1クロック信号がハイレベルで入力され，前記第2クロック信号がローレベルで入力される期間に，前記評価遂行が行われ，

前記第2走査駆動部の奇数番目の前記ステージで前記評価遂行される時，前記第2走査駆動部の偶数番目の前記ステージは，前記第2走査駆動部の奇数番目の前記ステージから出力される信号を入力する前記フリーチャージを行うことを特徴とする，請求項15～20のいずれかに記載の走査駆動回路。10

#### 【請求項22】

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージにおいて，

前記フリーチャージされる期間には，前記第1電源の電圧に相当するハイレベルの信号が出力され，

前記評価遂行される期間には，前記フリーチャージされる期間に入力される前記最初入力信号または前記一つ前のステージからの出力信号に相当するレベルの信号が出力されて，

前記最初入力信号または前記一つ前のステージからの出力信号がローレベルで入力される場合，前記評価遂行される期間で，ローレベルの信号を出力し，20

前記一つ前のステージからローレベルの出力信号が順次入力されることによって，前記一つ前のステージに比べて，前記第1クロック信号または前記第2クロック信号の前記1周期の半分だけシフトされる前記ローレベルの信号が順次出力されることを特徴とする，請求項15～21のいずれかに記載の走査駆動回路。

#### 【請求項23】

前記第1走査駆動部の偶数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号は，前記第2走査駆動部の奇数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号と同一であることを特徴とする，請求項15～22のいずれかに記載の走査駆動回路。30

#### 【請求項24】

前記第1走査駆動部の奇数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号は，前記第2走査駆動部の偶数番目の前記ステージの前記第1クロック端子，前記第2クロック端子に入力される前記第1クロック信号，前記第2クロック信号と同一であることを特徴とする，請求項15～23のいずれかに記載の走査駆動回路。

#### 【請求項25】

前記第2走査駆動部に入力される前記最初入力信号は，前記第1クロック信号または前記第2クロック信号の複数の前記周期に相当する所定の期間，ローレベルに提供されることを特徴とする，請求項15～24のいずれかに記載の走査駆動回路。40

#### 【請求項26】

前記所定の期間は，前記第1走査駆動部および前記第2走査駆動部に各々の前記最初入力信号が入力され，前記選択信号および前記発光信号が出力される1データフレーム内の一定の期間であることを特徴とする，請求項25に記載の走査駆動回路。

#### 【請求項27】

前記第2走査駆動部に入力される前記最初入力信号によって，前記第2走査駆動部の各々前記ステージは，前記所定の期間に対応して，少なくとも一度以上，順次ローレベル信号およびハイレベル信号に変換される信号を出力することを特徴とする，請求項25または26に記載の走査駆動回路。50

**【請求項 2 8】**

選択信号線，データ線および発光信号線に接続されるように配置される複数の画素を含む画素部と；

前記データ線にデータ信号を供給するデータ駆動回路と；

連続して接続される複数のステージを具備し，複数の前記ステージを通じて，順次選択信号を出力する第1走査駆動部および連続して接続される複数のステージを具備し，複数の前記ステージを通じて，順次発光信号を出力する第2走査駆動部で構成される走査駆動回路と；

が含まれ，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，入力信号線または一つ前の前記ステージの出力線に従属接続され，第1クロック信号入力線および第2クロック信号入力線に接続され，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージにおいて，

入力される第1クロック信号および第2クロック信号の1周期は，各々一つのハイレベルおよびローレベルの信号を出力する期間に相当し，前記1周期は，ハイレベルまたはローレベルの信号を出力する期間に相当する第1期間および第2期間に分けられ，

前記第1走査駆動部および前記第2走査駆動部の各々前記ステージは，

前記第1期間には，ハイレベルまたはローレベルの信号が入力され，ハイレベルの信号を出力するフリーチャージを遂行し，

前記第2期間には，前記第1期間に入力される信号レベルに相当する信号を出力する評価遂行が行われ，

前記第1期間で，ローレベルの信号が入力される場合，前記第2期間で，前記ローレベルの信号を出力し，

前記ステージの前記第1期間において，一つ前の前記ステージの前記第2期間で出力される前記ローレベルの出力信号が入力されることによって，前記第1クロック信号または前記第2クロック信号の前記1周期の半分だけ，前記ローレベルの信号を順次シフトして出力することを特徴とする，有機電界発光表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は，有機電界発光表示装置に関し，特に，有機電界発光表示装置に利用される走査駆動回路に関する。

**【背景技術】**

**【0002】**

一般に，有機電界発光表示装置は，蛍光性有機化合物を電気的に励起させて発光させる表示装置であり， $M \times N$  個の有機発光セルを電圧書込み，あるいは，電流書込みして映像を表現する。このような有機発光セルは，アノード(I TO)，有機薄膜，カソードレイヤー(metal)の構造を備える。

**【0003】**

有機薄膜は，電子と正孔との均衡を良くして発光効率を高めるために，発光層(Emission Layer; EML)，電子輸送層(Electron Transport Layer; ETL)および正孔輸送層(Hole Transport Layer; HTL)を含む多層構造から構成される。また別途に，電子注入層(Electron Injection Layer; EIL)と正孔注入層(Hole Injection Layer; HIL)とを含む。

**【0004】**

このように構成される有機発光セルを駆動する方式には，単純マトリックス(passive matrix)方式と，薄膜トランジスタ(Thin Film Transistor; TFT)を利用した能動駆動(active matrix)方式がある。単純マトリックス方式は，陽極と陰極を直交するように形成し，ラインを選択して駆動す

10

20

30

40

50

る。能動駆動方式は、薄膜トランジスタをITO(Indium Tin Oxide; インジウムスズ酸化物)画素電極に接続して、薄膜トランジスタのゲートに接続されたキャパシタの容量によって維持された電圧に応じて駆動する方式である。

#### 【0005】

この時、キャパシタに電圧を設定するために印加される信号の形態によって、能動駆動方式は、電圧書込み(voltage programming)方式と電流書込み(current programming)方式に分けられる。

#### 【0006】

このような能動駆動方式の有機電界発光表示装置は、大きく分けて、表示パネル、データ駆動回路、走査駆動回路、タイミング制御部を含んで構成される。走査駆動回路は、タイミング制御部から走査駆動制御信号の供給を受ける。これによって、走査駆動回路は、走査信号を生成し、生成された走査信号を表示パネルの走査線に順次供給する。

10

#### 【0007】

すなわち、走査駆動回路は、パネル内に具備された複数の画素を駆動するために順次走査信号を生成して、走査信号をパネルに提供する。

#### 【0008】

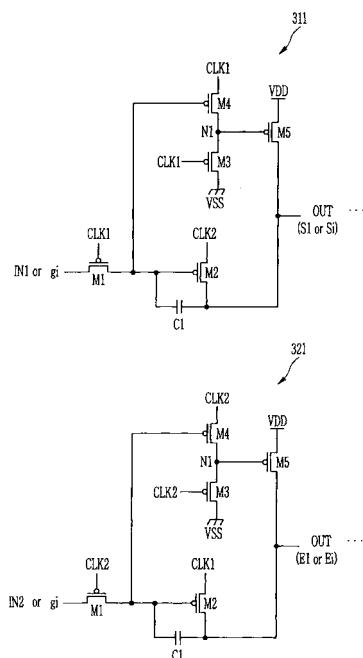

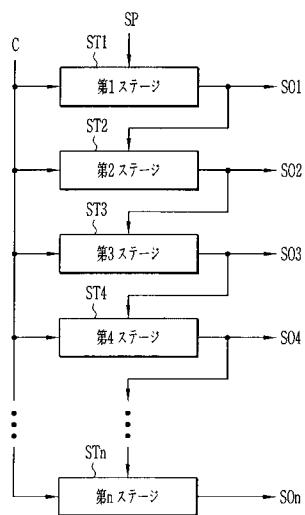

図1は、従来の一般的な走査駆動回路の構成を示すブロック図である。図1を参照すると、従来の一般的な走査駆動回路は、スタートパルスSP入力ラインに従属的に接続された複数のステージ(ST1～STn)で構成される。複数のステージ(ST1～STn)は、スタートパルス(SP)をクロック信号(C)によって順次シフトさせて、出力信号(SO1～SON)を発生する。この場合、第2～第nステージ(ST2～STn)の各々は、一つ前のステージからの出力信号をスタートパルスとして入力してもらい、一つ前のステージからの出力信号をシフトさせる。これによって、複数のステージ(ST1～STn)は、スタートパルスが順次シフトされる形態の出力信号(SO1～SON)を発生して、出力信号(SO1～SON)をマトリックス画素アレイに提供する。

20

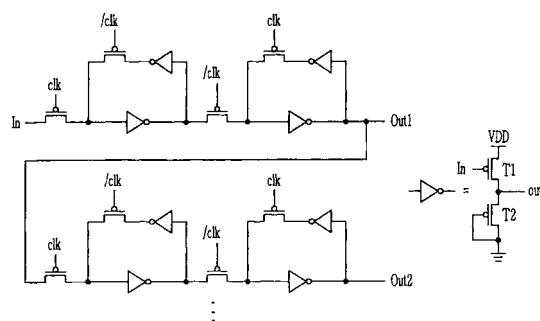

#### 【0009】

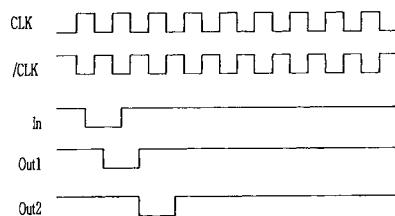

図2は、図1に図示された走査駆動回路において、任意のステージの回路図である。図3は、図2に図示されたステージの入力信号/出力信号波形図である。

#### 【0010】

図2および図3を参照すると、従来の場合、走査駆動回路を構成する各々ステージは、マスタースレーブ(Master-Slave)形態のフリップフロップ(flip/flop)を使用する。このようなフリップフロップは、クロック信号(clk)がローレベルの時、入力を続けて受け、出力は、以前の出力を維持する。

30

#### 【0011】

一方、クロック信号(clk)がハイレベルの場合には、クロック信号(clk)がローレベルの時受けた入力を維持し、これを出力してこれ以上の入力を受けない。

#### 【0012】

そして、図2の回路において、出力電圧(out)のハイレベルは、供給電圧(VDD)と接地との間を連結する抵抗の比による電圧値(ratioed logic)で決定され、出力電圧(out)のローレベルは、接地よりトランジスタの閾値電圧ほど高くなる。

40

#### 【0013】

一方、従来の走査駆動回路と、これを利用した有機電界発光表示装置に関する技術を記載した文献としては、下記特許文献1等がある。

#### 【0014】

【特許文献1】特許第2921510号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0015】

しかし、従来の走査駆動回路において、フリップフロップ内部にインバータを具備する

50

場合、ローレベルの入力を受ける時、スタティック電流 (static current) が流れるという問題がある。また、フリップフロップ内部で、ハイレベルの入力を受けたインバータとローレベルの入力を受けるインバータの数が同一であるから、フリップフロップ内部のインバータの中の半分では、スタティック電流が発生されて消費電力が大きくなるという短所がある。さらに、従来の走査駆動回路で用いられるインバータに具備されるトランジスタの特性偏差によって、各々ステージにハイレベルで受け入れる入力電圧レベルが異なるので、このような回路を採用する場合、出力電圧のハイレベルにも偏差が生じて回路が誤動作するという短所がある。また、出力電圧のローレベル偏差は、図2の回路に具備されるインバータの入力トランジスタ (T1) のオン抵抗の偏差として反映されて、出力電圧のハイレベル偏差を加重させことがある。特に、有機電界発光表示装置パネルでは、特性偏差の大きいトランジスタを使用するので、このような走査駆動回路の誤作動問題がさらに深刻になる。また、インバータは、入力トランジスタ (T1) を通じて電流が流れて出力端を充電し、ロードトランジスタ (T2) を通じて電流が流れて出力端を放電するが、出力端を充電する場合、ロードトランジスタ (T2) のソース - ゲート電圧がますます減ってしまい、放電電流が急激に減少して放電効率が落ちるという問題がある。

10

## 【0016】

そこで、本発明は、このような問題に鑑みてなされたもので、その目的とするところは、能動駆動方式の有機電界発光表示装置で、消費電力の低減、走査駆動回路の誤作動、放電効率の減少、および各画素の劣化を防止する走査駆動回路、および走査駆動回路を利用した有機電界発光表示装置を提供することにある。

20

## 【課題を解決するための手段】

## 【0017】

上記課題を解決するために、本発明の第1の観点によれば、連続して接続される複数のステージを具備して、各々ステージを通じて順次選択信号を出力する第1走査駆動部と、連続して接続される複数のステージを具備して、各々ステージを通じて順次発光信号を出力する第2走査駆動部とを含む走査駆動回路において、第1走査駆動部および第2走査駆動部の各々ステージは、第1クロック端子 (CLKa) にゲート端子が接続され、最初入力信号 (IN1またはIN2) または一つ前のステージからの出力信号 (gi) が入力される第1トランジスタ (M1) と、第1トランジスタ (M1) の出力端にゲート端子が接続され、第2クロック端子 (CLKb) および出力線 (out) に接続される第2トランジスタ (M2) と、第1クロック端子 (CLKa) にゲート端子が接続され、第2電源 (VSS) と第1ノード (N1) との間に接続される第3トランジスタ (M3) と、第1トランジスタ (M1) の出力端にゲート端子が接続され、第1クロック端子 (CLKa) と第1ノード (N1) との間に接続される第4トランジスタ (M4) と、第1ノード (N1) にゲート端子が接続され、第1電源 (VDD) と出力線 (out) との間に接続される第5トランジスタ (M5) とを含んで構成される走査駆動回路が提供される。

30

## 【0018】

本発明によれば、選択信号を供給する第1走査駆動部と、発光信号を供給する第2走査駆動部とで構成される走査駆動回路において、スタティック電流が流れる経路 (従来の走査駆動回路におけるインバータ) を除去することで、消費電力を低減することができる。

40

## 【0019】

第1トランジスタ (M1) の出力端と出力線 (out) との間に接続される第1キャバシタ (C1) がさらに含まれてもよい。

## 【0020】

第1走査駆動部のステージが奇数番目の場合には、第1クロック端子 (CLKa) に第1クロック信号 (CLK1) が供給され、第2クロック端子 (CLKb) に第2クロック信号 (CLK2) が供給されてもよく、第1走査駆動部のステージが偶数番目の場合には、第1クロック端子 (CLKa) に第2クロック信号 (CLK2) が供給され、第2クロック端子 (CLKb) に第1クロック信号 (CLK1) が供給されてもよい。

50

## 【0021】

第2走査駆動部のステージが奇数番目の場合には、第1クロック端子(CLK<sub>a</sub>)に第2クロック信号(CLK<sub>2</sub>)が供給され、第2クロック端子(CLK<sub>b</sub>)に第1クロック信号(CLK<sub>1</sub>)が供給されてもよく、第2走査駆動部のステージが偶数番目の場合には、第1クロック端子(CLK<sub>a</sub>)に第1クロック信号(CLK<sub>1</sub>)が供給され、第2クロック端子(CLK<sub>b</sub>)に第2クロック信号(CLK<sub>2</sub>)が供給されてもよい。

## 【0022】

第1クロック信号(CLK<sub>1</sub>)および第2クロック信号(CLK<sub>2</sub>)は、ローレベルおよびハイレベルの信号を繰り返し、互いに相反する位相を備えることができ、各ターンのハイレベルおよびローレベルの信号を出力する期間を1周期とすることができる。

10

## 【0023】

第1走査駆動部の各々のステージにおいて、最初入力信号(IN<sub>1</sub>)または一つ前のステージからの出力信号(g<sub>i</sub>)が入力されるフリーチャージと、上記フリーチャージによって入力される最初入力信号(IN<sub>1</sub>)または一つ前のステージからの出力信号(g<sub>i</sub>)のレベルに相当する信号を出力する評価遂行とが行われ、第1走査駆動部のステージが奇数番目の場合には、第1クロック信号(CLK<sub>1</sub>)がローレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がハイレベルで入力される期間に、上記フリーチャージが遂行され、第1クロック信号(CLK<sub>1</sub>)がハイレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がローレベルで入力される期間に、上記評価遂行が行われ、第1走査駆動部のステージが偶数番目の場合には、第2クロック信号(CLK<sub>2</sub>)がローレベルで入力され、第1クロック信号(CLK<sub>1</sub>)がハイレベルで入力される期間に、上記フリーチャージが遂行され、第2クロック信号(CLK<sub>2</sub>)がハイレベルで入力され、第1クロック信号(CLK<sub>1</sub>)がローレベルで入力される期間に、上記評価遂行が行われ、第1走査駆動部の奇数番目のステージで上記評価遂行される時、第1走査駆動部の偶数番目のステージは、第1走査駆動部の奇数番目のステージから出力される信号を入力する上記フリーチャージを行うことができる。

20

## 【0024】

第2走査駆動部の各々のステージにおいて、最初入力信号(IN<sub>2</sub>)または一つ前のステージからの出力信号(g<sub>i</sub>)が入力されるフリーチャージと、上記フリーチャージによって入力される最初入力信号(IN<sub>2</sub>)または一つ前のステージからの出力信号(g<sub>i</sub>)のレベルに相当する信号を出力する評価遂行とが行われ、第2走査駆動部のステージが奇数番目の場合には、第1クロック信号(CLK<sub>1</sub>)がハイレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がローレベルで入力される期間に、上記フリーチャージが遂行され、第1クロック信号(CLK<sub>1</sub>)がローレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がハイレベルで入力される期間に、上記評価遂行が行われ、第2走査駆動部のステージが偶数番目の場合には、第1クロック信号(CLK<sub>1</sub>)がローレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がハイレベルで入力される期間に、上記フリーチャージが遂行され、第1クロック信号(CLK<sub>1</sub>)がハイレベルで入力され、第2クロック信号(CLK<sub>2</sub>)がローレベルで入力される期間に、上記評価遂行が行われ、第2走査駆動部の奇数番目のステージで上記評価遂行される時、第2走査駆動部の偶数番目のステージは、第2走査駆動部の奇数番目のステージから出力される信号を入力する上記フリーチャージを行うことができる。

30

## 【0025】

第1走査駆動部および第2走査駆動部の各々ステージにおいて、フリーチャージされる期間には、第1電源の電圧に相当するハイレベルの信号が出力され、評価遂行される期間には、フリーチャージされる期間に入力される最初入力信号または一つ前のステージからの出力信号に相当するレベルの信号が出力されて、最初入力信号または一つ前のステージからの出力信号がローレベルで入力される場合、評価遂行される期間で、ローレベルの信号を出力し、一つ前のステージからローレベルの出力信号が順次入力されることによって、一つ前のステージに比べて、第1クロック信号(CLK<sub>1</sub>)または第2クロック信号(

40

50

C L K 2 ) の 1 周期の半分だけシフトされる上記ローレベルの信号が順次出力されてもよい。

#### 【 0 0 2 6 】

本発明によれば、フリーチャージされる期間で、第5トランジスタ(M5)を通じて、第1電源(VDD)のハイレベルの信号が出力されるので、従来の走査駆動回路より、ハイレベルで出力される信号がトランジスタの特性偏差の影響を受けないため、走査駆動回路の誤作動を防止できる。フリーチャージされる期間で、ハイレベルの一つ前のステージからの出力信号(gi)または最初入力信号(IN1またはIN2)が入力される場合における評価期間においても、同様である。また、ステージからハイレベルの信号を出力する時、第5トランジスタ(M5)を通じて、第1電源(VDD)のハイレベルの信号が出力されるので、従来の走査駆動回路のようにインバータの出力端を充電しないので、漏れる電流(leakage current)を最小化でき、放電効率を改善して動作速度を向上できる。10

#### 【 0 0 2 7 】

また、本発明によれば、評価期間において、第2トランジスタ(M2)を通じて、ローレベルの第2クロック信号(CLK2)(または、ローレベルの第1クロック信号(CLK1))が出力線から出力されるので、従来の走査駆動回路より、ローレベルで出力される信号がトランジスタの特性偏差の影響を受けないため、走査駆動回路の誤作動を防止できる。さらに、ステージからローレベルの信号を出力する時、第2トランジスタ(M2)を通じて、ローレベルの第2クロック信号(CLK2)(または、ローレベルの第1クロック信号(CLK1))が出力線から出力されるので、従来の走査駆動回路のようにインバータの出力端を放電する電流の減少程度を最小化でき、放電効率を改善して動作速度を向上できる。20

#### 【 0 0 2 8 】

第1走査駆動部の偶数番目のステージの第1クロック端子、第2クロック端子に入力される第1クロック信号、第2クロック信号は、第2走査駆動部の奇数番目のステージの第1クロック端子、第2クロック端子に入力される第1クロック信号、第2クロック信号と同一であってよい。また、第1走査駆動部の奇数番目のステージの第1クロック端子、第2クロック端子に入力される第1クロック信号、第2クロック信号は、第2走査駆動部の偶数番目のステージの第1クロック端子、第2クロック端子に入力される第1クロック信号、第2クロック信号と同一であってよい。30

#### 【 0 0 2 9 】

つまり、第1走査駆動部の奇数番目のステージで、評価遂行される期間に、第2走査駆動部の奇数番目のステージでは、フリーチャージが行われ、第1走査駆動部の奇数番目のステージで、評価遂行によって、選択信号が出力された後に、第2走査駆動部の奇数番目のステージでは、評価遂行が行われ、発光信号を出力することができる。そして、第1走査駆動部の偶数番目のステージで、評価遂行される期間に、第2走査駆動部の偶数番目のステージでは、フリーチャージが行われ、第1走査駆動部の偶数番目のステージで、評価遂行によって、選択信号が出力された後に、第2走査駆動部の偶数番目のステージでは、評価遂行が行われ、発光信号を出力することができる。40

#### 【 0 0 3 0 】

第2走査駆動部に入力される最初入力信号(IN2)は、第1クロック信号(CLK1)または第2クロック信号(CLK2)の複数の周期に相当する所定の期間、ローレベルに提供されてもよい。

#### 【 0 0 3 1 】

所定の期間は、第1走査駆動部および第2走査駆動部に各々の最初入力信号が入力され、選択信号および発光信号が出力される1データフレーム内の一定期間であってよい。

#### 【 0 0 3 2 】

第2走査駆動部に入力される最初入力信号(IN2)によって、第2走査駆動部の各々ステージは、所定の期間に対応して、少なくとも一度以上、順次ローレベル信号およびハ50

イレベル信号に変換される信号を出力することができる。

【0033】

本発明によれば、発光信号をデータフレームの1周期中、所定期間の間、少なくとも一度以上ローレベルおよびハイレベルに変換して印加するので、各画素の劣化を防止することができる。

【0034】

上記課題を解決するために、本発明の第2の観点によれば、選択信号を出力する第1走査駆動部と、発光信号を出力する第2走査駆動部とを含む走査駆動回路において、第1走査駆動部および第2走査駆動部は、連続して接続されるn個のステージを各々具備し、第1走査駆動部および第2走査駆動部の各々ステージは、入力信号線(IN1またはIN2)または一つ前のステージの出力線(gi)に従属接続され、第1クロック信号入力線(CLK1)および第2クロック信号入力線(CLK2)に接続され、第1走査駆動部および第2走査駆動部の各々ステージにおいて、入力される第1クロック信号(CLK1)および第2クロック信号(CLK2)の1周期は、各々一つのハイレベルおよびローレベルの信号を出力する期間に相当し、上記1周期は、ハイレベルまたはローレベルの信号を出力する期間に相当する第1期間および第2期間に分けられ、第1走査駆動部および第2走査駆動部の各々ステージは、第1期間には、ハイレベルの信号を出力するフリーチャージを遂行し、第2期間には、第1期間に入力される信号のレベルに相当する信号を出力する評価遂行を行う走査駆動回路が提供される。

10

【0035】

第1走査駆動部および第2走査駆動部の各々ステージは、第1クロック端子(CLKa)にゲート端子が接続され、一つ前のステージの出力線からの出力信号(gi)または入力信号線からの最初入力信号(IN1またはIN2)が入力される第1トランジスタ(M1)と、第1トランジスタ(M1)の出力端にゲート端子が接続され、第2クロック端子(CLKb)および出力線(out)に接続される第2トランジスタ(M2)と、第1クロック端子(CLKa)にゲート端子が接続され、第2電源(VSS)と第1ノード(N1)との間に接続される第3トランジスタと、第1トランジスタ(M1)の出力端にゲート端子が接続され、第1クロック端子(CLKa)と第1ノード(N1)との間に接続される第4トランジスタ(M4)と、第1ノード(N1)にゲート端子が接続され、第1電源(VDD)と出力線(out)との間に接続される第5トランジスタ(M5)とを含んで構成されてもよい。

20

30

【0036】

第1トランジスタ(M1)の出力端と出力線(out)との間に接続される第1キャバシタ(C1)がさらに含まれてもよい。

【0037】

第1クロック信号(CLK1)および第2クロック信号(CLK2)は、ローレベルおよびハイレベルの信号を繰り返し、互いに相反する位相を備えることができる。

40

【0038】

第1走査駆動部のステージが奇数番目の場合には、第1クロック端子(CLKa)に第1クロック信号(CLK1)が供給され、第2クロック端子(CLKb)に第2クロック信号(CLK2)が供給されてもよく、第1走査駆動部のステージが偶数番目の場合には、第1クロック端子(CLKa)に第2クロック信号(CLK2)が供給され、第2クロック端子(CLKb)に第1クロック信号(CLK1)が供給されてもよい。

【0039】

第1走査駆動部の各々のステージにおいて、最初入力信号(IN1)または一つ前のステージからの出力信号(gi)が入力されるフリーチャージと、上記フリーチャージによって入力される最初入力信号(IN1)または一つ前のステージからの出力信号(gi)のレベルに相当する信号を出力する評価遂行とが行われ、第1走査駆動部のステージが奇数番目の場合では、第1クロック信号(CLK1)がローレベルで入力され、第2クロック信号(CLK2)がハイレベルで入力される期間に、上記フリーチャージが遂行され、

50

第1クロック信号( C L K 1 )がハイレベルで入力され，第2クロック信号( C L K 2 )がローレベルで入力される期間に，上記評価遂行が行われ，第1走査駆動部のステージが偶数番目の場合では，第2クロック信号( C L K 2 )がローレベルで入力され，第1クロック信号( C L K 1 )がハイレベルで入力される期間に，上記フリーチャージが遂行され，第2クロック信号( C L K 2 )がハイレベルで入力され，第1クロック信号( C L K 1 )がローレベルで入力される期間に，上記評価遂行が行われ，第1走査駆動部の奇数番目のステージで上記評価遂行される時，第1走査駆動部の偶数番目のステージは，第1走査駆動部の奇数番目のステージから出力される信号を入力する上記フリーチャージを行うことができる。

## 【 0 0 4 0 】

10

第2走査駆動部のステージが奇数番目の場合には，第1クロック端子( C L K a )に第2クロック信号( C L K 2 )が供給され，第2クロック端子( C L K b )に第1クロック信号( C L K 1 )が供給されてもよく，第2走査駆動部のステージが偶数番目の場合には，第1クロック端子( C L K a )に第1クロック信号( C L K 1 )が供給され，第2クロック端子( C L K b )に第2クロック信号( C L K 2 )が供給されてもよい。

## 【 0 0 4 1 】

20

第2走査駆動部の各々のステージにおいて，最初入力信号( I N 2 )または一つ前のステージからの出力信号( g i )が入力されるフリーチャージと，上記フリーチャージによって入力される最初入力信号( I N 2 )または一つ前のステージからの出力信号( g i )のレベルに相当する信号を出力する評価遂行とが行われ，第2走査駆動部のステージが奇数番目の場合では，第1クロック信号( C L K 1 )がハイレベルで入力され，第2クロック信号( C L K 2 )がローレベルで入力される期間に，上記フリーチャージが遂行され，第1クロック信号( C L K 1 )がローレベルで入力され，第2クロック信号( C L K 2 )がハイレベルで入力される期間に，上記評価遂行が行われ，第2走査駆動部のステージが偶数番目の場合では，第1クロック信号( C L K 1 )がローレベルで入力され，第2クロック信号( C L K 2 )がハイレベルで入力される期間に，上記フリーチャージが遂行され，第1クロック信号( C L K 1 )がハイレベルで入力され，第2クロック信号( C L K 2 )がローレベルで入力される期間に，上記評価遂行が行われ，第2走査駆動部の奇数番目のステージで上記評価遂行される時，第2走査駆動部の偶数番目のステージは，第2走査駆動部の奇数番目のステージから出力される信号を入力する上記フリーチャージを行うことができる。

30

## 【 0 0 4 2 】

40

第1走査駆動部および第2走査駆動部の各々ステージにおいて，フリーチャージされる期間には，第1電源の電圧に相当するハイレベルの信号が出力され，評価遂行される期間には，フリーチャージされる期間に入力される最初入力信号または一つ前のステージからの出力信号に相当するレベルの信号が出力されて，最初入力信号または一つ前のステージからの出力信号がローレベルで入力される場合，評価遂行される期間で，ローレベルの信号を出力し，一つ前のステージからローレベルの出力信号が順次入力されることによって，一つ前のステージに比べて，第1クロック信号( C L K 1 )または第2クロック信号( C L K 2 )の1周期の半分だけシフトされる上記ローレベルの信号が順次出力されてもよい。

## 【 0 0 4 3 】

第1走査駆動部の偶数番目のステージの第1クロック端子，第2クロック端子に入力される第1クロック信号，第2クロック信号は，第2走査駆動部の奇数番目のステージの第1クロック端子，第2クロック端子に入力される第1クロック信号，第2クロック信号と同一であってよい。また，第1走査駆動部の奇数番目のステージの第1クロック端子，第2クロック端子に入力される第1クロック信号，第2クロック信号は，第2走査駆動部の偶数番目のステージの第1クロック端子，第2クロック端子に入力される第1クロック信号，第2クロック信号と同一であってよい。

## 【 0 0 4 4 】

50

つまり，第1走査駆動部の奇数番目のステージで，評価遂行される期間に，第2走査駆動部の奇数番目のステージでは，フリーチャージが行われ，第1走査駆動部の奇数番目のステージで，評価遂行によって，選択信号が出力された後に，第2走査駆動部の奇数番目のステージでは，評価遂行が行われ，発光信号を出力することができる。そして，第1走査駆動部の偶数番目のステージで，評価遂行される期間に，第2走査駆動部の偶数番目のステージでは，フリーチャージが行われ，第1走査駆動部の偶数番目のステージで，評価遂行によって，選択信号が出力された後に，第2走査駆動部の偶数番目のステージでは，評価遂行が行われ，発光信号を出力することができる。

#### 【0045】

第2走査駆動部に入力される最初入力信号( $I_N 2$ )は，第1クロック信号( $C_L K 1$ )または第2クロック信号( $C_L K 2$ )の複数の周期に相当する所定の期間，ローレベルに提供されてもよい。10

#### 【0046】

所定の期間は，第1走査駆動部および第2走査駆動部に各々の最初入力信号が入力され，選択信号および発光信号が出力される1データフレーム内の一定の期間であってよい。

#### 【0047】

第2走査駆動部に入力される最初入力信号( $I_N 2$ )によって，第2走査駆動部の各々ステージは，所定の期間に対応して，少なくとも一度以上，順次ローレベル信号およびハイレベル信号に変換される信号を出力することができる。

#### 【0048】

上記課題を解決するために，本発明の第3の観点によれば，選択信号線，データ線および発光信号線に接続されるように配置される複数の画素を含む画素部と，データ線にデータ信号を供給するデータ駆動回路と，連続して接続される複数のステージを具備し，複数のステージを通じて，順次選択信号を出力する第1走査駆動部および連続して接続される複数のステージを具備し，複数のステージを通じて，順次発光信号を出力する第2走査駆動部で構成される走査駆動回路とが含まれ，第1走査駆動部および第2走査駆動部の各々ステージは，入力信号線( $I_N 1$ または $I_N 2$ )または一つ前のステージの出力線( $g_i$ )に従属接続され，第1クロック信号入力線( $C_L K 1$ )および第2クロック信号入力線( $C_L K 2$ )に接続され，第1走査駆動部および第2走査駆動部の各々ステージにおいて，入力される第1クロック信号( $C_L K 1$ )および第2クロック信号( $C_L K 2$ )の1周期は，各々一つのハイレベルおよびローレベルの信号を出力する期間に相当し，上記1周期は，ハイレベルまたはローレベルの信号を出力する期間に相当する第1期間および第2期間に分けられ，第1走査駆動部および第2走査駆動部の各々ステージは，第1期間には，ハイレベルまたはローレベルの信号が入力され，ハイレベルの信号を出力するフリーチャージを遂行し，第2期間には，第1期間に入力される信号レベルに相当する信号を出力する評価遂行が行われ，第1期間で，ローレベルの信号が入力される場合，第2期間で，ローレベルの信号を出力し，ステージの第1期間において，一つ前のステージの第2期間で出力されるローレベルの出力信号が入力されることによって，第1クロック信号( $C_L K 1$ )または第2クロック信号( $C_L K 2$ )の1周期の半分だけ，上記ローレベルの信号を順次シフトして出力する有機電界発光表示装置が提供される。30

#### 【発明の効果】

#### 【0049】

以上説明したように本発明によれば，走査駆動回路でスタティック電流が流れる経路を除去することで，消費電力を低減することができる。また，走査駆動回路を通じてハイレベル出力を行う時，出力端を充電しなくなつて漏れる電流(*leakage current*)を最小化し，ローレベル出力を行う時，出力端を放電する電流の減少程度を最小化して，放電効率を向上させて動作速度を速くすることができる。さらに，選択信号を提供する第1走査駆動部と，発光信号を提供する第2走査駆動部とで構成される走査駆動回路において，発光信号をデータフレームの1周期中，所定期間の間，少なくとも一度以上ハイレベルおよびローレベルとするように印加して各画素の劣化を防止することができる。40

**【発明を実施するための最良の形態】**

**【0050】**

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

**【0051】**

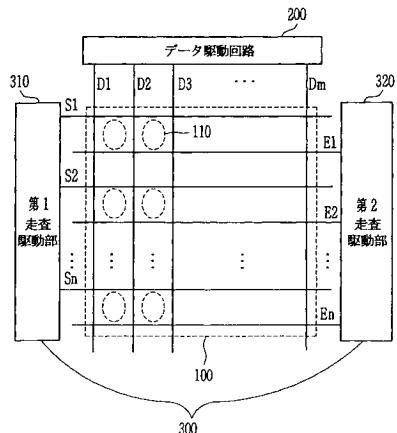

図4は、本発明の実施形態に係る有機電界発光表示装置を概略的に図示したブロック図である。図4に図示されるように、本発明の実施形態に係る有機電界発光表示装置は、有機EL表示パネル（以下、表示パネル）100、データ駆動回路200、走査駆動回路300を含んで構成される。走査駆動回路300は、選択信号を供給する第1走査駆動部310と、発光信号を供給する第2走査駆動部320から構成される。

10

**【0052】**

表示パネル100は、列方向に延長して形成される複数のデータ線（D<sub>1</sub>～D<sub>m</sub>）、行方向に延長して形成される複数の信号線（S<sub>1</sub>～S<sub>n</sub>）、複数の信号線（E<sub>1</sub>～E<sub>n</sub>）、およびマトリックス形状に形成される複数の画素回路110を含む。ここで、信号線は、画素を選択するための選択信号を伝達する複数の選択信号線（S<sub>1</sub>～S<sub>n</sub>）および有機EL素子の発光期間を制御するための発光信号を伝達する複数の発光信号線（E<sub>1</sub>～E<sub>n</sub>）を含む。そして、データ線（D<sub>1</sub>～D<sub>m</sub>）と選択信号線（S<sub>1</sub>～S<sub>n</sub>）および発光信号線（E<sub>1</sub>～E<sub>n</sub>）によって定義される画素領域に、各々画素回路110が形成される。

20

**【0053】**

データ駆動回路200は、データ線（D<sub>1</sub>～D<sub>m</sub>）にデータ電流（DATA）を印加する。走査駆動回路300の第1走査駆動部310は、選択信号線（S<sub>1</sub>～S<sub>n</sub>）に画素回路を選択するための選択信号を順次印加する。また、第2走査駆動部320は、画素回路110の輝度を制御するための発光信号を発光信号線（E<sub>1</sub>～E<sub>n</sub>）に順次印加する。

**【0054】**

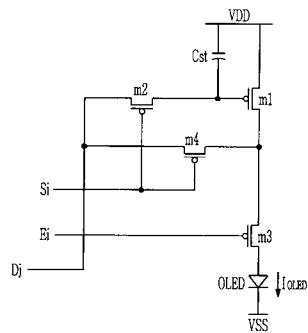

図5は、図4に図示される有機電界発光表示装置の各画素領域に具備される画素回路の実施形態を示す回路図である。但し、図5では、説明の便宜上、j番目のデータ線（D<sub>j</sub>）とi番目の選択信号線（S<sub>i</sub>），i番目の発光信号線（E<sub>i</sub>）に接続される画素回路のみを図示する。

**【0055】**

図5で図示されるように、本発明の実施形態に係る画素回路110は、有機EL素子（OLED）、トランジスタ（m<sub>1</sub>～m<sub>4</sub>），およびキャパシタ（Cst）を含む。ここで、トランジスタ（m<sub>1</sub>～m<sub>4</sub>）では、PMOSトランジスタを用いるが、これに限定されない。

30

**【0056】**

トランジスタ（m<sub>1</sub>）は、電源（VDD）と有機EL素子（OLED）との間に接続され、有機EL素子（OLED）に流れる電流を制御する。具体的には、トランジスタ（m<sub>1</sub>）のソースは、電源（VDD）に接続され、ドレイン（出力端）は、トランジスタ（m<sub>3</sub>）を通じて有機EL素子（OLED）のカソードに接続される。また、トランジスタ（m<sub>2</sub>）は、ゲートが選択信号線（S<sub>i</sub>）に接続され、ソースがデータ線（D<sub>j</sub>）に、ドレインがトランジスタ（m<sub>1</sub>）のゲートに接続されるので、選択信号線（S<sub>i</sub>）からの選択信号に応答して、データ線（D<sub>j</sub>）からのデータ信号（データ電流DATA）をトランジスタ（m<sub>1</sub>）のゲートに伝達する。トランジスタ（m<sub>4</sub>）は、ゲートが選択信号線（S<sub>i</sub>）に接続され、ソースがデータ線（D<sub>j</sub>）に、ドレインがトランジスタ（m<sub>1</sub>）のドレインに接続されるので、トランジスタ（m<sub>4</sub>）は、選択信号に応答して、トランジスタ（m<sub>1</sub>）をダイオード連結させる。

40

**【0057】**

また、キャパシタ（Cst）は、トランジスタ（m<sub>1</sub>）のゲートとソースとの間に接続され、データ線（D<sub>j</sub>）からのデータ電流（DATA）に相当する電圧を充電する。トランジスタ（m<sub>3</sub>）は、ゲートが発光信号線（E<sub>i</sub>）に接続され、ソースがトランジスタ

50

(m1) のドレインに、ドレインが有機EL素子(OLED)のカソードに接続されるので、トランジスタ(m3)は、発光信号線(Ei)からの発光信号に応答して、トランジスタ(m1)に流れる電流を有機EL素子(OLED)に伝達する。

#### 【0058】

図6は、図5の画素回路に入力される選択信号および発光信号に対するタイミング図である。図6に図示されるように、選択信号線(Si)，選択信号線(Si+1)，選択信号線(Si+2)には、トランジスタ(m2)をターンオンするための選択信号が順に印加される。このように、選択信号によってトランジスタ(m2)がターンオンされると、データ線(D1～Dm)からデータ電流(IDATA)がトランジスタ(m1)のゲートに印加される。この時、選択信号によってトランジスタ(m4)がターンオンされ、トランジスタ(m1)がダイオード連結される。したがって、キャパシタ(Cst)に、トランジスタ(m1)を通じて流れるデータ電流(IDATA)に相当する電圧が充電される。したがって、キャパシタ(Cst)にデータ電流(IDATA)に相当する電圧が保存されて維持され、この電圧に対応する電流によって有機EL素子(OLED)が、反復的に発光することができる。

#### 【0059】

以後、充電が完了すれば、トランジスタ(m2)およびトランジスタ(m4)がターンオフされ、発光信号線(Ei)，発光信号線(Ei+1)，発光信号線(Ei+2)から印加される発光信号によって、トランジスタ(m3)がターンオンされて、トランジスタ(m3)を通じてデータ電流(IDATA)が有機EL素子(OLED)に流れ、これにより、有機EL素子(OLED)が発光する。

#### 【0060】

但し、本発明の実施形態の場合、このような有機電界発光表示装置の動作時に、図6に示すように発光信号線(Ei)，発光信号線(Ei+1)，発光信号線(Ei+2)に印加される発光信号のレベルがデータフレームの1周期中における所定の期間、少なくとも一度以上順次変わって供給されることを特徴とする。すなわち、発光信号線(Ei)，発光信号線(Ei+1)，発光信号線(Ei+2)に印加される発光信号は、データフレームの1周期中、所定の期間、順次ローレベルおよびハイレベルに変わって供給される。ここで、発光信号線(Ei)，発光信号線(Ei+1)，発光信号線(Ei+2)に印加される発光信号がローレベルの場合には、トランジスタ(m3)がターンオンされて、トランジスタ(m1)から印加される電流(データ電流IDATA)が有機EL素子(OLED)に供給され、この電流に対応して有機EL素子(OLED)は、発光する。発光信号がハイレベルの場合には、トランジスタ(m3)がターンオフされて、トランジスタ(m1)から印加される電流が有機EL素子(OLED)に供給されず、有機EL素子(OLED)は、発光しない。本発明の実施形態では、データフレームの1周期とは、第1走査駆動部310から選択信号、第2走査駆動部320から発光信号が、有機電界発光表示装置の複数の画素のうち、一つの画素に順次印加される周期である。

#### 【0061】

より詳しく説明すると、図6に図示されるように、ハイレベルの発光信号が印加される非発光期間(Poff)の間、選択信号線(Si)にトランジスタ(m2)，トランジスタ(m4)をターンオンするための選択信号が印加され、トランジスタ(m1)のゲート端子にデータ線(D1～Dm)からのデータ電流(IDATA)が印加されるので、データ電流(IDATA)に対応する電圧がキャパシタ(Cst)に充電される(記録期間Pw)。記録期間Pwが終わって少しのタイミング後に、発光信号線(Ei)に印加される発光信号がローレベルになって、トランジスタ(m3)がターンオンされ、トランジスタ(m1)から有機EL素子(OLED)に、キャパシタ(Cst)で充電された電圧に相当する電流(データ電流IDATA)が印加されるので、有機EL素子(OLED)が発光する1次発光期間(Pon)が始まる。一定の時間の間、発光がなされた後に、発光信号のレベルがハイレベルになって、トランジスタ(m3)がターンオフされるので、有機EL素子(OLED)に電流が印加されなくなって、有機EL素子(OLED)が発光

10

20

30

40

50

しない非発光期間 (P off) になる。これは、図6に図示されるように、データフレームの1周期中、所定の期間、順次1次発光期間 (P on) と非発光期間 (P off) が繰り返される。ここで、所定の期間がデータフレームの1周期の全部になる場合には、有機EL素子 (OLED) の発光期間がデータフレームの1周期の50%になる。ここで、記録期間 Pw が終わった後の少しのタイミング以後に発光信号がローレベルになるのは、画素回路110にローレベルの選択信号が入力された後の少しのタイミング以後にローレベルの発光信号が入力されるように、入力される各々信号の間に所定の時間間隔を置いて、クロックスキュー (skew) または遅延 (delay) に対するマージンを確保するためである。

#### 【0062】

このような選択信号および発光信号は、図4を通じて説明したように、第1走査駆動部310および第2走査駆動部320を通じて出力されてパネルに提供される。以下では、図6に図示される波形を備える選択信号および発光信号を出力する本発明の実施形態に係る走査駆動回路の構成および動作について説明する。

#### 【0063】

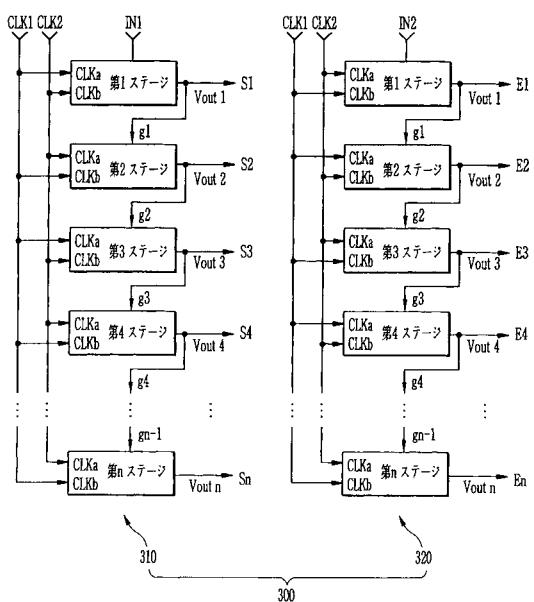

図7は、本発明の実施形態に係る走査駆動回路の構成を示すブロック図である。図7を参照すると、本発明の実施形態の走査駆動回路300は、上記で説明したように、M×N画素アレイ (Pixel Array) を駆動するための選択信号を出力する第1走査駆動部310と、発光信号を出力する第2走査駆動部320とで構成される。第1走査駆動部310および第2走査駆動部320の各々は、連続して接続される複数のn個のステージを具備する。第1走査駆動部310のn個のステージは、入力信号線 (IN1) または一つ前のステージの出力線に従属接続され、第2走査駆動部320のn個のステージは、入力信号線 (IN2) または一つ前のステージの出力線に従属接続される。より詳しく説明すると、第1走査駆動部310の第1ステージが、入力信号線 (IN1) に直接接続され、第2ステージは、第1ステージの出力線に接続され、第1ステージ以降のステージにおいて、一つ前のステージの出力線に接続される。よって、従属接続とは、入力信号線 (IN1) に直接接続される第1ステージを介して、第2～第nステージが間接的に入力信号線 (IN1) に接続されることを意味する。第2走査駆動部320のn個のステージにおいても、同様である。また、第1走査駆動部310および第2走査駆動部320の各々ステージは、第1クロック信号入力線 (CLK1) および第2クロック信号入力線 (CLK2) に接続される。

#### 【0064】

第1走査駆動部310のn個のステージの出力線は、画素アレイに含まれるn個の選択信号線 (S1～Sn) に接続され、第2走査駆動部320のn個のステージの出力線は、発光信号線 (E1～En) に接続されて、画素アレイを構成する各々の画素に、選択信号および発光信号を伝達する。ここで、第1走査駆動部310に具備される第1ステージには、最初入力信号 (IN1) が供給され、第2走査駆動部320に具備される第1ステージには、最初入力信号 (IN2) が供給されて、第1～第n-1ステージの出力信号は、各々の一つ後のステージに入力信号として供給される。

#### 【0065】

また、選択信号を出力する第1走査駆動部310の各ステージは、第1クロック端子 (CLKa) と第2クロック端子 (CLKb) とを具備する。第1走査駆動部310の奇数番目のステージで、第1クロック端子 (CLKa) は、第1クロック信号入力線 (CLK1) に接続されるので、第1クロック信号 (CLK1) が供給され、第2クロック端子 (CLKb) は、第2クロック信号入力線 (CLK2) に接続されるので、第2クロック信号 (CLK2) が供給される。これと反対に、第1走査駆動部310の偶数番目のステージで、第1クロック端子 (CLKa) は、第2クロック信号入力線 (CLK2) に接続されるので、第2クロック信号 (CLK2) が供給され、第2クロック端子 (CLKb) は、第1クロック信号入力線 (CLK1) に接続されるので、第1クロック信号 (CLK1) が供給される。ここで、第1クロック信号 (CLK1) および第2クロック信号 (CLK2)

10

20

30

40

50

K<sub>2</sub>)は、ローレベルおよびハイレベルの信号を繰り返して、互いに相反する位相を備える。

#### 【0066】

すなわち、最初入力信号(IN1)または一つ前のステージからの出力信号(gi)と、第1クロック信号(CLK1)および第2クロック信号(CLK2)の供給を受ける第1走査駆動部310の各々ステージは、最初入力信号(IN1)がローレベルの場合、各々ステージの出力線を通じて、順次ローレベルの選択信号を出力する。

#### 【0067】

一方、発光信号を出力する第2走査駆動部320の各ステージは、第1クロック端子(CLKa)と第2クロック端子(CLKb)を具備する。第2走査駆動部320の奇数番目のステージで、第1クロック端子(CLKa)は、第2クロック信号入力線(CLK2)に接続されるので、第2クロック信号(CLK2)が供給され、第2クロック端子(CLKb)は、第1クロック信号入力線(CLK1)に接続されるので、第1クロック信号(CLK1)が供給される。これと反対に、第2走査駆動部320の偶数番目のステージで、第1クロック端子(CLKa)は、第1クロック信号入力線(CLK1)に接続されるので、第1クロック信号(CLK1)が供給され、第2クロック端子(CLKb)は、第2クロック信号入力線(CLK2)に接続されるので、第2クロック信号(CLK2)が供給される。

#### 【0068】

すなわち、最初入力信号(IN2)または一つ前のステージからの出力信号(gi)と、第1クロック信号(CLK1)および第2クロック信号(CLK2)の供給を受ける第2走査駆動部320の各々ステージは、最初入力信号(IN2)がローレベルの場合、各々ステージの出力線を通じて、発光信号のレベルをデータフレームの1周期中、所定の期間、少なくとも一度以上順次ローレベルおよびハイレベル信号に変換して出力する。

#### 【0069】

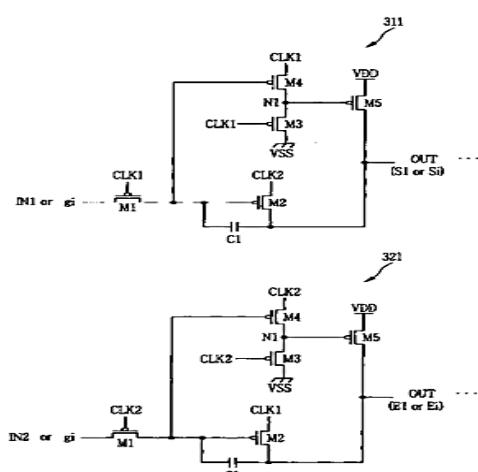

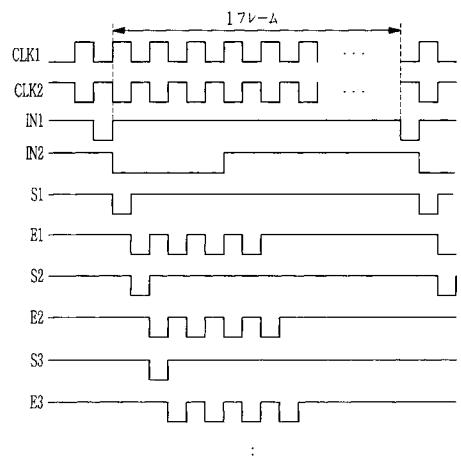

図8は、本発明の実施形態に係る走査駆動回路内の任意のステージに対する回路図であり、図7に図示される第1走査駆動部と第2走査駆動部の奇数番目のステージに対する具体的な回路構成を示すものである。また、図9は、図8に図示されるステージの入力信号/出力信号のタイミング図である。

#### 【0070】

図9を参照すると、第1クロック信号(CLK1)および第2クロック信号(CLK2)の1周期は、一つのローレベル信号および一つのハイレベル信号を出力する期間である。第1クロック信号(CLK1)および第2クロック信号(CLK2)の1周期は、第1期間および第2期間に区分され、第1期間および第2期間は、第1クロック信号(CLK1)および第2クロック信号(CLK2)のローレベル信号またはハイレベル信号を出力する期間に相当する。第1走査駆動部310および第2走査駆動部320の各々ステージは、第1期間の間には、フリーチャージを遂行して、第2期間の間に、評価遂行を行う。ここで、フリーチャージとは、最初入力信号(IN1またはIN2)または一つ前のステージからの出力信号(gi)の入力を受け付けることである。評価遂行とは、フリーチャージで入力される信号(最初入力信号(IN1またはIN2)または一つ前のステージからの出力信号(gi))のレベルに相当する信号を出力することである。

#### 【0071】

従って、第1走査駆動部310の奇数番目のステージ311および第2走査駆動部320の奇数番目のステージ321において、フリーチャージされる期間(第1期間)に、ローレベルの最初入力信号(IN1またはIN2)または一つ前のステージからの出力信号(gi)が入力される場合、評価遂行される期間(第2期間)では、ローレベルの信号(選択信号および発光信号)を出力し、ローレベルの信号(選択信号および発光信号)を第1走査駆動部310の偶数番目のステージおよび第2走査駆動部320の偶数番目のステージに印加する。よって、第1走査駆動部310の偶数番目のステージおよび第2走査駆動部320の偶数番目のステージでは、第1走査駆動部310の奇数番目のステージおよ

10

20

30

40

50

び第2走査駆動部320の奇数番目のステージより、第1クロック信号(CLK1)または第2クロック信号(CLK2)の1周期の半分だけシフトして、ローレベルの信号(選択信号および発光信号)を出力する。

#### 【0072】

すなわち、第1走査駆動部310および第2走査駆動部320の各々ステージにおいて、フリーチャージされる期間(第1期間)では、ハイレベルの信号(選択信号および発光信号)を出力する一方で、最初入力信号(IN1またはIN2)または一つ前のステージからの出力信号(gi)がローレベルである時、そのローレベル信号を入力(充電)する。評価される期間(第2期間)には、フリーチャージ期間に入力される信号レベルに相当する信号を出力する。また、第1走査駆動部310および第2走査駆動部320の各々ステージにおいて、奇数番目のステージの評価期間を偶数番目のステージのフリーチャージ期間と同じにすることで、ローレベルの信号が、第1クロック信号(CLK1)または第2クロック信号(CLK2)の1周期の半分だけの時間間隔で、すべてのステージに順次伝達するようとする。

#### 【0073】

以下、図8に図示される第1走査駆動部310の奇数番目のステージ311および第2走査駆動部320の奇数番目のステージ321の回路構成を通じて、より具体的にステージの動作を説明する。但し、ステージに具備されるトランジスタは、以下では、PMOS薄膜トランジスタを例として説明しているが、本発明の実施形態は、必ずしもこれに限定されない。

#### 【0074】

図8を参照すると、第1走査駆動部310の奇数番目のステージ311および第2走査駆動部320の奇数番目のステージ321は、第1クロック端子(CLK<sub>a</sub>)にゲート端子が接続され、最初入力信号(IN1またはIN2)または一つ前のステージから出力信号(gi)が入力される第1トランジスタ(M1)と、第1トランジスタ(M1)の出力端にゲート端子が接続され、第2クロック端子(CLK<sub>b</sub>)および出力線(out)に接続される第2トランジスタ(M2)と、第1クロック端子(CLK<sub>a</sub>)にゲート端子が接続され、第2電源(VSS)と第1ノード(N1)との間に接続される第3トランジスタ(M3)と、第1トランジスタ(M1)の出力端にゲート端子が接続され、第1クロック端子(CLK<sub>a</sub>)と第1ノード(N1)との間に接続される第4トランジスタ(M4)と、第1ノード(N1)にゲート端子が接続され、第1電源(VDD)と出力線(out)との間に接続される第5トランジスタ(M5)を含んで構成される。そして、第1走査駆動部310の奇数番目のステージ311の出力線は、一つ後の偶数番目のステージの第1トランジスタ(M1)のソースに接続される。第2走査駆動部320の場合についても、同様である。

#### 【0075】

また、第1トランジスタ(M1)の出力端と出力線(out)との間に接続される第1キャパシタ(C1)をさらに含んで構成される。ここで、ステージが第1走査駆動部310の奇数番目のステージ311の場合には、図7で図示されるように、第1クロック端子(CLK<sub>a</sub>)に第1クロック信号入力線(CLK1)が接続されるので、第1クロック信号(CLK1)が供給され、第2クロック端子(CLK<sub>b</sub>)に第2クロック信号入力線(CLK2)が接続されるので、第2クロック信号(CLK2)が供給される。これと反対に、ステージが偶数番目の場合には、第1クロック端子(CLK<sub>a</sub>)には、第2クロック信号入力線(CLK2)が接続されるので、第2クロック信号(CLK2)が供給され、第2クロック端子(CLK<sub>b</sub>)には、第1クロック信号入力線(CLK1)が接続されるので、第1クロック信号(CLK1)が供給される。以上、第1走査駆動部310の奇数番目のステージ、偶数番目のステージで、第1クロック端子(CLK<sub>a</sub>)、第2クロック端子(CLK<sub>b</sub>)に接続される第1クロック信号入力線(CLK1)、第2クロック信号入力線(CLK2)を互いに相反するようにすることで、互いに反対のレベルの信号が第1クロック端子(CLK<sub>a</sub>)、第2クロック端子(CLK<sub>b</sub>)に印加される。従って、フ

リーチャージされる期間にローレベルの信号が入力されると、各々ステージにおいて、一つ前のステージに比べて、第1クロック信号(CLK1)または第2クロック信号(CLK2)の1周期の半分だけシフトされるローレベルの選択信号が順次出力される。

#### 【0076】

一方、ステージが第2走査駆動部320の奇数番目のステージ321の場合には、図7で示されるように、第1クロック端子(CLK<sub>a</sub>)に第2クロック信号入力線(CLK2)が接続されるので、第2クロック信号(CLK2)が供給され、第2クロック端子(CLK<sub>b</sub>)に第1クロック信号入力線(CLK1)が接続されるので、第1クロック信号(CLK1)が供給される。これと反対に、ステージが偶数番目の場合には、第1クロック端子(CLK<sub>a</sub>)には、第1クロック信号入力線(CLK1)が接続されるので、第1クロック信号(CLK1)が供給され、第2クロック端子(CLK<sub>b</sub>)には、第2クロック信号入力線(CLK2)が接続されるので、第2クロック信号(CLK2)が供給される。また、第2電源(VSS)には、別途の負の電源が印加されるが、図8のように接地されて構成されることも可能である。本発明の実施形態では、第2電源が接地で具現される。

10

#### 【0077】

第1走査駆動部310および第2走査駆動部320の各々ステージは、大きく分けて伝達部、反転部、バッファーパートで構成される。伝達部は、第1トランジスタ(M1)、第2トランジスタ(M2)および第1キャパシタ(C1)で構成される。反転部は、第1トランジスタ(M1)、第3トランジスタ(M3)、第4トランジスタ(M4)で構成される。バッファーパートは、第5トランジスタ(M5)で構成される。

20

#### 【0078】

ステージが第1走査駆動部310の奇数番目のステージ311と仮定する場合、第1クロック信号(CLK1)がローレベル、すなわち、第2クロック信号(CLK2)がハイレベルである期間がフリーチャージ期間になる。第1クロック信号(CLK1)がハイレベル、すなわち、第2クロック信号(CLK2)がローレベルである期間が評価期間となる。フリーチャージ期間では、ハイレベルの信号(選択信号)を出力し、評価期間には、フリーチャージ期間に入力される信号レベルと同じレベルの信号(選択信号)を出力する。ステージが第1走査駆動部310の偶数番目のステージの場合、第1クロック信号(CLK1)がハイレベル、すなわち、第2クロック信号(CLK2)がローレベルである期間がフリーチャージ期間になる。第1クロック信号(CLK1)がローレベル、すなわち、第2クロック信号(CLK2)がハイレベルである期間が評価期間となる。

30

#### 【0079】

一方、ステージが第2走査駆動部320の奇数番目のステージ321と仮定する場合、第1クロック信号(CLK1)がハイレベル、すなわち、第2クロック信号(CLK2)がローレベルである期間がフリーチャージ期間になる。第1クロック信号(CLK1)がローレベル、すなわち、第2クロック信号(CLK2)がハイレベルである期間が評価期間になる。ステージが第2走査駆動部320の偶数番目のステージと仮定する場合、第1クロック信号(CLK1)がローレベル、すなわち、第2クロック信号(CLK2)がハイレベルである期間がフリーチャージ期間になる。第1クロック信号(CLK1)がハイレベル、すなわち、第2クロック信号(CLK2)がローレベルである期間が評価期間になる。第2走査駆動部320の各々ステージにおいて、フリーチャージ期間では、ハイレベルの信号(発光信号)を出力し、評価期間には、フリーチャージ期間に入力される信号レベルと同じレベルの信号(発光信号)を出力する。

40

#### 【0080】

図8および図9を参照すると、第1走査駆動部310の奇数番目のステージ311に対する回路の動作をよく見れば、まず、フリーチャージ期間、すなわち、第1クロック信号(CLK1)がローレベル、第2クロック信号(CLK2)がハイレベルに入力される間には、第1トランジスタ(M1)、第3トランジスタ(M3)がオンになり、入力信号線(IN1)より第1トランジスタ(M1)に印加される最初入力信号(IN1)または一

50

つ前のステージからの出力信号 (g\_i) がそれぞれ第 2 トランジスタ (M2), 第 4 トランジスタ (M4) のゲート端子に伝達される。したがって, フリーチャージ期間には, 第 1 キャパシタ (C1) に, 入力信号としての一つ前のステージからの出力信号 (g\_i) または最初入力信号 (IN1) に相当する電圧が保存される。第 1 ノード (N1) には, 第 1 クロック信号 (CLK1) または第 2 電源 (VSS) によってローレベルの信号が充電されるので, 第 5 トランジスタ (M5) がオンされて, ハイレベルの第 1 電源 (VDD) が出力端を通じて出力される。すなわち, フリーチャージ期間で, ステージのバッファ部 (第 5 トランジスタ (M5)) よる出力は, ハイレベルになる。

#### 【0081】

また, 第 1 走査駆動部 310 の奇数番目のステージ 311 の評価期間の間, すなわち, 第 1 クロック信号 (CLK1) がハイレベル, 第 2 クロック信号 (CLK2) がローレベルに入力される間には, 第 1 トランジスタ (M1) がオフされるので, 最初入力信号 (IN1) または一つ前のステージからの出力信号 (g\_i) が遮断される。このため第 2 トランジスタ (M2), 第 4 トランジスタ (M4) もオフされる。第 3 トランジスタ (M3) も第 1 トランジスタ (M1) とともに, オフされる。この時, フリーチャージ期間の間に入力 (保存) される信号, すなわち, 一つ前のステージからの出力信号 (g\_i) または最初入力信号 (IN1) がハイレベルの場合には, フリーチャージ期間で, 第 1 キャパシタ (C1) にハイレベルの信号が保存されるので, 評価期間において, 第 2 トランジスタ (M2), 第 4 トランジスタ (M4) はオフされる。しかし, フリーチャージ期間で, 第 3 トランジスタ (M3) は, オンとなるので, 第 1 ノード (N1) は, 第 2 電源 (VSS) のローレベルの信号が充電されるので, 第 5 トランジスタ (M5) はオンされ, 第 5 トランジスタ (M5) (バッファ部) は, 第 1 電源 (VDD) から相変らずハイレベルを出力するようになる。以上, 第 1 走査駆動部 310 の奇数番目のステージの回路動作について説明したが, 第 1 走査駆動部 310 の偶数番目のステージでは, 奇数番目のステージで入力されるクロック信号が反対となり, 回路動作は同じなので, 詳細な説明は, 略する。

#### 【0082】

本発明の実施形態によれば, フリーチャージ期間で, 第 5 トランジスタ (M5) を通じて, 第 1 電源 (VDD) のハイレベルの信号が出力されるので, 従来の走査駆動回路より, ハイレベルで出力される信号がトランジスタの特性偏差の影響を受けないため, 走査駆動回路の誤作動を防止できる。フリーチャージ期間で, ハイレベルの一つ前のステージからの出力信号 (g\_i) または最初入力信号 (IN1) が入力される場合における評価期間においても, 同様である。また, ハイレベルの信号を出力する時, 第 5 トランジスタ (M5) を通じて, 第 1 電源 (VDD) のハイレベルの信号が出力されるので, 従来の走査駆動回路のようにインバータの出力端を充電しないので, 漏れる電流 (leakage current) を最小化でき, 放電効率を改善して動作速度を向上できる。

#### 【0083】

一方, 評価期間の間, フリーチャージ期間の間に入力される信号, すなわち, 一つ前のステージからの出力信号 (g\_i) または最初入力信号 (IN1) がローレベルの場合には, 第 1 キャパシタ (C1) によって保存されるローレベルの信号によって, 第 2 トランジスタ (M2) がオンされ, 第 4 トランジスタ (M4) がオンになる。第 4 トランジスタ (M4) がオンされることによって, 第 1 ノード (N1) に, 第 4 トランジスタ (M4) を通じて, ハイレベルの第 1 クロック信号 (CLK1) が充電されるので, 第 5 トランジスタ (M5) はオフされる。このため, 伝達部では, 第 2 トランジスタ (M2) がオンになることによって, ローレベル値を備える第 2 クロック信号 (CLK2) が出力端を通じて出力される。

#### 【0084】

本発明の実施形態によれば, 走査駆動回路にインバータを用いないので, フリーチャージ期間に入力される一つ前のステージからの出力信号 (g\_i) または最初入力信号 (IN1) がローレベルの場合には, 走査駆動回路にスタティック電流が流れないため, 従来の走査駆動回路に比べて, 消費電力を低減することができる。また, 評価期間において, 第

10

20

30

40

50

2トランジスタ(M2)を通じて、ローレベルの第2クロック信号(CLK2)が出力線から出力されるので、従来の走査駆動回路より、ローレベルで出力される信号がトランジスタの特性偏差の影響を受けないため、走査駆動回路の誤作動を防止できる。さらに、ローレベルの信号を出力する時、第2トランジスタ(M2)を通じて、ローレベルの第2クロック信号(CLK2)が出力線から出力されるので、従来の走査駆動回路のようにインバータの出力端を放電する電流の減少程度を最小化でき、放電効率を改善して動作速度を向上できる。

#### 【0085】

以上説明したように、第1走査駆動部310の奇数番目のステージ311の評価期間において、ステージは、以前フリーチャージ期間に入力される信号、すなわち、一つ前のステージからの出力信号(gi)または最初入力信号(IN1)がローレベルの場合には、ローレベルの信号(ローレベルの選択信号)を出力し、ハイレベルの場合には、ハイレベルの信号(ハイレベルの選択信号)を出力する。結果的に、最初入力信号(IN1)または一つ前のステージからの出力信号(gi)と、第1クロック信号(CLK1)および第2クロック信号(CLK2)の供給を受ける第1走査駆動部310の各ステージは、第1期間の間には、フリーチャージを遂行し、第2期間の間に評価を遂行して、第1期間にローレベルの信号が印加される場合、一つ前のステージに比べて、ローレベルの信号(選択信号)を第1クロック信号(CLK1)または第2クロック信号(CLK2)の1周期の半分(第1期間または第2期間)だけシフトして、出力する。

#### 【0086】

すなわち、フリーチャージ期間では、ハイレベルの出力し、最初入力信号(IN1)または一つ前のステージからの出力信号(gi)の入力を受ける。評価期間には、フリーチャージ期間に入力される信号レベルと同じレベルの信号を出力することで、ローレベルの最初入力信号(IN1)が印加される場合、各ステージの出力線を通じて順次ローレベルの信号を出力することができる。第1走査駆動部310の各々のステージにおいて、順次出力されるローレベルの信号は、画素部の各画素に供給される選択信号となる。

#### 【0087】

図8および図9に図示される第2走査駆動部320の奇数番目のステージ321に対する回路の構成は、説明した第1走査駆動部310の奇数番目のステージ311に対する回路の構成と同様なので、回路の動作を含めた詳細な説明は、省略する。

#### 【0088】

但し、第2走査駆動部320の奇数番目のステージ321には、第1クロック端子(CLKa)に第2クロック信号(CLK2)が供給され、第2クロック端子(CLKb)に第1クロック信号(CLK1)が供給されるので、結果的には、第1走査駆動部310の奇数番目のステージ311の第1クロック端子(CLKa)および第2クロック端子(CLKb)に入力される信号とは、互いに反転されて入力されることを特徴とする。したがって、第1走査駆動部310と第2走査駆動部320において、フリーチャージ期間および評価期間は、図9に図示されるように、互いに行き違って構成されるのである。つまり、第1走査駆動部310の奇数番目のステージの評価期間は、第2走査駆動部320の奇数番目のステージのフリーチャージ期間に相当し、第1走査駆動部310の奇数番目のステージのフリーチャージ期間は、第2走査駆動部320の奇数番目のステージの評価期間に相当する。

#### 【0089】

すなわち、第1走査駆動部310の偶数番目のステージの第1クロック端子(CLKa)、第2クロック端子(CLKb)に入力される第1クロック信号(CLK1)、第2クロック信号(CLK2)は、第2走査駆動部320の奇数番目のステージの第1クロック端子(CLKa)、第2クロック端子(CLKb)に入力される第1クロック信号(CLK1)、第2クロック信号(CLK2)と同じとなる。これと同様に、第1走査駆動部310の奇数番目のステージの第1クロック端子(CLKa)、第2クロック端子(CLKb)に入力される第1クロック信号(CLK1)、第2クロック信号(CLK2)は、第

10

20

30

40

50

2走査駆動部320の偶数番目のステージの第1クロック端子(CLKa), 第2クロック端子(CLKb)に入力される第1クロック信号(CLK1), 第2クロック信号(CLK2)と同じとなる。

#### 【0090】

これによって、第1走査駆動部310の奇数番目のステージが、ローレベルの出力を出す時、第2走査駆動部320の奇数番目のステージは、ハイレベルの出力を出し、第1クロック信号(CLK1), 第2クロック信号(CLK2)の1周期の半分後に、ローレベルの出力を出すようになる。言い換えると、第1走査駆動部310の奇数番目のステージで、評価遂行される期間に、第2走査駆動部320の奇数番目のステージでは、フリーチャージが行われ、第1走査駆動部310の奇数番目のステージで、評価遂行によって、選択信号が出力された後に、第2走査駆動部320の奇数番目のステージでは、評価遂行が行われ、発光信号を出力する。これは、第1走査駆動部310の偶数番目のステージ、第2走査駆動部320の偶数番目のステージについても、同様である。従って、図6のように、第1走査駆動部310からローレベルの選択信号が出力されて、画素回路でデータ線からのデータ電流(IDATA)が充電される記録期間(Pw)の後、第2走査駆動部320からローレベルの発光信号が出力されて、画素回路の有機EL素子(OLED)が発光する1次発光期間(Pon)が始まる。

#### 【0091】

また、第2走査駆動部320に入力される最初入力信号(IN2)は、図9に図示されるように、第1走査駆動部310に入力される最初入力信号(IN1)とは異なって、第1クロック信号(CLK1), 第2クロック信号(CLK2)の複数の周期に相当する所定の期間、ローレベルに提供することを特徴とする。ここで、所定の期間は、データフレームの1周期内の一定の期間となる。データフレームの1周期とは、第1走査駆動部310および第2走査駆動部320に各々の最初入力信号(IN1, IN2)が入力され、選択信号および発光信号が出力される期間である。

#### 【0092】

これによって、最初入力信号(IN2)による第2走査駆動部320の各ステージの出力信号(発光信号)は、所定の期間に対応して、少なくとも一度以上順次ローレベルおよびハイレベル信号に変換されて出力される。これは、画素部の各画素に提供される発光信号となる。従って、本発明の実施形態によれば、データフレームの1周期の所定の期間、発光信号が少なくとも一度以上順次ローレベルおよびハイレベル信号に変換されるので、有機電界発光表示装置の各々画素の劣化を防止できる。ここで、所定の期間がデータフレームの1周期の全部になる場合、所定の期間に対応して、第2走査駆動部320の出力信号、すなわち、発光信号は、データフレームの1周期の50%に相当する期間、ローレベル信号で提供される。結果的に、各画素に具備される有機EL素子(OLED)の発光期間がデータフレームの1周期の50%となる。

#### 【0093】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されることは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それについても当然に本発明の技術的範囲に属するものと了解される。

#### 【図面の簡単な説明】

#### 【0094】

【図1】従来の一般的な走査駆動回路の構成を示すブロック図である。

【図2】図1に図示される走査駆動回路における任意のステージの回路図である。

【図3】図2に図示されるステージの入力信号/出力信号波形図である。

【図4】本発明の実施形態に係る有機電界発光表示装置を概略的に図示するブロック図である。

【図5】図4に図示される有機電界発光表示装置の各画素領域に具備される画素回路の実施形態を現わす回路図である。

【図6】図5の画素回路に入力される選択信号および発光信号に対するタイミング図である。

【図7】本発明の実施形態に係る走査駆動回路の構成を示すブロック図である。

【図8】本発明の実施形態に係る走査駆動回路内の任意のステージに対する回路図である。

【図9】図8に図示されるステージの入力信号／出力信号のタイミング図である。

【符号の説明】

【0095】

3 0 0 走査駆動回路

3 1 0 第1走査駆動部

10

3 1 1 第1走査駆動部の奇数番目のステージ

3 2 0 第2走査駆動部

3 2 1 第2走査駆動部の奇数番目のステージ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 09 G 3/20 611A

H 05 B 33/14 A

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 使用扫描驱动器扫描驱动电路和有机电致发光显示设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2007086727A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2007-04-05 |

| 申请号            | JP2006108759                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2006-04-11 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 申東蓉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 申 東蓉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/325 G09G3/20 G09G3/3266 G09G2300/0842 G09G2310/0286 G09G2330/021 G11C19/184                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/30.J G09G3/20.622.A G09G3/20.622.C G09G3/20.622.D G09G3/20.622.G G09G3/20.611.A H05B33/14.A G09G3/20.622.E G09G3/3233 G09G3/3266 G09G3/3283 G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC04 3K107/CC14 3K107/CC21 3K107/EE03 3K107/HH02 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD09 5C080/DD26 5C080/JJ02 5C080/JJ03 5C080/JJ04 5B074/AA10 5B074/CA01 5C380/AA01 5C380/AB06 5C380/BA01 5C380/BA10 5C380/BA20 5C380/BA34 5C380/BA50 5C380/BC20 5C380/BD07 5C380/CA13 5C380/CB01 5C380/CB14 5C380/CB17 5C380/CB18 5C380/CB26 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC61 5C380/CC63 5C380/CD014 5C380/CE20 5C380/CF07 5C380/CF10 5C380/CF22 5C380/CF23 5C380/CF43 5C380/DA02 5C380/DA06 5C380/DA32 |         |            |

| 优先权            | 1020050087425 2005-09-20 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | <a href="#">JP4612580B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

### 摘要(译)

在有机发光显示装置中使用的扫描驱动电路。栅极端子连接到扫描驱动电路的每一级的第一时钟端子，并且来自前一级的第一输入信号 ( IN1 或 IN2 ) 或输出信号 ( gi ) 被输入到第一级。栅极端子连接至晶体管 ( M1 ) 和第一晶体管的输出端子，第二晶体管 ( M2 ) 连接至第二时钟端子和输出线，并且栅极端子连接至第一时钟端子。 ( 2 ) 连接在电源 ( VSS ) 和第一节点 ( N1 ) 之间的第三晶体管 ( M3 ) ，和连接到第一晶体管的输出端子的栅极端子，其连接第一时钟端子和第一节点。它包括连接在它们之间的第四晶体管 ( M4 ) 和第五晶体管 ( M5 ) ，该第五晶体管的栅极端子连接到第一节点并且连接在第一电源 ( VDD ) 和输出线之间。 [选择图]图8