(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-91089

(P2006-91089A)

(43) 公開日 平成18年4月6日(2006.4.6)

| (51) Int.CI.                | F 1                                                | テマコード (参考) |

|-----------------------------|----------------------------------------------------|------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K007                                  |            |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B 5C080                               |            |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 641C<br>G09G 3/20 641D<br>G09G 3/20 680H |            |

審査請求 未請求 請求項の数 28 O L (全 40 頁) 最終頁に続く

|           |                              |          |                                                     |

|-----------|------------------------------|----------|-----------------------------------------------------|

| (21) 出願番号 | 特願2004-273206 (P2004-273206) | (71) 出願人 | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号          |

| (22) 出願日  | 平成16年9月21日 (2004.9.21)       | (74) 代理人 | 100096699<br>弁理士 鹿嶋 英實                              |

|           |                              | (72) 発明者 | 白崎 友之<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター内 |

|           |                              | (72) 発明者 | 山口 郁博<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター内 |

最終頁に続く

(54) 【発明の名称】画素駆動回路及び画像表示装置

## (57) 【要約】

【課題】 製造プロセスの簡素化や歩留まりの向上を図りつつ、開口率や信頼性の向上を実現して、表示品質が良好な画素駆動回路及び画像表示装置を提供する。

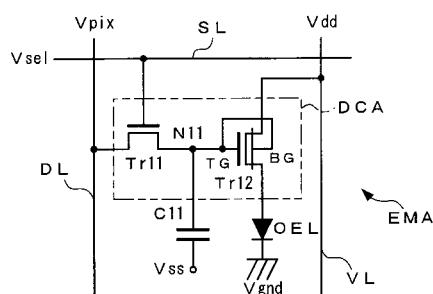

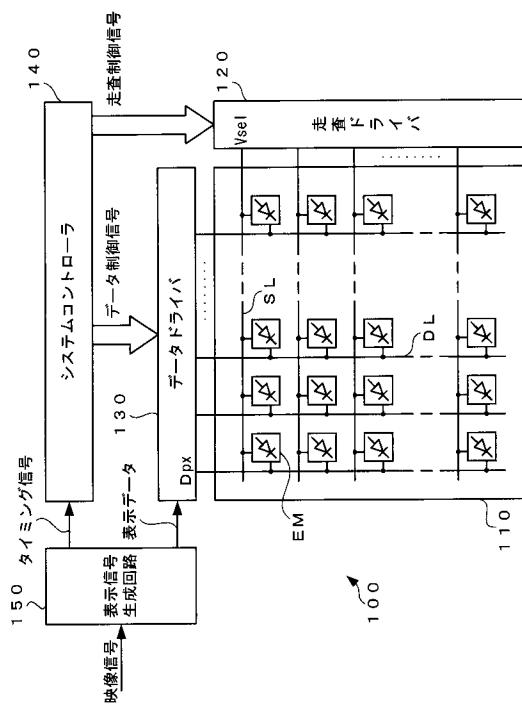

【解決手段】 表示画素E M Aは、走査ラインS LとデータラインD Lとの各交点近傍に、ゲート端子が走査ラインS Lに、ソース端子及びドレイン端子がデータラインD L及び接点N 11に各々接続された薄膜トランジスタTr 11と、トップゲート端子T G及びボトムゲート端子B Gが接点N 11に、ソース端子Sが電源ラインV Lに各々接続されたダブルゲート型トランジスタTr 12と、接点N 11と所定の低電位電源V ssとの間に接続されたコンデンサC 11とを備えた画素駆動回路D C A、及び、該画素駆動回路D C Aのダブルゲート型トランジスタTr 12のドレイン端子Dにアノード端子が接続され、カソード端子が接地電位に接続された有機EL素子O E Lを有して構成されている。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

表示画素に設けられた電流制御型の発光素子に対して、階調信号に応じた電流値を有する発光駆動電流を供給して、前記階調信号に基づく所定の輝度階調で発光動作させる画素駆動回路において、

少なくとも、

前記階調信号に基づく電荷を電圧成分として保持する電荷保持手段と、

該電荷保持手段に保持された電圧成分に基づいて、前記発光駆動電流を生成して、前記発光素子に供給する駆動電流制御手段と、

を備え、

前記駆動電流制御手段は、半導体層の上方に設けられた第1のゲート電極と、前記半導体層の下方に設けられた第2のゲート電極と、前記半導体層の両端部に設けられたソース電極及びドレイン電極と、を具備するダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする画素駆動回路。

**【請求項 2】**

前記駆動電流制御手段は、前記第1のゲート電極と前記第2のゲート電極が電気的に接続されていることを特徴とする請求項1記載の画素駆動回路。

**【請求項 3】**

前記電荷保持手段は、前記第1のゲート電極及び前記第2のゲート電極と前記ソース電極が対向することにより形成される容量成分であることを特徴とする請求項1又は2記載の画素駆動回路。

**【請求項 4】**

前記駆動電流制御手段は、前記半導体層がアモルファスシリコンからなることを特徴とする請求項1乃至3のいずれかに記載の画素駆動回路。

**【請求項 5】**

前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に設けられた絶縁膜上に延在するように設けられていることを特徴とする請求項1乃至4のいずれかに記載の画素駆動回路。

**【請求項 6】**

前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に直接延在するように設けられていることを特徴とする請求項1乃至4のいずれかに記載の画素駆動回路。

**【請求項 7】**

前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、同一になるように設定されていることを特徴とする請求項5又は6記載の画素駆動回路。

**【請求項 8】**

前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、異なるように設定されていることを特徴とする請求項5又は6記載の画素駆動回路。

**【請求項 9】**

前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極のうち、前記発光素子に直接接続される側の一の電極が前記半導体層上に重なり合うように延在する寸法が、他の電極の延在する寸法に対して短くなるように設定されていることを特徴とする請求項8記載の画素駆動回路。

**【請求項 10】**

前記駆動電流制御手段は、前記第1のゲート電極が前記ソース電極と前記ドレイン電極との間の領域に設けられていることを特徴とする請求項1乃至9のいずれかに記載の画素駆動回路。

**【請求項 11】**

10

20

30

40

50

前記階調信号は、前記輝度階調に応じた電流値を有する信号電流であることを特徴とする請求項1乃至10のいずれかに記載の画素駆動回路。

**【請求項12】**

前記階調信号は、前記輝度階調に応じた電圧値を有する信号電圧であることを特徴とする請求項1乃至10のいずれかに記載の画素駆動回路。

**【請求項13】**

前記画素駆動回路は、前記階調信号を前記電荷保持手段に供給するタイミングを制御する階調信号制御手段を備えていることを特徴とする請求項1乃至12のいずれかに記載の画素駆動回路。

**【請求項14】**

前記階調信号制御手段は、単一のゲート電極を備える電界効果型トランジスタにより構成されていることを特徴とする請求項13記載の画素駆動回路。

**【請求項15】**

前記階調信号制御手段は、ダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする請求項13記載の画素駆動回路。

**【請求項16】**

表示パネルに互いに直行するように配設された複数の走査ライン及び複数の信号ラインの各交点近傍に配置された複数の表示画素に対して、前記各信号ラインを介して、表示データに応じた階調信号を供給することにより、前記表示パネルに所望の画像情報を表示する画像表示装置において、

前記各表示画素は、電流制御型の発光素子と、前記発光素子の発光動作を制御する画素駆動回路と、を備え、

前記画素駆動回路は、少なくとも、前記階調信号に基づく電荷を電圧成分として保持する電荷保持手段と、該電荷保持手段に保持された電圧成分に基づいて、前記発光駆動電流を生成して、前記発光素子に供給する駆動電流制御手段と、前記階調信号を前記電荷保持手段に供給するタイミングを制御する階調信号制御手段と、を備え、

前記駆動電流制御手段は、半導体層の上方に設けられた第1のゲート電極と、前記半導体層の下方に設けられた第2のゲート電極と、前記半導体層の両端部に設けられたソース電極及びドレイン電極と、を具備するダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする画像表示装置。

**【請求項17】**

前記画像表示装置は、少なくとも、

前記走査ラインに選択信号を印加して、前記走査ラインに接続された前記表示画素に設けられた前記階調信号制御手段により、前記階調信号の当該表示画素への書き込みを可能とする選択状態に設定する走査駆動手段と、

前記選択状態に設定された前記表示画素に対応した前記表示データに基づく前記階調信号を生成して、前記信号ラインに供給する信号駆動手段と、

を備えることを特徴とする請求項16記載の画像表示装置。

**【請求項18】**

前記信号駆動手段から供給される前記階調信号は、前記表示データに応じた電流値を有する信号電流であることを特徴とする請求項16又は17記載の画像表示装置。

**【請求項19】**

前記信号駆動手段から供給される前記階調信号は、前記表示データに応じた電圧値を有する信号電圧であることを特徴とする請求項16又は17記載の画像表示装置。

**【請求項20】**

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記第1のゲート電極と前記第2のゲート電極が電気的に接続されていることを特徴とする請求項16乃至19のいずれかに記載の画像表示装置。

**【請求項21】**

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレイ

10

20

30

40

50

ン電極が前記半導体層上に設けられた絶縁膜上に延在するように設けられていることを特徴とする請求項 16 乃至 20 のいずれかに記載の画像表示装置。

【請求項 22】

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレン電極が前記半導体層上に直接延在するように設けられていることを特徴とする請求項 16 乃至 20 のいずれかに記載の画像表示装置。

【請求項 23】

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレン電極が前記半導体層上に重なり合うように延在する寸法が、同一になるように設定されていることを特徴とする請求項 21 又は 22 記載の画像表示装置。 10

【請求項 24】

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレン電極が前記半導体層上に重なり合うように延在する寸法が、異なるように設定されていることを特徴とする請求項 21 又は 22 記載の画像表示装置。

【請求項 25】

前記画素駆動回路に設けられる前記駆動電流制御手段は、前記第 1 のゲート電極が前記ソース電極と前記ドレン電極との間の領域に設けられていることを特徴とする請求項 16 乃至 24 のいずれかに記載の画像表示装置。

【請求項 26】

前記画素駆動回路に設けられる前記階調信号制御手段は、単一のゲート電極を備える電界効果型トランジスタにより構成されていることを特徴とする請求項 16 記載の画像表示装置。 20

【請求項 27】

前記画素駆動回路に設けられる前記階調信号制御手段は、ダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする請求項 16 記載の画像表示装置。

【請求項 28】

前記発光素子は、有機エレクトロルミネッセント素子であることを特徴とする請求項 16 乃至 27 のいずれかに記載の画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素駆動回路及び画像表示装置に関し、特に、階調信号に応じた発光駆動電流に基づいて、電流制御型の発光素子を所定の輝度階調で発光動作させるための画素駆動回路、及び、該画素駆動回路と上記発光素子とからなる表示画素を 2 次元配列した表示パネルを備えた画像表示装置に関する。 30

【背景技術】

【0002】

従来、有機エレクトロルミネッセント素子（以下、「有機 E L 素子」と略記する）や無機エレクトロルミネッセント素子、発光ダイオード（L E D）等のように、供給される駆動電流の電流値に応じて所定の輝度階調で発光動作する電流制御型の発光素子を具備する表示画素を、2 次元配列した表示パネルを備えた発光素子型のディスプレイ（表示装置）が知られている。 40

【0003】

特に、アクティブマトリックス駆動方式を適用した発光素子型ディスプレイは、携帯情報機器を始め、パーソナルコンピュータやテレビジョン受像器等、様々な電子機器に広く利用されている液晶表示装置（L C D）に比較して、表示応答速度が速く、また、視野角依存性もなく、高輝度・高コントラスト化、表示画質の高精細化等が可能であるとともに、液晶表示装置の場合のように、バックライトを必要としないので、一層の薄型軽量化や低消費電力化が可能である、という極めて優位な特徴を有しており、次世代のディスプレイとして研究開発が盛んに行われている。 50

## 【0004】

そして、このような発光素子型ディスプレイにおいては、上述した電流制御型の発光素子を発光制御するための駆動制御機構や制御方法が種々提案されている。例えば、特許文献1や特許文献2等に記載されているように、表示パネルを構成する各表示画素ごとに、上記発光素子に加えて、該発光素子を発光制御するための複数のスイッチング手段からなる駆動回路(画素駆動回路)を備えたものが知られている。

## 【0005】

以下、従来技術における、画素駆動回路を備えた表示画素について簡単に説明する。

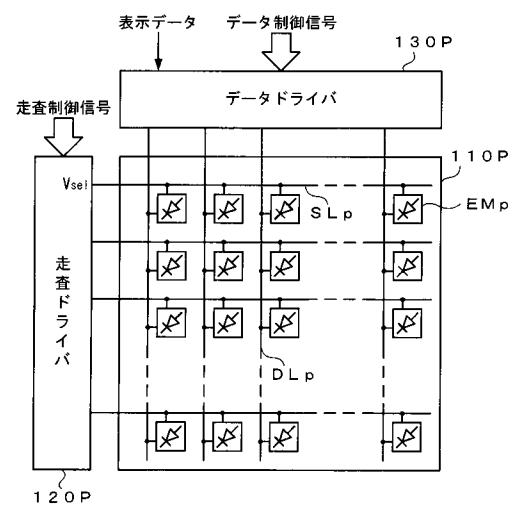

図24は、従来技術における発光素子型ディスプレイの要部を示す概略構成図である。

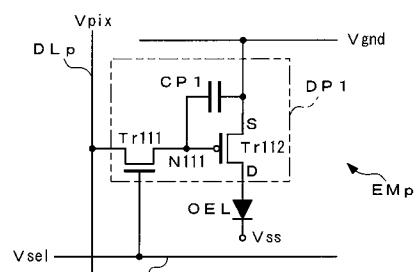

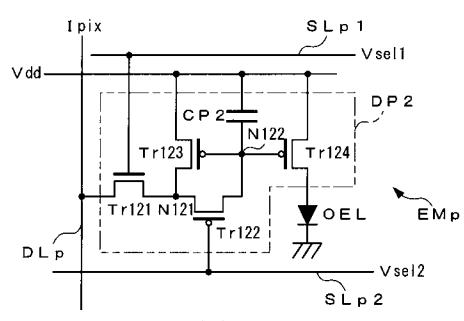

図25は、従来技術における発光素子型ディスプレイに適用可能な各表示画素(画素駆動回路及び発光素子)の要部構成例を示す等価回路図である。

10

## 【0006】

従来技術におけるアクティブマトリクス型の発光素子型ディスプレイ(有機EL表示装置)は、概略、図24に示すように、行、列方向に配設された複数の走査ライン(選択ライン)SLp及びデータライン(信号ライン)DLpの各交点近傍に、複数の表示画素EMPがマトリクス状に配置された表示パネル110Pと、各走査ラインSLpに接続された走査ドライバ(走査線駆動回路)120Pと、各データラインDLpに接続されたデータドライバ(データ線駆動回路)130Pと、を備え、データドライバ130Pにおいて表示データに応じた階調信号(後述する階調信号電圧Vpix、もしくは、階調信号電流Ipix)を生成して、各データラインDLpを介して各表示画素EMPに供給する構成を有している。

20

## 【0007】

ここで、特許文献1等に記載された表示画素EMPは、図25(a)に示すように、ゲート端子が走査ラインSLpに、ソース端子及びドレイン端子がデータラインDLp及び接点N111に各々接続された薄膜トランジスタ(TFT)Tr111と、ゲート端子が接点N111に接続され、ソース端子に接地電位Vgndが印加された薄膜トランジスタTr112と、を備えた画素駆動回路DP1、及び、該画素駆動回路DP1の薄膜トランジスタTr112のドレイン端子にアノード端子が接続され、カソード端子に接地電位Vgndよりも低い低電源電圧Vssが印加された有機EL素子(電流制御型の発光素子)OELを有して構成されている。

30

## 【0008】

ここで、図25(a)において、CP1は、薄膜トランジスタTr112のゲート-ソース間に形成される寄生容量(保持容量)である。また、薄膜トランジスタTr111は、nチャネル型の電界効果型トランジスタにより構成され、薄膜トランジスタTr112は、pチャネル型の電界効果型トランジスタにより構成されている。

## 【0009】

そして、このような構成を有する表示画素EMPからなる表示パネル110Pを備えた表示装置においては、まず、走査ドライバ120Pから各行の走査ラインSLpに選択レベル(ハイレベル)の走査信号Vselを順次印加することにより、行ごとの表示画素EMP(画素駆動回路DP1)の薄膜トランジスタTr111がオン動作して、当該表示画素EMPが選択状態に設定される。

40

## 【0010】

この選択タイミングに同期して、データドライバ130Pにより表示データに応じた電圧値を有する階調信号電圧Vpixを生成して、各列のデータラインDLpに印加することにより、当該階調信号電圧Vpixが各表示画素EMP(画素駆動回路DP1)の薄膜トランジスタTr111を介して、接点N111(すなわち、薄膜トランジスタTr112のゲート端子)に印加される。これにより、薄膜トランジスタTr112が当該階調信号電圧Vpixに応じた導通状態でオン動作して、接地電位Vgndから所定の発光駆動電流が薄膜トランジスタTr112及び有機EL素子OELを介して低電源電圧Vssに流れ、有機EL素子OELが表示データに応じた輝度階調で発光動作する。

50

## 【0011】

次いで、走査ドライバ120Pから走査ラインS L pに非選択レベル(ローレベル)の走査信号V selを印加することにより、行ごとの各行の表示画素E M pの薄膜トランジスタT r 1 1 1がオフ動作して、当該表示画素E M pが非選択状態に設定され、データラインD L pと画素駆動回路D P 1とが電気的に遮断される。このとき、薄膜トランジスタT r 1 1 2のゲート端子に印加され、寄生容量C P 1に保持された電圧に基づいて、薄膜トランジスタT r 1 1 2は、オン状態を持続することになり、上記選択状態と同様に、接地電位V gndから所定の発光駆動電流が薄膜トランジスタT r 1 1 2を介して有機E L 素子O E Lに流れて、発光動作が継続される。この発光動作は、次の表示データに応じた階調信号電圧V pixが各行の表示画素E M pに印加される(書き込まれる)まで、例えは、1フレーム期間継続するように制御される。

## 【0012】

このような駆動制御方法は、各表示画素E M p(画素駆動回路D P 1の薄膜トランジスタT r 1 1 2のゲート端子)に印加する電圧(階調信号電圧V pix)を調整することにより、有機E L 素子O E Lに流す発光駆動電流の電流値を制御して、所定の輝度階調で発光動作させていることから、電圧指定方式(又は、電圧印加方式)と呼ばれている。

## 【0013】

一方、特許文献2等に記載された表示画素は、図25(b)に示すように、相互に並行して配設された一組の走査ラインS L p 1、S L p 2(上述した走査ラインS L pに相当する)とデータラインD L pとの各交点近傍に、ゲート端子が走査ラインS L p 1に、ソース端子及びドレイン端子がデータラインD L p及び接点N 1 2 1に各々接続された薄膜トランジスタT r 1 2 1と、ゲート端子が走査ラインS L p 2に、ソース端子及びドレイン端子が接点N 1 2 1及び接点N 1 2 2に各々接続された薄膜トランジスタT r 1 2 2と、ゲート端子が接点N 1 2 2に、ドレイン端子が接点N 1 2 1に各々接続され、ソース端子に高電圧V ddが印加された薄膜トランジスタT r 1 2 3と、ゲート端子が接点N 1 2 2に接続され、ソース端子に高電源電圧V ddが印加された薄膜トランジスタT r 1 2 4とを備えた画素駆動回路D P 2、及び、該画素駆動回路D P 2の薄膜トランジスタT r 1 2 4のドレイン端子にアノード端子が接続され、カソード端子に接地電位V gndが印加された有機E L 素子O E Lを有して構成されている。

## 【0014】

ここで、図25(b)において、C P 2は、薄膜トランジスタT r 1 2 3及びT r 1 2 4のゲート-ソース間に形成される寄生容量(保持容量)である。また、薄膜トランジスタT r 1 2 1は、nチャネル型の電界効果型トランジスタにより構成され、薄膜トランジスタT r 1 2 2乃至T r 1 2 4は、pチャネル型の電界効果型トランジスタにより構成されている。

## 【0015】

そして、このような構成を有する表示画素E M pからなる表示パネル110Pを備えた表示装置においては、まず、走査ドライバ120Pから各行の走査ラインS L p 1にハイレベルの走査信号V sel1を、走査ラインS L p 2にローレベルの走査信号V sel2を各々印加して行ごとの表示画素E M p(画素駆動回路D P 2)を選択状態に設定することにより、薄膜トランジスタT r 1 2 1、T r 1 2 2及びT r 1 2 3がオン動作し、この選択タイミングに同期して、データドライバ130Pにより表示データに応じた電流値を有する階調信号電流I pixを生成して、各列のデータラインD L pに供給することにより、当該階調信号電流I pixが薄膜トランジスタT r 1 2 1及びT r 1 2 3を介して高電圧V ddに流れる。

## 【0016】

このとき、薄膜トランジスタT r 1 2 2により薄膜トランジスタT r 1 2 3のゲート-ドレイン間が電気的に短絡されるため、薄膜トランジスタT r 1 2 3は、飽和領域でオン動作する。これにより、上記階調信号電流I pixの電流レベルが薄膜トランジスタT r 1 2 3により電圧レベルに変換されてゲート-ソース間に所定の電圧が生じる(書き動作)

。

**【0017】**

この薄膜トランジスタTr123のゲート-ソース間に生じた電圧に応じて薄膜トランジスタTr124がオン動作し、高電源電圧Vddから所定の発光駆動電流が薄膜トランジスタTr124及び有機EL素子OELを介して接地電位Vgndに流れ、有機EL素子OELが表示データに応じた輝度階調で発光動作する（発光動作）。

**【0018】**

次いで、走査ラインSLp2にハイレベルの走査信号Vsel2を印加すると、薄膜トランジスタTr122がオフ動作することにより、薄膜トランジスタTr123のゲート-ソース間に生じた電圧が寄生容量CP2により保持され、次に、走査ラインSLp1にローレベルの走査信号Vsel1を印加すると、薄膜トランジスタTr121がオフ動作することにより、データラインDLpと画素駆動回路DP2とが電気的に遮断される。これにより、上記寄生容量CP2に保持された電圧に基づく電位差により、薄膜トランジスタTr124が継続してオン動作し、高電源電圧Vddから所定の発光駆動電流が薄膜トランジスタTr124及び有機EL素子OELを介して接地電位に流れ、有機EL素子OELの発光動作が継続される。この発光動作は、次の表示データに応じた階調信号電流Ipixが各表示画素EMPに書き込まれるまで、例えば、1フレーム期間継続するように制御される。

**【0019】**

このような駆動制御方法は、各表示画素EMP（画素駆動回路DP2の薄膜トランジスタTr123のソース-ドレイン間）に供給する電流（階調信号電流Ipix）に応じて、寄生容量（保持容量）CP2に保持される電圧を調整することにより、有機EL素子OELに流す発光駆動電流の電流値を制御して、所定の輝度階調で発光動作させていることから、電流指定方式又は電流印加方式と呼ばれている。

**【0020】**

なお、図25に示した各回路構成は、電圧指定方式及び電流指定方式の駆動制御方法に対応した表示画素（画素駆動回路）の一例を示すものに過ぎず、画素駆動回路を構成するスイッチング手段（薄膜トランジスタ）の個数やそのチャネル極性については、各種考案されており、例えば、単一のチャネル極性の薄膜トランジスタのみを用いた回路構成も知られている。

**【0021】**

**【特許文献1】**特開2002-156923号公報（第3頁～第4頁、図1、図2）

**【特許文献2】**特開2001-147659号公報（第7頁～第8頁、図1）

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0022】**

上述したような回路構成を有する表示画素（画素駆動回路）を適用した表示パネルにおいて、当該表示パネルの大型化や高精細化に伴って、画素数が増加すると、製造プロセスの増加や煩雑化、製品歩留まりの低下や製品コストの高騰を招く。そこで、画素駆動回路を構成する各薄膜トランジスタを、例えば、アモルファスシリコンを用いたトランジスタ構造にすることにより、単結晶シリコンを適用した場合に比較して、製造プロセスが簡単で、かつ、その製造技術が確立され、さらに、素子特性の安定性も高い、アモルファスシリコン製造プロセスを適用することができるので、安価に素子特性に優れた表示パネルを実現することができる。

**【0023】**

しかしながら、アモルファスシリコン薄膜トランジスタは、電子移動度が低いため、例えば、発光素子に発光駆動電流を供給する発光駆動用の薄膜トランジスタにこのようなアモルファスシリコン薄膜トランジスタを適用した場合、所定の階調信号に対応した駆動電流を流すために、（1）当該薄膜トランジスタのゲート電極幅（ゲート幅）を大きく設定するとともに、（2）ゲート電極の長さ（ゲート長）を短く設定したり、あるいは、（3）所定の駆動電流を流すために、ゲートに印加される電圧（ゲート電圧）を高く設定した

10

20

30

40

50

り、する必要があった。

【0024】

この場合、ゲート幅を大きく設定することは、予め規定された各表示画素の形成面積において、当該ゲートが占める面積が大きくなるため、相対的に発光素子の発光領域の面積が減少することになり、開口率の低下を招くという問題を有している。

また、ゲート長を短く設定することは、微細加工を必要とするため、製品歩留まりの低下や製品コストの上昇を招くという問題を有している。

さらに、ゲート電圧を高く設定することは、消費電力の増加を招くとともに、当該薄膜トランジスタの特性劣化が進行して製品寿命が短命化し、動作不良等が生じて製品の信頼性の低下を招くという問題を有している。

【0025】

そこで、本発明は、上述した課題に鑑み、製造プロセスの簡素化や歩留まりの向上を図りつつ、開口率や信頼性の向上を実現して、表示品質が良好な画素駆動回路及び画像表示装置を提供することを目的とする。

【課題を解決するための手段】

【0026】

請求項1記載の発明は、表示画素に設けられた電流制御型の発光素子に対して、階調信号に応じた電流値を有する発光駆動電流を供給して、前記階調信号に基づく所定の輝度階調で発光動作させる画素駆動回路において、少なくとも、前記階調信号に基づく電荷を電圧成分として保持する電荷保持手段と、該電荷保持手段に保持された電圧成分に基づいて、前記発光駆動電流を生成して、前記発光素子に供給する駆動電流制御手段と、を備え、前記駆動電流制御手段は、半導体層の上方に設けられた第1のゲート電極と、前記半導体層の下方に設けられた第2のゲート電極と、前記半導体層の両端部に設けられたソース電極及びドレイン電極と、を具備するダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする。

【0027】

請求項2記載の発明は、請求項1記載の画素駆動回路において、前記駆動電流制御手段は、前記第1のゲート電極と前記第2のゲート電極が電気的に接続されていることを特徴とする。

請求項3記載の発明は、請求項1又は2記載の画素駆動回路において、前記電荷保持手段は、前記第1のゲート電極及び前記第2のゲート電極と前記ソース電極が対向することにより形成される容量成分であることを特徴とする。

【0028】

請求項4記載の発明は、請求項1乃至3のいずれかに記載の画素駆動回路において、前記駆動電流制御手段は、前記半導体層がアモルファスシリコンからなることを特徴とする。

請求項5記載の発明は、請求項1乃至4のいずれかに記載の画素駆動回路において、前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に設けられた絶縁膜上に延在するように設けられていることを特徴とする。

【0029】

請求項6記載の発明は、請求項1乃至4のいずれかに記載の画素駆動回路において、前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に直接延在するように設けられていることを特徴とする。

請求項7記載の発明は、請求項5又は6記載の画素駆動回路において、前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、同一になるように設定されていることを特徴とする。

【0030】

請求項8記載の発明は、請求項5又は6記載の画素駆動回路において、前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、異なるように設定されていることを特徴とする。

10

20

30

40

50

請求項 9 記載の発明は、請求項 8 記載の画素駆動回路において、前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極のうち、前記発光素子に直接接続される側の一つの電極が前記半導体層上に重なり合うように延在する寸法が、他の電極の延在する寸法に對して短くなるように設定されていることを特徴とする。

【 0 0 3 1 】

請求項 10 記載の発明は、請求項 1 乃至 9 のいずれかに記載の画素駆動回路において、前記駆動電流制御手段は、前記第 1 のゲート電極が前記ソース電極と前記ドレイン電極との間の領域に設けられていることを特徴とする。

請求項 11 記載の発明は、請求項 1 乃至 10 のいずれかに記載の画素駆動回路において、前記階調信号は、前記輝度階調に応じた電流値を有する信号電流であることを特徴とする。10

【 0 0 3 2 】

請求項 12 記載の発明は、請求項 1 乃至 10 のいずれかに記載の画素駆動回路において、前記階調信号は、前記輝度階調に応じた電圧値を有する信号電圧であることを特徴とする。

請求項 13 記載の発明は、請求項 1 乃至 12 のいずれかに記載の画素駆動回路において、前記画素駆動回路は、前記階調信号を前記電荷保持手段に供給するタイミングを制御する階調信号制御手段を備えていることを特徴とする。

【 0 0 3 3 】

請求項 14 記載の発明は、請求項 13 記載の画素駆動回路において、前記階調信号制御手段は、単一のゲート電極を備える電界効果型トランジスタにより構成されていることを特徴とする。20

請求項 15 記載の発明は、請求項 13 記載の画素駆動回路において、前記階調信号制御手段は、ダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする。

【 0 0 3 4 】

請求項 16 記載の発明は、表示パネルに互いに直行するように配設された複数の走査ライン及び複数の信号ラインの各交点近傍に配置された複数の表示画素に対して、前記各信号ラインを介して、表示データに応じた階調信号を供給することにより、前記表示パネルに所望の画像情報を表示する画像表示装置において、前記各表示画素は、電流制御型の発光素子と、前記発光素子の発光動作を制御する画素駆動回路と、を備え、前記画素駆動回路は、少なくとも、前記階調信号に基づく電荷を電圧成分として保持する電荷保持手段と、該電荷保持手段に保持された電圧成分に基づいて、前記発光駆動電流を生成して、前記発光素子に供給する駆動電流制御手段と、前記階調信号を前記電荷保持手段に供給するタイミングを制御する階調信号制御手段と、を備え、前記駆動電流制御手段は、半導体層の上方に設けられた第 1 のゲート電極と、前記半導体層の下方に設けられた第 2 のゲート電極と、前記半導体層の両端部に設けられたソース電極及びドレイン電極と、を具備するダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする。30

【 0 0 3 5 】

請求項 17 記載の発明は、請求項 16 記載の画像表示装置において、前記画像表示装置は、少なくとも、前記走査ラインに選択信号を印加して、前記走査ラインに接続された前記表示画素に設けられた前記階調信号制御手段により、前記階調信号の当該表示画素への書き込みを可能とする選択状態に設定する走査駆動手段と、前記選択状態に設定された前記表示画素に対応した前記表示データに基づく前記階調信号を生成して、前記信号ラインに供給する信号駆動手段と、を備えることを特徴とする。40

【 0 0 3 6 】

請求項 18 記載の発明は、請求項 16 又は 17 記載の画像表示装置において、前記信号駆動手段から供給される前記階調信号は、前記表示データに応じた電流値を有する信号電流であることを特徴とする。

請求項 19 記載の発明は、請求項 16 又は 17 記載の画像表示装置において、前記信号駆動手段から供給される前記階調信号は、前記表示データに応じた電圧値を有する信号電50

圧であることを特徴とする。

【0037】

請求項20記載の発明は、請求項16乃至19のいずれかに記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記第1のゲート電極と前記第2のゲート電極が電気的に接続されていることを特徴とする。

請求項21記載の発明は、請求項16乃至20のいずれかに記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に設けられた絶縁膜上に延在するように設けられていることを特徴とする。

【0038】

請求項22記載の発明は、請求項16乃至20のいずれかに記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に直接延在するように設けられていることを特徴とする。

請求項23記載の発明は、請求項21又は22記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、同一になるように設定されていることを特徴とする。

【0039】

請求項24記載の発明は、請求項21又は22記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記ソース電極及び前記ドレイン電極が前記半導体層上に重なり合うように延在する寸法が、異なるように設定されていることを特徴とする。

【0040】

請求項25記載の発明は、請求項16乃至24のいずれかに記載の画像表示装置において、前記画素駆動回路に設けられる前記駆動電流制御手段は、前記第1のゲート電極が前記ソース電極と前記ドレイン電極との間の領域に設けられていることを特徴とする。

請求項26記載の発明は、請求項16記載の画像表示装置において、前記画素駆動回路に設けられる前記階調信号制御手段は、単一のゲート電極を備える電界効果型トランジスタにより構成されていることを特徴とする。

【0041】

請求項27記載の発明は、請求項16記載の画像表示装置において、前記画素駆動回路に設けられる前記階調信号制御手段は、ダブルゲート型の薄膜トランジスタ構造を有していることを特徴とする。

請求項28記載の発明は、請求項16乃至27のいずれかに記載の画像表示装置において、前記発光素子は、有機エレクトロルミネッセント素子であることを特徴とする。

【発明の効果】

【0042】

すなわち、本発明に係る画素駆動回路は、有機EL素子や発光ダイオード等のように、供給される電流値に応じて所定の輝度で自己発光する電流制御型の発光素子に対して、所望の輝度階調で発光動作させるための発光駆動電流を供給する画素駆動回路において、少なくとも、階調信号（階調信号電圧、階調信号電流）に対応した電流値を有する発光駆動電流を上記発光素子に流す駆動電流制御手段を構成するスイッチング素子が、ダブルゲート型トランジスタにより構成されている。

【0043】

ここで、画素駆動回路に供給された階調信号は、容量成分からなる電荷保持手段に電圧成分として保持され、該電圧成分が上記ダブルゲート型トランジスタのゲート端子（トップゲート端子及びボトムゲート端子）に印加されて、上記発光駆動電流の電流値が制御される。

【0044】

このような構成を有する画素駆動回路によれば、駆動電流制御手段を構成するダブルゲ

10

20

30

40

50

ート型トランジスタが、電子移動度が比較的低いアモルファスシリコン半導体層を用いたトランジスタ構造を有している場合であっても、单一のゲート電極を備えた周知の電界効果型トランジスタ（薄膜トランジスタ）に比較して、電圧・電流特性（ゲート電圧に対するドレイン電流）が改善するので、同一のゲート電圧で、より大きなドレイン電流（発光駆動電流）を発光素子に流すことができる。

#### 【0045】

また、これは換言すると、同一のドレイン電流（発光駆動電流）を流すためには、駆動電流制御手段を構成するスイッチング素子の素子サイズ（ダブルゲート型トランジスタのゲート幅）を小さくすることができる意味するので、表示画素の形成領域の面積が一定の場合には、相対的に発光素子（有機EL素子等）の形成面積を増やすことができ、発光輝度を向上させることができる。10

#### 【0046】

また、この場合、発光素子を同一の輝度で発光させる場合、発光駆動電流の電流密度を小さくすることもできるので、有機EL素子の素子特性の劣化や消費電力を抑制することもできる。

さらに、同一のドレイン電流を流すために、ゲート電圧を低く設定することができるので、ゲート電極に高電圧が継続的に印加されることによるトランジスタ特性の劣化を抑制して、動作特性に優れた画素駆動回路を実現することができる。

#### 【0047】

また、本発明に係る画素駆動回路においては、駆動電流制御手段を構成するダブルゲート型トランジスタのゲート端子に、階調信号に応じたゲート電圧を印加する電荷保持手段として、ダブルゲート型トランジスタを構成するトップゲート電極（第1のゲート電極）とソース電極、及び、ボトムゲート電極（第2のゲート電極）とソース電極とを所定の絶縁膜を介して対向して（積層して）形成することにより、所望の容量値を有する容量成分を、比較的狭い領域（面積）で形成することができる。20

#### 【0048】

また、本発明に係る画素駆動回路において、階調電流として所望の電流値を有する階調信号電流を供給して、発光駆動電流の電流値を制御する場合（電流印加方式）にあっては、駆動電流制御手段としてダブルゲート型トランジスタを適用することにより、書き電流（階調信号電流）に対する発光駆動電流の関係（電流特性）が良好な線形性を示し、また、書き電流（階調信号電流）に対する書き率（書き特性）も、单一のゲート電極を備えた周知の電界効果型トランジスタに比較して顕著に改善するので、発光素子を階調信号に応じた適切な輝度階調で発光動作させることができる。30

#### 【0049】

さらに、本発明に係る画素駆動回路においては、駆動電流制御手段を構成するダブルゲート型トランジスタのソース、ドレイン電極が半導体層上に延在する寸法を異なるように形成した構成を有するものであってもよいし、ソース、ドレイン電極を半導体層上に直接延在するように形成された構成を有するものであってもよい。

#### 【0050】

これにより、ダブルゲート型トランジスタの電圧・電流特性（ゲート電圧に対するドレイン電流）が、顕著に改善するので、発光素子を同一の輝度で発光させる場合（すなわち、同一の発光駆動電流を流す場合）、ダブルゲート型トランジスタのトランジスタサイズをより小さくできるとともに、ゲート電圧を低電圧化してトランジスタ特性の劣化を一層抑制することができる。40

#### 【0051】

そして、本発明に係る画像表示装置は、上述したような回路構成を有する画素駆動回路と電流制御型の発光素子とを備えた表示画素を、相互に直交する複数の走査ラインと複数の信号ライン（データライン）の各交点近傍に、配列した表示パネルを備えることにより、走査駆動手段（走査ドライバ）により各走査ラインに接続された表示画素を選択状態に設定し、信号駆動手段（データドライバ）により表示データに基づく電圧値又は電流値を50

有する階調信号（階調信号電圧、階調信号電流）を、当該表示画素に供給することにより、階調信号（表示データ）に応じた輝度階調で各表示画素（発光素子）を発光動作させる。

### 【0052】

これにより、各表示画素に設けられる画素駆動回路が、電圧印加方式及び電流印加方式のいずれの駆動制御方法に対応した画素駆動回路であっても、発光素子に発光駆動電流を供給する駆動電流制御手段がダブルゲート型トランジスタにより構成されていることにより、電圧・電流特性が改善するので、所定の発光輝度で発光素子を発光動作させる場合（所定の電流値を有する発光駆動電流を発光素子に流す場合）、トランジスタサイズを周知の電界効果型トランジスタに比較して縮小することができ、相対的に発光素子の形成面積を増加させて、表示パネルの開口率を向上させることができる。10

### 【0053】

また、所定の発光輝度で発光素子を発光動作させる場合、ダブルゲート型トランジスタに印加するゲート電圧を低電圧化することができるるので、当該トランジスタの素子特性の劣化を抑制して、表示特性に優れた表示パネルを実現することができるとともに、画像表示動作に伴う消費電力を抑制することができる。その場合、発光素子に流す発光駆動電流の電流密度を小さくすることができるので、発光素子の素子特性の劣化を抑制して表示パネルの製品寿命を長くすることができる。

### 【発明を実施するための最良の形態】

#### 【0054】

以下に、本発明に係る画素駆動回路及び該画素駆動回路を表示パネルに備えた画像表示装置の実施の形態について、詳しく説明する。20

##### <画像表示装置の全体構成>

まず、本発明に係る画像表示装置の全体構成について、図面を参照して説明する。

図1は、本発明に係る表示装置の全体構成の一例を示すブロック図である。

#### 【0055】

図1に示すように、本発明に係る表示装置100は、概略、行方向及び列方向に各々配設された複数の走査ラインSLと複数のデータライン（信号ライン）DLとの各交点近傍に、電流制御型の発光素子を備えた複数の表示画素EMが配列された表示パネル110と、該表示パネル110の各走査ラインSLに接続され、各走査ラインSLに所定のタイミングで順次走査信号Vselを印加することにより、行ごとの表示画素EMを選択状態に設定（走査）する走査ドライバ（走査駆動手段）120と、表示パネル110の各データラインDLに接続され、表示データに基づく階調信号Dpxを生成して、各データラインDLに供給するデータドライバ（信号駆動手段）130と、少なくとも、走査ドライバ120及びデータドライバ130の動作状態を制御するための走査制御信号及びデータ制御信号を生成して出力するシステムコントローラ140と、表示装置100の外部から供給される映像信号に基づいて、デジタル信号からなる表示データ（表示信号）を生成して、上記データドライバ130に供給するとともに、該表示データに基づいて表示パネル110に所定の画像情報を表示するためのタイミング信号（システムクロック等）を抽出、又は、生成してシステムコントローラ140に供給する表示信号生成回路150と、を備えて構成されている。3040

#### 【0056】

##### （表示パネル）

表示パネル110にマトリクス状に配列された表示画素EMは、走査ドライバ120から走査ラインSLに印加される走査信号Vsel、及び、信号ドライバ130からデータラインDLに供給される階調信号Dpx（具体的には、階調信号電圧Vpix又は階調信号電流Ipix）に基づいて、表示画素EMへの当該階調信号Dpxの書き動作、及び、階調信号Dpxに基づく輝度階調での発光素子の発光動作を制御する画素駆動回路と、該画素駆動回路から供給される発光駆動電流の電流値に応じた輝度階調で発光動作する有機EL素子OLELや発光ダイオード等の電流制御型の発光素子と、を有して構成されている。50

## 【0057】

ここで、画素駆動回路は、走査信号  $V_{sel}$  に基づいて選択状態又は非選択状態に設定され、選択状態において表示データに応じた階調信号  $D_{px}$  を取り込んで電圧レベルとして保持し、非選択状態において保持した電圧レベルに応じた発光駆動電流を発光素子に流して、所定の輝度階調で継続的に発光させる機能を有している。なお、本発明に適用可能な表示画素（画素駆動回路）の具体例については後述する。

## 【0058】

## (走査ドライバ120)

走査ドライバ120は、システムコントローラ140から供給される走査制御信号に基づいて、各走査ラインSLに選択レベル（例えば、ハイレベル）の走査信号  $V_{sel}$  を順次印加することにより、各行ごとの表示画素EMを選択状態に設定し、データドライバ130により各データラインDLを介して供給される、表示データに基づく階調信号  $D_{px}$  を、各表示画素EM（画素駆動回路）に書き込むように制御する。

## 【0059】

ここで、走査ドライバ120は、例えば、シフトレジスタとバッファからなるシフトブロックが、各走査ラインSLに対応して複数段設けられ、後述するシステムコントローラ140から供給される走査制御信号（走査スタート信号、走査クロック信号等）に基づいて、シフトレジスタによりシフト信号を順次シフトしつつ、生成されたシフト信号を、バッファを介して所定の電圧レベル（ハイレベル）に変換して走査信号  $V_{sel}$  として各走査ラインSLに順次出力する、周知の構成を適用することができる。

## 【0060】

## (データドライバ130)

データドライバ130は、システムコントローラ140から供給されるデータ制御信号（出力イネーブル信号、データラッチ信号、サンプリングスタート信号、シフトクロック信号等）に基づいて、表示信号生成回路150から供給される表示データを所定のタイミングで取り込んで保持し、該表示データに対応するアナログ信号電圧又はアナログ信号電流を生成して、階調信号  $D_{px}$ （階調信号電圧  $V_{data}$  又は階調信号電流  $I_{pix}$ ）として各データラインDLに供給するように制御する。

## 【0061】

## (システムコントローラ140)

システムコントローラ140は、後述する表示信号生成回路150から供給されるタイミング信号に基づいて、少なくとも、走査ドライバ120及びデータドライバ130に対して、走査制御信号及びデータ制御信号を生成して出力することにより、各ドライバを所定のタイミングで動作させて、走査信号  $V_{sel}$  及び階調信号  $D_{px}$  を生成させ、各走査ラインSL及びデータラインDLに印加して各表示画素（画素駆動回路及び発光素子）EMにおける発光動作を連続的に実行させて、所定の映像信号に基づく画像情報を表示パネル110に表示させる制御を行う。

## 【0062】

## (表示信号生成回路150)

表示信号生成回路150は、例えば、表示装置100の外部から供給される映像信号から輝度階調信号成分を抽出して、表示パネル110の1行分ごとに、該輝度階調信号成分をデジタル信号からなる表示データとしてデータドライバ130に供給する。ここで、上記映像信号が、テレビ放送信号（コンポジット映像信号）のように、画像情報の表示タイミングを規定するタイミング信号成分を含む場合には、表示信号生成回路150は、図1に示すように、上記輝度階調信号成分を抽出する機能のほか、タイミング信号成分を抽出してシステムコントローラ140に供給する機能を有するものであってもよい。この場合においては、上記システムコントローラ140は、表示信号生成回路150から供給されるタイミング信号に基づいて、走査ドライバ120やデータドライバに対して個別に供給する走査制御信号及びデータ制御信号を生成する。

## 【0063】

10

20

30

40

50

なお、表示装置 100 の外部から供給される映像信号がデジタル信号により形成され、また、タイミング信号が映像信号とは別に供給されている場合には、当該映像信号（デジタル信号）をそのまま表示データとして、データドライバ 130 に供給するとともに、当該タイミング信号を直接システムコントローラ 140 に供給するようにして、表示信号生成回路 150 を省略するようにしてもよい。

#### 【0064】

##### <表示画素>

次に、上述した本実施形態に係る表示装置に適用される表示パネルに配列される表示画素（画素駆動回路）について、図面を参照して詳しく説明する。

ここで、本発明に係る画像表示装置に適用される表示画素は、上述した従来技術に示したような、電圧印加方式の駆動制御方法に対応した画素駆動回路を備えるものであってもよいし、電流印加方式に対応した画素駆動回路を備えるものであってもよい。また、以下に示す構成例においては、各駆動制御方法に対応した画素駆動回路を備えた表示画素について、各々一例を示すが、本発明はこれに限定されるものではなく、表示データに基づく階調信号電圧又は階調信号電流に応じた電圧成分を保持し、当該電圧成分に基づく発光駆動電流を生成して、電流制御型の発光素子に供給する構成を有するものであれば、他の回路構成を有するものであってもよい。

#### 【0065】

##### (第1の実施形態)

図2は、本発明に係る画素駆動回路を備えた表示画素の第1の実施形態を示す回路構成図である。

図2に示すように、本実施形態に係る表示画素EMAは、上述した表示パネル110に相互に直交するように配設された走査ラインSLとデータラインDLとの各交点近傍に、例えば、ゲート端子が走査ラインSLに、ソース端子及びドレイン端子がデータラインDL及び接点N11に各々接続された薄膜トランジスタ（TFT；階調信号制御手段）Tr11と、トップゲート端子TG及びボトムゲート端子BGが接点N11に、ソース端子Sが電源ラインVL（高電位電源Vdd）に各々接続されたダブルゲート型の薄膜トランジスタ（ダブルゲート型トランジスタ；駆動電流制御手段）Tr12と、接点N11と所定の低電位電源Vss（例えば、接地電位）との間に接続されたコンデンサ（電荷保持手段）C11とを備えた画素駆動回路DCA、及び、該画素駆動回路DCAのダブルゲート型トランジスタTr12のドレイン端子Dにアノード端子が接続され、カソード端子が接地電位に接続された有機EL素子（発光素子）OELを有して構成されている。

#### 【0066】

また、本実施形態に係る画素駆動回路DCAにおいては、薄膜トランジスタTr11及びダブルゲート型トランジスタTr12は、例えば、いずれもnチャネル型の半導体層をチャネル領域として備えた素子構造を有し、特に、ダブルゲート型トランジスタTr12は、当該半導体層がアモルファスシリコンにより形成されている。

#### 【0067】

すなわち、本実施形態に係る画素駆動回路においては、少なくとも、発光素子である有機EL素子OELに発光駆動電流を供給する発光駆動用のスイッチング素子として、一般的な電界効果型トランジスタ（薄膜トランジスタ）ではなく、後述するようなダブルゲート型の薄膜トランジスタ（ダブルゲート型トランジスタ）を適用した構成を有している。なお、ダブルゲート型トランジスタの素子構造及びその素子特性については、詳しく後述する。

#### 【0068】

このような構成を有する画素駆動回路DCAの駆動制御動作は、まず、走査ドライバ120から走査ラインSLに対してハイレベルの走査信号Vselを印加することにより、トランジスタTr11がオン動作して当該画素駆動回路DCAが選択状態に設定される。この選択状態に同期して、データドライバ130からデータラインDLを介して表示データに基づく電圧値を有する階調信号電圧Vpixを印加することにより、当該階調信号電圧Vp

10

20

30

40

50

$v_{ix}$ が薄膜トランジスタ  $T_{r11}$  を介して、ダブルゲート型トランジスタ  $T_{r12}$  のトップゲート端子  $T_G$  及びボトムゲート端子  $B_G$  に印加される。これにより、ダブルゲート型トランジスタ  $T_{r12}$  が階調信号電圧  $V_{pix}$  に応じた導通状態でオン動作して、電源ライン  $V_L$  からダブルゲート型トランジスタ  $T_{r12}$  を介して所定の発光駆動電流が流れ、有機EL素子  $OEL$  が表示データに応じた輝度階調で発光する。

#### 【0069】

次いで、選択ライン  $S_L$  にローレベルの走査信号  $V_{sel}$  を印加することにより、トランジスタ  $T_{r11}$  がオフ動作して当該画素駆動回路  $DCA$  が非選択状態に設定される。これにより、データライン  $DL$  と画素駆動回路  $DCA$  とが電気的に遮断されて、ダブルゲート型トランジスタ  $T_{r12}$  のトップゲート端子  $T_G$  及びボトムゲート端子  $B_G$  に印加された電圧がコンデンサ  $C_{11}$  に保持されて、ダブルゲート型トランジスタ  $T_{r12}$  は、オン状態を維持することになり、電源ライン  $V_L$  からダブルゲート型トランジスタ  $T_{r12}$  を介して有機EL素子  $OEL$  に所定の発光駆動電流が流れ、発光動作が継続される。この発光動作は、次の表示データに応じた階調信号電圧  $V_{pix}$  が当該表示画素  $EMA$  (画素駆動回路  $DCA$ ) に書き込まれるまで、例えば、1フレーム期間継続されるように制御される。

#### 【0070】

##### (第2の実施形態)

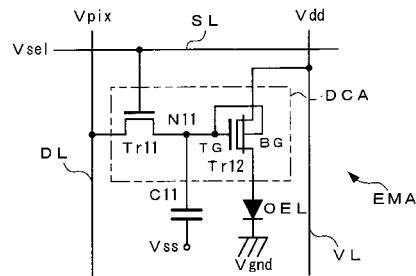

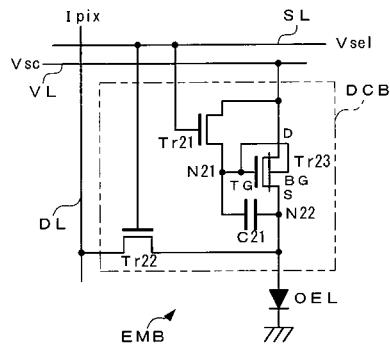

図3は、本発明に係る画素駆動回路を備えた表示画素の第2の実施形態を示す回路構成図である。

図3に示すように、本実施形態に係る表示画素  $EMB$  は、上述した表示パネル  $110$  に相互に直交するように配設された走査ライン  $S_L$  とデータライン  $DL$  との各交点近傍に、例えば、ゲート端子が走査ライン  $S_L$  に、ソース端子及びドレイン端子が電源ライン  $V_L$  (電源電圧  $V_{sc}$ ) 及び接点  $N_{21}$  に各々接続された薄膜トランジスタ  $T_{r21}$  と、ゲート端子が走査ライン  $S_L$  に、ソース端子及びドレイン端子がデータライン  $DL$  及び接点  $N_{22}$  に各々接続された薄膜トランジスタ (階調信号制御手段)  $T_{r22}$  と、トップゲート端子  $T_G$  及びボトムゲート端子  $B_G$  が接点  $N_{21}$  に、ソース端子  $S$  及びドレイン端子  $D$  が電源ライン  $V_L$  及び接点  $N_{22}$  に各々接続されたダブルゲート型の薄膜トランジスタ (ダブルゲート型トランジスタ；駆動電流制御手段)  $T_{r23}$  と、接点  $N_{21}$  と接点  $N_{22}$  の間に接続されたコンデンサ (電荷保持手段)  $C_{21}$  と、を備えた画素駆動回路  $DCB$ 、及び、該画素駆動回路  $DCB$  の接点  $N_{22}$  にアノード端子が接続され、カソード端子が接地電位に接続された有機EL素子 (発光素子)  $OEL$  を有して構成されている。ここで、コンデンサ  $C_{21}$  は、ダブルゲート型トランジスタ  $T_{r23}$  のトップゲート電極及びボトムゲート電極とソース電極間に形成される容量成分であってもよい。

#### 【0071】

また、本実施形態に係る画素駆動回路  $DCB$  においては、薄膜トランジスタ  $T_{r21}$ 、 $T_{r22}$  及びダブルゲート型トランジスタ  $T_{r23}$  は、例えば、いずれも  $n$  チャネル型の半導体層をチャネル領域として備えた素子構造を有し、特に、ダブルゲート型トランジスタ  $T_{r23}$  は、当該半導体層がアモルファスシリコンにより形成されている。

#### 【0072】

すなわち、本実施形態に係る画素駆動回路においても、少なくとも、発光駆動用のスイッチング素子として、一般的な電界効果型トランジスタ (薄膜トランジスタ) ではなく、後述するようなダブルゲート型の薄膜トランジスタ (ダブルゲート型トランジスタ) を適用した構成を有している。

#### 【0073】

次いで、本実施形態に係る表示画素 (画素駆動回路) の駆動制御方法について、詳しく説明する。なお、ここでは、上述した回路構成を有する画素駆動回路を備えた表示画素が、複数2次元配列された上記表示パネル  $110$  における画像情報の表示動作と関連付けながら説明する。

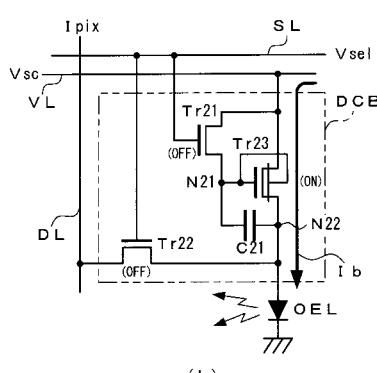

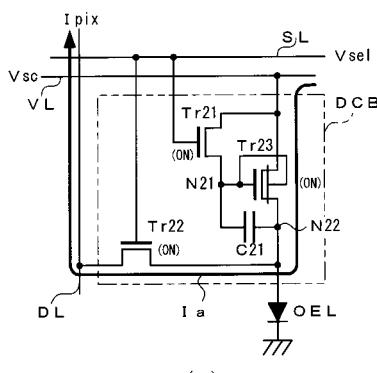

図4は、本実施形態に係る表示画素 (画素駆動回路) の動作状態を示す概念図であり、

10

20

30

40

50

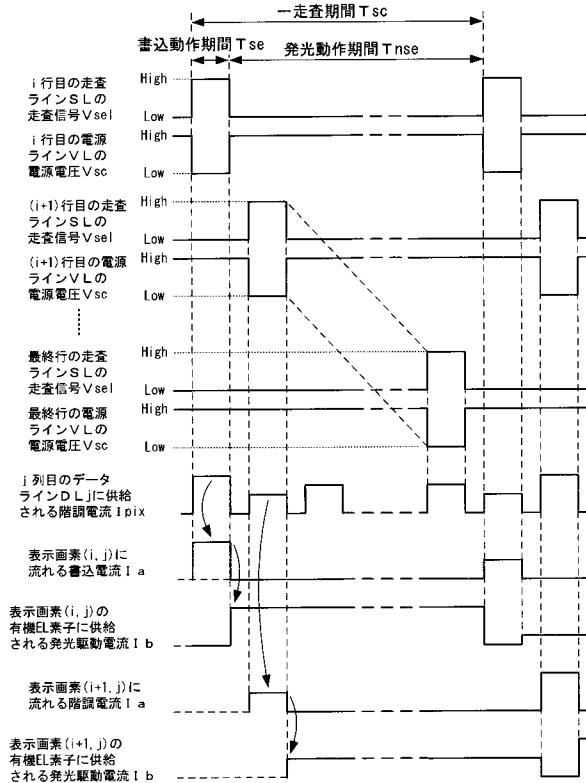

図5は、本実施形態に係る画素駆動回路を適用した表示画素の基本動作を示すタイミングチャートである。

#### 【0074】

上述したような構成を有する画素駆動回路DCBにおける発光素子(有機EL素子OEL)の駆動制御方法(発光駆動制御)は、例えば、図5に示すように、一走査期間Tscを1サイクルとして、該一走査期間Tsc内に、走査ラインSLに接続された表示画素EMBを選択して表示データに応じた階調信号電流Ipixを書き込み、電圧成分として保持する書き動作期間(選択期間)Tseと、該書き動作期間Tseに書き込み、保持された電圧成分に基づいて、上記表示データに応じた発光駆動電流を生成して有機EL素子OELに供給し、所定の輝度階調で発光動作させる発光動作期間(非選択期間)Tnseと、を包むように設定することにより実行される(Tsc-Tse+Tnse)。ここで、各行の走査ラインSLごとに設定される書き動作期間Tseは、相互に時間的な重なりが生じないように設定される。10

#### 【0075】

##### (書き動作期間)

まず、表示画素EMBの書き動作期間Tseにおいては、図5に示すように、まず、走査ドライバ120から走査ライン(例えば、i行目の走査ライン；iは、走査ラインSLを特定するための任意の自然数)SLに対して、ハイレベルの走査信号Vselが印加されて当該行の表示画素EMBが選択状態に設定されるとともに、当該行の表示画素EMBの電源ラインVLに対して、ローレベルの電源電圧Vscが印加される。また、このタイミングに同期して、データドライバ130から当該行の表示データに対応する電流値を有する負極性の階調信号電流(-Ipix)がデータラインDLに供給される。20

#### 【0076】

これにより、画素駆動回路DCBを構成する薄膜トランジスタTr21及びTr22がオン動作して、ローレベルの電源電圧Vscが接点N21(すなわち、ダブルゲート型トランジスタTr23のトップゲート端子TG及びボトムゲート端子BG、並びに、コンデンサC21の一端側)に印加されるとともに、データドライバ130によりデータラインDLを介して負極性の階調信号電流(-Ipix)を引き込む動作が行われることにより、ローレベルの電源電圧Vscよりも低電位の電圧レベルが接点N22(すなわち、ダブルゲート型トランジスタTr23のソース端子S、及び、コンデンサC21の他端側)に印加される。30

#### 【0077】

このように、接点N21及びN22間(ダブルゲート型トランジスタTr23のゲート-ソース間)に電位差が生じることにより、ダブルゲート型トランジスタTr23がオン動作して、図4(a)に示すように、電源ラインVLからダブルゲート型トランジスタTr23、接点N22、薄膜トランジスタTr22、データラインDLを介して、データドライバ130に、階調信号電流Ipixの電流値に対応した書き電流Iaが流れれる。

#### 【0078】

このとき、コンデンサC21には、接点N21及びN22間(ダブルゲート型トランジスタTr23のゲート-ソース間)に生じた電位差に対応する電荷が蓄積され、電圧成分として保持される(充電される)。また、電源ラインVLには、接地電位Vgnd以下の電圧レベルを有する電源電圧Vscが印加され、さらに、書き電流IaがデータラインDL方向に流れるように制御されることから、有機EL素子OELのアノード端子(接点N22)に印加される電位はカソード端子の電位(接地電位Vgnd)よりも低くなり、有機EL素子OELに逆バイアス電圧が印加されることになるため、有機EL素子OELには発光駆動電流が流れず、発光動作は行われない。40

#### 【0079】

##### (発光動作期間)

次いで、書き動作期間Tse終了後の発光動作期間Tnseにおいては、図5に示すように、走査ドライバ120から当該走査ラインSLに対して、ローレベルの走査信号Vselが50

印加されて表示画素 E M B が非選択状態に設定されるとともに、当該行の表示画素 E M B の電源ライン V L に対して、ハイレベルの電源電圧 V sc が印加される。また、このタイミングに同期して、データドライバ 1 3 0 による階調信号電流 I pix の引き込み動作（階調信号電流 I pix の供給動作）が停止される。

#### 【 0 0 8 0 】

これにより、画素駆動回路 D C B を構成する薄膜トランジスタ T r 2 1 及び T r 2 2 がオフ動作して、接点 N 2 1（すなわち、ダブルゲート型トランジスタ T r 2 3 のトップゲート端子 T G 及びボトムゲート端子 B G、並びに、コンデンサ C 2 1 の一端側）への電源電圧 V sc の印加が遮断されるとともに、接点 N 2 2（すなわち、ダブルゲート型トランジスタ T r 2 3 のソース端子 S、及び、コンデンサ C 2 1 の他端側）へのデータドライバ 1 3 0 による階調信号電流 I pix の引き込み動作に起因する電圧レベルの印加が遮断されるので、コンデンサ C 2 1 は、上述した書き動作期間 T se において蓄積された電荷を保持する。

#### 【 0 0 8 1 】

このように、コンデンサ C 2 1 が書き動作時の充電電圧を保持することにより、接点 N 2 1 及び N 2 2 間（ダブルゲート型トランジスタ T r 2 3 のゲート - ソース間）の電位差が保持されることになり、ダブルゲート型トランジスタ T r 2 3 はオン状態を維持する。また、電源ライン V L には、接地電位 V gnd よりも高い電圧レベルを有する電源電圧 V sc が印加されるので、有機 E L 素子 O E L のアノード端子（接点 N 2 2 ）に印加される電位はカソード端子の電位（接地電位）よりも高くなる。

#### 【 0 0 8 2 】

したがって、図 4 ( b ) に示すように、電源ライン V L からダブルゲート型トランジスタ T r 2 3 、接点 N 2 2 を介して、有機 E L 素子 O E L に順バイアス方向に所定の発光駆動電流 I b が流れ、有機 E L 素子 O E L が発光する。ここで、コンデンサ C 2 1 により蓄積された電荷に基づく電位差（充電電圧）は、ダブルゲート型トランジスタ T r 2 3 において階調信号電流 I pix に対応した書き込み電流 I a を流す場合の電位差に相当するので、有機 E L 素子 O E L に供給される発光駆動電流 I b は、上記書き込み電流 I a と同等の電流値を有することになる。これにより、書き動作期間 T se 後の発光動作期間 T nse においては、書き動作期間 T se に書き込まれた表示データ（階調信号電流 I pix ）に対応する電圧成分に基づいて、ダブルゲート型トランジスタ T r 2 3 を介して、発光駆動電流 I b が継続的に供給されることになり、有機 E L 素子 O E L は表示データに対応する輝度階調で発光する動作を継続する。

#### 【 0 0 8 3 】

そして、上述した一連の動作を、表示パネル 1 1 0 を構成する全ての走査ライン S L について順次繰り返し実行することにより、表示パネル 1 画面分の表示データが書き込まれて、所定の輝度階調で発光し、所望の画像情報が表示される。

ここで、本実施例に係る画素駆動回路 D C B においては、少なくとも、ダブルゲート型トランジスタ T r 2 3 を構成する半導体層（チャネル層）が n チャネル型のアモルファスシリコンにより形成された構成を有しているが、薄膜トランジスタ T r 2 1 、 T r 2 2 についても、同じチャネル極性（n チャネル型）を有することから、半導体層（チャネル層）を n チャネル型のアモルファスシリコンにより形成することにより、すでに確立されたアモルファスシリコン製造技術を適用して、動作特性の安定した画素駆動回路を比較的安価に製造することができる。

#### 【 0 0 8 4 】

また、本実施形態に係る画素駆動回路 D C B においては、上述したように（図 5 参照）、電源ライン V L に所定の電圧値を有する電源電圧 V sc を印加する必要があるが、そのための構成としては、例えば、図 1 に示した表示装置 1 0 0 の構成に加え、表示パネル 1 1 0 の各走査ライン S L に並行に配設された複数の電源ライン V L に接続された電源ドライバを備え、上述したシステムコントローラ 1 4 0 から供給される電源制御信号に基づいて、走査ドライバ 1 2 0 から出力される走査信号 V sel に同期するタイミング（図 5 参照）

10

20

30

40

50

で、当該電源ドライバから所定の電圧値を有する電源電圧  $V_{sc}$  を、走査ドライバ 120 により走査信号  $V_{sel}$  が印加される行（選択状態に設定される表示画素 EMB）の電源ライン  $V_L$  に対して印加するようにした構成を適用するものであってもよいし、走査ドライバ 120 から出力される走査信号  $V_{sel}$  に同期するタイミングで電源ライン  $V_L$  に印加されることから、走査ドライバ 120 において、走査信号  $V_{sel}$ （又は、走査信号を生成するためのシフト出力信号）を反転処理し、所定の信号レベルに増幅して、電源ライン  $V_L$  に対して印加するようにした構成を適用するものであってもよい。

#### 【0085】

<ダブルゲート型トランジスタの素子構造及び素子特性>

次に、上述した各実施形態に示した画素駆動回路の発光駆動用トランジスタとして適用されるダブルゲート型トランジスタの素子構造及び素子特性について、図面を参照して詳しく説明する。

#### 【0086】

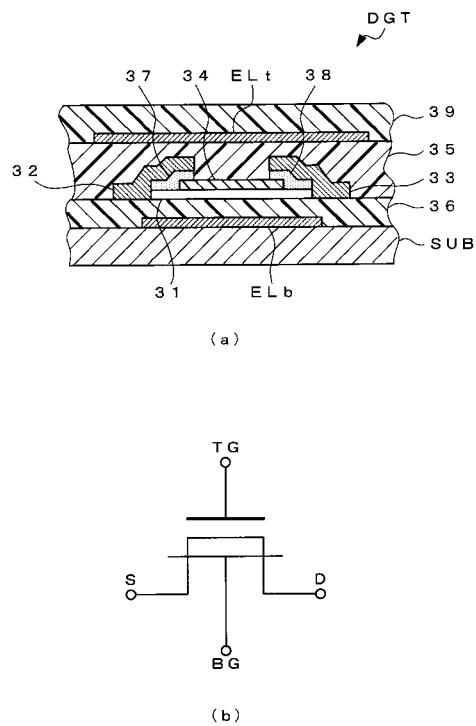

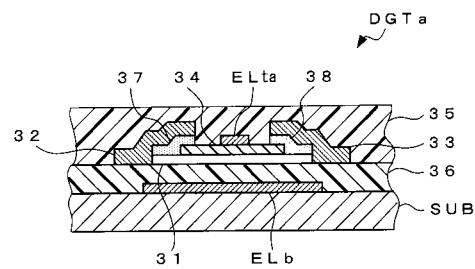

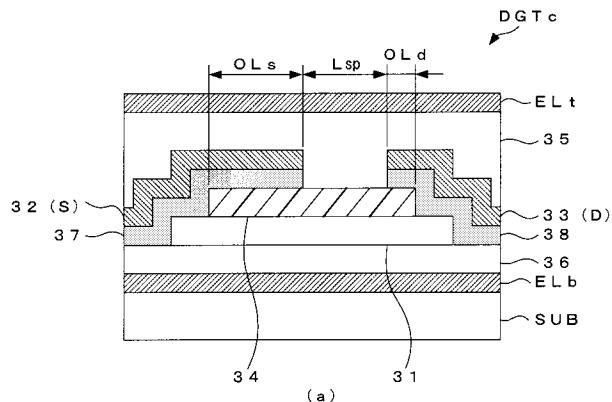

<第1の構成例>

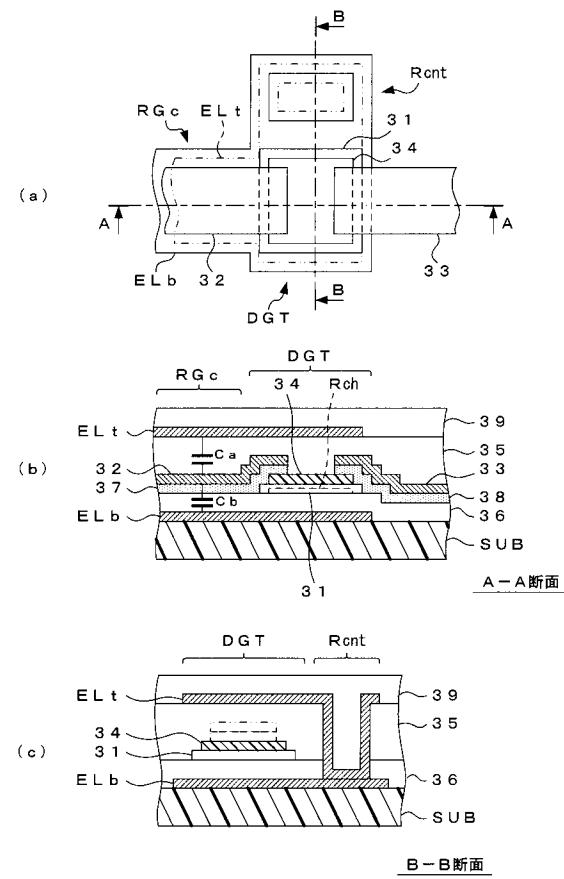

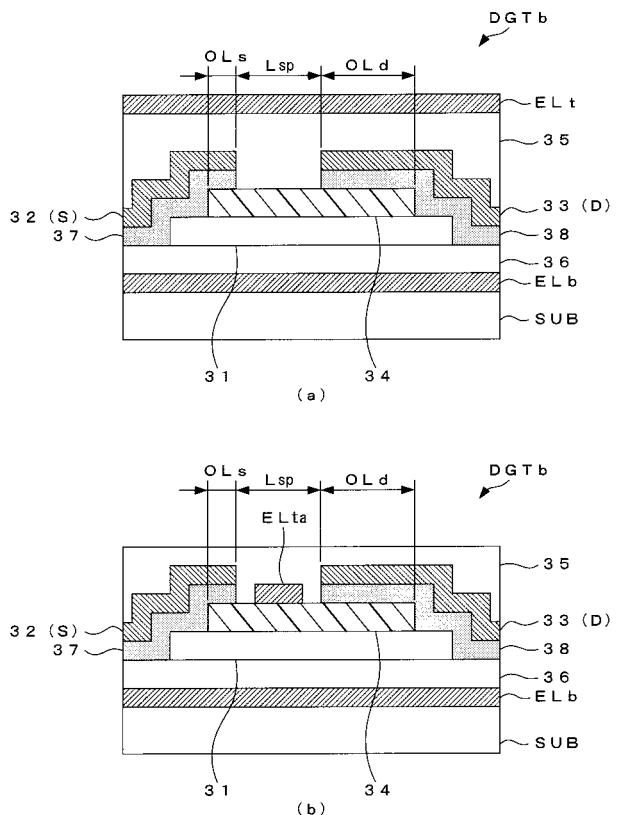

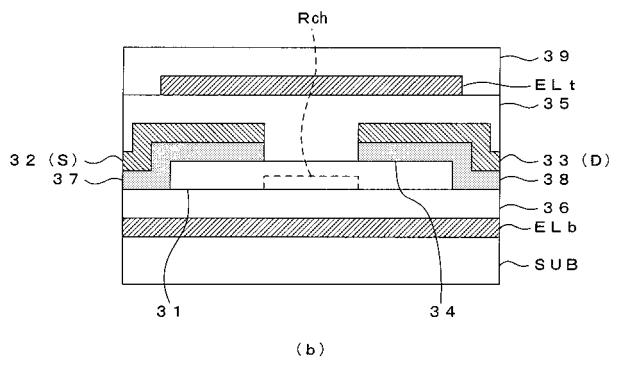

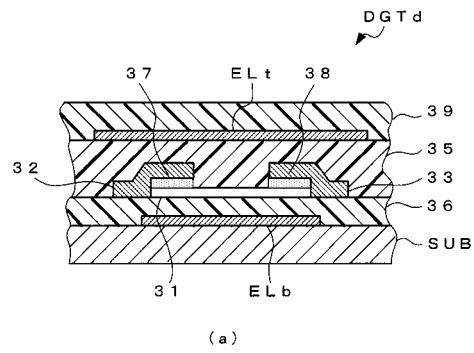

図 6 は、本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第1の構成例を示す断面構成図及び回路図である。また、図 7 は、本構成例に係るダブルゲート型トランジスタを、上述した各実施形態に係る表示画素（画素駆動回路）に適用した場合の素子構造の一例を示す概略構成図である。なお、図 7 においては、図示の都合上、図 7 (a) に示した平面構成図のトップゲート電極を 2 点鎖線で表し、図 7 (b)、(c) に示した断面構成図のハッチングを一部省略した。

#### 【0087】

図 6 に示すように、本実施形態に係る発光駆動トランジスタに適用されるダブルゲート型トランジスタ DGT は、概略、アモルファスシリコン等の半導体層（チャネル領域）31 と、半導体層 31 の両端に、各々  $n^+$  シリコンからなる不純物層（オーミックコンタクト層）37、38 を介して形成されたソース電極 32（ソース端子 S）及びドレイン電極 33（ドレイン端子 D）と、半導体層 31 の上方（図面上方）にロック絶縁膜（エッチングストップ膜）34 及びトップゲート絶縁膜 35 を介して形成されたトップゲート電極 ELt（第1のゲート電極；トップゲート端子 TG）と、半導体層 31 の下方（図面下方）にボトムゲート絶縁膜 36 を介して形成されたボトムゲート電極 E L b（第2のゲート電極；ボトムゲート端子 BG）と、を有して構成されている。

#### 【0088】

また、このような構成を有するダブルゲート型トランジスタ DGT は、図 6 (a) に示すように、ガラス基板等の絶縁性基板 SUB 上に形成されている。また、該ダブルゲート型トランジスタ DGT を含む絶縁性基板 SUB の一面側全域には保護絶縁膜 39 が被覆形成されている。なお、図 6 (a) に示した素子構造において、半導体層 31 上に設けられたロック絶縁膜 34 は、半導体層 31 上に設けられるソース電極 32 及びドレイン電極 33 をパターニング形成する際のエッティング工程における、エッティングストップとしての機能を有するとともに、当該エッティングによる半導体層 31 へのダメージを防止するための機能を有するものである。

#### 【0089】

ここで、ダブルゲート型トランジスタ DGT を構成するトップゲート電極 E Lt、ボトムゲート電極 E L b は、例えば、アルミニウムとチタンの合金（アルミチタン）等の導電性材料により形成され、ソース電極 32 及びドレイン電極 33 は、クロム又はクロム合金等の導電性材料により形成されている。また、ロック絶縁膜 34、トップゲート絶縁膜 35、ボトムゲート絶縁膜 36 及び保護絶縁膜 39 は、例えば、シリコン窒化膜（SiN）等の絶縁性材料により形成されている。

なお、図 6 (a) に示した構成を有するダブルゲート型トランジスタは、一般に、図 6 (b) に示すような等価回路により表される。

#### 【0090】

そして、このような構成を有するダブルゲート型トランジスタ DGT を、上述したよう

10

20

30

40

50

な表示画素 E M A、E M B の画素駆動回路 D C A（図 2 参照）、D C B（図 3 参照）に適用する場合にあっては、例えば、トップゲート電極 E L t（トップゲート端子 T G）とボトムゲート電極 E L b（ボトムゲート端子 B G）とが電気的に接続（短絡）された構成を有している。この場合、図 6 に示したダブルゲート型トランジスタ D G T の素子構造において、例えば、図 7（a）、（c）に示すように、ダブルゲート型トランジスタ D G T の形成領域近傍に設けられたコンタクト領域 R c n t において、延在して形成されたトップゲート電極 E L t がトップゲート絶縁膜 3 5 及びボトムゲート絶縁膜 3 6 を貫通して形成された開口部（コンタクトホール）を介して、延在して形成されたボトムゲート電極 E L b に電気的に接続されるように構成されている。

## 【0091】

10

また、画素駆動回路 D C A（図 2 参照）、D C B（図 3 参照）において、ゲート - ソース間にコンデンサ C 1 1、C 1 2 が接続された構成を有していることから、例えば、図 7（a）、（b）に示すように、ダブルゲート型トランジスタ D G T の形成領域近傍に設けられた容量領域 R G c において、各々延在して形成されたトップゲート電極 E L t 及びソース電極 3 2 がトップゲート絶縁膜 3 5 を介して対向（積層）して設けられることにより容量成分 C a が形成され、また、各々延在して形成されたボトムゲート電極 E L b 及びソース電極 3 2 がボトムゲート絶縁膜 3 6 を介して対向（積層）して設けられることにより、容量成分 C b が形成されている。

## 【0092】

20

したがって、画素駆動回路 D C A、D C B に設けられたコンデンサ C 1 1、C 1 2 の容量値は、各々、同一の容量領域 R G c に形成された上記容量成分 C a 及び C b の総和に相当するので、このような素子構造を有する容量領域 R G c を適用することにより、所望の容量値をより狭い領域（面積）で実現することができる。

## 【0093】

次いで、上述したような素子構造及び接続構造を有するダブルゲート型トランジスタの素子特性について説明する。

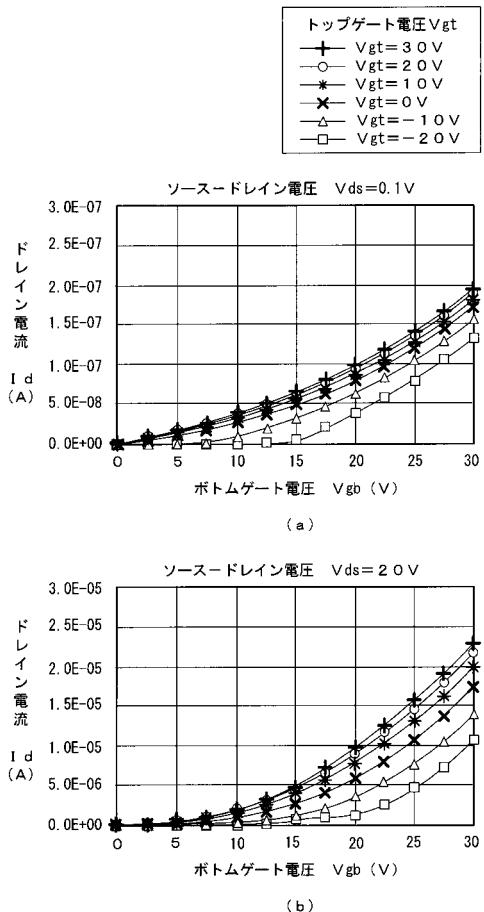

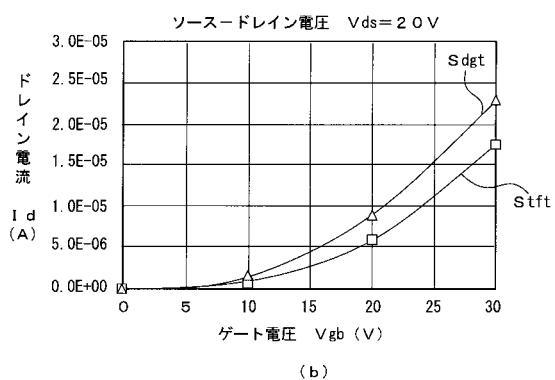

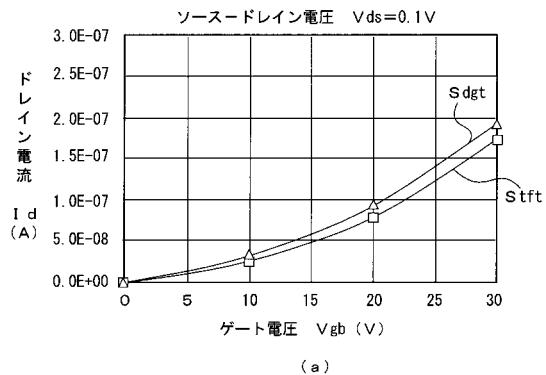

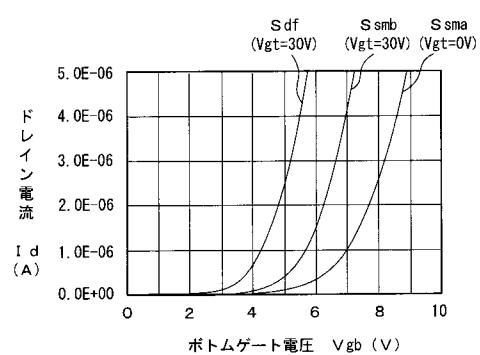

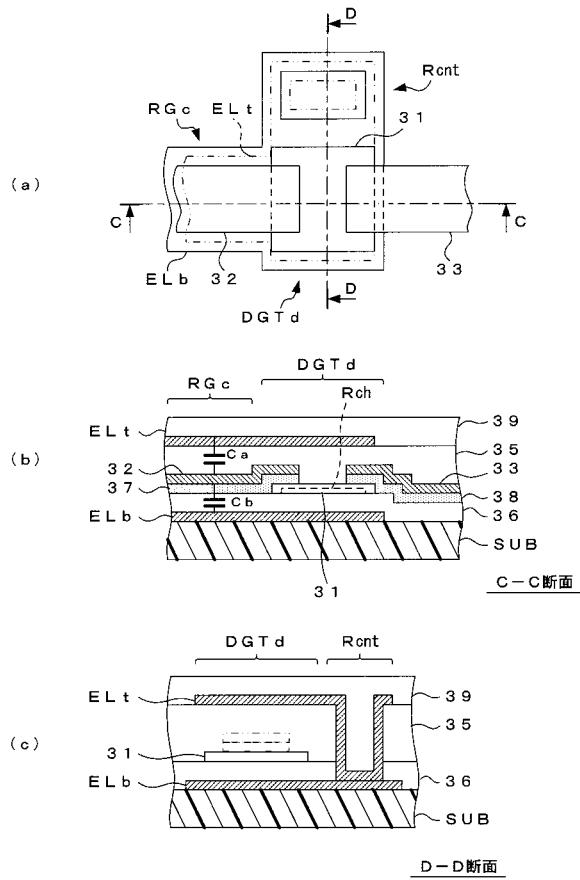

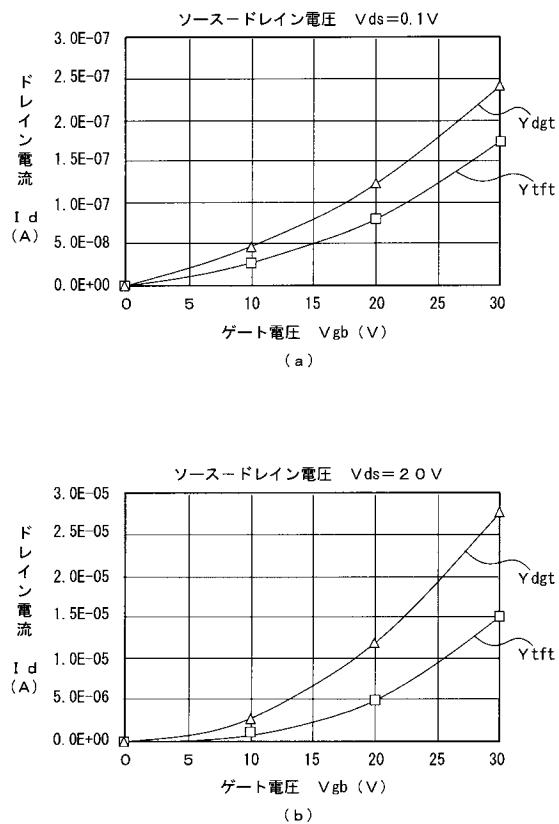

図 8 は、本構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧 - 電流特性を示す図（シミュレーション結果）であり、図 9 は、本構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に接続（短絡）した状態における電圧 - 電流特性を示す図（シミュレーション結果）である。

30

## 【0094】

まず、上述したダブルゲート型トランジスタ D G T において、トップゲート端子とボトムゲート端子とを電気的に独立した状態（すなわち、図 6 に示したダブルゲート型トランジスタの基本構成）における、ボトムゲート電圧 V g b に対するドレイン電流（オン電流）I d の変化傾向（電圧 - 電流特性）について検証する。

## 【0095】

40

トップゲート端子（トップゲート電極）とボトムゲート端子（ボトムゲート電極）とを電気的に独立した状態のダブルゲート型トランジスタ D G T においては、図 8（a）、（b）に示すように、ソース - ドレイン端子間の電位差（すなわち、バイアス電圧）V d s が比較的大きい場合には（V d s = 2 0 V）、ボトムゲート電圧 V g b に対するドレイン電流 I d の変化傾向は、トップゲート電圧 V g t に正の電圧（1 0 V 2 0 V 3 0 V）を印加することにより、ドレイン電流 I d が顕著に増加し、また、トップゲート電圧 V g t に負の電圧（- 1 0 V - 2 0 V）を印加することにより、ドレイン電流 I d が顕著に減少することが観測された。

## 【0096】

50

これに対して、ソース - ドレイン端子間のバイアス電圧 V d s が比較的小さい場合には（V d s = 0 . 1 V）、ボトムゲート電圧 V g b に対するドレイン電流 I d の変化傾向は、トップゲート電圧 V g t に負の電圧（- 1 0 V - 2 0 V）を印加することにより、ドレイン電流 I d が顕著に減少するものの、トップゲート電圧 V g t に正の電圧（1 0 V 2 0 V 3

0 V) を印加した場合には、ドレイン電流  $I_d$  の大幅な増加は観測されなかった。

#### 【0097】

これは、図6に示したダブルゲート型トランジスタDGTの素子構造において、半導体層31上のブロック絶縁膜34上に延在して形成されたソース電極32、ドレイン電極33が、半導体層に形成されるチャネル領域に対して、擬似的なトップゲート電極としての役割を果たし、当該ソース電極32及びドレイン電極33の上方に設けられた本来のトップゲート電極ELtによるチャネル領域への寄与は、ソース電極32及びドレイン電極33が形成されていないチャネル領域中央部に限定されることに起因すると考えられる。

#### 【0098】

また、他の原因として、チャネル領域内の抵抗分布に起因するものと考えられる。すなわち、ソース - ドレイン端子間のバイアス電圧  $V_{ds}$  が比較的小さい場合(線形動作領域)には、チャネル領域の抵抗分布は、ソース側からドレイン側にわたり、ほぼ一様に低抵抗状態を示す。したがって、この状態においては、トップゲート電圧を印加することによりチャネル領域の中央部における抵抗値が減少したとしても、ドレイン電流(オン電流)  $I_d$  の大幅な増加は生じないため、図8(a)に示したような電圧 - 電流特性が得られたものと考えられる。

#### 【0099】

一方、ソース - ドレイン端子間のバイアス電圧  $V_{ds}$  が充分大きい場合(飽和動作領域)には、チャネル領域の抵抗分布は、中央部やドレイン側近傍において高抵抗状態を示す。したがって、この状態においては、トップゲート電圧を印加することによりチャネル領域の中央部における抵抗値を減少させることにより、ドレイン電流(オン電流)  $I_d$  の大幅な増加が生じるため、図8(b)に示したような電圧 - 電流特性が得られたものと考えられる。

#### 【0100】

特に、上述した第2の実施形態に示したような表示画素EMB(画素駆動回路DCB)においては、薄膜トランジスタTr21がオン動作することにより、ダブルゲート型トランジスタTr23のゲート電極(ゲート端子)とドレイン電極(ドライバ端子)が短絡した状態となり、飽和状態で動作することになるため、図8(b)に示したように、トップゲート電圧  $V_{gt}$  を制御することにより、ドレイン電流  $I_d$  を顕著に増大させることができるので、これを言い換えれば、所望の電流値のドレイン電流(オン電流)を得るために必要なトランジスタの形成領域の面積を大幅に削減することができるようになる。

#### 【0101】

なお、図8(a)、(b)において、ダブルゲート型トランジスタDGTのトップゲート電圧  $V_{gt}$  を0Vに設定した場合の電圧 - 電流特性は、トップゲート電圧がチャネル領域に全く寄与していないと考えることができるところから、単一のゲート電極を備えた、一般(周知)の電界効果型トランジスタにおける電圧 - 電流特性と同等であると考えることができる。

#### 【0102】

また、ダブルゲート型トランジスタDGTのトップゲート電圧  $V_{gt}$  とボトムゲート電圧  $V_{gb}$  を同一の電圧値に設定した場合のボトムゲート電圧に対するドレイン電流は、トップゲート電極とボトムゲート電極とを電気的に接続(短絡)した状態の電圧 - 電流特性と同等であると考えることができる。

#### 【0103】

したがって、単一のゲート電極を備えた薄膜トランジスタとダブルゲート型トランジスタDGTにおける電圧 - 電流特性を比較すると、図8に示した場合と同様に、ソース - ドレイン端子間のバイアス電圧  $V_{ds}$  が比較的大きい場合には( $V_{ds} = 20V$ )、ゲート電圧(ボトムゲート電圧)  $V_{gb}$  に対するドレイン電流  $I_d$  の変化傾向は、図9(b)に示すように、ダブルゲート型トランジスタDGTにおけるドレイン電流  $I_d$  の方が顕著に増加し、また、バイアス電圧  $V_{ds}$  が比較的小さい場合においても( $V_{ds} = 0.1V$ )、図9(a)に示すように、ダブルゲート型トランジスタDGTにおけるドレイン電流  $I_d$  の方が僅

10

20

30

40

50

かながら増加することが観測された。なお、図9(a)、(b)において、 $S_{tft}$ は、単一のゲート電極を備えた電界効果型トランジスタにおける電圧-電流特性を示す特性線であり、 $S_{dgt}$ は、本構成例に係るトップゲート電極とボトムゲート電極とを短絡したダブルゲート型トランジスタにおける電圧-電流特性を示す特性線である。

#### 【0104】

このことから、図2、図3に示したような第1及び第2の実施形態に係る表示画素E M A、E M Bにおいて、画素駆動回路D C A、D C Bの発光駆動用トランジスタとして、図7に示したようなトップゲート電極E L tとボトムゲート電極E L bとを短絡したことにより、電子移動度が比較的低いアモルファスシリコン半導体層を用いたトランジスタ構造においても、同一のゲート電圧で、より大きなドレイン電流(発光駆動電流)を有機EL素子O E Lに流すことができる。

10

#### 【0105】

これは換言すると、電圧印加方式及び電流印加方式のいずれの駆動制御方法に対応した画素駆動回路においても、同一のドレイン電流(発光駆動電流)を流すために、ダブルゲート型トランジスタのトランジスタサイズ(特に、ゲート幅)を小さくすることができることになるので、各表示画素の形成領域の面積が一定の場合には、相対的に有機EL素子の形成面積(発光領域)を増やすことができ、表示パネルの開口率を向上させることができる。

#### 【0106】

また、同一のドレイン電流を流すために、ダブルゲート型トランジスタのゲート電圧を低く設定することができるので、ゲート電極に高電圧が継続的に印加されることによるトランジスタ特性(電圧-電流特性)の劣化を抑制して、動作特性に優れた画素駆動回路(すなわち、表示特性に優れた表示パネル)を実現することができるとともに、画像表示動作に伴う消費電力を抑制することができる。その場合、有機EL素子に流す発光駆動電流の電流密度を小さくすることができるので、有機EL素子の素子特性の劣化を抑制して寿命を長くすることができる。

20

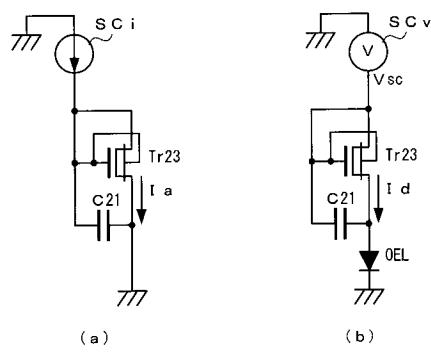

#### 【0107】

次に、本構成例に係るダブルゲート型トランジスタを、上述した第2の実施形態に係る画素駆動回路(すなわち、電流印加方式に対応した画素駆動回路；図3参照)に適用した場合に特有の効果について説明する。

30

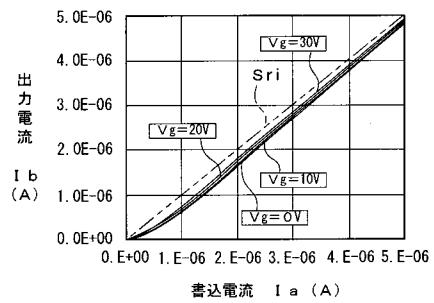

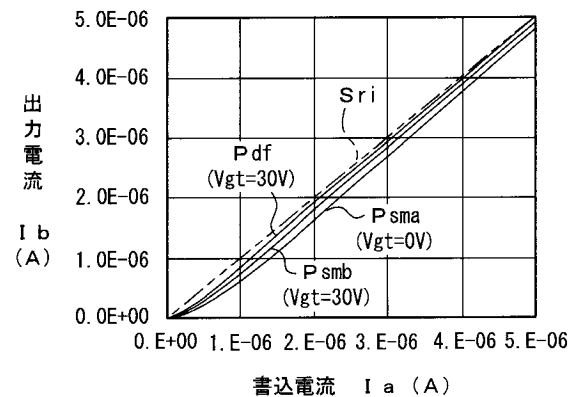

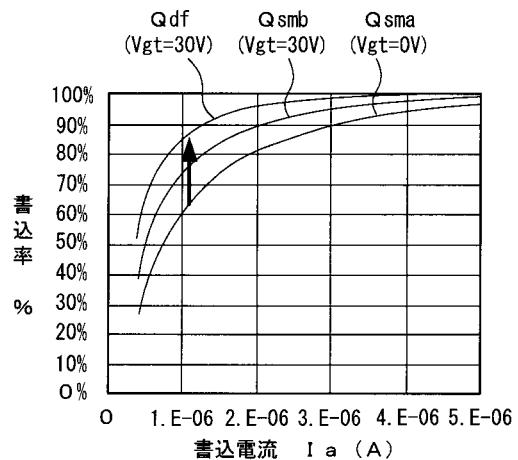

図10は、第2の実施形態に示した画素駆動回路におけるダブルゲート型トランジスタの書込動作を検証するためのシミュレーションモデル(簡略化した等価回路)を示す回路図である。また、図11は、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流(入力電流)と発光駆動電流(出力電流)の関係(電流特性)を示す特性図(シミュレーション結果)であり、図12は、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流(入力電流)と当該画素駆動回路への書込率との関係を示す特性図(シミュレーション結果)である。

#### 【0108】

上述した第2の実施形態に示した表示画素E M B(画素駆動回路D C B)において、書込動作における、各スイッチング素子(薄膜トランジスタT r 2 1、T r 2 2及びダブルゲート型トランジスタT r 2 3)の導通状態は、図4(a)に示したように、薄膜トランジスタT r 2 2及びダブルゲート型トランジスタT r 2 3がオン動作するので、階調信号電流I pixが供給される(引き抜かれる)データラインD Lから、薄膜トランジスタT r 2 2、接点2 2、ダブルゲート型トランジスタT r 2 3及び電源ラインV Lに至る経路が一本につながって、書込電流I aが電源ラインV Lから画素駆動回路D C Bを介してデータラインD L方向に流れれる。

40

#### 【0109】

一方、この状態においては、薄膜トランジスタT r 2 1がオン動作するので、ダブルゲ

ート型トランジスタTr23のゲート端子（トップゲート端子及びボトムゲート端子）とドレイン端子が接続された状態と等価となる。

したがって、書込動作状態における表示画素EMBの回路構成を簡略化すると、概略、図10(a)に示すように、書込電流Ia(階調信号電流Ipixに相当する)の電流供給源SCiと接地電位との間に電流路が形成され、トップゲート端子及びボトムゲート端子とドレイン端子が短絡されたダブルゲート型トランジスタTr23と、該ダブルゲート型トランジスタTr23のゲート-ソース間に接続されたコンデンサC21と、からなる等価回路で表すことができる。

#### 【0110】

また、表示画素EMB(画素駆動回路DCB)において、発光動作における、各スイッチング素子(薄膜トランジスタTr21、Tr22及びダブルゲート型トランジスタTr23)の導通状態は、図4(b)に示したように、薄膜トランジスタTr21及びTr22がオフ動作し、ダブルゲート型トランジスタTr23がオン動作を継続するので、電源ラインVLから、ダブルゲート型トランジスタTr23、接点22、有機EL素子OEL及び接地電位Vgndに至る経路が一本につながって、発光駆動電流(出力電流)Ibが電源ラインVLから画素駆動回路DCB及び有機EL素子OELを介して接地電位Vgnd方向に流れれる。

#### 【0111】

一方、この状態においては、コンデンサC21に保持された電荷によりダブルゲート型トランジスタTr23のトップゲート端子及びボトムゲート端子には、ハイレベルのゲート電圧が印加されるとともに、ハイレベルの電源電圧Vscに設定された電源ラインVLから当該ダブルゲート型トランジスタTr23を介して、発光駆動電流Ibが流れることにより、接点21の電位(ダブルゲート型トランジスタTr23のゲート電圧)はさらに上昇して、実質的に電源ラインVLのハイレベルと同等になり、ダブルゲート型トランジスタTr23のゲート端子(トップゲート端子及びボトムゲート端子；接点N21)とドレイン端子(電源ラインVL)が接続された状態と等価となる。

#### 【0112】

したがって、発光動作状態における表示画素EMBの回路構成を簡略化すると、概略、図10(b)に示すように、電源電圧Vscの電圧供給源SCvと接地電位との間に電流路が形成され、トップゲート端子及びボトムゲート端子とドレイン端子が短絡されたダブルゲート型トランジスタTr23と、該ダブルゲート型トランジスタTr23のソース端子と接地電位間に接続された有機EL素子OELと、からなる等価回路で表すことができる。

#### 【0113】

このような等価回路(シミュレーションモデル)において、ダブルゲート型トランジスタTr23のしきい値電圧Vth=0V、チャネル長L=7μm、コンデンサC21容量=20pF、書込電流Ia=50μA、書込時間=80μsecに設定して解析を行った結果、図11に示すように、表示画素EMB(画素駆動回路DCB)への書込電流Ia(階調電流Ipix)に対する、有機EL素子OELに供給される発光駆動電流(出力電流)Ibの電流値の関係(電流特性)は、ダブルゲート型トランジスタTr23のトップゲート端子及びボトムゲート端子に印加するゲート電圧Vgを増加させるほど(0V 10V 20V 30V)、書込電流Iaに対して同等の電流値を有する(線形性を有する)出力電流Ibが有機EL素子OELに供給される、理想的な書込状態を示す電流特性線Sriに近似するとともに、非線形性が改善されて略線形性を示すシミュレーション結果が得られた。

#### 【0114】

また、この場合、図12に示すように、書込電流Iaに対する書込率の関係(書込特性)も、ダブルゲート型トランジスタTr23に印加するゲート電圧Vgを増加させるほど(0V 10V 20V 30V)、書込率が顕著に上昇する傾向を示すシミュレーション結果が得られた。

10

20

30

40

50

## 【0115】

このことは、上述した電圧 - 電流特性においても説明したように、ダブルゲート型トランジスタにおいては、単一のゲート電極のみを備えた一般的な薄膜トランジスタに比較して、同一の書き込み電流を流すために必要なゲート電圧を低減することができるので、ダブルゲート型トランジスタのゲート - ソース間に接続されるコンデンサ C 21 に充電すべき書き込み電圧を低減することができ、それに伴って、当該書き込み動作に要する時間を短く設定することができるることに基づくものである。

## 【0116】

このように、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示したような表示画素 E M B (電流印加方式に対応した画素駆動回路 D C B )に適用することにより、上述したような電圧 - 電流特性の改善に伴って、ダブルゲート型トランジスタのゲート幅を小さくして開口率を向上することができ、また、ゲート電圧を低電圧化してトランジスタ特性の劣化や消費電力を抑制することができるとともに、電流特性及び書き込み特性の改善に伴って、書き込み電流に対する出力電流の線形性、及び、書き込み電流に対する書き込み率を向上させることができるので、画像情報を適切な輝度階調で表示することができ、表示画質に優れた画像表示装置を実現することができる。

## 【0117】

なお、本構成例に係るダブルゲート型トランジスタが適用される、上述した第1及び第2の実施形態においては、画素駆動回路 D C A 、 D C B において、発光素子である有機 E L 素子 O E L に発光駆動電流を供給する発光駆動用トランジスタ (スイッチング素子) に対してのみ、ダブルゲート型トランジスタを適用した構成について説明したが、本発明はこれに限定されるものでなく、例えば、画素駆動回路を構成する全てのスイッチング素子をダブルゲート型トランジスタで構成するものであってもよい。

## 【0118】

この場合、発光駆動用トランジスタにおいては、回路構成上、飽和動作領域でオン動作するので、上述したような電圧 - 電流特性に基づいて、ゲート電圧に対する発光駆動電流 (ドレイン電流) を増大させることができるが、画素駆動回路における発光駆動用トランジスタ以外の薄膜トランジスタについては、線形動作領域でオン動作するので、上記電圧 - 電流特性に基づく発光駆動電流の顕著な増大効果は得られないものの、トップゲートが設けられていない単一のゲート電極のみを有する、一般的な薄膜トランジスタ (電界効果型トランジスタ) に比較して、半導体層 (チャネル領域) 上に不透明なトップゲート電極が設けられたダブルゲート型トランジスタの方が、チャネル領域に入射する外光に起因する光誘起リーク電流を低減する効果や、外部電界の影響を遮断する効果を得ることができ、画素駆動回路 (表示画素) を安定的に動作させて良好な表示画質を実現することができる。

## 【0119】

図13は、本構成例に係るダブルゲート型トランジスタの素子構造の他の構成例を示す断面構成図である。ここで、上述した構成例 (図6参照) と同等の構成については同一の符号を付してその説明を簡略化する。

上述した第1の構成例においては、ダブルゲート型トランジスタ D G T の素子構造として、図6に示したように、半導体層 3 1 の上方に、ソース電極 3 2 及びドレイン電極 3 3 が延在して形成され、当該半導体層 3 1 、ソース電極 3 2 及びドレイン電極 3 3 の上方に、トップゲート絶縁膜 3 5 を介して半導体層 3 1 の平面的な広がりに対応する形状を有するトップゲート電極 E L t を設けた構成を示したが、上述したように、半導体層 3 1 上のプロック絶縁膜 3 4 上に延在して形成されたソース電極 3 2 及びドレイン電極 3 3 が、半導体層 3 1 に形成されるチャネル領域に対して、擬似的なトップゲート電極としての役割を果たし、トップゲート電極 E L t によるチャネル領域への実質的な寄与は、ソース電極 3 2 及びドレイン電極 3 3 が形成されていない領域 (チャネル領域中央部) に限定されることから、図13に示すように、半導体層 3 1 上のプロック絶縁膜 3 4 上であって、ソース電極 3 2 及びドレイン電極 3 3 間の領域 (すなわち、チャネル領域中央部上方に、トッ

ゲート電極 E L taを設けた構成を有するものであってもよい。

#### 【0120】

このような構成を有するダブルゲート型トランジスタ D G T aによれば、トップゲート電極 E L taが、トップゲート絶縁膜 3 5 を介さずに半導体層 3 1 上のプロック絶縁膜 3 4 上に直接設けられているため、上述した構成例の場合と同じトップゲート電圧 V gtで、より高い効果が得られるとともに、画素駆動回路 D C B を構成する積層構造における積層数を少なくすることができるので、製造プロセスを簡素化してプロセス数を削減し、製造歩留まりの向上や製造コストの削減を図ることができる。

#### 【0121】

<第2の構成例>

次いで、本発明に係る画素駆動回路に適用されるダブルゲート型トランジスタの素子構造の第2の構成例について図面を参照して説明する。

図14は、本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第2の構成例を示す断面構成図及び回路図である。

#### 【0122】

上述した第1の構成例に係るダブルゲート型トランジスタ D G T においては、半導体層 3 1 上のプロック絶縁膜 3 4 上に延在して形成されるソース電極 3 2 及びドレイン電極 3 3 と、プロック絶縁膜 3 4 との重なり寸法が、略均等（すなわち、図6及び図13に示した構成においては、左右対称）になるように形成した素子構造を示したが、本構成例に係るダブルゲート型トランジスタ D G T b においては、図14(a)、(b)に示すように、ソース電極 3 2 及びドレイン電極 3 3 と、プロック絶縁膜 3 4 との重なり寸法が異なる（すなわち、左右非対称）ように形成した素子構造を有している。

#### 【0123】

具体的には、例えば、図14(a)、(b)に示すように、ダブルゲート型トランジスタ D G T b において、ソース電極 3 2 とプロック絶縁膜 3 4 との重なり寸法 O L s が、ドレイン電極 3 3 とプロック絶縁膜 3 4 との重なり寸法 O L d に比較して短くなる（O L s < O L d ）とともに、ソース電極 3 2 とドレイン電極 3 3 との離間距離 L sp が上述した第1の構成例に示した構成（図6及び図13）におけるソース電極 3 2 及びドレイン電極 3 3 の離間距離と同一になるように形成されている。すなわち、表示画素 E M B （画素駆動回路 D C B ）において、発光駆動電流（出力電流） I b が発光素子（有機 E L 素子 O E L ）に流れ出す側の電極とプロック絶縁膜 3 4 との重なり寸法を、相対的に短くなるように形成する。

#### 【0124】

次いで、上述したような素子構造を有するダブルゲート型トランジスタの素子特性について説明する。

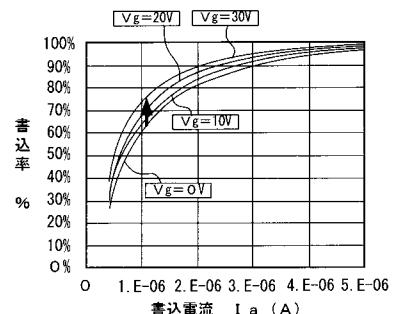

図15は、本構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧 - 電流特性を示す図（シミュレーション結果）であり、図16は、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における電圧 - 電流特性を説明するためである。

#### 【0125】

また、図17は、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流（入力電流）と発光駆動電流（出力電流）の関係（電流特性）を示す特性図（シミュレーション結果）であり、図18は、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流（入力電流）と当該画素駆動回路への書き込み率との関係を示す特性図（シミュレーション結果）である。

#### 【0126】

まず、本実施形態に係るダブルゲート型トランジスタ D G T b において、トップゲート端子 T G とボトムゲート端子 B G とを電気的に独立した状態における、ボトムゲート電圧

10

20

30

40

50

$V_{gb}$ に対するドレイン電流（オン電流） $I_d$ の変化傾向（電圧 - 電流特性）について検証する。

#### 【0127】

ここでは、検証の対象となるダブルゲート型トランジスタの素子構造として、半導体層31上のブロック絶縁膜34のソース - ドレイン方向（図14の左右方向）の長さを、例えば7μm、ソース電極32及びドレイン電極33とブロック絶縁膜34との各重なり寸法を、例えば1μm及び3μmに設定した場合について観測した。なお、比較対象として、ソース電極32及びドレイン電極33とブロック絶縁膜34との各重なり寸法を、例えば2μmに設定した場合についても観測した。

#### 【0128】

本構成例に係るダブルゲート型トランジスタDGTbにおいて、トップゲート端子（トップゲート電極）とボトムゲート端子（ボトムゲート電極）とを電気的に独立した状態で電圧 - 電流特性を観測すると、図15に示すように、ソース電極32及びドレイン電極33とブロック絶縁膜34との重なり寸法が同一になるように形成した素子構造（すなわち、第1の構成例に示したダブルゲート型トランジスタDGT）に対して、ソース電極32及びドレイン電極33とブロック絶縁膜34との重なり寸法が異なるように形成した素子構造の場合の方が、ボトムゲート電圧 $V_{gb}$ に対するドレイン電流 $I_d$ の変化傾向が顕著に改善することが判明した。

#### 【0129】

なお、図15において、 $S_{sma}$ は、ソース電極及びドレイン電極とブロック絶縁膜との重なり寸法が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加していない状態（ $V_{gt} = 0\text{ V}$ ）における電圧 - 電流特性を示す特性線であり、 $S_{smb}$ は、ソース電極及びドレイン電極とブロック絶縁膜との重なり寸法が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態（ $V_{gt} = 30\text{ V}$ ）における電圧 - 電流特性を示す特性線であり、 $S_{df}$ は、本構成例に係るソース電極及びドレイン電極とブロック絶縁膜との重なり寸法が異なるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態（ $V_{gt} = 30\text{ V}$ ）における電圧 - 電流特性を示す特性線である。

#### 【0130】

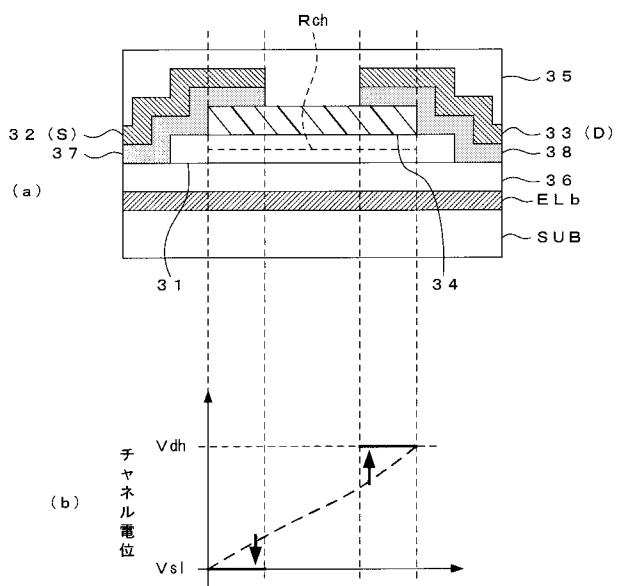

これは、例えば、図16(a)に示すような薄膜トランジスタ構造（すなわち、ダブルゲート型トランジスタDGTのトップゲート電極ELtをなくした素子構造、もしくは、ダブルゲート型トランジスタDGTにおいて、トップゲート端子TGにゲート電圧 $V_{gt}$ を印加していない状態）において、上述した場合と同様に、ソース電極32及びドレイン電極33が半導体層31上のブロック絶縁膜34上に延在することにより、擬似的なトップゲート電極としての役割を果たすことに起因するものと説明することができる。

#### 【0131】

すなわち、図16(a)に示した素子構造を有するトランジスタにおいては、半導体層31上にブロック絶縁膜34を介してソース電極32及びドレイン電極33が重なり合っている領域では、これら電極に印加された電圧により半導体層にチャネル領域が形成され、ソース電極32及びドレイン電極33が形成されていない領域に形成される本来のチャネル領域（すなわち、トップゲート電圧 $V_{gt}$ により半導体層31の略中央部に形成されるチャネル領域）に加え、ソース電極32及びドレイン電極33に対応する領域にもチャネル領域が形成されて、ブロック絶縁膜34が形成された、ソース電極32からドレイン電極33に至る領域の半導体層31にチャネル領域Rchが形成される。このとき、チャネル領域には、ソース - ドレイン端子間に印加されるバイアス電圧（ソース電圧及びドレイン電圧）に応じた電位変化が生じる。

#### 【0132】

ここで、図16(b)に示すように、ソース - ドレイン端子間に所定のバイアス電圧が印加され、ソース電極32に低電位電圧 $V_{sl}$ が、また、ドレイン電極33に高電位電圧 $V$

10

20

30

40

50

$V_{dh}$ が印加されると、低電位電圧  $V_{s1}$  が印加されるソース電極 3 2 側ではチャネル電位を下げる方向、すなわち電圧  $V_{s1}$  に収束（近似）する方向に作用するため、オン電流（ドレイン電流）が抑制され、一方、高電位電圧  $V_{dh}$  が印加されるドレイン電極 3 3 側ではチャネル電位を上げる方向、すなわち電圧  $V_{dh}$  に収束（近似）する方向に作用するため、オン電流が増加する。なお、図 16 (b) において、破線は、チャネル領域における電位変化の理想値を示す。

### 【0133】

第 1 の構成例に示したダブルゲート型トランジスタ D G T においては、ソース電極 3 2 及びドレイン電極 3 3 とチャネル領域（ブロック絶縁膜 3 4）との重なりが同一の寸法になるように均等に形成されていることにより、図 16 (b) に示したようなチャネル電位を下降又は上昇させる作用は、同等になって均衡しているが、本構成例に係るダブルゲート型トランジスタ D G T b においては、ソース電極 3 2 及びドレイン電極 3 3 とチャネル領域（ブロック絶縁膜 3 4）との重なりが異なり、ソース電極 3 2 側に比較してドレイン電極 3 3 側の重なり寸法が大きくなると、チャネル領域における電位変化が高電位側に偏ることになり、ドレイン電流  $I_d$  が増加する方向に作用することになる。

### 【0134】

このことから、図 2、図 3 に示したような第 1 及び第 2 の実施形態に係る表示画素 E M A、E M B において、画素駆動回路 D C A、D C B の発光駆動用トランジスタとして、図 14 に示したように、チャネル領域（ブロック絶縁膜 3 4）とソース電極及びドレイン電極との重なり寸法を非対称に形成した素子構造を有するダブルゲート型トランジスタを適用することにより、電圧 - 電流特性を向上させることができ、電子移動度が比較的低いアモルファスシリコン半導体層を用いたトランジスタ構造においても、同一のゲート電圧で、より大きなドレイン電流（発光駆動電流）を有機 E L 素子 O E L に流すことができる。

### 【0135】

すなわち、同一のドレイン電流を流すために印加すべきゲート電圧を低く設定することができるので、ダブルゲート型トランジスタのトランジスタサイズ（特に、ゲート幅）を小さくすることができ、各表示画素の形成領域における有機 E L 素子の形成面積（発光領域）を相対的に増加させて、表示パネルの開口率を向上させるとともに、ゲート電極に高電圧が印加されることによるトランジスタ特性（電圧 - 電流特性）の劣化を抑制して、動作特性に優れた画素駆動回路（すなわち、表示特性に優れた表示パネル）を実現することができる。

### 【0136】

また、本構成例に係るダブルゲート型トランジスタ D G T b のトップゲート端子及びボトムゲート端子を電気的に接続（短絡）して、第 2 の実施形態に係る表示画素 E M B（画素駆動回路 D C B）の発光駆動用トランジスタ T r 2 3 に適用した場合、図 10 (a)、(b) に示したシミュレーションモデル（各種設定条件は、上述した第 1 の構成例における場合と同等）を用いて、上述した書込動作及び発光動作における電流特性を検証すると、図 17 に示すように、表示画素 E M B（画素駆動回路 D C B）への書込電流  $I_a$ （階調電流  $I_{pix}$ ）に対する、有機 E L 素子 O E L に供給される発光駆動電流（出力電流） $I_b$  の電流値の関係は、ダブルゲート型トランジスタ T r 2 3 に適用される素子構造（図 14）のソース電極 3 2 及びドレイン電極 3 3 とブロック絶縁膜 3 4 との重なり寸法を非対称に設定した場合の方が、重なり寸法を同一に設定した場合（図 6 (a) に示した素子構造）に比較して、書込電流  $I_a$  に対する出力電流  $I_b$  の電流値が線形性を示す理想的な電流特性（特性線 S ri）により近似するとともに、非線形性がさらに改善されるシミュレーション結果が得られた。

### 【0137】

なお、図 17において、 $P_{sma}$ は、ソース電極及びドレイン電極とブロック絶縁膜との重なり寸法が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加していない状態 ( $V_{gt} = 0 \text{ V}$ ) における電流特性を示す特性線であり、 $P_{smb}$ は、ソース電極及びドレイン電極とブロック絶縁膜との重なり寸法

10

20

30

40

50

が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態 ( $V_{gt} = 30V$ ) における電流特性を示す特性線であり、 $P_{df}$ は、本構成例に係るソース電極及びドレイン電極とブラック絶縁膜との重なり寸法が異なるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態 ( $V_{gt} = 30V$ ) における電流特性を示す特性線である。

#### 【0138】

また、この場合、図18に示すように、書込電流  $I_a$  に対する書込率の関係（書込特性）も、ソース電極32及びドレイン電極33とブラック絶縁膜34との重なり寸法を非対称に設定した場合の方が、書込率が顕著に上昇する傾向を示すシミュレーション結果が得られた。

10

#### 【0139】

なお、図18において、 $Q_{sma}$ は、ソース電極及びドレイン電極とブラック絶縁膜との重なり寸法が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加していない状態 ( $V_{gt} = 0V$ ) における書込特性を示す特性線であり、 $Q_{smb}$ は、ソース電極及びドレイン電極とブラック絶縁膜との重なり寸法が同一になるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態 ( $V_{gt} = 30V$ ) における書込特性を示す特性線であり、 $Q_{df}$ は、本構成例に係るソース電極及びドレイン電極とブラック絶縁膜との重なり寸法が異なるように形成した素子構造を有するダブルゲート型トランジスタにおいて、トップゲート電圧を印加した状態 ( $V_{gt} = 30V$ ) における書込特性を示す特性線である。

20

#### 【0140】

このように、本構成例に係るダブルゲート型トランジスタを、第2の実施形態に示したような表示画素EMB（電流印加方式に対応した画素駆動回路DCB）に適用することにより、上述したような電圧-電流特性の改善に伴って、ダブルゲート型トランジスタのゲート幅を小さくして表示パネルの開口率を向上することができ、また、ゲート電圧を低電圧化してトランジスタ特性の劣化や消費電力を抑制することができるとともに、電流特性及び書込特性の顕著な改善に伴って、書込電流に対する出力電流の線形性、及び、書込電流に対する書込率を顕著に向上させることができるので、画像情報を適切な輝度階調で表示することができ、表示画質がさらに優れた画像表示装置を実現することができる。

30

#### 【0141】

図19は、本構成例に係るダブルゲート型トランジスタの素子構造の他の構成例と、当該ダブルゲート型トランジスタを、電流印加方式に対応した画素駆動回路（表示画素）に適用した場合の他の回路構成例を示す図である。ここで、上述したダブルゲート型トランジスタの素子構造（図14）及び表示画素（画素駆動回路；図3）と同等の構成については同一の符号を付してその説明を簡略化する。

#### 【0142】

上述した第2の構成例に係るダブルゲート型トランジスタDGTbにおいては、図14に示したように、ソース電極32とブラック絶縁膜34との重なり寸法OLsに対して、ドレイン電極33とブラック絶縁膜34との重なり寸法OLdを大きく設定し、かつ、ドレイン電極33（ドレイン端子D）に高電位電圧が、また、ソース電極32（ソース端子S）に低電位電圧が印加されたバイアス状態に設定することにより、ソース電極32を介して有機EL素子（発光素子）OELに流れる発光駆動電流  $I_b$ （ドレイン電流  $I_d$ ）を増加させることができる（電圧-電流特性を向上させることができる）ことについて説明したが、ドレイン電極33（ドレイン端子D）及びソース電極32（ソース端子S）が印加されるバイアス電圧の関係が逆極性に設定されている場合には、図19（a）に示すように、ドレイン電極側の重なり寸法OLdをソース電極側の重なり寸法OLsよりも小さく設定した素子構造を有するダブルゲート型トランジスタDGTcを適用することができる。

40

#### 【0143】

なお、このように、ソース電極32（ソース端子S）に高電位電圧が、また、ドレイン

50

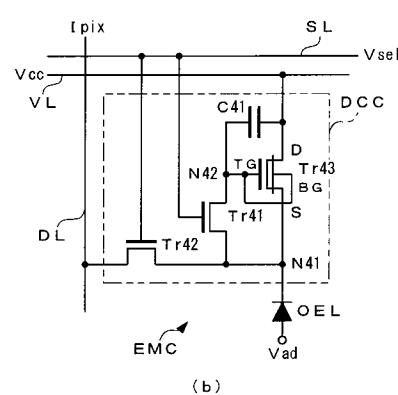

電極 33 (ドレイン端子 D) に低電位電圧が印加されたバイアス状態で、有機 E L 素子 (発光素子) O E L に負の発光駆動電流 (ドレイン電流) を供給する (引き抜く) 素子構造を有するダブルゲート型トランジスタ D G T c は、例えば、図 19 (b) に示すように、ゲート端子が走査ライン S L に、ソース端子及びドレイン端子がデータライン D L 及び接点 N 41 に各々接続された薄膜トランジスタ T r 42 と、ゲート端子が走査ライン S L に、ソース端子及びドレイン端子が接点 N 41 及び接点 N 42 に各々接続された薄膜トランジスタ T r 41 と、ゲート端子が接点 N 42 に、ドレイン端子が電源ライン V L に接続されるとともに、ソース端子が接点 N 41 に各々接続されたダブルゲート型トランジスタ T r 43 (本構成例に係るダブルゲート型トランジスタ D G T c に相当する) と、接点 N 42 及び電源ライン V L 間に接続されたコンデンサ C 41 と、を備えた画素駆動回路 D C C 10 及び、該画素駆動回路 D C C の接点 N 42 にカソード端子が接続され、アノード端子が接地電位に接続された有機 E L 素子 (発光素子) O E L を有して構成される表示画素 E M C に良好に適用することができる。ここで、ダブルゲート型トランジスタ T r 43 は、トップゲート端子 T G 及びボトムゲート端子 B G が電気的に短絡するように接続されている。

#### 【0144】

このような表示画素 E M C (画素駆動回路 D C C )においては、上述したデータトランジスタ 130 からの階調信号電流 I pix の書き動作時には、図 4 (a) に示した動作状態とは逆に、データライン D L 側から画素駆動回路 D C C (薄膜トランジスタ T r 42 、接点 N 41 、ダブルゲート型トランジスタ T r 43 ) を介して電源ライン V L 方向に、書き電流 I a が流れる。一方、表示画素 E M C における発光動作時には、図 4 (b) に示した動作状態とは逆に、有機 E L 素子 O E L 側から画素駆動回路 D C C (接点 N 41 、ダブルゲート型トランジスタ T r 43 ) を介して電源ライン V L 方向に、発光駆動電流 I b が流れる。 20

#### 【0145】

この場合においても、図 19 (a) に示したような、ソース電極及びドレイン電極とブロック絶縁膜 (チャネル領域) との重なり寸法が異なる素子構造を有するダブルゲート型トランジスタを、発光駆動用トランジスタとして適用することにより、上述した場合と同様に、電圧 - 電流特性を改善して、当該ダブルゲート型トランジスタのトランジスタサイズ (ゲート幅) を小さくすることができるので、表示パネル 110 の開口率を向上させることができ、また、ゲート電圧を低電圧化してトランジスタ特性の劣化や消費電力を抑制することができるとともに、電流特性及び書き特性を顕著に改善して、表示画質に優れた画像表示装置を実現することができる。 30

#### 【0146】

このように、本構成例に係るダブルゲート型トランジスタを、第 2 の実施形態に示したような表示画素 E M B (電流印加方式に対応した画素駆動回路 D C B ) に適用することにより、上述したような電圧 - 電流特性の改善に伴って、ダブルゲート型トランジスタのゲート幅を小さくして開口率を向上することができ、また、ゲート電圧を低電圧化してトランジスタ特性の劣化や消費電力を抑制することができるとともに、電流特性及び書き特性の改善に伴って、書き電流に対する出力電流の線形性、及び、書き電流に対する書き率を向上させることができるので、画像情報を適切な輝度階調で表示することができ、表示画質に優れた画像表示装置を実現することができる。 40

#### 【0147】

##### <第 3 の構成例>

次いで、本発明に係る画素駆動回路に適用されるダブルゲート型トランジスタの素子構造の第 3 の構成例について図面を参照して説明する。

図 20 は、本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第 3 の構成例を示す断面構成図である。また、図 21 は、本構成例に係るダブルゲート型トランジスタを、上述した各実施形態に係る表示画素 (画素駆動回路) に適用した場合の素子構造の一例を示す概略構成図である。なお、図 21

においては、図示の都合上、図7(a)に示した平面構成図のトップゲート電極を2点鎖線で表し、図21(b)、(c)に示した断面構成図のハッチングを一部省略した。また、上述した各実施形態と同等の構成については、同一の符号を付してその説明を簡略化する。

#### 【0148】

上述した第1及び第2の構成例に係るダブルゲート型トランジスタDGT、DGTa～DGTcにおいては、半導体層31上にプロック絶縁膜34を介して、当該プロック絶縁膜34上にソース電極32及びドレイン電極33が延在して形成された素子構造を示したが、本構成例に係るダブルゲート型トランジスタDGTdにおいては、図20(a)に示すように、半導体層(チャネル領域)31の両端領域に、該半導体層31上に直接形成されたn<sup>+</sup>シリコンからなる不純物層(オーミックコンタクト層)37、38を介して、ソース電極32(ソース端子S)及びドレイン電極33(ドレイン端子D)が形成された素子構造を有している。すなわち、図6(a)に示した第1の構成例に係るダブルゲート型トランジスタの素子構造において、半導体層31上に形成されたプロック絶縁膜34を除いた構成を有している。

#### 【0149】

そして、このような構成を有するダブルゲート型トランジスタDGTdを、上述したような表示画素EMA、EMBの画素駆動回路DCA(図2参照)、DCB(図3参照)に適用する場合にあっては、トップゲート電極ELt(トップゲート端子TG)とボトムゲート電極ELb(ボトムゲート端子BG)とが電気的に接続(短絡)された構成を有していることから、上述した第1の構成例に係るダブルゲート型トランジスタDGTと同様に、例えば、図21(a)、(c)に示すように、ダブルゲート型トランジスタDGTdの形成領域近傍に設けられたコンタクト領域Rcntにおいて、延在して形成されたトップゲート電極ELtがトップゲート絶縁膜35及びボトムゲート絶縁膜36を貫通して形成された開口部(コンタクトホール)を介して、延在して形成されたボトムゲート電極ELbに電気的に接続されるように構成されている。

#### 【0150】

また、画素駆動回路DCA(図2参照)、DCB(図3参照)において、ゲート-ソース間に接続されるコンデンサC11、C12は、例えば、図21(a)、(b)に示すように、ダブルゲート型トランジスタDGTdの形成領域近傍に設けられた容量領域RGcにおいて、各々延在して形成されたトップゲート電極ELt及びソース電極32がトップゲート絶縁膜35を介して対向することにより容量成分Caが形成され、また、各々延在して形成されたボトムゲート電極ELb及びソース電極32がボトムゲート絶縁膜36を介して対向することにより、容量成分Cbが形成される。そして、これらの容量成分Ca、Cbの総和が各コンデンサC11、C12の容量値となる。

#### 【0151】

次いで、上述したような素子構造及び接続構造を有するダブルゲート型トランジスタの素子特性について説明する。

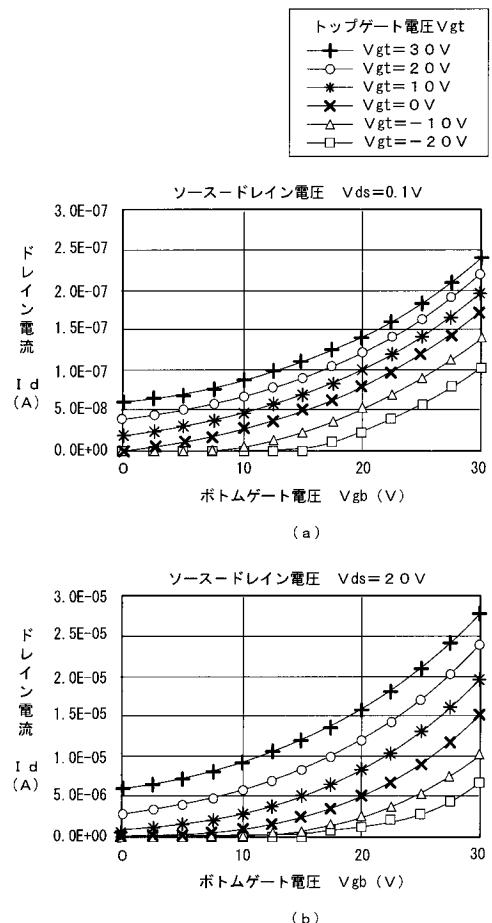

図22は、本構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧-電流特性を示す図(シミュレーション結果)であり、図23は、本構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に接続(短絡)した状態における電圧-電流特性を示す図(シミュレーション結果)である。

#### 【0152】

まず、上述したダブルゲート型トランジスタDGTにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における、ボトムゲート電圧Vgbに対するドレイン電流(オン電流)Idの変化傾向(電圧-電流特性)について検証すると、図22(a)、(b)に示すように、ボトムゲート電圧Vgbに対するドレイン電流Idの変化傾向は、ソース-ドレイン端子間の電位差(すなわち、バイアス電圧)Vdsが比較的大きい場合(Vds=20V)であっても、また、比較的小さい場合(Vds=0.1V)であっても、

10

20

30

40

50

上述した第1の構成例に係るダブルゲート型トランジスタの素子特性(図8(a)、(b)参照)に比較して、トップゲート電圧 $V_{gt}$ に正の電圧(10V 20V 30V)を印加した場合には、ドレイン電流 $I_d$ が増加する傾向を示し、また、トップゲート電圧 $V_{gt}$ に負の電圧(-10V -20V)を印加した場合には、ドレイン電流 $I_d$ が顕著に減少する傾向を示すことが観測された。特に、トップゲート電圧 $V_{gt}$ に正の電圧を印加した場合には、ドレイン電流 $I_d$ が顕著に増加することが判明した。

#### 【0153】

これは、本構成例に係るダブルゲート型トランジスタDGTdにおいては、図6に示したダブルゲート型トランジスタDGTの素子構造のように、半導体層31とソース電極32及びドレイン電極33との間にプロック絶縁膜34上が介在しないため、上述した擬似的なトップゲート電極としての機能が働くことなく、図20(b)に示すように、ソース電極32及びドレイン電極33が延在して形成されていない領域の半導体層31においてのみ、チャネル領域Rchが形成されて、トップゲート電極ELtに印加されたゲート電圧 $V_{gt}$ による当該チャネル領域Rchへの電界の影響が遮られることがないものと考えられる。10

#### 【0154】

また、図22(a)、(b)において、ダブルゲート型トランジスタDGTdのトップゲート電圧 $V_{gt}$ を0Vに設定した場合の電圧-電流特性は、トップゲート電極を備えず、単一のゲート電極のみからなる一般的な電界効果型トランジスタ(薄膜トランジスタ)における電圧-電流特性と同等と考えることができるので、当該薄膜トランジスタと、本構成例に係るダブルゲート型トランジスタDGTdにおいてトップゲート端子とボトムゲート端子とを電気的に接続した素子構造(図21)と、における電圧-電流特性を比較すると、図22に示した場合と同様に、ソース-ドレイン端子間のバイアス電圧 $V_{ds}$ の大小に関わらず、ゲート電圧(ボトムゲート電圧) $V_{gb}$ に対するトレイン電流 $I_d$ の変化傾向は、図23(a)、(b)に示すように、ダブルゲート型トランジスタDGTにおけるドレイン電流 $I_d$ の方が顕著に増加することが観測された。なお、図23(a)、(b)において、 $Y_{tft}$ は、単一のゲート電極を備えた電界効果型トランジスタにおける電圧-電流特性を示す特性線であり、 $Y_{dgt}$ は、本構成例に係るトップゲート電極とボトムゲート電極とを短絡したダブルゲート型トランジスタにおける電圧-電流特性を示す特性線である。20

#### 【0155】

このことから、図2、図3に示したような第1及び第2の実施形態に係る表示画素EMA、EMBにおいて、画素駆動回路DCA、DCBの発光駆動用トランジスタとして、図21に示したようなトップゲート電極ELtとボトムゲート電極ELbとを短絡した素子構造を有するダブルゲート型トランジスタDGTdを適用することにより、電子移動度が比較的低いアモルファスシリコン半導体層を用いたトランジスタ構造においても、同一のゲート電圧で、より大きなドレイン電流(発光駆動電流)を有機EL素子OLEに流すことができる。30

#### 【0156】

したがって、電圧印加方式及び電流印加方式のいずれの駆動制御方法に対応した画素駆動回路においても、同一のドレイン電流(発光駆動電流)を流すために、ダブルゲート型トランジスタのトランジスタサイズ(特に、ゲート幅)を小さくすることができるので、各表示画素における有機EL素子の形成面積(発光領域)を相対的に増やすことができ、表示パネルの開口率を向上させることができる。40

#### 【0157】

また、同一のドレイン電流を流すために、ダブルゲート型トランジスタのゲート電圧を低く設定することができるので、トランジスタ特性(電圧-電流特性)の劣化を抑制して、動作特性に優れた画素駆動回路(すなわち、表示特性に優れた表示パネル)を実現することができるとともに、画像表示動作に伴う消費電力を抑制することができる。

#### 【0158】

さらに、本構成例に係るダブルゲート型トランジスタにおいては、ソース-ドレイン端50

子間の電位差（バイアス電圧） $V_{ds}$ が比較的小さい場合であっても、ドレン電流 $I_d$ が顕著に増加する傾向を示すことから、画素駆動回路DCAやDCBにおいて、発光駆動用トランジスタのような、バイアス電圧が大きい飽和動作領域で動作する場合のみならず、バイアス電圧が比較的小さい線形動作領域で動作する場合においても、ドレン電流 $I_d$ を増加させることができるので、例えば、画素駆動回路DCAやDCBを構成する薄膜トランジスタTr11や、薄膜トランジスタTr21、Tr22等の、発光駆動用トランジスタ以外の薄膜トランジスタにも良好に適用することができ、これらの薄膜トランジスタのトランジスタサイズ（ゲート幅）を縮小して、表示パネルの開口率を一層向上させることができる。

## 【0159】

10

なお、上述した各実施形態においては、画素駆動回路における発光素子に発光駆動電流を流すダブルゲート型トランジスタの、トップゲート端子とボトムゲート端子とが短絡される構成としたが、これに限るものではなく、例えば、トップゲート端子にボトムゲート端子とは異なる電圧を印加するようにしてもよい。この場合、例えばトップゲート端子にボトムゲート端子より高い電圧を印加することにより、トップゲート端子とボトムゲート端子とを短絡した場合に比較して、電圧・電流特性（ゲート電圧に対するドレン電流）を更に改善して、同一のゲート電圧で、より大きな発光駆動電流を流すことができ、また、同一の発光駆動電流を流すためのスイッチング素子の素子サイズを更に小さくすることができる。

## 【図面の簡単な説明】

20

## 【0160】

【図1】本発明に係る表示装置の全体構成の一例を示すブロック図である。

【図2】本発明に係る画素駆動回路を備えた表示画素の第1の実施形態を示す回路構成図である。

【図3】本発明に係る画素駆動回路を備えた表示画素の第2の実施形態を示す回路構成図である。

【図4】第2の実施形態に係る表示画素（画素駆動回路）の動作状態を示す概念図である。

【図5】第2の実施形態に係る画素駆動回路を適用した表示画素の基本動作を示すタイミングチャートである。

30

【図6】本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第1の構成例を示す断面構成図及び回路図である。

【図7】第1の構成例に係るダブルゲート型トランジスタを、上述した各実施形態に係る表示画素（画素駆動回路）に適用した場合の素子構造の一例を示す概略構成図である。

【図8】第1の構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧・電流特性を示す図（シミュレーション結果）である。

【図9】第1の構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に接続（短絡）した状態における電圧・電流特性を示す図（シミュレーション結果）である。

40

【図10】第2の実施形態に示した画素駆動回路におけるダブルゲート型トランジスタの書き動作を検証するためのシミュレーションモデル（簡略化した等価回路）を示す回路図である。

【図11】第1の構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流（入力電流）と発光駆動電流（出力電流）の関係（電流特性）を示す特性図（シミュレーション結果）である。

【図12】第1の構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流（入力電流）と当該画素駆動回路への書き率との関係を示す特性図（シミュレーション結果）である。

【図13】第1の構成例に係るダブルゲート型トランジスタの素子構造の他の構成例を示

50

す断面構成図である。

【図14】本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第2の構成例を示す断面構成図及び回路図である。

【図15】第2の構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧-電流特性を示す図(シミュレーション結果)である。

【図16】第2の構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における電圧-電流特性を説明するためである。

【図17】第2の構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流(入力電流)と発光駆動電流(出力電流)の関係(電流特性)を示す特性図(シミュレーション結果)である。

【図18】第2の構成例に係るダブルゲート型トランジスタを、第2の実施形態に示した画素駆動回路に適用した場合における階調信号電流(入力電流)と当該画素駆動回路への書き率との関係を示す特性図(シミュレーション結果)である。

【図19】第2の構成例に係るダブルゲート型トランジスタの素子構造の他の構成例と、当該ダブルゲート型トランジスタを、電流印加方式に対応した画素駆動回路(表示画素)に適用した場合の他の回路構成例を示す図である。

【図20】本発明に係る画素駆動回路の発光駆動用トランジスタに適用されるダブルゲート型トランジスタの素子構造の第3の構成例を示す断面構成図及び回路図である。

【図21】第3の構成例に係るダブルゲート型トランジスタを、上述した各実施形態に係る表示画素(画素駆動回路)に適用した場合の素子構造の一例を示す概略構成図である。

【図22】第3の構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に独立した状態における電圧-電流特性を示す図(シミュレーション結果)である。

【図23】第3の構成例に係るダブルゲート型トランジスタにおいて、トップゲート端子とボトムゲート端子とを電気的に接続(短絡)した状態における電圧-電流特性を示す図(シミュレーション結果)である。

【図24】従来技術における発光素子型ディスプレイの要部を示す概略構成図である。

【図25】従来技術における発光素子型ディスプレイに適用可能な各表示画素(画素駆動回路及び発光素子)の要部構成例を示す等価回路図である。

#### 【符号の説明】

##### 【0161】

|                         |               |

|-------------------------|---------------|

| 1 0 0                   | 表示装置          |

| 1 1 0                   | 表示パネル         |

| 1 2 0                   | 走査ドライバ        |

| 1 3 0                   | データドライバ       |

| S L                     | 走査ライン         |

| D L                     | データライン        |

| E M、E M A ~ E M C       | 表示画素          |

| D C A ~ D C C           | 画素駆動回路        |

| D G T、D G T a ~ D G T d | ダブルゲート型トランジスタ |

| O E L                   | 有機EL素子        |

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

(a)

(b)

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 05 B 33/14

A

(72)発明者 武居 学

東京都八王子市石川町2951番地の5

センター内

カシオ計算機株式会社八王子技術

F ターム(参考) 3K007 AB02 AB12 AB17 AB18 BA06 DB03 GA00

5C080 AA06 BB05 DD22 DD28 EE29 FF01 FF11 HH09 JJ02 JJ03

JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素驱动电路和图像显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2006091089A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-04-06 |

| 申请号            | JP2004273206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2004-09-21 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 白寄友之<br>山口郁博<br>武居学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 白寄 友之<br>山口 郁博<br>武居 学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0417 G09G2300/0842 G09G2300/0861 G09G2330/021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.C G09G3/20.641.D G09G3/20.680.H H05B33/14.A<br>G09G3/3241 G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB12 3K007/AB17 3K007/AB18 3K007/BA06 3K007/DB03 3K007/GA00 5C080<br>/AA06 5C080/BB05 5C080/DD22 5C080/DD28 5C080/EE29 5C080/FF01 5C080/FF11 5C080/HH09<br>5C080/JJ02 5C080/JJ03 5C080/JJ05 5C080/JJ06 3K107/AA01 3K107/BB01 3K107/CC21 3K107<br>/CC31 3K107/CC36 3K107/CC45 3K107/EE04 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01<br>5C380/AA03 5C380/AB06 5C380/AB22 5C380/AC07 5C380/AC08 5C380/BA01 5C380/BA05 5C380<br>/BA11 5C380/BA29 5C380/BB22 5C380/BD05 5C380/BD09 5C380/BD10 5C380/BD16 5C380/CA04<br>5C380/CA12 5C380/CA13 5C380/CA32 5C380/CA34 5C380/CB01 5C380/CB14 5C380/CB16 5C380<br>/CB33 5C380/CC02 5C380/CC13 5C380/CC14 5C380/CC27 5C380/CC33 5C380/CC41 5C380/CC52<br>5C380/CC62 5C380/CC63 5C380/CC72 5C380/CC77 5C380/CD012 5C380/CD013 5C380/CD014<br>5C380/CE17 5C380/CE19 5C380/CE21 5C380/CF07 5C380/CF09 5C380/CF20 5C380/CF22 5C380<br>/CF24 5C380/DA02 5C380/DA06 5C380/DA32 5C380/DA35 |         |            |

| 其他公开文献         | <a href="#">JP5152448B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

## 摘要(译)

提供了一种像素驱动电路和图像显示装置，其通过在简化制造工艺和提高成品率的同时实现改善的开口率和可靠性而具有良好的显示质量。显示像素EMA具有薄膜晶体管Tr11，其中栅极端子连接到扫描线SL，源极端子和漏极端子连接到数据线DL，并且在扫描线SL和数据线DL的每个交叉点附近都有触点N11。顶栅极端子TG和底栅极端子BG连接到触点N11，源极端子S连接到电源线VL，并且双栅极晶体管Tr12连接在触点N11和预定的低电位电源Vss之间。像素驱动电路DCA包括电容器C11和有机EL元件OEL，有机EL元件OEL的阳极端子连接至像素驱动电路DCA的双栅晶体管Tr12的漏极端子D，并且阴极端子连接至地电位。它被配置为具有。[\[选择图\]图2](#)