(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-181422

(P2005-181422A)

(43) 公開日 平成17年7月7日(2005.7.7)

(51) Int.Cl.<sup>7</sup>

**G09F 9/30**

**H01L 29/786**

**H05B 33/10**

**H05B 33/14**

F 1

G09F 9/30 365Z

G09F 9/30 338

G09F 9/30 349C

H05B 33/14 A

テーマコード(参考)

3K007

5C094

5F110

審査請求 未請求 請求項の数 16 O L (全 27 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2003-418320 (P2003-418320)

平成15年12月16日 (2003.12.16)

(71) 出願人 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(74) 代理人 100114672

弁理士 宮本 恵司

(72) 発明者 伊賀 大輔

東京都港区芝五丁目7番1号 日本電気株

式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 FA00

5C094 AA03 AA06 AA25 AA42 BA03

BA27 ED15 FB01 FB20

最終頁に続く

(54) 【発明の名称】発光型表示装置及びその製造方法

## (57) 【要約】

【課題】EL発光素子から放出される光に起因した TFT の光リークを防止する構造を備えるアクティブマトリクス有機EL表示装置の提供。

【解決手段】絶縁性基板1上のゲート線12とデータ線10とで囲まれた画素25に1以上のトランジスタを含む画素駆動TFT18と、複数の層間膜と、陽極5とEL有機層7と陰極8とによりなるEL発光素子19とが順次形成され、画素駆動TFT18とEL発光素子19とが基板の法線方向から見て重ならないよう配置されるアクティブマトリクス有機EL表示装置において、陽極5の周囲又は画素駆動TFT18の周囲又は表示領域16の周囲の少なくとも一部に、EL発光素子19下層に位置する第2層間膜4を縦断する遮光帯22を備え、遮光帯22によって層間膜中を伝搬する迷光を反射又は減衰させ、TFTの誤動作による画素表示欠陥やコントラストの低下を防止する。

【選択図】図6

**【特許請求の範囲】****【請求項 1】**

絶縁基板上に互いに略直交する方向に延在する複数の配線が形成され、前記複数の配線により囲まれた領域に設けられた単位画素が複数個配列されて表示領域が形成され、各々の前記単位画素に、1つ以上のトランジスタにより構成される画素駆動回路と、前記画素駆動回路を被覆する少なくとも2層の絶縁層と、発光部とが順次積層形成され、前記画素駆動回路と前記発光部とは前記絶縁基板の法線方向から見て重なり合わないように配置されてなる発光表示装置において、

前記少なくとも2層の絶縁層のうち、前記画素駆動回路を構成する前記トランジスタに接続された配線層よりも上に積層されている絶縁層の少なくとも1層に、該絶縁層を伝播する光を反射する手段、又は該絶縁層を伝播する光を減衰する手段の少なくとも一方として機能する遮光手段を有することを特徴とする発光表示装置。10

**【請求項 2】**

請求項1に記載の発光表示装置において、前記遮光手段が、前記少なくとも1層の絶縁層とは光学的屈折率の異なる部材を用いて、該絶縁層を縦断するように形成されていることを特徴とする発光表示装置。

**【請求項 3】**

請求項1又は2に記載の発光表示装置において、前記遮光手段の側面が、前記絶縁基板の面に対して略垂直又は逆テーパー状に形成されていることを特徴とする発光表示装置。20

**【請求項 4】**

請求項1乃至3のいずれか一に記載の発光表示装置において、前記遮光手段が、前記絶縁基板の法線方向から見て、前記発光部周囲の少なくとも一部に、該発光部を取り囲むように帯状に形成されることを特徴とする発光表示装置。20

**【請求項 5】**

請求項4に記載の発光表示装置において、前記遮光手段が、前記絶縁基板の法線方向から見て、前記複数の配線の少なくとも一方と重なり合うように形成されることを特徴とする発光表示装置。

**【請求項 6】**

請求項1乃至3のいずれか一に記載の発光表示装置において、前記遮光手段が、前記画素駆動回路を構成する前記トランジスタ周囲の少なくとも一部に、該発光部を取り囲むように帯状に形成されることを特徴とする発光表示装置。30

**【請求項 7】**

請求項1乃至6のいずれか一に記載の発光表示装置において、前記遮光手段の上部が略平坦に形成されることを特徴とする発光表示装置。

**【請求項 8】**

請求項1乃至7のいずれか一に記載の発光表示装置において、前記画素駆動回路を構成する前記トランジスタの下層、又は、周辺回路領域の回路を構成するトランジスタの下層の少なくとも一方に、遮光層を備えることを特徴とする発光表示装置。

**【請求項 9】**

請求項1乃至8のいずれか一に記載の発光表示装置において、前記発光部が有機EL発光素子で構成されることを特徴とする発光表示装置。40

**【請求項 10】**

絶縁基板上に互いに略直交する方向に延在する複数の配線を形成し、前記複数の配線により囲まれた領域に設けた単位画素を複数個配列して表示領域を形成し、各々の前記単位画素には、1つ以上のトランジスタにより構成される画素駆動回路と、前記画素駆動回路を被覆する少なくとも2層の絶縁層と、発光部とを順次積層形成し、前記画素駆動回路と前記発光部とを前記絶縁基板の法線方向から見て重なり合わないように配置する発光表示装置の製造方法において、

前記少なくとも2層の絶縁層のうち、前記画素駆動回路を構成する前記トランジスタに接続された配線層よりも上に積層されている絶縁層の少なくとも1層に、該絶縁層を伝播

50

20

30

40

50

する光を反射する手段、又は該絶縁層を伝播する光を減衰する手段の少なくとも一方として機能する遮光手段を形成する工程を有することを特徴とする発光表示装置の製造方法。

【請求項 1 1】

請求項 1 0 に記載の発光表示装置の製造方法において、前記遮光手段を形成する工程は、前記少なくとも 1 層の絶縁層に溝を形成する工程と、形成された前記溝に前記絶縁層とは光学的屈折率の異なる部材を充填する工程とを含むことを特徴とする発光表示装置の製造方法。

【請求項 1 2】

請求項 1 1 に記載の発光表示装置の製造方法において、前記少なくとも 1 層の絶縁層に溝を形成する工程を、前記複数の配線のいずれか一方と前記発光部の陽極とを接続するためのコンタクトホールを形成する工程と同時にを行うことを特徴とする発光表示装置の製造方法。

【請求項 1 3】

請求項 1 1 に記載の発光表示装置の製造方法において、前記少なくとも 1 層の絶縁層に溝を形成する工程を、前記発光部の陽極を形成した後に行なうことを行なうことを特徴とする発光表示装置の製造方法。

【請求項 1 4】

請求項 1 1 乃至 1 3 のいずれか一に記載の発光表示装置の製造方法において、前記少なくとも 1 層の絶縁層に溝を形成する工程では、前記溝の側面を前記絶縁基板の面に対して略垂直又は逆テーパー状に加工することを特徴とする発光表示装置の製造方法。

【請求項 1 5】

請求項 1 1 乃至 1 4 のいずれか一に記載の発光表示装置の製造方法において、前記光学的屈折率の異なる部材とは、前記発光部の前記陽極上に形成される平坦化膜であることを特徴とする発光表示装置の製造方法。

【請求項 1 6】

請求項 1 0 乃至 1 5 のいずれか一に記載の発光表示装置の製造方法において、有機 E L 発光素子により前記発光部を形成することを特徴とする発光表示装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は発光型表示装置及びその製造方法に関し、特に、有機エレクトロルミネッセンス ( E L : Electro Luminescence ) 発光部と、薄膜トランジスタ ( T F T : Thin Film Transistor ) からなる駆動回路部を備えた、アクティブマトリクス方式の有機エレクトロルミネッセンス表示装置及びその製造方法に関する。

【背景技術】

【0 0 0 2】

有機 E L 素子は、電界を印加することにより、陽極より注入された正孔と陰極より注入された電子の再結合エネルギーによって蛍光性物質が発光する原理を利用した自発光型の表示素子である。視野角が広く、応答特性が良いという特性から、近年 C R T や L C D に変わる表示装置として注目されている。なかでもマトリクス状に配置した有機 E L 発光素子を、T F T を利用して駆動する、アクティブマトリクス型有機 E L 素子が注目されている。

【0 0 0 3】

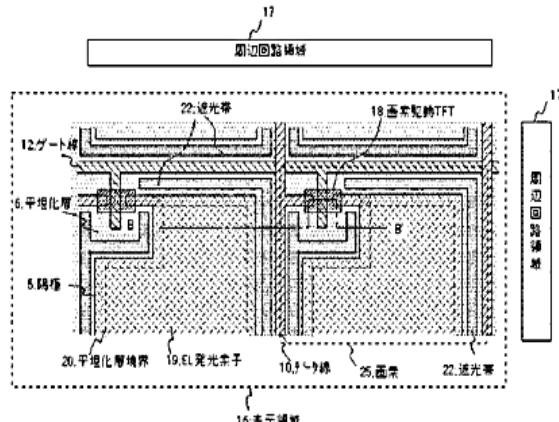

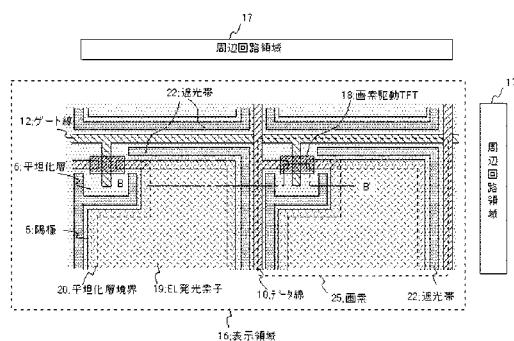

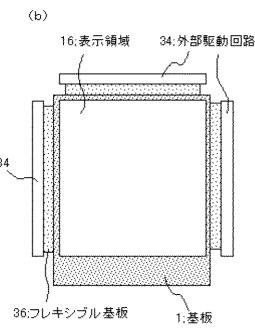

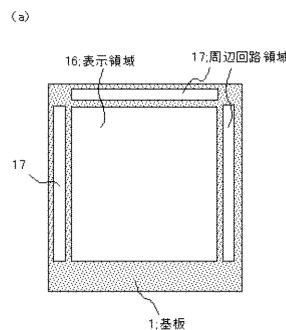

アクティブマトリクス有機 E L 表示装置は、有機 E L 発光素子と、その有機 E L 発光素子を駆動する T F T 能動素子の組み合わせからなる単位画素と、単位画素を制御するための能動素子とコンデンサや抵抗などの受動素子からなる周辺回路から構成される。典型的な構成は図 1 に示すようなもので、( a ) のように基板上に表示領域 1 6 が形成され、その周辺に表示領域 1 6 と同一の基板上に、T F T 能動素子を用いて構成された周辺回路領域 1 7 が配置されている例と、( b ) のように、表示領域 1 6 の周辺に L S I などによって構成された外部駆動回路 3 4 がフレキシブル基板 3 6 などによって接続されている例と

10

20

30

40

50

がある。

【0004】

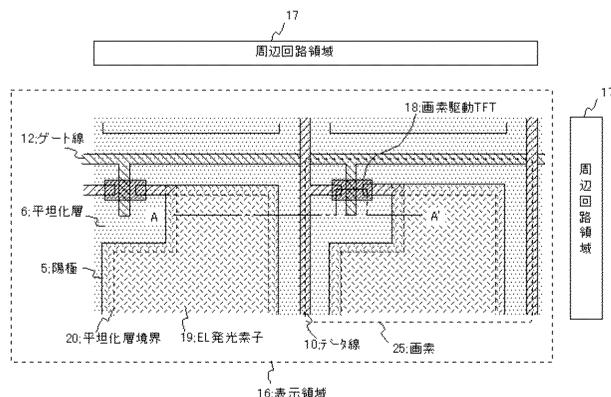

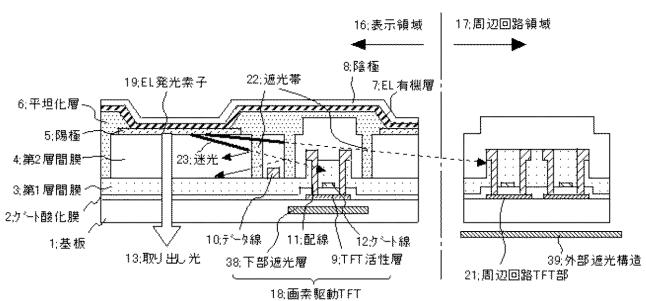

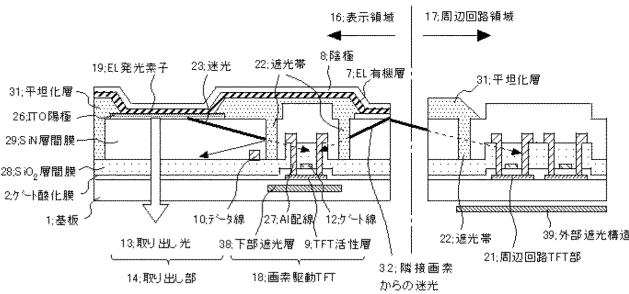

図2にアクティブマトリクス有機EL表示装置の表示領域の詳しい平面図を、図3に図2のA-A'に沿った断面図を示す。なお両図は、表示領域16と同一基板上に周辺回路を形成した場合の例であって、LSIによって基板の外部に設けられる場合もある。

【0005】

図2を用いて平面構造を説明すると、従来のアクティブマトリクス有機EL表示装置は、互いに直行する方向に延びたゲート線12とデータ線10とを備え、その交点の1つ1つに対応して画素25が形成されている。

【0006】

画素25は画素駆動TFT18を具有し、その上を、構造物に起因する凹凸を平坦化する目的で平坦化層6が覆っている。平坦化層6は陽極5の上部で開口しており、平坦化層境界20の内側でEL発光素子19が形成されている。なお、図2では画素駆動TFT18は1つのみであるが、駆動方式により複数のTFTにより構成される場合もある。そして、画素25は格子状に配列されて表示領域16を構成し、表示領域16の外周には駆動回路が構成された周辺回路領域17が形成される。

【0007】

図3を用いて断面構造を説明すると、従来のアクティブマトリクス有機EL表示装置は、ガラスなどの透明な基板1上にTFT活性層9が形成され、その上にゲート酸化膜2を介してゲート線12が形成されている。そして、ゲート線12を覆うようにして第1層間膜3が形成され、第1層間膜3の上に配線層が形成される。配線11はコンタクトホールを介して、TFT活性層9のソース／ドレイン領域に接続されている。配線11の上には第2層間膜4が形成され、その上に陽極5が形成されている。陽極5はコンタクトホールを介して、画素駆動TFT18に接続された配線11に接続されている。ここでは基板1から上、陽極5より下の部分を、便宜上、TFT基板と呼ぶ。

【0008】

表示領域16の内側では、上記TFT基板の上部に、平坦化層6が形成されている。平坦化層6の目的は、陽極5の段差、画素駆動TFT18上に発生する段差といった、構造物に起因する凹凸を緩和し、TFT基板の上に形成されるEL有機層7と陰極8の間で発生するオープン不良と、陰極8と陽極5の間で発生するショート不良を防止することである。なお、周辺回路領域17には、EL有機層7と陰極8が形成されないので、平坦化層6は形成されない。

【0009】

平坦化層6は陽極5の上部で開口していて、その上にEL有機層7と陰極8が形成され、開口部で接合が形成されEL発光素子19となる。なお、EL有機層7は第1ホール輸送層、第2のホール輸送層、発光層、電子輸送層からなり、陰極8は銀・マグネシウム合金、アルミ+アルミ・リチウム合金の2層、アルミ+フッ化リチウムの2層などにより形成されている。EL発光素子19で発せられた光は、光取り出し部14から取り出し光13となって外部へ導かれる。画像は図において下側に表示される。

【0010】

ここで図3を用いて、従来のアクティブマトリクス有機EL発光素子の製造方法を説明する。まず、透明な基板1上にCVD法により、TFT活性層9となる半導体層を形成した後、素子分離を行い、イオン注入による伝導型制御を行った後、CVD法によりゲート酸化膜2を形成し、スパッタ法によりゲート電極となる金属を堆積する。その後、ゲート線12のパターニングを行ってTFTが形成される。なお、素子分離、ゲート電極のパターニングには、ドライエッティングが用いられるのが一般的である。また、上記のTFT形成方法は非結晶SiTFTを用いる場合であり、ポリシリコンTFTを用いる場合には、シリコン層形成後に熱アニールまたはレーザーアニールにより多結晶化を行う工程が追加される。

【0011】

10

20

30

40

50

TFT 形成後は、CVD により第 1 層間膜 3 を成長する。続いて、所望の位置に、ドライエッチングによりコンタクトホールを形成し、スパッタによりデータ線 10 および配線 11 となる金属膜を成長後、ドライエッチングにより配線のパターニングを行う。さらに、配線 11 が形成される層の上に CVD 法により第 2 層間膜 4 を形成し、ドライエッチにより陽極 5 と配線 11 をつなぐコンタクトホールを形成後、スパッタ法により陽極 5 となる透明導電膜層を形成し、ドライエッチングにより陽極 5 をパターニングする。以上で TFT 基板が完成する。

#### 【0012】

TFT 基板完成後は、平坦化層 6 を形成し、開口部のパターニングを行った後、アニールを行って開口部端のリフローおよび平坦化を行う。その後、有機EL層 7 と陰極 8 を形成し、アクティブマトリクス有機EL表示装置が完成する。例として特開 2002-252088 号公報、特開 2002-231459 号公報に TFT により駆動されるアクティブマトリクス有機EL表示装置の構成が記載されている。10

#### 【0013】

【特許文献 1】特開 2002-252088 号公報（第 4 - 5 頁、第 55 図）

【特許文献 2】特開 2002-231459 号公報（第 5 頁、第 47 図）

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0014】

TFT 応用製品では、一般に光電効果により発生する TFT の光リーク電流の削減が課題となる。光リーク電流は、TFT で構成された回路の誤動作を引き起こし、表示装置への応用を考えた場合には、画素表示欠陥やコントラストの低下を引き起こしてしまう。この課題は本発明が関するアクティブマトリクス有機EL表示装置においても同様であり、アクティブマトリクス有機EL表示装置において考えられる光リークの原因となる光源は、太陽光や環境光といった外光と、自身が具有する EL 発光素子 19 から発せられる自発光である。20

#### 【0015】

リーク電流の影響について定量的に説明すると、アクティブマトリクス有機EL表示装置において、画素 25 に流れる最大電流量は、表示装置の要求輝度、発光効率、開口率などの要素に依存するものであるが、一般的に 50 nA ~ 150 nA 程度である。今、階調表示精度を 256 階調とすれば、1 階調あたり約 0.5 nA、64 階調の場合で約 2 nA となる。これに対して外光（太陽光）の場合では 1 nA から 10 nA 程度、EL 発光素子 19 からの光によるリーク電流の場合は 0.1 nA から 1 nA が見込まれる。よって階調表示精度が高くなればなるほどリーク電流の影響を大きく受けてしまう。30

#### 【0016】

外光から TFT を遮光する対策としては、同じく TFT をスイッチングに用いる液晶表示装置の分野においてすでに対策がなされていて、これらの手法はアクティブマトリクス有機EL表示素子においても有効であり、一般的には、TFT 基板中に、金属から成る遮光体を付加する構造が用いられる。たとえば、特開平 9-80476 号公報、特開平 11-84363 号公報、特開 2000-164875 号公報などに、TFT の上部、下部に遮光体を設けることによって、外部から画素駆動 TFT 18 へ入射する光を遮断する構造が記載されている。40

#### 【0017】

また、周辺回路領域 17 についての対策としては、周辺回路領域 17 はそれ自身が画像表示に寄与しないため、保護したい領域を完全に覆うように、十分に大きな遮光構造を表示装置の外部に設けることが可能である。

#### 【0018】

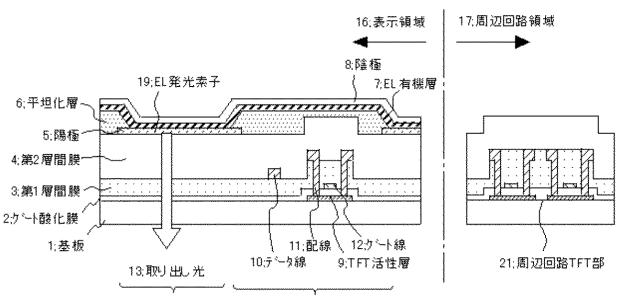

これら外光に対する対策を施した構造として、例えば図 4 に示すような構成があり、図 3 に示された構造において、画素駆動 TFT 18 と周辺回路 TFT 部 21 の下部に、それぞれ下部遮光層 38 と外部遮光構造 39 を追加した構造となっている。50

## 【0019】

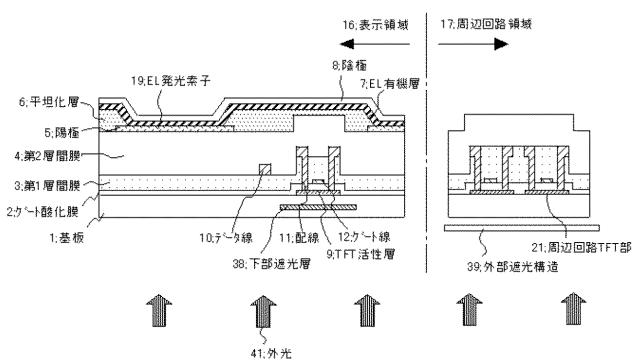

一方自発光については、光源であるEL発光素子19がTFTに隣接して配置されているため、基板横方向からTFTに入射する光を考慮しなくてはならない。また、EL発光素子19から発せられる光には指向性がなく、全方向に発せられるため、一部はTFT基板を構成する層間膜の界面で反射された後にTFT活性層9に入射する。特に、層間膜の屈折率から一義的に決まる、ある臨界角以上で界面に入射した光は、複数回の反射を繰り返した後、基板面の方向へ伝播した後TFT活性層9に入射する場合もある。

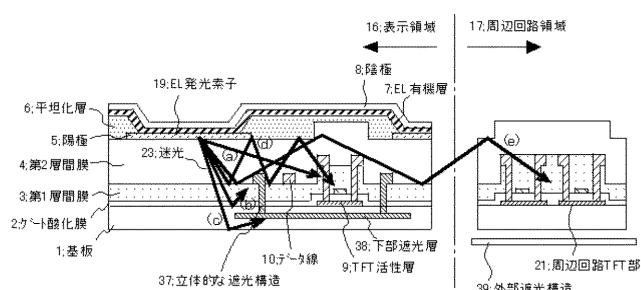

## 【0020】

上記、自発光がTFTへ入射する様子を図5を用いて詳しく説明する。基板横方向からTFTに入射するモードは図5中の(a)で示されるモードであり、反射による入射は(b)、(c)のモードであり、複数回の反射による入射は(d)、(e)のモードである。さらに詳しく説明すると、(b)は第1層間膜3と基板1の界面で反射を起こすモード、(c)は基板1の裏面で反射を起こすモード、(d)と(e)は第2層間膜4と第1層間膜3の界面と平坦化層6と第2層間膜4の界面で反射を起こすモードである。(d)と(e)の違いは到達距離の差を模式的に示すものである。実際には(b)～(e)のモードが複合的に組み合わさり、(b)および(c)のモードを経て(d)および(e)のモードに移行する場合や、(d)および(e)のモードを経て(b)および(c)のモードに移行する場合も存在する。

## 【0021】

さらに留意すべきは、(b)～(e)のモードでは、反射を繰り返すことで、EL発光素子19に隣接するTFTだけでなく、表示領域16の周囲に配置された周辺回路領域17を構成する周辺回路TFT部21にも自発光が到達可能である点である。そのため、周辺回路領域17が表示領域16と同一の基板上に形成される構成をとるアクティブマトリクス有機EL表示装置では、EL発光素子19に隣接する画素駆動TFT18だけでなく、表示領域16よりも外側に形成された周辺回路領域17に含まれている周辺回路TFT部21にも自発光に対する遮光対策が必要となる。

## 【0022】

上記5つのモードの内、(a)のモードのように直接TFTへ向かう光については、例えば特開2000-172198号公報のように着色平坦化絶縁膜を用いる例や、特開2000-172199号公報のようにEL発光層とTFT能動素子の間に、光の経路をさえぎるように遮光体を設ける方法が考案されている。しかしながら、これらの例では、TFTの側面に遮光を持たないため、(b)～(e)のように界面での反射によってTFTに到達した光により発生する光リークについては、効果的に防止できない。

## 【0023】

また、(b)～(e)のモードのように反射によってTFTに到達する光の対策としては、例えば特開2002-132186号公報には、配線材料を利用してTFT能動素子またはEL発光素子を囲むように立体的な遮光構造を形成する方法が記載されている。しかしながら、この構造は図5に示すように(b)のモードについては有効な遮光効果が得られるが、第2層間膜4には遮光体が形成されないため、(d)と(e)のモードの場合に対して有効な遮光効果を持たない。

## 【0024】

本発明は上記のような課題を解決すべく考案されたものであって、その主たる目的は、アクティブマトリクス有機EL表示装置で発生するTFT能動素子の光リークの原因となる自発光を確実に遮光することができる遮光構造を備える発光型表示装置及びその製造方法を提供することにある。より詳しくは、上記自発光のうち、図5の(d)、(e)のモードで例示されるような、EL発光素子19の直下に位置する層間膜中を該層間膜の界面で反射しながら基板の面方向に伝播してTFTに到達する光を確実に遮光し、TFTの誤動作による画素表示欠陥やコントラストの低下を防止することができる遮光構造を備えるアクティブマトリクス型有機EL素子及びその製造方法を提供することにある。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0025】

上記課題を解決するため、本発明のアクティプマトリクス有機EL表示装置は、絶縁基板上に互いに略直交する方向に延在する複数の配線が形成され、前記複数の配線により囲まれた領域に設けられた単位画素が複数個配列されて表示領域が形成され、各々の前記単位画素に、1つ以上のトランジスタにより構成される画素駆動回路と、前記画素駆動回路を被覆する少なくとも2層の絶縁層と、発光部とが順次積層形成され、前記画素駆動回路と前記発光部とは前記絶縁基板の法線方向から見て重なり合わないように配置されてなる発光表示装置において、前記少なくとも2層の絶縁層のうち、前記画素駆動回路を構成する前記トランジスタに接続された配線層よりも上に積層されている絶縁層の少なくとも1層に、該絶縁層を伝播する光を反射する手段、又は該絶縁層を伝播する光を減衰する手段の少なくとも一方として機能する遮光手段を有するものである。10

## 【0026】

本発明においては、前記遮光手段が、前記少なくとも1層の絶縁層とは光学的屈折率の異なる部材を用いて、該絶縁層を縦断するように形成されていることが好ましく、前記遮光手段の側面が、前記絶縁基板の面に対して略垂直又は逆テーパー状に形成されている構成とすることができます。

## 【0027】

また、本発明においては、前記遮光手段が、前記絶縁基板の法線方向から見て、前記発光部周囲の少なくとも一部に、該発光部を取り囲むように帯状に形成され、又は、前記画素駆動回路を構成する前記トランジスタ周囲の少なくとも一部に、該発光部を取り囲むように帯状に形成される構成とすることができます。20

## 【0028】

また、本発明においては、前記遮光手段の上部が略平坦に形成され、また、前記遮光手段の上部が略平坦に形成される前記画素駆動回路を構成する前記トランジスタの下層、又は、周辺回路領域の回路を構成するトランジスタの下層の少なくとも一方に、遮光層を備える構成とすることもできる。

## 【0029】

また、本発明においては、前記発光部が有機EL発光素子で構成されることが好ましい。30

## 【0030】

また、本発明の製造方法は、絶縁基板上に互いに略直交する方向に延在する複数の配線を形成し、前記複数の配線により囲まれた領域に設けた単位画素を複数個配列して表示領域を形成し、各々の前記単位画素には、1つ以上のトランジスタにより構成される画素駆動回路と、前記画素駆動回路を被覆する少なくとも2層の絶縁層と、発光部とを順次積層形成し、前記画素駆動回路と前記発光部とを前記絶縁基板の法線方向から見て重なり合わないように配置する発光表示装置の製造方法において、前記少なくとも2層の絶縁層のうち、前記画素駆動回路を構成する前記トランジスタに接続された配線層よりも上に積層されている絶縁層の少なくとも1層に、該絶縁層を伝播する光を反射する手段、又は該絶縁層を伝播する光を減衰する手段の少なくとも一方として機能する遮光手段を形成する工程を有するものである。40

## 【0031】

本発明においては、前記遮光手段を形成する工程は、前記少なくとも1層の絶縁層に溝を形成する工程と、形成された前記溝に前記絶縁層とは光学的屈折率の異なる部材を充填する工程とを含むことが好ましく、前記少なくとも1層の絶縁層に溝を形成する工程を、前記複数の配線のいずれか一方と前記発光部の陽極とを接続するためのコンタクトホールを形成する工程と同時に構成、又は、前記少なくとも1層の絶縁層に溝を形成する工程を、前記発光部の陽極を形成した後に行う構成とすることができます。

## 【0032】

また、本発明においては、前記光学的屈折率の異なる部材を、前記発光部の前記陽極上に形成される平坦化膜とすることができます。50

## 【発明の効果】

## 【0033】

以上説明したように、本発明によれば、自己の具有するEL発光素子から放出され、基板や層間膜の界面において反射された光をTFTに到達する前に遮光帯により減衰させることができ、自発光に起因するTFTの光リークを低減することができ、欠陥が少なく、階調制御性に優れたアクティブマトリクス有機EL表示装置を提供することができる。

## 【発明を実施するための最良の形態】

## 【0034】

本発明は、その好ましい一実施の形態において、絶縁性基板上に互いに直交する方向に延在するゲート線とデータ線とで囲まれた各々の領域に単位画素が設けられて表示領域が形成され、各々の単位画素には1以上のトランジスタを含む画素駆動TFTと、画素駆動TFT上に形成される複数の層間膜と、陽極とEL有機層と陰極とにより構成されるEL発光素子とが順次積層されて形成され、画素駆動TFTとEL発光素子とが基板の法線方向から見て相重なり合わないよう配置されるアクティブマトリクス有機EL表示装置において、陽極の周囲、又は画素駆動TFTの周囲、又は表示領域の周囲の少なくとも一部に、データ線の上層であってEL発光素子の下層に位置する層間膜を縦断する遮光帯を備え、遮光帯によって層間膜中を伝搬する迷光を反射又は減衰させ、これにより表示領域の画素駆動TFTや周辺回路領域の周辺回路TFTの誤動作による画素表示欠陥やコントラストの低下を防止するものである。

## 【0035】

上記遮光帯の効果を確認するために、図3に示すような遮光構造を持たない表示装置と、図4に示すような下部遮光層38のみを備える表示装置と、図7に示すような遮光帯及び下部遮光層を備える本発明の表示装置を用いて、画像を表示させた状態で、EL発光素子に流れる陰極電流の総和を測定した。動作原理より、光リーク電流が発生すると、トランジスタにより駆動される電流が減少し、陰極電流の総和は減少する。すなわちEL発光素子に流れる電流の総和が大きいほど、光リーク電流が少ないことを示すものである。

## 【0036】

まず、図4に例示されるような下部遮光層38のみを備える表示装置と、図3に例示されるような遮光構造を持たない表示装置を、屋外にて6000ルックス以上の照度の太陽光下に暴露して、外光に対する遮光性能を比較した結果、前者が後者に比べて30%大きい陰極電流を示した。

## 【0037】

一方、図7に例示されるような下部遮光層38と遮光帯22の両方を備える本発明の表示装置と、図4に例示されるような下部遮光層38のみを備える表示装置を、暗所にて動作させ、自発光に対する遮光性能を比較した結果、前者が後者に比べて10%大きい陰極電流を示した。

## 【0038】

上記の結果は、本発明によるところの遮光帯22が、図4に例示されるような下部遮光層38よりも、自発光に対して優れた遮光性能を持つことと、本発明によるところの遮光帯22が自発光に対してもつ効果は、従来液晶表示装置に応用されている図4に例示されるような下部遮光層38が外光に対して持つ効果の1/3に達することを示すものである。以下、本発明のアクティブマトリクス有機EL表示装置の構造及び製造方法について図面を参照して説明する。

## 【0039】

## [実施形態1]

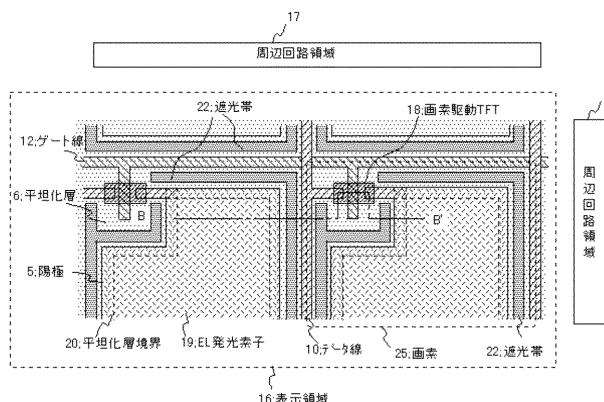

まず、本発明の第1の実施形態に係るアクティブマトリクス有機EL表示装置の構造及びその製造方法について、図6及び図7を参照して説明する。図6は本実施形態のアクティブマトリクス有機EL表示装置の平面図であり、図7はそのB-B'線に沿った断面図である。

## 【0040】

10

20

30

40

50

図6を用いて平面構造を説明する。本実施形態におけるアクティブマトリクス有機EL表示装置は、互いに直行する方向に延びたゲート線12とデータ線10とを備え、その交点の1つ1つに対応して画素駆動TFT18が形成されている。図6では画素駆動TFT18は1つのみであるが、駆動方式により複数のTFTにより構成される場合もある。画素駆動TFT18のドレイン端子はデータ線10に、ソース端子は陽極5に、ゲート端子はゲート線12に接続されている。

#### 【0041】

平坦化層6はゲート線12やデータ線10や画素駆動TFT18や陽極5といった構造物に起因する凹凸を平坦化する目的で形成されており、陽極5の内側で開口している。平坦化層6の上部にはEL有機層7と陰極8が積層されていて、平坦化層境界20の内側でEL発光素子19を形成する。そして、本発明にしたがって、EL発光素子19の周囲には、画素駆動TFT18とEL発光素子19を隔絶するように、遮光帯22が形成されている。10

#### 【0042】

そして、ゲート線12とデータ線10と画素駆動TFT18とEL発光素子19と遮光帯22とが1組となって画素25が構成され、画素25が格子状に配列されて表示領域16が構成される。また、表示領域16の周辺には、表示領域16と同一の絶縁基板上に能動層を持つTFTにより構成された周辺回路領域17が配置されている。

#### 【0043】

次に、図7を用いて本実施の形態の断面構造を説明する。ガラスなどの透明な基板1上にTFT活性層9が形成され、その上にゲート酸化膜2を介してゲート線12が形成されている。そして、ゲート線12を覆うようにして第1層間膜3が形成され、第1層間膜3の上に配線層が形成される。配線11はコンタクトホールを介して、TFT活性層9のソース／ドレイン領域に接続されている。配線11の上には第2層間膜4が形成され、その上に陽極5が形成されている。陽極5はコンタクトホールを介して、画素駆動TFT18に接続された配線11に接続されている。画素駆動TFT18の直下には、外光から画素駆動TFTを遮蔽する下部遮光層38が設けられる。20

#### 【0044】

陽極5の上部には、陽極5の段差と画素駆動TFT18の上部に生じる凹凸を緩和するために平坦化層6が形成される。平坦化層6は陽極5の上部で開口していて、その上にEL有機層7と陰極8が形成され、開口部で接合が形成され、EL発光素子19となる。30

#### 【0045】

そして、本発明に従って、画素駆動TFT18と有機EL発光素子19を隔てるよう、遮光帯22が形成されている。

#### 【0046】

次に、本実施形態のアクティブマトリクス有機EL表示装置の製造方法を説明する。まず、ガラスなどの透明な基板1上にCVD法によりシリコン層を形成した後、素子分離を行い、その後伝導型を決定する不純物注入を行う。続いてCVD法によりゲート酸化膜2を形成し、スパッタ法によりゲート電極2となる金属を堆積後、パターニングを行ってTFTを形成する。素子分離、ゲート電極のパターニングには、ドライエッチングが用いられるのが一般的である。なお、上記のTFT形成方法は非結晶Si TFTを用いる場合の例であり、多結晶Si TFTを用いる場合には、シリコン層形成後に熱アニールまたはレーザーアニールによりポリ化を行う工程が追加される。40

#### 【0047】

TFT形成後は、CVDにより第1層間膜3を成長する。続いて、所望の位置に、ドライエッチングによりコンタクトホールを形成し、スパッタにより配線11及びデータ線10となる金属膜を成長後、ドライエッチングによりパターニングを行う。さらに、配線11の上にCVD法により第2層間膜4を形成する。

#### 【0048】

遮光帯22を形成するには2通りの方法がある。1つ目の方法は、陽極5を形成後、第50

2層間膜4を縦断するように、遮光帯22が形成される領域をドライエッティングにより除去し、その後平坦化層6を塗布して充填する方法である。この方法では、遮光帯22が形成される領域をドライエッティングにより除去する工程が追加で必要となるが、前工程で陽極5が形成済みであるので、第2層間膜4が除去された領域に陽極5の部材が残留する恐れが無い。

#### 【0049】

2つ目の方法は、陽極5の形成前、前述の陽極5と配線11をつなぐコンタクトホール形成と同時に、第2層間膜4を縦断するように、遮光帯22が形成される領域をドライエッティングにより除去し、陽極5のパターニング終了後に、平坦化層6を塗布して充填する方法である。この方法では陽極5のパターニングの際、第2層間膜4が除去された領域に陽極5の部材が残留する恐れがあるが、陽極5と配線11をつなぐコンタクトホール形成と同時に第2層間膜4を除去するため、工程の増加が無くコストに優れる。

#### 【0050】

この後、平坦化層6に開口部のパターニングを行った後、アニールを行って開口部端のリフローと、画素駆動TFT18と遮光帯22が形成されている領域の平坦化を行い、EL有機層7と陰極8を形成し、アクティブマトリクス有機EL表示装置が完成する。

#### 【0051】

ここで本発明における遮光帯22の構成と動作を説明すると、第2層間膜4が除去された領域が基板1の法線方向に縦断して形成されており、その中に平坦化層6を構成する部材が充填された構造となっている。このような構造において、第2層間膜4と平坦化層6の部材の屈折率が異なっていると、界面においては光学的な反射率が大きい界面が形成され、第2層間膜4中を伝播してきた光の一部を反射し、TFTへ到達する光を減衰させる機能を持つ。この第2層間膜4と平坦化層6の材料の組み合わせは、製造方法が許す範囲で任意であって、両者の屈折率の差が大きい組み合わせほど反射率が大きくなるため、減衰効果が大きくなるので好ましい。また、第2層間膜4が除去された領域に充填される、平坦化層6の部材の光吸収係数が大きい場合には、吸収による減衰効果もあわせて得られる。

#### 【0052】

この遮光帯22は、第2層間膜4を表示装置の法線方向に縦断して、EL発光素子19を取り囲むように、かつ画素駆動TFT18とEL発光素子19を隔てるよう形成される。EL発光素子19から発せられた光のうち、第2層間膜4の中で迷光23となって画素駆動TFT18へ到達しようとする光は遮光帯22の境界面で一部が反射され、また遮光帯22を通過する際に平坦化層6の部材により一部が吸収されるため、画素駆動TFTへ到達する迷光23を削減することができ、その結果、光リーク電流は減少する。

#### 【0053】

また、遮光帯22は画素ごとに形成されているため、迷光23は周辺回路領域17に到達するまでに、少なくとも1回以上遮光帯22を通過しなくてはならず、周辺回路領域17へ到達する迷光23の量も削減することができる。

#### 【0054】

以上によって、本発明の目的である、EL発光素子19の直下に位置する層間膜中を反射しながらTFTに到達する光を削減し、TFTの光リーク電流を低減させることで、誤動作による画素表示欠陥やコントラストの低下を極小化する構造を提供できる。

#### 【0055】

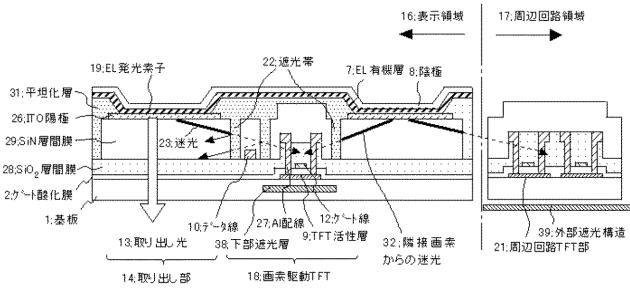

##### [実施形態2]

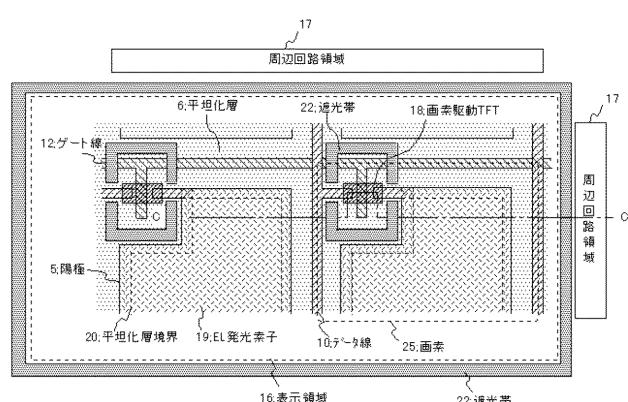

次に、本発明の第2の実施形態に係るアクティブマトリクス有機EL表示装置の構造及びその製造方法について、図8及び図9を参照して説明する。図8は本実施形態のアクティブマトリクス有機EL表示装置の平面図であり、図9は図8のC-C'線に沿った断面図である。

#### 【0056】

本発明におけるアクティブマトリクス有機EL表示装置は、互いに直行する方向に延び

たゲート線 12 とデータ線 10 とを備え、その交点の 1つ1つに対応して画素駆動 TFT 18 が形成されている。図 8 では画素駆動 TFT 18 は1つのみであるが、駆動方式により複数の TFT により構成される場合もある。画素駆動 TFT 18 のドレイン端子はデータ線 10 に、ソース端子は陽極 5 に、ゲート端子はゲート線 12 に接続されている。

#### 【0057】

平坦化層 6 はゲート線 12 やデータ線 10 や画素駆動 TFT 18 や陽極 5 といった構造物に起因する凹凸を平坦化する目的で形成されており、陽極 5 の内側で開口している。平坦化層 6 の上部には EL 有機層 7 と陰極 8 が積層されていて、平坦化層境界 20 の内側で EL 発光素子 19 を形成する。

#### 【0058】

ゲート線 12 とデータ線 10 と画素駆動 TFT 18 と EL 発光素子 19 と遮光帯 22 とが1組となって画素 25 が構成され、画素 25 が格子状に配列されて表示領域 16 が構成される。表示領域 16 の周辺には、表示領域 16 と同一の絶縁基板上に能動層を持つ TFT により構成された周辺回路領域 17 が配置されている。

#### 【0059】

そして、本実施形態では、画素駆動 TFT 18 と EL 発光素子 19 が隔絶されるように、遮光帯 22 が画素駆動 TFT 18 を立体的に取り囲んで形成され、更に、表示領域 16 の周囲には、表示領域 16 と周辺回路領域 17 を隔絶するように、遮光帯 22 が形成されている。

#### 【0060】

次に、図 9 を用いて本実施形態の断面構造を説明する。ガラスなどの透明な基板 1 上に TFT 活性層 9 が形成され、その上にゲート酸化膜 2 を介してゲート線 12 が形成されている。そして、ゲート線 12 を覆うようにして第 1 層間膜 3 が形成され、第 1 層間膜 3 の上に配線層が形成される。配線 11 はコンタクトホールを介して、TFT 活性層 9 のソース / ドレイン領域に接続されている。配線 11 の上には第 2 層間膜 4 が形成され、その上に陽極 5 が形成されている。陽極 5 はコンタクトホールを介して、画素駆動 TFT 18 に接続された配線 11 に接続されている。画素駆動 TFT 18 の直下には外光から画素駆動 TFT を遮蔽する下部遮光層 38 が設けられている。

#### 【0061】

陽極 5 の上部には、陽極 5 の段差と画素駆動 TFT 18 の上部に生じる凹凸を緩和するために平坦化層 6 が形成される。平坦化層 6 は陽極 5 の上部で開口していて、その上に EL 有機層 7 と陰極 8 が形成され、開口部で接合が形成され、EL 発光素子 19 となる。

#### 【0062】

そして、本発明に従って、画素駆動 TFT 18 を立体的に取り囲むように、かつ、画素駆動 TFT 18 と EL 発光素子 19 を隔てるように、遮光帯 22 が形成され、さらに、本発明に従って表示領域 16 の周囲には、表示領域 16 と周辺回路領域 17 を隔絶するように、遮光帯 22 が形成されている。

#### 【0063】

次に、本実施形態のアクティブマトリクス有機 EL 表示装置の製造方法を説明する。まず、ガラスなどの透明な基板 1 上に CVD 法によりシリコン層を形成した後、素子分離を行い、その後伝導型を決定する不純物注入を行う。続いて CVD 法によりゲート酸化膜 2 を形成し、スパッタ法によりゲート電極となる金属を堆積後、パターニングを行って TFT を形成する。素子分離、ゲート電極のパターニングには、ドライエッチングが用いられるのが一般的である。なお、上記の TFT 形成方法は非結晶 Si TFT を用いる場合であり、多結晶 Si TFT を用いる場合には、シリコン層形成後に熱アニールまたはレーザーアニールによりポリ化を行う工程が追加される。

#### 【0064】

TFT 形成後は、CVD により第 1 層間膜 3 を成長する。続いて、所望の位置に、ドライエッチングによりコンタクトホールを形成し、スパッタにより配線 11 とおよびデータ線 10 となる金属膜を成長後、ドライエッチングによりパターニングを行う。さらに、配

10

20

30

40

50

線 1 1 の上に C V D 法により第 2 層間膜 4 を形成する。

【 0 0 6 5 】

遮光帯 2 2 を形成するには 2 通りの方法がある。1 つ目の方法は、陽極 5 を形成後、第 2 層間膜 4 を縦断するように、遮光帯 2 2 が形成される領域をドライエッティングにより除去し、その後平坦化層 6 を塗布して充填する方法である。この方法では、遮光帯 2 2 が形成される領域をドライエッティングにより除去する工程が追加で必要となるが、前工程で陽極 5 が形成済みであるので、第 2 層間膜 4 が除去された領域に陽極 5 の部材が残留する恐れが無い。

【 0 0 6 6 】

2 つ目の方法は、陽極 5 の形成前、陽極 5 と配線 1 1 をつなぐコンタクトホール形成と同時に、第 2 層間膜を縦断するように、遮光帯 2 2 が形成される領域をドライエッティングにより除去し、陽極 5 を形成後、平坦化層 6 を塗布して充填する方法である。この方法では陽極 5 のパターニングの際、第 2 層間膜 4 が除去された領域に陽極 5 の部材が残留する恐れがあるが、陽極 5 と配線 1 1 をつなぐコンタクトホール形成と同時に第 2 層間膜 4 を除去するため、工程の増加が無くコストに優れる。

【 0 0 6 7 】

この後、平坦化層 6 に開口部のパターニングを行った後、アニールを行って開口部端のリフローと、画素駆動 TFT 1 8 と遮光帯 2 2 が形成されている領域の平坦化を行い、EL 有機層 7 と陰極 8 を形成し、アクティブマトリクス有機 EL 表示装置が完成する。

【 0 0 6 8 】

ここで本発明における遮光帯 2 2 の構成と動作を説明すると、第 2 層間膜 4 が除去された領域が基板 1 の法線方向に縦断して形成されており、その中に平坦化層 6 を構成する部材が充填された構造となっている。このような構造において、第 2 層間膜 4 と平坦化層 6 の部材の屈折率が異なっていると、界面においては光学的な反射率が大きい界面が形成され、第 2 層間膜 4 中を伝播してきた光の一部を反射し、TFT へ到達する光を減衰させる機能を持つ。第 2 層間膜 4 と平坦化層 6 の材料の組み合わせは、製造方法が許す範囲で任意であって、両者の屈折率の差が大きい組み合わせほど反射率が大きくなるため、減衰効果が大きくなるので好ましい。また、第 2 層間膜 4 が除去された領域に充填される、平坦化層 6 の部材の光吸收係数が大きい場合には、吸収による減衰効果もあわせて得られる。

【 0 0 6 9 】

この遮光帯 2 2 は第 2 層間膜 4 を表示装置の法線方向に縦断して、画素駆動 TFT 1 8 を取り囲むように、かつ画素駆動 TFT 1 8 と EL 発光素子 1 9 を隔てるように形成される。EL 発光素子 1 9 から発せられた光のうち、第 2 層間膜 4 の中で迷光 2 3 となって画素駆動 TFT 1 8 へ到達しようとする光は遮光帯 2 2 の境界面で一部が反射され、また遮光帯 2 2 を通過する際に平坦化層 6 の部材により一部が吸収されるため、画素駆動 TFT へ到達する迷光 2 3 を削減することができ、その結果、光リーケ電流は減少する。

【 0 0 7 0 】

また、表示領域 1 6 を取り囲むように、かつ表示領域 1 6 と周辺画素領域 1 7 を隔てるよう遮光帯 2 2 が形成されているため、迷光 2 3 は周辺回路領域 1 7 に到達するまでに、少なくとも 1 回以上遮光帯 2 2 を通過しなくてはならず、周辺回路領域 1 7 へ達する迷光 2 3 の量も削減することができる。

【 0 0 7 1 】

以上によって、本発明の目的である、EL 発光素子 1 9 の直下に位置する層間膜中を反射しながら TFT に到達する光を削減し、TFT の光リーケ電流を低減させることで、誤動作による画素表示欠陥やコントラストの低下を極小化する構造を提供できる。

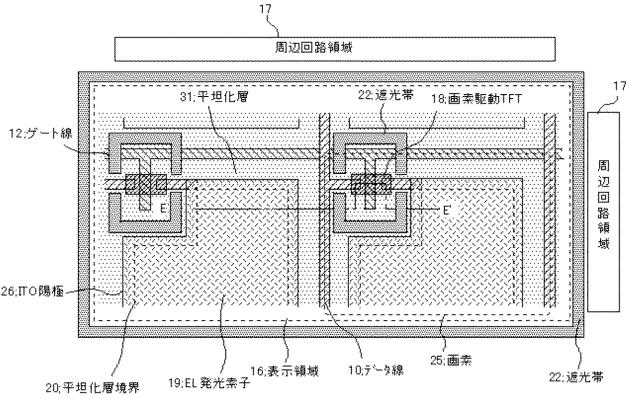

【 実施例 1 】

【 0 0 7 2 】

次に、本発明の実施の形態について、具体的な実施例を用いて動作を説明する。まず、本発明の第 1 の実施例に係るアクティブマトリクス有機 EL 表示装置について、図 1 0 及び図 1 1 を参照して説明する。図 1 0 は、第 1 の実施例のアクティブマトリクス有機 EL

10

20

30

40

50

表示装置の平面図であり、図11は図10のD-D'線に沿った断面図である。

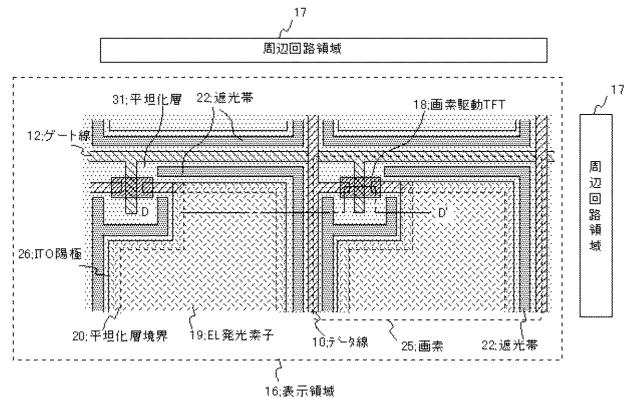

#### 【0073】

まず、本実施例のアクティブマトリクス有機EL表示装置の平面構造について図10を用いて説明する。本実施例のアクティブマトリクス有機EL表示装置は、互いに直行する方向に伸びた、WSiやCr、Alといった金属から成るゲート線12とAlからなるデータ線10とを備え、その交点の1つ1つに対応して画素25が形成されている。画素25は格子状に配列され、全体として表示領域16が構成される。さらに表示領域16の周辺には、同一基板上に、TFT能動素子により構成された周辺回路領域17が配置されている。

#### 【0074】

各々の画素25にはEL発光素子19と、それを駆動するための、多結晶Si半導体膜からなる能動層を備えた画素駆動TFT18が備えられている。なお、画素駆動TFT18には、非結晶Si薄膜半導体からなる能動層を備えたTFTを用いることもできる。画素駆動TFT18のドレイン端子はデータ線10に、ソース端子はITO陽極26に、ゲート端子はゲート線12に接続されている。図10では画素駆動TFT18は1つのみであるが、駆動方式により複数のTFTにより構成される場合もある。

#### 【0075】

ITO陽極26上部には、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和する目的で平坦化層31が形成されている。平坦化層31はITO陽極26の内側で開口していて、平坦化層境界20の内側の領域でEL発光素子19を形成する。そして、本発明にしたがって、EL発光素子19の周囲には、遮光帯22が画素駆動TFT18とEL発光素子19を隔絶するように形成されている。

#### 【0076】

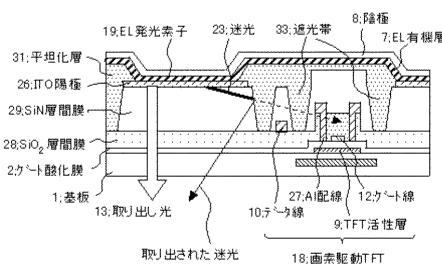

続いて、本実施例のアクティブマトリクス有機EL表示装置の構成について図11を用いて断面構造を説明する。ガラスなどの透明な基板1上に、非結晶Si半導体膜を用いたTFT活性層9が形成され、その上にゲート酸化膜2を介してゲート線12が形成されている。本実施例において、ゲート線12の材料はWSiやCrやAlといった金属が使用可能である。ゲート線12を覆うようにして、SiO<sub>2</sub>層間膜28が形成され、SiO<sub>2</sub>層間膜28の上にデータ線10とA1配線27が形成される。A1配線27はコンタクトホールを介して、TFT活性層9のソース/ドレイン領域に接続されている。

#### 【0077】

また、本実施例においては、画素駆動TFT18の直下に外光から画素駆動TFT18を遮蔽する下部遮光層38が設けられている。この下部遮光体38は、一般的にTFT応用製品の分野で外光からTFTを遮断するために用いられるもので、WSiやCrやAlといった金属が使用可能である。

#### 【0078】

データ線10およびA1配線27の上にはSiN層間膜29が形成され、その上にITO陽極26が形成されている。ITO陽極26はコンタクトホールを介して、A1配線27に接続されている。基板1から上、ITO陽極26より下の部分を、便宜上、TFT基板と呼ぶ。

#### 【0079】

TFT基板を構成する層間膜の膜厚は、膜の透過率、絶縁性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例においては、ゲート酸化膜2は100nm、SiO<sub>2</sub>層間膜28は400nm、SiN層間膜29は800nmとしたが、それぞれ30~150nm、200~1000nm、200~1200nm程度の範囲になることが望ましい。

#### 【0080】

上記TFT基板の上部には、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和する目的で、ITO陽極26をとり囲むように平坦化層31が形成されている。平坦化層31の膜厚は凹凸の緩和性能と、ITO陰極26の段差解消性能を鑑みて、製

10

20

30

40

50

造方法の許す範囲で任意に決定される。本実施例では、ITO陽極26とSiN層間膜29の界面を基準として1000nmとしたが、500~1500nm程度の範囲となる事が望ましい。

#### 【0081】

平坦化層31の上部には、EL有機層7と陰極8が形成され、平坦化層31の開口部でITO陽極26と接合を形成して、EL発光素子19を構成する。EL有機層7は第1ホール輸送層、第2のホール輸送層、発光層、電子輸送層からなり、陰極8は銀・マグネシウム合金、アルミ+アルミ・リチウム合金の2層、アルミ+フッ化リチウムの2層などにより形成されている。EL発光素子19で発生した取り出し光13は、光取り出し部14より表示装置の外部へ取り出され、図中、下側に画像が表示される。10

#### 【0082】

そして、本発明にしたがって、EL発光素子19の周囲を取り囲むようにして、遮光帯22が形成されている。

#### 【0083】

次に、本実施例によるアクティブマトリクス有機EL表示装置の製造方法を、図11を用いて説明する。まず、ガラスなどの透明な基板1上にCVD法により非結晶Si半導体薄膜を堆積し、エキシマレーザーアニールまたは熱アニールにより多結晶化を行ったあと、素子分離を行う。素子分離には、一般的にドライエッティングが用いられる。素子分離後、CVD法によりゲート酸化膜2を形成し、スパッタ法によりゲート線12となるWSiやCrやAlといった金属を堆積後、ドライエッティングによりパターニング行う。20

#### 【0084】

ゲート線12形成後は、CVD法によりSiO<sub>2</sub>層間膜28を形成し、所望の位置にコンタクトホールを形成し、データ線10と配線27となるAlをスパッタ法により堆積し、ドライエッティングによりパターニングを行う。その後、CVD法によりSiN層間膜29を形成する。20

#### 【0085】

その後、ITO陽極26とAl配線27を接続するためのコンタクトホールを所望の位置に形成すると同時に、SiN層間膜29で遮光帯22が形成される部分を除去する。この工程にはドライエッティングが用いられる。続いてスパッタ法によりITO層を形成後、ドライエッチによりITO陽極26のパターニングを行う。以下、便宜上、基板1からITO陽極26までをTFT基板と呼ぶ。30

#### 【0086】

TFT基板完成後はスピニ塗布により平坦化層31を形成する。本実施例においては、平坦化層31の部材として、一般的に半導体集積回路の製造におけるフォトリソグラフィーに使用されるフォトレジストを用いた。平坦化層31の塗布後は、フォトリソグラフィーにより開口部のパターニングを行った後、アニールを行って開口部端のリフローおよび凹凸部の平坦化を行う。最後に、蒸着法によってEL有機層7と陰極8を堆積し、EL発光素子19が形成されて、アクティブマトリクス有機EL表示装置が完成する。

#### 【0087】

ここで本実施例における遮光帯22の構成と動作を説明すると、SiN層間膜29が除去された領域が、基板1の法線方向に縦断して形成されており、その中に平坦化層31を構成するフォトレジストが充填された構造となっている。SiN層間膜29の屈折率と、フォトレジストの屈折率は異なっているため、界面において光学的な反射率が大きい界面が形成され、SiN層間膜29を伝播してきた光の一部を反射し、TFTへ到達する光を減衰させる役割を果たす。40

#### 【0088】

平坦化層31の材料としては、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和でき、かつSiN層間膜29と屈折率が異なる部材であれば、製造方法が許す範囲で任意であって、付け加えて両者の屈折率の差が大きいほうがより好ましい。たとえば、ポリイミド塗布膜や、APCVDにより成膜するTEOS系SiO<sub>2</sub>などが、段差50

および凹凸緩和能力と、SiN層間膜29との屈折率の差の面から使用可能である。

#### 【0089】

また、平坦化層31の部材の光吸收係数が大きい場合には、吸収による減衰の効果も合わせて得られる。本実施例で使用したフォトレジスト部材は一般的に着色しており、光を吸収するため、上記の界面における反射による減衰の効果と、フォトレジスト部材による光吸収による減衰の効果も得られる。

#### 【0090】

この遮光帯22は、SiN層間膜29を表示装置の法線方向に縦断して、画素駆動TFT18とEL発光素子19を隔てるよう形成される。EL発光素子19から発せられた光のうち、SiN層間膜29中で迷光23となり画素駆動TFT18へ到達しようとする光は、遮光帯22の境界面で一部が反射され、また遮光帯22を通過する際に平坦化層31の部材により一部が吸収される。これにより、画素駆動TFT18へ到達する迷光23を削減することができ、結果、光リーク電流は減少する。

#### 【0091】

また、遮光帯22は画素ごとにEL発光素子19を取り囲んで形成されているため、隣接画素からの反射光32は画素駆動TFT18に到達する間に減衰される。同様の理由から、迷光23と隣接画素からの反射光32は表示領域16の外に到達するまでに、遮光帯22を少なくとも1回以上通過しなくてはならず、周辺回路領域17へ達する迷光23の量を削減することができ、その結果、光リーク電流は減少する。

#### 【0092】

さらに副次的な効果として、基板1側から、法線と角度を持ってTFT基板に進入した外光がSiN層間膜29内に到達し、層間膜界面にて反射光が発生して、横方向に伝播した場合にも、遮光帯22によって減衰されるため、たとえば特開平9-80476号公報、特開平11-84363号公報、特開2000-164875号公報などに記載のある、外光に対する遮光構造によって遮光することができなかつた外光を減衰し、これにより発生するTFTのリーク電流を極小化する効果もある。

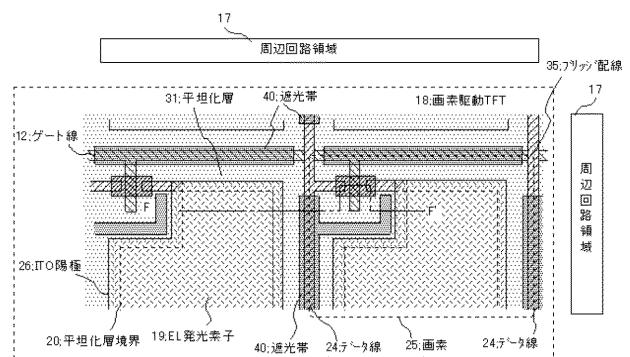

#### 【実施例2】

#### 【0093】

次に、本発明の第2の実施例に係るアクティブマトリクス有機EL表示装置について、図12及び図13を参照して説明する。図12は、第2の実施例のアクティブマトリクス有機EL表示装置の平面図であり、図13はそのE-E'線に沿った断面図である。

#### 【0094】

本実施例のアクティブマトリクス有機EL表示装置は、互いに直行する方向に延びた、WSiやCr、A1といった金属から成るゲート線12とデータ線10とを備え、その交点の1つ1つに対応して画素25が形成されている。画素25は格子状に配列され、全体として表示領域16が構成される。さらに表示領域16の周辺には、同一基板上に、TFT能動素子により構成された周辺回路領域17が配置されている。

#### 【0095】

各々の画素25にはEL発光素子19と、それを駆動するための、多結晶Si半導体膜からなる能動層を備えた画素駆動TFT18が備えられている。なお、画素駆動TFT18には、非結晶Si薄膜半導体からなる能動層を備えたTFTを用いることもできる。画素駆動TFT18のドレイン端子はデータ線10に、ソース端子はITO陽極26に、ゲート端子はゲート線12に接続されている。図12では画素駆動TFT18は1つのみであるが、駆動方式により複数のTFTにより構成される場合もある。

#### 【0096】

ITO陽極26上部には、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和する目的で平坦化層31が形成されている。平坦化層31はITO陽極26の内側で開口していて、平坦化層境界20の内側の領域でEL発光素子19を形成する。そして、本発明にしたがって、画素駆動TFT18とEL発光素子19が隔絶されるように、遮光帯22が画素駆動TFT18を立体的に取り囲んで形成されている。さらに、本発明

10

20

30

40

50

にしたがって、表示領域16の周囲には、表示領域16と周辺回路領域17を隔絶するよう、遮光帯22が形成されている。

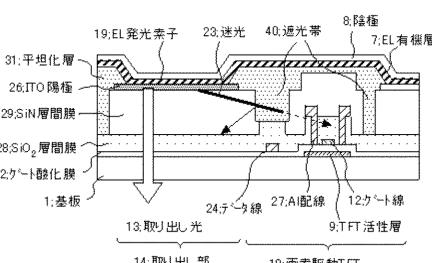

#### 【0097】

続いて、図13を用いて断面構造を説明する。ガラスなどの透明な基板1上に、非結晶Si半導体膜を用いたTFT活性層9が形成され、その上にゲート酸化膜2を介してゲート線12が形成されている。本実施例において、ゲート線12の材料はWSiやCrやAlといった金属が使用可能である。ゲート線12を覆うようにして、SiO<sub>2</sub>層間膜28が形成され、SiO<sub>2</sub>層間膜28の上にデータ線10とAl配線27が形成される。Al配線27はコンタクトホールを介して、TFT活性層9のソース／ドレイン領域に接続されている。

10

#### 【0098】

また、本実施例においては、画素駆動TFT18の直下に外光から画素駆動TFT18を遮蔽する下部遮光層38が設けられている。この下部遮光体38は、一般的にTFT応用製品の分野で外光からTFTを遮断するために用いられるもので、WSiやCrやAlといった金属が使用可能である。

#### 【0099】

データ線10およびAl配線27の上にはSiN層間膜29が形成され、その上にITO陽極26が形成されている。ITO陽極26はコンタクトホールを介して、Al配線27に接続されている。基板1から上、ITO陽極26より下の部分を、便宜上、TFT基板と呼ぶ。

20

#### 【0100】

TFT基板を構成する層間膜の膜厚は、膜の透過率、絶縁性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例においては、ゲート酸化膜2は100nm、SiO<sub>2</sub>層間膜28は400nm、SiN層間膜29は800nmとしたが、それぞれ30～150nm、200～1000nm、200～1200nm程度の範囲になることが望ましい。

#### 【0101】

上記TFT基板の上部には、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和する目的で、ITO陽極26をとり囲むように平坦化層31が形成されている。平坦化層31の膜厚は凹凸の緩和性能と、ITO陰極26の段差解消性能を鑑みて、製造方法の許す範囲で任意に決定される。1000nmとしたが、500～1500nm程度の範囲となる事が望ましい。

30

#### 【0102】

平坦化層31の上部には、EL有機層7と陰極8が形成され、平坦化層31の開口部でITO陽極26と接合を形成して、EL発光素子19を構成する。EL有機層7は第1ホール輸送層、第2のホール輸送層、発光層、電子輸送層からなり、陰極8は銀・マグネシウム合金、アルミ+アルミ・リチウム合金の2層、アルミ+フッ化リチウムの2層などにより形成されている。EL発光素子19で発生した取り出し光13は、光取り出し部14より表示装置の外部へ取り出され、図中、下側に画像が表示される。

#### 【0103】

そして、本発明にしたがって、画素駆動TFT18の周囲を取り囲むようにして、遮光帯22が形成されている。また、本発明にしたがって、表示領域16の周囲を取り囲むようにして、遮光帯22が形成されている。

40

#### 【0104】

次に、本実施例によるアクティブマトリクス有機EL表示装置の製造方法を、図13を用いて説明する。まず、ガラスなどの透明な基板1上にCVD法により非結晶Si半導体薄膜を堆積し、エキシマレーザーアニールまたは熱アニールにより多結晶化を行ったあと、素子分離を行う。素子分離には、一般的にドライエッティングが用いられる。素子分離後、CVD法によりゲート酸化膜2を形成し、スパッタ法によりゲート線12となるWSiやCrやAlといった金属を堆積後、ドライエッティングによりパターニングを行う。

50

## 【0105】

ゲート線12形成後は、CVD法によりSiO<sub>2</sub>層間膜28を形成し、所望の位置にコンタクトホールを形成し、データ線10と配線27となるA1をスパッタ法により堆積し、ドライエッチングによりパターニングを行う。その後、CVD法によりSiN層間膜29を形成する。

## 【0106】

その後、ITO陽極26とA1配線27を接続するためのコンタクトホールを所望の位置に形成すると同時に、SiN層間膜29で遮光帯22が形成される部分を除去する。この工程にはドライエッチングが用いられる。続いてスパッタ法によりITO層を形成後、ドライエッチによりITO陽極26のパターニングを行う。以上でTFT基板が完成する。

## 【0107】

TFT基板完成後はスピニ塗布により平坦化層31を形成する。本実施例においては、平坦化層31の部材として、一般的に半導体集積回路の製造におけるフォトリソグラフィーに使用されるフォトレジストを用いた。平坦化層31の塗布後は、フォトリソグラフィーにより開口部のパターニングを行った後、アニールを行って開口部端のリフローおよび凹凸部の平坦化を行う。最後に、蒸着法によってEL有機層7と陰極8を堆積し、EL発光素子19が形成されて、アクティブマトリクス有機EL表示装置が完成する。

## 【0108】

ここで本実施例における遮光帯22の構成と動作を説明すると、SiN層間膜29が除去された領域が、基板1の法線方向に縦断して形成されており、その中に平坦化層31を構成するフォトレジストが充填された構造となっている。SiN層間膜29の屈折率と、フォトレジストの屈折率は異なっているため、界面において光学的な反射率が大きい界面が形成され、SiN層間膜29を伝播してきた光の一部を反射し、TFTへ到達する光を減衰させる役割を果たす。

## 【0109】

平坦化層31の材料としては、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和でき、かつSiN層間膜29と屈折率が異なる部材であれば、製造方法が許す範囲で任意であって、付け加えて両者の屈折率の差が大きいほうがより好ましい。たとえば、ポリイミド塗布膜や、APCVDにより成膜するTEOS系SiO<sub>2</sub>などが、段差および凹凸緩和能力と、SiN層間膜29との屈折率の差の面から使用可能である。

## 【0110】

また、平坦化層31の部材の光り吸収係数が大きい場合には、吸収による減衰の効果も合わせて得られる。本実施例で使用したフォトレジスト部材は一般的に着色しており、光を吸収するため、上記の界面における反射による減衰の効果と、フォトレジスト部材による光吸収による減衰の効果も得られる。

## 【0111】

この遮光帯22は、SiN層間膜29を表示装置の法線方向に縦断して、画素駆動TFT18とEL発光素子19を隔てるよう形成される。EL発光素子19から発せられた光のうち、SiN層間膜29中で迷光23となり画素駆動TFT18へ到達しようとする光は、遮光帯22の境界面で一部が反射され、また遮光帯22を通過する際に平坦化層31の部材により一部が吸収される。これにより、画素駆動TFT18へ到達する迷光23を削減することができ、その結果、光リーク電流は減少する。

## 【0112】

また、表示領域16を取り囲むように遮光帯22が形成されているため、迷光23は表示領域16の外に到達するまでに、遮光帯22を通過しなくてはならず、周辺回路領域17へ達する迷光23の量を削減することができる。結果、光リーク電流は減少する。

## 【0113】

さらに副次的な効果として、基板1側から法線と角度を持ってTFT基板に進入した外光が、層間膜界面にて反射光となって、横方向に伝播した場合にも、遮光帯22によって

減衰されるため、たとえば特開平9-80476号公報、特開平11-84363号公報、特開2000-164875号公報などに記載のある、外光に対する遮光構造によって遮光することができなかった外光を減衰し、これにより発生するTFTのリーク電流を極小化する効果もある。

### 【実施例3】

#### 【0114】

次に、本発明の第3の実施例に係るアクティブマトリクス有機EL表示装置について、図14を参照して説明する。図14は、第3の実施例のアクティブマトリクス有機EL表示装置の断面図である。

#### 【0115】

図13に示すように、ガラスなどの透明な基板1上に、多結晶Si半導体膜を用いたTFT活性層9が形成され、その上にゲート酸化膜2を介してゲート線12が形成されている。本実施例において、ゲート線12の材料はWSiやCrやAlといった金属が使用可能である。ゲート線12を覆うようにして、SiO<sub>2</sub>層間膜28が形成され、SiO<sub>2</sub>層間膜28の上にデータ線10とA1配線27が形成される。A1配線27はコンタクトホールを介して、TFT活性層9のソース／ドレイン領域に接続されている。

#### 【0116】

また、本実施例においては、画素駆動TFT18の直下に外光から画素駆動TFTを遮蔽する下部遮光層38が設けられている。下部遮光体38は、一般的にTFT応用製品の分野で外光からTFTを遮断するために用いられるもので、WSiやCrやAlといった金属が使用可能である。

#### 【0117】

データ線10およびA1配線27の上にはSiN層間膜29が形成され、その上にITO陽極26が形成されている。ITO陽極26はコンタクトホールを介して、A1配線27に接続されている。基板1から上、ITO陽極26より下の部分を、便宜上、TFT基板と呼ぶ。

#### 【0118】

TFT基板を構成する層間膜の膜厚は、膜の透過率、絶縁性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例においては、ゲート酸化膜2は100nm、SiO<sub>2</sub>層間膜28は400nm、SiN層間膜29は800nmとしたが、それぞれ30～150nm、200～1000nm、200～1200nm程度の範囲になることが望ましい。

#### 【0119】

上記TFT基板の上部には、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和する目的で、ITO陽極26をとり囲むように平坦化層31が形成されている。平坦化層31の膜厚は凹凸の緩和性能と、ITO陰極26の段差解消性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例では、ITO陽極26とSiN層間膜29の界面を基準として1000nmとしたが、500～1500nm程度の範囲となる事が望ましい。

#### 【0120】

平坦化層31の上部には、EL有機層7と陰極8が形成され、平坦化層31の開口部でITO陽極26と接合を形成して、EL発光素子19を構成する。EL有機層7は第1ホール輸送層、第2のホール輸送層、発光層、電子輸送層からなり、陰極8は銀・マグネシウム合金、アルミ+アルミ・リチウム合金の2層、アルミ+フッ化リチウムの2層などにより形成されている。EL発光素子19で発生した取り出し光13は、光取り出し部14より表示装置の外部へ取り出され、図中、下側に画像が表示される。

#### 【0121】

そして、本発明にしたがって、EL発光素子19の周囲を取り囲むようにして、上部から下部に向かって細くなるように、遮光帯33が形成されている。

#### 【0122】

10

20

30

40

50

次に、本実施例によるアクティブマトリクス有機EL表示装置の製造方法を、図14を用いて説明する。まず、ガラスなどの透明な基板1上にCVD法により非結晶Si半導体薄膜を堆積し、エキシマレーザーアニールまたは熱アニールにより多結晶化を行ったあと、素子分離を行う。素子分離には、一般的にドライエッチングが用いられる。素子分離後、CVD法によりゲート酸化膜2を形成し、スパッタ法によりゲート線12となるWSiやCrやAlといった金属を堆積後、ドライエッチングによりパターニングを行う。

#### 【0123】

ゲート線12形成後は、CVD法により $\text{SiO}_2$ 層間膜28を形成し、所望の位置にコンタクトホールを形成し、データ線10とA1配線27となるA1をスパッタ法により堆積し、ドライエッチングによりパターニングを行う。その後、CVD法によりSiN層間膜29を形成する。

#### 【0124】

その後、ITO陽極26とA1配線27を接続するためのコンタクトホールを所望の位置に形成すると同時に、SiN層間膜29で遮光帯33が形成される部分を除去する。このとき、基板の上部から下部に向かって大きさが小さくなるようにエッチングを行う。続いてスパッタ法によりITO層を形成後、ドライエッチによりITO陽極26のパターニングを行う。以下、便宜上、基板1からITO陽極26までをTFT基板と呼ぶ。

#### 【0125】

TFT基板完成後はスピニ塗布により平坦化層31を形成する。本実施例においては、平坦化層31の部材として、フォトレジストを用いた。平坦化層31の塗布後は、フォトリソグラフィーにより開口部のパターニングを行った後、アニールを行って開口部端のリフローおよび凹凸部の平坦化を行う。最後に、蒸着法によってEL有機層7と陰極8を堆積し、EL発光素子19が形成されて、アクティブマトリクス有機EL表示装置が完成する。

#### 【0126】

ここで本実施例における遮光帯33の構成と動作を説明すると、SiN層間膜29が除去された領域が、基板1の法線方向に縦断して形成されており、その中に平坦化層31を構成するフォトレジストが充填された構造となっている。SiN層間膜29の屈折率と、フォトレジストの屈折率は異なっているため、界面において光学的な反射率が大きい界面が形成され、SiN層間膜29を伝播してきた光の一部を反射し、TFTへ到達する光を減衰させる役割を果たす。

#### 【0127】

平坦化層31の材料としては、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和でき、かつSiN層間膜29と屈折率が異なる部材であれば、製造方法が許す範囲で任意であって、付け加えて両者の屈折率の差が大きいほうがより好ましい。たとえば、ポリイミド塗布膜や、APCVDにより成膜するTEOS系 $\text{SiO}_2$ などが、段差および凹凸緩和能力と、SiN層間膜29との屈折率の差の面から使用可能である。

#### 【0128】

また、平坦化層31の部材の光吸収係数が大きい場合には、吸収による減衰の効果も合せて得られる。本実施例で使用したフォトレジスト部材は一般的に着色しており、光を吸収するため、上記の界面における反射による減衰の効果と、フォトレジスト部材による光吸収による減衰の効果も得られる。

#### 【0129】

この遮光帯33が、SiN層間膜29を表示装置の法線方向に縦断して、画素駆動TFT18と有機EL発光素子19を隔てるよう形成される。EL発光素子19から発せられた光のうち、SiN層間膜29中で迷光23となり画素駆動TFT18へ到達しようとする光は、遮光帯33の境界面で一部が反射され、また遮光帯33を通過する際に平坦化層31の部材により一部が吸収される。これにより、画素駆動TFT18へ到達する迷光23を低減することができる。

#### 【0130】

10

20

30

40

50

さらに遮光帯 33 は上部から下部に向かって細くなるように形成され、界面が光取り出し部 14 に向かって傾斜している。これにより迷光 23 の一部は光取り出し部 14 に向かって反射されて、外部に取り出すことができ、もって、表示装置の外部量子効率が向上する。

#### 【0131】

さらに副次的な効果として、基板 1 側から法線と角度を持って TFT 基板に進入した外光が、外光が SiN 層間膜 29 内に到達し、層間膜界面にて反射光が発生して、横方向に伝播した場合にも、遮光帯 33 によって減衰されるため、たとえば特開平 9-80476 号公報、特開平 11-84363 号公報、特開 2000-164875 号公報などに記載のある、外光に対する遮光構造によって遮光することができなかつた外光を減衰し、これにより発生する TFT のリーク電流を極小化する効果もある。10

#### 【実施例 4】

#### 【0132】

次に、本発明の第 4 の実施例に係るアクティブマトリクス有機 EL 表示装置について、図 15 及び図 16 を参照して説明する。図 15 は、第 4 の実施例のアクティブマトリクス有機 EL 表示装置の平面図であり、図 16 はその F-F' 線に沿った断面図である。

#### 【0133】

まず、本実施例のアクティブマトリクス有機 EL 表示装置の構成について図 15 を用いて平面構造を説明する。本実施例のアクティブマトリクス有機 EL 表示装置は、互いに直行する方向に延びた、WSi や Cr、Al といった金属から成るゲート線 12 とデータ線 24 とを備え、その交点の 1 つ 1 つに対応して画素 25 が形成されている。データ線 24 はゲート線 12 と同層に同一の部材を使用して形成されていて、データ線 24 とゲート線 12 が交差する部分のみ、Al から成るブリッジ配線 35 でブリッジされている。20

#### 【0134】

各々の画素 25 には EL 発光素子 19 と、それを駆動するための、多結晶 Si 半導体膜からなる能動層を備えた画素駆動 TFT 18 が備えられている。なお、画素駆動 TFT 18 には、非結晶 Si 薄膜半導体からなる能動層を備えた TFT を用いることもできる。画素駆動 TFT 18 のドレイン端子はデータ線 10 に、ソース端子は ITO 陽極 26 に、ゲート端子はゲート線 12 に接続されている。図 15 では画素駆動 TFT 18 は 1 つのみであるが、駆動方式により複数の TFT により構成される場合もある。30

#### 【0135】

ITO 陽極 26 上部には、ITO 陽極 26 の段差と画素駆動 TFT 18 上に発生する凹凸を緩和する目的で平坦化層 31 が形成されている。平坦化層 31 は ITO 陽極 26 の内側で開口していて、平坦化層境界 20 の内側の領域で EL 発光素子 19 を形成する。

#### 【0136】

画素 25 は格子状に配列され、全体として表示領域 16 が構成される。表示領域 16 の周辺には TFT 能動素子により構成された周辺回路領域 17 が配置された構造となっている。そして、本発明にしたがって、EL 発光素子 19 の周囲に、画素駆動 TFT 18 と EL 発光素子 19 を隔絶するように、かつゲート線 12 とデータ線 24 にオーバーラップするように、遮光帯 40 が形成されている。40

#### 【0137】

続いて、本実施例のアクティブマトリクス有機 EL 表示装置の構成について図 16 を用いて断面構造を説明する。ガラスなどの透明な基板 1 上に、多結晶 Si 半導体膜を用いた TFT 活性層 9 が形成され、その上にゲート酸化膜 2 を介してデータ線 24 とゲート線 12 が形成されている。本実施例において、データ線 24 とゲート線 12 の材料は WSi や Cr や Al といった金属が使用可能である。データ線 24 は、紙面の手前方向から奥の方向に伸びており、ゲート線 12 と交差する部分でいったん切断されて、ブリッジ配線 35 によってジャンパー接続されている。

#### 【0138】

データ線 24 とゲート線 12 の上には、SiO<sub>2</sub> 層間膜 28 が形成され、SiO<sub>2</sub> 層間

10

20

30

40

50

膜 2 8 の上に A 1 配線 2 7 が形成される。A 1 配線 2 7 はコンタクトホールを介して、TFT 活性層 9 のソース / ドレイン領域に接続されている。

#### 【 0 1 3 9 】

データ線 1 0 および A 1 配線 2 7 の上には SiN 層間膜 2 9 が形成され、その上に ITO 陽極 2 6 が形成されている。ITO 陽極 2 6 はコンタクトホールを介して、A 1 配線 2 7 に接続されている。基板 1 から上、ITO 陽極 2 6 より下の部分を、便宜上、TFT 基板と呼ぶ。

#### 【 0 1 4 0 】

TFT 基板を構成する層間膜の膜厚は、膜の透過率、絶縁性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例においては、ゲート酸化膜 2 は 30 nm ~ 150 nm、SiO<sub>2</sub> 層間膜 2 8 は 200 nm ~ 1000 nm、SiN 層間膜 2 9 は 200 nm ~ 1200 nm である。10

#### 【 0 1 4 1 】

上記 TFT 基板の上部には、ITO 陽極 2 6 の段差と画素駆動 TFT 1 8 上に発生する凹凸を緩和する目的で、ITO 陽極 2 6 を囲むように平坦化層 3 1 が形成されている。平坦化層 3 1 の膜厚は凹凸の緩和性能と、ITO 陰極 2 6 の段差解消性能を鑑みて、製造方法の許す範囲で任意に決定される。本実施例では、ITO 陽極 2 6 と SiN 層間膜 2 9 の界面を基準として 500 ~ 1500 nm とした。

#### 【 0 1 4 2 】

平坦化層 3 1 の上部には、EL 有機層 7 と陰極 8 が形成され、平坦化層 3 1 の開口部で ITO 陽極 2 6 と接合を形成して、EL 発光素子 1 9 を構成する。EL 有機層 7 は第 1 ホール輸送層、第 2 のホール輸送層、発光層、電子輸送層からなり、陰極 8 は銀・マグネシウム合金、アルミ + アルミ・リチウム合金の 2 層、アルミ + フッ化リチウムの 2 層などにより形成されている。EL 発光素子 1 9 で発生した取り出し光 1 3 は、取り出し部 1 4 より表示装置の外部へ取り出され、図中、下側に画像が表示される。20

#### 【 0 1 4 3 】

そして、本発明にしたがって、EL 発光素子 1 9 の周囲を取り囲むように、かつゲート線 1 2 とデータ線 2 4 にオーバーラップするように、遮光帯 4 0 が形成されている。

#### 【 0 1 4 4 】

次に、本実施例によるアクティブマトリクス有機 EL 表示装置の製造方法を、図 1 6 を用いて説明する。まず、ガラスなどの透明な基板 1 上に CVD 法により非結晶 Si 半導体薄膜を堆積し、エキシマレーザーアニールまたは熱アニールにより多結晶化を行ったあと、素子分離を行う。素子分離には、一般的にドライエッチングが用いられる。素子分離後、CVD 法によりゲート酸化膜 2 を形成し、スパッタ法によりゲート線 1 2 となる WSi<sub>x</sub> や Cr や Al といった金属を堆積後、ドライエッチングによりパターニングを行う。30

#### 【 0 1 4 5 】

ゲート線 1 2 とデータ線 2 4 形成後は、CVD 法により SiO<sub>2</sub> 層間膜 2 8 を形成し、所望の位置にコンタクトホールを形成し、A 1 配線 2 7 とプリッジ配線 3 5 となる A 1 をスパッタ法により堆積し、ドライエッチングによりパターニングを行う。その後、CVD 法により SiN 層間膜 2 9 を形成する。40

#### 【 0 1 4 6 】

その後、ITO 陽極 2 6 と A 1 配線 2 7 を接続するためのコンタクトホールを所望の位置に形成すると同時に、SiN 層間膜 2 9 で遮光帯 4 0 が形成される部分を除去する。このとき、遮光帯 4 0 が形成される部分がデータ線 2 4 と重なるように形成する。この工程にはドライエッチングが用いられる。続いてスパッタ法により ITO 層を形成後、ドライエッチにより ITO 陽極 2 6 のパターニングを行う。便宜上、基板 1 から ITO 陽極 2 6 までを TFT 基板と呼ぶ。

#### 【 0 1 4 7 】

TFT 基板完成後はスピン塗布により平坦化層 3 1 を形成する。本実施例においては、平坦化層 3 1 の部材として、一般的に半導体集積回路の製造におけるフォトリソグラフィ50

ーに使用されるフォトレジストを用いた。平坦化層31の塗布後は、フォトリソグラフィーにより開口部のパターニングを行った後、アニールを行って開口部端のリフローおよび凹凸部の平坦化を行う。最期に、蒸着法によってEL有機層7と陰極8を堆積し、EL発光素子19が形成されて、アクティブマトリクス有機EL表示装置が完成する。

#### 【0148】

ここで本実施例における遮光帯40の構成と動作を説明すると、SiN層間膜29が除去された領域が、基板1の法線方向に縦断して形成されており、その中に平坦化層31を構成するフォトレジストが充填された構造となっている。SiN層間膜29の屈折率と、フォトレジストの屈折率は異なっているため、界面において光学的な反射率が大きい界面が形成され、SiN層間膜29を伝播してきた光の一部を反射し、TFTへ到達する光を減衰させる役割を果たす。

#### 【0149】

平坦化層31の材料としては、ITO陽極26の段差と画素駆動TFT18上に発生する凹凸を緩和でき、かつSiN層間膜29と屈折率が異なる部材であれば、製造方法が許す範囲で任意であって、付け加えて両者の屈折率の差が大きいほうがより好ましい。たとえば、ポリイミド塗布膜や、APCVDにより性膜するTEOS系SiO<sub>2</sub>などが、段差および凹凸緩和能力と、SiN層間膜29との屈折率の差の面から使用可能である。

#### 【0150】

また、平坦化層31の部材の光吸収係数が大きい場合には、吸収による減衰の効果も合わせて得られる。本実施例で使用したフォトレジスト部材は一般的に着色しており、光を吸収するため、上記の界面における反射による減衰の効果と、フォトレジスト部材による光吸収による減衰の効果も得られる。

#### 【0151】

この遮光帯40はSiN層間膜29を表示装置の法線方向に縦断して、画素駆動TFT18とEL発光素子19を隔てるよう形成される。EL発光素子19から発せられた光のうち、SiN層間膜29中で迷光23となり画素駆動TFT18へ到達しようとする光は、遮光帯40の境界面で一部が反射され、また遮光帯40を通過する際に平坦化層31の部材により一部が吸収される。これにより、画素駆動TFT18へ到達する迷光23を削減することができ、その結果、光リーク電流は減少する。

#### 【0152】

また、遮光帯40は画素ごとにEL発光素子19を取り囲んで形成されているため、隣接画素からの反射光32は画素駆動TFT18に到達する間に減衰される。同様の理由から、迷光23と隣接画素からの反射光32は表示領域16の外に到達するまでに、遮光帯40を少なくとも1回以上通過しなくてはならず、周辺回路領域17へ達する迷光23の量を削減することができ、その結果、光リーク電流は減少する。

#### 【0153】

第1の実施例においては、遮光帯22はデータ10を避けるように形成されており、画素25に占めるEL発光素子19の面積である開口率を低下させる要因となっていた。これは遮光帯22を形成するためには、SiN層間膜29を除去する必要があるが、実施例1の構成においてデータ線10にオーバーラップするように遮光帯22を形成すると、データ線を覆うSiN層間膜29がなくなってしまい、信頼性が低下してしまう恐れがあったためであった。

#### 【0154】

これに対して本実施例においては、データ線24はゲート線12と同層に形成されており、SiO<sub>2</sub>層間膜28によって保護されているため、データ線24にオーバーラップするように遮光帯40を形成しても上記の信頼性問題は発生しない。このような構成を探ることにより、遮光帯40を形成するために占有する面積を最小とすることが可能で、これによって、遮光帯40を備えることによる画素25の開口率低下を最小限に抑えることが可能となる。

#### 【0155】

10

20

30

40

50

また、副次的な効果として、データ線 24 をゲート線 12 と同層に形成したことにより、データ線 24 と陰極 8 の距離が増大すること、および、遮光帯 40 の形成の際に SiN 層間膜 29 が、より誘電率の低いフォトレジストに置き換えられることによって、データ線 24 と陰極 8 の間に挟まつた部材の誘電率が低下するため、データ線 24 と陰極 8 の間に発生する寄生容量が低減される効果がある。

#### 【0156】

さらに副次的な効果として、光取り出し部 14 より、基板の法線と角度を持って TFT 基板に進入した外光が SiN 層間膜 29 内に到達し、層間膜界面にて反射光が発生して、横方向に伝播した場合にも、遮光帯 40 によって減衰される、たとえば特開平 9-80476 号公報、特開平 11-84363 号公報、特開 2000-164875 号公報などに記載のある、外光に対する遮光構造によって遮光することができなかった外光を減衰する効果もある。10

#### 【図面の簡単な説明】

#### 【0157】

【図 1】一般的なアクティブマトリクス有機 EL 表示装置の構成図である。

【図 2】従来のアクティブマトリクス有機 EL 表示装置の構造を示す平面図である。

【図 3】従来のアクティブマトリクス有機 EL 表示装置の構造を示す断面図である。

【図 4】従来のアクティブマトリクス有機 EL 表示装置における遮光構造を示す断面図である。20

【図 5】従来のアクティブマトリクス有機 EL 表示装置における自発光の伝播モードを説明する図である。

【図 6】本発明の第 1 の実施形態に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す平面図である。20

【図 7】本発明の第 1 の実施形態に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。

【図 8】本発明の第 2 の実施形態に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す平面図である。

【図 9】本発明の第 2 の実施形態に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。30

【図 10】本発明の第 1 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す平面図である。

【図 11】本発明の第 1 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。

【図 12】本発明の第 2 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す平面図である。

【図 13】本発明の第 2 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。

【図 14】本発明の第 3 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。

【図 15】本発明の第 4 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す平面図である。40

【図 16】本発明の第 4 の実施例に係るアクティブマトリクス有機 EL 表示装置の 1 部分を示す断面図である。

#### 【符号の説明】

#### 【0158】

1 基板

2 ゲート酸化膜

3 第 1 層間膜

4 第 2 層間膜

5 陽極

|     |                      |    |

|-----|----------------------|----|

| 6   | 平坦化層                 |    |

| 7   | E L 有機層              |    |

| 8   | 陰極                   |    |

| 9   | T F T 活性層            |    |

| 1 0 | データ線                 |    |

| 1 1 | 配線                   |    |

| 1 2 | ゲート線                 |    |

| 1 3 | 取り出し光                |    |

| 1 4 | 取り出し部                |    |

| 1 6 | 表示領域                 | 10 |

| 1 7 | 周辺回路領域               |    |

| 1 8 | 画素駆動TFT              |    |

| 1 9 | E L 発光素子             |    |

| 2 0 | 平坦化層境界               |    |

| 2 1 | 周辺回路TFT部             |    |

| 2 2 | 遮光帯                  |    |

| 2 3 | 迷光                   |    |

| 2 4 | ゲート線と同層に形成したデータ線     |    |

| 2 5 | 画素                   |    |

| 2 6 | I TO 陽極              | 20 |

| 2 7 | A1配線                 |    |

| 2 8 | SiO <sub>2</sub> 層間膜 |    |

| 2 9 | SiN層間膜               |    |

| 3 1 | 平坦化層                 |    |

| 3 2 | 隣接画素からの反射光           |    |

| 3 3 | 遮光帯                  |    |

| 3 4 | 外部駆動回路               |    |

| 3 5 | ブリッジ配線               |    |

| 3 6 | フレキシブル基板             |    |

| 3 8 | 下部遮光層                | 30 |

| 3 9 | 外部遮光構造               |    |

| 4 0 | 遮光帯                  |    |

| 4 1 | 外光                   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【 四 9 】

【 図 10 】

【 図 1 3 】

【 図 1 4 】

【 図 1 1 】

【 図 1 2 】

【 図 15 】

( 16 )

( 16 )

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01 L 29/78 619 B

F ターム(参考) 5F110 AA06 BB02 DD02 EE03 EE04 EE05 EE44 FF02 FF29 GG02

GG13 GG15 GG44 GG52 HL03 HL23 NN03 NN04 NN23 NN24

NN35 NN45 NN46 NN47 NN49 NN71 PP01 PP03 QQ08 QQ19

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 发光显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号     | <a href="#">JP2005181422A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2005-07-07 |

| 申请号         | JP2003418320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-12-16 |

| 申请(专利权)人(译) | NEC公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人      | 伊賀大輔                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人         | 伊賀 大輔                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号      | H05B33/10 G09F9/30 H01J1/62 H01L27/32 H01L29/786 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号      | H01L27/3272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号       | G09F9/30.365.Z G09F9/30.338 G09F9/30.349.C H05B33/10 H05B33/14.A H01L29/78.619.B G09F9/30.365 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号   | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/FA00 5C094/AA03 5C094/AA06 5C094/AA25 5C094 /AA42 5C094/BA03 5C094/BA27 5C094/ED15 5C094/FB01 5C094/FB20 5F110/AA06 5F110/BB02 5F110/DD02 5F110/EE03 5F110/EE04 5F110/EE05 5F110/EE44 5F110/FF02 5F110/FF29 5F110 /GG02 5F110/GG13 5F110/GG15 5F110/GG44 5F110/GG52 5F110/HL03 5F110/HL23 5F110/NN03 5F110/NN04 5F110/NN23 5F110/NN24 5F110/NN35 5F110/NN45 5F110/NN46 5F110/NN47 5F110 /NN49 5F110/NN71 5F110/PP01 5F110/PP03 5F110/QQ08 5F110/QQ19 3K107/AA01 3K107/BB01 3K107/CC32 3K107/CC33 3K107/DD90 3K107/EE03 3K107/EE27 3K107/GG00 |         |            |

| 代理人(译)      | 宮本敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献      | <a href="#">JP4736013B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

解决的问题：提供一种有源矩阵有机EL显示装置，其具有防止由EL发光元件发出的光引起的TFT的漏光的结构。像素驱动TFT 18包括在绝缘基板1上的由栅极线12和数据线10围绕的像素25中的一个或多个晶体管，多个层间膜，阳极5和EL有机层7。在有源矩阵有机EL显示装置中，其中依次形成包括阴极8的EL发光元件19，并且从基板的法线方向观看时，像素驱动TFT 18和EL发光元件19布置为不重叠。像素驱动TFT 18的外围或外围的至少一部分或显示区域16的外围的至少一部分设置有遮光带22，该遮光带22纵向切穿位于EL发光元件19下方的第二层间膜4，并且通过遮光带22在层间膜中传播。杂散光会被反射或衰减，以防止由于TFT故障而导致像素显示缺陷和对比度降低。[选择图]图6