(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-170815

(P2004-170815A)

(43) 公開日 平成16年6月17日(2004.6.17)

(51) Int.Cl.<sup>7</sup>

**G09G** 3/30

**G09F** 9/30

**G09G** 3/20

**H05B** 33/14

F 1

GO9G 3/30 J 3K007

GO9F 9/30 338 5C080

GO9F 9/30 365Z 5C094

GO9G 3/20 611J

GO9G 3/20 622C

テーマコード(参考)

審査請求 未請求 請求項の数 15 O L (全 33 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2002-338525 (P2002-338525)

平成14年11月21日 (2002.11.21)

(71) 出願人 599142729

奇美電子股▲ふん▼有限公司

台湾台南県台南科学工業園区新市郷奇業路

1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 小林 芳直

神奈川県大和市下鶴間1623番地14

インターナショナル ディスプレイ テク

ノロジー株式会社内

(72) 発明者 小野 晋也

神奈川県大和市下鶴間1623番地14

インターナショナル ディスプレイ テク

ノロジー株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA04

最終頁に続く

(54) 【発明の名称】 E L表示装置およびその駆動方法

## (57) 【要約】

【課題】電圧書き込み型の大画面のアクティブマトリクスパネルに対しても、各表示セルのキャパシタに所望の電圧を正確に書き込むことができるE L表示装置およびその駆動方法を提供する。

【解決手段】共通線を排除し、従来においてその共通線に接続されていたキャパシタの一端を、そのキャパシタを備えた表示セルに隣接した他の表示セルの走査線に接続するとともに、走査線駆動回路20は、電圧V1とその電圧V1よりも十分に大きな電圧V2とで形成された階段形状のパルスを各走査線に供給する。また、データ線駆動回路30は、電圧V1以上でかつ電圧V3以下(但し、電圧V2より小さい)の電圧をデータ電圧として各データ線に供給する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子とを有して構成されたEL表示装置において、

前記走査線に、第1電圧と該第1電圧よりも値の大きい第2電圧とで形成される階段形状パルスを供給する走査線駆動回路を備え、

前記走査線で選択される表示セル内の前記駆動トランジスタのソースもしくはドレインと前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続されたことを特徴とするEL表示装置。

**【請求項 2】**

前記走査線駆動回路は、前記第1電圧と前記第2電圧を連続した所定の単位期間にそれぞれ割り当てることで前記階段形状パルスを生成するとともに、前記階段形状パルスを、前記複数の走査線に順次、前記単位期間だけずらして供給することを特徴とする請求項1に記載のEL表示装置。

**【請求項 3】**

前記走査線駆動回路は、前記階段形状パルスを前記走査線に供給すると同時に、前記階段形状パルスのパルス幅を有する第3電圧で形成された矩形パルスを、前記階段形状パルスが供給されている走査線とは異なる他の走査線に供給することを特徴とする請求項1に記載のEL表示装置。

**【請求項 4】**

前記走査線駆動回路は、前記階段形状パルスを前記走査線に供給すると同時に、前記階段形状パルスのパルス幅を有する第3電圧で形成された矩形パルスを、前記階段形状パルスが供給されている走査線とは異なる他の走査線に順次、前記単位期間だけずらして供給することを特徴とする請求項2に記載のEL表示装置。

**【請求項 5】**

前記第3電圧は、前記第2電圧の値と等しいことを特徴とする請求項3または4に記載のEL表示装置。

**【請求項 6】**

前記データ線に、前記第1電圧以上かつ前記第2電圧未満の値を有するデータ電圧を供給するデータ線駆動回路を備えたことを特徴とする請求項1～5のいずれか一つに記載のEL表示装置。

**【請求項 7】**

複数の選択走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記選択走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子とを有して構成されたEL表示装置において、前記選択走査線と対となって配置されるとともに、前記選択走査線で選択される表示セル内の前記駆動トランジスタのソースもしくはドレインおよび前記キャパシタの他端、または、前記選択走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が接続された複数の書き込み走査線と、

前記選択走査線に対して走査線選択電圧を供給するとともに、該選択走査線と対となる前記書き込み走査線に対して書き込み基準電圧を供給する走査線駆動回路とを備え、

前記走査線駆動回路は、前記有機エレクトロルミネッセンス素子を発光させずに前記デー

10

20

30

40

50

タ電圧が前記キャパシタに書き込まれる第1フェーズと、前記有機エレクトロルミネッセンス素子を発光させずに前記キャパシタの蓄積電圧を保持する第2フェーズと、前記キャパシタの蓄積電圧に基づいて有機エレクトロルミネッセンス素子の発光を次の前記第1フェーズまで持続させる第3フェーズと、が順次繰り返されるような電圧値とタイミングで、前記走査線選択電圧と前記書き込み基準電圧を供給することを特徴とするE L表示装置。

【請求項8】

前記走査線駆動回路は、前記第1フェーズ～第3フェーズに並行して、該第1フェーズ～第3フェーズが適用されている選択走査線および書き込み走査線とは異なる選択走査線および書き込み走査線に対して、前記キャパシタに負の電圧が供給されるような電圧値とタイミングで、前記走査線選択電圧と前記書き込み基準電圧を供給することを特徴とする請求項7に記載のE L表示装置。

【請求項9】

複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(E L)素子とを有して構成されたE L表示装置において、

前記走査線で選択される表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続された共通線と、前記共通線に対する表示セルの走査線方向の位置と、前記共通線の前記表示セル間の配線抵抗の抵抗値とに基づいて、該位置における表示セル内の前記エレクトロルミネッセンス素子の電圧降下分を算出し、算出した結果に基づいて補正したデータ電圧を前記データ線に供給するデータ線駆動回路と、

を備えたことを特徴とするE L表示装置。

【請求項10】

前記エレクトロルミネッセンス素子は、有機E L素子であることを特徴とする請求項1～9のいずれか一つに記載のE L表示装置。

【請求項11】

複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(E L)素子とを有して構成され、前記走査線で選択される表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続されたE L表示装置の駆動方法において、

前記走査線に第1電圧を所定の単位期間だけ供給する第1走査ステップと、

前記第1走査ステップに引き続き、前記走査線に前記第1電圧よりも値の大きい第2電圧を前記単位期間だけ供給する第2走査ステップと、

前記第2走査ステップに引き続き、前記走査線に前記選択トランジスタの閾値電圧以下の電圧を少なくとも前記単位期間の間供給する第3走査ステップと、

を含んだことを特徴とするE L表示装置の駆動方法。

【請求項12】

前記第1走査ステップは、さらに、前記第1電圧を供給している走査線とは異なる走査線に対して、前記単位時間だけ第3電圧を供給し、

前記第2走査ステップは、さらに、前記第1走査ステップにおいて前記第3電圧が供給された走査線に対して、前記単位時間だけさらに前記第3電圧を供給し、

10

20

30

40

50

前記第3走査ステップは、さらに、前記第2走査ステップにおいて前記第3電圧が供給された走査線に対して、前記選択トランジスタの閾値電圧以下の電圧を少なくとも前記単位期間の間供給することを特徴とする請求項11に記載のEL表示装置の駆動方法。

【請求項13】

複数の選択走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記選択走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子と、前記選択走査線と対となって配置されるとともに、前記選択走査線で選択される表示セル内の前記駆動トランジスタのソースもしくはドレインおよび前記キャパシタの他端、または、前記選択走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が接続された複数の書き込み走査線とを有して構成されたEL表示装置の駆動方法において、

前記有機エレクトロルミネッセンス素子を発光させずに前記データ電圧が前記キャパシタに書き込まれるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第1走査ステップと、

前記有機エレクトロルミネッセンス素子を発光させずに前記キャパシタの蓄積電圧が保持されるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第2走査ステップと、

前記キャパシタの蓄積電圧に基づいて有機エレクトロルミネッセンス素子の発光を次の前記第1走査ステップまで持続させるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第3走査ステップと、

を含んだことを特徴とするEL表示装置の駆動方法。

【請求項14】

前記第1走査ステップ～第3走査ステップに並行して、該前記第1走査ステップ～第3走査ステップが適用されている選択走査線および書き込み走査線とは異なる選択走査線および書き込み走査線に対し、前記キャパシタに負の電圧が供給されるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する消去ステップを含んだことを特徴とする請求項13に記載のEL表示装置の駆動方法。

【請求項15】

複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子とを有して構成され、かつ、前記走査線ごとに設けられた共通線に、同一の走査線を共有する各表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、同一の走査線を共有する各表示セル内の前記エレクトロルミネッセンス素子の他端が接続されたEL表示装置の駆動方法において、

前記共通線に対する表示セルの走査線方向の位置と、前記共通線の前記表示セル間の配線抵抗の抵抗値とに基づいて、該位置における表示セル内の前記エレクトロルミネッセンス素子の電圧降下分を算出する電圧降下算出ステップと、

前記電圧降下算出ステップによって算出された結果に基づいてデータ電圧を補正し、補正したデータ電圧を前記データ線に供給するデータ電圧供給ステップと、

を含んだことを特徴とするEL表示装置の駆動方法。

【発明の詳細な説明】

10

20

30

40

50

## 【0001】

## 【発明の属する技術分野】

本発明は、有機EL(electroluminescence:エレクトロルミネッセンス)素子等の自発光素子とその自発光素子を駆動させるTFT(Thin Film Transistor:薄膜トランジスタ)とがマトリクス状に配置されたEL表示装置およびその駆動方法に関し、特に大画面表示においても輝度ムラの生じない電圧書き込み型のEL表示装置およびその駆動方法に関する。

## 【0002】

## 【従来の技術】

有機EL素子を用いた有機EL表示装置は、液晶素子を用いた液晶表示装置に比べて、視野角が広いこと、コントラストがよいこと、視認性に優れていることなどを理由に近年注目されている。また、有機EL表示装置では、バックライトが不要なため、薄型・軽量型が実現でき、消費電力の面でも有利である。さらに、有機EL表示装置は、直流低電圧駆動が可能であることから応答速度も速いこと、すべて固体であることから振動に強く、使用温度範囲が広くかつフレキシブルな形状が可能であることなどの特徴を有している。

## 【0003】

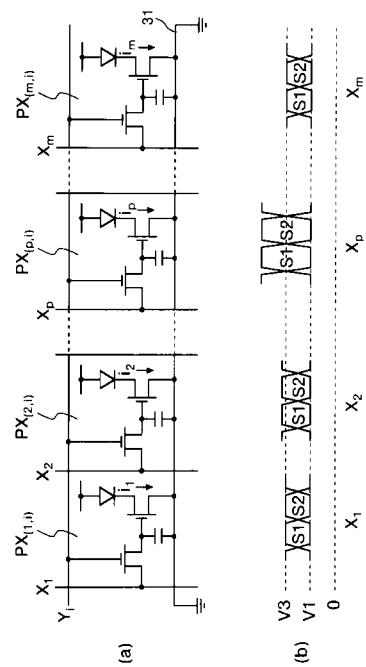

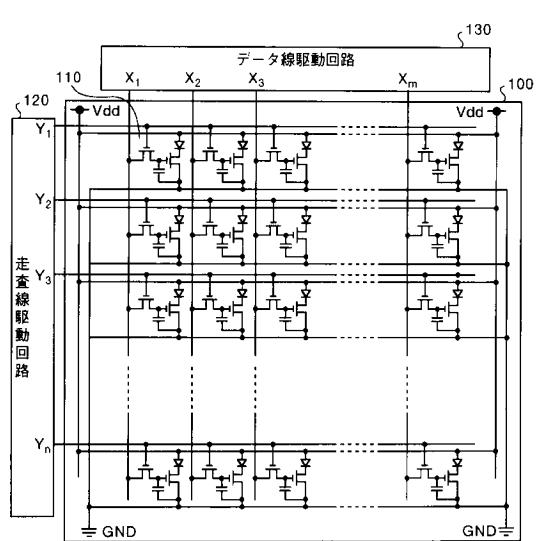

以下に、従来の有機EL表示装置について、特にアクティブマトリクスパネルを中心に説明する。図13は、従来の有機EL表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。図13において、アクティブマトリクスパネル100は、n本の走査線Y<sub>1</sub>～Y<sub>n</sub>とm本のデータ線X<sub>1</sub>～X<sub>m</sub>の各交差点に表示セル110を配置しており、その基本構造はアクティブマトリクス型の液晶表示装置と同様である。

## 【0004】

よって、アクティブマトリクスパネル100は、液晶表示装置と同様に、n本の走査線Y<sub>1</sub>～Y<sub>n</sub>に対して所定のタイミングで走査線選択電圧を供給する走査線駆動回路120と、m本のデータ線X<sub>1</sub>～X<sub>m</sub>に対して所定のタイミングでデータ電圧を供給するデータ線駆動回路130とを備えている。なお、図13では、有機EL表示装置を駆動させるためのその他の種々の回路については省略している。

## 【0005】

アクティブマトリクスパネル100において、液晶表示装置と異なる点は、各表示セル110が、液晶素子に換えて有機EL素子を備えていることである。この表示セル110の構成として、選択TFT、駆動TFT、キャパシタ、有機EL素子をそれぞれ一つずつ備えた、いわゆる電圧書き込み型の表示セルが最もよく知られている(例えば、特許文献1参照)。

## 【0006】

電圧書き込み型の表示セルの等価回路の一例を挙げると、図13に示すように、選択TFTは、ゲートを走査線に接続するとともにドレインをデータ線に接続し、駆動TFTは、ゲートを選択TFTのソースに接続するとともにソースを共通線(多くの場合、接地線GND)に接続している。また、上記したキャパシタは、駆動TFTのソース-ゲート間に接続され、有機EL素子は、アノード側を電源電圧線(図中ではV<sub>dd</sub>)に接続するとともにカソード側を駆動TFTのドレインに接続している。

## 【0007】

ここで、この電圧書き込み型の表示セルの動作を簡単に説明する。まず、選択TFTのゲートに走査線駆動回路120から走査線選択電圧が供給されると、選択TFTはオン状態となり、データ線駆動回路130から供給されたデータ電圧が駆動TFTのゲートとキャパシタに印加される。これにより、駆動TFTはオン状態となり、有機EL素子のカソード側から共通線への電流路が形成される。すなわち、有機EL素子は、データ電圧に応じて決定される電流によって発光する。一方、キャパシタには、データ電圧が蓄積される。

## 【0008】

蓄積されたデータ電圧は、駆動TFTとキャパシタとの上記接続関係から、駆動TFTのゲートに供給されるので、選択TFTのゲートに走査線選択電圧が供給されなくなっても

10

20

30

40

50

、すなわち走査線駆動回路 120 が次の走査線の選択に移行した後であっても、有機 E L 素子は、次に走査線駆動回路 120 によって走査線が選択されるまで発光を持続する。換言すれば、キャパシタに書き込まれたデータ電圧によって有機 E L 素子は発光し続ける。これが、電圧書き込み型と呼ばれる所以である。

#### 【0009】

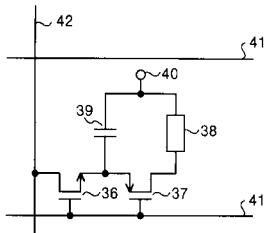

一方、共通線を必要としない表示セルの構成も提案されている（特許文献 2 参照）。図 14 は、特許文献 2 に開示された一実施例を説明するための表示セルの等価回路を示す図である。図 14 に示す等価回路は、n チャネル型 TFT 36、p チャネル型 TFT 37、有機薄膜 E L 素子 38 および容量 39（上記したキャパシタに相当）を備えて構成される。

#### 【0010】

図 14において、走査線 41 は n チャネル型 TFT 36 と p チャネル型 TFT 37 のゲート電極に接続され、信号線 42（上記したデータ線に相当）は n チャネル型 TFT 36 の一方の電極に接続されている。また、n チャネル型 TFT 36 の他方の電極は容量 39 の一方の端子と p チャネル型 TFT 37 の一方の電極との接続点に接続され、p チャネル型 TFT 37 の他方の電極は有機薄膜 E L 素子 38 の一方の電極に接続されている。そして、容量 39 の他方の端子と有機薄膜 E L 素子 38 の他方の電極とは電源電極 40 に接続されている。

#### 【0011】

この構成によれば、走査線 41 が選択されると、n チャネル型 TFT 36 がオン状態となり、信号線 42 から n チャネル型 TFT 36 を介して容量 39 に電圧が印加される。このとき p チャネル型 TFT 37 はオフ状態となり、有機薄膜 E L 素子 38 は発光しない。次に、走査線 41 が非選択状態になると、n チャネル型 TFT 36 がオフ状態となるため、信号線 42 の電圧は容量 39 に印加されなくなる。その一方で、p チャネル型 TFT 37 はオン状態となり、容量 39 に蓄えられた電荷が p チャネル型 TFT 37 を介して有機薄膜 E L 素子 38 に流れ込み、これにより有機薄膜 E L 素子 38 が発光する。

#### 【0012】

また、上述した特許文献 1 および 2 は、電圧書き込み型の有機 E L 表示装置に関するものであったが、後述する輝度ムラを解消することができる電流書き込み型の有機 E L 表示装置も提案されている（例えば、特許文献 3 参照）。

#### 【0013】

##### 【特許文献 1】

特開平 8 - 234683 号公報（第 5 頁左段、第 1 図）

##### 【特許文献 2】

特許第 2689917 号公報（第 7 頁左段～第 8 頁右段、第 11 図）

##### 【特許文献 3】

特開 2001 - 147659 号公報（第 7 頁左段～第 8 頁左段、第 1 図）

#### 【0014】

##### 【発明が解決しようとする課題】

しかしながら、電圧書き込み型の表示セルを採用した有機 E L 表示装置は、大画面化を実現する上で輝度ムラが発生してしまうという問題を有している。輝度ムラの問題については本来、大画面でなくても、表示セル間において駆動 TFT の特性（例えば、閾値電圧  $V_{th}$ ）が異なることを起因としていることが知られている。但し、この駆動 TFT のバラツキに起因する問題については種々の解決法が提案されているので、ここでは問題としない。

#### 【0015】

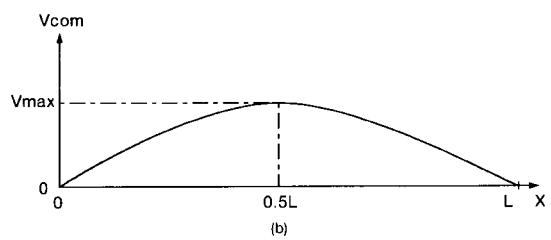

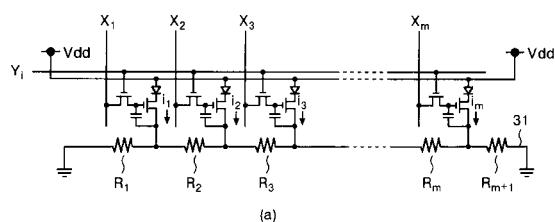

ここでいう大画面化による輝度ムラの発生とは、駆動 TFT のバラツキに起因するものではなく、共通線の配線抵抗を起因としたものである。以下にその問題について説明する。図 15 (a) は、アクティブマトリクスパネル 100 の第 i 行目の表示セル列を示す図である。図 15 (a) に示すように、第 i 行目の m 個の表示セルにおいて、各駆動 TFT のソースはすべて同一の共通線 31 に接続されている。すなわち、すべての駆動 TFT がオ

10

20

30

40

50

ン状態となっている間において、各有機EL素子に流れる電流  $i_1 \sim i_m$  はすべて同一の共通線31に流れ込む。ここで、共通線31は、高導電性の材料によって形成されてはいるが、多少の配線抵抗（図中の抵抗  $R_1 \sim R_{m+1}$ ）を有しており、大画面化に伴ってその長さが長くなつた場合には、その配線抵抗による電圧降下は無視できないものとなる。

【0016】

また、通常、大画面化に伴つて高精細化も実現されるため、行方向における表示セルの数も多くなる。これは、共通線31に流れ込む電流の総和が増大することを意味し、上記した配線抵抗による電圧降下をさらに増大させる。よつて、アクティブマトリクスパネル100の輝度を最大にした場合には、共通線31に流れ込む電流値も最大になる。図15(b)は、共通線における電圧降下を説明するための説明図である。共通線31は、通常、図13に示したように、行ごとにかつ行方向に平行してそれぞれ配置されており、その両端は共通電源に接続されている。共通電源は多くの場合接地電位であるため、各表示セルから共通線31に流れ込んだ電流は、その流入した位置に応じた電流値で分割されて共通線31の両端に向かう。よつて、共通線31の端部からの位置に応じて配線抵抗が重畠されることを考慮すると、共通線31の配線長を  $L$  とした場合、図15(b)に示すように、共通線31の一端から  $0.5L$  の位置の電位が最大となる。なお、この最大値  $V_{max}$  は、各有機EL素子に流れる電流を  $i$  とし、表示セル間に相当する共通線31の配線抵抗の抵抗値を  $r$  とすると、  $m$  個の表示セルを有する行では、

$$V_{max} = (1/2)ri((m+1)/2)^2 \quad \dots [m: \text{奇数}]$$

$$V_{max} = (1/2)ri(m/2)((m+2)/2) \quad \dots [m: \text{偶数}]$$

で表わされる。

【0017】

有機EL表示装置では、すべての有機EL素子を定常的に発光させているため、表示セル内のキャパシタに新たなデータ電圧を書き込む直前においても、各表示セルから共通線31へと電流が流れ込んでいる。換言すれば、データ電圧の書き込む直前においても、共通線31の電位は、データ電圧の書き込みが行われる表示セルの位置に応じた大きさ、すなわち図15(b)に示したような電位分布に従つた大きさを有する。ここで、図15(a)に示された表示セルの構成を見てもわかるように、キャパシタの一端は共通線31に接続されているため、キャパシタに書き込まれる電圧は、結局、その共通線31の電位を基準とした大きさとなる。すなわち、1列目の表示セルと  $m/2$  列目の表示セルにそれぞれ同じ電圧値のデータが入力されたとしても、各表示セルのキャパシタに書き込まれる電圧は異なることになる。

【0018】

例えば、データ線駆動回路130からすべてのデータ線  $X_1 \sim X_m$  にデータ電圧  $V_{sing}$  が供給された場合でも、図15のデータ線  $X_1$  に位置する表示セルのキャパシタには電圧  $V_{sing}$  が書き込まれるもの、データ線  $X_{0.5L}$  に位置する表示セルのキャパシタには、電圧  $V_{sing}$  よりも小さい電圧  $V_{sing} - V_{max}$  が書き込まれる。すなわち、アクティブマトリクスパネル100は、中央部が暗く、端に向かって明るくなる。これはアクティブマトリクスパネル100の大型化・高輝度化を実現する上で重要な問題である。

【0019】

また、上述した特許文献2によれば、共通線を必要としないことと、容量39への電圧書き込み時において有機薄膜EL素子38に電流が流れないことから、キャパシタに書き込まれる電圧（以下、蓄積電圧と称する。）に関する問題は生じない。ところが、特許文献2において想定されている表示セルは、容量39に蓄積された電荷によって直接に有機薄膜EL素子38を発光させる構成であり、特許文献1に示すような現在主流の駆動TFTを用いた構成ではない。より詳細に言えば、容量39はTFTを駆動させるために用いられない。よつて、そもそも特許文献2では、大画面化によって蓄積電圧がばらつくという問題は生じない。

【0020】

さらに、上記した特許文献3は、電流書き込み型の表示セルを開示するが、この電流書き込み

10

20

30

40

50

型では、各表示セルに微小な電流を正確な値で与える必要があり、大画面になると特にその電流制御は困難なものとなる。また、電流書き込み型では、表示セルを構成するのに電圧書き込み型で必要とする数以上のTFTが必要となり(例えば4つ)、これは表示セルの開口率の向上やコスト削減の障害になる。

【0021】

本発明は上記に鑑みてなされたものであって、駆動TFTを備えた電圧書き込み型の大画面のアクティブマトリクスピネルに対しても、各表示セルのキャパシタに所望の電圧を正確に書き込むことができるEL表示装置およびその駆動方法を提供することを目的とする。

【0022】

【課題を解決するための手段】

上記目的を達成するため、請求項1にかかるEL表示装置は、複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子とを有して構成されたEL表示装置において、前記走査線に、第1電圧と該第1電圧よりも値の大きい第2電圧とで形成される階段形状パルスを供給する走査線駆動回路を備え、前記走査線で選択される表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続されたことを特徴としている。

【0023】

この請求項1の発明によれば、キャパシタの他端の電位が、走査線に供給される第1電圧または第2電圧によって固定されるので、キャパシタの一端に所望の電圧を正確に書き込むことができる。

【0024】

また、請求項2にかかるEL表示装置は、上記の発明において、前記走査線駆動回路が、前記第1電圧と前記第2電圧を連続した所定の単位期間にそれぞれ割り当てることで前記階段形状パルスを生成するとともに、前記階段形状パルスを、前記複数の走査線に順次、前記単位期間だけずらして供給することを特徴としている。

【0025】

また、請求項3にかかるEL表示装置は、上記の発明において、前記走査線駆動回路が、前記階段形状パルスを前記走査線に供給するとともに、前記階段形状パルスのパルス幅を有する第3電圧で形成された矩形パルスを、前記階段形状パルスが供給されている走査線とは異なる他の走査線に供給することを特徴としている。

【0026】

また、請求項4にかかるEL表示装置は、上記の発明において、前記走査線駆動回路は、前記階段形状パルスを前記走査線に供給するとともに、前記階段形状パルスのパルス幅を有する第3電圧で形成された矩形パルスを、前記階段形状パルスが供給されている走査線とは異なる他の走査線に順次、前記単位期間だけずらして供給することを特徴としている。

【0027】

また、請求項5にかかるEL表示装置は、上記の発明において、前記第3電圧は、前記第2電圧の値と等しいことを特徴としている。

【0028】

また、請求項6にかかるEL表示装置は、上記の発明において、前記データ線に、前記第1電圧以上かつ前記第2電圧未満の値を有するデータ電圧を供給するデータ線駆動回路を備えたことを特徴としている。

【0029】

10

20

30

40

50

また、請求項 7 にかかる E L 表示装置は、複数の選択走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記選択走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方で一端が接続されたエレクトロルミネッセンス ( E L ) 素子とを有して構成された E L 表示装置において、前記選択走査線と対となって配置されるとともに、前記選択走査線で選択される表示セル内の前記駆動トランジスタのソースもしくはドレインおよび前記キャパシタの他端、または、前記選択走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が接続された複数の書き込み走査線と、前記選択走査線に対して走査線選択電圧を供給するとともに、該選択走査線と対となる前記書き込み走査線に対して書き込み基準電圧を供給する走査線駆動回路とを備え、前記走査線駆動回路は、前記有機エレクトロルミネッセンス素子を発光させずに前記データ電圧が前記キャパシタに書き込まれる第 1 フェーズと、前記有機エレクトロルミネッセンス素子を発光させずに前記キャパシタの蓄積電圧を保持する第 2 フェーズと、前記キャパシタの蓄積電圧に基づいて有機エレクトロルミネッセンス素子の発光を次の前記第 1 フェーズまで持続させる第 3 フェーズと、が順次繰り返されるような電圧値とタイミングで、前記走査線選択電圧と前記書き込み基準電圧を供給することを特徴としている。

10

## 【 0 0 3 0 】

この請求項 7 の発明によれば、走査線駆動回路によって、キャパシタの他端の電位が書き込み走査線に供給される電圧で固定されるので、キャパシタの一端に所望の電圧を正確に書き込むことができる。

20

## 【 0 0 3 1 】

また、請求項 8 にかかる E L 表示装置は、上記の発明において、前記走査線駆動回路は、前記第 1 フェーズ～第 3 フェーズに並行して、該第 1 フェーズ～第 3 フェーズが適用されている選択走査線および書き込み走査線とは異なる選択走査線および書き込み走査線に対して、前記キャパシタに負の電圧が供給されるような電圧値とタイミングで、前記走査線選択電圧と前記書き込み基準電圧を供給することを特徴としている。

30

## 【 0 0 3 2 】

また、請求項 9 にかかる E L 表示装置は、上記の発明において、複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方で一端が接続されたエレクトロルミネッセンス ( E L ) 素子とを有して構成された E L 表示装置において、前記走査線で選択される表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続された共通線と、前記共通線に対する表示セルの走査線方向の位置と、前記共通線の前記表示セル間の配線抵抗の抵抗値とに基づいて、該位置における表示セル内の前記エレクトロルミネッセンス素子の電圧降下分を算出し、算出した結果に基づいて補正したデータ電圧を前記データ線に供給するデータ線駆動回路と、を備えたことを特徴としている。

40

## 【 0 0 3 3 】

この請求項 9 の発明によれば、共通線上の各位置で生じる電圧降下量に応じて、各エレクトロルミネッセンス素子に流す電流を所望の値に補正することができる。

## 【 0 0 3 4 】

また、請求項 10 にかかる E L 表示装置は、上記の発明において、前記エレクトロルミネッセンス素子は、有機 E L 素子であることを特徴としている。

## 【 0 0 3 5 】

また、請求項 11 にかかる E L 表示装置の駆動方法は、複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス ( E L ) 素子とを有して構成され、前記走査線で選択される表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、前記走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が、該走査線に隣接した他の走査線に接続された E L 表示装置の駆動方法において、前記走査線に第 1 電圧を所定の単位期間だけ供給する第 1 走査ステップと、前記第 1 走査ステップに引き続き、前記走査線に前記第 1 電圧よりも値の大きい第 2 電圧を前記単位期間だけ供給する第 2 走査ステップと、前記第 2 走査ステップに引き続き、前記走査線に前記選択トランジスタの閾値電圧以下の電圧を少なくとも前記単位期間の間供給する第 3 走査ステップと、を含んだことを特徴としている。

10

#### 【 0 0 3 6 】

この請求項 11 の発明によれば、キャパシタの他端の電位が、走査線に供給される第 1 電圧または第 2 電圧によって固定されるので、キャパシタの一端に所望の電圧を正確に書き込むことができる。

#### 【 0 0 3 7 】

また、請求項 12 にかかる E L 表示装置の駆動方法は、上記の発明において、前記第 1 走査ステップが、さらに、前記第 1 電圧を供給している走査線とは異なる走査線に対して、前記単位時間だけ第 3 電圧を供給し、前記第 2 走査ステップが、さらに、前記第 1 走査ステップにおいて前記第 3 電圧が供給された走査線に対して、前記単位時間だけさらに前記第 3 電圧を供給し、前記第 3 走査ステップが、さらに、前記第 2 走査ステップにおいて前記第 3 電圧が供給された走査線に対して、前記選択トランジスタの閾値電圧以下の電圧を少なくとも前記単位期間の間供給することを特徴としている。

20

#### 【 0 0 3 8 】

また、請求項 13 にかかる E L 表示装置の駆動方法は、複数の選択走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記選択走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス ( E L ) 素子と、前記選択走査線と対となって配置されるとともに、前記選択走査線で選択される表示セル内の前記駆動トランジスタのソースもしくはドレインおよび前記キャパシタの他端、または、前記選択走査線で選択される表示セル内の前記エレクトロルミネッセンス素子の他端が接続された複数の書き込み走査線とを有して構成された E L 表示装置の駆動方法において、前記有機エレクトロルミネッセンス素子を発光させずに前記データ電圧が前記キャパシタに書き込まれるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第 1 走査ステップと、前記有機エレクトロルミネッセンス素子を発光させずに前記キャパシタの蓄積電圧が保持されるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第 2 走査ステップと、前記キャパシタの蓄積電圧に基づいて有機エレクトロルミネッセンス素子の発光を次の前記第 1 走査ステップまで持続させるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する第 3 走査ステップと、を含んだことを特徴としている。

30

#### 【 0 0 3 9 】

この請求項 13 の発明によれば、走査線駆動回路によって、キャパシタの他端の電位が書

40

込み走査線に供給される電圧で固定されるので、キャパシタの一端に所望の電圧を正確に書き込むことができる。

【0040】

また、請求項14にかかるEL表示装置の駆動方法は、上記の発明において、前記第1走査ステップ～第3走査ステップに並行して、該前記第1走査ステップ～第3走査ステップが適用されている選択走査線および書き込み走査線とは異なる選択走査線および書き込み走査線に対し、前記キャパシタに負の電圧が供給されるような電圧値とタイミングで前記選択走査線と前記書き込み走査線にそれぞれ前記走査線選択電圧と前記書き込み基準電圧を供給する消去ステップを含んだことを特徴としている。

【0041】

また、請求項15にかかるEL表示装置の駆動方法は、複数の走査線と複数のデータ線の各交差点近傍に表示セルを設け、前記表示セルが、少なくとも、前記走査線から供給された走査線選択電圧をゲートに入力する選択トランジスタと、前記選択トランジスタを介して前記データ線から供給されたデータ電圧をゲートに入力する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続されたキャパシタと、前記駆動トランジスタのソースおよびドレインの一方に一端が接続されたエレクトロルミネッセンス(EL)素子とを有して構成され、かつ、前記走査線ごとに設けられた共通線に、同一の走査線を共有する各表示セル内の前記駆動トランジスタのソースおよびドレインの他方と前記キャパシタの他端、または、同一の走査線を共有する各表示セル内の前記エレクトロルミネッセンス素子の他端が接続されたEL表示装置の駆動方法において、前記共通線に対する表示セルの走査線方向の位置と、前記共通線の前記表示セル間の配線抵抗の抵抗値とに基づいて、該位置における表示セル内の前記エレクトロルミネッセンス素子の電圧降下分を算出する電圧降下算出ステップと、前記電圧降下算出ステップによって算出された結果に基づいてデータ電圧を補正し、補正したデータ電圧を前記データ線に供給するデータ電圧供給ステップと、を含んだことを特徴としている。

【0042】

この請求項15の発明によれば、共通線上の各位置で生じる電圧降下量に応じて、各エレクトロルミネッセンス素子に流す電流を所望の値に補正することができる。

【0043】

【発明の実施の形態】

以下に、本発明にかかるEL表示装置およびその駆動方法の実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態により本発明が限定されるものではない。

【0044】

(実施の形態1)

まず、実施の形態1にかかるEL表示装置およびその駆動方法について説明する。実施の形態1にかかるEL表示装置およびその駆動方法は、共通線を排除し、従来においてその共通線に接続されていたキャパシタの一端を、そのキャパシタを備えた表示セルに隣接した他の表示セルの走査線に接続するとともに、走査線に印加する電圧を階段形状のパルスにしたことを特徴としている。

【0045】

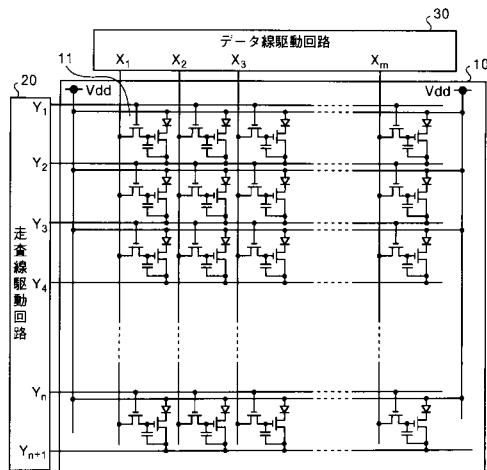

図1は、実施の形態1にかかるEL表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。図1において、アクティブマトリクスパネル10は、ガラス基板上に格子状に形成されたn本の走査線Y<sub>1</sub>～Y<sub>n</sub>とm本のデータ線X<sub>1</sub>～X<sub>m</sub>を備えており、さらにそれら走査線とデータ線との交差点にそれぞれ表示セル11を配置している。また、各表示セル11は、後述するようにTFTを備えている。また、アクティブマトリクスパネル10は、n本の走査線Y<sub>1</sub>～Y<sub>n</sub>に対して所定のタイミングで走査線選択電圧を供給する走査線駆動回路20と、m本のデータ線X<sub>1</sub>～X<sub>m</sub>に対して所定のタイミングでデータ電圧を供給するデータ線駆動回路30とを備えている。すなわち、これら説明した構成については、図8に示した従来の有機EL表示装置と変わりない。なお、図1では、EL表示装置を駆動させるためのその他の種々の回路については省略している

10

20

30

40

50

。

## 【0046】

図1に示すEL表示装置において、図13に示した従来の有機EL表示装置と異なる点は、共通線が排除されたことと、各表示セルのキャパシタの一端が、隣接した表示セルの走査線に接続されたことと、n行目(最終行)の各表示セルのキャパシタの一端に接続される補助走査線 $Y_{n+1}$ が設けられていることである。また、走査線駆動回路20が走査線選択電圧として階段状のパルスを供給するとともに、同様なパルスを補助走査線 $Y_{n+1}$ に対して供給する点も異なる。すなわち、走査線駆動回路20による駆動方法にも特徴がある。なお、補助走査線 $Y_{n+1}$ については、走査線駆動回路20によって内部的に走査線 $Y_1$ と同じパルスが供給される。

10

## 【0047】

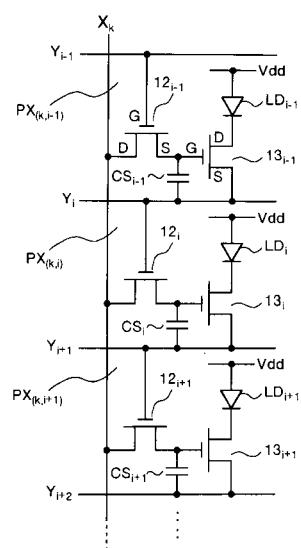

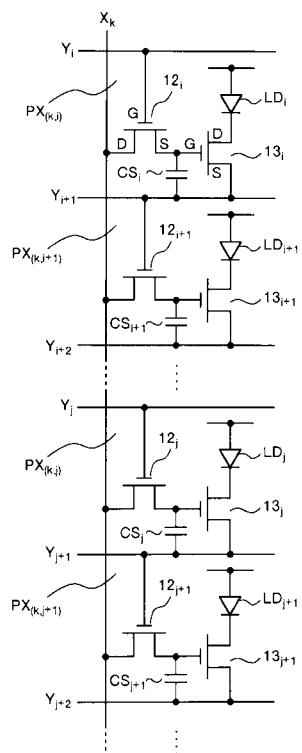

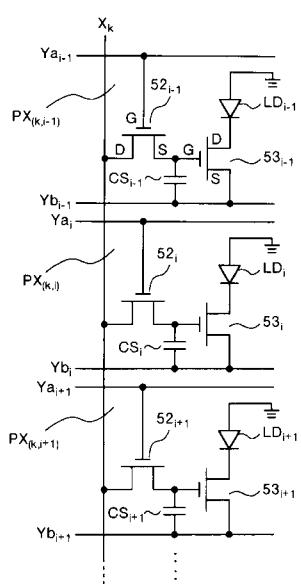

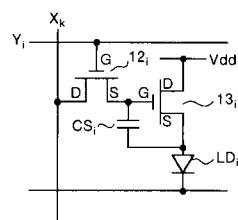

図2は、実施の形態1にかかるEL表示装置の表示セルの等価回路を示す図である。なお、図2は、k列目の*i*-1行目～*i*+1行目に位置する3つの表示セル $PX_{(k, i-1)}$ 、 $PX_{(k, i)}$ 、 $PX_{(k, i+1)}$ を表わしている。ここで、k列*i*行目の表示セル $PX_{(k, i)}$ の等価回路について説明する。表示セル $PX_{(k, i)}$ は、ゲートを走査線 $Y_i$ に接続するとともにドレインをデータ線 $X_k$ に接続したnチャネル型の選択TFT $TFT_{12i}$ と、ゲートを選択TFT $TFT_{12i}$ のソースに接続するとともにソースを下位の表示セル $PX_{(k, i+1)}$ の走査線 $Y_{i+1}$ に接続したnチャネル型の駆動TFT $TFT_{13i}$ と、駆動TFT $TFT_{13i}$ のソース-ゲート間に接続されたキャパシタ $CS_i$ と、アノード側を電源電圧 $V_{dd}$ の供給線に接続するとともにカソード側を駆動TFT $TFT_{13i}$ のドレインに接続した有機EL素子 $LD_i$ とを備えて構成される。表示セル $PX_{(k, i-1)}$ 、 $PX_{(k, i+1)}$ および他の表示セルについても上記 $PX_{(k, i)}$ と同様な等価回路で表わされる。

20

## 【0048】

次に、図2に示した等価回路の動作について説明する。図3は、上記等価回路において、走査線 $Y_{i-1}$ ～ $Y_{i+2}$ に供給される走査線選択電圧とデータ線 $X_k$ に供給されるデータ電圧のタイミングチャートである。なお、図3には、説明の便宜上、表示セル $PX_{(k, i+2)}$ に供給される走査線 $Y_{i+2}$ の電圧も示している。

30

## 【0049】

まず、期間 $t_0$ において、走査線駆動回路20は、走査線 $Y_{i-1}$ に対して電圧 $V1$ を供給し、走査線 $Y_i$ ～ $Y_{i+2}$ および図示しない他の走査線に対しては各選択TFTの閾値電圧以下の電圧(以下、説明を簡単にするため、図3に示すように0[V]とする)を供給する。これにより、表示セル $PX_{(k, i-1)}$ 内の選択TFT $TFT_{12i-1}$ のみがオン状態となり、他の選択TFTはオフ状態となる。なお、電圧 $V1$ は、

30

$$V1 = V_{dd} - V_{th}$$

で表わされる。ここで、 $V_{dd}$ は上記した電源電圧であり、 $V_{th}$ は各表示セル内の有機EL素子の発光閾値電圧である。

## 【0050】

また、期間 $t_0$ においては、データ線駆動回路30によって、データ線 $X_k$ に電圧 $S0$ が供給される。ここで、駆動TFT $TFT_{13i-1}$ のソースは走査線 $Y_i$ に接続されているので、その電位は走査線 $Y_i$ の電位、すなわち0[V]を示す。よって、選択TFT $TFT_{12i-1}$ がオン状態になると、駆動TFT $TFT_{13i-1}$ のゲートには、駆動TFT $TFT_{13i-1}$ のソース-ゲート間電圧、すなわち電圧 $S0$ が入力される。電圧 $S0$ は、正の値を示しかつ駆動TFT $TFT_{13i-1}$ の閾値電圧以上であるので、駆動TFT $TFT_{13i-1}$ はオン状態となる。駆動TFT $TFT_{13i-1}$ がオン状態になると、有機EL素子 $LD_{i-1}$ には、電源電圧 $V_{dd}$ から駆動TFT $TFT_{13i-1}$ のドレイン-ソース間電圧を差し引いた電圧が印加される。ドレイン-ソース間電圧は十分に小さいので、有機EL素子 $LD_{i-1}$ は、発光閾値以上の電圧が印加されることになり発光し始める。

40

## 【0051】

また、キャパシタ $CS_{i-1}$ の一端も走査線 $Y_i$ に接続されているので、期間 $t_0$ では、

50

その電位も走査線  $Y_i$  の電位、すなわち  $0 [V]$  を示す。結局、キャパシタ  $CS_{i-1}$  には、データ線  $X_k$  と走査線  $Y_i$  の電位差、すなわち電圧  $S_0$  が書き込まれる。なお、データ線駆動回路 30 によって供給されるデータ電圧は、上記電圧  $V_1$  以上でありかつ電圧  $V_3$  以下である。すなわち、上記電圧  $S_0$ 、後述する電圧  $S_1 \sim S_5$ 、電圧  $V_1$  および  $V_3$  は、

$$V_1 < S_0 \sim S_5 < V_3$$

の関係を有する。

#### 【0052】

一方、表示セル  $PX_{(k, i-1)}$  以外の表示セル内の選択 TFT は、期間  $t_0$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。

#### 【0053】

次の期間  $t_1$  では、走査線駆動回路 20 は、走査線  $Y_{i-1}$  に対して、電圧  $V_1$  よりも大きい電圧  $V_2$  を供給し、走査線  $Y_i$  に対して電圧  $V_1$  を供給し、走査線  $Y_{i+1}, Y_{i+2}$  および図示しないその他の走査線に対しては  $0 [V]$  を供給する。これにより、表示セル  $PX_{(k, i-1)}$  内の選択 TFT  $T_{12i-1}$  および表示セル  $PX_{(k, i)}$  内の選択 TFT  $T_{12i}$  がオン状態となり、他の選択 TFT はオフ状態となる。なお、電圧値  $V_2$  は、上記した電圧  $V_3$  よりも十分に大きな値である。

#### 【0054】

また、この期間  $t_1$  においては、データ線駆動回路 30 によって、データ線  $X_k$  に電圧  $S_1$  が供給される。ここで、駆動 TFT  $T_{13i-1}$  のソースは走査線  $Y_i$  に接続されているので、その電位は走査線  $Y_i$  の電位、すなわち  $V_1$  を示す。よって、電圧  $V_2$  の入力により選択 TFT  $T_{12i-1}$  がオン状態になると、駆動 TFT  $T_{13i-1}$  のゲートには、駆動 TFT  $T_{13i-1}$  のソース - ゲート間電圧、すなわち電圧  $S_1 - V_1$  が入力される。電圧  $S_1 - V_1$  は、正の値を示しかつ駆動 TFT  $T_{13i-1}$  の閾値電圧以上でもあるので、駆動 TFT  $T_{13i-1}$  はオン状態となる。

#### 【0055】

駆動 TFT  $T_{13i-1}$  がオン状態になると、有機 EL 素子  $LD_{i-1}$  には、電源電圧  $V_d$  から駆動 TFT  $T_{13i-1}$  のドレイン - ソース間電圧と電圧  $V_1$  を差し引いた電圧が印加されることになる。ドレイン - ソース間電圧は十分に小さいが、電圧  $V_1$  は、上記したように  $V_1 = V_{dd} - V_{th}$  の関係を有するため、有機 EL 素子  $LD_{i-1}$  は発光閾値未満の電圧が印加されることになり発光しない。また、キャパシタ  $CS_{i-1}$  の一端も走査線  $Y_i$  に接続されているので、結局、キャパシタ  $CS_{i-1}$  にも、データ線  $X_k$  と走査線  $Y_i$  の電位差、すなわち電圧  $S_1 - V_1$  が書き込まれる。

#### 【0056】

また、駆動 TFT  $T_{13i}$  のソースは走査線  $Y_{i+1}$  に接続されているので、その電位は走査線  $Y_{i+1}$  の電位、すなわち  $0 [V]$  を示す。よって、電圧  $V_1$  の入力により選択 TFT  $T_{12i}$  がオン状態になると、駆動 TFT  $T_{13i}$  のゲートには、駆動 TFT  $T_{13i}$  のソース - ゲート間電圧、すなわち電圧  $S_1$  が入力される。電圧  $S_1$  は、正の値を示しかつ駆動 TFT  $T_{13i}$  の閾値電圧以上でもあるので、結局、駆動 TFT  $T_{13i}$  はオン状態となる。駆動 TFT  $T_{13i}$  がオン状態になると、走査線  $Y_{i+1}$  の電位が  $0 [V]$  であるので、有機 EL 素子  $LD_i$  に、電源電圧  $V_{dd}$  から駆動 TFT  $T_{13i}$  のドレイン - ソース間電圧を差し引いた電圧が印加される。この状態は、上記した期間  $t_0$  での有機 EL 素子  $LD_{i-1}$  と同様な状態であるので、有機 EL 素子  $LD_i$  は発光し始める。また、キャパシタ  $CS_i$  についても、上記した期間  $t_0$  でのキャパシタ  $CS_{i-1}$  と同様な状態となるので、データ線  $X_k$  と走査線  $Y_i$  の電位差、すなわちデータ電圧  $S_1$  が書き込まれる。

#### 【0057】

一方、表示セル  $PX_{(k, i-1)}$  および  $PX_{(k, i)}$  以外の表示セル内の選択 TFT は、期間  $t_1$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も

10

20

30

40

50

発光しない。

【0058】

次の期間 $t_2$ では、走査線駆動回路20は、走査線 $Y_{i-1}$ に対して0[V]を供給し、走査線 $Y_i$ に対して上記した電圧 $V_2$ を供給し、走査線 $Y_{i+1}$ に対して上記した電圧 $V_1$ を供給し、走査線 $Y_{i+2}$ および図示しない他の走査線に対しては0[V]を供給する。これにより、表示セル $PX_{(k,i)}$ 内の選択TFT $12_{i-1}$ および表示セル $PX_{(k,i+1)}$ 内の選択TFT $12_{i+1}$ がオン状態となり、表示セル $PX_{(k,i-1)}$ 内の選択TFT $12_{i-1}$ および他の表示セル内の各選択TFTはオフ状態となる。また、この期間 $t_2$ においては、データ線駆動回路30によって、データ線 $X_k$ に電圧 $S_2$ が供給される。

10

【0059】

この状態で、表示セル $PX_{(k,i-1)}$ 内の選択TFT $12_{i-1}$ はオフ状態であるが、上記した期間 $t_1$ において、同表示セル内のキャパシタ $CS_{i-1}$ には電圧 $S_1 - V_1$ が書き込まれているため、駆動TFT $13_{i-1}$ はその電圧をゲートに入力してオン状態となる。しかしながら、駆動TFT $13_{i-1}$ のソースに接続されている走査線 $Y_i$ には十分に大きな値を有する電圧 $V_2$ が供給されているため、有機EL素子 $LD_{i-1}$ は発光閾値未満の電圧が印加されることになり発光しない。

【0060】

一方、駆動TFT $13_i$ のソースは走査線 $Y_{i+1}$ に接続されているので、期間 $t_2$ では、その電位は走査線 $Y_{i+1}$ の電位、すなわち $V_1$ を示す。よって、選択TFT $12_i$ がオン状態になると、駆動TFT $13_i$ のゲートには、駆動TFT $13_i$ のソース-ゲート間電圧、すなわち電圧 $S_2 - V_1$ が入力される。また、駆動TFT $13_{i+1}$ のソースは走査線 $Y_{i+2}$ に接続されているので、期間 $t_2$ では、その電位は走査線 $Y_{i+1}$ の電位、すなわち0[V]を示す。よって、選択TFT $12_{i+1}$ がオン状態になると、駆動TFT $13_{i+1}$ のゲートおよびキャパシタ $CS_{i+1}$ には、駆動TFT $13_{i+1}$ のソース-ゲート間電圧、すなわち電圧 $S_2$ が入力される。

20

【0061】

これら表示セル $PX_{(k,i)}$ および $PX_{(k,i+1)}$ の状態は、上記した期間 $t_1$ における表示セル $PX_{(k,i-1)}$ および表示セル $PX_{(k,i)}$ と同様な状態である。よって、有機EL素子 $LD_i$ は発光閾値未満の電圧が印加されることになり発光せず、キャパシタ $CS_i$ には、データ線 $X_k$ と走査線 $Y_i$ の電位差、すなわちデータ電圧 $S_2 - V_1$ が書き込まれる。また、有機EL素子 $LD_{i+1}$ は発光し始め、キャパシタ $CS_{i+1}$ には、データ線 $X_k$ と走査線 $Y_i$ の電位差、すなわちデータ電圧 $S_2$ が書き込まれる。

30

【0062】

上記表示セル以外の表示セル内の選択TFTは、期間 $t_2$ においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動TFTはオフ状態であり、各有機EL素子も発光しない。

【0063】

次の期間 $t_3$ では、走査線駆動回路20は、走査線 $Y_{i-1}$ および $Y_i$ に対して0[V]を供給し、走査線 $Y_{i+1}$ に対して上記した電圧 $V_2$ を供給し、走査線 $Y_{i+2}$ に対して上記した電圧 $V_1$ を供給し、図示しない他の走査線に対しては0[V]を供給する。これにより、表示セル $PX_{(k,i+1)}$ 内の選択TFT $12_{i+1}$ および表示セル $PX_{(k,i+2)}$ 内の選択TFT $12_{i+2}$ がオン状態となり、表示セル $PX_{(k,i-1)}$ 内の選択TFT $12_{i-1}$ 、表示セル $PX_{(k,i)}$ 内の選択TFT $12_i$ および他の表示セル内の各選択TFTはオフ状態となる。また、この期間 $t_3$ においては、データ線駆動回路30によって、データ線 $X_k$ に電圧 $S_3$ が供給される。

40

【0064】

この状態で、表示セル $PX_{(k,i-1)}$ 内の選択TFT $12_{i-1}$ はオフ状態であるが、同表示セル内のキャパシタ $CS_{i-1}$ には電圧 $S_1 - V_1$ が保持されているため、駆動TFT $13_{i-1}$ はその電圧をゲートに入力してオン状態となる。さらに、駆動TFT $13_i$ はその電圧をゲートに入力してオフ状態となる。

50

$3_{i-1}$  のソースに接続されている走査線  $Y_i$  は  $0 [V]$  であるため、有機 EL 素子  $L D_i$  は発光閾値以上の電圧が印加されて発光し始める。

【0065】

また、この期間  $t_3$  において、表示セル  $P X_{(k, i)}$  内の選択 TFT $12_i$  はオフ状態であるが、上記した期間  $t_2$  において、同表示セル内のキャパシタ  $C S_i$  には電圧  $S_2 - V_1$  が書き込まれているため、駆動 TFT $13_i$  はその電圧をゲートに入力してオン状態となる。しかしながら、駆動 TFT $13_i$  のソースに接続されている走査線  $Y_{i+1}$  には上記した電圧  $V_2$  が供給されているため、有機 EL 素子  $L D_i$  には発光閾値未満の電圧が印加されることになり発光しない。すなわち、表示セル  $P X_{(k, i)}$  は、上記した期間  $t_2$  における表示セル  $P X_{(k, i-1)}$  と同様な状態となる。

10

【0066】

一方、駆動 TFT $13_{i+1}$  のソースは走査線  $Y_{i+2}$  に接続されているので、期間  $t_3$  では、その電位は走査線  $Y_{i+2}$  の電位、すなわち  $V_1$  を示す。よって、選択 TFT $12_{i+1}$  がオン状態になると、駆動 TFT $13_{i+1}$  のゲートおよびキャパシタ  $C S_{i+1}$  に、駆動 TFT $13_{i+1}$  のソース - ゲート間電圧、すなわち電圧  $S_3 - V_1$  が入力される。

【0067】

この状態は、上記した期間  $t_1$  における駆動 TFT $13_{i-1}$  と同様な状態である。よって、有機 EL 素子  $L D_{i+1}$  は発光閾値未満の電圧が印加されることになり発光せず、キャパシタ  $C S_{i+1}$  には、データ線  $X_k$  と走査線  $Y_{i+2}$  の電位差、すなわちデータ電圧  $S_3 - V_1$  が書き込まれる。

20

【0068】

表示セル  $P X_{(k, i+2)}$  以外の表示セル内の選択 TFT は、期間  $t_3$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。

【0069】

続く期間  $t_4$  以降においては、走査線駆動回路 20 によって選択された順、すなわち走査線に走査線選択電圧として電圧  $V_1$  が供給された順に、各表示セルに電圧  $V_1$  と電圧  $V_2$  からなる図 3 に示すような階段形状のパルスが供給され、上述した動作が繰り返される。

30

【0070】

これら動作を一般的に記述すると、各表示セルは、走査線に電圧  $V_1$  が供給された際のデータ電圧に基づいて一瞬だけ有機 EL 素子を発光させる第 1 フェーズと、有機 EL 素子を発光させずに、走査線に電圧  $V_1$  よりも大きい電圧  $V_2$  が供給された際のデータ電圧をキャパシタに書き込む第 2 フェーズと、有機 EL 素子を発光させずに、キャパシタへの書き込みを停止しつつ書き込まれた電圧を保持する第 3 フェーズと、キャパシタへの書き込みを停止しつつ書き込まれた電圧に基づいて有機 EL 素子の発光を新たな第 1 フェーズまで持続させる第 4 フェーズとにいった流れで動作する。

【0071】

ここで特に、上記した第 2 フェーズの電圧書き込み時において、従来の構成で共通線に接続されていたキャパシタの一端の電位が、表示セルの位置とは無関係に電圧  $V_1$  に固定されるので、そのキャパシタに所望の電圧（データ電圧 - 電圧  $V_1$ ）を正確に書き込むことができる。但し、データ線には、キャパシタに書き込みたい電圧よりも電圧  $V_1$  だけ大きい電圧を供給する必要がある。なお、第 1 フェーズにおいて望まない発光が生じるがそれは第 4 フェーズにおいて持続する発光時間に比べて無視できる程に短い時間であり、視認することもできないために問題とはならない。

40

【0072】

以上に説明したように、実施の形態 1 にかかる EL 表示装置およびその駆動方法によれば、キャパシタの一端と駆動 TFT のソースを、それらを含む表示セルの下位の行を選択するための走査線に接続するので、従来必要であった共通線を排除することができる。また、表示セル内のキャパシタの一端の電位をその走査線に入力される電圧  $V_1$  に固定しつつ

50

有機EL素子に電流を流さない状態で、データ電圧をそのキャパシタに書き込むので、行上の表示セルの位置に応じてキャパシタの一端の電位が変動するようなことも無く、キャパシタに所望の電圧を正確に保持させることができる。すなわち、アクティブマトリクスパネル10の大画面化により行方向に位置する表示セルの数が増加しても、中央部が暗くて端に向かって明るくなるというような従来生じていた輝度ムラは発生しない。

#### 【0073】

##### (実施の形態2)

つぎに、実施の形態2にかかるEL表示装置およびその駆動方法について説明する。実施の形態2にかかるEL表示装置およびその駆動方法は、実施の形態1に説明した駆動方法に加えて、上述した階段形状のパルス幅に等しい矩形パルスを、階段形状のパルスが書き込まれている表示セル以外の表示セルに入力することで、同一パネル上においてデータの書き込みとデータの消去を同時に行うことを特徴としている。

#### 【0074】

なお、実施の形態2にかかるEL表示装置の概略構成については図1に示したとおりであるので、ここではその説明を省略する。よって、以下においては、走査線駆動回路20による駆動方法について説明する。

#### 【0075】

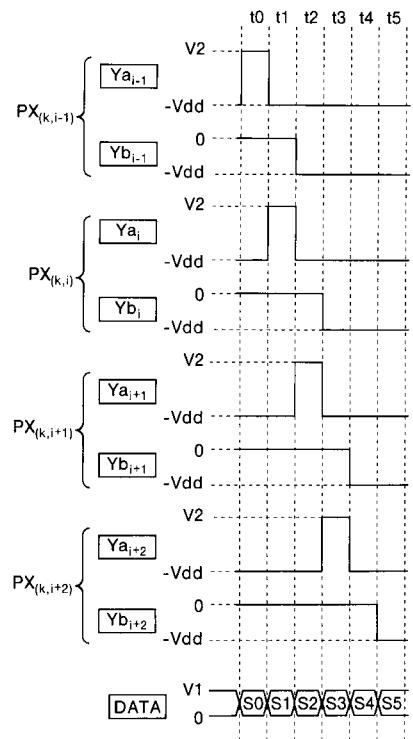

図4は、実施の形態2にかかるEL表示装置の表示セルの等価回路を示す図である。特に図4は、k列目のi行目およびi+1行目に位置する2つの表示セルPX<sub>(k, i)</sub>、PX<sub>(k, i+1)</sub>と、それら表示セルから所定行数分離れたj行目およびj+1行目に位置する2つの表示セルPX<sub>(k, j)</sub>、PX<sub>(k, j+1)</sub>とを表わしている。各表示セルの回路構成および符号については実施の形態1と同様であるのでここでは説明を省略する。

#### 【0076】

図5は、図4に示した等価回路において、走査線Y<sub>i</sub>、Y<sub>i+1</sub>、Y<sub>j</sub>、Y<sub>j+1</sub>に供給される走査線選択電圧とデータ線X<sub>k</sub>に供給されるデータ電圧のタイミングチャートである。なお、図中の電圧V1、V2およびV3は、実施の形態1に示したとおりの関係を有する。

#### 【0077】

まず、期間t1において、走査線駆動回路20は、走査線Y<sub>i</sub>に対して電圧V1を供給し、走査線Y<sub>j</sub>に対して電圧V2を供給し、走査線Y<sub>i+1</sub>、Y<sub>j+1</sub>および図示しない他の走査線に対して0[V]を供給する。これにより、表示セルPX<sub>(k, i)</sub>内の選択TFT12<sub>i</sub>と表示セルPX<sub>(k, j)</sub>内の選択TFT12<sub>j</sub>がオン状態となり、他の選択TFTはオフ状態となる。

#### 【0078】

また、この期間t1においては、データ線駆動回路30によって、データ線X<sub>k</sub>にデータ電圧S1が供給される。ここで、駆動TFT13<sub>i</sub>のソースは走査線Y<sub>i+1</sub>に接続されているので、その電位は走査線Y<sub>i+1</sub>の電位、すなわち0[V]を示す。よって、選択TFT12<sub>i</sub>がオン状態になると、キャパシタCS<sub>i</sub>と駆動TFT13<sub>i</sub>のゲートには、駆動TFT13<sub>i</sub>のソース-ゲート間電圧、すなわち電圧S1が入力される。この状態は、実施の形態1で説明した期間t1における表示セルPX<sub>(k, i)</sub>の状態と同じである。よって、有機EL素子LD<sub>i</sub>は、発光閾値以上の電圧が印加されて発光し始め、キャパシタCS<sub>i</sub>には、データ線X<sub>k</sub>と走査線Y<sub>i+1</sub>の電位差、すなわち電圧S1が書き込まれる。

#### 【0079】

また、駆動TFT13<sub>j</sub>のソースは走査線Y<sub>j+1</sub>に接続されているので、その電位は走査線Y<sub>j+1</sub>の電位、すなわち0[V]を示す。よって、選択TFT12<sub>j</sub>がオン状態になると、キャパシタCS<sub>j</sub>と駆動TFT13<sub>j</sub>のゲートには、データ電圧S1が入力される。この状態も、上記した表示セルPX<sub>(k, i)</sub>と同様な状態であるため、有機EL素子LD<sub>j</sub>は、発光閾値以上の電圧が印加されて発光し始め、キャパシタCS<sub>j</sub>には、データ電圧S1が書き込まれる。

10

20

30

40

50

タ線  $X_k$  と走査線  $Y_{j+1}$  の電位差、すなわちデータ電圧  $S_1$  が書き込まれる。

【0080】

一方、表示セル  $PX_{(k,i)}$  および  $PX_{(k,j)}$  以外の表示セル内の選択 TFT は、期間  $t_1$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。

【0081】

次の期間  $t_2$  では、走査線駆動回路 20 は、走査線  $Y_i, Y_j, Y_{j+1}$  に対して電圧  $V_2$  を供給し、走査線  $Y_{i+1}$  に対して電圧  $V_1$  を供給し、図示しない他の走査線に対しては 0 [V] を供給する。これにより、表示セル  $PX_{(k,i)}$  内の選択 TFT12i 10 、表示セル  $PX_{(k,i+1)}$  内の選択 TFT12i+1 、表示セル  $PX_{(k,j)}$  内の選択 TFT12j および表示セル  $PX_{(k,j+1)}$  内の選択 TFT12j+1 がオン状態となり、他の選択 TFT はオフ状態となる。

【0082】

また、この期間  $t_2$  においては、データ線駆動回路 30 によって、データ線  $X_k$  に電圧  $S_2$  が供給される。ここで、駆動 TFT13i のソースは走査線  $Y_{i+1}$  に接続されているので、その電位は走査線  $Y_{i+1}$  の電位、すなわち電圧  $V_1$  を示す。よって、選択 TFT12i がオン状態になると、キャパシタ  $CS_i$  と駆動 TFT13i のゲートには、電圧  $S_2 - V_1$  が入力される。また、駆動 TFT13i+1 のソースは走査線  $Y_{i+2}$  に接続されているので、その電位は走査線  $Y_{i+2}$  の電位、すなわち 0 [V] を示す。よって、選択 TFT12i+1 がオン状態になると、キャパシタ  $CS_{i+1}$  と駆動 TFT13i+1 のゲートには、データ電圧  $S_2$  が入力される。これら表示セル  $PX_{(k,i)}$  および  $PX_{(k,i+1)}$  の状態は、実施の形態 1 で説明した期間  $t_2$  における表示セル  $PX_{(k,i)}$  および  $PX_{(k,i+1)}$  の状態と同じである。よって、有機 EL 素子  $LD_i$  は、発光閾値未満の電圧が印加されて発光せず、キャパシタ  $CS_i$  には、データ線  $X_k$  と走査線  $Y_{i+1}$  の電位差、すなわちデータ電圧  $S_2 - V_1$  が書き込まれる。また、有機 EL 素子  $LD_{i+1}$  は、発光閾値以上の電圧が印加されて発光し始め、キャパシタ  $CS_{i+1}$  には、データ線  $X_k$  と走査線  $Y_{i+2}$  の電位差、すなわちデータ電圧  $S_2$  が書き込まれる。

【0083】

一方、駆動 TFT13j のソースは走査線  $Y_{j+1}$  に接続されているので、その電位は走査線  $Y_{j+1}$  の電位、すなわち  $V_2$  を示す。よって、この期間  $t_2$  においては、選択 TFT12j がオン状態になると、駆動 TFT13j のゲートに、駆動 TFT13j のソース - ゲート間電圧、すなわち電圧  $S_2 - V_2$  が入力される。電圧  $V_2$  は、実施の形態 1 で説明したように、データ電圧よりも大きな値を有するので、上記電圧  $S_2 - V_2$  は負の値を示す。すなわち、駆動 TFT13j はオフ状態となり、有機 EL 素子  $LD_j$  は発光しない。また、キャパシタ  $CS_j$  の一端も走査線  $Y_{j+1}$  に接続されているので、結局、キャパシタ  $CS_j$  にも、データ線  $X_k$  と走査線  $Y_{j+1}$  の電位差、すなわち負の電圧  $S_2 - V_2$  が書き込まれる。

【0084】

また、駆動 TFT13j+1 のソースは走査線  $Y_{j+2}$  に接続されているので、その電位は走査線  $Y_{j+2}$  の電位、すなわち 0 [V] を示す。よって、電圧  $V_2$  の入力により選択 TFT12j+1 がオン状態になると、キャパシタ  $CS_{j+1}$  と駆動 TFT13j+1 のゲートには、データ電圧  $S_2$  が入力される。この状態は、上記した期間  $t_1$  における表示セル  $PX_{(k,j)}$  と同様な状態であるため、有機 EL 素子  $LD_{j+1}$  は、発光閾値以上の電圧が印加されて発光し始め、キャパシタ  $CS_{j+1}$  には、データ線  $X_k$  と走査線  $Y_{j+2}$  の電位差、すなわちデータ電圧  $S_2$  が書き込まれる。

【0085】

また、上記以外の表示セル内の選択 TFT は、この期間  $t_2$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。

10

20

30

40

50

## 【0086】

次の期間  $t_3$  では、走査線駆動回路 20 は、走査線  $Y_{i+1}, Y_{j+1}$  に対して電圧  $V_2$  を供給し、走査線  $Y_i, Y_j$  および図示しない他の走査線に対しては 0 [V] を供給する。これにより、表示セル  $PX_{(k, i+1)}$  内の選択 TFT12 $_{i+1}$  および表示セル  $PX_{(k, j+1)}$  内の選択 TFT12 $_{j+1}$  がオン状態となり、他の選択 TFT はオフ状態となる。

## 【0087】

また、この期間  $t_3$  においては、データ線駆動回路 30 によって、データ線  $X_k$  に電圧  $S_3$  が供給される。この状態で、表示セル  $PX_{(k, i)}$  内の選択 TFT12 $_i$  はオフ状態であるが、上記した期間  $t_2$  において、同表示セル内のキャパシタ  $CS_i$  には電圧  $S_2 - V_1$  が書き込まれているため、駆動 TFT13 $_i$  はその電圧をゲートに入力してオン状態となる。しかしながら、駆動 TFT13 $_i$  のソースに接続されている走査線  $Y_i$  には上記した電圧  $V_2$  が供給されているため、実施の形態 1 で説明した期間  $t_3$  における表示セル  $PX_{(k, i)}$  の状態と同様に、有機 EL 素子  $LD_i$  は発光閾値未満の電圧が印加されることになり発光しない。

## 【0088】

また、駆動 TFT13 $_{i+1}$  のソースは走査線  $Y_{i+2}$  に接続されているが、走査線  $Y_{i+2}$  以降の走査線に対しても、期間  $t_1$  および  $t_2$  における走査線  $Y_i$  のタイミングチャートで示した電圧が順次与えられるので、その駆動 TFT13 $_{i+1}$  のソースの電位は走査線  $Y_{i+2}$  の電位、すなわち電圧  $V_1$  を示す。よって、選択 TFT12 $_{i+1}$  がオン状態になると、キャパシタ  $CS_{i+1}$  と駆動 TFT13 $_{i+1}$  のゲートには、電圧  $S_3 - V_1$  が入力される。この表示セル  $PX_{(k, i+1)}$  の状態は、実施の形態 1 で説明した期間  $t_3$  における表示セル  $PX_{(k, i+1)}$  の状態と同じである。すなわち、有機 EL 素子  $LD_{i+1}$  は、発光閾値未満の電圧が印加されて発光せず、キャパシタ  $CS_{i+1}$  には、データ線  $X_k$  と走査線  $Y_{i+2}$  の電位差、すなわち電圧  $S_3 - V_1$  が書き込まれる。

## 【0089】

一方、表示セル  $PX_{(k, j)}$  内の選択 TFT12 $_j$  はオフ状態であり、さらには、上記した期間  $t_2$  において、同表示セル内のキャパシタ  $CS_i$  には負の電圧  $S_2 - V_2$  が書き込まれているため、駆動 TFT13 $_j$  もまたオフ状態となる。すなわち、有機 EL 素子  $LD_j$  は発光しない。特に、この非発光状態は、期間  $t_1$  における表示セル  $PX_{(k, i)}$  のように新たな電圧書き込みが行われるまで持続する。換言すれば、表示セル  $PX_{(k, j)}$  に対してデータの消去が行われる。

## 【0090】

また、駆動 TFT13 $_{j+1}$  のソースは走査線  $Y_{j+1}$  に接続されているが、走査線  $Y_{j+2}$  以降の走査線に対しても、期間  $t_1$  および  $t_2$  における走査線  $Y_j$  のタイミングチャートで示した電圧が順次与えられるので、その駆動 TFT13 $_{j+1}$  のソースの電位は走査線  $Y_{j+2}$  の電位、すなわち電圧  $V_2$  を示す。この状態は、期間  $t_2$  における表示セル  $PX_{(k, j)}$  の状態と同様である。すなわち、駆動 TFT13 $_{j+1}$  は、ゲートに負の電圧  $S_3 - V_2$  を入力してオフ状態となり、有機 EL 素子  $LD_{j+1}$  は発光しない。また、キャパシタ  $CS_{j+1}$  にも、データ線  $X_k$  と走査線  $Y_{j+2}$  の電位差、すなわち負の電圧  $S_3 - V_2$  が書き込まれる。

## 【0091】

また、上記以外の表示セル内の選択 TFT は、期間  $t_3$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。

## 【0092】

続く期間  $t_4$  以降においては、各表示セルに対して順次、上述した動作と同様な動作が繰り返される。すなわち、各表示セルは、上記した表示セル  $PX_{(k, i)}, PX_{(k, i+1)}$  のように、走査線駆動回路 20 によって、走査線に階段形状のパルスの一段目として電圧  $V_1$  が供給された順に、正確な電圧書き込みによって有機 EL 素子を発光させる。ま

10

20

30

40

50

た、各表示セルは、上記した表示セル  $P X_{(k, j)}$  ,  $P X_{(k, j+1)}$  のように、走査線駆動回路 20 によって、走査線に矩形パルスである電圧  $V_2$  が供給された順に、データの消去を行う。

#### 【0093】

以上に説明したように、実施の形態 2 にかかる EL 表示装置およびその駆動方法によれば、実施の形態 1 で説明した駆動方法に加え、発光のための電圧書込みが行われていない走査線上の表示セルに対して、順次、そのキャパシタへ負の電圧を書き込むので、アクティブマトリクスパネル 10 上において同時にデータ表示とデータの消去を実行することができる。特に、そのデータの消去動作においては、駆動 TFT のソース - ゲート間に逆電圧を印加することになるので、駆動 TFT の閾値電圧シフトを抑制することもできる。

10

#### 【0094】

##### (実施の形態 3)

次に、実施の形態 3 にかかる EL 表示装置およびその駆動方法について説明する。実施の形態 3 にかかる EL 表示装置およびその駆動方法は、同一行の表示セルの選択 TFT に接続された走査線（以下、選択走査線と称する。）と、同一行の表示セルのキャパシタに接続された線路（以下、書込み走査線と称する。）とが、それぞれ独立して走査線駆動回路に接続され、それら選択走査線と書込み走査線に所定のタイミングで互いに異なる電圧パルスを印加することを特徴としている。

#### 【0095】

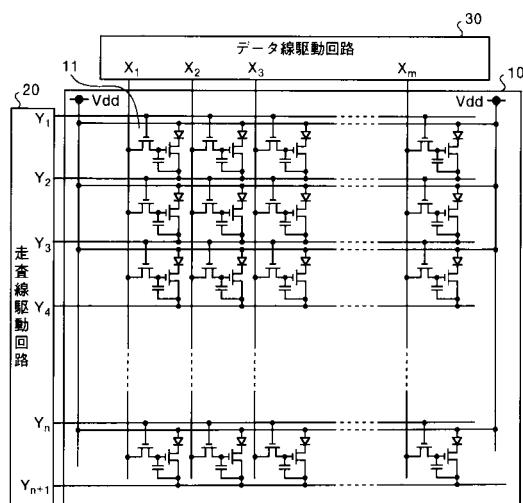

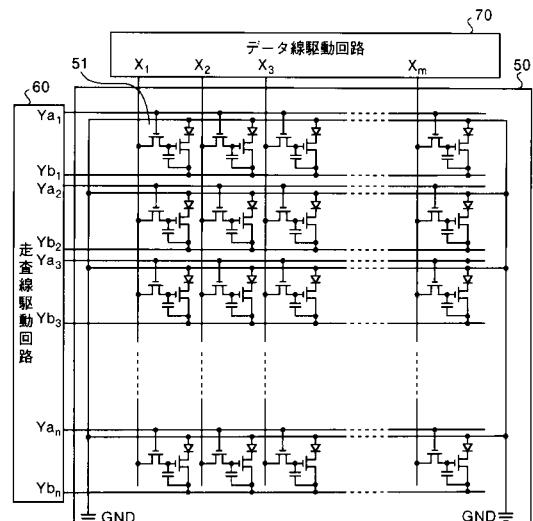

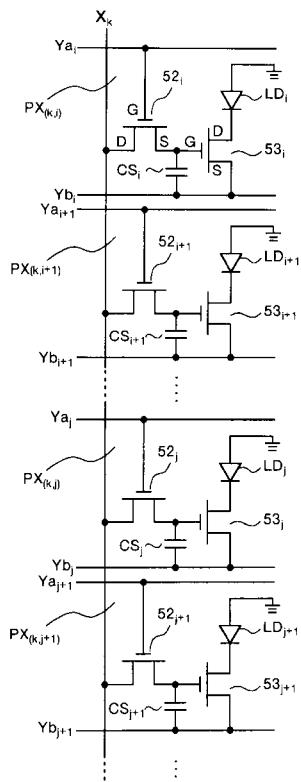

図 6 は、実施の形態 3 にかかる EL 表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。図 6 において、アクティブマトリクスパネル 50 は、ガラス基板上に格子状に形成された  $n$  本の選択走査線  $Y_{a_1}$  ~  $Y_{a_n}$  と  $n$  本の書込み走査線  $Y_{b_1}$  ~  $Y_{b_n}$  と  $m$  本のデータ線  $X_1$  ~  $X_m$  を備えており、さらにそれら選択走査線とデータ線との交差点にそれぞれ表示セル 51 を配置している。また、各表示セル 51 は、後述するように TFT を備えている。また、アクティブマトリクスパネル 50 は、 $n$  本の選択走査線  $Y_{a_1}$  ~  $Y_{a_n}$  に対して所定のタイミングで走査線選択電圧を供給するとともに  $n$  本の書込み走査線  $Y_{b_1}$  ~  $Y_{b_n}$  に対して所定のタイミングで書込み基準電圧を供給する走査線駆動回路 60 と、 $m$  本のデータ線  $X_1$  ~  $X_m$  に対して所定のタイミングでデータ電圧を供給するデータ線駆動回路 30 とを備えている。なお、図 6 では、EL 表示装置を駆動させるためのその他の種々の回路については省略している。

20

30

#### 【0096】

図 6 に示す EL 表示装置において、図 13 に示した従来の有機 EL 表示装置と異なる点は、各表示セルのキャパシタに接続されていた共通線が走査線駆動回路 60 に接続され、各表示セルの有機 EL 素子のアノード側が接地線 GND に接続されていることである。また、走査線駆動回路 60 が上記走査線選択電圧と上記書込み基準電圧を所定の大小関係を有した状態でそれぞれ選択走査線と書込み走査線に供給する点も異なる。すなわち、走査線駆動回路 50 による駆動方法にも特徴がある。

#### 【0097】

図 7 は、実施の形態 3 にかかる EL 表示装置の表示セルの等価回路を示す図である。なお、図 7 は、 $k$  列目の  $i-1$  行目 ~  $i+1$  行目に位置する 3 つの表示セル  $P X_{(k, i-1)}$  ,  $P X_{(k, i)}$  ,  $P X_{(k, i+1)}$  を表わしている。ここで、 $k$  列  $i$  行目の表示セル  $P X_{(k, i)}$  の等価回路について説明する。表示セル  $P X_{(k, i)}$  は、ゲートを選択走査線  $Y_{a_i}$  に接続するとともにドレインをデータ線  $X_k$  に接続した  $n$  チャネル型の選択 TFT  $TFT_{52i}$  と、ゲートを選択 TFT  $TFT_{52i}$  のソースに接続するとともにソースを書き込み走査線  $Y_{b_i}$  に接続した  $n$  チャネル型の駆動 TFT  $TFT_{53i}$  と、駆動 TFT  $TFT_{53i}$  のソース - ゲート間に接続されたキャパシタ  $CS_i$  と、アノード側を接地線 GND に接続するとともにカソード側を駆動 TFT  $TFT_{53i}$  のドレインに接続した有機 EL 素子  $LD_i$  とを備えて構成される。表示セル  $P X_{(k, i-1)}$  ,  $P X_{(k, i+1)}$  および他の表示セルについても上記  $P X_{(k, i)}$  と同様な等価回路で表わされる。

40

#### 【0098】

50

次に、図7に示した等価回路の動作について説明する。図8は、上記等価回路において、選択走査線  $Y_{a_{i-1}} \sim Y_{a_{i+2}}$  に供給される走査線選択電圧と書き込み走査線  $Y_{b_{i-1}} \sim Y_{b_{i+2}}$  に供給される書き込み基準電圧とデータ線  $X_k$  に供給されるデータ電圧のタイミングチャートである。なお、図8には、説明の便宜上、表示セル  $PX_{(k, i+2)}$  に供給される選択走査線  $Y_{a_{i+2}}$  および書き込み走査線  $Y_{b_{i+2}}$  の電圧も示している。

#### 【0099】

まず、期間  $t_0$ において、走査線駆動回路60は、選択走査線  $Y_{a_{i-1}}$  に対して電圧  $V_2$  を供給し、選択走査線  $Y_{a_i} \sim Y_{a_{i+2}}$  および図示しない他の選択走査線に対して負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y_{b_{i-1}} \sim Y_{b_{i+2}}$  および図示しない他の書き込み走査線に対して接地電位(0[V])を供給する。これにより、表示セル  $PX_{(k, i-1)}$  内の選択 TFT52<sub>i-1</sub> のみがオン状態となり、他の選択 TFT はオフ状態となる。

#### 【0100】

また、期間  $t_0$ においては、データ線駆動回路70によって、データ線  $X_k$  に電圧  $S_0$  が供給される。ここで、駆動 TFT53<sub>i-1</sub> のソースは書き込み走査線  $Y_{b_{i-1}}$  に接続されているので、その電位は書き込み走査線  $Y_{b_{i-1}}$  の電位、すなわち 0[V] を示す。よって、選択 TFT52<sub>i-1</sub> がオン状態になると、駆動 TFT53<sub>i-1</sub> のゲートには、駆動 TFT53<sub>i-1</sub> のソース-ゲート間電圧、すなわち電圧  $S_0$  が入力される。ここで、データ線駆動回路70によって供給される電圧  $S_0$  および後述する電圧  $S_1 \sim S_5$  は、正の値を示しかつ駆動 TFT53<sub>i-1</sub> の閾値電圧以上である。すなわち、ゲートに電圧  $S_0$  が供給された駆動 TFT53<sub>i-1</sub> はオン状態となり、有機EL素子  $LD_{i-1}$  のカソード側と書き込み走査線  $Y_{b_{i-1}}$  との間の電流路が形成される。ところが、書き込み走査線  $Y_{b_{i-1}}$  は 0[V] を示しているので、有機EL素子  $LD_{i-1}$  に電圧は印加されず発光しない。

#### 【0101】

この状態では、キャパシタ  $CS_{i-1}$  の一端も書き込み走査線  $Y_{b_{i-1}}$  に接続されているので、期間  $t_0$  では、その電位も書き込み走査線  $Y_{b_{i-1}}$  の電位、すなわち 0[V] を示す。結局、キャパシタ  $CS_{i-1}$  には、データ線  $X_k$  と書き込み走査線  $Y_{b_{i-1}}$  の電位差、すなわち電圧  $S_0$  が書き込まれる。特に、この電圧書き込み時においては、上記したように書き込み走査線  $Y_{b_{i-1}}$  に接続された各表示セル内の有機EL素子に電流が流れないと、各有機EL素子から書き込み走査線  $Y_{b_{i-1}}$  へと電流が流入することはない。これは、従来の共通線で生じていた表示セル位置に基づく電圧降下が生じないことを意味している。

#### 【0102】

一方、表示セル  $PX_{(k, i-1)}$  以外の表示セル内の選択 TFT は、期間  $t_0$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機EL素子も発光しない。

#### 【0103】

次の期間  $t_1$  では、走査線駆動回路60は、選択走査線  $Y_{a_i}$  に対して電圧  $V_2$  を供給し、選択走査線  $Y_{a_{i-1}} \sim Y_{a_{i+2}}$  および図示しない他の選択走査線に対して負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y_{b_{i-1}} \sim Y_{b_{i+2}}$  および図示しない他の書き込み走査線に対して接地電位(0[V])を供給する。これにより、表示セル  $PX_{(k, i)}$  内の選択 TFT52<sub>i</sub> のみがオン状態となり、他の選択 TFT はオフ状態となる。

#### 【0104】

また、期間  $t_1$  においては、データ線駆動回路70によって、データ線  $X_k$  に電圧  $S_1$  が供給される。ここで、駆動 TFT53<sub>i</sub> のソースは書き込み走査線  $Y_{b_i}$  に接続されているので、その電位は書き込み走査線  $Y_{b_i}$  の電位、すなわち 0[V] を示す。よって、選択 TFT52<sub>i</sub> がオン状態になると、駆動 TFT53<sub>i</sub> のゲートには、駆動 TFT53<sub>i</sub> のソース-ゲート間電圧、すなわち電圧  $S_1$  が入力される。この状態は、期間  $t_0$  における表

10

20

30

40

50

示セル  $P X_{(k, i-1)}$  の状態と同様であり、結局、ゲートに電圧  $S_1$  が供給された駆動  $TFT_{53i}$  はオン状態となるが、有機 EL 素子  $L D_i$  に電圧は印加されず発光しない。

### 【0105】

また、この状態において、キャパシタ  $C S_i$  には、期間  $t_0$  における表示セル  $P X_{(k, i-1)}$  のキャパシタ  $C S_{i-1}$  と同様に、データ線  $X_k$  と書き込み走査線  $Y b_i$  の電位差、すなわち電圧  $S_1$  が書き込まれる。この電圧書き込み時においても、上記したように、各表示セルの有機 EL 素子から書き込み走査線  $Y b_i$  へと電流が流入しないため、電圧降下は生じない。

### 【0106】

一方、表示セル  $P X_{(k, i)}$  以外の表示セル内の選択 TFT は、期間  $t_1$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。但し、表示セル  $P X_{(k, i-1)}$  内のキャパシタ  $C S_{i-1}$  には、期間  $t_0$  において電圧  $S_0$  が書き込まれるために、その駆動  $TFT_{53i-1}$  はオン状態となる。ところが、書き込み走査線  $Y b_{i-1}$  は  $0 [V]$  を示しているために、有機 EL 素子  $L D_{i-1}$  に電圧は印加されず発光しない。

### 【0107】

次の期間  $t_2$  では、走査線駆動回路 60 は、選択走査線  $Y a_{i+1}$  に対して電圧  $V_2$  を供給し、選択走査線  $Y a_{i-1}$ 、 $Y a_i$ 、 $Y a_{i+2}$  および図示しないその他の選択走査線に対して負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y b_{i-1}$  にも負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y b_i \sim Y b_{i+2}$  および図示しないその他の書き込み走査線に対して接地電位 ( $0 [V]$ ) を供給する。これにより、表示セル  $P X_{(k, i+1)}$  内の選択  $TFT_{53i+1}$  のみがオン状態となり、他の選択 TFT はオフ状態となる。

### 【0108】

また、期間  $t_2$  においては、データ線駆動回路 70 によって、データ線  $X_k$  に電圧  $S_2$  が供給される。ここで、駆動  $TFT_{53i+1}$  のソースは書き込み走査線  $Y b_{i+1}$  に接続されているので、その電位は書き込み走査線  $Y b_{i+1}$  の電位、すなわち  $0 [V]$  を示す。よって、選択  $TFT_{52i+1}$  がオン状態になると、駆動  $TFT_{53i+1}$  のゲートには、駆動  $TFT_{53i+1}$  のソース - ゲート間電圧、すなわち電圧  $S_2$  が入力される。この状態は、期間  $t_0$  における表示セル  $P X_{(k, i-1)}$  の状態と同様であり、結局、ゲートに電圧  $S_2$  が供給された駆動  $TFT_{53i+1}$  はオン状態となるが、有機 EL 素子  $L D_{i+1}$  に電圧は印加されず発光しない。

### 【0109】

また、この状態において、キャパシタ  $C S_{i+1}$  には、期間  $t_0$  における表示セル  $P X_{(k, i-1)}$  のキャパシタ  $C S_{i-1}$  と同様に、データ線  $X_k$  と書き込み走査線  $Y b_{i+1}$  の電位差、すなわち電圧  $S_2$  が書き込まれる。この電圧書き込み時においても、上記したように、各表示セルの有機 EL 素子から書き込み走査線  $Y b_{i+1}$  へと電流が流入しないため、電圧降下は生じない。

### 【0110】

一方、表示セル  $P X_{(k, i+1)}$  以外の表示セル内の選択 TFT は、この期間  $t_2$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。但し、表示セル  $P X_{(k, i-1)}$  内のキャパシタ  $C S_{i-1}$  には、期間  $t_0$  において電圧  $S_0$  が書き込まれるために、その駆動  $TFT_{53i-1}$  はオン状態となる。さらに、書き込み走査線  $Y b_{i-1}$  は負の電源電圧  $-V_{dd}$  を示しているために、有機 EL 素子  $L D_{i-1}$  には電圧  $V_{dd}$  が印加され、発光し始める。

### 【0111】

また、表示セル  $P X_{(k, i)}$  内のキャパシタ  $C S_i$  には、期間  $t_1$  において電圧  $S_1$  が書き込まれるために、その駆動  $TFT_{53i}$  はオン状態となる。ところが、書き込み走

10

20

30

40

50

査線  $Y b_i$  は  $0 [V]$  を示しているために、有機 EL 素子  $L D_i$  に電圧は印加されず発光しない。

【0112】

次の期間  $t_3$  では、走査線駆動回路 60 は、選択走査線  $Y a_{i+2}$  に対して電圧  $V_2$  を供給し、選択走査線  $Y a_i \sim Y a_{i+2}$  および図示しない他の選択走査線に対して負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y b_{i-1}$  および  $Y b_i$  にも負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y b_{i+1}$ 、 $Y b_{i+2}$  および図示しない他の書き込み走査線に対して接地電位 ( $0 [V]$ ) を供給する。これにより、表示セル  $P X_{(k, i+2)}$  内の選択 TFT  $53_{i+2}$  のみがオン状態となり、他の選択 TFT はオフ状態となる。

【0113】

また、期間  $t_3$  においては、データ線駆動回路 70 によって、データ線  $X_k$  に電圧  $S_3$  が供給される。ここで、駆動 TFT  $53_{i+2}$  のソースは書き込み走査線  $Y b_{i+2}$  に接続されているので、その電位は書き込み走査線  $Y b_{i+2}$  の電位、すなわち  $0 [V]$  を示す。よって、選択 TFT  $52_{i+1}$  がオン状態になると、駆動 TFT  $53_{i+2}$  のゲートには、駆動 TFT  $53_{i+2}$  のソース - ゲート間電圧、すなわち電圧  $S_3$  が入力される。この状態は、期間  $t_0$  における表示セル  $P X_{(k, i-1)}$  の状態と同様であり、結局、ゲートに電圧  $S_3$  が供給された駆動 TFT  $53_{i+2}$  はオン状態となるが、有機 EL 素子  $L D_{i+2}$  に電圧は印加されず発光しない。

【0114】

また、この状態において、キャパシタ  $C S_{i+2}$  には、期間  $t_0$  における表示セル  $P X_{(k, i-1)}$  のキャパシタ  $C S_{i-1}$  と同様に、データ線  $X_k$  と書き込み走査線  $Y b_{i+2}$  の電位差、すなわち電圧  $S_3$  が書き込まれる。この電圧書き込み時においても、上記したように、各表示セルの有機 EL 素子から書き込み走査線  $Y b_{i+2}$  へと電流が流入しないため、電圧降下は生じない。

【0115】

一方、表示セル  $P X_{(k, i+2)}$  以外の表示セル内の選択 TFT は、この期間  $t_3$  においてはオフ状態になるので、それら表示セル内のキャパシタに電荷が保持されていない初期状態にあっては、各駆動 TFT はオフ状態であり、各有機 EL 素子も発光しない。但し、表示セル  $P X_{(k, i)}$  内の駆動 TFT  $53_{i-1}$  は、電圧  $S_0$  が書き込まれたキャパシタ  $C S_i$  によってオン状態となり、さらに、書き込み走査線  $Y b_{i-1}$  は負の電源電圧  $-V_{dd}$  を示しているために、有機 EL 素子  $L D_{i-1}$  は期間  $t_2$  に引き続いて発光を持続する。

【0116】

また、表示セル  $P X_{(k, i)}$  内のキャパシタ  $C S_i$  には、期間  $t_1$  において電圧  $S_1$  が書き込まれるために、その駆動 TFT  $53_i$  はオン状態となり、さらに、書き込み走査線  $Y b_i$  は負の電源電圧  $-V_{dd}$  を示しているために、有機 EL 素子  $L D_i$  は発光し始める。また、表示セル  $P X_{(k, i+1)}$  内のキャパシタ  $C S_{i+1}$  には、期間  $t_2$  において電圧  $S_2$  が書き込まれるために、その駆動 TFT  $53_{i+1}$  はオン状態となる。ところが、書き込み走査線  $Y b_{i+1}$  は  $0 [V]$  を示しているために、有機 EL 素子  $L D_{i+1}$  に電圧は印加されず発光しない。

【0117】

続く期間  $t_4$  以降においても、上述したような動作を繰り返す。すなわち、走査線駆動回路 70 によって選択された順に、選択走査線に電圧  $V_2$  が供給され、それに対応する書き込み走査線に負の電源電圧  $-V_{dd}$  が供給される。

【0118】

この繰り返し動作を一般的に記述すると、各表示セルは、選択走査線に電圧  $V_2$  が供給されかつ書き込み走査線に  $-V_{dd}$  が供給された状態で有機 EL 素子を発光させずにデータ電圧をキャパシタに書き込む第 1 フェーズと、選択走査線に電圧  $0 [V]$  が供給されかつ書き込み走査線に  $-V_{dd}$  が供給された状態で有機 EL 素子を発光させずにキャパシタの蓄積電圧を保持する第 2 フェーズと、選択走査線と書き込み走査線に  $-V_{dd}$  が供給された状態

10

20

30

40

50

でキャパシタの蓄積電圧に基づいて有機EL素子の発光を新たな第1フェーズまで持続させる第3フェーズといった流れで動作する。すなわち、この動作が、走査線駆動回路70によって選択された表示セルに対して順に行われる。なお、上記した各電圧間の大きさの関係は以下のとおりである。

$$V_2 > V_1 > 0 > -V_{dd}$$

#### 【0119】

以上に説明したように、実施の形態3にかかるEL表示装置およびその駆動方法によれば、各表示セルにおいて、有機EL素子に電流を流さずにキャパシタにデータ電圧を書き込むことができるよう、選択TFTのゲートとキャパシタの一端とに与える電圧が所定の関係を有して順次与えられるので、行上の表示セルの位置に応じてキャパシタの一端の電位が変動するようなことも無く、キャパシタに所望の電圧を正確に保持させることができる。すなわち、アクティブマトリクスパネル50の大画面化により行方向に位置する表示セルの数が増加しても、中央部が暗くて端に向かって明るくなるというような従来生じていた輝度ムラは発生しない。

#### 【0120】

##### (実施の形態4)

つぎに、実施の形態4にかかるEL表示装置およびその駆動方法について説明する。実施の形態4にかかるEL表示装置およびその駆動方法は、実施の形態3に説明した駆動方法に加えて、図8に示したようなパターンのパルスが書き込まれている表示セル以外の表示セルに対して他の異なるパターンのパルスを入力することで、同一パネル上においてデータの書き込みとデータの消去を同時に行うことの特徴としている。

#### 【0121】

なお、実施の形態4にかかるEL表示装置の概略構成については図6に示したとおりであるので、ここではその説明を省略する。よって、以下においては、走査線駆動回路60による駆動方法について説明する。

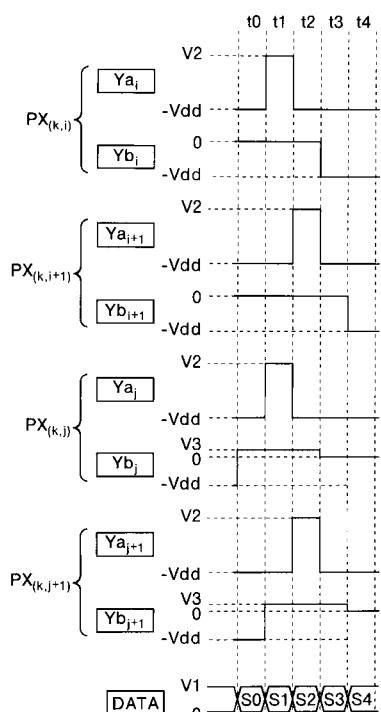

#### 【0122】

図9は、実施の形態4にかかるEL表示装置の表示セルの等価回路を示す図である。特に図9は、k列目のi行目およびi+1行目に位置する2つの表示セルPX(k, i), PX(k, i+1)と、それら表示セルから所定行数分離れたj行目およびj+1行目に位置する2つの表示セルPX(k, j), PX(k, j+1)とを表わしている。各表示セルの回路構成および符号については実施の形態3と同様であるのでここでは説明を省略する。

#### 【0123】

図10は、図9に示した等価回路において、選択走査線Ya<sub>i</sub>, Ya<sub>i+1</sub>, Ya<sub>j</sub>, Ya<sub>j+1</sub>に供給される走査線選択電圧と、書き込み走査線Yb<sub>i</sub>, Yb<sub>i+1</sub>, Yb<sub>j</sub>, Yb<sub>j+1</sub>に供給される書き込み基準電圧と、データ線X<sub>k</sub>に供給されるデータ電圧のタイミングチャートである。なお、図中の電圧V1, V2および-V<sub>dd</sub>は、実施の形態3に示したとおりの関係を有し、さらに後述する電圧V3と上記電圧V1の関係は、V3>V1である。また、以下において、表示セルPX(k, i)およびPX(k, i+1)についての各期間t0~t4の動作は、実施の形態3で説明した各期間の動作と同じなのでそれらの説明を省略し、表示セルPX(k, j)およびPX(k, j+1)内の動作、換言すれば消去対象となっている表示セルの動作について説明する。

#### 【0124】

まず、期間t0において、走査線駆動回路60は、選択走査線Ya<sub>j</sub>, Ya<sub>j+1</sub>および図示しないその他の消去処理対象の表示セルの選択走査線に負の電源電圧-V<sub>dd</sub>を供給し、書き込み走査線Yb<sub>j</sub>に対して電圧V3を供給し、書き込み走査線Yb<sub>j+1</sub>および図示しないその他の消去処理対象の表示セルの書き込み走査線に対して負の電源電圧-V<sub>dd</sub>を供給する。ここで、期間t0の直前ににおいて、表示セルPX(k, j), PX(k, j+1)および図示しないその他の消去処理対象の表示セルは発光状態にあったとする。よって、走査線駆動回路60による上記電圧の供給により、表示セルPX(k, j), PX(k, j+1)

10

20

30

40

50

$k, j+1$  内および図示しないその他の消去処理対象の表示セル内の各選択 TFT はオフ状態となる。

【0125】

また、この期間  $t_0$  においては、データ線駆動回路 70 によって、データ線  $X_k$  にデータ電圧  $S_0$  が供給される。ところが、消去処理対象の表示セル内の各選択 TFT はオフ状態であるので、それら表示セル内のキャパシタは、電圧  $S_0$  に影響されない。その一方で、それら表示セル内のキャパシタには、他の期間においてデータ電圧が書き込まれているため、キャパシタの一端に接続された書き込み走査線の電位状態に応じて、発光されるかまたは消去される。この期間  $t_0$  では、書き込み走査線  $Y_{b_j}$  はデータ電圧よりも大きな電圧  $V_3$  を示しているため、キャパシタ  $CS_j$  に書き込まれていた正の電圧は放電して表示セル  $PX_{(k, j)}$  の駆動 TFT 53j はオフ状態となり、有機 EL 素子  $LD_j$  は消灯する。また、書き込み走査線  $Y_{b_{j+1}}$  は負の電源電圧  $-V_{dd}$  を示しているため、表示セル  $PX_{(k, j+1)}$  の駆動 TFT 53j+1 のゲートには、キャパシタ  $CS_{j+1}$  の蓄積電圧が与えられ、有機 EL 素子  $LD_{j+1}$  は発光を持続する。

10

【0126】

次の期間  $t_1$  では、走査線駆動回路 60 は、選択走査線  $Y_{a_j}$  に電圧  $V_2$  を供給し、選択走査線  $Y_{a_{j+1}}$  および図示しないその他の消去処理対象の表示セルの選択走査線に負の電源電圧  $-V_{dd}$  を供給し、書き込み走査線  $Y_{b_j}$  および  $Y_{b_{j+1}}$  に対して電圧  $V_3$  を供給し、図示しないその他の消去処理対象の表示セルの書き込み走査線に対して負の電源電圧  $-V_{dd}$  を供給する。これにより、表示セル  $PX_{(k, j)}$  の選択 TFT 52j はオン状態となり、表示セル  $PX_{(k, j+1)}$  の選択 TFT 52j+1 はオフ状態となる。

20

【0127】

また、期間  $t_1$  においては、データ線駆動回路 70 によって、データ線  $X_k$  に電圧  $S_1$  が供給される。ここで、駆動 TFT 53j のソースは書き込み走査線  $Y_{b_j}$  に接続されているので、その電位は書き込み走査線  $Y_{b_j}$  の電位、すなわち電圧  $V_3$  を示す。よって、選択 TFT 52j がオン状態になると、キャパシタ  $CS_j$  と駆動 TFT 53j のゲートには、負の電圧  $S_1 - V_3$  が入力される。よって、駆動 TFT 53j はオフ状態となり、有機 EL 素子  $LD_j$  は消灯状態を維持する。また、キャパシタ  $CS_j$  には負の電圧  $S_1 - V_3$  が書き込まれる。

30

【0128】

一方、選択 TFT 52j+1 はオフ状態であるが、書き込み走査線  $Y_{b_{j+1}}$  はデータ電圧よりも大きな電圧  $V_3$  を示しているため、キャパシタ  $CS_{j+1}$  に書き込まれていた正の電圧は放電し、表示セル  $PX_{(k, j+1)}$  の駆動 TFT 53j+1 はオフ状態となる。すなわち、有機 EL 素子  $LD_{j+1}$  は消灯する。

【0129】

次の期間  $t_2$  では、走査線駆動回路 60 は、選択走査線  $Y_{a_j}$  および図示しないその他の消去処理対象の表示セルの選択走査線に負の電源電圧  $-V_{dd}$  を供給し、選択走査線  $Y_{a_{j+1}}$  に電圧  $V_2$  を供給し、書き込み走査線  $Y_{b_j}$  および  $Y_{b_{j+1}}$  に対して電圧  $V_3$  を供給し、図示しないその他の消去処理対象の表示セルの書き込み走査線に対して負の電源電圧  $-V_{dd}$  を供給する。これにより、表示セル  $PX_{(k, j)}$  の選択 TFT 52j はオフ状態となり、表示セル  $PX_{(k, j+1)}$  の選択 TFT 52j+1 はオン状態となる。

40

【0130】

また、期間  $t_2$  においては、データ線駆動回路 70 によって、データ線  $X_k$  に電圧  $S_2$  が供給される。ここで、駆動 TFT 53j+1 のソースは書き込み走査線  $Y_{b_{j+1}}$  に接続されているので、その電位は書き込み走査線  $Y_{b_{j+1}}$  の電位、すなわち電圧  $V_3$  を示す。よって、選択 TFT 52j+1 がオン状態になると、キャパシタ  $CS_{j+1}$  と駆動 TFT 53j+1 のゲートには、負の電圧  $S_2 - V_3$  が入力される。よって、駆動 TFT 53j+1 はオフ状態となり、有機 EL 素子  $LD_{j+1}$  は消灯状態を維持する。また、キャパシタ  $CS_{j+1}$  には負の電圧  $S_2 - V_3$  が書き込まれる。

【0131】

50

一方、選択 T F T 5 2<sub>j</sub> はオフ状態であるが、期間 t<sub>1</sub>においてキャパシタ C S<sub>j</sub> に負の電圧 S<sub>1</sub> - V<sub>3</sub> が書き込まれているため、駆動 T F T 5 3<sub>j</sub> はオフ状態のままであり、有機 E L 素子 L D<sub>j</sub> は消灯状態を維持する。

#### 【 0 1 3 2 】

次の期間 t<sub>3</sub>では、走査線駆動回路 6 0 は、選択走査線 Y a<sub>j</sub>、Y a<sub>j+1</sub> および図示しないその他の消去処理対象の表示セルの選択走査線に負の電源電圧 - V<sub>d\_d</sub> を供給し、書き込み走査線 Y b<sub>j</sub> に 0 [V] を供給し、書き込み走査線 Y b<sub>j+1</sub> に対して電圧 V<sub>3</sub> を供給し、図示しないその他の消去処理対象の表示セルの書き込み走査線に対して負の電源電圧 - V<sub>d\_d</sub> を供給する。これにより、表示セル P X<sub>(k, j)</sub> の選択 T F T 5 2<sub>j</sub> と表示セル P X<sub>(k, j+1)</sub> の選択 T F T 5 2<sub>j+1</sub> はともにオフ状態となる。

10

#### 【 0 1 3 3 】

また、期間 t<sub>3</sub>においては、データ線駆動回路 7 0 によって、データ線 X<sub>k</sub> にデータ電圧 S<sub>3</sub> が供給される。ところが、消去処理対象の表示セル内の各選択 T F T はオフ状態であるので、それら表示セル内のキャパシタは、電圧 S<sub>3</sub> に影響されない。その一方で、表示セル P X<sub>(k, j)</sub> 内のキャパシタ C S<sub>j</sub> には、期間 t<sub>1</sub>において負の電圧 S<sub>1</sub> - V<sub>3</sub> が書き込まれているため、駆動 T F T 5 3<sub>j</sub> はオフ状態のままであり、有機 E L 素子 L D<sub>j</sub> は消灯状態を維持する。同様に、表示セル P X<sub>(k, j+1)</sub> 内のキャパシタ C S<sub>j+1</sub> には、期間 t<sub>2</sub>において負の電圧 S<sub>2</sub> - V<sub>3</sub> が書き込まれているため、駆動 T F T 5 3<sub>j+1</sub> はオフ状態のままであり、有機 E L 素子 L D<sub>j+1</sub> は消灯状態を維持する。

20

#### 【 0 1 3 4 】

続く期間 t<sub>4</sub>以降においては、各表示セルに対して順次、上述した動作と同様な動作が繰り返される。すなわち、各表示セルは、実施の形態 3 で説明したように、ある位置の選択走査線に位置する表示セルから順に、その選択走査線上での電圧降下を生じさせることなく、発光させることができるとともに、同一のアクティブマトリクスパネル上の他の選択走査線に位置する表示セルから順に、データの消去を行う。

20

#### 【 0 1 3 5 】

以上に説明したように、実施の形態 4 にかかる E L 表示装置およびその駆動方法によれば、実施の形態 3 で説明した駆動方法に加え、発光のための電圧書き込みが行われていない走査線上の表示セルに対して、順次、そのキャパシタへ負の電圧を書き込むので、アクティブマトリクスパネル 5 0 上において同時にデータ表示とデータの消去を実行することができる。特に、そのデータの消去動作においては、駆動 T F T のソース - ゲート間に逆電圧を印加することになるので、駆動 T F T の閾値電圧シフトを抑制することもできる。

30

#### 【 0 1 3 6 】

##### ( 実施の形態 5 )

つぎに、実施の形態 5 にかかる E L 表示装置およびその駆動方法について説明する。実施の形態 5 にかかる E L 表示装置およびその駆動方法は、図 15 ( a ) に示したような共通線を有する従来構造において、各表示セルにおける共通線の電圧降下を予測し、その予測結果に応じてデータ電圧の大きさを調整することを特徴としている。

#### 【 0 1 3 7 】

図 11 は、実施の形態 5 にかかる E L 表示装置の駆動方法を説明するための説明図である。特に、同図 ( a ) は、アクティブマトリクスパネルの第 i 行目の表示セル列を示す図であり、同図 ( b ) は、各表示セルに供給するデータ電圧を示す図である。

40

#### 【 0 1 3 8 】

各表示セルから共通線 3 1 に流れ込む電流をそれぞれ i<sub>1</sub>, i<sub>2</sub>, ..., i<sub>p</sub>, ..., i<sub>m</sub> とすると、p 番目の画素までの共通線 3 1 の表示セル間の電圧降下を共通線 3 1 の左端から加算した電圧 ( V<sub>s, p</sub> ) は、k 番目の表示セル P X<sub>(p, i)</sub> の共通線 3 1 における電位となり、以下に示す式 ( 1 ) のように表わされる。

#### 【 0 1 3 9 】

##### ( 数 1 )

$$V_{s,p} = r \sum_{j=1}^p \left( \sum_{k=j}^m i_{L,k} - \sum_{k=1}^{j-1} i_{R,k} \right) \quad (1)$$

ここで、 $r$  は、表示セル間の配線抵抗の抵抗値を表わす。

【0140】

また、

【数2】

$$i_{L,k} = \frac{n+1-k}{n+1} i_k, \quad i_{R,k} = \frac{k}{n+1} i_k \quad (2)$$

であり、 $i_{L,k}$  は表示セル  $PX(p, i)$  から共通線 31 の左側に向かって流れる電流を表わし、 $i_{R,k}$  は表示セル  $PX(p, i)$  から共通線 31 の右側に向かって流れる電流を表わす。

【0141】

よって、共通線 31 に電圧降下が生じない状態、すなわち共通線 31 が接地電位である場合と、上記した電圧降下によって結果的に共通線 31 の電位が上昇してしまった場合との駆動 TFT のドレイン - ソース間電圧のずれ  $V_{ds,m}$  は、

【数3】

$$\delta V_{ds,p} = V'_{ds,p} - V_{ds,p} = (V_{d,p} - V_{s,p}) - (V_{d,p} - 0) = -V_{s,p} \quad (3)$$

として表わすことができる。ここで、 $V_{d,p}$  は駆動 TFT のドレイン電位を表わし、 $V_{s,p}$  は駆動 TFT のソース電位を表わす。

【0142】

すなわち、各表示セルの有機 EL 素子には、本来よりも上記ずれ  $V_{ds,m}$  分だけ電圧が少なく印加され、その結果、有機 EL 素子に流れる電流が減少して輝度が低下することになる。よって、この電流の減少を補った電圧（以下、補償電圧と称する。） $V'_{gs}$  を本来の電圧  $V_{gs}$  に換えて駆動 TFT のゲートに印加すれば、上記した電圧降下による有機 EL 素子の輝度低下を補償することが可能になる。ここで、有機 EL 素子の印加電圧の減少分を  $V_{ds}$ 、駆動 TFT のコンダクタンスを  $g_m$ 、出力抵抗を  $r_D$  とすると、駆動 TFT に流れる電流の変化 ( $I_{ds}$ ) は、以下に示す式 (4) のように表わされる。

【0143】

【数4】

$$\delta I_{ds} = \frac{\partial I_{ds}}{\partial V_{gs}} \delta V_{gs} + \frac{\partial I_{ds}}{\partial V_{ds}} \delta V_{ds} = g_m \cdot \delta V_{gs} + \frac{1}{r_D} \delta V_{ds} \quad (4)$$

【0144】

よって、 $I_{ds} = 0$  より、

【数5】

$$\delta V_{gs} = -\frac{1}{r_D \cdot g_m} \cdot \delta V_{ds} \quad (5)$$

と表わすことができる。

【0145】

ここで、表示セル  $P X_{(p, i)}$  の駆動 TFT のゲートに与えられる本来の電圧  $V_{gs, p}$  とし、補償電圧を  $V'_{gs, p}$  とすると、

【数6】

$$\begin{aligned} V'_{gs, p} &= V_{gs, p} + \delta V_{gs, p} = V_{gs, p} - \frac{\delta V_{ds, p}}{r_D \cdot g_m} \\ &= V_{gs, p} + \frac{r}{r_D \cdot g_m} \sum_{j=1}^p \left( \sum_{k=j}^m i_{L, k} - \sum_{k=1}^{j-1} i_{R, k} \right) \end{aligned} \quad (6)$$

10

と表わすことができる。

【0146】

よって、データ線駆動回路が、表示セル  $P X_{(p, i)}$  の駆動 TFT のゲートにこの補償電圧  $V'_{gs, p}$  が与えられるようにデータ電圧を増加すれば、所望の輝度の発光を得ることができる。表示セル  $P X_{(p, i)}$  以外の各表示セルについても、上記式(6)において、 $p$  の値を表示セルの列位置に対応させることでそれぞれ補償電圧を得ることができる。すなわち、データ線駆動回路は、図11(b)に示すように式(6)で与えられる補償電圧に基づいてデータ電圧を調整することにより、行全体にわたる表示セルの有機EL素子を所望の輝度で発光させることができる。

20

【0147】

以上に説明したように、実施の形態5にかかるEL表示装置およびその駆動方法によれば、共通線を有する従来のアクティブマトリクスパネルの構造において、共通線の電圧降下に起因する各有機EL素子の印加電圧の低下を補償する補償電圧を予測し、データ線駆動回路が、その予測値に基づいてデータ電圧の大きさを調整するので、アクティブマトリクスパネルの大画面化により行方向に位置する表示セルの数が増加しても、中央部が暗くて端に向かって明るくなるという従来生じていた輝度ムラは発生しない。

20

【0148】

なお、以上に説明した実施の形態1~5では、有機EL素子のアノード側に電源電圧  $V_d$  の供給線が接続された、いわゆるアノードコモン型の表示セルを示したが、図12に示すように、有機EL素子のカソード側に走査線または共通線が接続された、いわゆるカソードコモン型の表示セルを採用しても上記同様の効果を得ることができる。

30

【0149】

また、以上に説明した実施の形態1~5では、自発光素子として有機EL素子を例に挙げたが、有機EL素子に換えて、無機EL素子や発光ダイオード等の他のエレクトロルミネッセンス素子を用いた場合でも、上記同様の効果を得ることができる。

30

【0150】

【発明の効果】

以上に説明したように、本発明にかかるEL表示装置およびその駆動方法によれば、キャパシタの一端と駆動トランジスタのソースを、それらを含む表示セルの下位の行を選択するための走査線に接続するので、従来必要であった共通線を排除することができ、さらには、表示セル内のキャパシタの一端の電位をその走査線に入力される電圧  $V_1$  に固定しつつEL素子に電流を流さない状態で、データ電圧をそのキャパシタに書き込むので、行上の表示セルの位置に応じてキャパシタの一端の電位が変動するようなことも無く、キャパシタに所望の電圧を正確に保持させることができるという効果を奏する。

40

【0151】

また、本発明にかかるEL表示装置およびその駆動方法によれば、上記発明の効果に加え、発光のための電圧書き込みが行われていない走査線の表示セルに対して、順次、そのキャパシタへ負の電圧を書き込むことになるので、アクティブマトリクスパネル上において同時にデータ表示とデータの消去を実行することができるという効果を奏する。

50

## 【0152】

また、本発明にかかるEL表示装置およびその駆動方法によれば、各表示セルのキャパシタに対して、選択トランジスタを駆動させる選択走査線とは独立した書き込み走査線によって所定の電位に固定しあつEL素子に電流を流さない状態で、データ電圧をそのキャパシタに書き込むので、行上の表示セルの位置に応じてキャパシタの一端の電位が変動するようなことも無く、キャパシタに所望の電圧を正確に保持させることができるという効果を奏する。

## 【0153】

また、本発明にかかるEL表示装置およびその駆動方法によれば、上記発明の効果に加え、発光のための電圧書き込みが行われていない書き込み走査線の表示セルに対して、順次、そのキャパシタへ負の電圧を書き込むので、アクティブマトリクスパネル上において同時にデータ表示とデータの消去を実行することができるという効果を奏する。

## 【0154】

また、本発明にかかるEL表示装置およびその駆動方法によれば、共通線を有する従来のアクティブマトリクスパネルの構造において、共通線の電圧降下に起因する各EL素子の印加電圧の低下を補償する補償電圧を予測し、データ線駆動回路が、その予測値に基づいてデータ電圧の大きさを調整するので、アクティブマトリクスパネルの大画面化により行方向に位置する表示セルの数が増加しても、中央部が暗くて端に向かって明るくなるというような従来生じていた輝度ムラを解消することができるという効果を奏する。

## 【図面の簡単な説明】

【図1】実施の形態1にかかるEL表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。

【図2】実施の形態1にかかるEL表示装置の表示セルの等価回路を示す図である。

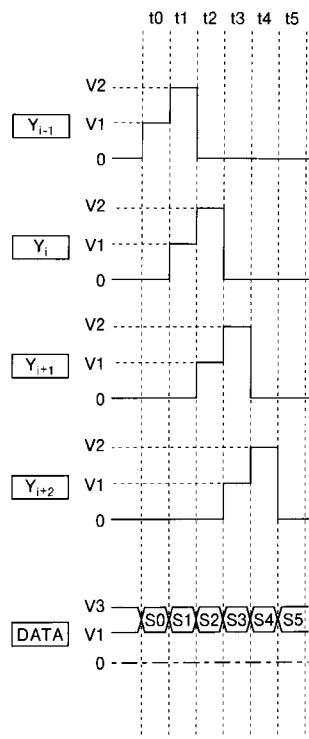

【図3】実施の形態1にかかるEL表示装置の表示セルの等価回路において、走査線 $Y_{i-1} \sim Y_{i+2}$ に供給される走査線選択電圧とデータ線 $X_k$ に供給されるデータ電圧のタイミングチャートである。

【図4】実施の形態2にかかるEL表示装置の表示セルの等価回路を示す図である。

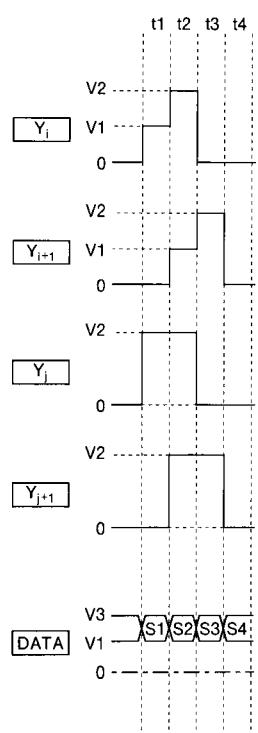

【図5】実施の形態2にかかるEL表示装置の表示セルの等価回路において、走査線 $Y_i, Y_{i+1}, Y_j, Y_{j+1}$ に供給される走査線選択電圧とデータ線 $X_k$ に供給されるデータ電圧のタイミングチャートである。

【図6】実施の形態3にかかるEL表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。

【図7】実施の形態3にかかるEL表示装置の表示セルの等価回路を示す図である。

【図8】実施の形態3にかかるEL表示装置の表示セルの等価回路において、選択走査線に供給される走査線選択電圧と書き込み走査線に供給される書き込み基準電圧とデータ線 $X_k$ に供給されるデータ電圧のタイミングチャートである。

【図9】実施の形態4にかかるEL表示装置の表示セルの等価回路を示す図である。

【図10】実施の形態4にかかるEL表示装置の表示セルの等価回路において、選択走査線に供給される走査線選択電圧と書き込み走査線に供給される書き込み基準電圧とデータ線 $X_k$ に供給されるデータ電圧のタイミングチャートである。

【図11】実施の形態5にかかるEL表示装置の駆動方法を説明するための説明図である。

【図12】実施の形態1～5において置換可能なカソードコモン型の表示セルの等価回路を示す図である。

【図13】従来の有機EL表示装置の概略構成のうち、アクティブマトリクスパネルと駆動回路を示す図である。

【図14】特許文献2に開示された一実施例を説明するための表示セルの等価回路を示す図である。

【図15】(a)は、アクティブマトリクスパネル100の第i行目の表示セル列を示す図であり、(b)は、共通線における電圧降下を説明するための説明図である。

10

20

30

40

50

## 【符号の説明】

1 0 , 5 0 , 1 0 0 アクティプマトリクスパネル

1 1 , 5 1 , 1 1 0 表示セル

1 2 <sub>i - 1</sub> , 1 2 <sub>i</sub> , 1 2 <sub>i + 1</sub> , 1 2 <sub>j</sub> , 1 2 <sub>j + 1</sub> , 1 2 <sub>i - 1</sub> , 5 2 <sub>i</sub> , 5 2 <sub>i + 1</sub> , 5 2 <sub>j</sub> , 5 2 <sub>j + 1</sub> 選択 TFT

1 3 <sub>i - 1</sub> , 1 3 <sub>i</sub> , 1 3 <sub>i + 1</sub> , 1 3 <sub>j</sub> , 1 3 <sub>j + 1</sub> , 5 3 <sub>i - 1</sub> , 5 3 <sub>i</sub> , 5 3 <sub>i + 1</sub> , 5 3 <sub>j</sub> , 5 3 <sub>j + 1</sub> 駆動 TFT

2 0 , 6 0 , 1 2 0 走査線駆動回路

3 0 , 7 0 , 1 3 0 データ線駆動回路

3 1 共通線

3 6 n チャネル型 TFT

3 7 p チャネル型 TFT

3 8 有機薄膜EL素子

3 9 容量

4 0 電源電極

4 1 走査線

4 2 信号線

L D <sub>i - 1</sub> , L D <sub>i</sub> , L D <sub>i + 1</sub> , L D <sub>j</sub> , L D <sub>j + 1</sub> 有機EL素子

C S <sub>i - 1</sub> , C S <sub>i</sub> , C S <sub>i + 1</sub> , C S <sub>j</sub> , C S <sub>j + 1</sub> キャパシタ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

| F I          | テーマコード(参考) |

|--------------|------------|

| G 09 G 3/20  | 6 2 2 D    |

| G 09 G 3/20  | 6 2 2 Q    |

| G 09 G 3/20  | 6 2 3 R    |

| G 09 G 3/20  | 6 2 4 B    |

| G 09 G 3/20  | 6 4 1 C    |

| G 09 G 3/20  | 6 4 1 P    |

| G 09 G 3/20  | 6 4 2 A    |

| H 05 B 33/14 | A          |

F ターム(参考) 5C080 AA06 BB05 DD05 EE28 FF11 JJ02 JJ03 JJ04

5C094 AA03 AA10 AA13 BA03 BA27 CA19 EA04 EA07 FB19 GA10

HA08

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | EL显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2004170815A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2004-06-17 |

| 申请号            | JP2002338525                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2002-11-21 |

| [标]申请(专利权)人(译) | 群创光电股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 奇美电子股▲ふん▼有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 小林芳直<br>小野晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 小林 芳直<br>小野 晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/10 G09G3/20 G09G3/30 G09G3/32 H01L27/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0465 G09G2300/0842 G09G2300/0866 G09G2300/0876 G09G2310/0254<br>G09G2310/0262 G09G2320/0223 G09G2320/0233 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/30.J G09F9/30.338 G09F9/30.365.Z G09G3/20.611.J G09G3/20.622.C G09G3/20.622.D<br>G09G3/20.622.Q G09G3/20.623.R G09G3/20.624.B G09G3/20.641.C G09G3/20.641.P G09G3/20.642.<br>A H05B33/14.A G09F9/30.365 G09G3/3233 G09G3/3266 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD05 5C080<br>/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C094/AA03 5C094/AA10 5C094/AA13<br>5C094/BA03 5C094/BA27 5C094/CA19 5C094/EA04 5C094/EA07 5C094/FB19 5C094/GA10 5C094<br>/HA08 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 3K107/HH05<br>5C380/AA01 5C380/AB06 5C380/AB46 5C380/BA12 5C380/BA19 5C380/BA28 5C380/BB03 5C380<br>/BD08 5C380/BD10 5C380/CA12 5C380/CB01 5C380/CB02 5C380/CB19 5C380/CB20 5C380/CB31<br>5C380/CC02 5C380/CC08 5C380/CC26 5C380/CC33 5C380/CC41 5C380/CC42 5C380/CC62 5C380<br>/CC63 5C380/CD012 5C380/CE04 5C380/CF17 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA03<br>5C380/HA05 |         |            |

| 代理人(译)         | 酒井宏明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | <a href="#">JP4409821B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

解决的问题：提供一种即使对于电压写入型大屏幕有源矩阵面板也能够将期望的电压准确地写入每个显示单元的电容器的EL显示装置及其驱动方法。消除公共线，常规上连接到公共线的电容器的一端连接到与包括该电容器的显示单元相邻的另一显示单元的扫描线，并且驱动扫描线。电路20向每条扫描线提供由电压V1和足够大于电压V1的电压V2形成的阶梯状脉冲。此外，数据线驱动电路30向每条数据线提供等于或高于电压V1且等于或低于电压V3（但是，小于电压V2）的电压作为数据电压。

[选型图]图1