(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5665256号

(P5665256)

(45) 発行日 平成27年2月4日(2015.2.4)

(24) 登録日 平成26年12月19日(2014.12.19)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| G09G 3/30 (2006.01)  | G09G 3/30 J    |

| G09G 3/20 (2006.01)  | G09G 3/20 611H |

| H01L 51/50 (2006.01) | G09G 3/20 624B |

|                      | G09G 3/20 641D |

|                      | G09G 3/20 670J |

請求項の数 5 (全 29 頁) 最終頁に続く

|              |                               |           |                                            |

|--------------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2007-292109 (P2007-292109)  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成19年11月9日 (2007.11.9)        | (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65) 公開番号    | 特開2008-176287 (P2008-176287A) | (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (43) 公開日     | 平成20年7月31日 (2008.7.31)        | (72) 発明者  | 安部 勝美<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

| 審査請求日        | 平成22年11月2日 (2010.11.2)        |           |                                            |

| (31) 優先権主張番号 | 特願2006-342578 (P2006-342578)  |           |                                            |

| (32) 優先日     | 平成18年12月20日 (2006.12.20)      |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

|              |                               | 審査官       | 武田 悟                                       |

最終頁に続く

(54) 【発明の名称】発光表示デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を備える発光表示デバイスであつて、

前記画素は、アノード端子及びカソード端子を有し、かつ供給される電流で決まる輝度

で発光する発光素子と、データ線から供給される制御電圧に基づいて前記発光素子に電流

を供給する駆動回路と、を備え、

前記駆動回路は、前記発光素子を駆動し、かつゲート端子、ソース端子、及びドレイン

端子を有する駆動用トランジスタと、容量素子と、を備え、

前記駆動用トランジスタは、前記ゲート端子が第一のスイッチ素子を経由して前記ソ

ース端子と接続され、前記ソース端子が第五のスイッチ素子を経由して前記発光素子のア

ノード端子と接続されかつ第四のスイッチを経由して参照電圧線又は前記ドレイン端子と接

続され、前記ドレイン端子が電源線に接続され、

前記容量素子の一端は直接前記駆動用トランジスタのゲート端子に接続され、前記容量

素子の他の一端は第二のスイッチ素子を経由して前記駆動用トランジスタのソース端子に接

続され、かつ第三のスイッチを経由して前記データ線に接続されており、

前記第一のスイッチと前記第三のスイッチが導通し、前記第二のスイッチと前記第五の

スイッチが非導通になり、前記第四のスイッチが導通したのち非導通となることにより、

前記容量素子が、前記駆動用トランジスタのドレイン端子の電圧から前記データ線から供

給される制御電圧を減算した電圧に、前記駆動用トランジスタのしきい値電圧を加えた電

圧を保持し、

前記駆動回路が前記発光素子へ電流を供給する期間に、前記第四のスイッチが非導通の状態のまま、前記第二のスイッチと前記第五のスイッチが導通し、前記第一のスイッチと前記第三のスイッチが非導通になり、前記容量素子に保持された電圧を前記駆動用トランジスタのゲート端子とソース端子との電圧差とすることを特徴とする発光表示デバイス。

**【請求項 2】**

前記参照電圧線の電圧は、前記駆動用トランジスタのソース端子と前記ドレイン端子との電圧差を前記駆動トランジスタのしきい値電圧より大きくする電圧であることを特徴とする請求項 1 に記載の発光表示デバイス。

**【請求項 3】**

前記電源線に供給する電圧を変動する手段をさらに備え、前記駆動回路が前記発光素子へ電流を供給する期間に前記電源線に供給する電圧を、前記容量素子に前記駆動用トランジスタのドレイン端子に印加される電圧から前記データ線から供給される制御電圧を減算した電圧に、前記駆動用トランジスタのしきい値電圧を加えた電圧を保持する期間に前記電源線に供給する電圧よりも高くすることを特徴とする請求項 1 または 2 に記載の発光表示デバイス。10

**【請求項 4】**

前記発光素子が、有機 E L 素子であることを特徴とする請求項 1 乃至 3 のいずれか一項に記載の発光表示デバイス。

**【請求項 5】**

前記駆動用トランジスタが、キャリア密度が  $10^{18}$  ( $\text{cm}^{-3}$ ) 以下である n 型の金属酸化物アモルファス半導体膜をチャネル層として用い、移動度が  $1$  ( $\text{cm}^2/\text{Vs}$ ) 以上、かつ、オンオフ比が  $10^6$  以上であることを特徴とする請求項 1 乃至 4 のいずれか一項に記載の発光表示デバイス。20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、発光表示デバイスに係り、特に発光素子として有機エレクトロルミネッセンス (Electro-Luminescence、以下 E L ) 素子を用いた発光表示デバイスに関する。より詳細には、本発明は、有機 E L 素子と共に電流を供給するための駆動回路とで構成される画素をマトリックス状に備えた発光表示デバイスに関する。30

**【背景技術】**

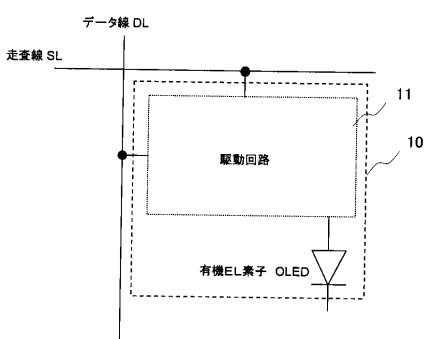

**【0002】**

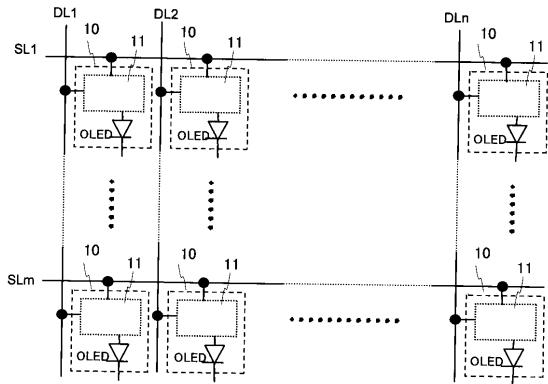

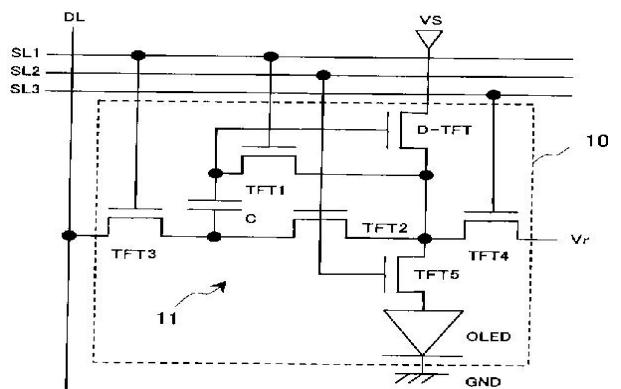

従来、有機 E L 素子と駆動回路で構成される画素をマトリックス状に備えた発光表示デバイスとして、アクティブマトリックス (Active-Matrix、以下 A M ) 型有機 E L ディスプレイが検討されている。この一例を図 8 及び図 9 に示す。

**【0003】**

図 8 及び図 9 は、A M 型有機 E L ディスプレイの画素内の構成及びその画素配置をそれぞれ示す。図 8 に示すように、画素 1 0 には、有機 E L 素子 O L E D と、そのアノード端子に接続されたアクティブ素子を有する駆動回路 1 1 とが設けられている。駆動回路 1 1 は、データ線 D L と、走査線 S L とにそれぞれ接続される。図の例では、走査線 S L が 1 種類の場合を示す。このように有機 E L 素子 O L E D と駆動回路 1 1 とで構成された画素 1 0 は、図 9 に示すようにマトリックス状 ( $m$  行  $\times$   $n$  列) に複数配置され、1 行目から  $m$  行目の走査線 S L 1 から S L  $m$  と 1 列目から  $n$  列目のデータ線 D L 1 から D L  $n$  とにそれぞれ接続されている。40

**【0004】**

このような構成の A M 型有機 E L ディスプレイは、データ線を介して各画素の駆動回路に印加される電圧又は電流信号に従って、駆動回路内のアクティブ素子により有機 E L 素子へ供給する電圧、電流等を制御する。こうすることで、有機 E L 素子の輝度を調節し、階調表示を行う。駆動回路の構成要素であるアクティブ素子としては、通常、薄膜トランジスタ (Thin-Film-Transistor : T F T ) が用いられている (特許50

文献 1 - 4、非特許文献 1)。

【特許文献 1】特表 2002-517806 号公報

【特許文献 2】特開 2001-147659 号公報

【特許文献 3】特開 2004-093777 号公報

【特許文献 4】特開 2005-189379 号公報

【非特許文献 1】J. H. Jung et al., SID 05 DIGEST 49

. 1 Fig. 1

【発明の開示】

【発明が解決しようとする課題】

【0005】

前記 A M 型有機 E L ディスプレイにおいて、有機 E L 素子の電圧 - 輝度特性の経時変化が課題となっている。また、駆動回路の構成要素である薄膜トランジスタ（以下、T F T）の特性ばらつき、電気的ストレスによるT F T の特性変化も同様に課題となっている。このように特性が変化する、或いはばらつく場合、同一信号を駆動回路に印加しても、有機 E L 素子の輝度が変わる。そのため、表示にムラ、輝点、暗点などが現れる。従って、高品質な表示を実現するには、有機 E L 素子特性の経時変化やT F T の特性ばらつき・変化の影響を受けにくい駆動回路・駆動方法の開発が必要である。

【0006】

上記駆動回路のこのような課題に対して、従来技術として、特許文献 1、2 が提案されている。

【0007】

特許文献 1 では、まず、有機 E L 素子に電流を供給する駆動（p 型）T F T に、画素外部より有機 E L 素子の発光輝度に相当する電流を供給して、その電流が流れるゲート端子 - ソース端子間電圧を保持させる。引き続き、T F T より、保持したゲート端子 - ソース端子間電圧により決まる電流を有機 E L 素子に供給することで有機 E L 素子が発光する。本例では、発光輝度に相当する電流を流すゲート端子 - ソース端子間電圧を保持し、T F T は定電流源として働くため、駆動 T F T の特性がばらついた場合でも、有機 E L 素子に供給する電流がばらつかない。

【0008】

特許文献 2 では、カレントミラー構成をとる 2 つの T F T の内、1 つが有機 E L 素子に電流を供給する駆動（p 型）T F T であり、他の一つが有機 E L 素子の発光輝度に相当する電流が、画素外部より供給される負荷（p 型）T F T である。まず、画素外部より電流を供給して、その電流が負荷 T F T に流れるゲート端子 - ソース端子間電圧を保持させる。引き続き、保持したゲート端子 - ソース端子間電圧により決まる電流を駆動 T F T が有機 E L 素子に供給することで有機 E L 素子が発光する。T F T の特性が位置によってばらついても、駆動 T F T と負荷 T F T が近接にあり、同一特性を示すことから、特許文献 1 と同様に、有機 E L 素子に供給する電流がばらつかない。

【0009】

T F T のチャネル層の材料として、多結晶シリコン（以下 p - S i と記す）、非晶質シリコン（以下 a - S i と記す）、有機半導体（以下 O S と記す）、金属酸化物半導体等の半導体が検討されている。ここで、p - S i は polycrystalline-Si、a - S i は amorphous-Si、O S は Organic Semiconductor である。

【0010】

p - S i T F T は、移動度が高く、動作電圧を低くできるが、結晶粒界のために特性ばらつきが大きくなりやすく、また製造コストが高くなる。一方、a - S i や、O S T F T は、p - S i T F T に比べ移動度が低いために、動作電圧が高く、消費電力が大きいが、製造ステップ数が少なく、製造コスト抑えることが可能である。また、酸化亜鉛（Z n O ）などの金属酸化物半導体をチャネル層として用いる T F T は、近年、開発が進められており、a - S i や、O S T F T よりも高い移動度、かつ、低コストの可能性が報

10

20

30

40

50

告されている。

【0011】

ただし、a-Si、OS、金属酸化物半導体TFTは、p-Si TFTと異なり、n型TFTとp型TFTを同一基板上に形成する相補型TFTとすることは難しい。例えば、a-Siや金属酸化物では高移動度のp型半導体というのが得られておらず、p型TFTの形成が困難である。また、OSでは、高移動度のn型半導体とp型半導体の材料が異なるために、工程が2倍となり、安価な製造が難しくなる。従って、これらのTFTを用いた駆動回路は、n型あるいはp型のTFTのみで構成する必要がある。

【0012】

また、a-Si、OS、金属酸化物をチャネル層とするTFTは、長時間電圧を印加することによって、電流・電圧特性が変動するため、何らかの手法によってその変動を補償する必要がある。

【0013】

一方、有機EL素子は、一般に、アノード電極とカソード電極の間に、少なくとも有機材料による発光層が挟まれた構造を有し、有機材料は、熱や電磁波、水分などの影響を受け特性変化を起こしやすい。このため、有機EL素子を用いた発光表示デバイスは、駆動回路やアノード電極作成後に、有機材料発光層を形成し、ダメージの少ない真空蒸着などによりカソード電極を作成するという製造過程が好ましい。

【0014】

そこで、AM型有機ELディスプレイを、n型TFTで構成される駆動回路と、下からアノード電極、有機発光層、カソード電極という順で形成される有機EL素子と、により画素を構成する場合を考える。この場合、特許文献1、2の駆動回路のp型TFTをn型TFTに置き換えただけでは実現できない。なぜなら、特許文献1、2において、p型TFTをn型TFTに置き換えると、ゲート端子 - ドレイン端子間が固定されることになるため、定電流源として機能しないためである。従って、特許文献1、2と異なる駆動回路構成とする必要がある。

【0015】

特許文献3の図2に提案されている駆動回路は、n型TFTのみで、特性ばらつきや特性変動の影響を抑えるための技術である。この駆動回路は、有機EL素子を駆動するn型TFT(駆動TFT)のゲート端子 - ソース端子間に容量を備える。有機EL素子を駆動する電流を設定する期間には、TFTのゲート端子 - ドレイン端子間を導通し、有機EL素子への経路を遮断し、かつ、外部から電流を供給する。この時、ゲート端子 - ソース端子間の電圧は、外部から供給される電流が流れる電圧(設定電圧)となる。有機EL素子を駆動する期間には、n型TFTは、設定電圧に従って、有機EL素子に電流を供給する定電流源として機能する。

【0016】

近年、有機EL素子の電流・輝度特性の向上がすすみ、有機EL素子への供給電流が低下している。また、有機ELディスプレイは、より大型・高精細のものが求められており、配線負荷が増大する傾向にある。従って、特許文献3において、低階調に相当する低い電流を外部から供給する場合、配線負荷を充電するための時間が長くなる。従って、高精細、大画面の表示装置に、特許文献3の駆動回路を適用することは難しい。

【0017】

例えば、大画面の表示装置の配線負荷を容量40pF、抵抗5k(時定数0.2μsec)とし、外部から供給される電流を設定するのに必要な電圧変動を3Vとすると、充電すべき電荷量は120pCとなる。これを低階調に相当する10nAの電流で充電するためには、12msの時間が必要である。一方、高精細テレビの走査線(1250)を60Hzで駆動する際には、1走査線当たりの選択期間は13μsecとなり、充電することは不可能である。

【0018】

上記の課題を解決する手段が、特許文献3の図1に提案されている。この駆動回路では

10

20

30

40

50

、充電電流を10倍程度まで増やすことができる。しかし、その場合、充電期間は、1.2 msecから1.2 msecに短縮することができるが、高精細テレビに用いるには不十分である。

#### 【0019】

上記の課題を解決する別の手段が、特許文献4の図1の駆動回路である。本駆動回路は、駆動TFTのしきい値を補正する機能を備える。本回路では、外部からの電圧により、有機EL素子の駆動電流を設定する。この時、主に、配線負荷の充電期間により、設定期間が決まる。配線負荷の時定数0.2μsecであるため、99.8%の充電が終了する時間を設定期間とすると、時定数の6倍の1.2μsecとなる。従って、本従来技術を用いると高精細テレビの駆動が可能となる。

10

#### 【0020】

しかし、本回路において、駆動TFTのゲート端子 - ソース端子間に印加される電圧は、駆動回路内に設けられた2つの容量により分圧された電圧により決定される。従って、高い精度の駆動を実現するためには、2つの容量を画素内に設け、その容量間で正確な容量比を実現する必要がある。

#### 【0021】

上記課題を解決する別な駆動回路が、非特許文献1に提案されている。本回路も、特許文献4の回路と同様、外部からの電圧により、有機EL素子の駆動電流を設定するため、設定期間を短くすることができる。さらに、この回路において、駆動TFTのゲート端子に印加する電圧は1つの容量のみにて決まり、他の1つの容量は保持用としてのみ用いられるため、容量間の比のばらつきが問題にならない。

20

#### 【0022】

しかし、この回路において、駆動TFTのゲート端子 - ソース端子間電圧が固定されてしまう、駆動TFTは、定電流源ではなく、ソース端子に電圧を印加するソースフォロワとして動作する。また、駆動TFTのゲート端子には、駆動TFTと有機EL素子のしきい値電圧を補正した電圧が印加される。従って、有機EL素子の電圧 - 電流特性の変化が、印加電圧に対し平行移動の場合にのみ、本補正は成立する。

#### 【0023】

本発明は、このような従来技術では、解決できない課題を解決することを目的とする。

#### 【0024】

すなわち、本発明は、駆動用トランジスタの特性ばらつきや、電気的ストレスによる特性シフトの影響を抑え、かつ、発光素子に供給する電流を制御する駆動回路を有する発光表示デバイスを提供することを目的とする。

30

#### 【0025】

さらに、本発明は、容量を1つとし、ばらつきの要因の少ない駆動回路を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0026】

本発明に係る発光表示デバイスは、複数の画素を備える発光表示デバイスであって、前記画素は、アノード端子及びカソード端子を有し、かつ供給される電流で決まる輝度で発光する発光素子と、データ線から供給される制御電圧に基づいて前記発光素子に電流を供給する駆動回路と、を備える。前記駆動回路は、前記発光素子を駆動し、かつゲート端子、ソース端子、及びドレイン端子を有する駆動用トランジスタと、容量素子と、を備える。前記駆動用トランジスタは、前記ゲート端子が第一のスイッチ素子を経由して前記ソース端子と接続され、前記ソース端子が直接あるいは第五のスイッチ素子を経由して前記発光素子のアノード端子と接続される。前記容量素子の一端は直接前記駆動用トランジスタのゲート端子に接続され、前記容量素子の他の一端は第二のスイッチ素子を経由して前記駆動用トランジスタのソース端子に接続され、かつ第三のスイッチを経由して前記データ線に接続される。

40

また、前記容量素子と前記第一ないし第三のスイッチ素子は、前記駆動トランジスタの

50

電流設定期間に、前記第一のスイッチと前記第三のスイッチが導通し、前記第二のスイッチが非導通になり、前記駆動用トランジスタのドレイン端子の電圧と前記データ線から供給される制御電圧とから決定される電圧と、前記駆動用トランジスタのしきい値電圧と、を加えた電圧を前記容量素子が保持し、前記駆動回路が前記発光素子へ電流を供給する期間に、前記第二のスイッチが導通し、前記第一のスイッチと前記第三のスイッチが非導通になり、前記容量素子に保持された電圧を前記駆動用トランジスタのゲート端子とソース端子との電圧差とすることを特徴とする。

【発明の効果】

【0027】

本発明によれば、発光表示デバイスの画素に設けられる駆動回路は、駆動用トランジスタのしきい値電圧に依存することなく、発光素子に供給する電流を設定することができる。

10

【0028】

また、本発明によれば、駆動回路内に容量素子は1つであり、その容量値が寄生容量に比べ十分大きければ、発光素子に供給する電流は容量素子に依存しない。

【0029】

また、本発明によれば、発光素子に電流を供給する際、容量素子の両端が駆動用トランジスタのゲート端子、ソース端子と各々接続している。従って、発光素子の特性に関わらず、駆動用トランジスタは、飽和領域動作において定電流源として動作する。

【0030】

また、本発明によれば、発光素子に供給する電流の設定を電圧により行うため、負荷の大きい大型、高精細の発光表示デバイスに適用可能である。

20

【0031】

また、本発明によれば、駆動回路をn型TFTのみで構成し、発光素子のアノードを駆動回路側に設け、下から、アノード電極、発光層、カソード電極という順に積層する構成が可能である。

【0032】

また、本発明によれば、n型TFTとして、キャリア密度が $10^{18}$ (cm<sup>-3</sup>)以下、かつ電界効果移動度が1(cm<sup>2</sup>/Vs)以上、かつ、オンオフ比が10<sup>6</sup>以上である金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、a-Siや、OS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、必要なTFTサイズが小さくてすみ、高精細化が可能となる。

30

【0033】

また、本発明によれば、アモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、アモルファス層であるため平坦性が高く、特性ばらつきの小さいTFTを形成できる。

【発明を実施するための最良の形態】

【0034】

以下、本発明に係る発光表示デバイスの実施の形態について、図面を参照して説明する

40

【0035】

以下の実施形態は、有機EL素子を用いる発光表示デバイスについて説明するが、本発明は、有機EL素子以外の供給される電流により発光する発光表示デバイスや、供給される電流により任意の機能を示す一般的な電流負荷を用いる電流負荷デバイスにも適用できる。

【0036】

また、以下の実施形態は、n型TFTについて説明しているが、以下の説明において、n型TFTの代わりにp型TFTを用い、有機EL素子のアノード端子をカソード端子とすれば、同様な動作が可能である。

50

**【0037】**

ここで、以下の実施形態に使用されるTFTは、TFT特性を現すパラメータの内、しきい値電圧がばらつく、あるいは、電気的ストレスによるTFT特性シフトとして、しきい値電圧シフトが見られるものである。移動度のばらつき、あるいは、シフトは、求められる電流負荷デバイスの仕様の範囲内であるとする。

**【0038】**

また、以下の実施形態における上記しきい値とは、理想的には、ドレイン・ソース端子間に電流を流すことができる最小のゲート・ソース端子間電圧のことである。現実のTFT素子では、しきい値以下の電圧でも、ドレイン・ソース端子間に電流が流れる。しかし、しきい値以下の電圧においては、電圧が低下するに従い、その電流が急激に低下する。

10

**【0039】**

さらに、実際の回路においては、当該しきい値は、素子や材料の特性上必ずしも一定の値となるものではなく、接続する端子と、印加する電圧との関係で決まるものである。

**【0040】**

以下の実施形態における具体的な例としては、以下のようなになる。

**【0041】**

1) ソース端子をオープン、かつ、ゲート・ドレイン端子を接続し、電圧Vを印加した場合には、ドレイン端子よりソース端子に電圧が充電される。一定期間後のゲート・ドレイン端子電圧Vとソース端子電圧V1の電圧差V-V1(V>V1)がしきい値となる。

**【0042】**

2) 逆に、ソース端子に電圧Vを印加し、かつ、ゲート・ドレイン端子を接続し、電圧Vよりも十分高い電圧を印加後、オープンにした場合には、ドレイン端子の電圧がソース端子に放電される。一定期間後のゲート・ドレイン端子電圧V2とソース端子電圧Vとの電圧差V2-V(V2>V)がしきい値となる。

20

**【0043】**

以下、有機EL素子を用いた発光表示デバイスについて最良の形態を説明するが、前述の通り、本発明は、有機EL素子に限定されるものではなく、他の電流駆動型発光素子や電流負荷にも適用できる。さらに、以下では、駆動回路内のTFTとして、キャリア密度が $10^{18}$ (cm<sup>-3</sup>)以下であるアモルファス金属酸化物半導体をチャネル層としたn型TFTを用いる。このn型TFTは、電界効果移動度が $1(\text{cm}^2/\text{Vs})$ 以上、かつ、オンオフ比が $10^6$ 以上である。本発明はこれに限らず、a-Si TFTや、OLED TFTにも適用できる。さらに、他の半導体材料をチャネル層とする、n型TFTのみで構成される場合にも適用可能である。なお、以下の説明では、発光表示デバイスの画素配置に関しては、走査線が1種類ではなく、複数種類配置される以外は、前述した図9と同様であるため、その詳細を割愛し、画素の構成及び動作を中心に説明する。

30

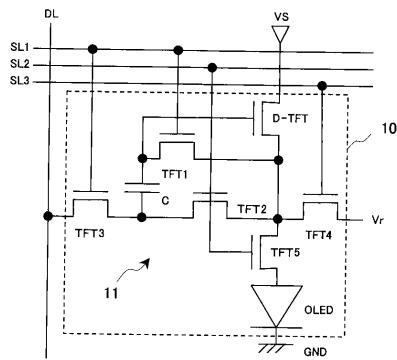

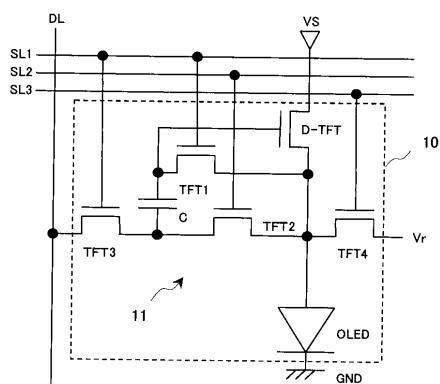

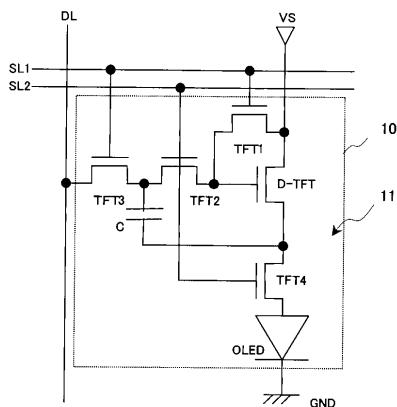

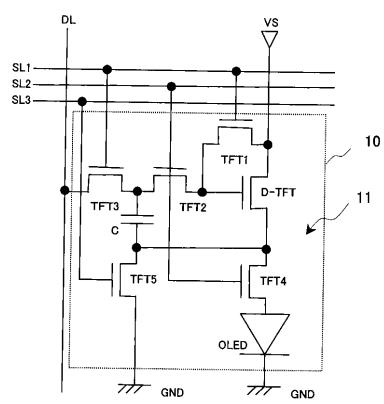

**【0044】****(第一の実施形態)**

本発明の第一の実施形態における有機EL素子を用いた発光表示デバイス(以下、有機ELディスプレイ)の画素の構成を図1に示す。

**【0045】**

本実施形態による有機ELディスプレイは、各画素10に、カソード端子がGND(接地)線(以下、GND)に接続(接地)している有機EL素子(以下、OLED)と、そのOLEDのアノード端子に接続される駆動回路11とを備える。

40

**【0046】**

OLEDは、アノード端子とカソード端子の間に、有機材料による発光層が挟まれた構造を有し、駆動回路11から供給される電流に応じた輝度で発光する。駆動回路11からOLEDへ供給される電流は、データ線からの制御電圧に基づいて決定される。

**【0047】**

駆動回路11は、OLEDを駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端がD-TFTのゲート端子に接続されている容量素子C

50

と、複数のスイッチ素子とを有する。

**【0048】**

駆動用トランジスタは、n型薄膜トランジスタ（以下、D-TFT）で構成される。D-TFTは、ドレイン端子が電源線VSと接続され、ゲート端子が容量素子Cの一端に接続される。また、D-TFTのソース端子はOLEDのアノード端子とスイッチ素子を経由して接続されている。尚、D-TFTのソース端子は直接OLEDのアノード端子と接続されていてもよい。

**【0049】**

容量素子Cと複数のスイッチ素子は、駆動回路11がOLEDへ電流を供給する時に、D-TFTのゲート端子電圧を、OLEDへの電流を供給する電圧と、D-TFTのしきい値電圧と、D-TFTのソース端子電圧を加えた電圧とする昇圧部を構成する。

10

**【0050】**

複数のスイッチ素子は、第一から第五のスイッチ素子を有する。

**【0051】**

第一のスイッチ素子は、n型TFT（以下、TFT1）で構成される。TFT1は、ソース／ドレイン端子の一端がD-TFTのソース端子と接続され、ソース／ドレイン端子の他端がD-TFTのゲート端子と接続される。

**【0052】**

第二のスイッチ素子は、n型TFT（以下、TFT2）で構成される。TFT2は、ソース／ドレイン端子の一端がD-TFTのソース端子と接続され、ソース／ドレイン端子の他端が容量素子Cの他端（D-TFTのゲート端子と接続されていない一端）と接続されている。

20

**【0053】**

第三のスイッチ素子は、n型TFT（以下、TFT3）で構成される。TFT3は、ソース端子／ドレイン端子の一端がデータ線DLに接続され、ソース端子／ドレイン端子の他端が容量素子Cの他端（D-TFTのゲート端子と接続されていない一端）と接続されている。データ線DLは、階調相当の電圧である制御電圧を印加可能な構成となっている。

**【0054】**

第四のスイッチ素子は、n型TFT（以下、TFT4）で構成される。TFT4は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端が参照電圧Vrefを供給する参照電圧線Vrと接続されている。

30

**【0055】**

第五のスイッチ素子は、n型TFT（以下、TFT5）で構成される。TFT5は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端がOLEDのアノード端子と接続されている。

**【0056】**

有機ELディスプレイは、さらにGND、参照電圧線Vrのほか、データ線DLと、第一から第三の走査線SL1からSL3と、電源線VSとを有する。データ線DLは、TFT3のソース端子／ドレイン端子のいずれかと接続され、D-TFTからOLEDに供給する電流を制御する制御電圧VDを供給する。第一の走査線SL1は、TFT1、TFT3のゲート端子と接続され、電圧信号SV1を供給する。第二の走査線SL2は、TFT2、TFT5のゲート端子と接続され、電圧信号SV2を供給する。第三の走査線SL3は、TFT4のゲート端子と接続され、電圧信号SV3を供給する。電源線VSは、電圧VS1とVS2のいずれかを供給する（電源線VSの電圧を変動する手段に対応する）。

40

**【0057】**

ここで、電源線VSの電圧VS1、VS2は、D-TFTのしきい値電圧をVtとすれば、 $VS1 > VS2$ 、かつ、 $Vref > Vt > VS2$ を満たす。さらに、電圧VS1は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とする。かつ、容量素子Cの容量値は、D-TFTに関するオーバーラップ容量などの寄生容量の総和の3倍

50

以上とする。

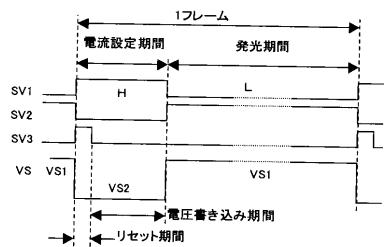

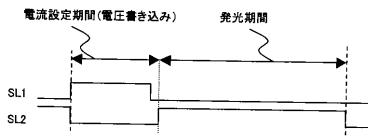

**【0058】**

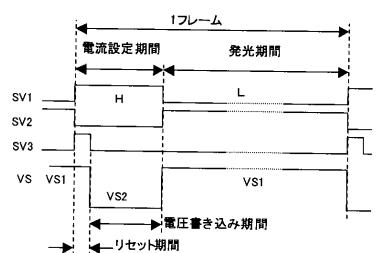

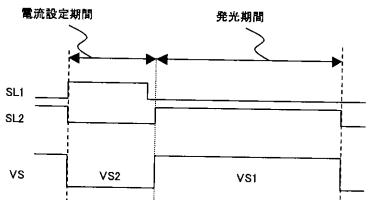

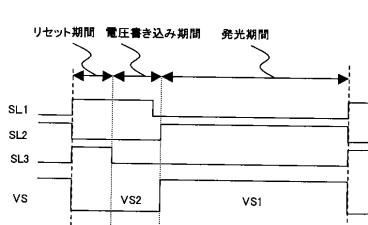

本実施形態の動作のタイミングチャートを図2に示し、以下にその動作を示す。

**【0059】**

まず、第一の走査線SL1の電圧信号SV1をH(High)レベル、第二の走査線SL2の電圧信号SV2をL(Low)レベル、第三の走査線SL3の電圧信号SV3をHレベル、電源線VSを電圧VS2とする。この期間(以下、リセット期間)では、TFT1、TFT3が導通状態(ON)に、TFT2、TFT5が非導通状態(OFF)に、TFT4が導通状態(ON)となる。本期間ににおいて、D-TFTのゲート端子、ソース端子電圧は、共に参照電圧線Vrの参照電圧Vrefとなる。また、ドレイン端子電圧は、電源線VSの電圧VS2となる。さらに、容量素子Cの他端(D-TFTのゲート端子と接続していない一端)の電圧は、データ線DLの制御電圧VDとなる。10

**【0060】**

引き続き、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、第三の走査線SL3の電圧信号SV3をLレベル、電源線VSを電圧VS2とする。この期間(以下、電圧書き込み期間)では、TFT1、TFT3がONに、TFT2、TFT5がOFFに、TFT4がOFFとなる。本期間ににおいて、D-TFTのゲート端子、ソース端子電圧は、共に電源線VSの電圧VS2とD-TFTのしきい値電圧Vtとの和VS2+Vtとなる。また、ドレイン端子電圧は、電源線VSの電圧VS2となる。さらに、容量素子Cの他端(D-TFTのゲート端子と接続していない一端)の電圧は、データ線DLの制御電圧VDとなる。この結果、容量素子Cの両端には、電圧差VS2+Vt-VDが保持される。20

**【0061】**

本実施形態では、リセット期間と電圧書き込み期間を合わせ、TFT1、TFT3がON、TFT2、TFT5がOFFする期間を電流設定期間とする。

**【0062】**

この後、第一の走査線SL1の電圧信号SV1をLレベル、第二の走査線SL2の電圧信号SV2をHレベル、第三の走査線SL3の電圧信号SV3をLレベル、電源線VSを電圧VS1とする。この期間(以下、発光期間)では、TFT1、TFT3がOFF、TFT2、TFT5がON、TFT4がOFFとなる。本期間ににおいて、D-TFTのゲート端子-ソース端子の電圧差は、D-TFTのソース端子の電圧が変動しても、チャージポンプ効果により、VS2+Vt-VDが保持される。30

**【0063】**

つまり、本実施形態では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧(VS2)とデータ線から供給される制御電圧(VD)とから決定される電圧は、次の通りである。すなわち、この電圧は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧(VS2)からデータ線より供給される制御電圧(VD)を減算した電圧(VS2-VD)である。

**【0064】**

よって、駆動用トランジスタのゲート端子とソース端子との電圧差(Vg-Vs)は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧(Vt)とを加えた電圧であり、 $Vg - Vs = VS2 + Vt - VD$ となる。ここで、VgはD-TFTのゲート端子電圧、VsはD-TFTのソース端子電圧である。40

**【0065】**

OLEDを発光させる際は、D-TFTのしきい値電圧がVtであるので、 $VS2 - VD > 0$ 、 $VS2 - VD < VS1$ 、かつ、電源線VSの電圧VS1が十分高く、D-TFTが飽和領域で動作するように電圧を設定する。

**【0066】**

この時、D-TFTは、次の式で表される電流IDをLEDに与える。

$ID = 0.5 \times \times (Vg - Vs - Vt)^2 = 0.5 \times \times (Vs2 - VD)^2$  また、

は、D-TFTの電流能力を示すパラメータであり、D-TFTの移動度、ゲート容量

、サイズに依存する。

#### 【0067】

これによると、電流IDは、データ線DLの制御電圧VDでコントロールでき、LEDは、その電流・輝度特性に従い、与えられた電流IDに相当する明るさで発光する。

#### 【0068】

有機ELディスプレイの表示動作では、例えば、上記動作を同一行の画素10に対し同時に、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを1/60秒ごとに繰り返し、表示を書き換えることで、画像を表示する。10

#### 【0069】

したがって、本実施形態において、電流IDを表す式より明らかのように、D-TFTは、しきい値Vtに影響を受けない電流IDをLEDに供給することが可能となる。従って、D-TFTのしきい値電圧Vtがばらついたり、電気的ストレスにより変動したりする場合においても、LEDに供給する電流は変わらず、定電流源として動作する。これにより、ムラのない高品質な表示が可能である。

#### 【0070】

また、本実施形態において、駆動回路内に用いている容量は1つだけであり、容量比精度の課題とは無関係となる。20

#### 【0071】

また、本実施形態において、電流IDは電圧により制御するため、高速に動作でき、負荷の大きい大型、高精細の発光表示デバイスに適用可能である。

#### 【0072】

また、本実施形態において、駆動回路をn型TFTのみで構成しているにも関わらず、LEDのアノードを駆動回路側に設ける構成が可能である。

#### 【0073】

また、本実施形態において、データ線DLの制御電圧VDは、正電圧、負電圧どちらでも可能である。30

#### 【0074】

また、本実施形態において、n型TFTとして、キャリア密度が $10^{18} (\text{cm}^{-3})$ 以下、かつ電界効果移動度が $1 (\text{cm}^2/\text{Vs})$ 以上である金属酸化物半導体層をチャネル層としたn型TFTを用いることができる。金属酸化物半導体層をチャネル層としたn型TFTを用いることより、a-SiやOS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、必要なTFTサイズが小さくてすみ、高精細化が可能となる。

#### 【0075】

また、本実施形態において、アモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いている。これにより、アモルファス層であるため平坦性が高く、特性ばらつきの小さいTFTを形成できる。40

#### 【0076】

さらに、本実施形態において、発光期間内で、TFT5を非導通とする、あるいは、VSの電圧をD-TFTがLEDに電流を供給しない電圧とする、等の手段により、LEDが発光しない期間を設けることができる。このような期間を設けることで、人間の目に対する動画表示を高品質化することが可能である。

#### 【0077】

また、第一の走査線SL1を2つに分け、TFT1のゲート端子に接続する走査線SL1-1と、TFT3のゲート端子に接続する走査線SL1-2を設ける。さらに、走査線SL1-1の電圧信号SV1-1は、走査線SL1-2の電圧信号SV1-2よりも、早50

くHレベルからLレベルへ遷移するようにする。これにより、TFT1電流設定期間から発光期間へ変わる際、TFT1の導通から非導通への遷移を、TFT2、TFT5の非導通から導通への遷移や、TFT3の導通から非導通への遷移よりも早く行う。この場合、容量素子Cに保持される電圧は、他のTFTが動作することに起因する誤差要因、例えばノイズ、の影響を受けにくくなり、より高精度の動作が可能となる。

#### 【0078】

##### (第二の実施形態)

本発明の第二の実施形態における有機EL素子を用いた発光表示デバイスの画素の構成は、第一の実施形態と同じである。ただし、本実施形態において、電源線VSの電圧VS2は一定であり、D-TFTのしきい値電圧をVtとすれば、 $V_{ref} > V_t > V_{S2}$ を満たす。つまり、第一、第二、第三の走査線SL1、SL2、SL3の電圧信号SV1、SV2、SV3を除き、最も高い電圧が参照電圧線VRの参照電圧Vrefとなる。さらに、電源線VSの電圧VS2は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とする。

10

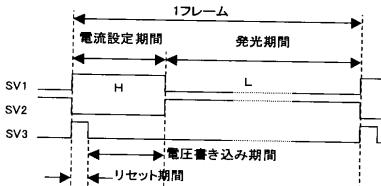

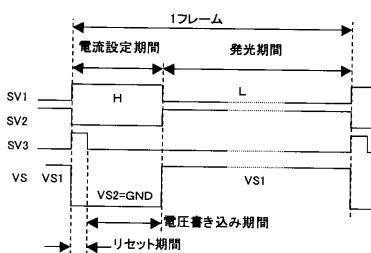

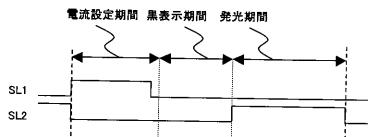

#### 【0079】

本実施形態の動作のタイミングチャートを図3に示す。本実施形態の動作は、前述通り、電源線VSの電圧VS2が一定であるほかは、第一の実施形態と同じである。

#### 【0080】

本実施の形態は、第一の実施形態と同様の効果が得られる。さらに、電源線VSの電圧を変動する手段が必要ではないため、有機ELを用いた発光表示デバイスとしての構成が簡単となる。

20

#### 【0081】

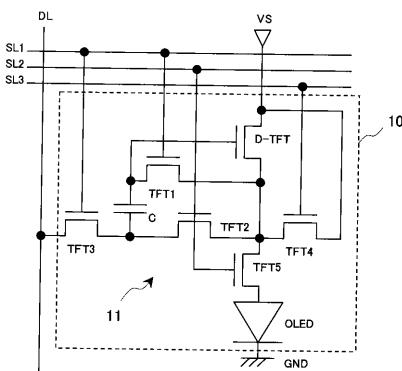

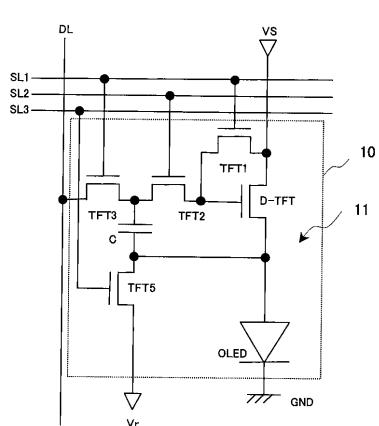

##### (第三の実施形態)

本発明の第三の実施形態における有機EL素子を用いた発光表示デバイスの画素の構成を図4に示す。第一の実施形態と同様の構成要素については、その説明を簡略又は省略する。

#### 【0082】

本実施形態は、各画素10に、カソード端子がGND(接地)線(以下、GND)に接続(接地)している有機EL素子(以下、OLED)と、そのOLEDのアノード端子に接続される駆動回路11とを備える。

30

#### 【0083】

駆動回路11は、OLEDを駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端がD-TFTのゲート端子に接続されている容量素子Cと、複数のスイッチ素子とを有する。

#### 【0084】

駆動用トランジスタは、n型TFT(以下、D-TFT)で構成される。D-TFTは、ドレイン端子が電源線VSと接続され、ゲート端子が容量素子Cの一端に接続される。

#### 【0085】

複数のスイッチ素子は、第一から第五のスイッチ素子を有する。

40

#### 【0086】

第一のスイッチ素子は、n型TFT(以下、TFT1)で構成される。TFT1は、ソース/ドレイン端子の一端がD-TFTのソース端子と接続され、ソース/ドレイン端子の他端がD-TFTのゲート端子と接続されている。

#### 【0087】

第二のスイッチ素子は、n型TFT(以下、TFT2)で構成される。TFT2は、ソース/ドレイン端子の一端がD-TFTのソース端子と接続され、ソース/ドレイン端子の他端が容量素子Cの他端(D-TFTのゲート端子と接続していない一端)と接続される。

#### 【0088】

第三のスイッチ素子は、n型TFT(以下、TFT3)で構成される。TFT3は、ソ

50

ソース端子 / ドレイン端子の一端がデータ線 D<sub>L</sub>に接続され、ソース端子 / ドレイン端子の他端が容量素子 C の他端 (D-TFT のゲート端子と接続していない一端) と接続されている。

#### 【0089】

第四のスイッチ素子は、n 型 TFT (以下、TFT4) で構成される。TFT4 は、ソース端子 / ドレイン端子の一端が D-TFT のソース端子に接続され、ソース端子 / ドレイン端子の他端が D-TFT のドレイン端子と接続されている。

#### 【0090】

第五のスイッチ素子は、n 型 TFT (以下、TFT5) で構成される。TFT5 は、ソース端子 / ドレイン端子の一端が D-TFT のソース端子に接続され、ソース端子 / ドレイン端子の他端が OLED のアノード端子と接続されている。10

#### 【0091】

有機ELディスプレイは、さらに GND、データ線 D<sub>L</sub> と、第一から第三の走査線 SL<sub>1</sub> から SL<sub>3</sub> と、電源線 VS を有する。データ線 D<sub>L</sub> は、TFT3 のソース端子 / ドレイン端子のいずれかと接続され、D-TFT から OLED に供給する電流を制御する制御電圧 V<sub>D</sub> を供給する。第一の走査線 SL<sub>1</sub> は、TFT1、TFT3 のゲート端子と接続され、電圧信号 SV<sub>1</sub> を供給する。第二の走査線 SL<sub>2</sub> は、TFT2、TFT5 のゲート端子と接続され、電圧信号 SV<sub>2</sub> を供給する。第三の走査線 SL<sub>3</sub> は、TFT4 のゲート端子と接続され、電圧信号 SV<sub>3</sub> を供給する。電源線 VS は、電圧 VS<sub>1</sub> と VS<sub>2</sub> のいずれかを供給する。20

#### 【0092】

ここで、電源線 VS の電圧 VS<sub>1</sub>、VS<sub>2</sub> は、D-TFT のしきい値電圧を V<sub>t</sub> とすれば、VS<sub>1</sub> > V<sub>t</sub> > VS<sub>2</sub> を満たす。さらに、電圧 VS<sub>1</sub> は、OLED に電流を供給する際、D-TFT が飽和領域で動作する電圧とする。かつ、容量素子 C の容量値は、D-TFT に関するオーバーラップ容量などの寄生容量の総和の 3 倍以上とする。

#### 【0093】

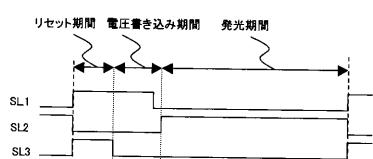

本実施形態の動作のタイミングチャートを図 5 に示し、以下にその動作を示す。

#### 【0094】

まず、第一の走査線 SL<sub>1</sub> の電圧信号 SV<sub>1</sub> を H レベル、第二の走査線 SL<sub>2</sub> の電圧信号 SV<sub>2</sub> を L レベル、第三の走査線 SL<sub>3</sub> の電圧信号 SV<sub>3</sub> を H レベル、電源線 VS を電圧 VS<sub>1</sub> とする。この期間 (以下、リセット期間) では、TFT1、TFT3 が導通状態 (ON) に、TFT2、TFT5 が非導通状態 (OFF) に、TFT4 が導通状態 (ON) となる。本期間ににおいて、D-TFT のゲート端子、ソース端子、ドレイン端子電圧は、共に電源線 VS の電圧 VS<sub>1</sub> となる。さらに、容量素子 C の他端 (D-TFT のゲート端子と接続していない一端) の電圧は、データ線 D<sub>L</sub> の電圧 V<sub>D</sub> となる。30

#### 【0095】

引き続き、第一の走査線 SL<sub>1</sub> の電圧信号 SV<sub>1</sub> を H レベル、第二の走査線 SL<sub>2</sub> の電圧信号 SV<sub>2</sub> を L レベル、第三の走査線 SL<sub>3</sub> の電圧信号 SV<sub>3</sub> を L レベル、電源線 VS を電圧 VS<sub>2</sub> とする。この期間 (以下、電圧書き込み期間) では、TFT1、TFT3 が ON に、TFT2、TFT5 が OFF に、TFT4 が OFF となる。本期間ににおいて、D-TFT のゲート端子、ソース端子電圧は、共に電源線 VS の電圧 VS<sub>2</sub> と D-TFT のしきい値電圧 V<sub>t</sub> との和 VS<sub>2</sub> + V<sub>t</sub> となる。また、ドレイン端子電圧は、電源線 VS の電圧 VS<sub>2</sub> となる。さらに、容量素子 C の他端 (D-TFT のゲート端子と接続していない一端) の電圧は、データ線 D<sub>L</sub> の電圧 V<sub>D</sub> となる。この結果、容量素子 C の両端には、電圧差 VS<sub>2</sub> + V<sub>t</sub> - V<sub>D</sub> が保持される。40

#### 【0096】

本実施形態では、リセット期間と電圧書き込み期間を合わせ、TFT1、TFT3 が ON、TFT2、TFT5 が OFF する期間を電流設定期間とする。

#### 【0097】

この後、第一の走査線 SL<sub>1</sub> の電圧信号 SV<sub>1</sub> を L レベル、第二の走査線 SL<sub>2</sub> の電圧50

信号 S V 2 を H レベル、第三の走査線 S L 3 の電圧信号 S V 3 を L レベル、電源線 V S を電圧 V S 1 とする。この期間（以下、発光期間）では、T F T 1、T F T 3 が OFF、T F T 2、T F T 5 が ON、T F T 4 が OFF となる。本期間ににおいて、D - TFT のゲート端子 - ソース端子の電圧差は、D - TFT のソース端子の電圧が変動しても、チャージポンプ効果により、V S 2 + V t - V D が保持される。

## 【0098】

つまり、本実施形態では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧（V S 2）とデータ線から供給される制御電圧（V D）とから決定される電圧が、V S 2 - V D である。

## 【0099】

よって、駆動用トランジスタのゲート端子とソース端子との電圧差（V g - V s）は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧（V t）とを加えた電圧であり、 $V g - V s = V S 2 + V t - V D$  となる。ここで、V g は D - TFT のゲート端子電圧、V s は D - TFT のソース端子電圧である。

## 【0100】

D - TFT のしきい値電圧が V t であるので、 $V S 2 - V D > 0$ 、 $V S 2 - V D < V S 1$ 、かつ、電源線 V S の電圧 V S 1 が十分高く、D - TFT が飽和領域で動作するように電圧を設定する。

10

## 【0101】

この時、D - TFT は、次の式で表される電流 I D を O L E D に与える。

$I D = 0.5 \times \times (V g - V s - V t)^2 = 0.5 \times \times (V S 2 - V D)^2$  また、

は、D - TFT の電流能力を示すパラメータであり、D - TFT の移動度、ゲート容量、サイズに依存する。

20

## 【0102】

これによると、電流 I D は、V D でコントロールでき、O L E D は、その電流 - 輝度特性に従い、与えられた電流 I D に相当する明るさで発光する。

## 【0103】

有機 E L ディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを 1 / 60 秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

30

## 【0104】

本実施形態は、第一の実施形態で述べたものと同様の効果が得られる。さらに、参照電圧線 V r を必要としないため、構成が簡単となる。

## 【0105】

## (第四の実施形態)

本発明の第四の実施形態における有機 E L 素子を用いた発光表示デバイスの画素の構成を図 6 に示す。第一の実施形態と同様の構成要素については、その説明を簡略又は省略する。

40

## 【0106】

本実施形態は、各画素 10 に、カソード端子が G N D ( 接地 ) 線 ( 以下、G N D ) に接続 ( 接地 ) している有機 E L 素子 ( 以下、O L E D ) と、その O L E D のアノード端子に接続される駆動回路 11 とを備える。

## 【0107】

駆動回路 11 は、O L E D を駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端が D - TFT のゲート端子に接続されている容量素子 C と、複数のスイッチ素子とを有する。

## 【0108】

50

駆動用トランジスタは、n型TFT（以下、D-TFT）で構成される。D-TFTは、ドレイン端子が電源線VSと接続され、ゲート端子が容量素子Cの一端に接続している。

#### 【0109】

複数のスイッチ素子は、第一から第四のスイッチ素子を有する。

#### 【0110】

第一のスイッチ素子は、n型TFT（以下、TFT1）で構成される。TFT1は、ソース／ドレイン端子の一端がD-TFTのソース端子と接続され、ソース／ドレイン端子の他端がD-TFTのゲート端子と接続されている。

#### 【0111】

第二のスイッチ素子は、n型TFT（以下、TFT2）で構成される。TFT2は、ソース／ドレイン端子の一端がD-TFTのソース端子と接続され、ソース／ドレイン端子の他端が容量素子Cの他端（D-TFTのゲート端子と接続していない一端）と接続されている。

#### 【0112】

第三のスイッチ素子は、n型TFT（以下、TFT3）で構成される。TFT3は、ソース端子／ドレイン端子の一端がデータ線DLに接続され、ソース端子／ドレイン端子の他端が容量素子Cの他端（D-TFTのゲート端子と接続していない一端）と接続されている。

#### 【0113】

第四のスイッチ素子は、n型TFT（以下、TFT4）で構成される。TFT4は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端が参照電圧Vrefを供給する参照電圧線Vrと接続されている。

#### 【0114】

有機ELディスプレイは、さらにGND、参照電圧線Vrのほか、データ線DLと、第一から第三の走査線SL1からSL3と、電源線VSとを有する。データ線DLは、TFT3のソース端子／ドレイン端子のいずれかと接続され、D-TFTからOLEDに供給する電流を制御する制御電圧VDを供給する。第一の走査線SL1は、TFT1、TFT3のゲート端子と接続され、電圧信号SV1を供給する。第二の走査線SL2は、TFT2のゲート端子と接続され、電圧信号SV2を供給する。第三の走査線SL3は、TFT4のゲート端子と接続され、電圧信号SV3を供給する。電源線VSは、電圧VS1とVS2のいずれかを供給する。

#### 【0115】

ここで、電源線VSの電圧VS1、VS2は、D-TFTのしきい値電圧をVtとすれば、 $VS1 > VS2$ 、かつ、 $Vref > Vt > VS2$ を満たす。さらに、電源線VSの電圧VS1は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とする。また、参照電圧Vrefは、OLEDが電流を流し、発光するしきい値電圧以下とする。ここで、本実施形態では、電源線VSの電圧VS2をGNDとし、データ線DLの制御電圧VDを負電圧とする。かつ、容量素子Cの容量値は、D-TFTに関するオーバーラップ容量などの寄生容量の総和の3倍以上とする。

#### 【0116】

本実施形態の動作のタイミングチャートを図7に示し、以下にその動作を示す。

#### 【0117】

まず、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、第三の走査線SL3の電圧信号SV3をHレベル、電源線VSを電圧VS2とする。この期間（以下、リセット期間）では、TFT1、TFT3が導通状態（ON）に、TFT2が非導通状態（OFF）に、TFT4が導通状態（ON）となる。本期間ににおいて、D-TFTのゲート端子、ソース端子電圧は、共に参照電圧線Vrの参照電圧Vrefとなる。また、ドレイン端子電圧は、電源線VSの電圧VS2となる。さらに、容量素子Cの他端（D-TFTのゲート端子と接続していない一端）の電圧は、デ

10

20

30

40

50

ータ線 D L の電圧 V D となる。

【 0 1 1 8 】

引き続き、第一の走査線 S L 1 の電圧信号 S V 1 を H レベル、第二の走査線 S L 2 の S V 2 を L レベル、第三の走査線 S L 3 の電圧信号 S V 3 を L レベル、電源線 S を電圧 V S 2 とする。この期間（以下、電圧書き込み期間）では、T F T 1、T F T 3 が O N に、T F T 2 が O F F に、T F T 4 が O F F となる。本期間ににおいて、D - T F T のゲート端子、ソース端子電圧は、共に電源線 V S の電圧 V S 2 と D - T F T のしきい値電圧 V t との和 V S 2 + V t となる。また、ドレイン端子電圧は、電源線 V S の電圧 V S 2 となる。さらに、容量素子 C の他端（D - T F T のゲート端子と接続していない一端）の電圧は、データ線 D L の電圧となる。この結果、容量素子 C の両端には、電圧差 V S 2 + V t - V D 10 が保持される。

【 0 1 1 9 】

本実施形態では、リセット期間と電圧書き込み期間を合わせ、T F T 1、T F T 3 が O N、T F T 2 が O F F する期間を電流設定期間とする。本期間ににおいて、O L E D に電流は流れない。

【 0 1 2 0 】

この後、第二の走査線 S L 1 の電圧信号 S V 1 を L レベル、第二の走査線 S L 2 の電圧信号 S V 2 を H レベル、第三の走査線 S L 3 の電圧信号 S V 3 を L レベル、電源線 V S を電圧 V S 1 とする。この期間（以下、発光期間）では、T F T 1、T F T 3 が O F F、T F T 2 が O N、T F T 4 が O F F となる。本期間ににおいて、D - T F T のゲート端子 - ソース端子の電圧差は、D - T F T のソース端子の電圧が変動しても、チャージポンプ効果により、V S 2 + V t - V D 20 が保持される。

【 0 1 2 1 】

つまり、本実施形態では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧（V S 2）とデータ線から供給される制御電圧（V D）とから決定される電圧が、V S 2 - V D である。

【 0 1 2 2 】

よって、駆動用トランジスタのゲート端子とソース端子との電圧差（V g - V s）は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧（V t）とを加えた電圧であり、V g - V s = V S 2 + V t - V D 30 となる。ここで、V g は D - T F T のゲート端子電圧、V s は D - T F T のソース端子電圧である。

【 0 1 2 3 】

D - T F T のしきい値電圧が V t であるので、V S 2 - V D > 0、V S 2 - V D < V S 1、かつ、電源線 V S の電圧 V S 1 が十分高く、D - T F T が飽和領域で動作するように電圧を設定する。

【 0 1 2 4 】

この時、D - T F T は、次の式で表される電流 I D を O L E D に与える。

$$I D = 0.5 \times \times (V g - V s - V t)^2 = 0.5 \times \times (V S 2 - V D)^2$$

また、

は、D - T F T の電流能力を示すパラメータであり、D - T F T の移動度、ゲート容量、サイズに依存する。

【 0 1 2 5 】

これによると、電流 I D は、データ線 D L の制御電圧 V D でコントロールでき、O L E D は、その電流 - 輝度特性に従い、与えられた電流 I D に相当する明るさで発光する。

【 0 1 2 6 】

有機 E L ディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを 1 / 60 秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

**【0127】**

本実施形態は、第一の実施形態で述べたものと同様の効果が得られる。さらに、第一の実施形態と異なり、TFT5を必要としないため、構成が簡単となる。

**【0128】**

第一の実施形態から第四の実施形態において、画素内の駆動回路は、電流設定期間において、容量素子Cが、D-TFTのゲート端子 - ソース端子間に、D-TFTのしきい値電圧のOLEDに供給する電流を設定する電圧の和を保持する。従って、D-TFTのしきい値電圧に依存することなく、OLEDに供給する電流を設定することができる。

**【0129】**

また、駆動回路内に容量素子Cは1つであり、その容量値が寄生容量に比べ十分大きければ、OLEDに供給する電流は容量素子Cに依存しない。10

**【0130】**

また、本実施形態によれば、OLEDに供給する電流の設定を電圧により行うため、負荷の大きい大型、高精細の発光表示デバイスに適用可能である。

**【0131】**

また、本実施形態によれば、駆動回路をn型TFTのみで構成し、OLEDのアノードを駆動回路側に設け、下から、アノード電極、有機材料発光層、カソード電極という順に積層する構成が可能である。

**【0132】**

また、本実施形態によれば、n型TFTとして、キャリア密度が $10^{18}$ (cm<sup>-3</sup>)以下、かつ電界効果移動度が1(cm<sup>2</sup>/Vs)以上である金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、a-SiやOTS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、必要なTFTサイズが小さくてすみ、高精細化が可能となる。20

**【0133】**

また、本実施形態によれば、アモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、アモルファス層であるため平坦性が高く、特性ばらつきの小さいTFTを形成できる。

**【0134】**30**(第一の参考例)**

本発明の第一の参考例における有機EL素子を用いた発光表示デバイスの画素の構成を図10に示す。

**【0135】**

本参考例による有機ELディスプレイは、各画素10に、カソード端子がGND(接地)線(以下、GND)に接続(接地)している有機EL素子(以下、OLED)と、そのOLEDのアノード端子に接続される駆動回路11とを備える。

**【0136】**

OLEDは、アノード端子とカソード端子の間に、有機材料による発光層が挟まれた構造を有し、駆動回路11から供給される電流に応じた輝度で発光する。40

**【0137】**

駆動回路11は、OLEDを駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端がD-TFTのソース端子に接続されている容量素子Cと、複数のスイッチ素子とを有する。

**【0138】**

駆動用トランジスタは、n型TFT(以下、D-TFT)で構成される。D-TFTは、ドレイン端子が電源線VSと接続されている。

**【0139】**

容量素子Cと複数のスイッチ素子は、駆動回路11がOLEDへ電流を供給する時に、D-TFTのゲート端子電圧を、OLEDへの電流を供給する電圧と、D-TFTのしき

50

い値電圧と、D-TFTのソース端子電圧を加えた電圧とする昇圧部を構成する。

**【0140】**

複数のスイッチ素子は、第一から第四のスイッチ素子を有する。

**【0141】**

第一のスイッチ素子は、n型TFT（以下、TFT1）で構成される。TFT1は、ソース／ドレイン端子の一端がD-TFTのドレイン端子と接続され、ソース／ドレイン端子の他端がD-TFTのゲート端子と接続されている。

**【0142】**

第二のスイッチ素子は、n型TFT（以下、TFT2）で構成される。TFT2は、ソース／ドレイン端子の一端がD-TFTのゲート端子と接続され、ソース／ドレイン端子の他端が容量素子Cの他端（D-TFTのソース端子と接続されていない一端）と接続されている。10

**【0143】**

第三のスイッチ素子は、n型TFT（以下、TFT3）で構成される。TFT3は、ソース端子／ドレイン端子の一端がデータ線DLに接続され、ソース端子／ドレイン端子の他端が容量素子Cの他端（D-TFTのソース端子と接続されていない一端）と接続されている。

**【0144】**

第四のスイッチ素子は、n型TFT（以下、TFT4）で構成される。TFT4は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端がOLEDのアノード端子と接続されている。20

**【0145】**

有機ELディスプレイは、さらにGNDのほか、データ線DLと、第一、第二の走査線SL1、SL2と、電源線VSとを有する。データ線DLは、D-TFTからOLEDに供給する電流を制御する制御電圧VDを供給する。電源線VSは、電圧VS1を供給する。第一の走査線SL1は、TFT1、TFT3のゲート端子と接続され、電圧信号SV1を供給する第二の走査線SL2は、TFT2、TFT4のゲート端子と接続され、電圧信号SV2を供給する。

**【0146】**

ここで、電源線VSの電圧VS1は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とする。かつ、容量素子Cの容量値は、D-TFTに関するチャネル容量と、オーバーラップ容量などの寄生容量との和の3倍以上とする。30

**【0147】**

本参考例のタイミングチャートを図11に示し、以下にその動作を説明する。

**【0148】**

まず、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベルとする。この期間（以下、電圧書き込み期間）では、TFT1、TFT3がONに、TFT2、TFT4がOFFとなる。本期間ににおいて、D-TFTのソース端子電圧は、D-TFTのしきい値電圧をVtとすると、VS1 - Vtとなる。また、容量素子Cの他端（D-TFTのソース端子と接続していない一端）の電圧は、データ線DLの電圧VDとなる。この結果、容量素子Cの両端には、電圧差VD - VS1 + Vtが保持される。40

**【0149】**

本参考例では、電圧書き込み期間がOLEDに供給する電流を設定する電流設定期間となる。

**【0150】**

この後、第一の走査線SL1の電圧信号SV1をLレベル、第二の走査線SL2の電圧信号SV2をHレベルとする。この期間（以下、発光期間）では、TFT1、TFT3がOFF、TFT2、TFT4がONとなる。本期間ににおいて、D-TFTのゲート端子 - ソース端子の電圧差は、D-TFTのソース端子の電圧が変動しても、チャージポンプ効50

果により、 $V_D - V_S 1 + V_t$  が保持される。

#### 【0151】

つまり、本参考例では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧 ( $V_S 1$ ) とデータ線から供給される制御電圧 ( $V_D$ ) とから決定される電圧は、次の通りである。すなわち、この電圧は、データ線より供給される制御電圧 ( $V_D$ ) から駆動用トランジスタの電流設定期間におけるドレイン端子の電圧 ( $V_S 1$ ) を減算した電圧 ( $V_D - V_S 1$ ) である。

#### 【0152】

よって、駆動用トランジスタのゲート端子とソース端子との電圧差 ( $V_g - V_s$ ) は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧 ( $V_t$ ) とを加えた電圧であり、 $V_g - V_s = V_D - V_S 1 + V_t$  となる。ここで、 $V_g$  は D-TFT のゲート端子電圧、 $V_s$  は D-TFT のソース端子電圧である。

10

#### 【0153】

電源線  $V_S$  の電圧  $V_S 1$  が十分高く、D-TFT が飽和領域で動作するように電圧を設定する。

#### 【0154】

この時、D-TFT は、次の式で表される電流  $I_D$  を OLE D に与える。

$$I_D = 0.5 \times \times (V_g - V_s - V_t)^2 = 0.5 \times \times (V_D - V_S 1)^2$$

20

また、D-TFT の電流能力を示すパラメータであり、D-TFT の移動度、ゲート容量、サイズに依存する。

#### 【0155】

これによると、電流  $I_D$  は、データ線  $D_L$  の制御電圧  $V_D$  でコントロールでき、OLE D は、その電流 - 輝度特性に従い、与えられた電流  $I_D$  に相当する明るさで発光する。

#### 【0156】

有機ELディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを、例えば、1/60秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

30

#### 【0157】

本参考例において、電流  $I_D$  を表す式より明らかのように、D-TFT は、しきい値  $V_t$  に影響を受けない電流  $I_D$  を、OLE D に供給することが可能となる。従って、前記  $V_t$  がばらついたり、電気的ストレスにより変動したりする場合においても、OLE D に供給する電流は変わらず、定電流源として動作する。これにより、ムラのない高品質な表示が可能である。

#### 【0158】

また、本参考例において、駆動回路内に用いている容量素子は1つだけであり、容量比精度の課題とは無関係となる。さらに、容量素子  $C$  の容量値は、D-TFT のチャネル容量と、オーバーラップ容量などの寄生容量との和の3倍以上であるため、電流設定期間と発光期間でのD-TFT のソース端子、ドレイン端子の電圧変化の影響を抑制できる。

40

#### 【0159】

また、本構成において、電流  $I_D$  は電圧により制御するため、高速に動作でき、負荷の大きい大型、高精細の発光表示デバイスに適用可能である。

#### 【0160】

また、本参考例において、駆動回路をn型TFTのみで構成しているにも関わらず、OLE D のアノードを駆動回路側に設ける構成が可能である。

#### 【0161】

また、本参考例において、n型TFTとして、キャリア密度が $10^{18}$  ( $\text{cm}^{-3}$ ) 以下、かつ電界効果移動度が $1$  ( $\text{cm}^2/\text{Vs}$ ) 以上である金属酸化物半導体層をチャネル

50

層としたn型TFTを用いている。これにより、a-SiやOS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、必要なTFTサイズが小さくてすみ、高精細化が可能となる。

#### 【0162】

また、本参考例において、アモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いている。これにより、アモルファス層であるため平坦性が高く、特性ばらつきの小さいTFTを形成できる。

#### 【0163】

また、本参考例において、第一の走査線SL1を2つに分け、TFT1のゲート端子に接続する走査線SL1-1と、TFT3のゲート端子に接続する走査線SL1-2を設ける。さらに、走査線SL1-2の電圧信号SV1-2は、走査線SL1-1の電圧信号SV1-1よりも、早くHレベルからLレベルへ遷移するようとする。これにより、電流設定期間から発光期間へ変わる際、TFT3のONからOFFへの遷移を、TFT2、TFT4のOFFからONへの遷移や、TFT1のONからOFFへの遷移よりも早く行う。この場合、容量素子Cに保持される電圧は、他のTFTが動作することに起因する誤差要因、例えばノイズの影響を受けにくくなり、より高精度の動作が可能となる。以上のような、電流設定期間から発光期間の遷移の際、TFT3の動作を他のTFTよりも早く行う手段は、以下に述べるでも用いることができ、同様の効果を得られる。

#### 【0164】

さらに、本参考例において、タイミングチャートを図12に示すような動作を行うことで新たな効果が得られる。図12では、第二の走査線SL2の電圧信号SV2がLレベルからHレベルへ変化するタイミングをずらし、TFT1、TFT3がONからOFFへ遷移するタイミングから、TFT2、TFT4がOFFからONへ遷移するタイミングの間に一定の期間を設けている。この期間は、OLEDに電流が流れないため、発光しない期間（以下、黒表示期間）となる。本期間を設けることで、新たに信号線を設けることなく、人間の目に映る残像が減少し、動画表示品質を向上することができる。以上のような黒表示期間を設けることは、以下に述べるでも用いることができ、同様の効果を得られる。

#### 【0165】

##### （第二の参考例）

本発明の第二の参考例における有機EL素子を用いた発光表示デバイスの画素の構成は、第一の参考例と同様に図10で示される。

#### 【0166】

ただし、本参考例は、電源線VSは、電圧VS1に固定ではなく、電圧VS1、VS2いずれかの値を取ることを特徴としている（D-TFTのドレイン端子電圧を変動する手段に対応する）。本参考例の動作のタイミングチャートを図13に示し、以下にその動作を示す。

#### 【0167】

まず、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、電源線VSを電圧VS2とする。この期間（以下、電圧書き込み期間）では、TFT1、TFT3が導通状態（ON）に、TFT2、TFT4が非導通状態（OFF）になる。本期間ににおいて、D-TFTのゲート端子、ドレイン端子電圧は、共に電源線の電圧VS2となる。また、D-TFTのソース端子電圧は、D-TFTのしきい値電圧をVtとすると、VS2-Vtとなり、容量素子Cの他端（D-TFTのソース端子と接続していない一端）の電圧は、データ線DLの電圧VDとなる。この結果、容量素子Cの両端には、電圧VD-VS2+Vtが保持される。

#### 【0168】

本参考例では、電圧書き込み期間がOLEDに供給する電流を設定する電流設定期間となる。

#### 【0169】

10

20

30

40

50

この後、第一の走査線 S L 1 の電圧信号 S V 1 を L レベル、第二の走査線 S L 2 の電圧信号 S V 2 を H レベル、電源線 V S を電圧 V S 1 とする。この期間（以下、発光期間）では、T F T 1、T F T 3 が OFF、T F T 2、T F T 4 が ON となる。本期間ににおいて、D - T F T のゲート端子 - ソース端子の電圧差は、D - T F T のソース端子の電圧が変動しても、チャージポンプ効果により、V D - V S 2 + V t が保持される。

#### 【0170】

つまり、本参考例では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧（V S 2）とデータ線から供給される制御電圧（V D）とから決定される電圧が、V D - V S 2 である。

#### 【0171】

よって、駆動用トランジスタのゲート端子とソース端子との電圧差（V g - V s）は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧（V t）とを加えた電圧であり、 $V g - V s = V D - V S 2 + V t$  となる。ここで、V g は D - T F T のゲート端子電圧、V s は D - T F T のソース端子電圧である。

#### 【0172】

V S 1 は、V S 2 よりも高く、D - T F T が飽和領域で動作するように電圧を設定する。

#### 【0173】

この時、D - T F T は、次の式で表される電流 I D を O L E D に与える。

$I D = 0.5 \times \times (V g - V s - V t)^2 = 0.5 \times \times (V D - V S 2)^2$  また、

は、D - T F T の電流能力を示すパラメータであり、D - T F T の移動度、ゲート容量、サイズに依存する。

#### 【0174】

これによると、電流 I D は、データ線 D L の制御電圧 V D でコントロールでき、O L E D は、その電流 - 輝度特性に従い、与えられた電流 I D に相当する明るさで発光する。

#### 【0175】

有機 E L ディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを、例えば、1 / 60 秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

#### 【0176】

本参考例は、第一の参考例で述べたものと同様の効果が得られる。さらに、V S 2 が低いため、第一の参考例に比べデータ線 D L の V D の電圧が低くても、同じ電流を流すことが可能となる。これにより、データ線 D L の V D を印加するための回路や、表示装置全体の消費電力を抑えることができる。

#### 【0177】

また、V S 2 を、O L E D が電流を流し、発光するしきい値電圧以下とする。その場合、T F T 4 が無くても上記と同じ動作が可能となり、少ない素子数で、同様の効果が得られる。

#### 【0178】

##### （第三の参考例）

本発明の第三の参考例における有機 E L 素子を用いた発光表示デバイスの画素の構成を図 14 に示す。第一の参考例と同様の構成要素については、その説明を簡略又は省略する。

#### 【0179】

本参考例は、各画素 10 に、カソード端子が G N D ( 接地 ) 線 ( 以下、G N D ) に接続 ( 接地 ) している有機 E L 素子 ( 以下、O L E D ) と、その O L E D のアノード端子に接続される駆動回路 11 とを備える。

10

20

30

40

50

**【0180】**

駆動回路11は、OLEDを駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端がD-TFTのソース端子に接続されている容量素子Cと、複数のスイッチ素子とを有する。

**【0181】**

駆動用トランジスタは、n型TFT（以下、D-TFT）で構成される。D-TFTは、ドレイン端子が電源線VSと接続されている。

**【0182】**

複数のスイッチ素子は、第一から第五のスイッチ素子を有する。

**【0183】**

第一のスイッチ素子は、n型TFT（以下、TFT1）で構成される。TFT1は、ソース／ドレイン端子の一端がD-TFTのドレイン端子と接続され、ソース／ドレイン端子の他端がD-TFTのゲート端子と接続されている。

**【0184】**

第二のスイッチ素子は、n型TFT（以下、TFT2）で構成される。TFT2は、ソース／ドレイン端子の一端がD-TFTのゲート端子と接続され、ソース／ドレイン端子の他端が容量素子Cの他端（D-TFTのソース端子と接続されていない一端）と接続されている。

**【0185】**

第三のスイッチ素子は、n型TFT（以下、TFT3）で構成される。TFT3は、ソース端子／ドレイン端子の一端がデータ線DLに接続され、ソース端子／ドレイン端子の他端が容量素子Cの他端（D-TFTのソース端子と接続されていない一端）と接続されている。

**【0186】**

第四のスイッチ素子は、n型TFT（以下、TFT4）で構成される。TFT4は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端がOLEDのアノード端子と接続している。

**【0187】**

第五のスイッチ素子は、n型TFT（以下、TFT5）で構成される。TFT5は、ソース端子／ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子／ドレイン端子の他端がGNDに接続（接地）されている。

**【0188】**

有機ELディスプレイは、GNDのほか、データ線DLと、第一から第三の走査線SL1からSL3と、電源線VSとを有する。データ線DLは、D-TFTからOLEDに供給する電流を制御する制御電圧VDを供給する。電源線VSは、電圧VS1を供給する。第一の走査線SL1は、TFT1、TFT3のゲート端子と接続され、電圧信号SV1を供給する。第二の走査線SL2は、TFT2、TFT4のゲート端子と接続され、電圧信号SV2を供給する。第三の走査線SL3は、TFT5のゲート端子と接続され、電圧信号SV3を供給する。

**【0189】**

ここで、電源線VSの電圧VS1は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とする。かつ、容量素子Cの容量値は、D-TFTに関するチャネル容量と、オーバーラップ容量などの寄生容量との和の3倍以上とする。

**【0190】**

本参考例のタイミングチャートを図15に示し、以下にその動作を示す。

**【0191】**

まず、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、第三の走査線SL3の電圧信号SV3をHレベルとする。この期間（以下、リセット期間）において、TFT1、TFT3がONに、TFT2、TFT4がOFFに、TFT5がONになる。本期間ににおいて、D-TFTのソース端子電圧は、G

10

20

30

40

50

N D となる。

**【 0 1 9 2 】**

引き続き、第一の走査線 S L 1 の電圧信号 S V 1 を H レベル、第二の走査線 S L 2 の電圧信号 S V 2 を L レベル、第三の走査線 S L 3 の電圧信号 S V 3 を L レベルとする。この期間（電圧書き込み期間）では、T F T 1、T F T 3 が ON に、T F T 2、T F T 4 が OFF、T F T 5 が OFF となる。本期間ににおいて、D - T F T のソース端子電圧は、D - T F T のしきい値電圧を V t とすると、V S 1 - V t となり、容量素子 C の他端（D - T F T のソース端子と接続していない一端）の電圧は、データ線 D L の電圧 V D となる。この結果、容量素子 C の両端には、電圧差 V D - V S 1 + V t が保持される。

**【 0 1 9 3 】**

本参考例では、リセット期間と電圧書き込み期間を加えた期間が、O L E D に供給する電流を設定する電流設定期間となる。

**【 0 1 9 4 】**

この後、第一の走査線 S L 1 の電圧信号 S V 1 を L レベル、第二の走査線 S L 2 の電圧信号 S V 2 を H レベル、第三の走査線 S L 3 の電圧信号 S V 3 を L レベルとする。この期間（以下、発光期間）では、T F T 1、T F T 3 が OFF、T F T 2、T F T 4 が ON、T F T 5 が OFF となる。本期間ににおいて、D - T F T のゲート端子 - ソース端子の電圧差は、D - T F T のソース端子の電圧が変動しても、チャージポンプ効果により、V D - V S 1 + V t が保持される。

**【 0 1 9 5 】**

つまり、本参考例では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧（V S 1）とデータ線から供給される制御電圧（V D）とから決定される電圧が、V D - V S 1 である。

**【 0 1 9 6 】**

よって、駆動用トランジスタのゲート端子とソース端子との電圧差（V g - V s）は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧（V t）とを加えた電圧であり、V g - V s = V D - V S 1 + V t となる。ここで、V g は D - T F T のゲート端子電圧、V s は D - T F T のソース端子電圧である。

**【 0 1 9 7 】**

電源線 V S の電圧 V S 1 が十分高く、D - T F T が飽和領域で動作するように電圧を設定する。

**【 0 1 9 8 】**

この時、D - T F T は、次の式で表される電流 I D を O L E D に与える。

$$I D = 0.5 \times \times (V g - V s - V t)^2 = 0.5 \times \times (V D - V S 1)^2$$

また、

は、D - T F T の電流能力を示すパラメータであり、D - T F T の移動度、ゲート容量、サイズに依存する。

**【 0 1 9 9 】**

これによると、電流 I D は、データ線 D L の制御電圧 V D でコントロールでき、O L E D は、その電流 - 輝度特性に従い、与えられた電流 I D に相当する明るさで発光する。

**【 0 2 0 0 】**

有機 E L ディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを、例えば、1 / 60 秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

**【 0 2 0 1 】**

本参考例において、リセット期間を設けることで、ノイズ等の影響により、D - T F T のソース端子の電圧が、電源線 V S の電圧よりも高くなった場合でも、正常に動作することができる。また、本参考例は、第一の実施形態と同様の効果が得られる。さらに、第二

10

20

30

40

50

の参考例と同様な動作を実現することも可能である。

**【0202】**

(第四の参考例)

本発明の第四の参考例における有機EL素子を用いた発光表示デバイスの画素の構成を図16に示す。第一の参考例と同様の構成要素については、その説明を簡略又は省略する。

**【0203】**

本参考例は、各画素10に、カソード端子がGND(接地)線(以下、GND)に接続(接地)されている有機EL素子(以下、OLED)と、そのOLEDのアノード端子に接続される駆動回路11とを備える。

10

**【0204】**

駆動回路11は、OLEDを駆動し、かつゲート端子、ソース端子、ドレイン端子を有する駆動用トランジスタと、一端がD-TFTのソース端子に接続されている容量素子Cと、複数のスイッチ素子とを有する。

**【0205】**

駆動用トランジスタは、n型TFT(以下、D-TFT)で構成される。D-TFTは、ドレイン端子が第一の電源線VSと接続されている。

**【0206】**

複数のスイッチ素子は、第一から第五のスイッチ素子(第四のスイッチ素子を除く)を有する。

20

**【0207】**

第一のスイッチ素子は、n型TFT(以下、TFT1)で構成される。TFT1は、ソース/ドレイン端子の一端がD-TFTのドレイン端子と接続され、ソース/ドレイン端子の他端がD-TFTのゲート端子と接続されている。第一のn型TFT(以下、TFT1)を有する。

**【0208】**

第二のスイッチ素子は、n型TFT(以下、TFT2)で構成される。TFT2は、ソース/ドレイン端子の一端がD-TFTのゲート端子と接続され、ソース/ドレイン端子の他端が容量素子Cの他端(D-TFTのソース端子と接続されていない一端)と接続されている。

30

**【0209】**

第三のスイッチ素子は、n型TFT(以下、TFT3)で構成される。TFT3は、ソース端子/ドレイン端子の一端がデータ線DLに接続され、ソース端子/ドレイン端子の他端が容量素子Cの他端(D-TFTのソース端子と接続されていない一端)と接続している。

**【0210】**

第五のスイッチ素子は、n型TFT(以下、TFT5)で構成される。TFT5は、ソース端子/ドレイン端子の一端がD-TFTのソース端子に接続され、ソース端子/ドレイン端子の他端が第二の電源線VRに接続されている。

**【0211】**

有機ELディスプレイは、GNDのほか、データ線DLと、第一の電源線VSと、第二の電源線VRと、第一から第三の走査線SL1からSL3とを有する。データ線DLは、D-TFTからOLEDに供給する電流を制御する制御電圧VDを供給する。第一の電源線VSは、電圧VS1及びVS2を供給する。第二の電源線VRは、電圧Vrefを供給する。第一の走査線SL1は、TFT1、TFT3のゲート端子と接続され、電圧信号SV1を供給する。第二の走査線SL2は、TFT2のゲート端子と接続され、電圧信号SV2を供給する。第三の走査線SL3は、TFT5のゲート端子と接続され、電圧信号SV3を供給する。

40

**【0212】**

ここで、第一の電源線VSは、電圧VS1及びVS2を期間ごとに印加する。電圧VS

50

1は、OLEDに電流を供給する際、D-TFTが飽和領域で動作する電圧とし、電圧VS2は、OLEDが駆動する電圧以下とする。また、第二の電源線VRの電圧Vrefは、D-TFTのしきい値をVtとする場合、VS2-Vt以下とする。かつ、容量素子Cの容量値は、D-TFTに関するチャネル容量と、オーバーラップ容量などの寄生容量との和の3倍以上とする。

#### 【0213】

本参考例のタイミングチャートを図17に示し、以下にその動作を示す。

#### 【0214】

まず、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、第三の走査線SL3の電圧信号SV3をHレベル、第一の電源線VSを電圧VS2とする。この期間（以下、リセット期間）では、TFT1、TFT3がONに、TFT2がOFFに、TFT5がONになる。本期間ににおいて、D-TFTのソース端子電圧は、第二の電源線VRの電圧Vrefとなる。

10

#### 【0215】

引き続き、第一の走査線SL1の電圧信号SV1をHレベル、第二の走査線SL2の電圧信号SV2をLレベル、第三の走査線SL3の電圧信号SV3をLレベル、第一の電源線VSを電圧VS2とする。この期間（以下、電圧書き込み期間）では、TFT1、TFT3がONに、TFT2がOFF、TFT5がOFFとなる。本期間ににおいて、第一の電源線VSの電圧VS2がOLEDの駆動電圧以下のため、OLEDに電流が流れず、D-TFTのソース端子電圧はVS2-Vtとなる。また、容量素子Cの他端（D-TFTのソース端子と接続されていない一端）の電圧は、データ線DLの電圧VDとなる。この結果、容量素子Cの両端には、電圧差VD-VS2+Vtが保持される。

20

#### 【0216】

本参考例では、リセット期間と電圧書き込み期間を加えた期間が、OLEDに供給する電流を設定する電流設定期間となる。

#### 【0217】

この後、第一の走査線SL1のSV1をLレベル、第二の走査線SL2のSV2をHレベル、第三の走査線SL3のSV3をLレベル、第一の電源線VSを電圧VS1とする。この期間（以下、発光期間）では、TFT1、TFT3がOFF、TFT2がON、TFT5がOFFとなる。本期間ににおいて、D-TFTのゲート端子-ソース端子の電圧差は、D-TFTのソース端子の電圧が変動しても、チャージポンプ効果により、VD-VS2+Vtが保持される。

30

#### 【0218】

つまり、本参考例では、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧(VS2)とデータ線から供給される制御電圧(VD)とから決定される電圧が、VD-VS2である。

#### 【0219】

よって、駆動用トランジスタのゲート端子とソース端子との電圧差(Vg-Vs)は、次の通りである。すなわち、この電圧差は、駆動用トランジスタの電流設定期間におけるドレイン端子の電圧とデータ線から供給される制御電圧とから決定される電圧と、駆動用トランジスタのしきい値電圧(Vt)とを加えた電圧であり、Vg-Vs=VD-VS2+Vtとなる。ここで、VgはD-TFTのゲート端子電圧、VsはD-TFTのソース端子電圧である。

40

#### 【0220】

第一の電源線VSの電圧VS1が十分高く、D-TFTが飽和領域で動作するように電圧を設定する。

#### 【0221】

この時、D-TFTは、次の式で表される電流IDをOLEDに与える。

$$ID = 0.5 \times \times (Vg - Vs - Vt)^2 = 0.5 \times \times (VD - VS2)^2 \text{ また、} \\ \text{は、D-TFTの電流能力を示すパラメータであり、D-TFTの移動度、ゲート容量}$$

50

、サイズに依存する。

**【0222】**

これによると、電流IDは、データ線DLの制御電圧VDでコントロールでき、OLEDは、その電流・輝度特性に従い、与えられた電流IDに相当する明るさで発光する。

**【0223】**

有機ELディスプレイの表示動作では、例えば、上記動作を同一行の画素に対し同時にを行い、それを全行に対し順次行うことで、1画面分の表示を行う。1画面分の表示期間は、フレームと呼ばれる。このフレームを、例えば、1/60秒ごとに繰り返し、表示を書き換えることで、画像を表示する。

**【0224】**

本参考例は、リセット期間を設けることで、ノイズ等の影響により、D-TFTのソース端子の電圧が、第一の電源線VSの電圧よりも高くなった場合でも、正常に動作することができる。また、本参考例は、第一の実施形態と同様の効果が得られる。さらに、第二の実施形態と同様な動作を実現することも可能である。さらに、第二の参考例と同様に、電源線VSの電圧VS2が低いため、第一の実施形態に比べデータ線DLの制御電圧VDの電圧が低くても、同じ電流を流すことが可能となる。これにより、データ線DLの制御電圧VDを印加するための回路や、表示装置全体の消費電力を抑えることができる。

**【0225】**

第一の参考例から第四の参考例において、画素内の駆動回路は、電流設定期間において、容量素子Cが、D-TFTのゲート端子・ソース端子間に、D-TFTのしきい値電圧とOLEDに供給する電流を設定する電圧との和を保持する。従って、D-TFTのしきい値電圧に依存することなく、OLEDに供給する電流を設定することができる。

**【0226】**

また、駆動回路内に容量素子Cは1つであるため、容量比精度の問題は生じない。

**【0227】**

また、容量素子の容量値が寄生容量の3倍以上と十分大きいため、寄生容量による影響が小さく、精度よくOLEDに電流を供給することができる。

**【0228】**

以上説明したように、本参考例によれば、OLEDに供給する電流の設定を電圧により行うため、負荷の大きい大型、高精細の発光表示デバイスに適用可能である。

**【0229】**

また、本参考例によれば、駆動回路をn型TFTのみで構成し、OLEDのアノードを駆動回路側に設け、下から、アノード電極、有機材料発光層、カソード電極という順に積層する構成が可能である。

**【0230】**

また、本参考例によれば、n型TFTとして、キャリア密度が $10^{18}$ (cm<sup>-3</sup>)以下、かつ電界効果移動度が1(cm<sup>2</sup>/Vs)以上である金属酸化物アモルファス半導体膜をチャネル層としたn型TFTを用いる。これにより、a-Siや、OS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、必要なTFTサイズが小さくてすみ、高精細化が可能となる。

**【0231】**

また、本参考例によれば、アモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、アモルファス層であるため平坦性が高く、特性ばらつきの小さいTFTを形成できる。

**【産業上の利用可能性】**

**【0232】**

本発明は、発光表示素子を用いた発光表示デバイスに利用できる。特に本発明は、有機EL素子と、有機EL素子に電流を供給するための駆動回路とで構成される画素をマトリックス状に備える発光表示デバイスに適用可能である。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0233】

【図1】第一の実施形態に係る発光表示デバイスの構成を示す回路図である。

【図2】第一の実施形態の動作を説明するタイミングチャートである。

【図3】第二の実施形態の動作を説明するタイミングチャートである。

【図4】第三の実施形態に係る発光表示デバイスの構成を示す回路図である。

【図5】第三の実施形態の動作を説明するタイミングチャートである。

【図6】第四の実施形態に係る発光表示デバイスの構成を示す回路図である。

【図7】第四の実施形態の動作を説明するタイミングチャートである。

【図8】画素の構成を示す図である。

10

【図9】走査線が1種類の場合の有機EL表示装置の構成を示す図である。

【図10】第一の参考例に係る発光表示デバイスの構成を示す回路図である。

【図11】第一の参考例の動作を説明するタイミングチャートである。

【図12】第一の参考例の動作を説明する他のタイミングチャートである。

【図13】第二の参考例のタイミングチャートである。

【図14】第三の参考例に係る発光表示デバイスの動作を説明する構成を示す回路図である。

【図15】第三の参考例の動作を説明するタイミングチャートである。

【図16】第四の参考例に係る発光表示デバイスの構成を示す回路図である。

【図17】第四の参考例の動作を説明するタイミングチャートである。

20

## 【符号の説明】

## 【0234】

10 画素

11 駆動回路

OLED 有機EL素子

D-TFT 駆動用トランジスタ (n型駆動TFT)

TFT1からTFT5 第一から第五のスイッチ素子 (n型スイッチングTFT)

V<sub>S</sub> 電源線 (第一の電源線)

GND GND線

S<sub>L</sub>(n) (n行目の) 走査線 (走査線が1種類の場合)

30

S<sub>L</sub>1 第一の走査線

S<sub>L</sub>2 第二の走査線

S<sub>L</sub>3 第三の走査線

D<sub>L</sub>(n) (n列目の) データ線

C 容量素子

V<sub>r</sub> 参照電圧線

V<sub>r</sub> 第二の電源線 (第四の参考例)

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

---

フロントページの続き

(51)Int.Cl. F I

H 05 B 33/14 A

(56)参考文献 特開2005-326828(JP,A)

特開2004-280059(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

H 01 L 51 / 50

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP5665256B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2015-02-04 |

| 申请号            | JP2007292109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2007-11-09 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 安部勝美                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 安部 勝美                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2300/0866 G09G2310/0251<br>G09G2310/061 G09G2320/0233 G09G2320/0261 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.624.B G09G3/20.641.D G09G3/20.670.J H05B33/14.A G09G3/20.612.E G09G3/3241 G09G3/325 G09G3/3258 G09G3/3266 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC33 3K107/CC35 3K107/EE04 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD29 5C080/EE29 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AB25 5C380/AB46 5C380/AC04 5C380/BA01 5C380/BA05 5C380/BA08 5C380/BA12 5C380/BA13 5C380/BA19 5C380/BA28 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BC20 5C380/BD02 5C380/BD09 5C380/BD10 5C380/BE05 5C380/CA12 5C380/CA13 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB20 5C380/CB31 5C380/CC04 5C380/CC06 5C380/CC07 5C380/CC13 5C380/CC14 5C380/CC18 5C380/CC19 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC57 5C380/CC61 5C380/CC63 5C380/CC64 5C380/CD014 5C380/CD015 5C380/CD016 5C380/CE04 5C380/CE20 5C380/DA01 5C380/DA02 5C380/DA06 5C380/DA42 5C380/DA47 5C380/HA02 5C380/HA03 5C380/HA05 5C380/HA08 5C380/HA12 |         |            |

| 代理人(译)         | 佐藤安倍晋三<br>黑岩Soware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 审查员(译)         | 武田 悟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 优先权            | 2006342578 2006-12-20 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | JP2008176287A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

**摘要(译)**

提供一种具有驱动电路的发光显示装置，该驱动电路用于控制提供给发光元件的电流，同时抑制驱动晶体管的特性偏移和由于电应力引起的特性偏移的影响。发光显示装置包括多个像素。像素10包括：有机EL元件(OLED)，其发射具有由待供应的电流确定的亮度的光；以及驱动电路11，其基于来自数据线的控制电压向OLED供应电流。驱动电路11包括用于驱动OLED的驱动晶体管(D-TFT)，电容元件C和多个开关元件。D-TFT的源极端子连接到OLED的阳极端子。电容器C和多个开关元件，当驱动电路11将电流提供给OLED，栅极端子与d-TFT的源极端子，并且所述驱动晶体管的电流设置时段的漏极端子的电压之间的电压差以及从数据线提供的控制电压和驱动晶体管的阈值电压。点域1

【図 1】

【図 2】