(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4153855号

(P4153855)

(45) 発行日 平成20年9月24日(2008.9.24)

(24) 登録日 平成20年7月11日(2008.7.11)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/30 | K       |

| <b>H03K</b> | <b>17/78</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 1 A |

|             |              |                  | G09G | 3/20 | 6 2 4 B |

請求項の数 20 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2003-337968 (P2003-337968)

(22) 出願日

平成15年9月29日 (2003.9.29)

(65) 公開番号

特開2004-310014 (P2004-310014A)

(43) 公開日

平成16年11月4日 (2004.11.4)

審査請求日

平成16年4月12日 (2004.4.12)

(31) 優先権主張番号

2003-020433

(32) 優先日

平成15年4月1日 (2003.4.1)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 590002817

三星エスディアイ株式会社

大韓民国京畿道水原市靈通区▲しん▼洞5

75番地

(74) 代理人 100095957

弁理士 龟谷 美明

(74) 代理人 100096389

弁理士 金本 哲男

(72) 発明者 権 五敬

大韓民国ソウル市松坡区新川洞 (番地なし)

薔薇アパート14-1102

審査官 濱本 祥広

最終頁に続く

(54) 【発明の名称】発光表示装置、発光表示装置の駆動方法、発光表示装置の表示パネル

## (57) 【特許請求の範囲】

## 【請求項 1】

画像信号を表すデータ電流を伝達する複数のデータ線と、選択信号を伝達する複数の走査線と、前記データ線および前記走査線によって定義される複数の画素に各々形成される複数の画素回路と、を備える発光表示装置において、

前記画素回路は、

印加される電流に対応して発光する発光素子と；

前記発光素子を発光させるための駆動電流を出力し、第1及び第2主電極と制御電極とを有する第1トランジスタと；

第1制御信号に応答して前記第1トランジスタをダイオード形態に連結させる第1スイッチング素子と； 10

前記走査線からの第1選択信号に応答して前記データ線からの前記データ電流を前記第1トランジスタに伝達する第2スイッチング素子と；

第2制御信号の動作許可レベルに応答して並列に連結されて、前記第2スイッチング素子からの前記データ電流に対応する第1電圧を保存する第1及び第2キャパシタと；

第3制御信号に応答して前記第1トランジスタからの前記駆動電流を前記発光素子に伝達する第3スイッチング素子と；を含み、

前記第1キャパシタは、前記第2制御信号の動作禁止レベルに応答して、ダイオード形態に連結された前記第1トランジスタのしきい電圧に対応する第2電圧を保存し、

前記第1及び第2キャパシタに前記第1電圧が印加された後、前記第1キャパシタに前記

10

20

第2電圧が印加され，前記第2制御信号の動作許可レベルに応答して前記第1及び第2キャパシタを並列に連結することによって第3電圧が前記第1トランジスタに印加され，前記駆動電流が前記発光素子に出力されることを特徴とする，発光表示装置。

【請求項2】

第1及び第2制御信号と第1選択信号とが動作許可レベルとなることにより，並列に連結される第1キャパシタと第2キャパシタとに第1電圧が保存される第1期間；前記第1制御信号が動作許可レベルとなり，前記第2制御信号及び前記第1選択信号が動作禁止レベルとなることにより，前記第1キャパシタに第2電圧が保存される第2期間；前記第1制御信号が動作禁止レベルとなり，第2及び第3制御信号が動作許可レベルとなることにより，前記第1キャパシタと前記第2キャパシタとが並列に連結されて、並列に連結される前記第1キャパシタと前記第2キャパシタに第3電圧が保存され、前記第3電圧が第1トランジスタに印加され，前記第3電圧に対応する駆動電流が発光素子に供給される第3期間；

の順に動作することを特徴とする，請求項1に記載の発光表示装置。

【請求項3】

画像信号を表すデータ電流を伝達する複数のデータ線と，選択信号を伝達する複数の走査線と，前記データ線および前記走査線によって定義される複数の画素に各々形成される複数の画素回路と，を備える発光表示装置において，

前記画素回路は，

印加される電流に対応して発光する発光素子と；

前記発光素子を発光させるための駆動電流を出力し，第1及び第2主電極と制御電極とを有する第1トランジスタと；

第1制御信号に応答して前記第1トランジスタをダイオード形態に連結させる第1スイッチング素子と；

前記走査線からの第1選択信号に応答して前記データ線からの前記データ電流を前記第1トランジスタに伝達する第2スイッチング素子と；

第2制御信号のオンレベルに応答して，前記第2スイッチング素子からの前記データ電流に対応する第1電圧を保存する第1キャパシタと；

第3制御信号に応答して前記第1トランジスタからの前記駆動電流を前記発光素子に伝達する第3スイッチング素子と；

前記第1キャパシタと直列に連結されている第2キャパシタと；

を含み，

直列に連結された前記第1及び第2キャパシタは，前記第2制御信号の動作禁止レベルに応答して，ダイオード形態に連結された前記第1トランジスタのしきい電圧に対応する第2電圧を保存し，

前記第1キャパシタに前記第1電圧が印加された後，直列に連結された前記第1及び第2キャパシタに前記第2電圧が印加され，前記第2制御信号の動作許可レベルに応答して直列に連結された前記第1及び第2キャパシタ中の前記第1キャパシタに保存された第3電圧が前記第1トランジスタに印加され，前記駆動電流が前記発光素子に出力されることを特徴とする，発光表示装置。

【請求項4】

第1及び第2制御信号と第1選択信号とが動作許可レベルとなることにより，第1キャパシタに第1電圧が保存される第1期間；

前記第1制御信号が動作許可レベルとなり，前記第2制御信号及び前記第1選択信号が動作禁止レベルとなることにより，直列に連結された第1キャパシタと第2キャパシタに第2電圧が保存される第2期間；

前記第1制御信号が動作禁止レベルとなり，第2及び第3制御信号が動作許可レベルとなることにより，前記第2期間で前記第1キャパシタに保存された前記第3電圧が第1トランジスタに印加され，前記第3電圧に対応する駆動電流が発光素子に供給される第3期間；

10

20

30

40

50

の順に動作することを特徴とする，請求項 3 に記載の発光表示装置。

【請求項 5】

前記第 1 制御信号は，前記第 1 選択信号と，前記第 1 選択信号後に動作許可期間を有する次の走査線からの第 2 選択信号とから構成され；

前記第 1 スイッチング素子は，前記第 1 選択信号に応答して前記第 1 トランジスタをダイオード形態に連結させる第 2 トランジスタと，前記第 2 選択信号に応答して前記第 1 トランジスタをダイオード形態に連結させる第 3 トランジスタと，を含むことを特徴とする，請求項 1，2，3 または 4 のいずれかに記載の発光表示装置。

【請求項 6】

前記第 2 制御信号は，前記第 1 選択信号と，前記第 3 制御信号とから構成され；

10

前記画素回路は，前記第 2 制御信号に応答して導通し前記第 1 トランジスタの制御電極に第 1 端が連結され前記第 2 キャパシタに第 2 端が連結される第 4 スイッチング素子に並列に連結される第 5 スイッチング素子とをさらに含み；

前記第 4 スイッチング素子は，前記第 1 選択信号に応答して導通し，前記第 5 スイッチング素子は，前記第 3 制御信号に応答して導通することを特徴とする，請求項 1，2，3 または 4 のいずれかに記載の発光表示装置。

【請求項 7】

前記第 1 制御信号は，前記第 1 選択信号と，前記第 1 選択信号後に動作許可期間を有する次の走査線からの第 2 選択信号とから構成され；

前記第 2 制御信号は，前記第 1 選択信号と，前記第 3 制御信号とから構成され；

20

前記第 1 スイッチング素子は，前記第 1 選択信号に応答して前記第 1 トランジスタをダイオード形態に連結させる第 2 トランジスタと，前記第 2 選択信号に応答して前記第 1 トランジスタをダイオード形態に連結させる第 3 トランジスタとを含み；

前記画素回路は，前記第 2 制御信号に応答して導通し前記第 1 トランジスタの制御電極に第 1 端が連結され前記第 2 キャパシタに第 2 端が連結される第 4 スイッチング素子に並列に連結される第 5 スイッチング素子とをさらに含み；

前記第 4 スイッチング素子は，前記第 1 選択信号に応答して導通し，前記第 5 スイッチング素子は，前記第 3 制御信号に応答して導通することを特徴とする，請求項 1，2，3 または 4 のいずれかに記載の発光表示装置。

【請求項 8】

30

走査線からの選択信号に応答してデータ線からのデータ電流を伝達するスイッチング素子と，前記データ電流に対応した駆動電流を出力し第 1 及び第 2 主電極と制御電極とを有するトランジスタと，前記トランジスタからの駆動電流に対応して発光する発光素子と，を含む画素回路を備えた発光表示装置を駆動する方法において：

前記トランジスタの制御電極と第 1 主電極との間に並列に連結される第 1 及び第 2 キャパシタに，前記スイッチング素子からのデータ電流に対応する第 1 電圧を印加する第 1 段階と；

前記第 1 及び第 2 キャパシタの並列連結を遮断することにより、前記第 1 キャパシタに，前記トランジスタのしきい電圧に対応する第 2 電圧を印加する第 2 段階と；

前記第 1 及び第 2 キャパシタを並列に連結することにより，前記トランジスタの制御電極と第 1 主電極との間の電圧を第 3 電圧とし，前記トランジスタからの駆動電流を前記発光素子に伝達する第 3 段階と；

を含み，

前記トランジスタからの駆動電流は，前記第 3 電圧に対応して決定されることを特徴とする，発光表示装置の駆動方法。

【請求項 9】

走査線からの選択信号に応答してデータ線からのデータ電流を伝達するスイッチング素子と，前記データ電流に対応した駆動電流を出力し第 1 及び第 2 主電極と制御電極とを有するトランジスタと，前記トランジスタからの駆動電流に対応して発光する発光素子と，を含む画素回路を備えた発光表示装置を駆動する方法において：

40

50

前記トランジスタの制御電極と第1主電極との間に第1キャパシタを連結することにより，前記第1キャパシタに前記スイッチング素子からのデータ電流に対応する第1電圧を印加する第1段階と；

前記トランジスタの制御電極と第1主電極との間に前記第1キャパシタと第2キャパシタを直列に連結することにより，直列に連結される前記第1及び第2キャパシタに，前記トランジスタのしきい電圧に対応する第2電圧を印加する第2段階と；

前記トランジスタの制御電極と第1主電極との間に第1キャパシタを連結することにより，前記トランジスタの制御電極と第1主電極との間の電圧を第3電圧とし，前記トランジスタからの駆動電流を前記発光素子に伝達する第3段階と；

を含み，

10

前記第3電圧は，前記第1キャパシタによって決定され、

前記トランジスタからの駆動電流は，前記第3電圧に対応して決定されることを特徴とする，発光表示装置の駆動方法。

【請求項10】

前記第1段階は，

第1制御信号に応答して前記トランジスタがダイオード形態に連結される段階と；

第2制御信号の第1レベルに応答して前記第1及び第2キャパシタが並列に連結される段階と；

前記走査線からの第1選択信号に応答して前記データ電流が伝達される段階と；

前記第1電圧が並列に連結される前記第1及び第2キャパシタに印加される段階と；

20

を含み：

前記第2段階は，

前記第1制御信号に応答して前記トランジスタがダイオード形態に連結される段階と；

前記第2制御信号の第2レベルに応答して前記第1及び第2キャパシタの並列連結が遮断される段階と；

前記第2電圧が前記第1キャパシタに印加される段階と；

を含み：

前記第3段階は，

前記第2制御信号の第1レベルに応答して前記第1及び第2保存素子が並列に連結される段階と；

30

第3制御信号に応答して前記駆動電流が前記発光素子に伝達される段階と；

を含むことを特徴とする，請求項8に記載の発光表示装置の駆動方法。

【請求項11】

前記第1段階は，

第1制御信号に応答して前記トランジスタがダイオード形態に連結される段階と；

第2制御信号の第1レベルに応答して前記トランジスタの制御電極と第1主電極との間に第1キャパシタが連結される段階と；

前記走査線からの第1選択信号に応答して前記データ電流が伝達される段階と；

前記第1電圧が前記第1キャパシタに印加される段階と；

を含み：

40

前記第2段階は，

前記第1制御信号に応答して前記トランジスタがダイオード形態に連結される段階と；

前記第2制御信号の第2レベルに応答して前記トランジスタの制御電極と第1主電極との間に前記第1及び第2キャパシタが直列に連結される段階と；

前記第2電圧が直列に連結される前記第1及び第2キャパシタに印加される段階と；

を含み：

前記第3段階は，

前記第2制御信号の第1レベルに応答して前記トランジスタの制御電極と第1主電極との間に第1キャパシタが連結される段階と；

第3制御信号に応答して前記駆動電流が前記発光素子に伝達される段階と；

50

を含むことを特徴とする，請求項 9 に記載の発光表示装置の駆動方法。

【請求項 1 2】

前記第 1 段階での前記第 1 制御信号は，前記第 1 選択信号で構成され；

前記第 2 段階での前記第 1 制御信号は，前記第 1 選択信号後に動作許可期間を有する次の走査線からの第 2 選択信号で構成されることを特徴とする，請求項 1 0 に記載の発光表示装置の駆動方法。

【請求項 1 3】

前記第 1 段階での前記第 2 制御信号は，前記第 1 選択信号で構成され；

前記第 3 段階での前記第 2 制御信号は，前記第 3 制御信号で構成されることを特徴とする，請求項 1 0 に記載の発光表示装置の駆動方法。

10

【請求項 1 4】

前記第 1 段階での前記第 2 制御信号及び前記第 1 制御信号は，前記第 1 選択信号で構成され；

前記第 2 段階での前記第 1 制御信号は，前記第 1 選択信号後に動作許可期間を有するその次の走査線からの第 2 選択信号で構成され；

前記第 3 段階での前記第 2 制御信号は，前記第 3 制御信号で構成されることを特徴とする，請求項 1 0 に記載の発光表示装置の駆動方法。

【請求項 1 5】

画像信号を表すデータ電流を伝達する複数のデータ線と，選択信号を伝達する複数の走査線と，前記データ線および前記走査線によって定義される複数の画素に各々形成される複数の画素回路と，を備える発光表示装置の表示パネルにおいて，

20

前記画素回路は，

印加される電流に対応して光を発する発光素子と；

前記発光素子を発光させるための駆動電流を出力し，第 1 及び第 2 主電極と制御電極とを有する第 1 トランジスタと；

第 1 制御信号に応答して前記第 1 トランジスタをダイオード形態に連結する第 1 スイッチング素子と；

前記走査線からの第 1 選択信号に応答して前記データ線からの前記データ電流を前記第 1 トランジスタに伝達する第 2 スイッチング素子と；

第 3 制御信号に応答して前記第 1 トランジスタからの駆動電流を前記発光素子に伝達する第 3 スイッチング素子と；

30

第 2 制御信号に応答して動作する第 4 スイッチング素子と；

前記第 1 トランジスタの制御電極と第 1 主電極の間に連結される第 1 キャパシタと；

前記第 4 スイッチング素子がオン状態である時，前記第 1 キャパシタに並列に連結され、前記第 4 スイッチング素子がオフ状態である時，前記第 1 キャパシタとの並列連結が遮断される第 2 キャパシタと；

を含み：

前記データ電流に対応する第 1 電圧が並列に連結される前記第 1 と第 2 キャパシタに印加される第 1 期間，前記第 1 トランジスタのしきい電圧に対応する第 2 電圧が前記第 1 キャパシタに印加される第 2 期間，前記第 2 電圧を保存している前記第 1 キャパシタと前記第 1 電圧を保存している前記第 2 キャパシタを並列に連結することによって決定される第 3 電圧によって前記駆動電流が生成される第 3 期間，の順に駆動することを特徴とする，発光表示装置の表示パネル。

40

【請求項 1 6】

画像信号を表すデータ電流を伝達する複数のデータ線と，選択信号を伝達する複数の走査線と，前記データ線および前記走査線によって定義される複数の画素に各々形成される複数の画素回路と，を備える発光表示装置の表示パネルにおいて，

前記画素回路は，

印加される電流に対応して光を発する発光素子と；

前記発光素子を発光させるための駆動電流を出力し，第 1 及び第 2 主電極と制御電極とを

50

有する第1トランジスタと；

第1制御信号に応答して前記第1トランジスタをダイオード形態に連結する第1スイッチング素子と；

前記走査線からの第1選択信号に応答して前記データ線からの前記データ電流を前記第1トランジスタに伝達する第2スイッチング素子と；

第3制御信号に応答して前記第1トランジスタからの駆動電流を前記発光素子に伝達する第3スイッチング素子と；

第2制御信号に応答して動作する第4スイッチング素子と；

前記第4スイッチング素子がオフ状態である時，前記第1トランジスタの制御電極と第1主電極の間に直列に連結される第1及び第2キャパシタと

を含み：

前記第4スイッチング素子がオン状態である時，前記第1トランジスタの制御電極と第1主電極の間に前記第2キャパシタを除いて前記第1キャパシタが連結され、

前記データ電流に対応する第1電圧が前記第1キャパシタに印加される第1期間，前記第1トランジスタのしきい電圧に対応する第2電圧が直列に連結される第1及び第2キャパシタに印加される第2期間，前記第2期間で前記第1キャパシタに保存された第3電圧によって前記駆動電流が生成される第3期間，の順に駆動することを特徴とする，発光表示装置の表示パネル。

#### 【請求項17】

前記第1期間では，前記第1及び第2制御信号と前記第1選択信号とが動作許可レベルとなり，前記第3制御信号が動作禁止レベルとなることによって動作し；

前記第2期間では，前記第1制御信号が動作許可レベルとなり，前記第2及び第3制御信号と前記第1選択信号とが動作禁止レベルとなることによって動作し，

前記第3期間では，前記第2及び第3制御信号が動作許可レベルとなり，前記第1選択信号と前記第1制御信号が動作禁止レベルとなることによって動作することを特徴とする，請求項15または16のいずれかに記載の発光表示装置の表示パネル。

#### 【請求項18】

前記第1期間での前記第1制御信号は，前記第1選択信号で構成され，前記第2期間での前記第1制御信号は，前記第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号で構成され；

前記第1スイッチング素子は，前記第1選択信号に応答するトランジスタと，前記第2選択信号に応答するトランジスタと，を含むことを特徴とする，請求項15に記載の発光表示装置の表示パネル。

#### 【請求項19】

前記第1期間での前記第2制御信号は，前記第1選択信号で構成され，前記第3期間での前記第2制御信号は，前記第3制御信号で構成され；

前記第4スイッチング素子は，前記第1選択信号に応答するトランジスタと，前記第3制御信号に応答するトランジスタとを含むことを特徴とする，請求項15に記載の発光表示装置の表示パネル。

#### 【請求項20】

前記第1期間での前記第1制御信号は，前記第1選択信号で構成され，前記第2期間での前記第1制御信号は，前記第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号で構成され；

前記第1期間での前記第2制御信号は，前記第1選択信号で構成され，前記第3期間での前記第2制御信号は，前記第3制御信号で構成され；

前記第1スイッチング素子は，前記第1選択信号に応答するトランジスタと，前記第2選択信号に応答するトランジスタとを含み；

前記第4スイッチング素子は，前記第1選択信号に応答するトランジスタと，前記第3制御信号に応答するトランジスタとを含むことを特徴とする，請求項15に記載の発光表示装置の表示パネル。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、発光表示装置およびその駆動方法、並びに発光表示装置の表示パネルに関する、特に、有機電界発光表示装置等に関する。

## 【背景技術】

## 【0002】

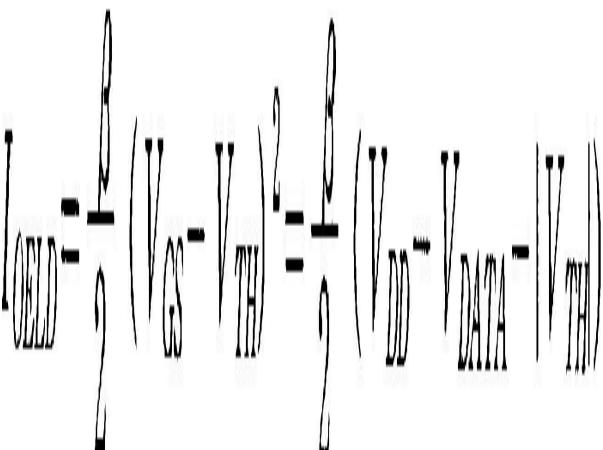

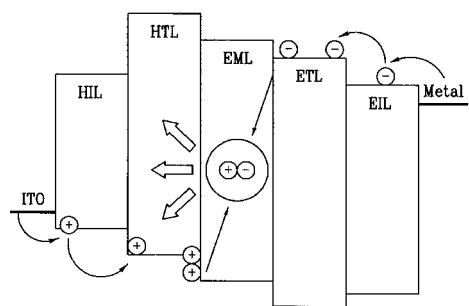

一般に、有機電界発光（以下、「有機EL」；Electro Luminescenceという。）表示装置は、蛍光性有機化合物を電気的に励起して発光させる表示装置である。この有機EL表示装置は、例えば、 $N \times M$ 個の有機発光セルを電圧駆動あるいは電流駆動して、映像を表現できる構成である。このような有機発光セルは、図1に示すように、アノード（ITO；Indium Tin Oxide）、有機薄膜、カソード（金属）の構造を有している。有機薄膜は、電子と正孔の均衡を良くして発光効率を向上させるために、一般的には、アノード側より、正孔注入層、正孔輸送層、発光層、電子輸送層及び電子注入層を含む多層構造を有している。

10

## 【0003】

このように構成される有機発光セルを駆動する方式としては、単純マトリックス方式と、薄膜トランジスタ（TFT；Thin Film Transistor）または比較的厚い電界効果型トランジスタ（MOSFET；Metal Oxide Semiconductor Field Effect Transistor）などを利用した能動駆動方式とがある。単純マトリックス方式は、正極駆動線と負極駆動線を直交させて形成し、駆動線を選択して有機発光セルを駆動発光させる。これに対して、能動駆動方式は、薄膜トランジスタとキャパシタを各ITO画素電極に接続し、キャパシタ容量によって電圧を維持するようにする駆動方式である。この時、キャパシタに電圧を維持するために印加する信号の形態によって、能動駆動方式は電圧指定方式（電圧記入方式）と電流指定方式（電流記入方式）とに分けられる。

20

## 【0004】

以下、図2及び図3を参照して、従来技術による電圧指定方式及び電流指定方式の有機EL表示装置について説明する。

30

## 【0005】

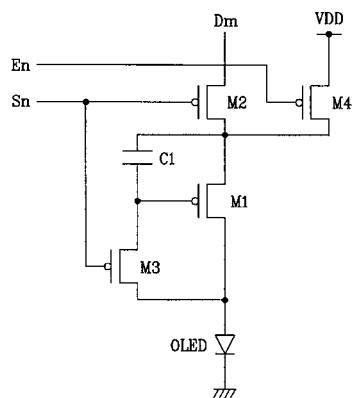

図2は、有機EL素子を駆動するための従来の電圧指定方式の画素回路であって、 $N \times M$ 個の画素のうちの一つを代表的に示した図面である。図2に示すように、有機EL素子（OLED）にトランジスタ（M1）が連結されており、発光のための電流を供給する。トランジスタ（M1）の電流量は、スイッチングトランジスタ（M2）を通じて印加されるデータ電圧によって制御される。この時、印加された電圧を一定期間維持するためのキャパシタ（C1）が、トランジスタ（M1）のソースとゲートの間に連結されている。トランジスタ（M2）のゲートには走査線（S<sub>n</sub>）が連結されており、ソース側にはデータ線（D<sub>m</sub>）が連結されている。

40

## 【0006】

このような構造の画素回路の動作について説明すると、スイッチングトランジスタ（M2）のゲートに印加される選択信号によってトランジスタ（M2）が導通すれば、データ線（D<sub>m</sub>）からのデータ電圧がトランジスタ（M1）のゲートに印加される。その後、ゲートとソース間で充電されたキャパシタ（C1）電圧（V<sub>GS</sub>）に応じてトランジスタ（M1）に電流（I<sub>OLED</sub>）が流れ、この電流（I<sub>OLED</sub>）に対応して有機EL素子（OLED）が発光する。

## 【0007】

この時、有機EL素子（OLED）に流れる電流は、電界効果型トランジスタ（M1）の特性に従って、次の式で表される。

## 【0008】

50

## 【数1】

$$I_{OELD} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = \frac{\beta}{2} (V_{DD} - V_{DATA} - |V_{TH}|)^2 \quad \dots \quad (\text{数式1})$$

この数式1で， $I_{OELD}$ は有機EL素子(OLED)に流れる電流， $V_{GS}$ はトランジスタ(M1)のソースとゲートの間の電圧， $V_{TH}$ はトランジスタ(M1)のしきい電圧， $V_{DATA}$ はデータ電圧， $\beta$ は定数値を示す。

## 【0009】

10

数式1に示したように，図2に示した画素回路によれば，印加されるデータ電圧に対応する電流が有機EL素子(OLED)に供給され，供給された電流に対応して有機EL素子が発光する。この時，印加されるデータ電圧は，階調を表現するために一定の範囲で多段階の値を有する。

## 【0010】

しかし，このような従来の電圧指定方式の画素回路では，製造工程での不均一性により生じるトランジスタのしきい電圧( $V_{TH}$ )の偏差及び電子移動度の偏差が原因で，安定した多段階階調を得ることが困難であるという問題点がある。例えば，全幅3Vで画素のトランジスタを駆動する場合，8ビット(256段階)階調を表現するためには12mV( $= 3V / 256$ )間隔でトランジスタのゲートに電圧を印加しなければならない。仮に，製造工程の不均一によるトランジスタのしきい電圧の偏差が100mVである場合には，隣接画素の輝度関係(明暗)が反転するなどの不具合を生じる可能性があり，多段階階調を表現するのが困難となる。また，電子移動度の偏差によって数式1での $\beta$ 値が変わるので，さらに多段階階調を表現するのは困難となる。

20

## 【0011】

これに対し，電流指定方式では，画素回路に電流を供給する電流源がパネル全体を通じて均一であるとすれば，例えば，各データ線の駆動特性だけを均一化すれば，各画素内の駆動トランジスタが不均一な電圧-電流特性を有するとしても，均一なディスプレイ特性を得ることができる。

## 【0012】

30

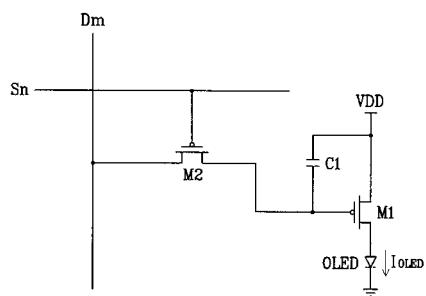

図3は，有機EL素子を駆動するための従来の電流指定方式の画素回路であって， $N \times M$ 個の画素のうちの一つを代表的に示した図面である。図3に示すように，有機EL素子(OLED)にトランジスタ(M1)が連結されて発光のための電流を供給する。トランジスタ(M1)の電流量は，トランジスタ(M2)を通じて印加されるデータ電流によって制御される。

## 【0013】

この画素回路の動作を説明すると，走査線( $S_n$ )に印加された選択信号(ローレベル)によってトランジスタ(M2, M3)が導通すれば，トランジスタ(M1)はダイオード連結状態になってデータ線( $D_m$ )からのデータ電流( $I_{DATA}$ )に対応するダイオード電圧がキャパシタ(C1)に充電保存される。次に，走査線( $S_n$ )の選択信号が消えて電位がハイレベルになるとトランジスタ(M2, M3)が遮断され，走査線( $E_n$ )に発光信号(ローレベル)が印加されればトランジスタ(M4)が導通する。その後，電源(正電圧 $VDD$ )から電流が供給され，キャパシタ(C1)に保存された電圧に対応する電流がトランジスタ(M1)と有機EL素子(OLED)に流れて発光が行われる。この時，有機EL素子(OLED)に流れる電流は数式2のようになる。

40

## 【0014】

【数2】

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = I_{DATA}$$

・・・ (数式2)

この数式2で、 $V_{GS}$ はトランジスタ(M1)のソースとゲートの間の電圧、 $V_{TH}$ はトランジスタ(M1)のしきい電圧、 $I_{DATA}$ は定数値を表す。

10

【0015】

数式2に示したように、図3に示した従来の画素回路によれば、有機EL素子に流れる電流( $I_{OLED}$ )はデータ電流( $I_{DATA}$ )と同一であるので、印加される電流源がパネル全体を通じて均一であるとすれば均一な発光特性を得ることができる。しかし、有機EL素子に流れる電流( $I_{OLED}$ )は、微細電流であるので、微細電流( $I_{DATA}$ )で画素回路を制御しなければならず、有機EL素子の所要電圧までデータ線を充電するのに長時間をするという問題点がある。例えば、データ線の負荷のキャパシタンスが30pFであると仮定する場合に、数十nAから数百nA程度のデータ電流でデータ線の負荷を充電するためには、数msの時間が必要である。これは数十μs水準であるライン時間(走査線毎の駆動時間)を考慮すると、充電時間が不十分となるという問題点がある。

20

【発明の開示】

【発明が解決しようとする課題】

【0016】

本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、トランジスタのしきい電圧や電子移動度を補償することができ、データ線を十分に充電させることが可能な、新規かつ改良された発光表示装置とその駆動方法およびその表示パネルを提供することにある。

【課題を解決するための手段】

【0017】

上記課題を解決するために、本発明のある観点によれば、画像信号を表すデータ電流を伝達する複数のデータ線と、選択信号を伝達する複数の走査線と、データ線および走査線によって定義される複数の画素に各々形成される複数の画素回路と、を備える発光表示装置が提供される。この発光表示装置の画素回路は、発光素子、第1トランジスタ、第1乃至第3スイッチング素子、第1及び第2保存素子を含む。発光素子は、第1トランジスタから印加される駆動電流の大きさに対応した光を発光する。第1トランジスタは、第1主電極(ソース電極)、第2主電極(ドレイン電極)と制御電極(ゲート電極)とを有する。この第1トランジスタは、画素回路に電気的に連結される電源供給線から発光素子への電流供給をオン/オフし、発光素子を発光させるための駆動電流を出力する。第1スイッチング素子は、第1制御信号に応答して第1トランジスタをダイオード形態に連結させる。第2スイッチング素子は、走査線からの第1選択信号に応答してデータ線からのデータ電流を第1トランジスタに伝達する。第1保存素子は、第2制御信号に応答して第2スイッチング素子からのデータ電流に対応する第1電圧を保存する。第2保存素子は、第2制御信号の動作禁止レベルに応答して第1トランジスタのしきい電圧に対応する第2電圧を保存する。第3スイッチング素子は、第3制御信号に応答して第1トランジスタからの駆動電流を発光素子に伝達する。かかる画素回路は、第1保存素子に第1電圧を印加した後、第2保存素子に第2電圧を印加し、さらに、第1及び第2保存素子の結合によって第1保存素子に保存された第3電圧を第1トランジスタに印加して、この第3電圧に応じた駆動電流が発光素子に出力され、発光素子が発光する。

30

【0018】

なお、上記「トランジスタをダイオード形態に連結させる」とは、トランジスタのドレ

40

50

インとゲートを接続することをいう。かかる接続によって、トランジスタのドレインとゲートに流れる電流の和が、データ線に流れる電流と同一になる。

【0019】

かかる構成により、まず、データ電流に対応する第1電圧を第1トランジスタのゲートとソースの間に形成される第1保存素子に印加し、次いで、駆動トランジスタのゲートとソースの間に形成される第2保存素子に第1トランジスタのしきい電圧に対応する第2電圧を印加し、さらに、第1電圧を保存する第1保存素子と、第2電圧を保存する第2保存素子とを連結することにより、第1トランジスタのゲートとソースの間の電圧を第3電圧とし、第1トランジスタからの駆動電流を発光素子に伝達することができる。この時、駆動電流は第3電圧に応じて決定される。これにより、比較的大きいデータ電流によって、発光素子の発光量を制御することができる。

10

【0020】

また、上記第1及び第2制御信号と第1選択信号とが動作許可レベルとなることにより、第1保存素子に第1電圧が保存される第1期間；第1制御信号が動作許可レベルとなり、第2制御信号及び第1選択信号が動作禁止レベルとなることにより、第2保存素子に第2電圧が保存される第2期間；第1制御信号が動作禁止レベルとなり、第3制御信号が動作許可レベルとなることにより、第3電圧に対応する駆動電流が発光素子に供給される第3期間；の順に動作するように構成してもよい。

20

【0021】

また、上記画素回路は、第2制御信号に応答して導通し第1トランジスタの制御電極に第1端が連結される第4スイッチング素子をさらに含むようにしてもよい。このとき、第4スイッチング素子が導通して第1保存素子が構成され、第4スイッチング素子が遮断して第2保存素子が構成されるようにしてもよい。

【0022】

また、上記第2保存素子は、第1トランジスタの制御電極と第1主電極との間に連結される第1キャパシタによって構成されるようにしてもよい。また、上記第1保存素子は、第1トランジスタの第1主電極と第4スイッチング素子の第2端との間に連結される第2キャパシタと、上記第1キャパシタとを並列に連結することによって構成されるようにしてもよい。

【0023】

30

また、上記第1保存素子は、第4スイッチング素子の第2端と第1トランジスタの第1主電極との間に連結される第1キャパシタによって構成されるようにしてもよい。さらに、上記第2保存素子は、第4スイッチング素子の第2端と第1トランジスタの制御電極との間に連結される第2キャパシタと、上記第1キャパシタとを直列に連結することによって構成されるようにしてもよい。

【0024】

また、上記第1制御信号は、第1選択信号と、第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号とから構成されるようにしてもよい。このとき、第1スイッチング素子は、第1選択信号に応答して第1トランジスタをダイオード形態に連結させる第2トランジスタと、第2選択信号に応答して第1トランジスタをダイオード形態に連結させる第3トランジスタと、を含むようにしてもよい。

40

【0025】

また、上記第2制御信号は、第1選択信号と、第3制御信号とから構成されるようにしてもよい。このとき、画素回路は、第4スイッチング素子に並列に連結される第5スイッチング素子をさらに含み；第4スイッチング素子は、第1選択信号に応答して導通し、第5スイッチング素子は、第3制御信号に応答して導通するようにしてもよい。

【0026】

また、上記第1制御信号は、第1選択信号と、第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号とから構成され、第2制御信号は、第1選択信号と、第3制御信号とから構成されようにもよい。このとき、第1スイッチング素子は、第1選

50

択信号に応答して第1トランジスタをダイオード形態に連結させる第2トランジスタと、第2選択信号に応答して第1トランジスタをダイオード形態に連結させる第3トランジスタとを含み、画素回路は、第4スイッチング素子に並列に連結される第5スイッチング素子をさらに含むようにしてもよい。さらに、第4スイッチング素子は、第1選択信号に応答して導通し、第5スイッチング素子は、第3制御信号に応答して導通するようにしてもよい。

【0027】

また、上記課題を解決するために、本発明の別の観点によれば、走査線からの選択信号に応答してデータ線からのデータ電流を伝達するスイッチング素子と、データ電流に対応した駆動電流を出力し第1及び第2主電極と制御電極とを有するトランジスタと、トランジスタからの駆動電流に対応して発光する発光素子と、を含む画素回路を備えた発光表示装置を駆動する方法が提供される。この発光表示装置を駆動方法は、第1段階と、第2段階と、第3段階とを含む。第1段階では、トランジスタの制御電極と第1主電極との間に構成される第1保存素子に、スイッチング素子からのデータ電流に対応する第1電圧を印加する。次いで、第2段階では、トランジスタの制御電極と第1主電極との間に構成される第2保存素子に、トランジスタのしきい電圧に対応する第2電圧を印加する。さらに、第3段階では、第1及び第2保存素子を連結することにより、トランジスタの制御電極と第1主電極との間の電圧を第3電圧とし、トランジスタからの駆動電流を発光素子に伝達する。このとき、トランジスタからの駆動電流は、第3電圧に対応して決定される。

【0028】

また、上記第1段階で、第1保存素子は、トランジスタの制御電極と第1主電極との間に並列に連結される第1及び第2キャパシタを含むようにしてもよい。また、上記第2段階で、第2保存素子は、第1キャパシタを含むようにしてもよい。さらに、上記第3段階で、第3電圧は、第1及び第2キャパシタを並列に連結することによって決定されるようにしてよい。

【0029】

また、上記第1段階で、第1保存素子は、トランジスタの制御電極と第1主電極との間に連結される第1キャパシタを含むようにしてもよい。また、上記第2段階で、第2保存素子は、第1キャパシタと、第1キャパシタとトランジスタの制御電極との間に連結される第2キャパシタとを含むようにしてもよい。また、上記第3段階で、第3電圧は、第1キャパシタによって決定されるようにしてよい。

【0030】

また、上記第1段階は、第1制御信号に応答してトランジスタがダイオード形態に連結される段階と；第2制御信号の第1レベルに応答して第1保存素子が構成される段階と；走査線からの第1選択信号に応答してデータ電流が伝達される段階と；第1電圧が第1保存素子に印加される段階と；を含むようにしてもよい。また、上記第2段階は、第1制御信号に応答してトランジスタがダイオード形態に連結される段階と；第2制御信号の第2レベルに応答して第2保存素子が構成される段階と；第2電圧が第2保存素子に印加される段階と；を含むようにしてもよい。さらに、上記第3段階は、第2制御信号の第1レベルに応答して第3電圧を保存する第1保存素子が構成される段階と；第3制御信号に応答して駆動電流が発光素子に伝達される段階と；を含むようにしてよい。

【0031】

また、上記第1段階での第1制御信号は第1選択信号で構成されるようにしてよい。また、上記第2段階での第1制御信号は、第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号で構成されるようにしてよい。さらに、上記第1段階での第2制御信号は、第1選択信号で構成され；上記第3段階での第2制御信号は、第3制御信号で構成されるようにしてよい。

【0032】

また、上記第1段階での第2制御信号及び第1制御信号は、第1選択信号で構成されるようにしてよい。また、上記第2段階での第1制御信号は、第1選択信号後に動作許可

10

20

30

40

50

期間を有するその次の走査線からの第2選択信号で構成されようにもよ。また、上記第3段階での第2制御信号は、第3制御信号で構成されるようにもよ。

### 【0033】

また、上記課題を解決するために、本発明の別の観点によれば、画像信号を表すデータ電流を伝達する複数のデータ線と、選択信号を伝達する複数の走査線と、データ線および走査線によって定義される複数の画素に各々形成される複数の画素回路と、を備える発光表示装置の表示パネルが提供される。この表示パネルの画素回路は、発光素子、第1トランジスタ、第1乃至第4スイッチング素子、第1及び第2保存素子を含む。発光素子は、印加される電流に対応して光を発光する。第1トランジスタは、発光素子を発光させるための駆動電流を出力し、第1及び第2主電極と制御電極とを有する。第1スイッチング素子は、第1制御信号に応答して第1トランジスタをダイオード形態に連結する。第2スイッチング素子は、走査線からの第1選択信号に応答してデータ線からのデータ電流を第1トランジスタに伝達する。第3スイッチング素子は、第3制御信号に応答して第1トランジスタからの駆動電流を発光素子に伝達する。第4スイッチング素子は、第2制御信号に応答して動作する。第1保存素子は、第4スイッチング素子がオン状態である時、第1トランジスタの制御電極と第1主電極の間に構成される。第2保存素子は、第4スイッチング素子がオフ状態である時、第1トランジスタの制御電極と第1主電極の間に構成される。この画素回路は、第1期間、第2期間、第3期間の順に動作する。第1期間では、データ電流に対応する第1電圧が第1保存素子に印加される。第2期間では、第1トランジスタのしきい電圧に対応する第2電圧が第2保存素子に印加される。第3期間では、第1及び第2電圧によって第1保存素子に保存された第3電圧によって駆動電流が生成される。

10

### 【0034】

また、上記第1期間では、第1及び第2制御信号と第1選択信号とが動作許可レベルとなり、第3制御信号の動作禁止レベルとなることによって動作するようにもよ。また、上記第2期間では、第1制御信号が動作許可レベルとなり、第2及び第3制御信号と第1選択信号とが動作禁止レベルとなることによって動作するようにもよ。また、上記第3期間では、第2及び第3制御信号が動作許可レベルとなり、第1選択信号と第1制御信号が動作禁止レベルとなることによって動作するようにもよ。

20

### 【0035】

また、上記第1期間での第1制御信号は、第1選択信号で構成され、第2期間での第1制御信号は、第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号で構成されようにもよ。このとき、第1スイッチング素子は、第1選択信号に応答するトランジスタと、第2選択信号に応答するトランジスタと、を含むようにしてよ。

30

### 【0036】

また、上記第1期間での第2制御信号は、第1選択信号で構成され、第3期間での第2制御信号は、第3制御信号で構成されようにもよ。このとき、第4スイッチング素子は、第1選択信号に応答するトランジスタと、第3制御信号に応答するトランジスタとを含むようにしてよ。

### 【0037】

また、上記第1期間での第1制御信号は、第1選択信号で構成され、第2期間での第1制御信号は、第1選択信号後に動作許可期間を有する次の走査線からの第2選択信号で構成され、上記第1期間での第2制御信号は、第1選択信号で構成され、第3期間での第2制御信号は、第3制御信号で構成されようにもよ。このとき、上記第1スイッチング素子は、第1選択信号に応答するトランジスタと、第2選択信号に応答するトランジスタとを含み；上記第4スイッチング素子は、第1選択信号に応答するトランジスタと、第3制御信号に応答するトランジスタとを含むようにしてよ。

40

### 【発明の効果】

### 【0038】

以上説明したように、本発明によれば、比較的大きいデータ電流によって発光素子に流れる微少電流を制御できるので、1ライン時間程度でデータ線を充分に充電できる。また

50

，発光素子に流れる電流は，第1トランジスタのしきい電圧偏差や電子移動度の偏差が補償されているので，多段階階調の自然な感じを再現可能な高解像度・大面積の発光表示装置を実現できる。

【発明を実施するための最良の形態】

【0039】

以下に添付図面を参照しながら，本発明の好適な実施の形態について詳細に説明する。なお，本明細書及び図面において，実質的に同一の機能構成を有する構成要素については，同一の符号を付することにより重複説明を省略する。また，図面において，本発明の実施の形態を明確に説明するために説明と無関係な部分は省略した。また，ある部分が他の部分と連結されていると言うときには，直接的に連結されている場合だけでなく，その中間に他の素子を介して電気的に連結されている場合も含むものとする。

【0040】

(第1の実施形態)

まず，本発明の第1の実施形態にかかる有機EL表示装置及びその画素回路と駆動方法について説明する。

【0041】

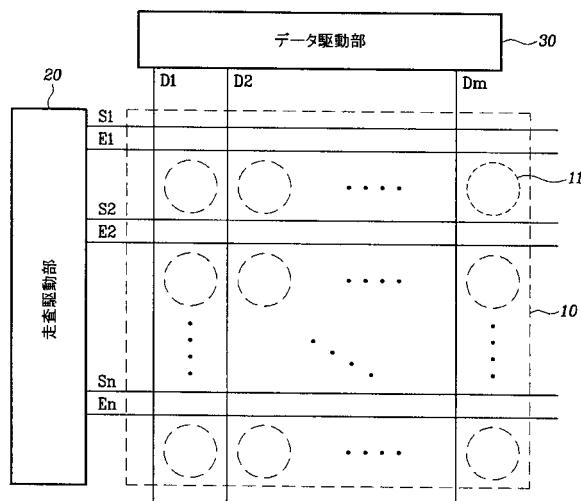

まず，図4に基づいて，本発明の第1の実施形態にかかる有機EL表示装置について詳細に説明する。なお，図4は本発明の第1の実施形態にかかる有機EL表示装置の概略的な構成を示す平面図である。

【0042】

図4に示すように，本実施形態にかかる有機EL表示装置は，例えば，有機EL表示パネル10と，走査駆動部(scan driver)20と，データ駆動部(data driver)30と，を備える。

【0043】

有機EL表示パネル10は，列方向に延長して配される複数のデータ線( $D_1 - D_M$ )と，行方向に延長して配される複数のゲート走査線( $S_1 - S_N$ )及び発光走査線( $E_1 - E_N$ )と，複数の画素回路11とを含む。データ線( $D_1 - D_M$ )は，画像信号として各画素の輝度を示すデータ信号を画素回路11に伝達する。ゲート走査線( $S_1 - S_N$ )は，選択信号を画素回路11に伝達する。画素回路11は，相隣接した二つのデータ線( $D_1 - D_M$ )および相隣接した二つのゲート走査線( $S_1 - S_N$ )によって定義される画素領域に形成されている。また，発光走査線( $E_1 - E_N$ )は画素回路11の発光を制御する発光信号を伝達する。

【0044】

走査駆動部20は，上記両走査線( $S_1 - S_N$ ， $E_1 - E_N$ )に各々選択信号と発光信号を順次に印加する。また，データ駆動部30は，データ線( $D_1 - D_M$ )に画像信号を示すデータ電流を印加する。

【0045】

走査駆動部20及び/又はデータ駆動部30は，例えば，有機EL表示パネル10に対して直接的に電気的に連結される。この場合，走査駆動部20及び/又はデータ駆動部30は，テープキャリアパッケージ(TCP)にチップなどの形態で装着され，表示パネル10に接着して電気的に連結することもでき，或いは，表示パネル10に接着されて電気的に連結されている可撓性印刷回路(FPC)またはフィルムなどにチップなどの形態で装着することもできる。これをCOF(chip on flexible board, chip on film)方式という。また，これとは異なり，走査駆動部20及び/又はデータ駆動部30は，表示パネル10のガラス基板上に直接装着することができ，或いはガラス基板上に走査線，データ線及び薄膜トランジスタと共に層で形成されている駆動回路と代替することも，直接装着することもできる。これをCOG(chip on glass)方式という。

【0046】

次に，図5及び図6に基づいて，本実施形態にかかる有機EL表示装置の画素回路11

10

20

30

40

50

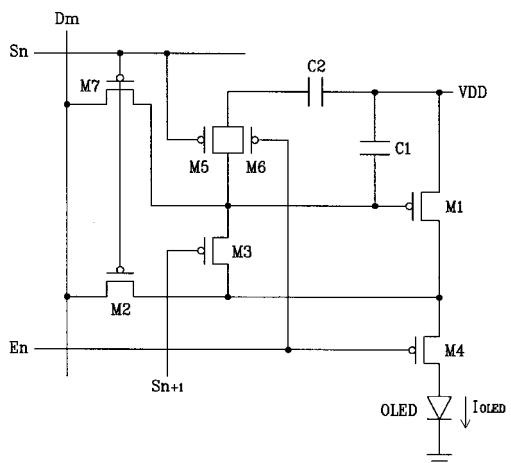

について詳細に説明する。図5は、本実施形態にかかる画素回路11の等価回路図であり、図6は、図5の画素回路11を駆動させるための駆動波形図である。なお、図5では説明の便宜上、m番目データ線( $D_m$ )とn番目走査線( $S_n$ )に連結された画素回路11だけを示してある。

#### 【0047】

図5に示すように、本実施形態にかかる画素回路11は、例えば、有機EL素子(OL ED)と、トランジスタ(M1-M7)と、キャパシタ(C1, C2)とを備える。トランジスタ(M1-M7)は、例えばPMOSトランジスタを用いている。このようなトランジスタは、例えば、表示パネル10のガラス基板上に形成されるゲート電極(制御電極)、ドレイン電極(第2主電極)及びソース電極(第1主電極)を、各々制御電極及び2個の主電極として有する非晶質または多結晶の電界効果トランジスタであるのが好ましいが、部分的にバイポーラトランジスタを用いても差し支えない。

10

#### 【0048】

「トランジスタ(M1)」は、本実施形態にかかる「第1トランジスタ」として構成されている。「トランジスタ(M2)」は、本実施形態にかかる「第2トランジスタ」および「第2スイッチング素子」として構成されている。「トランジスタ(M3)」は、本実施形態にかかる「第3トランジスタ」として構成されている。「トランジスタ(M4)」は、本実施形態にかかる「第3スイッチング素子」として構成されている。「トランジスタ(M5)」は、本実施形態にかかる「第4スイッチング素子」として構成されている。「トランジスタ(M6)」は、本実施形態にかかる「第5スイッチング素子」として構成されている。また、上記「トランジスタ(M2, 3, 7)」は、本実施形態にかかる「第1スイッチング素子」として構成されている。

20

#### 【0049】

「キャパシタ(C1)」は、本実施形態にかかる「第1キャパシタ」として構成されており、「キャパシタ(C2)」は、本実施形態にかかる「第2キャパシタ」として構成されている。また、相互に並列に接続された「キャパシタ(C1)」および「キャパシタ(C2)」は、本実施形態にかかる「第1保存素子」として構成されている。また、並列接続が解除された「キャパシタ(C1)」は、本実施形態にかかる「第2保存素子」として構成されている。

30

#### 【0050】

また、走査線は、例えば、選択信号( $SE_n$ )を入力するゲート走査線( $S_n$ )と、発光信号( $EM_n$ )を入力する発光走査線( $E_n$ )とからなる。また、m番目データ線( $D_m$ )とn番目走査線( $S_n$ )に連結された発光素子11には、現在のゲート走査線( $S_n$ )の次のゲート走査線、即ちn+1番目のゲート走査線( $SE_{n+1}$ )からの選択信号( $SE_n$ )も入力されている。

#### 【0051】

本実施形態にかかる「第1制御信号」は、例えば、ゲート走査線( $S_n$ )からの選択信号( $SE_n$ )と、ゲート走査線( $S_{n+1}$ )からの選択信号( $SE_{n+1}$ )とで構成されている。このうち、選択信号( $SE_n$ )は、本実施形態にかかる「第1選択信号」を構成し、選択信号( $SE_{n+1}$ )は、本実施形態にかかる「第2選択信号」を構成している。

40

#### 【0052】

また、本実施形態にかかる「第2制御信号」は、ゲート走査線( $S_n$ )からの選択信号( $SE_n$ )と、発光走査線( $E_n$ )からの発光信号( $EM_n$ )とで構成されている。また、本実施形態にかかる「第3制御信号」は、発光走査線( $E_n$ )からの発光信号( $EM_n$ )で構成されている。このため、本実施形態にかかる「第2制御信号」は、「第3制御信号」である発光信号( $EM_n$ )と、「第1選択信号」である選択信号( $SE_n$ )とで構成される。

#### 【0053】

このような各信号( $SE_n$ ,  $SE_{n+1}$ ,  $EM_n$ )は、例えば、ローレベルとハイレベルとを有する矩形波となっている。本実施形態では、各信号のローレベルが、本実施形態

50

にかかる「動作許可レベル」および「第1レベル」に該当し，一方，各信号のハイレベルが，本実施形態にかかる「動作禁止レベル」および「第2レベル」に該当する。この「動作許可レベル」は，各信号が入力された素子の動作を許可する（例えばトランジスタMを導通させ，オン状態にする。）信号レベルであり，一方，「動作禁止レベル」は，各信号が入力された素子の動作を禁止する（例えばトランジスタMを遮断させ，オフ状態にする。）信号レベルである。

#### 【0054】

まず，回路構成について説明する。出力電流制御用トランジスタ（M1）は，電源（正電圧VDD）にソース（第1主電極）が連結され，トランジスタ（M5）のドレインにゲート（制御電極）が連結されている。このトランジスタ（M1）は，電源（VDD）から発光素子（OLED）への電流供給をオン／オフすることができる。トランジスタ（M1）は，ゲートとソースの間にかかる電圧（VGS）に対応する電流を駆動電流（I<sub>OLED</sub>）として，トランジスタ（M4）を介して発光素子（OLED）に出力する。トランジスタ（M1）のゲートとドレイン（第2主電極）の間には，トランジスタ（M3）が連結されている。このトランジスタ（M3）は，トランジスタ（M1）のダイオード化を制御している。トランジスタ（M3）は，次に駆動される（n+1）番目の行に位置した画素回路11に連結されたゲート走査線（S<sub>n+1</sub>）からの選択信号（SE<sub>n+1</sub>）に応答して，トランジスタ（M1）をダイオード形態に連結させる。なお，「トランジスタ（M1）をダイオード形態に連結させる」とは，トランジスタ（M1）のドレインとゲートを接続することをいう。かかる接続によって，例えば，トランジスタ（M1）のドレインとゲートに流れる電流の和が，データ線に流れる電流と同一になる。

#### 【0055】

また，トランジスタ（M7）は，データ線（D<sub>m</sub>）とトランジスタ（M1）のゲートの間に連結され，今回駆動されるゲート走査線（S<sub>n</sub>）からの選択信号（SE<sub>n</sub>）に応答して，トランジスタ（M1）をダイオード形態に連結させる。この時，トランジスタ（M7）は，トランジスタ（M3）と同様にトランジスタ（M1）のゲートとドレインの間に連結されることもできる。なお，トランジスタ（M1）をダイオード形態に連結させると，例えば，トランジスタ（M1）のゲートとドレインを連結することにより，トランジスタ（M1）をダイオードとして機能せしめることをいう。

#### 【0056】

キャパシタ（C1）は，トランジスタ（M1）のゲートとソースの間に連結され，キャパシタ（C2）は，電源電圧（VDD）とトランジスタ（M5）の第1端（ソースとして動作）の間に連結される。このようなキャパシタ（C1，C2）は，トランジスタ（M1）のゲートとソースの間の電圧を保存する保存素子として作用する。トランジスタ（M5）の第2端（ドレインとして動作）はトランジスタ（M1）のゲートに連結され，トランジスタ（M6）のソース・ドレインはトランジスタ（M5）に並列連結されている。トランジスタ（M5）はゲート走査線（S<sub>n</sub>）からの選択信号（SE<sub>n</sub>）に応答して，キャパシタ（C1，C2）を並列連結させる。トランジスタ（M6）は，発光走査線（E<sub>n</sub>）からの発光信号（EM<sub>n</sub>）に応答して，キャパシタ（C1，C2）を並列連結する。

#### 【0057】

トランジスタ（M2）はゲート走査線（S<sub>n</sub>）からの選択信号（SE<sub>n</sub>）に応答して，データ線（D<sub>m</sub>）からのデータ電流（I<sub>DATA</sub>）をトランジスタ（M1）に伝達する。トランジスタ（M4）は，トランジスタ（M1）のドレインと有機EL素子（OLED）の間に連結され，発光走査線（E<sub>n</sub>）からの発光信号（EM<sub>n</sub>）に応答して，トランジスタ（M1）の電流（I<sub>OLED</sub>）を有機EL素子（OLED）に伝達する。有機EL素子（OLED）は，トランジスタ（M4）と基準電圧点，例えば接地点（アース）との間に連結されて，印加される電流（I<sub>OLED</sub>）の大きさに対応する強さの光を発光する。

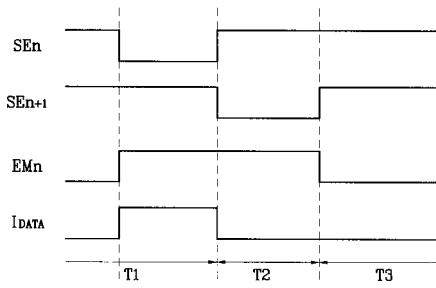

#### 【0058】

次に，図6に基づいて，本実施形態にかかる画素回路11の動作について詳細に説明する。この画素回路11の動作は，例えば，第1段階～第3段階の3段階方式である。具体

10

20

30

40

50

的には、第1期間( $T_1$ )において、データ線を充電する第1段階と、第2期間( $T_2$ )において、しきい電圧 $V_{th}$ を検出する第2段階と、第3期間( $T_3$ )において、出力電流対応電圧 $V_{GS}$ を設定し、発光素子(OLED)が発光する段階とからなる。

【0059】

図6に示すように、まず、第1期間( $T_1$ )のデータ線充電では、キャパシタ( $C_1, C_2$ )に、データ線を充電するための大電流( $I_{DATA}$ )に対応したトランジスタ( $M_1$ )のゲート・ソース間電圧 $V_{GS}$ が、充電される。

【0060】

詳細には、例えばローレベルの現在の走査線( $S_n$ )からの選択信号( $S_{En}$ )によって、トランジスタ( $M_5$ )が導通し、キャパシタ( $C_1, C_2$ )はトランジスタ( $M_1$ )のゲートとソースの間で並列に連結される。さらに、トランジスタ( $M_2, M_7$ )が導通してトランジスタ( $M_1$ )はダイオード形態に連結され、トランジスタ( $M_2$ )が導通して、データ線( $D_m$ )の吸い込みデータ電流( $I_{DATA}$ )が、電源 $VDD$ からトランジスタ( $M_1$ )に流れる。このようにトランジスタ( $M_1$ )にデータ電流( $I_{DATA}$ )が流れるので、データ電流( $I_{DATA}$ )は数式3のように示すことができる。また、数式3を変形すれば、第1期間( $T_1$ )でのゲート・ソース電圧( $V_{GS}(T_1)$ )は、数式4で与えられる。

【0061】

【数3】

10

$$I_{DATA} = \frac{\beta}{2} (|V_{GS}(T1)| - |V_{TH}|)^2 \quad \dots \quad (\text{数式3})$$

20

【0062】

【数4】

30

$$|V_{GS}(T1)| = \sqrt{\frac{2I_{DATA}}{\beta}} + |V_{TH}| \quad \dots \quad (\text{数式4})$$

この数式3および4で、 $\beta$ は定数値であり、 $V_{TH}$ はトランジスタ( $M_1$ )のしきい電圧である。

【0063】

したがって、キャパシタ( $C_1, C_2$ )にはデータ電流( $I_{DATA}$ )に相当する電圧( $V_{GS}(T_1)$ )が保存される。また、ハイレベルの発光信号( $EM_n$ )によってトランジスタ( $M_4$ )が遮断されて、有機EL素子(OLED)への電流が遮断されている。

【0064】

次いで、第2期間( $T_2$ )の $V_{th}$ 検出では、ダイオード連結状態のトランジスタ( $M_1$ )に接続されたキャパシタ( $C_1$ )の過大な上記 $V_{GS}(T_1)$ 電圧が放電され、 $V_{th}$ 電圧まで電圧降下する。

40

【0065】

詳細には、例えばハイレベルの選択信号( $S_{En}$ )に応答してトランジスタ( $M_2, M_5, M_7$ )が遮断され、次の走査線( $S_{n+1}$ )からのローレベルの選択信号( $S_{En+1}$ )に応答してトランジスタ( $M_3$ )が導通する。ハイレベルの発光信号( $EM_n$ )によってトランジスタ( $M_6$ )は遮断されている。遮断されたトランジスタ( $M_5, M_6$ )によってキャパシタ( $C_2$ )は、数式4に示した電圧を保存した状態でフローティングになる。遮断されたトランジスタ( $M_2$ )によってデータ電流( $I_{DATA}$ )が遮断されてい

50

て、導通したトランジスタ (M3) によってトランジスタ (M1) はダイオード連結状態に維持されるので、キャパシタ (C1) にはトランジスタ (M1) のしきい電圧 ( $V_{TH}$ ) が保存される。整理すると、キャパシタ (C1) の電圧によりM1が導通し、次回選択信号 ( $SE_{n+1}$ ) に応答してトランジスタ (M3) も導通している。従って、キャパシタ (C1) に蓄えられた電荷は、徐々に放電して、残存電圧がしきい電圧 ( $V_{TH}$ ) に近い値で保存される。

## 【0066】

次いで、第3期間 ( $T_3$ ) の出力電流対応  $V_{GS}$  設定・発光では、キャパシタ (C1, C2) が並列連結されて、例えば、上記  $V_{GS}$  ( $T_1$ ) と  $V_{TH}$  の中間値が新しい充電電圧となり、これが出力電流対応  $V_{GS}$  ( $T_3$ ) として使われ、出力電流が有機EL素子 (OLED) に供給されて発光する。

## 【0067】

詳細には、ハイレベルの選択信号 ( $SE_{n+1}$ ) に応答してトランジスタ (M3) が遮断され、ローレベルの発光信号 ( $EM_n$ ) に応答してトランジスタ (M4, M6) が導通する。トランジスタ (M6) が導通すればキャパシタ (C1, C2) は並列連結されるため、キャパシタ (C1, C2) の結合によって第3期間 ( $T_3$ ) でのトランジスタ (M1) のゲート-ソース電圧 ( $V_{GS}$  ( $T_3$ )) は数式5のようになる。

## 【0068】

## 【数5】

10

$$|V_{GS}(T3)| = |V_{TH}| + \frac{C_2}{C_1 + C_2} (|V_{GS}(T1)| - |V_{TH}|) \quad \dots \text{ (数式5)}$$

この数式5で、 $C_1$  及び  $C_2$  は、各々キャパシタ (C1, C2) のキャパシタンス (静電容量) である。

## 【0069】

したがって、トランジスタ (M1) に流れる電流 ( $I_{OLED}$ ) は、数式6のようになる。この電流 ( $I_{OLED}$ ) が導通したトランジスタ (M4) によって有機EL素子 (OLED) に供給されて発光が行われる。つまり、第3期間 ( $T_3$ ) ではキャパシタ (C1, C2) の結合によって電圧が分配され、有機EL素子 (OLED) の発光が行われる。

## 【0070】

## 【数6】

30

$$I_{OLED} = \frac{\beta}{2} \left\{ \frac{C_2}{C_1 + C_2} (|V_{GS}(T1)| - |V_{TH}|) \right\}^2 = \left( \frac{C_2}{C_1 + C_2} \right)^2 I_{DATA} \quad \dots \text{ (数式6)}$$

40

## 【0071】

数式6に示すように、有機EL素子 (OLED) に供給される電流 ( $I_{OLED}$ ) は、トランジスタ (M1) のしきい電圧 ( $V_{TH}$ ) や移動度に関係なく決定されるので、しきい電圧の偏差や移動度の偏差を補償できる。また、有機EL素子 (OLED) に供給される電流 ( $I_{OLED}$ ) は、データ電流 ( $I_{DATA}$ ) に比べて ( $C_2 / (C_1 + C_2)$ ) の二乗倍だけ小さい値である。例えば、 $C_1$  が  $C_2$  のM倍 ( $C_2 = M * C_1$ ) であれば、電流 ( $I_{OLED}$ ) に対して  $(M+1)^2$  倍だけ大きいデータ電流 ( $I_{DATA}$ ) で有機EL素子 (OLED) に流れる微細電流 ( $I_{OLED}$ ) を制御することができるので、安定して多段階階調を表現することができる。さらに、データ線 ( $D_1 - D_m$ ) に大きいデ

50

ータ電流 ( $I_{DATA}$ ) を供給するので、データ線の充電時間を十分に確保することができる。また、この第1の実施形態では、トランジスタ ( $M_1 - M_7$ ) が全て同一タイプのトランジスタであるので、表示パネル10のガラス基板上に薄膜トランジスタを形成する工程を簡単にすることができる。また、キャパシタ ( $C_1, C_2$ ) の形状を同幅・異長・並列配置(長い方を折り返し形状にしても良い)にして、上記の倍率Mのバラツキを軽減することも可能である。

#### 【0072】

このような第1の実施形態では、トランジスタ ( $M_1 - M_7$ ) は、PMOSトランジスタで構成されたが、かかる例に限定されず、例えば、NMOSトランジスタなどで構成することもできる。このようにトランジスタ ( $M_1 - M_5$ ) をNMOSトランジスタで構成する場合には、例えば、図5の画素回路11におけるトランジスタ ( $M_1$ ) のソースを、電源電位 ( $VDD$ ) の代りに負側の基準電位に連結し、有機EL素子 (OLED) のカソードをトランジスタ ( $M_4$ ) に連結し、アノードを正側の電源電位 ( $VDD$ ) に連結する。そして、選択信号 ( $SE_n, SE_{n+1}$ ) 及び発光信号 ( $EM_n$ ) は、例えば、図6に示した駆動波形に対して反転した形態を有する。このようにトランジスタ ( $M_1 - M_5$ ) をNMOSトランジスタで実現する場合についての詳細な説明は、上記第1の実施形態の説明から容易に分かるので省略する。また、例えば、トランジスタ ( $M_1 - M_7$ ) は、PMOSとNMOSの組み合わせ、または類似な機能をする他のスイッチング素子などで構成することもできる。

#### 【0073】

なお、上記第1の実施形態では例えば7個のトランジスタ ( $M_1 - M_7$ ) を使用して画素回路11を構成したが、制御信号を伝達する走査線を追加することにより、トランジスタの設置数を低減することもできる。以下に、このような実施形態について図7～図9を参照して詳細に説明する。

#### 【0074】

##### (第2の実施の形態)

次に、本発明の第2の実施形態にかかる有機EL表示装置及びその画素回路と駆動方法について説明する。第2の実施形態にかかる有機EL表示装置は、第1の実施形態にかかる有機EL表示装置と比して、画素回路11の構成の一部が異なる点で相違するのみであり、その他の機能構成は上記第1の実施形態の場合と略同一であるので、その説明は省略する。

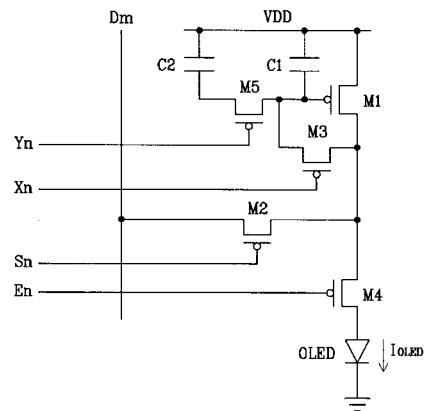

#### 【0075】

まず、図7及び図8に基づいて、本発明の第2の実施形態にかかる有機EL表示装置の画素回路11について詳細に説明する。なお、図7は、本実施形態にかかる画素回路11の等価回路図であり、図8は、図7の画素回路11を駆動させるための駆動波形図である。なお、図7では説明の便宜上、m番目データ線 ( $D_m$ ) とn番目走査線 ( $S_n$ ) に連結された画素回路だけを示してある。

#### 【0076】

図7に示すように、本実施形態にかかる画素回路11は、図5に示した画素回路11から、トランジスタ ( $M_6$ ) (第5スイッチング素子)とトランジスタ ( $M_7$ ) とが除去され、新たに、第3及び第4走査線 ( $X_n, Y_n$ ) が追加されている。さらに、トランジスタ ( $M_3$ ) のゲートは、第3走査線 ( $X_n$ ) に連結され、第3走査線 ( $X_n$ ) からの制御信号 ( $CS1_n$ ) に応答して、トランジスタ ( $M_1$ ) をダイオード形態に連結させる。トランジスタ ( $M_5$ ) のゲートは、第4走査線 ( $Y_n$ ) に連結され、第4走査線 ( $Y_n$ ) からの制御信号 ( $CS2_n$ ) に応答してキャパシタ ( $C_1, C_2$ ) を並列連結させる。

#### 【0077】

本実施形態にかかる「第1制御信号」は、例えば、ゲート走査線 ( $S_n$ ) からの選択信号 ( $SE_n$ ) と、第3走査線 ( $X_n$ ) からの制御信号 ( $CS1_n$ ) とで構成されている。また、本実施形態にかかる「第2制御信号」は、例えば、第4走査線 ( $Y_n$ ) からの制御信号 ( $CS2_n$ ) で構成されている。また、本実施形態にかかる「第3制御信号」は、発

10

20

30

40

50

光走査線 ( $E_n$ ) からの発光信号 ( $EM_n$ ) で構成されている。なお、その他の対応関係は、第1の実施形態の場合と略同一である。

#### 【0078】

次に、図8に基づいて、本実施形態にかかる画素回路11の動作について詳細に説明する。この画素回路11の動作は、例えば、上記第1の実施形態と同様に、第1段階～第3段階の3段階方式である。

#### 【0079】

図8に示すように、まず、第1期間 ( $T_1$ ) では、ローレベルの制御信号 ( $CS_{1n}$ ,  $CS_{2n}$ ) によってトランジスタ ( $M_3$ ,  $M_5$ ) が導通し、トランジスタ ( $M_1$ ) はダイオード形態に連結され、キャパシタ ( $C_1$ ,  $C_2$ ) はキャパシタ ( $C_1$ ,  $C_2$ ) はトランジスタ ( $M_1$ ) のゲートとソースの間で並列連結される。そしてローレベルの選択信号 ( $SE_n$ ) によってトランジスタ ( $M_2$ ) が導通して、データ線 ( $D_m$ ) の吸い込みデータ電流 ( $I_{DATA}$ ) が、トランジスタ ( $M_1$ ) からトランジスタ ( $M_2$ ) に流れる。したがって、第1の実施形態の第1期間 ( $T_1$ ) と同様に、トランジスタ ( $M_1$ ) のゲート-ソース電圧 ( $V_{GS}(T_1)$ ) は、上記式4のように表され、この電圧 ( $V_{GS}(T_1)$ ) は、キャパシタ ( $C_1$ ,  $C_2$ ) に保存される。また、ハイレベルの発光信号 ( $EM_n$ ) によってトランジスタ ( $M_4$ ) が遮断されて、有機EL素子 (OLED) への電流が遮断されている。

#### 【0080】

次いで、第2期間 ( $T_2$ ) では、ハイレベルの制御信号 ( $CS_{2n}$ ) によってトランジスタ ( $M_5$ ) が遮断され、キャパシタ ( $C_2$ ) は電圧が充電された状態でフローティングになる。また、ハイレベルの選択信号 ( $SE_n$ ) によりトランジスタ ( $M_2$ ) が遮断されて、データ電流 ( $I_{DATA}$ ) が遮断される。したがって、第1の実施形態の第2期間 ( $T_2$ ) と同様に、キャパシタ ( $C_1$ ) にはトランジスタ ( $M_1$ ) のしきい電圧 ( $V_{TH}$ ) が保存される。

#### 【0081】

次いで、第3期間 ( $T_3$ ) では、ハイレベルの制御信号 ( $CS_{1n}$ ) によってトランジスタ ( $M_3$ ) が遮断され、ローレベルの制御信号 ( $CS_{2n}$ ) に応答してトランジスタ ( $M_5$ ) が導通する。トランジスタ ( $M_5$ ) が導通すればキャパシタ ( $C_1$ ,  $C_2$ ) は並列連結され、第3期間 ( $T_3$ ) でのトランジスタ ( $M_1$ ) のゲート-ソース電圧 ( $V_{GS}(T_3)$ ) は、第1の実施形態の第3期間 ( $T_3$ ) と同様に、上記式5で与えられる。

#### 【0082】

このように、第2の実施形態にかかる画素回路11は、第1の本実施形態にかかる画素回路11と同様に動作するが、第1の本実施形態の場合と比べて、トランジスタの設置個数を低減することができる。

#### 【0083】

かかる第2の実施形態では、第1の本実施形態の場合と比べて、トランジスタの個数を2個減らすために走査線の本数を2本増加させたが、かかる例に限定されず、トランジスタの個数を1個減らすために走査線の本数を1本増加させるように設計変更してもよい。

#### 【0084】

例えば、図5の画素回路11におけるトランジスタ ( $M_6$ ) を除去し、図7のようにトランジスタ ( $M_5$ ) のゲートを制御信号 ( $CS_{2n}$ ) を伝達する走査線 ( $Y_n$ ) に連結することができる。これにより、制御信号 ( $CS_{2n}$ ) がローレベルである期間 ( $T_1$ ,  $T_3$ ) でトランジスタ ( $M_5$ ) が導通し、キャパシタ ( $C_1$ ,  $C_2$ ) が並列連結される。

#### 【0085】

一方、図5の画素回路におけるトランジスタ ( $M_7$ ) を除去し、図7のようにトランジスタ ( $M_3$ ) のゲートを制御信号 ( $CS_{1n}$ ) を伝達する走査線 ( $X_n$ ) に連結することもできる。これにより、制御信号 ( $CS_{1n}$ ) がローレベルである期間 ( $T_1$ ,  $T_2$ ) でトランジスタ ( $M_3$ ) が導通し、トランジスタ ( $M_1$ ) がダイオード形態に連結される。

#### 【0086】

10

20

30

40

50

このように、トランジスタの個数を1個低減し、走査線の本数を1本増加させるように設計変更しても、第1実施形態のように画素回路11の動作が略同一になる。

#### 【0087】

また、以上のような第1及び第2の実施形態では、2個のキャパシタ(C1, C2)を電源電圧(VDD)とトランジスタ(M1)のゲートの間に、並列に連結したが、かかる例に限定されない。例えば、2個のキャパシタ(C1, C2)を直列に連結することもできる。以下に、このような実施形態について、図9を参照して詳細に説明する。

#### 【0088】

##### (第3の実施の形態)

次に、本発明の第3の実施形態にかかる有機EL表示装置及びその画素回路と駆動方法について説明する。第3の実施形態にかかる有機EL表示装置は、第2の実施形態にかかる有機EL表示装置と比して、画素回路のキャパシタ(C1, C2)及びトランジスタ(M5)の連結状態が異なる点で相違するのみであり、その他の機能構成は上記第2の実施形態の場合と略同一であるので、その説明は省略する。

10

#### 【0089】

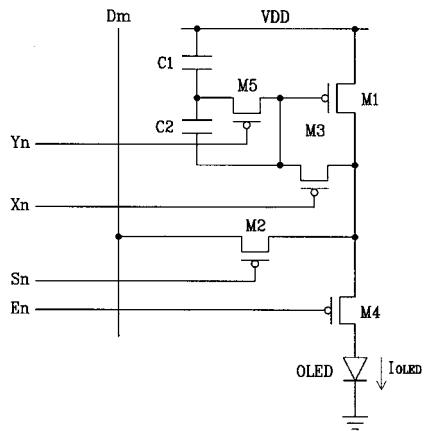

まず、図9に基づいて、本発明の第3の実施形態にかかる有機EL表示装置の画素回路11について詳細に説明する。なお、図9は、本実施形態にかかる画素回路11の等価回路図である。なお、図9では説明の便宜上、m番目データ線(D<sub>m</sub>)とn番目走査線(S<sub>n</sub>)に連結された画素回路だけを示してある。

20

#### 【0090】

図9に示すように、本発明の第3の実施形態にかかる画素回路11は、キャパシタ(C1, C2)及びトランジスタ(M5)の連結状態を除くと、第2実施形態にかかる画素回路11と略同一な構造を有する。詳しく説明すれば、第3の実施形態では、2個のキャパシタ(C1, C2)は、電源電圧(VDD)とトランジスタ(M1)のゲートの間に直列に連結され、トランジスタ(M5)は、キャパシタ(C1, C2)の接点とトランジスタ(M1)のゲートの間に連結されている。

20

#### 【0091】

「キャパシタ(C1)」は、本実施形態にかかる「第1キャパシタ」として構成されており、「キャパシタ(C2)」は、本実施形態にかかる「第2キャパシタ」として構成されている。また、「キャパシタ(C1)」は、本実施形態にかかる「第1保存素子」として構成されている。また、相互に直列に接続された「キャパシタ(C1)」および「キャパシタ(C2)」は、本実施形態にかかる「第2保存素子」として構成されている。なお、その他の対応関係は、第2の実施形態の場合と略同一である。

30

#### 【0092】

この第3実施形態にかかる画素回路11は、第2実施形態と略同一な駆動波形によって駆動される。以下に、図8および図9に基づいて、本実施形態にかかる画素回路11の動作について詳細に説明する。この画素回路11の動作は、例えば、上記第1の実施形態と同様に、第1段階～第3段階の3段階方式である。第3の実施形態にかかる画素回路11に入力される制御信号等は、図8に示した第2の実施形態の場合と略同一であるので、図示は省略する。

40

#### 【0093】

まず、第1期間(T1)では、ローレベルの制御信号(CS1<sub>n</sub>)によってトランジスタ(M3)が導通し、トランジスタ(M1)はダイオード形態に連結される。また、ローレベルの制御信号(CS2<sub>n</sub>)によってトランジスタ(M5)が導通し、キャパシタ(C2)の電圧はゼロボルトになる。そして、トランジスタ(M2)がローレベルの選択信号(SE<sub>n</sub>)に応答して、データ線(D<sub>m</sub>)の吸い込みデータ電流(I<sub>DAT\_A</sub>)がトランジスタ(M1)からトランジスタ(M2)に流れる。従って、このデータ電流(I<sub>DAT\_A</sub>)によってトランジスタ(M1)のゲート-ソース電圧(V<sub>GS</sub>(T1))は、上記式4のように表され、この電圧(V<sub>GS</sub>(T1))は、キャパシタ(C1, C2)に保存される。また、ハイレベルの発光信号(EM<sub>n</sub>)によってトランジスタ(M4)が遮断さ

50

れて、有機EL素子(OLED)への電流が遮断されている。

【0094】

次いで、第2期間(T2)では、制御信号(CS2n)がハイレベルになってトランジスタ(M5)が遮断され、選択信号(SEn)がハイレベルになってトランジスタ(M2)も遮断される。そしてデータ電流(IDATA)がゼロアンペアになり、導通しているトランジスタ(M3)によってトランジスタ(M1)はダイオード形態に連結されたままで、直列連結されたキャパシタ(C1, C2)の両端にはトランジスタ(M1)のしきい電圧(VTH)が印加される。従って、上記数式4に示した電圧(VGS(T1))を充電していたキャパシタ(C1)の電圧(Vc1)は、キャパシタ(C1, C2)の結合によって、次の数式7のようになる。

10

【0095】

【数7】

$$V_{C1} = |V_{TH}| + \frac{C_1}{C_1 + C_2} (|V_{GS}(T1)| - |V_{TH}|) \quad \dots \text{ (数式7)}$$

【0096】

次いで、第3期間(T3)では、ハイレベルの制御信号(CS1n)に応答してトランジスタ(M3)が遮断され、ローレベルの制御信号(CS2n)及び発光信号(EMn)によってトランジスタ(M5, M4)が導通する。トランジスタ(M3)が遮断されてトランジスタ(M5)が導通すれば、キャパシタ(C1)の電圧(Vc1)が、第3期間(T3)でのトランジスタ(M1)のゲート-ソース電圧(VGS(T3))になる。従って、トランジスタ(M1)に流れる電流(I<sub>OLED</sub>)は、次の数式8のようになり、この電流(I<sub>OLED</sub>)がトランジスタ(M4)を通って有機EL素子(OLED)に供給され、有機EL素子(OLED)が発光する。

20

【0097】

【数8】

$$I_{OLED} = \frac{\beta}{2} \left\{ \frac{C_1}{C_1 + C_2} (|V_{GS}(T1)| - |V_{TH}|) \right\}^2 = \left( \frac{C_1}{C_1 + C_2} \right)^2 I_{DATA} \quad \dots \text{ (数式8)}$$

30

【0098】

このように本発明の第3実施形態でも、第1実施形態と同様に、有機EL素子(OLED)に供給される電流(I<sub>OLED</sub>)は、トランジスタ(M1)のしきい電圧(V<sub>TH</sub>)や移動度に関係なく決定される。また、有機EL素子(OLED)に供給される電流(I<sub>OLED</sub>)は、データ電流(IDATA)に比べて( $C_2 / (C_1 + C_2)$ )の二乗倍だけ小さい値である。このため、電流(I<sub>OLED</sub>)に対して( $C_1 + C_2 / C_1$ )の二乗倍だけ大きいデータ電流(IDATA)によって、有機EL素子(OLED)に流れる微細電流(I<sub>OLED</sub>)を制御することができるので、多段階階調を表現することができる。そしてデータ線(D<sub>1</sub> - D<sub>m</sub>)に大きいデータ電流(IDATA)を供給するので、データ線の充電時間を十分に確保することができる。

40

【0099】

このような第3の実施形態では、トランジスタ(M1 - M5)は、PMOSトランジスタで構成されたが、これ以外にも、例えば、NMOS、またはPMOSとNMOSの組み合わせなどで構成することができ、また、類似な機能をする他のスイッチング素子などで

50

構成することもできる。

【0100】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されることは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それについても当然に本発明の技術的範囲に属するものと了解される。

【図面の簡単な説明】

【0101】

【図1】有機電界発光素子の概念図である。

【図2】従来の電圧指定方式の画素回路を示す等価回路図である。

10

【図3】従来の電流指定方式の画素回路を示す等価回路図である。

【図4】本発明の第1の実施形態にかかる有機EL表示装置の概略的な構成を示す平面図である。

【図5】本発明の第1の実施形態にかかる画素回路を示す等価回路図である。

【図6】図5に示した画素回路を駆動するための駆動波形図である。

【図7】本発明の第2の実施形態にかかる画素回路を示す等価回路図である。

【図8】図7に示した画素回路を駆動するための駆動波形図である。

【図9】本発明の第3の実施形態にかかる画素回路を示す等価回路図である。

【符号の説明】

【0102】

20

10 : 有機EL表示パネル

11 : 画素回路

20 : 走査駆動部

30 : データ駆動部

C1, C2 : キャパシタ

M1 - M7 : トランジスタ

OLED : 有機EL素子

D1 - DM : データ線

E1 - EN, S1 - SN, Xn, Yn : 走査線

SEn, SEN+1 : 選択信号

30

EMn : 発光信号

CS1n : 制御信号

CS2n : 制御信号

IDATA : データ電流

IOLED : 電流

VGS(T1), VGS(T3) : ゲート-ソース電圧

VDD : 電源電圧

VTH : しきい電圧

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 D

G 09 G 3/20 6 4 2 A

H 03 K 17/78 E

H 05 B 33/14 A

(56)参考文献 特開2003-177709 (JP, A)

特開2005-067294 (JP, A)

特開2004-310006 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

H 05 B 33 / 00 - 33 / 28

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发光显示装置，发光显示装置的驱动方法，发光显示装置的显示面板                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP4153855B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2008-09-24 |

| 申请号            | JP2003337968                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2003-09-29 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 權 五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H03K17/78 H01L51/50 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.H G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A H03K17/78.E H05B33/14.A G09G3/20.621.F G09G3/3241 G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291 G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC11 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD08 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/BA13 5C380/BA19 5C380/BA20 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB31 5C380/CC02 5C380/CC03 5C380/CC13 5C380/CC18 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC53 5C380/CC61 5C380/CC62 5C380/CC63 5C380/CC64 5C380/CC65 5C380/CD012 5C380/CD014 5C380/CD025 5C380/CD026 5C380/CD027 5C380/DA02 5C380/DA06 5J050/AA01 5J050/CC08 5J050/DD08 5J050/EE02 5J050/EE31 5J050/FF02 |         |            |

| 优先权            | 1020030020433 2003-04-01 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | <a href="#">JP2004310014A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

提供一种能够补偿晶体管的阈值电压和电子迁移率并且能够对数据线充分充电的发光显示装置。在由数据电流驱动的发光显示装置的像素电路中，首先，对应于数据电流的第一电压施加到形成在驱动晶体管M1的栅极和源极之间的电容器C1和C2。然后，对应于驱动晶体管的阈值电压的第二电压被施加到第二电容器C1。然后，通过连接电容器C1，C2并联，栅极和驱动晶体管M1的源极和所述第三电压，用于从所述驱动晶体管M1的驱动电流传递到发光元件之间的电压。此时，对应于第三电压确定在发光元件OLED中流动的驱动电流。因此，可以通过相对大的数据电流来控制发光显示装置的发光元件的发光量。点域5