(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-203081

(P2014-203081A)

(43) 公開日 平成26年10月27日(2014.10.27)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 641D 5C380  |

| <b>H05B 33/10</b> (2006.01) | G09G 3/20 | 642A        |

| <b>H05B 33/22</b> (2006.01) | G09G 3/20 | 670Q        |

審査請求 未請求 請求項の数 20 O L (全 32 頁) 最終頁に続く

|              |                            |          |                                                              |

|--------------|----------------------------|----------|--------------------------------------------------------------|

| (21) 出願番号    | 特願2014-72420 (P2014-72420) | (71) 出願人 | 512187343                                                    |

| (22) 出願日     | 平成26年3月31日 (2014.3.31)     |          | 三星ディスプレイ株式会社                                                 |

| (31) 優先権主張番号 | 10-2013-0035459            |          | Samsung Display Co., Ltd.                                    |

| (32) 優先日     | 平成25年4月1日 (2013.4.1)       |          | 大韓民国京畿道龍仁市器興区三星二路95                                          |

| (33) 優先権主張国  | 韓国 (KR)                    |          | 95, Samsung 2 Ro, Giheng-Gu, Yongin-City, Gyeonggi-Do, Korea |

|              |                            | (74) 代理人 | 100070024                                                    |

|              |                            |          | 弁理士 松永 宣行                                                    |

|              |                            | (74) 代理人 | 100159042                                                    |

|              |                            |          | 弁理士 辻 徹二                                                     |

|              |                            | (72) 発明者 | 康 起 寧                                                        |

|              |                            |          | 大韓民国京畿道龍仁市器興区三星二路95                                          |

|              |                            |          | 三星ディスプレイ株式会社内                                                |

|              |                            |          | 最終頁に続く                                                       |

(54) 【発明の名称】有機発光表示装置、該有機発光表示装置のリペア方法及び該有機発光表示装置の駆動方法

## (57) 【要約】

【課題】有機発光表示装置、該有機発光表示装置のリペア方法及び該有機発光表示装置の駆動方法を提供する。

【解決手段】有機発光表示装置、該有機発光表示装置のリペア方法及び該有機発光表示装置の駆動方法に係り、該有機発光表示装置は、列方向及び行方向に配置され、発光素子と、該発光素子と連結された第1画素回路と、を具備する複数の発光画素；各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素；及び各列ごとに形成されたリペア線；を含み、複数の発光画素のうち、リペア線に連結された発光画素と、リペア線に連結されたダミー画素とに同一のデータ信号が一定時間差で供給され、複数の発光画素が同時に発光することを特徴とする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素と、

各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素と、各列ごとに形成されたリペア線と、を含み、

前記複数の発光画素のうち、前記リペア線に連結された発光画素と、前記リペア線に連結されたダミー画素とに同一のデータ信号が一定時間差で供給され、前記複数の発光画素が同時に発光することを特徴とする有機発光表示装置。

**【請求項 2】**

前記ダミー画素は、各列の最初の行及び最後の行のうち少なくとも1行に形成されたことを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 3】**

前記発光画素は、表示部に形成され、前記ダミー画素は、非表示部に形成されることを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 4】**

前記第1画素回路と前記第2画素回路は、同一であることを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 5】**

前記リペア線に連結された発光画素は、発光素子と第1画素回路とが切り離されたことを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 6】**

前記発光素子は、アノード電極、カソード電極、及び前記アノード電極とカソード電極との間の発光層を含み、

前記リペア線に連結された発光画素は、発光素子のアノード電極と連結された第1画素回路の配線が切り離されたことを特徴とする請求項5に記載の有機発光表示装置。

**【請求項 7】**

前記リペア線に連結された発光画素は、発光素子のアノード電極と接触する第1導電部、並びに前記第1導電部及び前記リペア線を連結する第1コンタクト金属を含み、

前記リペア線に連結されたダミー画素は、第2画素回路から延長された第2導電部、並びに前記第2導電部及び前記リペア線を連結する第2コンタクト金属を含むことを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 8】**

前記第1導電部及び前記リペア線は、同一層に形成されたことを特徴とする請求項7に記載の有機発光表示装置。

**【請求項 9】**

前記リペア線は、前記第1画素回路並びに前記第2画素回路を構成する薄膜トランジスタのソース電極及びドレイン電極と同一層に同一物質から形成されたことを特徴とする請求項7に記載の有機発光表示装置。

**【請求項 10】**

前記リペア線は、前記アノード電極と同一層に同一物質から形成されたことを特徴とする請求項7に記載の有機発光表示装置。

**【請求項 11】**

前記リペア線に連結された発光画素の発光素子を構成するアノード電極と接触する第1導電部と前記リペア線との間、及び前記リペア線に連結されたダミー画素の第2画素回路と連結された第2導電部と前記リペア線との間に少なくとも1層の絶縁膜が形成され、

前記第1導電部及び前記リペア線、並びに前記第2導電部及び前記リペア線がレーザ・ウェルディングによって電気的に連結されたことを特徴とする請求項1に記載の有機発光表示装置。

**【請求項 12】**

10

20

30

40

50

前記第1導電部と前記第2導電部は、前記第1画素回路及び前記第2画素回路を構成する薄膜トランジスタのゲート電極と同一層に同一物質から形成され、前記リペア線は、前記薄膜トランジスタのソース電極及びドレイン電極と同一層に同一物質から形成されたことを特徴とする請求項11に記載の有機発光表示装置。

【請求項13】

列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素、各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素、及び各列ごとに形成されたリペア線を含む有機発光表示装置の駆動方法において、

前記複数の発光画素と前記ダミー画素とに順にデータ信号を供給するが、前記複数の発光画素のうちリペア線に連結された発光画素と、前記リペア線に連結されたダミー画素には、同一のデータ信号が供給される走査段階と、

前記データ信号に対応する駆動電流により、前記複数の発光画素の発光素子が同時に発光する発光段階と、を含む有機発光表示装置の駆動方法。

【請求項14】

前記ダミー画素は、各列の最初の行及び最後の行のうち少なくとも1行に形成されたことを特徴とする請求項13に記載の有機発光表示装置の駆動方法。

【請求項15】

前記走査段階が、前記発光段階より時間的に先行することを特徴とする請求項13に記載の有機発光表示装置の駆動方法。

【請求項16】

前記走査段階及び前記発光段階が、少なくとも一部時間的に重畠されることを特徴とする請求項13に記載の有機発光表示装置の駆動方法。

【請求項17】

列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素、各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素、及び各列ごとに形成されたリペア線を含み、前記複数の発光画素が同時に発光する有機発光表示装置のリペア方法において、

前記複数の発光画素のうち第1不良画素の発光素子と、第1画素回路とを切り離す段階と、

前記第1不良画素と同一列に配置されたリペア線と、前記第1不良画素の発光素子とを連結する段階と、

前記第1不良画素に供給されるデータ信号と同一のデータ信号を供給され、前記供給されたデータ信号に対応する駆動電流を、前記リペア線を介して、前記第1不良画素の発光素子に供給し、前記第1不良画素が、前記複数の発光画素と同時に発光するように、前記第1不良画素と同一列に配置された第1ダミー画素の第2画素回路を、前記リペア線と連結する段階と、を含むことを特徴とする有機発光表示装置のリペア方法。

【請求項18】

前記第1不良画素の連結段階は、前記第1不良画素の発光素子を構成するアノード電極と連結された第1導電部、並びに前記リペア線の前記第1導電部及び前記リペア線を連結する第1コンタクト金属を形成する段階を含み、

前記第1ダミー画素の連結段階は、前記第1ダミー画素の第2画素回路と連結された第2導電部、並びに前記リペア線の前記第2導電部及び前記リペア線を連結する第2コンタクト金属を形成する段階と、を含むことを特徴とする請求項17に記載の有機発光表示装置のリペア方法。

【請求項19】

前記第1不良画素の連結段階は、前記第1不良画素の発光素子を構成するアノード電極と連結された第1導電部、及び前記第1導電部と少なくとも1層の絶縁膜によって絶縁された前記リペア線をレーザ・ウェルディングによって電気的に連結する段階を含み、

前記第1ダミー画素の連結段階は、前記第1ダミー画素の第2画素回路と連結された第

10

20

30

40

50

2導電部、及び前記導電部と少なくとも1層の絶縁膜によって絶縁された前記リペア線をレーザ・ウェルディングによって電気的に連結する段階を含むことを特徴とする請求項17に記載の有機発光表示装置のリペア方法。

#### 【請求項20】

前記第1不良画素と同一列に配置された第2不良画素の発光素子と、第1画素回路とを切り離す段階と、

前記第1不良画素と、前記第2不良画素との間のリペア線を分離する段階と、

前記第2不良画素に供給されるデータ信号と同一のデータ信号を供給され、前記供給されたデータ信号に対応する駆動電流を、前記リペア線を介して、前記第2不良画素の発光素子に供給し、前記第2不良画素が、前記複数の発光画素と同時に発光するように、前記第1不良画素と同一列に配置された第2ダミー画素の第2画素回路を、前記リペア線の分離によって、第1不良画素が連結されていないリペア線と連結する段階と、をさらに含むことを特徴とする請求項17に記載の有機発光表示装置のリペア方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、有機発光表示装置、該有機発光表示装置のリペア方法及び該有機発光表示装置の駆動方法に関する。

##### 【背景技術】

##### 【0002】

特定画素で不良が発生する場合、特定画素は、走査信号及びデータ信号と係わり合いなく、常に光を発生させる。このように、画素で常に発光する画素は、観察者に明点(bright spot)（または輝点(hot spot)）として認識され、この明点は、視認性が高く、観察者に容易に観測される。従って、従来には、視認性が高い明点化された不良画素を暗点化するようにリペアすることにより、不良画素に対する認識が大きくならないようにした。しかしながら、画素内の回路が複雑になることにより、回路不良による明点を克服し難いという問題がある。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

本発明が解決しようとする課題は、パネル内にリダンダンシ・パターンを各列ごとに形成し、リダンダンシ・パターンを利用して、不良画素を正常駆動することができる表示装置を提供するものである。

##### 【課題を解決するための手段】

##### 【0004】

本発明の一実施形態による有機発光表示装置は、列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素；各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素；及び各列ごとに形成されたりペア線；を含み、前記複数の発光画素のうち、前記リペア線に連結された発光画素と、前記リペア線に連結されたダミー画素とに同一のデータ信号が一定時間差で供給され、前記複数の発光画素が同時に発光することを特徴とする。

##### 【0005】

前記ダミー画素は、各列の最初の行及び最後の行のうち少なくとも1行に形成されてもよい。

##### 【0006】

前記発光画素は、表示部に形成され、前記ダミー画素は、非表示部に形成されてもよい。

##### 【0007】

前記第1画素回路と前記第2画素回路は、同一である。

##### 【0008】

10

20

30

40

50

前記リペア線に連結された発光画素は、発光素子と第1画素回路とが切り離されたことを特徴とする。前記発光素子は、アノード電極、カソード電極、及び前記アノード電極とカソード電極との間の発光層を含み、前記リペア線に連結された発光画素は、発光素子のアノード電極と連結された第1画素回路の配線が切り離されたことを特徴とする。

【0009】

一実施形態として、前記リペア線に連結された発光画素は、発光素子のアノード電極と接触する第1導電部、並びに前記第1導電部及び前記リペア線を連結する第1コンタクト金属を含み、前記リペア線に連結されたダミー画素は、第2画素回路から延長された第2導電部、並びに前記第2導電部及び前記リペア線を連結する第2コンタクト金属を含んでもよい。

10

【0010】

前記第1導電部及び前記リペア線は、同一層に形成されてもよい。そして、前記リペア線は、前記第1画素回路並びに前記第2画素回路を構成する薄膜トランジスタのソース電極及びドレイン電極と同一層に同一物質から形成されてもよい。または前記リペア線は、前記アノード電極と同一層に同一物質から形成されてもよい。

【0011】

他の実施形態として、前記リペア線に連結された発光画素の発光素子を構成するアノード電極と接触する第1導電部と前記リペア線の間、及び前記リペア線に連結されたダミー画素の第2画素回路と連結された第2導電部と前記リペア線との間に少なくとも1層の絶縁膜が形成され、前記第1導電部及び前記リペア線、並びに前記第2導電部及び前記リペア線がレーザ・ウェルディングによって電気的に連結されてもよい。

20

【0012】

前記第1導電部と前記第2導電部は、前記第1画素回路及び前記第2画素回路を構成する薄膜トランジスタのゲート電極と同一層に同一物質から形成され、前記リペア線は、前記薄膜トランジスタのソース電極及びドレイン電極と同一層に同一物質から形成されてもよい。

【0013】

本発明の一実施形態による有機発光表示装置の駆動方法において、前記有機発光表示装置は、列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素、各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素、及び各列ごとに形成されたリペア線を含み、前記駆動方法は、前記複数の発光画素と前記ダミー画素とに順にデータ信号を供給するが、前記複数の発光画素のうちリペア線に連結された発光画素と、前記リペア線に連結されたダミー画素とには、同一のデータ信号が供給される走査段階と、前記データ信号に対応する駆動電流により、前記複数の発光画素の発光素子が同時に発光する発光段階と、を含んでもよい。

30

【0014】

前記ダミー画素は、各列の最初の行及び最後の行のうち少なくとも1行に形成されてもよい。

【0015】

前記走査段階が、前記発光段階より時間的に先行してもよい。または、前記走査段階及び前記発光段階が、少なくとも一部時間的に重畠されてもよい。

40

【0016】

本発明の一実施形態による有機発光表示装置のリペア方法において、前記有機発光表示装置は、列方向及び行方向に配置され、発光素子と、前記発光素子と連結された第1画素回路と、を具備する複数の発光画素、各列ごとに少なくとも一つ形成され、第2画素回路を具備するダミー画素、及び各列ごとに形成されたリペア線を含み、前記リペア方法は、前記複数の発光画素のうち第1不良画素の発光素子と、第1画素回路とを切り離す段階と、前記第1不良画素と同一列に配置されたリペア線と、前記第1不良画素の発光素子とを連結する段階と、前記第1不良画素に供給されるデータ信号と同一のデータ信号を供給され、前記供給されたデータ信号に対応する駆動電流を、前記リペア線を介して、前記第1

50

不良画素の発光素子に供給し、前記第1不良画素が、前記複数の発光画素と同時に発光するように、前記第1不良画素と同一列に配置された第1ダミー画素の第2画素回路を、前記リペア線と連結する段階と、を含んでもよい。

【0017】

一実施形態として、前記第1不良画素の連結段階は、前記第1不良画素の発光素子を構成するアノード電極と連結された第1導電部、並びに前記リペア線上部の前記第1導電部及び前記リペア線を連結する第1コンタクト金属を形成する段階を含み、前記第1ダミー画素の連結段階は、前記第1ダミー画素の第2画素回路と連結された第2導電部、並びに前記リペア線上部の前記第2導電部及び前記リペア線を連結する第2コンタクト金属を形成する段階を含んでもよい。

10

【0018】

他の実施形態として、前記第1不良画素の連結段階は、前記第1不良画素の発光素子を構成するアノード電極と連結された第1導電部、及び前記第1導電部と少なくとも1層の絶縁膜によって絶縁された前記リペア線をレーザ・ウェルディングによって電気的に連結する段階を含み、前記第1ダミー画素の連結段階は、前記第1ダミー画素の第2画素回路と連結された第2導電部、及び前記導電部と少なくとも1層の絶縁膜によって絶縁された前記リペア線をレーザ・ウェルディングによって電気的に連結する段階を含んでもよい。

【0019】

他の実施形態として、前記方法は、前記第1不良画素と同一列に配置された第2不良画素の発光素子と、第1画素回路とを切り離す段階と、前記第1不良画素と、前記第2不良画素との間のリペア線を分離する段階と、前記第2不良画素に供給されるデータ信号と同一のデータ信号を供給され、前記供給されたデータ信号に対応する駆動電流を、前記リペア線を介して、前記第2不良画素の発光素子に供給し、前記第2不良画素が、前記複数の発光画素と同時に発光するように、前記第1不良画素と同一列に配置された第2ダミー画素の第2画素回路を、前記リペア線の分離によって、第1不良画素が連結されていないリペア線と連結する段階と、をさらに含んでもよい。

20

【発明の効果】

【0020】

本発明によれば、同時発光駆動する表示装置の不良画素を、ダミー画素を利用して容易にリペアすることにより、明点を暗点に変えずに正常駆動することができる。

30

【図面の簡単な説明】

【0021】

【図1】本発明の一実施形態による表示装置を概略的に図示したブロック図である。

【図2】図1に図示された表示パネルの一例を概略的に示した図面である。

【図3】図1に図示された表示パネルの一例を概略的に示した図面である。

【図4】図1に図示された表示パネルの一例を概略的に示した図面である。

【図5】本発明の一実施形態による発光画素を概略的に示す図面である。

【図6】本発明の一実施形態によるダミー画素を概略的に示す図面である。

【図7】本発明の一実施形態による表示装置の駆動について説明するための図面である。

40

【図8】本発明の一実施形態による表示装置の駆動について説明するための図面である。

【図9】本発明の一実施形態による不良画素リペア方法について説明するための図面である。

【図10】図9に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

【図11】本発明の他の実施形態による不良画素リペア方法について説明するための図面である。

【図12】図11に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

【図13】本発明の他の実施形態による不良画素リペア方法について説明するための図面である。

50

【図14】図13に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

【図15】本発明の一実施形態による発光画素の回路図である。

【図16】図15の発光画素の駆動について説明するためのタイミング図である。

【図17】本発明の他の実施形態による発光画素の回路図である。

【図18】図17の発光画素の駆動について説明するためのタイミング図である。

【図19】本発明の他の実施形態による発光画素の回路図である。

【図20】図19の発光画素の駆動について説明するためのタイミング図である。

【図21】本発明の一実施形態による背面発光表示装置での発光画素リペアについて説明する断面図である。

10

【図22】本発明の一実施形態による背面発光表示装置での発光画素リペアについて説明する断面図である。

【図23】本発明の一実施形態による背面発光表示装置でのダミー画素連結について説明する断面図である。

【図24】本発明の一実施形態による前面発光表示装置での発光画素リペアについて説明する断面図である。

【図25】本発明の一実施形態による前面発光表示装置でのダミー画素連結について説明する断面図である。

【図26】本発明の他の実施形態による背面発光表示装置での発光画素リペアについて説明する断面図である。

20

【図27】本発明の他の実施形態による背面発光表示装置でのダミー画素連結について説明する断面図である。

【図28】本発明の他の実施形態による表示パネルを示す図面である。

【発明を実施するための形態】

【0022】

以下、本発明の望ましい実施形態について、添付された図面を参照して説明する。図面上の同一符号は、同一要素を指す。下記で本発明について説明するにおいて、関連公知の機能または構成に係わる具体的な説明が、本発明の要旨を必要以上に不明確にすると判断される場合には、その詳細な説明を省略する。

【0023】

また、図面に示された各構成の大きさ及び厚みは、説明の便宜のために任意に示してあるので、本発明は、必ずしも図示されたところに限定されるものではない。層、膜、領域、プレートなどの部分が、他の部分の「上」、または「上部」にあるとするとき、それは、他の部分の「真上」にある場合だけではなく、その中間に他の部分がある場合も含む。

30

【0024】

また、明細書全体で、ある部分がある構成要素を「含む」とするとき、それは、特別に反対となる記載がない限り、他の構成要素を除くものではなく、他の構成要素をさらに含んでもよいことを意味する。また、明細書全体で、「～上に」というのは、対象部分の上または下に位置することを意味するものであり、必ずしも重力方向を基準に、上側に位置するということを意味するものではない。

40

【0025】

第1、第2のような用語は、多様な構成要素について説明するのに使用されるが、前記構成要素が、かような用語によって限定されるものではない。前記用語は、1つの構成要素を他の構成要素から区別する目的でのみ使用される。例えば、本発明の権利範囲から外れずに、第1構成要素は、第2構成要素と命名されてもよく、同様に、第2構成要素も、第1構成要素と命名されてもよい。

【0026】

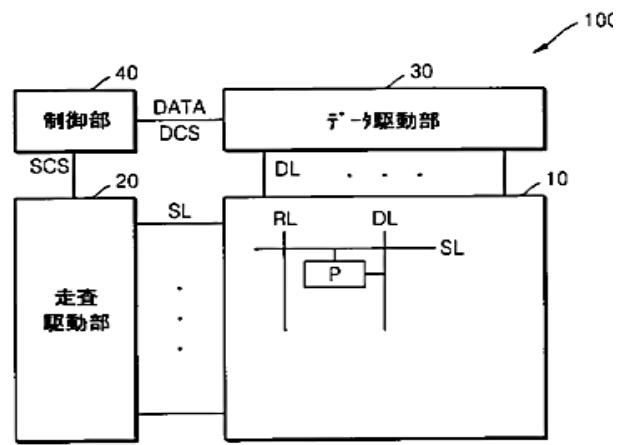

図1は、本発明の一実施形態による表示装置を概略的に図示したブロック図である。

【0027】

図1を参照すれば、本発明の実施形態による表示装置100は、複数の画素を含む表示

パネル 10、走査駆動部 20、データ駆動部 30 及び制御部 40 を含む。走査駆動部 20、データ駆動部 30 及び制御部 40 は、それぞれ別個の半導体チップによっても形成され、1つの半導体チップによっても集積される。また、走査駆動部 20 は、表示パネル 10 と同一の基板上に形成されもする。

【0028】

表示パネル 10 には、横方向に、複数の走査線 SL が形成されており、縦方向に、走査線 SL と垂直に交差する複数のデータ線 DL が形成されている。また、表示パネル 10 には、データ線 DL とほぼ平行に、一定距離離隔され、走査線 SL と垂直に交差する複数のリペア線 RL が形成されている。複数の走査線 SL、複数のデータ線 DL 及び複数のリペア線 RL の交差部には、横方向及び縦方向にそれぞれ所定距離離間され、ほぼ行列（マトリックス）状に配列された複数の画素 P が形成される。10

【0029】

図 1 では、画素 P に対して、右側にデータ線 DL、左側にリペア線 RL が配置されているが、本発明は、これに限定されるものではなく、データ線 DL とリペア線 RL との位置は、互いに変わりもする。また、リペア線 RL は、画素設計によって、走査線 SL とも平行に形成され、各画素列ごとに、一つ以上形成されてもよい。図示されていないが、表示パネル 10 には、発光制御信号を供給する複数の発光制御線、初期化電圧を供給する初期化電圧線、電源電圧を供給する駆動電圧線などがさらに形成されてもよい。

【0030】

走査駆動部 20 は、複数の走査線 SL を介して、表示パネル 10 に走査信号を生成して順次に供給してもよい。20

【0031】

データ駆動部 30 は、複数のデータ線 DL を介して、表示パネル 10 にデータ信号を順次に供給する。データ駆動部 30 は、制御部 40 から入力される階調を有する入力映像データ DATA を、電圧形態または電流形態のデータ信号に変換する。

【0032】

制御部 40 は、走査制御信号 SCS と、データ制御信号 DCs とを生成し、走査駆動部 20 とデータ駆動部 30 とにそれぞれ伝達する。それにより、走査駆動部 20 は、走査線に対して順に走査信号を印加し、データ駆動部 30 は、各画素 P にデータ信号を印加する。また、第 1 電源電圧 E LVDD ( 図 15 )、第 2 電源電圧 E LVSS ( 図 15 )、発光制御信号 ( EM )、初期化電圧 Vint ( 図 19 ) などが、制御部 40 の制御下で、各画素 P に印加される。30

【0033】

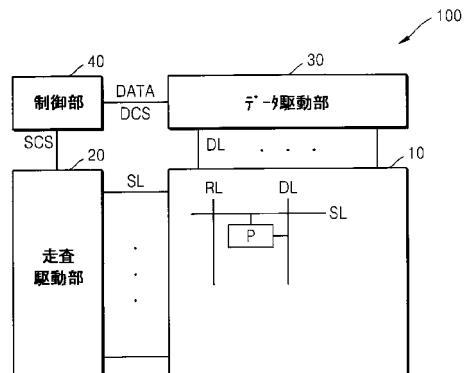

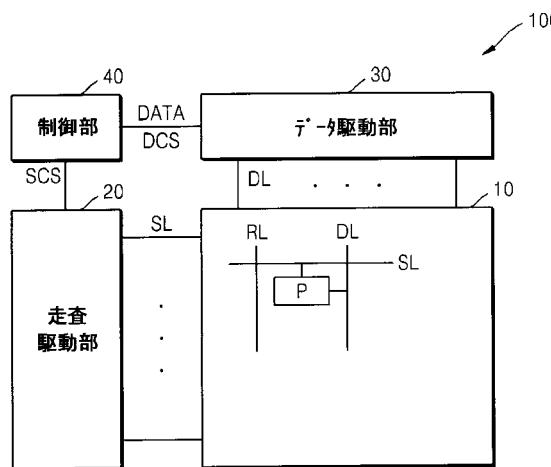

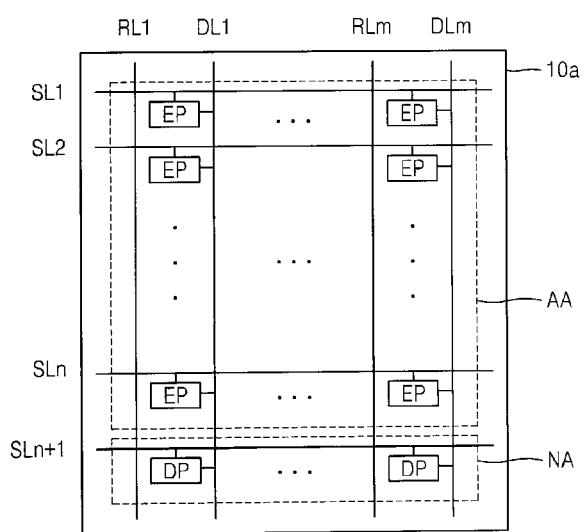

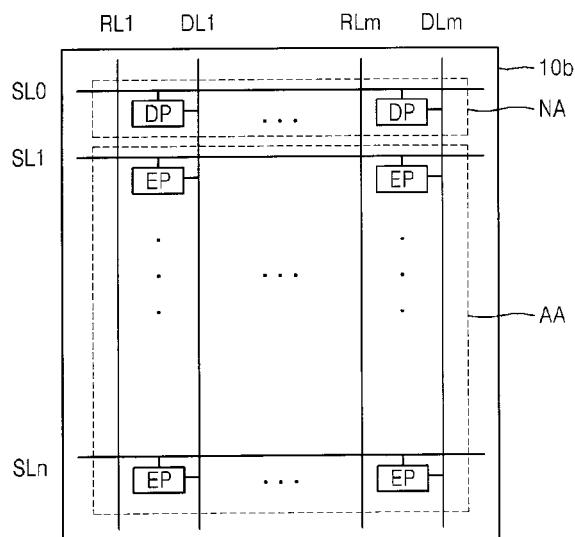

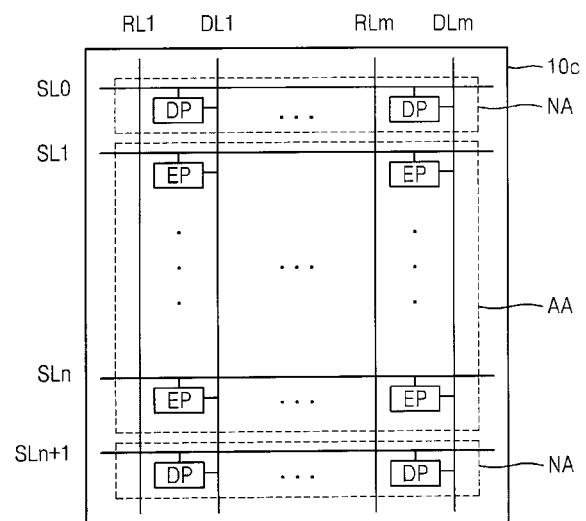

図 2 ないし図 4 は、図 1 に図示された表示パネル 10 の一例を概略的に示した図面である。

【0034】

図 2 ないし図 4 を共に参照すれば、表示パネル 10a, 10b, 10c には、複数の走査線 SL、複数のデータ線 DL 及び複数のリペア線 RL の交差部に、ほぼ行列状に配列された複数の画素 P が形成される。画素 P は、表示領域 AA に形成された発光画素 EP と、非表示領域 NA に形成されたダミー画素 DP とを含む。非表示領域 NA は、表示領域 AA の上下部のうち少なくとも 1 つの領域に形成されてもよい。それにより、ダミー画素 DP は、画素列の上下部のうち少なくとも 1 つの領域に、画素列ごとに一つ以上形成されてもよい。40

【0035】

図 2 を参照すれば、表示パネル 10a は、表示領域 AA と、表示領域 AA 下部の非表示領域 NA と、を含む。複数の走査線 SL 1 ないし SL n + 1 のうち、最初ないし n 番目の走査線 SL 1 ないし SL n は、表示領域 AA に形成され、最後の ( n + 1 ) 番目の走査線 SL n + 1 は、非表示領域 NA に形成される。そして、複数のデータ線 DL 1 ないし DL m と、複数のリペア線 RL 1 ないし RL m は、表示領域 AA と非表示領域 NA とに、画素列ごとに形成される。表示領域 AA には、最初ないし n 番目の走査線 SL 1 ないし SL n 50

と、複数のデータ線  $DL_1$  ないし  $DL_m$  とにそれぞれ連結された複数の発光画素  $EP$  が形成され、非表示領域  $NA$  には、最後の  $(n + 1)$  番目の走査線  $SL_{n+1}$  と、複数のデータ線  $DL_1$  ないし  $DL_m$  とにそれぞれ連結された複数のダミー画素  $DP$  が形成される。

【0036】

図3を参照すれば、表示パネル10bは、表示領域  $AA$  と、表示領域  $AA$  上部の非表示領域  $NA$  と、を含む。複数の走査線  $SL_0$  ないし  $SL_n$  のうち、2番目の走査線  $SL_2$  ないし  $n$  番目の走査線  $SL_n$  は、表示領域  $AA$  に形成され、最初の走査線  $SL_0$  は、非表示領域  $NA$  に形成される。そして、複数のデータ線  $DL_1$  ないし  $DL_m$  と、複数のリペア線  $RL_1$  ないし  $RL_m$  は、表示領域  $AA$  と非表示領域  $NA$  とに画素列ごとに形成される。表示領域  $AA$  には、2番目の走査線  $SL_2$  ないし  $n$  番目の走査線  $SL_n$  と、複数のデータ線  $DL_1$  ないし  $DL_m$  とにそれぞれ連結された複数の発光画素  $EP$  が形成され、非表示領域  $NA$  には、最初の走査線  $SL_0$  と、複数のデータ線  $DL_1$  ないし  $DL_m$  とにそれぞれ連結された複数のダミー画素  $DP$  が形成される。

10

【0037】

図4を参照すれば、表示パネル10cは、表示領域  $AA$  と、表示領域  $AA$  上下部の非表示領域  $NA$  と、を含む。複数の走査線  $SL_0$  ないし  $SL_{n+1}$  のうち、2番目の走査線  $SL_2$  ないし  $n$  番目の走査線  $SL_n$  は、表示領域  $AA$  に形成され、最初の走査線  $SL_0$  と最後の走査線  $SL_{n+1}$  は、非表示領域  $NA$  に形成される。そして、複数のデータ線  $DL_1$  ないし  $DL_m$  と、複数のリペア線  $RL_1$  ないし  $RL_m$  は、表示領域  $AA$  と、非表示領域  $NA$  とに画素列ごとに形成される。表示領域  $AA$  には、2番目の走査線  $SL_2$  ないし  $n$  番目の走査線  $SL_n$  と、複数のデータ線  $DL_1$  ないし  $DL_m$  にそれぞれ連結された複数の発光画素  $EP$  が形成され、非表示領域  $NA$  には、最初の走査線  $SL_{n+1}$  と、最後の  $(n + 1)$  番目の走査線  $SL_{n+1}$ 、及び複数のデータ線  $DL_1$  ないし  $DL_m$  にそれぞれ連結された複数のダミー画素  $DP$  が形成される。

20

【0038】

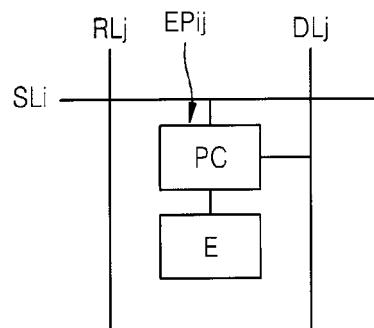

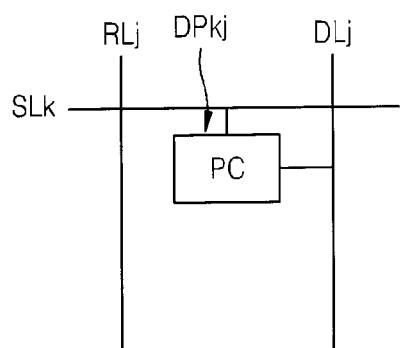

図5は、本発明の一実施形態による発光画素を概略的に示している。

【0039】

図5を参照すれば、 $i$  ( $i = 1, \dots, n$ ;  $n$  は自然数) 番目の走査線  $SL_i$  と、 $j$  ( $j = 1, \dots, m$ ;  $m$  は自然数) 番目データ線  $DL_j$  とに連結された発光画素  $EP_{ij}$  は、画素回路  $PC$  と、画素回路  $PC$  から駆動電流を伝達されて発光する発光素子  $E$  と、を含む。画素回路  $PC$  は、少なくとも1つの薄膜トランジスタ、及び少なくとも1つのキャパシタを含んでもよい。発光素子  $E$  は、アノード電極、カソード電極、アノード電極とカソード電極との間の発光層を含む有機発光素子  $OLED$  である。

30

【0040】

図6は、本発明の一実施形態によるダミー画素を概略的に示している。

【0041】

図6を参照すれば、 $k$  ( $k = 0$  または  $n + 1$ ;  $n$  は自然数) 番目の走査線  $SL_k$  と、 $j$  ( $j = 1, \dots, m$ ;  $m$  は自然数) 番目データ線  $DL_j$  とに連結されたダミー画素  $DP_{kj}$  は、画素回路  $PC$  のみを具備し、発光素子  $E$  は具備しない。ダミー画素  $DP_{kj}$  の画素回路  $PC$  は、発光画素  $EP_{ij}$  の画素回路  $PC$  と同一である。

40

【0042】

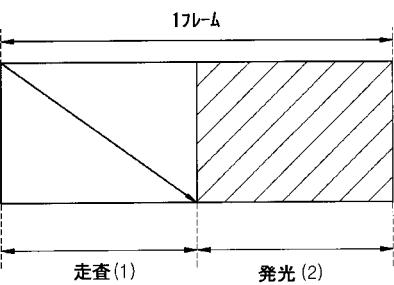

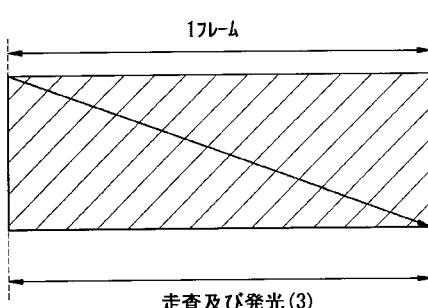

図7及び図8は、本発明の一実施形態による表示装置の駆動について説明するための図面である。

【0043】

図7を参照すれば、本発明の表示装置100は、1フレーム間走査区間(1)及び発光区間(2)で駆動する。走査区間(1)では、最初の走査線ないし最後の走査線に、走査信号が順次に供給され、各発光画素  $EP$  のキャパシタに、データ信号に対応する電圧が充電される。発光区間(2)では、全ての発光画素  $EP$  の有機発光素子  $OLED$  が充電された電圧に対応する電流を供給され、供給された電流に対応する輝度で、同時に発光する。

【0044】

50

発光画素 E P において不良画素が発生し、同一列のダミー画素 D P が利用される場合、走査区間 (1) では、ダミー画素 D P が連結された走査線を含んだ各走査線で、走査信号とデータ信号とが順次に供給される。このとき、不良画素に供給されるデータ信号と同一のデータ信号が、ダミー画素 D P に供給される。そして、発光区間 (2) では、不良画素を含む全ての発光画素 E P の有機発光素子 O L E D が充電された電圧に対応する電流をそれぞれ供給され、供給された電流に対応する輝度で、同時に発光する。このとき、不良画素の有機発光素子 O L E D は、ダミー画素 D P から電流を供給され、供給された電流に対応する輝度で発光する。

#### 【0045】

走査区間 (1) は、発光区間 (2) に先立って遂行される。走査区間 (1) で、各発光画素 E P とダミー画素 D P とに、N フレームのデータ信号に対応する電圧が充電され、発光区間 (2) で、全ての発光画素 E P の有機発光素子 O L E D が N フレームのデータ信号に対応する電流によって発光する。

10

#### 【0046】

図 8 を参照すれば、本発明の表示装置 100 は、1 フレームの間、走査区間と発光区間とが共に具現される走査及び発光区間 (3) で駆動する。走査及び発光区間 (3) では、最初の走査線ないし最後の走査線に、走査信号が順次に供給され、各発光画素 E P のキャパシタに、N フレームのデータ信号に対応する電圧が充電される。同時に、走査及び発光区間 (3) では、全ての発光画素 E P の有機発光素子 O L E D が、(N - 1) フレームのデータ信号に対応して充電された電圧に対応する電流を供給され、供給された電流に対応する輝度で同時に発光する。走査及び発光区間 (3) で発光区間は、走査区間と同一であるか、あるいは走査区間と同時に始まり、走査区間より短く設定されてもよい。

20

#### 【0047】

発光画素 E P において不良画素が発生し、同一列のダミー画素 D P が利用される場合、走査及び発光区間 (3) では、ダミー画素 D P が連結された走査線を含んだ各走査線で、走査信号と、N フレームのデータ信号とが順次に供給される。このとき、不良画素に供給されるデータ信号と同一のデータ信号が、ダミー画素 D P に供給される。同時に、走査及び発光区間 (3) では、不良画素を含む全ての発光画素 E P の有機発光素子 O L E D が、(N - 1) フレームのデータ信号に対応して充電された電圧に対応する電流を供給され、供給された電流に対応する輝度で同時に発光する。このとき、不良画素の有機発光素子 O L E D は、ダミー画素 D P から電流を供給され、供給された電流に対応する輝度で発光する。

30

#### 【0048】

図 7 及び図 8 では、1 フレームの間、走査区間及び発光区間のみを図示しているが、初期化区間、スレショルド電圧補償のための補償区間、発光オフ区間などが 1 フレームの間さらに遂行されてもよい。

#### 【0049】

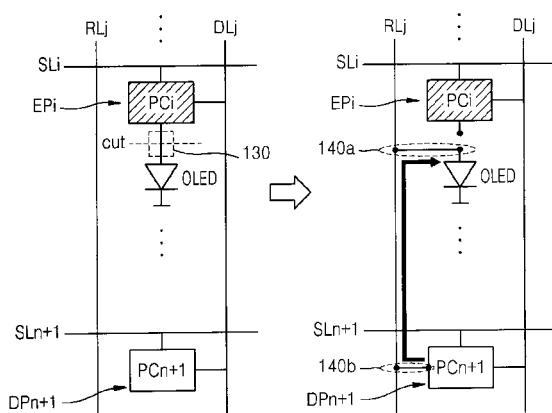

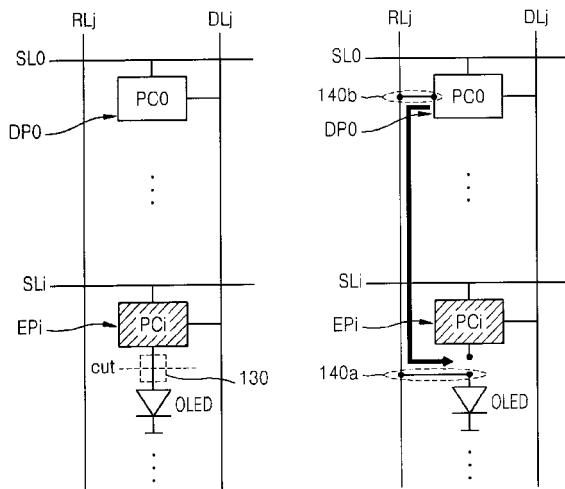

図 9 は、本発明の一実施形態による不良画素リペア方法について説明するための図面である。図 9 に図示された実施形態は、図 2 に図示された表示パネル 10a のように、ダミー画素 D P<sub>n+1</sub> が複数の走査線 S L 1 ないし S L<sub>n+1</sub> において、最後の走査線 S L<sub>n+1</sub> に連結された場合である。図 9 では、便宜上 j 列のみを図示し、発光素子 E として、有機発光素子 O L E D が図示された。

40

#### 【0050】

図 9 を参照すれば、i 番目の走査線に連結された発光画素 E P<sub>i</sub> の画素回路 P C<sub>i</sub> が不良である場合、画素回路 P C<sub>i</sub> と連結された有機発光素子 O L E D を、画素回路 P C<sub>i</sub> と断絶させる。このために、画素回路 P C<sub>i</sub> と有機発光素子 O L E D とを連結する切断部 130 にレーザビームを照射して切断 (cut) することにより、画素回路 P C<sub>i</sub> と、有機発光素子 O L E D とを電気的に分離させる。例えば、不良発光画素 E P<sub>i</sub> の有機発光素子 O L E D のアノード電極と、画素回路 P C<sub>i</sub> と、を切断して分離させることができる。

50

#### 【0051】

次に、第1リペア部140aで、不良発光画素EPIの有機発光素子OLEDを、リペア線RLjと連結し、第2リペア部140bで、ダミー画素DPn+1の画素回路PCn+1を、リペア線RLjと連結する。例えば、不良発光画素EPIの有機発光素子OLEDのアノード電極と、リペア線RLjとを連結し、ダミー画素DPn+1の画素回路PCn+1内の薄膜トランジスタTFTの1電極と、リペア線RLjとを連結してもよい。それにより、不良発光画素EPIの有機発光素子OLEDは、自体の画素回路PCiから電気的な接続が切り離され、リペア線RLjを介して、ダミー画素DPn+1の画素回路PCn+1と電気的に連結される。

#### 【0052】

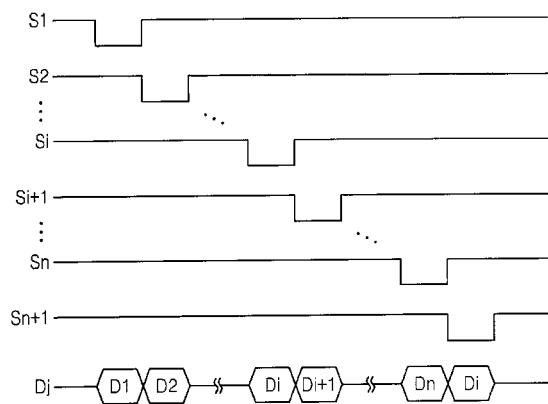

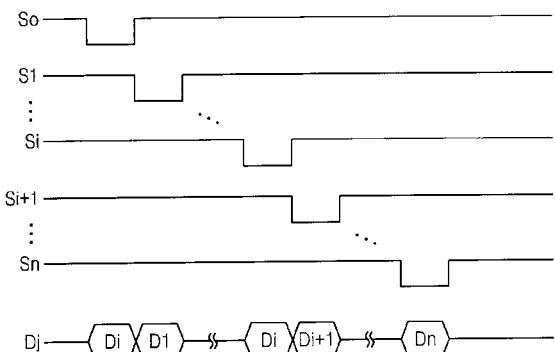

図10は、図9に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

10

#### 【0053】

図10を参照すれば、走査区間で、最初の走査線SL1ないし最後の走査線SLn+1で、走査信号S1ないしSn+1が順次に印加される。走査信号S1ないしSn+1に同期され、データ信号D1ないしDnが、データ線DLjに順次に印加される。このとき、不良発光画素EPIに印加されたデータ信号Diと同一のデータ信号Diが、ダミー画素DPn+1にさらに印加される。それにより、不良発光画素EPIの有機発光素子OLEDは、ダミー画素DPn+1の画素回路PCn+1と、リペア線RLjとを介して、データ信号Diに対応する電流を供給される。それにより、発光区間で、不良発光画素EPIを含んだ全ての発光画素が同時発光することができ、明点または暗点の発生を抑制することができる。

20

#### 【0054】

図11は、本発明の他の実施形態による不良画素リペア方法について説明するための図面である。図11に図示された実施形態は、図3に図示された表示パネル10bのように、ダミー画素DP0が、複数の走査線SL0ないしSLnにおいて、最初の走査線SL0に連結された場合である。図11では、便宜上、j列のみを図示し、発光素子Eとして、有機発光素子OLEDが図示されている。

30

#### 【0055】

図11を参照すれば、i番目の走査線に連結された発光画素EPIの画素回路PCiが不良である場合、画素回路PCiと連結された有機発光素子OLEDを、画素回路PCiと断絶させる。このために、画素回路PCiと有機発光素子OLEDとを連結する切断部130に、レーザビームを照射して切断することにより、画素回路PCiと、有機発光素子OLEDとを電気的に分離させる。例えば、不良発光画素EPIの有機発光素子OLEDのアノード電極と、画素回路PCiと、を切断して分離させることができる。

40

#### 【0056】

次に、第1リペア部140aで、不良発光画素EPIの有機発光素子OLEDを、リペア線RLjと連結し、第2リペア部140bで、ダミー画素DP0の画素回路PC0を、リペア線RLjと連結する。例えば、不良発光画素EPIの有機発光素子OLEDのアノード電極と、リペア線RLjとを連結し、ダミー画素DP0の画素回路PC0内の薄膜トランジスタTFTの1電極と、リペア線RLjとを連結してもよい。それにより、不良発光画素EPIの有機発光素子OLEDは、自体の画素回路PCiから切り離され、リペア線RLjを介して、ダミー画素DP0の画素回路PC0と電気的に連結される。

40

#### 【0057】

図12は、図11に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

50

#### 【0058】

図12を参照すれば、走査区間で、最初の走査線SL0ないし最後の走査線SLnで、走査信号S0ないしSnが順次に印加される。走査信号S0ないしSnに同期され、データ信号D1ないしDnがデータ線DLjに順次に印加される。このとき、不良発光画素EPIに印加されるデータ信号Diと同一のデータ信号Diが、ダミー画素DP0に先に印

加される。それにより、不良発光画素 E P i の有機発光素子 O L E D は、ダミー画素 D P 0 の画素回路 P C 0 と、リペア線 R L j とを介して、データ信号 D i に対応する電流を供給される。それにより、発光区間で、不良発光画素 E P i を含んだ全ての発光画素が同時に発光することができて、明点または暗点の発生を抑制することができる。

【0059】

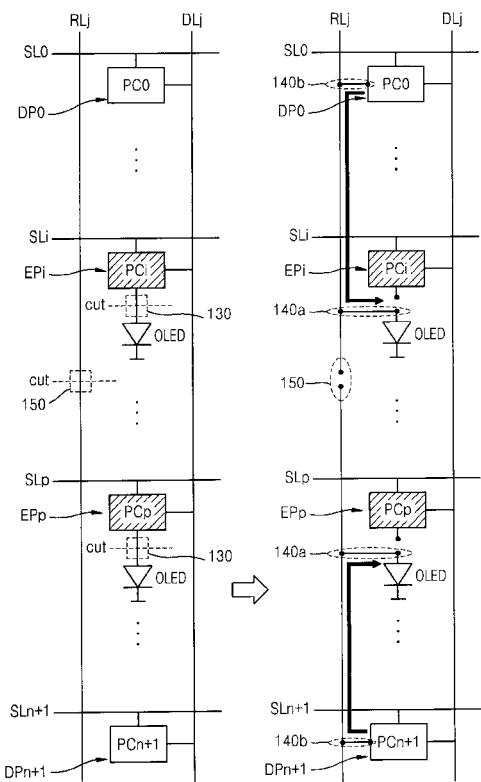

図 13 は、本発明の他の実施形態による不良画素リペア方法について説明するための図面である。図 13 に図示された実施形態は、図 4 に図示された表示パネル 10 c のように、ダミー画素 D P 0 , D P n + 1 が複数の走査線 S L 0 ないし S L n + 1 において、最初の走査線 S L 0 と最後の走査線 S L n + 1 とに、それぞれ連結された場合である。図 13 では、便宜上、j 列のみを図示し、発光素子 E として、有機発光素子 O L E D が図示されている。

10

【0060】

図 13 を参照すれば、i 番目の走査線に連結された発光画素 E P i の画素回路 P C i と、p 番目の走査線に連結された発光画素 E P p の画素回路 P C p とが不良である場合、画素回路 P C i , P C p と連結された有機発光素子 O L E D を、画素回路 P C i , P C p とそれぞれ断絶させる。このために、画素回路 P C i , P C p と、有機発光素子 O L E D とを連結する切断部 130 それぞれに、レーザビームを照射して切断することにより、画素回路 P C i , P C p と、有機発光素子 O L E D とをそれぞれ電気的に分離させる。例えば、不良発光画素 E P i , E P p の有機発光素子 O L E D のアノード電極と、画素回路 P C i , P C p とを切断して分離させることができる。また、リペア線 R L j の分離部 150 に、レーザビームを照射して切断することにより、リペア線 R L j を、上部リペア線と下部リペア線とに分離する。それにより、2 つのダミー画素 D P 0 , D P n + 1 の画素回路 P C 0 , P C n + 1 が互いに分離される。

20

【0061】

次に、第 1 リペア部 140 a で、不良発光画素 E P i , E P p の有機発光素子 O L E D を、それぞれ上部リペア線及び下部リペア線 R L j と連結し、第 2 リペア部 140 b で、ダミー画素 D P 0 , D P n + 1 の画素回路 P C 0 , P C n + 1 を、それぞれリペア線 R L j と連結する。例えば、不良発光画素 E P i , E P p の有機発光素子 O L E D のアノード電極と、リペア線 R L j とを連結し、ダミー画素 D P 0 , D P n + 1 の画素回路 P C 0 , P C n + 1 内の薄膜トランジスタ TFT の 1 電極と、リペア線 R L j とを連結する。それにより、不良発光画素 E P i , E P p の有機発光素子 O L E D は、自体の画素回路 P C i , P C p から切り離され、リペア線 R L j を介して、それぞれダミー画素 D P 0 , D P n + 1 の画素回路 P C 0 , P C n + 1 と電気的に連結される。

30

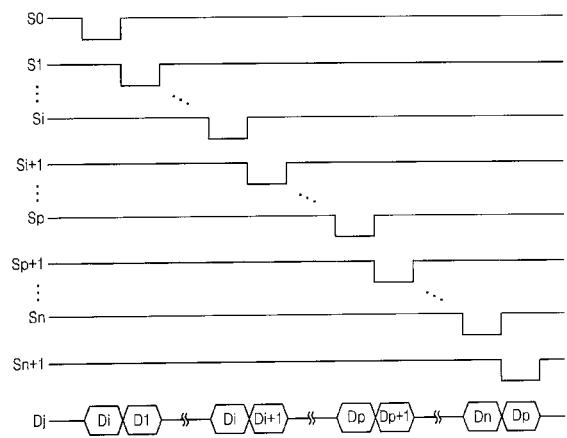

【0062】

図 14 は、図 13 に図示された方法で画素リペアされた表示パネルの走査駆動部に供給される走査信号及びデータ信号を示す波形図である。

【0063】

図 14 を参照すれば、走査区間で、最初の走査線 S L 0 ないし最後の走査線 S L n + 1 で、走査信号 S 0 ないし S n + 1 が順次に印加される。走査信号 S 0 ないし S n + 1 に同期され、データ信号 D 1 ないし D n が、データ線 D L j に順次に印加される。このとき、不良発光画素 E P i に印加されるデータ信号 D i と同一のデータ信号 D i が、ダミー画素 D P 0 に先に印加され、不良発光画素 E P p に印加されたデータ信号 D p と同一のデータ信号 D p が、ダミー画素 D P n + 1 にさらに印加される。それにより、不良発光画素 E P i の有機発光素子 O L E D は、ダミー画素 D P 0 の画素回路 P C 0 と、リペア線 R L j とを介して、データ信号 D i に対応する電流を供給され、不良発光画素 E P p の有機発光素子 O L E D は、ダミー画素 D P n + 1 の画素回路 P C n + 1 と、リペア線 R L j とを介して、データ信号 D p に対応する電流を供給される。それにより、発光区間で、不良発光画素 E P i , E P p を含んだ全ての発光画素が同時に発光することができ、明点または暗点の発生を抑制する。

40

【0064】

50

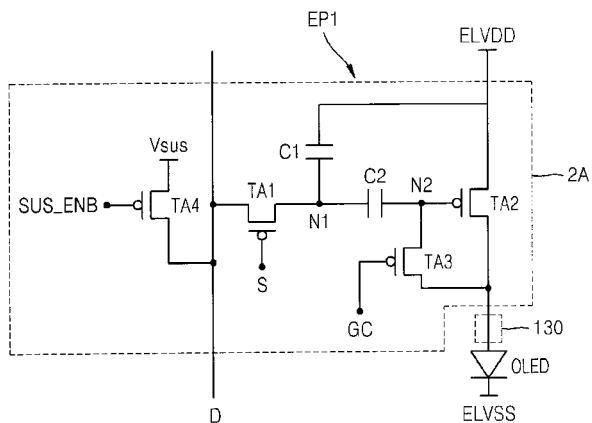

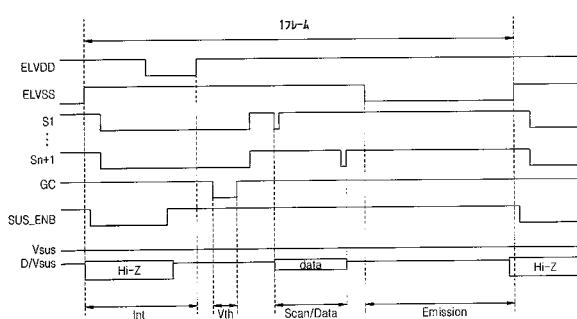

図15は、本発明の一実施形態による発光画素の回路図であり、図16は、図15の発光画素の駆動について説明するためのタイミング図である。

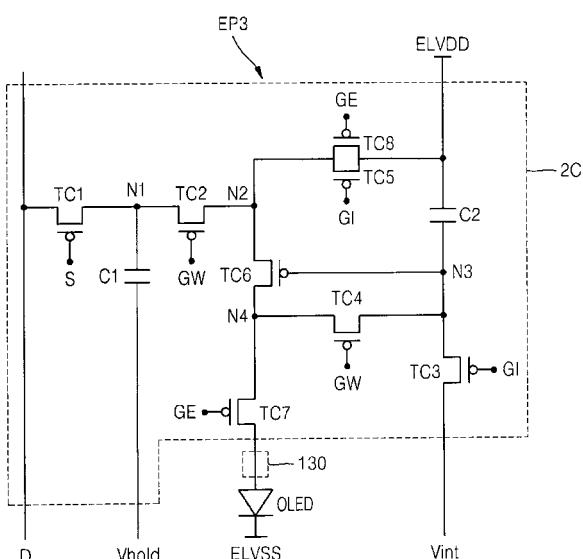

【0065】

図15を参照すれば、発光画素EP1は、有機発光素子OLEDと、有機発光素子OLEDに電流を供給するための画素回路2Aと、を具備する。図示されていないが、ダミー画素DP1は、有機発光素子OLEDが除かれた画素回路2Aを具備する。

【0066】

有機発光素子OLEDのアノード電極は、画素回路2Aに連結され、カソード電極は、第2電源電圧ELVSSを供給する第2電源と連結される。有機発光素子OLEDは、画素回路2Aから供給される電流に対応して所定輝度で発光する。有機発光素子OLEDと画素回路2Aとが連結される領域の切断部130は、発光画素EP1が不良画素であると判定された場合、レーザビームによって切断する領域である。

10

【0067】

画素回路2Aは、4個のトランジスタTA1ないしTA4、及び2個のキャパシタC1, C2を具備する。

【0068】

第1トランジスタTA1のゲート電極は、走査線から走査信号Sを印加され、第1電極は、データ線からデータ信号Dを印加される。そして、第1トランジスタTA1の第2電極は、第1ノードN1に接続される。

20

【0069】

第2トランジスタTA2のゲート電極は、第2ノードN2に連結され、第1電極は、第1電源から第1電源電圧ELVDDを印加され、第2電極は、有機発光素子OLEDのアノード電極に連結される。第2トランジスタTA2は、駆動トランジスタとしての役割を行う。

20

【0070】

第1ノードN1と、第2トランジスタTA2の第2電極との間に第1キャパシタC1が連結され、第1ノードN1と、第2ノードN2との間には、第2キャパシタC2が連結される。

【0071】

第3トランジスタTA3のゲート電極は、第1制御信号GCを印加され、第1電極は、第2トランジスタTA2のゲート電極と連結され、第2電極は、有機発光素子OLEDのアノード電極、及び第2トランジスタTA2の第2電極と連結される。

30

【0072】

第4トランジスタTA4のゲート電極は、第2制御信号SUS\_ENBを印加され、第1電極は、補助電圧Vsusを印加され、第2電極は、データ線に連結され、データ信号Dを印加される。

【0073】

図16では、図15の画素回路2Aを有する発光画素EP1と、ダミー画素DP1とが、図2に図示されたように、表示パネル10aに形成され、図9に図示されたように、不良画素リペアされた場合を例として説明する。

40

【0074】

図16を参照すれば、各発光画素EP1は、同時発光方式で駆動され、各フレーム別に、初期化区間Int、補償区間Vth、走査/データ入力区間Scan/Data、発光区間Emissionに区分して動作する。走査/データ入力区間Scan/Dataでは、走査信号が各走査線に対して順次に入力され、それに対応して、各発光画素EP1とダミー画素EP1とに、データ信号が順次に入力される。初期化区間Int及び補償区間Vth区間では、全ての発光画素EP1とダミー画素DP1とに、同時に一括的に走査信号が印加される。各発光画素EP1及びダミー画素DP1に具備された駆動トランジスタの初期化、スレショルド電圧補償、及び各発光画素EP1の発光動作は、フレーム別に同時に具現される。

【0075】

50

初期化区間  $I_{n,t}$  では、全ての走査線に、ローレベルの走査信号  $S_1$  ないし  $S_{n+1}$  が同時に印加される。そして、ローレベルの第 2 制御信号  $SUS\_ENB$  が、第 4 トランジスタ  $TA_4$  のゲート電極に印加される。このとき、データ線は、ハイ・インピーダンス ( $H_i - Z$ ) 状態である。それにより、第 1 トランジスタ  $TA_1$  及び第 4 トランジスタ  $TA_4$  がターンオンされ、第 1 ノード  $N_1$  に、ローレベルの補助電圧  $V_{sus}$  が印加され、第 2 ノード  $N_2$  の電圧が低下し、第 2 ノード  $N_2$  は、所定の初期化電圧  $V_{init}$  を維持する。次に、第 2 制御信号  $SUS\_ENB$  がハイレベルに遷移され、第 4 トランジスタ  $TA_4$  は、ターンオフされ、データ線のハイレベルの補助電圧  $V_{sus}$  が第 1 ノード  $N_1$  に印加される。第 2 ノード  $N_2$  の電圧が低下することにより、第 2 トランジスタ  $TA_2$  がターンオンされ、有機発光素子  $OLED$  のアノード電極の電圧が、駆動電圧  $ELVDD$  レベルにリセットされる。

10

## 【0076】

補償区間  $V_{th}$  では、データ線に印加されるハイレベルの補助電圧  $V_{sus}$  が、第 1 ノード  $N_1$  に印加される。そして、第 1 制御信号  $GC$  がローレベルに印加され、第 3 トランジスタ  $TA_3$  がターンオンされる。それにより、第 2 トランジスタ  $TA_2$  は、ダイオード連結され、第 2 キャパシタ  $C_2$  に、第 2 トランジスタ  $TA_2$  のスレショルド電圧に対応する電圧が保存されるまで電流が流れ、その後には、ターンオフされる。

## 【0077】

走査 / データ入力区間  $Scan / Data$  では、ローレベルの走査信号  $S_1$  ないし  $S_{n+1}$  が、各走査線に順次に入力され、第 1 トランジスタ  $TA_1$  は、ターンオンされ、走査線に連結された発光画素  $EP_1$  とダミー画素  $DP_1$  とに、データ信号が順次に入力される。このとき、ダミー画素  $DP_1$  には、不良画素に印加されたデータ信号と同一のデータ信号が印加される。それにより、第 1 キャパシタ  $C_1$  には、駆動電圧  $ELVDD$  と第 1 ノード  $N_1$  の電圧差が保存される。

20

## 【0078】

このとき、順次に印加される走査信号の幅を、2 水平時間 (2H) で印加し、隣接する走査信号の幅、例えば、( $n - 1$ ) 番目の走査信号  $S_{n-1}$  の幅と、 $n$  番目の走査信号  $S_n$  の幅は、1H 以下ほど重畳されるように印加することが望ましい。それは、表示領域の大面積化による信号線の RC 遅延 (delay) による充電不足現象を克服するためである。

## 【0079】

発光区間  $Emission$  では、第 1 電源電圧  $ELVDD$  は、ハイレベルに印加され、第 2 電源電圧  $ELVSS$  は、ローレベルに印加される。そして、第 2 トランジスタ  $TA_2$  を介して、第 1 電源電圧  $ELVDD$  から有機発光素子  $OLED$  のカソード電極までの電流経路が形成され、全ての発光画素  $EP_1$  の有機発光素子  $OLED$  は、データ信号に対応する輝度で発光する。このとき、不良画素の有機発光素子  $OLED$  は、ダミー画素  $DP_1$  から、リペア線を介して供給される電流によって発光する。

30

## 【0080】

図示されていないが、 $N$  フレームの発光区間後、( $N + 1$ ) フレームの開始前に、ブラック挿入 (black insertion) またはディミング (dimming) のために、発光を消す発光オフ区間が追加されてもよい。

40

## 【0081】

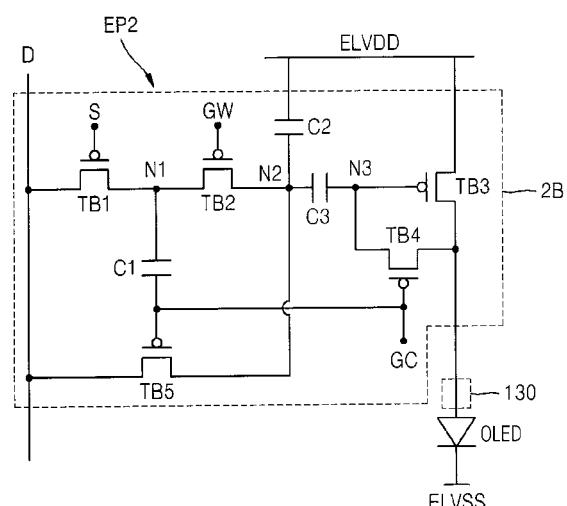

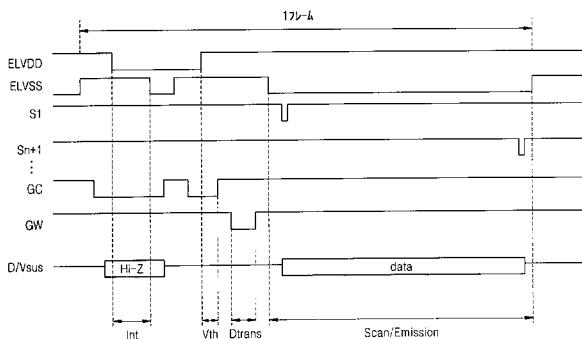

図 17 は、本発明の他の実施形態による発光画素の回路図であり、図 18 は、図 17 の発光画素の駆動について説明するためのタイミング図である。

## 【0082】

図 17 を参照すれば、発光画素  $EP_2$  は、有機発光素子  $OLED$  と、有機発光素子  $OLED$  に電流を供給するための画素回路  $2B$  とを具備する。図示されていないが、ダミー画素  $DP_2$  は、有機発光素子  $OLED$  が除外された画素回路  $2B$  を具備する。

## 【0083】

有機発光素子  $OLED$  のアノード電極は、画素回路  $2B$  に連結され、カソード電極は、第 2 電源電圧  $ELVSS$  を供給する第 2 電源と連結される。有機発光素子  $OLED$  は、画

50

素回路 2 B から供給される電流に対応して所定輝度で発光する。有機発光素子 O L E D と画素回路 2 B とが連結される領域の切断部 1 3 0 は、発光画素 E P 2 が不良画素であると判定された場合、レーザビームによって切断される領域である。

【 0 0 8 4 】

画素回路 2 B は、5 個のトランジスタ T B 1 ないし T B 5、及び 3 個のキャパシタ C 1 ないし C 3 を具備する。

【 0 0 8 5 】

第 1 トランジスタ T B 1 のゲート電極は、走査線から走査信号 S を印加され、第 1 電極は、データ線に連結されてデータ信号 D を印加され、第 2 電極は、第 1 ノード N 1 に連結される。

10

【 0 0 8 6 】

第 2 トランジスタ T B 2 のゲート電極は、第 1 制御信号 G W を印加され、第 1 電極は、第 1 ノード N 1 に連結され、第 2 電極は、第 2 ノード N 2 に連結される。

【 0 0 8 7 】

第 3 トランジスタ T B 3 のゲート電極は、第 3 ノード N 3 に連結され、第 1 電極は、第 1 電源から第 1 電源電圧 E L V D D を印加され、第 2 電極は、有機発光素子 O L E D のアノード電極に連結される。第 3 トランジスタ T B 3 は、駆動トランジスタとしての役割を行う。

20

【 0 0 8 8 】

第 4 トランジスタ T B 4 のゲート電極は、第 2 制御信号 G C を印加され、第 1 電極は、第 3 ノード N 3 及び第 3 トランジスタ T B 3 のゲート電極に連結され、第 2 電極は、有機発光素子 O L E D のアノード電極と連結される。

20

【 0 0 8 9 】

第 5 トランジスタ T B 5 のゲート電極は、第 2 制御信号 G C を印加され、第 1 電極は、データ線に連結されてデータ信号 D を印加され、第 2 電極は、第 2 ノード N 2 に連結される。

【 0 0 9 0 】

第 1 ノード N 1 と、第 5 トランジスタ T B 5 のゲート電極との間に、第 1 キャパシタ C 1 が連結され、第 2 ノード N 2 と第 1 電源との間に、第 2 キャパシタ C 2 が連結され、第 2 ノード N 2 と、第 3 ノード N 3 及び第 3 トランジスタ T B 3 のゲート電極との間に第 3 キャパシタ C 3 が連結される。第 1 キャパシタ C 1 は、第 1 トランジスタ T B 1 がターンオンされる時、データ線から供給されるデータ信号 D に対応する電圧を充電する。

30

【 0 0 9 1 】

図 1 8 では、図 1 7 の画素回路 2 B を有する発光画素 E P 2 と、ダミー画素 D P 2 とが、図 2 に図示されたように、表示パネル 1 0 a に形成され、図 9 に図示されたように、不良画素リペアされた場合を例として説明する。

40

【 0 0 9 2 】

図 1 8 を参照すれば、各発光画素 E P 2 は、同時発光方式で駆動され、各フレーム別に、初期化区間 I n t 、補償区間 V t h 、データ移動区間 D t r a n s 、及び走査 / 発光区間 Scan / Emission に区分して動作する。走査 / 発光区間 Scan / Emission では、走査信号が各走査線に対して順次に入力され、それに対応して、各発光画素 E P 2 とダミー画素 E P 2 とにデータ信号が順次に入力される。各発光画素 E P 2 及びダミー画素 D P 2 に具備された駆動トランジスタの初期化及びスレショルド電圧補償、データ移動、各発光画素 E P 2 の発光動作は、フレーム別に同時に具現される。

【 0 0 9 3 】

初期化区間 I n t で、第 1 電源電圧 E L V D D と第 2 制御信号 G C とがローレベルに印加される。そして、データ線は、ハイ・インピーダンス ( H i - Z ) 状態である。それにより、第 5 トランジスタ T B 5 がターンオンされ、第 4 トランジスタ T B 4 がターンオンされ、第 3 トランジスタ T B 3 は、ダイオード連結され、有機発光素子 O L E D のアノード電極の電圧と、第 3 ノード N 3 の電圧とが駆動電圧 E L V D D レベルに初期化される。

50

## 【0094】

補償区間  $V_{th}$  で、第2制御信号  $G_C$  がローレベルに印加され、データラインには、ハイレベルの補助電圧  $V_{sus}$  が印加される。それにより、第5トランジスタ  $TB_5$  がターンオンされ、第2ノード  $N_2$  に補助電圧  $V_{sus}$  が印加される。そして、第4トランジスタ  $TB_4$  がターンオンされ、第3トランジスタ  $TB_3$  は、ダイオード連結され、第3キャパシタ  $C_3$  に、第3トランジスタ  $TB_3$  のスレショルド電圧に対応する電圧が保存されるまで電流が流れ、その後にはターンオフされる。

## 【0095】

データ移動区間  $D_{trans}$  で、第1電源電圧  $ELVDD$ 、第2電源電圧  $ELVSS$  がハイレベルに印加され、第1制御信号  $GW$  がローレベルに印加される。それにより、第2トランジスタ  $TB_2$  がターンオンされ、第1キャパシタ  $C_1$  に保存されていた ( $N-1$ ) フレームの走査区間の間、発光画素  $EP_2$  に書き込まれたデータ信号  $D$  が、第2ノード  $N_2$  に移動する。それにより、第2キャパシタ  $C_2$  には、駆動電圧  $ELVDD$  と第2ノード  $N_2$  との電圧差が保存される。

10

## 【0096】

走査 / 発光区間  $Scan / Emission$  では、走査区間及び発光区間が同時に進められる。走査 / 発光区間  $Scan / Emission$  で、第1電源電圧  $ELVDD$  が、ハイレベルに印加され、第2電源電圧  $ELVSS$  が、ローレベルに印加される。そして、ローレベルの走査信号  $S_1$  ないし  $S_{n+1}$  が各走査線に順次に入力され、第1トランジスタ  $TB_1$  は、ターンオンされ、各走査線に連結された発光画素  $EP_2$  とダミー画素  $DP_2$  とにデータ信号が順次に入力される。このとき、ダミー画素  $DP_2$  には、不良画素に印加されたデータ信号と同一のデータ信号が印加される。それにより、第1キャパシタ  $C_1$  には、 $N$  フレームのデータ信号に対応する電圧が保存される。

20

## 【0097】

一方、第2トランジスタ  $TB_2$  は、ターンオフされ、第1ノード  $N_1$  と第2ノード  $N_2$  とを遮断する。そして、ターンオンされた第3トランジスタ  $TB_3$  を介して、第1電源電圧  $ELVDD$  から有機発光素子  $OLED$  のカソード電極までの電流経路が形成され、( $N-1$ ) フレームの走査区間の間、発光画素  $EP_2$  に書き込まれ、第2キャパシタ  $C_2$  に保存されたデータ信号に対応する輝度で、有機発光素子  $OLED$  が発光する。このとき、表示領域  $AA$  内の全ての発光画素  $EP_2$  が同時に発光する。不良画素の有機発光素子  $OLED$  は、ダミー画素  $DP_2$  からリペア線を介して供給される電流によって発光する。すなわち、走査 / 発光区間  $Scan / Emission$  では、 $N$  フレームのデータ信号が走査信号によって順次に入力され、それと同時に、( $N-1$ ) フレームのデータ信号に対応して表示領域  $AA$  内の全ての発光画素  $EP_2$  が同時に発光する。

30

## 【0098】

ここで、順次に印加される走査信号の幅を 2 水平時間 (2H) として印加し、隣接する走査信号の幅、例えば、( $n-1$ ) 番目の走査信号  $S_{n-1}$  の幅と、 $n$  番目の走査信号  $S_n$  の幅は、1H 以下ほど重畠されるように印加することが望ましい。それは、表示領域の大面積化による信号線の  $RC$  遅延による充電不足現象を克服するためである。

40

## 【0099】

図19は、本発明の他の実施形態による発光画素の回路図であり、図20は、図19の発光画素の駆動について説明するためのタイミング図である。

## 【0100】

図19を参照すれば、発光画素  $EP_3$  は、有機発光素子  $OLED$  と、有機発光素子  $OLED$  に電流を供給するための画素回路  $2C$  と、を具備する。図示されていないが、ダミー画素  $DP_3$  は、有機発光素子  $OLED$  が除外された画素回路  $2C$  を具備する。

## 【0101】

有機発光素子  $OLED$  のアノード電極は、画素回路  $2C$  に連結され、カソード電極は、第2電源電圧  $ELVSS$  を供給する第2電源と連結される。有機発光素子  $OLED$  は、画素回路  $2C$  から供給される電流に対応して所定輝度で発光する。有機発光素子  $OLED$  と

50

画素回路 2 C とが連結される領域の切断部 130 は、発光画素 E P 3 が不良画素であると判定された場合、レーザビームによって切断される領域である。

【0102】

画素回路 2 C は、8 個のトランジスタ T C 1 ないし T C 8、及び 2 個のキャパシタ C 1 及び C 2 を具備する。

【0103】

第 1 トランジスタ T C 1 のゲート電極は、走査線から走査信号 S を印加され、第 1 電極は、データ線に連結されてデータ信号 D を印加され、第 2 電極は、第 1 ノード N 1 に連結される。

【0104】

第 2 トランジスタ T C 2 のゲート電極は、第 1 制御信号 G W を印加され、第 1 電極は、第 1 ノード N 1 に連結され、第 2 電極は、第 2 ノード N 2 に連結される。

【0105】

第 3 トランジスタ T C 3 のゲート電極は、第 2 制御信号 G I を印加され、第 1 電極は、初期化電源に連結されて初期化電圧 V i n t を印加され、第 2 電極は、第 3 ノード N 3 に連結される。

【0106】

第 4 トランジスタ T C 4 のゲート電極は、第 1 制御信号 G W を印加され、第 1 電極は、第 3 ノード N 3 に連結され、第 2 電極は、第 4 ノード N 4 に連結される。

【0107】

第 5 トランジスタ T C 5 のゲート電極は、第 2 制御信号 G I を印加され、第 1 電極は、第 1 電源に連結されて第 1 電源電圧 E L V D D を印加され、第 2 電極は、第 2 ノード N 2 に連結される。

【0108】

第 6 トランジスタ T C 6 のゲート電極は、第 3 ノード N 3 に連結され、第 1 電極は、第 2 ノード N 2 に連結され、第 2 電極は、第 4 ノード N 4 に連結される。第 6 トランジスタ T C 6 は、駆動トランジスタとしての役割を行う。

【0109】

第 7 トランジスタ T C 7 のゲート電極は、第 3 制御信号 G E を印加され、第 1 電極は、第 4 ノード N 4 に連結され、第 2 電極は、有機発光素子 O L E D のアノード電極に連結される。

【0110】

第 8 トランジスタ T C 8 のゲート電極は、第 3 制御信号 G E を印加され、第 1 電極は、第 1 電源に連結されて第 1 電源電圧 E L V D D を印加され、第 2 電極は、第 2 ノード N 2 に連結される。

【0111】

第 1 キャパシタ C 1 は、第 1 ノード N 1 と、第 3 電源電圧 V h o l d を供給する第 3 電源との間に連結される。第 1 キャパシタ C 1 は、第 1 トランジスタ T C 1 がターンオンされるときのデータ線から供給されるデータ信号 D に対応する電圧を充電する。第 3 電源は、所定の電圧の固定電源（例えば、直流電源）に設定されてもよく、例えば、第 1 電源電圧 E L V D D を印加する第 1 電源、または初期化電圧 V i n t を印加する初期化電源に設定されてもよい。第 2 キャパシタ C 2 は、第 3 ノード N 3 と第 1 電源との間に連結される。

【0112】

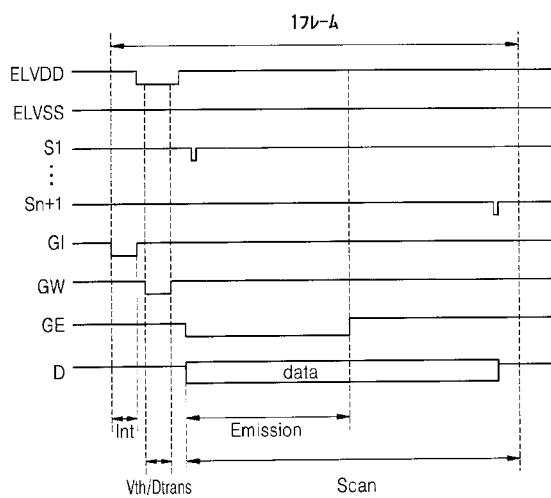

図 20 では、図 19 の画素回路 2 C を有する発光画素 E P 3 とダミー画素 D P 3 とが、図 2 に図示されたように、表示パネル 10 a に形成され、図 9 に図示されたように、不良画素リペアされた場合を例として説明する。

【0113】

図 20 を参照すれば、各発光画素 E P 3 は、同時発光方式で駆動され、各フレーム別に、初期化区間 I n t 、補償 / データ移動区間 V t h / D t r a n s 、及び走査 / 発光区間

Scan / Emissionに区分して動作する。走査 / 発光区間Scan / Emissionでは、走査信号が各走査線に対して順次に入力され、それに対応して、各発光画素E P 3とダミー画素D P 3とにデータ信号が順次に入力される。各発光画素E P 3及びダミー画素D P 3に具備された駆動トランジスタの初期化、スレショルド電圧補償、データ移動、及び各発光画素E P 3の発光動作は、フレーム別に同時に具現される。

【0114】

初期化区間I ntで、第1電源電圧E L V D Dがハイレベルに印加され、第2電源電圧E L V S S及び第2制御信号G Iが、ローレベルに印加される。それにより、第3トランジスタT C 3と、第5トランジスタT C 5とがターンオンされ、第2ノードN 2に第1電源電圧E L V D Dが印加され、第3ノードN 3に初期化電圧V i ntが印加される。

10

【0115】

補償 / データ移動区間V th / D transで、第1電源電圧E L V D D、第2電源電圧E L V S S、第1制御信号G Wがローレベルに印加される。それにより、第2トランジスタT C 2がターンオンされ、第1キャパシタC 1に保存されていた(N - 1)フレームの走査区間の間、発光画素E P 3に書き込まれたデータ信号Dが、第2ノードN 2に移動する。また、第4トランジスタT C 4がターンオンされ、第6トランジスタT C 6は、ダイオード連結され、ダイオード連結された第6トランジスタT C 6を介して、電流が流れ、第6トランジスタT C 6のスレショルド電圧を補償しながら、第2キャパシタC 2には駆動電圧E L V D Dと第2ノードN 2との電圧差が保存される。

20

【0116】

走査 / 発光区間Scan / Emissionでは、走査区間及び発光区間が同時に進められる。走査 / 発光区間Scan / Emissionで、第1電源電圧E L V D Dがハイレベルに印加され、第2電源電圧E L V S S及び第3制御信号G Eが、ローレベルに印加される。そして、ローレベルの走査信号S 1ないしS n + 1が、各走査線に順次に入力され、第1トランジスタT C 1は、ターンオンされ、各走査線に連結された発光画素E P 3に、Nフレームのデータ信号が順次に入力される。このとき、ダミー画素D P 3には、不良発光画素に印加されたデータ信号と同一のデータ信号が印加される。それにより、第1キャパシタC 1には、Nフレームのデータ信号に対応する電圧が保存される。

【0117】

一方、第2トランジスタT C 2は、ターンオフされ、第1ノードN 1と第2ノードN 2とを遮断する。そして、第7トランジスタT C 7及び第8トランジスタT C 8がターンオンされ、ターンオンされた第6トランジスタT C 6を介して、第1電源電圧E L V D Dから有機発光素子O L E Dのカソード電極までの電流経路が形成され、(N - 1)フレームの走査区間の間、発光画素E P 3に書き込まれて第2キャパシタC 2に保存されたデータ信号に対応する輝度で、有機発光素子O L E Dが発光する。このとき、表示領域A A内の全ての発光画素E P 2が同時に発光する。不良画素の有機発光素子O L E Dは、ダミー画素D P 3からリペア線を介して供給される電流によって発光する。すなわち、走査 / 発光区間Scan / Emissionでは、Nフレームのデータ信号が走査信号によって順次に入力され、それと同時に、(N - 1)フレームのデータ信号に対応して、表示領域A A内の全ての発光画素E P 3が同時に発光する。一方、発光区間Emissionは、走査区間Scanと一部重畳するが、走査区間Scanより短く遂行されてもよい。

30

40

【0118】

ここで、順次に印加される走査信号の幅を、2水平時間(2 H)で印加し、隣接する走査信号の幅、例えば、(n - 1)番目の走査信号S n - 1の幅と、n番目の走査信号S nの幅は、1 H以下ほど重畳されるように印加することが望ましい。それは、表示領域の大面積化による信号線のR C遅延による充電不足現象を克服するためである。

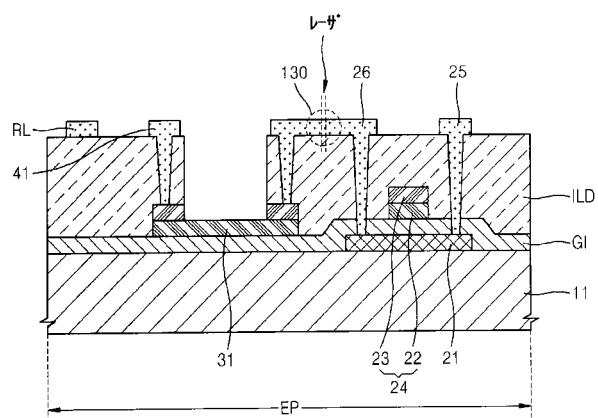

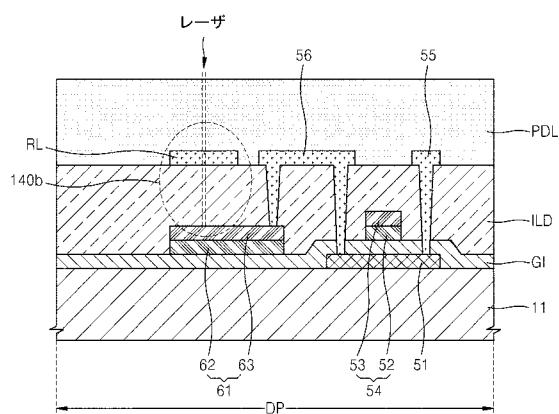

【0119】

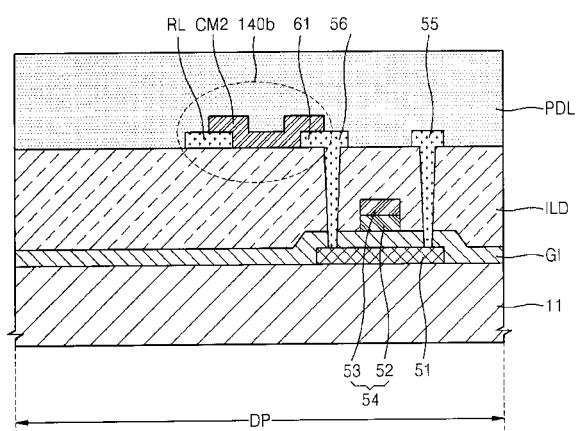

図21及び図22は、本発明の一実施形態による背面発光表示装置での発光画素リペアについて説明する断面図である。

【0120】

50

図21及び図22では、説明の便宜のために、各発光画素で、有機発光画素を構成する画素電極、及び画素回路のうち画素電極と連結される薄膜トランジスタTFTのみを図示する。薄膜トランジスタTFTは、図15に図示された画素回路2Aの第2トランジスタTA2、図17に図示された画素回路2Bの第3トランジスタTB3、または図19に図示された画素回路2Cの第7トランジスタTB7でもある。

【0121】

図21を参照すれば、基板11上部に、薄膜トランジスタTFTの活性層21を形成する。図示されていないが、基板11の上面に、不純物イオン拡散を防止し、水気や外気の浸透を防止し、表面を平坦化するためのバリア層、ブロッキング層及び/またはバッファ層のような補助層がさらに具備されてもよい。

10

【0122】

活性層21は、半導体を含んでもよく、ドーピングによって、イオン不純物を含んでもよい。また、活性層21は、酸化物半導体から形成されてもよい。活性層21は、ソース領域及びドレイン領域と、チャンネル領域とを含む。

【0123】

活性層21が形成された基板11上部に、ゲート絶縁膜GIが形成される。ゲート絶縁膜GI上部には、ゲート電極24と画素電極31とが形成される。ゲート電極24は、活性層21のチャンネル領域に対応するように形成される。

20

【0124】

ゲート電極24と画素電極31は、第1導電層及び第2導電層を、ゲート絶縁膜GI上に順に積層した後で、エッティングすることによって形成される。ゲート電極24は、第1導電層の一部に形成された第1ゲート電極22と、第2導電層の一部に形成された第2ゲート電極23とを含んでもよい。画素電極31は、第2導電層の一部が除去されながら露出された第1導電層の一部に形成されてもよい。ゲート電極24と画素電極31とが形成された基板11上部に、層間絶縁膜ILDが形成される。

20

【0125】

層間絶縁膜ILD上には、コンタクトホールを介して、活性層21のソース領域及びドレイン領域と接触するソース電極及びドレイン電極25, 26が形成される。ソース電極及びドレイン電極25, 26のうち1つの電極は、コンタクトホールを介して、画素電極31のエッジ領域に残存する第2導電層の一部と接触することにより、画素電極31と電気的に連結される。そして、層間絶縁膜ILD上には、導電物質のリペア線RLと第1連結部41とが形成される。第1連結部41は、画素電極31のエッジ領域に残存する第2導電層の一部と接触することにより、画素電極31と電気的に連結される。リペア線RLと第1連結部41は、ソース電極及びドレイン電極25, 26と同一の物質、または異なる物質から形成されてもよい。

30

【0126】

このように、バックプレーン形成後、画素回路をテストした結果、画素回路が不良である場合、画素電極31と連結されたソース電極及びドレイン電極25, 26のうち1つの電極と、画素電極31とを連結する切断部130にレーザビームを照射し、薄膜トランジスタTFTと画素電極31とを電気的に分離する。それにより、不良である発光画素の画素回路と画素電極31とが電気的に分離される。

40

【0127】

図22を参照すれば、第1リペア部140aで、リペア線RLと第1連結部41との上に、第1コンタクト金属CM(contact metal)1を形成し、リペア線RLと画素電極31とを電気的に連結する。第1コンタクト金属CM1は、化学気相蒸着(CVD)のような方法で形成する。リペア後、第1コンタクト金属CM1が形成された基板11上に、画素電極31を露出させるホールを具備する画素定義膜PDLが形成される。

【0128】

その後、画素電極31上には、発光層を含む有機膜及び対向電極が順に形成される。有機膜が赤色、緑色、青色の光をそれぞれ放出する場合、発光層は、赤色発光層、緑色発光

50

層及び青色発光層にそれぞれパターニングされる。一方、有機膜が白色光を放出する場合、発光層は、白色光を放出するように、赤色発光層、緑色発光層及び青色発光層が積層された多層構造を有するか、あるいは赤色発光物質、緑色発光物質及び青色発光物質を含んだ単一層構造を有することができる。対向電極は、基板11の全面に蒸着されて共通電極として形成される。本発明の実施形態では、画素電極31がアノード電極として使用され、対向電極は、カソード電極として使用される。電極の極性は、反対に適用されてもよいということは、言うまでもない。

【0129】

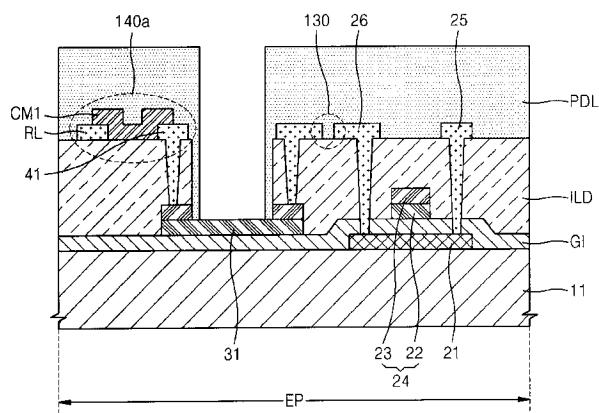

図23は、本発明の一実施形態による背面発光表示装置でのダミー画素連結について説明する断面図である。

10

【0130】

図23では、説明の便宜のために、ダミー画素の画素回路のうち、リペア線RLと連結される薄膜トランジスタTFTのみを図示する。ダミー画素DPの画素回路は、図21及び図22に図示された発光画素EPの画素回路が形成されると同時に、同一物質から形成される。従って、図23に図示された薄膜トランジスタTFTは、図15に図示された画素回路2Aの第2トランジスタTA2、図17に図示された画素回路2Bの第3トランジスタTB3、または図19に図示された画素回路2Cの第7トランジスタTB7でもある。

【0131】

図23を参照すれば、基板11上部に、薄膜トランジスタTFTの活性層51を形成する。活性層51は、半導体を含んでもよく、ドーピングによって、イオン不純物を含んでもよい。また活性層51は、酸化物半導体からも形成される。活性層51は、ソース領域及びドレイン領域と、チャネル領域とを含む。活性層51が形成された基板11上部に、ゲート絶縁膜GIが形成される。ゲート絶縁膜GI上部には、ゲート電極54が形成される。

20

【0132】

ゲート電極54は、活性層51のチャネル領域に対応するように形成される。ゲート電極54は、第1導電層及び第2導電層をゲート絶縁膜GI上に順に積層した後、エッチングすることによって形成される。ゲート電極54は、第1導電層の一部に形成された第1ゲート電極52と、第2導電層の一部に形成された第2ゲート電極53とを含んでもよい。ゲート電極54が形成された基板11上部に、層間絶縁膜ILDが形成される。

30

【0133】

層間絶縁膜ILD上には、コンタクトホールを介して、活性層51のソース領域及びドレイン領域と接触するソース電極及びドレイン電極55, 56が形成される。そして、層間絶縁膜ILD上には、導電物質のリペア線RLと第2連結部61とが形成される。第2連結部61は、ソース電極及びドレイン電極55, 56のうち1つの電極の延長部である。リペア線RLは、ソース電極及びドレイン電極55, 56と同一の物質、または異なる物質から形成されもする。

【0134】

第2リペア部140bで、リペア線RLと第2連結部61との上に、第2コンタクト金属CM2が形成され、リペア線RLと第2連結部61とが電気的に連結される。第2コンタクト金属CM2は、第1コンタクト金属CM1と同時に同一物質で、化学気相蒸着(CVD)のような方法で形成する。第2コンタクト金属CM2が形成された基板11上に、画素定義膜PDLが形成される。

40

【0135】

本発明の実施形態は、バックプレーン形成時に発生する発光画素の画素回路が不良である場合、画素回路不良による明点を克服するため、発光画素の画素電極と薄膜トランジスタとの連結を切り、画素電極と連結された連結部とリペア線とを連結する。発光画素の画素電極と連結されたリペア線は、ダミー画素の画素回路と連結される。それにより、発光画素の画素回路に入力されるデータ信号と同一のデータ信号が、ダミー画素の画素回路に

50

入力され、入力されたデータ信号に対応する輝度で、発光画素の発光素子が発光する。

【0136】

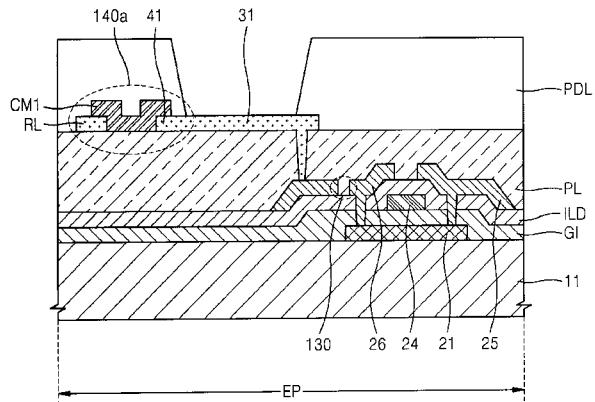

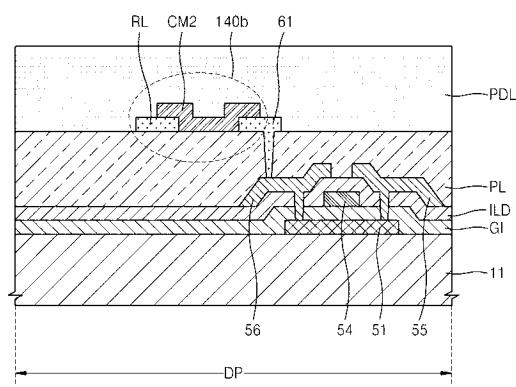

図24は、本発明の一実施形態による前面発光表示装置での発光画素リペアについて説明する断面図である。図25は、本発明の一実施形態による前面発光表示装置でのダミー画素連結について説明する断面図である。

【0137】

図24及び図25では、説明の便宜のために、発光画素とダミー画素との画素回路において、リペア線RLと連結される薄膜トランジスタTFTのみを図示する。

【0138】

図24及び図25を共に参照すれば、基板11上部に、発光画素EPの薄膜トランジスタTFTの活性層21と、ダミー画素DPの薄膜トランジスタTFTの活性層51とを形成する。図示されていないが、基板11の上面に、不純物イオン拡散を防止し、水気や外気の浸透を防止し、表面を平坦化するためのバリア層、ブロッキング層及び/またはバッファ層のような補助層がさらに具備される。

10

【0139】

活性層21, 51は、半導体を含んでもよく、ドーピングによってイオン不純物を含んでもよい。また活性層21, 51は、酸化物半導体から形成されてもよい。活性層21, 51は、ソース領域及びドレイン領域と、チャンネル領域とを含む。活性層21, 51が形成された基板11上部に、ゲート絶縁膜GIを形成する。

20

【0140】

ゲート絶縁膜GI上部には、発光画素EPのゲート電極24と、ダミー画素DPのゲート電極54とが形成される。ゲート電極24, 54それぞれは、活性層21, 51のチャンネル領域にそれぞれ対応するように形成される。ゲート電極24, 54が形成された基板11上部に、層間絶縁膜ILDを形成する。

20

【0141】

層間絶縁膜ILD上には、コンタクトホールを介して、活性層21, 51のソース領域及びドレイン領域と接触するソース電極及びドレイン電極25/26, 55/56がそれぞれ形成される。ソース電極及びドレイン電極25/26, 55/56が形成された基板11上部に、平坦化膜PLを形成する。平坦化膜PLは、画素電極31に対応する領域の表面を凹凸にエンボシング構造を有するように形成する。

30

【0142】

平坦化膜PL上部には、発光画素EPの画素電極31、第1連結部41、リペア線RL、及びダミー画素DPのソース電極及びドレイン電極55, 56のうち1つの電極と連結された第2連結部61が形成される。第1連結部41は、画素電極31から延長された延長部である。リペア線RLは、画素電極31の周辺に隣接するように形成される。リペア線RL、第2連結部61、画素電極31は、同一の物質または異なる物質から形成されてもする。画素電極31は、平坦化膜PLの形態により、凹凸のエンボシング構造を有するように形成することができる。

【0143】

このように、バックプレーン形成後、画素回路をテストした結果、画素回路が不良である場合、画素電極31と連結されたソース電極及びドレイン電極25, 26のうち1つの電極と、画素電極31とを連結する切断部130に、レーザビームを照射し、発光画素EPの薄膜トランジスタTFTと、画素電極31とを電気的に分離する。それにより、不良である発光画素の画素回路と画素電極31とが電気的に分離される。

40

【0144】

そして、第1リペア部140aで、第1コンタクト金属CM1によって、リペア線RLと第1連結部41とを電気的に連結する。そして、第2リペア部140bで、第2コンタクト金属CM2によって、リペア線RLと第2連結部61とを電気的に連結する。第1コンタクト金属CM1と第2コンタクト金属CM2は、同時に同一物質で化学気相蒸着(CVD)のような方法で形成する。リペア後、第1コンタクト金属CM1と第2コンタクト

50

金属C M 2 とが形成された基板1 1 上に、画素定義膜P L D が形成される。

【0 1 4 5】

図示されていないが、画素電極3 1 上には、発光層を含む有機膜と対向電極とが形成される。有機膜と対向電極は、画素電極3 1 と同様に、平坦化膜P L の形態によって、凹凸のエンボシング構造を有するように形成される。その場合、発光層から生じた光の進行方向に位置する構成要素の表面が屈曲を有するように、凹凸を具備することにより、全反射条件が満足して全反射が生じても、反射する光の入射角を変化させ、1 つの構成要素内で、継続的に全反射の発生を防止することにより、ユーザが見つめる面に透過してくる光量を増やし、光効率を極大化させるという効果がある。

【0 1 4 6】

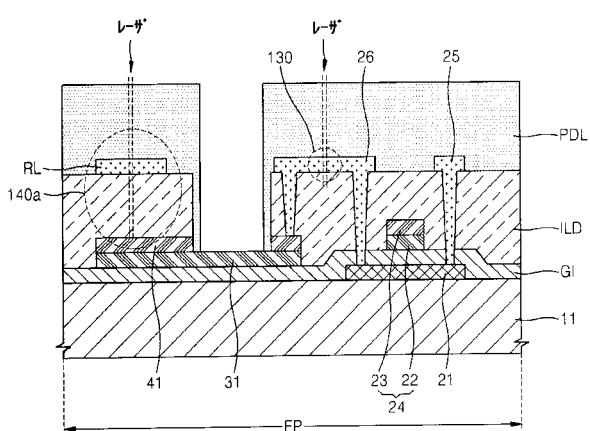

図2 6 は、本発明の他の実施形態による背面発光表示装置での発光画素リペアについて説明する断面図である。図2 7 は、本発明の他の実施形態による背面発光表示装置でのダミー画素連結について説明する断面図である。

【0 1 4 7】

図2 6 及び図2 7 では、説明の便宜のために、発光画素とダミー画素との画素回路のうち、リペア線R L と連結される薄膜トランジスタT F T のみを図示する。図2 6 及び図2 7 に図示された実施形態は、表示パネルのビジョン(vision)検査後、リペアを行う場合である。

【0 1 4 8】

図2 6 及び図2 7 を共に参照すれば、基板1 1 上部に、発光画素E P の薄膜トランジスタT F T の活性層2 1 と、ダミー画素D P の薄膜トランジスタT F T の活性層5 1 とを形成する。図示されていないが、基板1 1 の上面に、不純物イオン拡散を防止し、水気や外気の浸透を防止し、表面を平坦化するためのバリア層、ブロッキング層及び/またはバッファ層のような補助層がさらに具備される。

【0 1 4 9】

活性層2 1 , 5 1 は、半導体を含んでもよく、ドーピングによって、イオン不純物を含んでもよい。また活性層2 1 , 5 1 は、酸化物半導体からも形成される。活性層2 1 , 5 1 は、ソース領域及びドレイン領域と、チャンネル領域とを含む。活性層2 1 , 5 1 が形成された基板1 1 上部に、ゲート絶縁膜G I を形成する。

【0 1 5 0】

ゲート絶縁膜G I 上部には、発光画素E P のゲート電極2 4 と、ダミー画素D P のゲート電極5 4 とが形成される。ゲート電極2 4 , 5 4 は、活性層2 1 , 5 1 のチャンネル領域に対応するように形成される。ゲート電極2 4 , 5 4 は、第1導電層及び第2導電層を、ゲート絶縁膜G I 上に順に積層した後、エッチングすることによって形成される。ゲート電極5 4 は、第1導電層の一部に形成された第1ゲート電極2 2 , 5 2 と、第2導電層の一部に形成された第2ゲート電極2 3 , 5 3 と、を含んでもよい。

【0 1 5 1】

また、ゲート絶縁膜G I 上部には、発光画素E P の画素電極3 1 と第1連結部4 1 とが形成され、ダミー画素D P の第2連結部6 1 が形成される。画素電極3 1 は、第2導電層の一部が除去ながら露出された第1導電層の一部に形成される。第1連結部4 1 は、画素電極3 1 から延長された延長部でもあり、第1導電層と第2導電層との一部でもある。第2連結部6 1 は、第1導電層の一部に形成された第1層6 2 と、第2導電層の一部に形成された第2層6 3 と、を含んでもよい。ゲート電極2 4 , 5 4 及び第1連結部及び第2連結部4 1 , 6 1 が形成された基板1 1 上部に、層間絶縁膜I L D が形成される。

【0 1 5 2】

層間絶縁膜I L D 上には、コンタクトホールを介して、活性層2 1 , 5 1 のソース領域及びドレイン領域と接触するソース電極及びドレイン電極2 5 / 2 6 , 5 5 / 5 6 が形成される。そして、層間絶縁膜I L D 上には、リペア線R L が、第1連結部4 1 及び第2連結部6 1 と少なくとも一部重畳するように形成される。ソース電極及びドレイン電極2 5 / 2 6 , 5 5 / 5 6 、及びリペア線R L が形成された基板1 1 上部に、画素定義膜P D L

10

20

30

40

50

を形成する。

【0153】

ビジョン検査後、不良画素として検出された発光画素 E P で、画素電極 3 1 と連結されたソース電極及びドレイン電極 2 5, 2 6 のうち 1 つの電極と、画素電極 3 1 とを連結する切断部 1 3 0 にレーザビームを照射してカッティングすることにより、発光画素 E P の薄膜トランジスタ TFT と、画素電極 3 1 とを電気的に分離する。それにより、不良である発光画素の画素回路と画素電極 3 1 とが電気的に分離される。

【0154】

そして、発光画素 E P の第 1 リペア部 1 4 0 a にレーザビームを照射し、レーザ・ウェルディングを行う。それにより、リペア線 R L と第 1 連結部 4 1 との間の絶縁膜が破壊され、リペア線 R L と第 1 連結部 4 1 とが電気的に連結される。また、ダミー画素 D P の第 2 リペア部 1 4 0 b にレーザビームを照射し、レーザ・ウェルディングを行う。それにより、リペア線 R L と第 2 連結部 6 1 との間の絶縁膜が破壊され、リペア線 R L と第 2 連結部 6 1 とが電気的に連結される。

10

【0155】

ビジョン検査前後、画素電極 3 1 上には、発光層を含む有機膜及び対向電極が順に形成される。有機膜が、赤色、緑色、青色の光をそれぞれ放出する場合、発光層は、赤色発光層、緑色発光層及び青色発光層にそれぞれパターニングされる。一方、有機膜が白色光を放出する場合、発光層は、白色光を放出するように赤色発光層、緑色発光層及び青色発光層が積層された多層構造を有するか、あるいは赤色発光物質、緑色発光物質及び青色発光物質を含んだ単一層構造を有することができる。対向電極は、基板 1 1 の全面に蒸着され、共通電極として形成される。本発明の実施形態では、画素電極 3 1 がアノード電極として使用され、対向電極は、カソード電極として使用されるが、電極の極性は、反対に適用されてもよいことは、言うまでもない。

20

【0156】

本発明の実施形態は、特定回路の不良時、リペア線を利用して、レーザ・ウェルディング方法で、簡単にリペアを行うことにより、表示装置の製造収率を向上させることができる。

【0157】

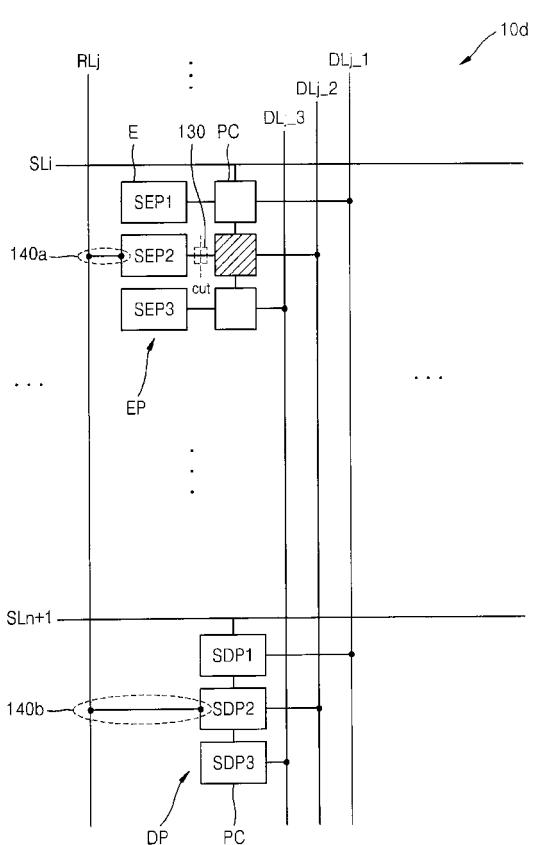

図 2 8 は、本発明の他の実施形態による表示パネルを示す図面である。

30

【0158】

図 2 8 を参照すれば、表示パネル 1 0 d には、複数の走査線 S L 、複数のデータ線 D L 、及び複数のリペア線 R L の交差部に、ほぼ行列状に配列された複数の画素 P が形成される。画素 P は、表示領域 A A に形成された発光画素 E P と、非表示領域 N A に形成されたダミー画素 D P と、を含む。非表示領域 N A は、表示領域 A A の上下部のうち少なくとも 1 つの領域に形成される。それにより、ダミー画素 D P は、画素列の上下部のうち少なくとも 1 つの領域に画素列ごとに形成される。図 2 8 では、画素列の下部にダミー画素 D P が形成された例を図示している。

【0159】

1 つの発光画素 E P は、3 つの発光副画素 S E P 1, S E P 2, S E P 3 から構成され、発光副画素 S E P 1, S E P 2, S E P 3 は、列方向に沿って配列される。各発光副画素 S E P 1, S E P 2, S E P 3 は、画素回路 P C と、画素回路 P C と連結された発光素子 E と、を具備する。発光素子 E は、アノード電極、カソード電極及びアノード電極とカソード電極との間の発光層を含む有機発光素子 O L E D である。各発光副画素 S E P 1, S E P 2, S E P 3 の画素回路 P C 、及び / または発光素子 E は、サイズが異なりもある。3 つの発光副画素 S E P 1, S E P 2, S E P 3 は、1 つの走査線 S L i に共通して連結され、3 本のデータ線 D L j \_ 1, D L j \_ 2, D L j \_ 3 にそれぞれ連結される。従って、走査線 S L i に走査信号が供給されれば、データ信号が、3 本のデータ線 D L j \_ 1, D L j \_ 2, D L j \_ 3 を介して、各発光副画素 S E P 1, S E P 2, S E P 3 に供給され、それにより、各発光副画素 S E P 1, S E P 2, S E P 3 は、当該データ信号

40

50

に対応する電圧を充電し、これに対応する輝度で発光する。

【0160】

ダミー画素DPもまた、3つのダミー副画素SDP1, SDP2, SDP3から構成され、ダミー副画素SDP1, SDP2, SDP3は、列方向に沿って配列される。各ダミー副画素SDP1, SDP2, SDP3は、発光素子Eなしに、画素回路PCのみを具備する。ダミー副画素SDP1, SDP2, SDP3の画素回路PCは、発光副画素SEP1, SEP2, SEP3の画素回路PCと同一である。3つのダミー副画素SDP1, SDP2, SDP3は、1つの走査線SLn+1に共通して連結され、3本のデータ線DLj\_1, DLj\_2, DLj\_3にそれぞれ連結される。従って、走査線SLn+1に走査信号が供給されれば、データ信号が、3本のデータ線DLj\_1, DLj\_2, DLj\_3を介して、各ダミー副画素SDP1, SDP2, SDP3に供給される。

10

【0161】

発光副画素SEP1, SEP2, SEP3のうち、第2発光副画素SEP2の画素回路PCが不良である場合、第2発光副画素SEP2の画素回路PCと発光素子Eとを連結する切断部130を分離し(cut)、発光素子Eをリペア線RLjと連結する。そして、ダミー副画素SDP1, SDP2, SDP3のうち、第2発光副画素SEP2に対応する第2ダミー副画素SDP2の画素回路PCをリペア線RLjと連結する。

20

【0162】

走査区間で、走査線SL1ないしSLnに走査信号が順に供給されれば、データ信号が、3本のデータ線DLj\_1, DLj\_2, DLj\_3を介して、各発光副画素SEP1, SEP2, SEP3に供給される。最後の走査線SLn+1に、最後の走査信号が供給されれば、i番目の走査線SLiに供給されたデータ信号と同一のデータ信号が各ダミー副画素SDP1, SDP2, SDP3に供給され、リペア線RLjと連結された第2ダミー副画素SDP2に、充電されたデータ信号に対応する電圧による電流がリペア線RLjを介して、第2発光副画素SEP2に供給される。それにより、発光区間に、全ての発光画素EPが同時に発光する。

20

【0163】

図28の実施形態は、1つの画素を構成する複数の副画素の特性が異なる場合、ダミー画素を複数の副画素で形成した例である。しかし、その場合にも、ダミー画素を1つの副画素で構成し、ダミー画素に印加されるデータ信号のガンマ値を補正することにより、同一に駆動することができる。

30

【0164】

前述の実施形態では、画素回路をPMOS(positive channel metal oxide semiconductor)トランジスタで具現し、ローレベルの信号がイネーブル信号であり、ハイレベルの信号がディスエーブル信号である例について説明したが、画素回路をNMOS(negative channel metal oxide semiconductor)トランジスタで具現し、印加される信号を反転させることにより、本発明の駆動方法を適用してもよいことは、言うまでもない。その場合、ハイレベルの信号がイネーブル信号になり、ローレベルの信号がディスエーブル信号になる。

40

【0165】

本発明の実施形態で、薄膜トランジスタTFTの動作点は、飽和領域(saturation range)に含まれ、不良画素のアノード電極の抵抗が高い場合、抵抗値を予測して不良画素の電流補正を行う。

【0166】

本発明の実施形態は、前述の特定画素構造及び同時発光駆動に限定されるものではなく、多様な方式で同時発光を行う多様な画素に適用され、発光画素の画素回路と発光素子とを分離し、リペア線を介して、ダミー画素の画素回路と連結することにより、画素回路の不良が発生しても、明点化または暗点化なしに同時発光を行うのである。

【0167】

本明細書では、本発明を限定された実施形態を中心に説明したが、本発明の範囲内で多

50

様な実施形態が可能である。また、説明しないにしても、均等な手段もまた、本発明にそのまま結合されるものと言うことができる。従って、本発明の真の保護範囲は、特許請求の範囲によって決まるものである。

【産業上の利用可能性】

【0168】

本発明の有機発光表示装置、該有機発光表示装置のリペア方法及び該有機発光表示装置の駆動方法は、例えば、ディスプレイ関連の技術分野に効果的に適用可能である。

【符号の説明】

【0169】

|                                     |         |    |

|-------------------------------------|---------|----|

| 2 A , 2 B , 2 C                     | 画素回路    | 10 |

| 1 0 , 1 0 a , 1 0 b , 1 0 c , 1 0 d | 表示パネル   |    |

| 1 1                                 | 基板      |    |

| 2 0                                 | 走査駆動部   |    |

| 2 1 , 5 1                           | 活性層     |    |

| 2 2 , 5 2                           | 第1ゲート電極 |    |

| 2 3 , 5 3                           | 第2ゲート電極 |    |

| 2 4 , 5 4                           | ゲート電極   |    |

| 2 5 , 5 5                           | ソース電極   |    |

| 2 6 , 5 6                           | ドレイン電極  |    |

| 3 0                                 | データ駆動部  | 20 |

| 3 1                                 | 画素電極    |    |

| 4 0                                 | 制御部     |    |

| 4 1                                 | 第1連結部   |    |

| 6 1                                 | 第2連結部   |    |

| 0 0                                 | 表示装置    |    |

| 1 3 0                               | 切断部     |    |

| 1 4 0 a                             | 第1リペア部  |    |

| 1 4 0 b                             | 第2リペア部  |    |

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 7】

【図 6】

【図 8】

【図 9】

【図 10】

【図11】

【図12】

【図13】

【図14】

【 図 15 】

【 図 17 】

## 【 図 1 6 】

【 図 1 8 】

【 図 1 9 】

【図20】

【図21】

【図22】

【図23】

【図24】

【図26】

【図25】

【図27】

【図28】

## フロントページの続き

| (51)Int.Cl.            | F I          | テーマコード(参考) |

|------------------------|--------------|------------|

| H 05 B 33/26 (2006.01) | G 09 G 3/20  | 6 7 0 A    |

| H 05 B 33/12 (2006.01) | H 05 B 33/14 | A          |

|                        | H 05 B 33/10 |            |

|                        | H 05 B 33/22 | Z          |

|                        | H 05 B 33/26 | Z          |

|                        | H 05 B 33/12 | B          |

(72)発明者 金 那 英

大韓民国京畿道龍仁市器興区三星二路 95 三星ディスプレイ株式會社内

(72)発明者 趙 秀 範

大韓民国京畿道龍仁市器興区三星二路 95 三星ディスプレイ株式會社内

(72)発明者 李 在 鍛

大韓民国京畿道龍仁市器興区三星二路 95 三星ディスプレイ株式會社内

(72)発明者 許 命 九

大韓民国京畿道龍仁市器興区三星二路 95 三星ディスプレイ株式會社内

F ターム(参考) 3K107 AA01 BB01 CC33 CC45 DD21 DD39 DD89 DD90 EE03 FF15

GG14 GG28 GG57 HH02 HH05

5C080 AA06 BB05 CC03 DD05 DD22 DD28 EE29 EE30 FF11 FF12

HH09 JJ02 JJ03 JJ04 JJ06

5C380 AA01 AB06 AB11 AB12 AB34 AB43 BA11 BA29 BA38 BA39

BB02 BE03 CA04 CA08 CA12 CA13 CA32 CA34 CB01 CB16

CB17 CB20 CC04 CC07 CC30 CC33 CC39 CC41 CC52 CC64

CC65 CD024 CD028 CD035 DA02 DA06 DA19 DA47 FA21 GA05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示装置，有机发光显示装置的修复方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2014203081A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2014-10-27 |

| 申请号            | JP2014072420                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2014-03-31 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星显示器的股票会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 康起寧<br>金那英<br>趙秀範<br>李在鎬<br>許命九                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 康起寧<br>金那英<br>趙秀範<br>李在鎬<br>許命九                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/10 H05B33/22 H05B33/26 H05B33/12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | H01L27/3276 G02F1/136259 G09G3/20 G09G3/3225 G09G3/3233 G09G3/3241 G09G2230/00<br>G09G2300/0413 G09G2300/0426 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2330/08<br>G09G2330/10 H01L27/3223 H01L2251/568                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A G09G3/20.670.Q G09G3/20.670.A<br>H05B33/14.A H05B33/10 H05B33/22.Z H05B33/26.Z H05B33/12.B G09G3/3225 G09G3/3233 G09G3<br>/3266 G09G3/3275 G09G3/3283 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC45 3K107/DD21 3K107/DD39 3K107/DD89 3K107<br>/DD90 3K107/EE03 3K107/FF15 3K107/GG14 3K107/GG28 3K107/GG57 3K107/HH02 3K107/HH05<br>5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD22 5C080/DD28 5C080/EE29 5C080<br>/EE30 5C080/FF11 5C080/FF12 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C380<br>/AA01 5C380/AB06 5C380/AB11 5C380/AB12 5C380/AB34 5C380/AB43 5C380/BA11 5C380/BA29<br>5C380/BA38 5C380/BA39 5C380/BB02 5C380/BE03 5C380/CA04 5C380/CA08 5C380/CA12 5C380<br>/CA13 5C380/CA32 5C380/CA34 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB20 5C380/CC04<br>5C380/CC07 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC52 5C380/CC64 5C380<br>/CC65 5C380/CD024 5C380/CD028 5C380/CD035 5C380/DA02 5C380/DA06 5C380/DA19 5C380<br>/DA47 5C380/FA21 5C380/GA05 |         |            |

| 代理人(译)         | 松永信行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 优先权            | 1020130035459 2013-04-01 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP6552157B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

**摘要(译)**

提供了一种有机发光显示装置，一种用于修复该有机发光显示装置的方法以及用于驱动该有机发光显示装置的方法。一种有机发光显示装置，一种用于修复该有机发光显示装置的方法以及用于驱动该有机发光显示装置的方法，其中，有机发光显示装置沿列方向和行方向布置，多个发光像素，每个发光像素包括连接至发光元件的第一像素电路；形成在每列中的至少一个伪像素，并且包括第二像素电路；以及形成在每列中的修复线。在多个发光像素中，相同的数据信号以恒定的时间差被提供给连接到修复线的发光像素和连接到修复线的虚拟像素，并且多个发光像素同时发光。它的特点是 [选型图]图1