(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-279667

(P2007-279667A)

(43) 公開日 平成19年10月25日(2007.10.25)

| (51) Int.CI.                | F 1                                 | テーマコード (参考) |

|-----------------------------|-------------------------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K107                   |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 611A 5C080                |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 642A                      |             |

| <b>H05B 33/08</b> (2006.01) | G09G 3/20 622Q                      |             |

|                             | G09G 3/20 622G                      |             |

|                             | 審査請求 有 請求項の数 17 O L (全 17 頁) 最終頁に続く |             |

|              |                              |          |                     |

|--------------|------------------------------|----------|---------------------|

| (21) 出願番号    | 特願2006-277770 (P2006-277770) | (71) 出願人 | 590002817           |

| (22) 出願日     | 平成18年10月11日 (2006.10.11)     |          | 三星エスディアイ株式会社        |

| (31) 優先権主張番号 | 10-2006-0031636              |          | 大韓民国京畿道水原市靈通区▲しん▼洞5 |

| (32) 優先日     | 平成18年4月6日 (2006.4.6)         |          | 75番地                |

| (33) 優先権主張国  | 韓国(KR)                       | (74) 代理人 | 100072349           |

|              |                              |          | 弁理士 八田 幹雄           |

|              |                              | (74) 代理人 | 100110995           |

|              |                              |          | 弁理士 奈良 泰男           |

|              |                              | (74) 代理人 | 100114649           |

|              |                              |          | 弁理士 宇谷 勝幸           |

|              |                              | (74) 代理人 | 100129126           |

|              |                              |          | 弁理士 藤田 健            |

|              |                              | (74) 代理人 | 100130971           |

|              |                              |          | 弁理士 郡祭 正則           |

最終頁に続く

(54) 【発明の名称】走査駆動回路とこれを利用した有機電界発光表示装置

## (57) 【要約】

【課題】電流書き込み型有機電界発光装置に利用される走査駆動回路を提供する。

【解決手段】走査信号を生成する複数の走査信号生成手段S C Uから構成される第1走査駆動部310と、発光制御信号を生成する複数の発光制御生成手段C C Uから構成される第2走査駆動部320と、を含み、複数の走査信号生成手段S C Uは互いに直列に配列され、各走査信号生成手段S C Uは、入力信号または隣接する走査信号生成手段S C Uから生成される走査信号と、第1クロック信号C L K 1および第2クロック信号C L K 2との入力を受けて走査信号を生成し、複数の発光制御信号生成手段C C Uは互いに直列に配列され、各発光制御信号生成手段C C Uは、2つの走査信号生成手段S C Uから順次に生成される2個の走査信号と、第1クロック信号C L K 1および/または第2クロック信号C L K 2との入力を受けて一つの発光制御信号を生成することを特徴とする。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

走査信号を生成する複数の走査信号生成手段から構成される第1走査駆動部と、発光制御信号を生成する複数の発光制御生成手段から構成される第2走査駆動部と、を含み、

前記複数の走査信号生成手段は互いに直列に配列され、前記各走査信号生成手段は、入力信号または隣接する前記走査信号生成手段から生成される走査信号と、第1クロック信号および第2クロック信号との入力を受けて走査信号を生成し、

前記複数の発光制御信号生成手段は互いに直列に配列され、前記各発光制御信号生成手段は、前記2つの走査信号生成手段から順次に生成される2個の走査信号と、第1クロック信号および／または第2クロック信号との入力を受けて一つの発光制御信号を生成することを特徴とする走査駆動回路。10

**【請求項 2】**

前記各走査信号生成手段は、

前記入力信号または隣接する前記走査信号生成手段から生成される走査信号の入力を受けて、第1クロック端子にゲート端子が接続された第1トランジスタと、

前記第1トランジスタの出力端にゲート端子が接続されて、第2クロック端子及び出力ラインに接続された第2トランジスタと、

前記第1クロック端子にゲート端子が接続されて、第2電源及び第1ノードの間に接続された第3トランジスタと、20

前記第1トランジスタの出力端にゲート端子が接続されて、第1クロック端子及び第1ノードの間に接続された第4トランジスタと、

前記第1ノードにゲート端子が接続されて、第1電源及び前記出力ラインの間に接続された第5トランジスタと、

が含まれて構成されることを特徴とする請求項1に記載の走査駆動回路。

**【請求項 3】**

前記第1トランジスタの出力端及び前記出力ラインの間に接続された第1キャパシタがさらに含まれて構成されることを特徴とする請求項2に記載の走査駆動回路。

**【請求項 4】**

前記走査信号生成手段および前記発光制御信号生成手段は、30

前記第1クロック信号および前記第2クロック信号が入力される端子である第1クロック端子および第2クロック端子を具備し、

前記第1クロック信号および第2クロック信号は、位相が相違し、レベルが同一となる期間を有することを特徴とする請求項1に記載の走査駆動回路。

**【請求項 5】**

前記複数の走査信号生成手段は、前記第1クロック信号が前記第1クロック端子に供給される第1走査信号生成手段と、前記第2クロック信号が前記第2クロック端子に供給される第2走査信号生成手段と、を含み、

前記第1走査信号生成手段と前記第2走査信号生成手段とが交互に配列されることを特徴とする請求項4に記載の走査駆動回路。40

**【請求項 6】**

前記第1クロック信号がローレベルに入力され、前記第2クロック信号がハイレベルに入力される期間にプリチャージが遂行されて、前記第1クロック信号がハイレベルで、前記第2クロック信号がローレベルに入力される期間に評価が遂行されることを特徴とする請求項5に記載の走査駆動回路。

**【請求項 7】**

前記複数の走査信号生成手段は、前記第2クロック信号が前記第1クロック端子に供給される第1走査信号生成手段と、前記第1クロック信号が前記第2クロック端子に供給される第2走査信号生成手段と、を含み、

前記第1走査信号生成手段と前記第2走査信号生成手段とが交互に配列されることを特50

徴とする請求項 4 に記載の走査駆動回路。

【請求項 8】

前記第 1 クロック信号がハイレベルに入力され、前記第 2 クロック信号がローレベルに入力される期間にプリチャージが遂行されて、前記第 1 クロック信号がローレベルで、前記第 2 クロック信号がハイレベルに入力される期間に評価が遂行されることを特徴とする請求項 7 に記載の走査駆動回路。

【請求項 9】

前記プリチャージ期間にはハイレベルが出力されて、前記評価期間には前記プリチャージ期間に受けた入力にあたるレベルの信号が出力されて、

前記第 1 クロック信号、および 2 クロック信号が共にハイレベルである期間の前がプリチャージ期間なら以前の出力を維持して、評価期間ならハイレベルが出力されることを特徴とする請求項 6 または請求項 8 に記載の走査駆動回路。 10

【請求項 10】

前記各発光制御信号生成手段は、

第 1 電源と出力端との間に接続された第 1 スイッチング素子と、

出力端と第 2 電源との間に接続された第 2 スイッチング素子と、

第 1 電極が出力端に接続されて、第 2 電極が第 2 スイッチング素子のゲート電極に連結する第 1 ノードに接続された第 1 キャパシタと、

第 1 ノードと出力端及び第 1 スイッチング素子のゲート電極とに接続された第 3 スイッチング素子と、 20

第 1 ノードと第 2 電源との間に接続されてゲート電極がコンバーション部の出力端に接続された第 4 スイッチング素子と、

を含んで構成されることを特徴とする請求項 1 に記載の走査駆動回路。

【請求項 11】

前記第 1 スイッチング素子及び第 3 スイッチング素子は、

それぞれ二つのトランジスタが結合して具現されるトランスマッシュゲート構造を持つトランジスタであることを特徴とする請求項 10 に記載の走査駆動回路。

【請求項 12】

前記コンバーション部は、

第 1 電源と第 3 ノードとの間に接続された第 5 スイッチング素子と、 30

第 3 ノードと第 1 入力端子との間に接続された第 6 スイッチング素子と、

コンバーション部の出力端と第 2 入力端子との間に接続されて、ゲート電極が第 3 ノードに接続された第 7 スイッチング素子と、

前記第 3 ノードとコンバーション部の出力端との間に接続された第 2 キャパシタと、

が含まれて構成されることを特徴とする請求項 10 に記載の走査駆動回路。

【請求項 13】

第 1 電源とコンバーション部の出力端との間に接続された第 8 スイッチング素子がさらに含まれることを特徴とする請求項 10 に記載の走査駆動回路。

【請求項 14】

前記第 8 スイッチング素子のゲート電極は、

第 2 走査信号の入力ラインまたは第 1 クロック信号に接続されることを特徴とする請求項 10 に記載の走査駆動回路。 40

【請求項 15】

前記第 5 スイッチング素子のゲート電極は、

第 1 走査信号の入力ラインに接続されて、前記第 6 スイッチング素子のゲート電極は第 2 走査信号の入力ラインまたは第 1 クロック信号に接続されることを特徴とする請求項 10 に記載の走査駆動回路。

【請求項 16】

前記第 1 入力端子には第 2 走査信号または第 1 クロック信号が入力されて、第 2 入力端子には第 2 クロック信号が入力されることを特徴とする請求項 10 に記載の走査駆動回路 50

。

### 【請求項 1 7】

走査線、データ線、および発光信号線に接続されるように位置される複数の画素を含む画素部と、

前記データ線にデータ信号を供給するデータ駆動回路と、

走査信号を生成する複数の走査信号生成手段から構成される第1走査駆動部と、発光制御信号を生成する複数の発光制御生成手段から構成される第2走査駆動部と、を含む走査駆動回路と、を含み

前記複数の走査信号生成手段は互いに直列に配列され、前記各走査信号生成手段は、入力信号または隣接する前記走査信号生成手段から生成される走査信号と、第1クロック信号および第2クロック信号と、の入力を受けて走査信号を生成し、

前記複数の発光制御信号生成手段は互いに直列に配列され、前記各発光制御信号生成手段は、前記2つの走査信号生成手段から順次に生成される2個の走査信号と、第1クロック信号およびノーマルまたは第2クロック信号と、の入力を受けて一つの発光制御信号を生成することを特徴とする有機電界発光表示装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は有機電界発光表示装置に関し、特に電流書き込み型有機電界発光装置に利用される走査駆動回路に関する。

#### 【背景技術】

#### 【0002】

最近、陰極線管(Cathode Ray Tube)の短所である重さと体積を減らすことができる各種平板表示装置が開発されている。平板表示装置では液晶表示装置(Liquid Crystal Display)、電界放出表示装置(Field Emission Display)、プラズマ表示パネル(Plasma Display Panel)、及び有機電界発光表示装置(Organic Light Emitting Display)などがある。

#### 【0003】

平板表示装置の中で有機電界発光表示装置は、電子と正孔との再結合によって光を発生する有機発光ダイオードを利用して映像を表示する。このような有機発光表示装置は早い応答速度を持つと同時に低い消費電力で駆動されるという長所がある。

#### 【0004】

一般的な有機発光表示装置は、画素ごとに形成されるトランジスタを利用してデータ信号に対応する電流を有機発光ダイオードに供給することで有機発光ダイオードから光が発生する。

#### 【0005】

このような従来の有機発光表示装置は、データ線にデータ信号を供給するためのデータ駆動部と、走査線に走査信号を順次に供給するための走査駆動部と、発光制御線に発光制御信号を供給するための発光制御駆動部と、データ線、走査線、及び発光制御線に接続される複数の画素を具備する画素部と、を具備する。

#### 【0006】

画素部に含まれた各画素は、走査線に走査信号が供給されたとき選択されてデータ線を介してデータ信号の供給を受ける。データ信号の供給を受けた画素は、データ信号に対応する所定輝度の光を生成しながら所定の映像を表示する。ここで、画素の発光時間は発光制御線を介して供給される発光制御信号によって制御される。

#### 【0007】

ここで、有機発光表示装置が大型パネルであるほど、サイズ、重さ、及び製造費用を低減するために走査駆動部または発光制御駆動部がパネルに実装されなければならない。

#### 【0008】

10

20

30

40

50

しかし、従来の走査駆動部または発光制御駆動部は、PMOSトランジスタ及びNMOSトランジスタで構成されるため、パネルに実装されにくかった。そして、従来の発光制御駆動部は、クロック信号の一周期以上ごとに出力信号を生成するために高速で駆動しにくい。また、PMOSトランジスタ及びNMOSトランジスタで構成された従来の走査駆動部または発光制御駆動部は出力信号を生成するとき所定の静電流(Static Current)が流れるので、消費電力が大きくなるという問題点がある。

【特許文献1】大韓民国特許出願公開第10-2005-0121357号明細書

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0009】

したがって、本発明は、能動駆動方式の電流書き込み型有機電界発光表示装置で、走査信号を提供する第1走査駆動部と、発光制御信号を提供する第2走査駆動部で構成された走査駆動回路において、トランジスタの閾値電圧を補償して輝度のバラつきを補償し、走査信号によって発光制御信号を生成して低電力を消費する前記第2走査駆動部を具備してスタティック電流(static current)が流れる経路を無くすることで、消費電力が小さい走査駆動回路とこれを利用した有機電界発光表示装置を提供することにその目的がある。

##### 【課題を解決するための手段】

##### 【0010】

前記目的を果たすために本発明の第1側面は、走査信号を生成する複数の走査信号生成手段から構成される第1走査駆動部と、発光制御信号を生成する複数の発光制御生成手段から構成される第2走査駆動部と、を含み、前記複数の走査信号生成手段は互いに直列に配列され、前記各走査信号生成手段は、入力信号または隣接する前記走査信号生成手段から生成される走査信号と、第1クロック信号および第2クロック信号と、の入力を受けて走査信号を生成し、前記複数の発光制御信号生成手段は互いに直列に配列され、前記各発光制御信号生成手段は、前記2つの走査信号生成手段から順次に生成される2個の走査信号と、第1クロック信号および/または第2クロック信号と、の入力を受けて一つの発光制御信号を生成することを特徴とする

また、本発明の第2側面は走査線、データ線、および発光信号線に接続されるように位置される複数の画素を含む画素部と、前記データ線にデータ信号を供給するデータ駆動回路と、走査信号を生成する複数の走査信号生成手段から構成される第1走査駆動部と、発光制御信号を生成する複数の発光制御生成手段から構成される第2走査駆動部と、を含む走査駆動回路と、を含み前記複数の走査信号生成手段は互いに直列に配列され、前記各走査信号生成手段は、入力信号または隣接する前記走査信号生成手段から生成される走査信号と、第1クロック信号および第2クロック信号と、の入力を受けて走査信号を生成し、前記複数の発光制御信号生成手段は互いに直列に配列され、前記各発光制御信号生成手段は、前記2つの走査信号生成手段から順次に生成される2個の走査信号と、第1クロック信号および/または第2クロック信号と、の入力を受けて一つの発光制御信号を生成することを特徴とする。

##### 【発明の効果】

##### 【0011】

このような本発明によれば、走査駆動回路においてトランジスタの閾値電圧を補償して輝度のバラつきを補償し、走査信号によって発光制御信号を生成して低電力を消費する第2走査駆動部を具備してスタティック電流が流れうる経路を無くすることで、消費電力を最小化することができるという長所がある。

##### 【発明を実施するための最良の形態】

##### 【0012】

以下、添付された図面を参照して本発明の実施形態をより詳しく説明する。

##### 【0013】

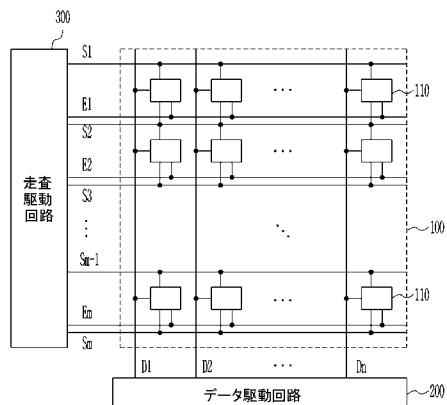

図1は、本発明の実施形態による有機電界発光表示装置を示す構成図である。

10

20

30

40

50

## 【0014】

図1を参照して説明すれば、本発明による有機電界発光表示装置は、画像を表現する画像表示部100、データ信号を伝達するデータ駆動回路200、走査信号及び発光制御信号を伝達する走査駆動回路300を含む。

## 【0015】

画像表示部100は、列方向に延びている複数のデータ線D1-Dn、行方向に延びている複数の信号線(S1-Sm、E1-Em)、及びマトリックス模様に形成された複数の画素回路110を含む。ここで、前記各信号線は、画素を選択するための走査信号を伝達する複数の走査信号線S1-Sm、及び有機EL素子の発光期間を制御するための発光制御信号を伝達する複数の発光制御信号線E1-Emを含む。

10

## 【0016】

走査駆動回路300は、前記走査信号を提供する第1走査駆動部と、前記発光制御信号を提供する第2走査駆動部とで構成される。そして、データ線D1-Dnと、走査制御信号線S1-Sm及び発光制御信号線E1-Emと、によって定義される画素領域にそれぞれ画素回路110が形成されている。

## 【0017】

データ駆動回路200は、データ線D1-Dnにデータ電流DATAを印加し、走査駆動回路300の第1走査駆動部は、走査信号線S1-Smに画素回路を選択するための走査信号を順次に印加する。また、走査駆動回路300の第2走査駆動部は、画素回路110の輝度を制御するための発光制御信号を発光制御信号線E1-Emに順次に印加する。

20

## 【0018】

本発明の場合、走査駆動回路300が走査信号を生成する第1走査駆動部及び前記走査信号の入力を受けて発光制御信号を生成する第2走査駆動部を含んで構成されることを特徴とし、前記第2走査駆動部は複数の発光制御信号生成手段CCUを含み、各発光制御信号生成手段CCUは2個の走査信号及び1個または2個のクロック信号の入力を受けて一つの発光制御信号を出力する。

## 【0019】

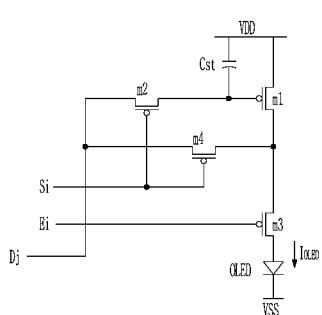

図2は、図1に示された有機電界発光表示装置の各画素領域に具備される画素回路110の一実施形態を示す回路図である。

30

## 【0020】

ただし、図2では説明の便宜上j番目データ線Djとi番目信号線Si、Eiに連結された画素回路のみを示した。

## 【0021】

図2に示されたように、本発明の一実施形態による画素回路110は、有機EL素子OLED、トランジスタm1-m4、及びキャパシタCstを含む。ここで、本実施形態では、トランジスタm1-m4にはPMOSトランジスタが使用されたが、これに限定されない。

## 【0022】

第1トランジスタm1は、電源VDDと有機EL素子OLEDとの間に接続されて、有機EL素子OLEDに流れる電流を制御する。具体的には、トランジスタm1のソースは電源VDDに接続されて、ドレインはトランジスタm3を通じて有機EL素子OLEDのカソードに接続される。

40

## 【0023】

また、第2トランジスタm2は、走査信号線Siからの走査信号に応答してデータ線Djからのデータ信号を第1トランジスタm1のゲートに伝達して、第4トランジスタm4は走査信号に応答して第1トランジスタm1をダイオード連結させる。

## 【0024】

また、キャパシタCstは、第1トランジスタm1のゲート及びソースの間に接続されて、データ線Djからのデータ電流DATAにあたる電圧を充電して、第3トランジス

50

タ m 3 は発光制御信号線 E i からの発光制御信号に応答して第 1 パソコン m 1 に流れる電流を有機 EL 素子 O L E D に伝達する。

【 0 0 2 5 】

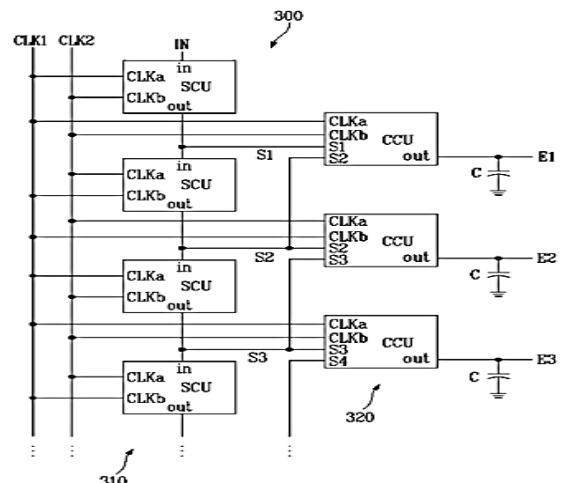

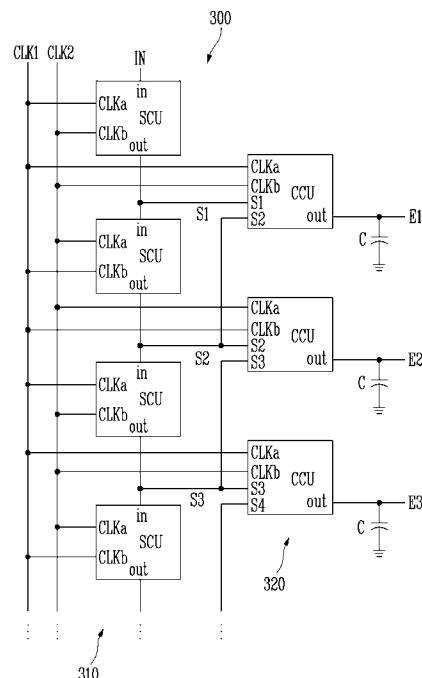

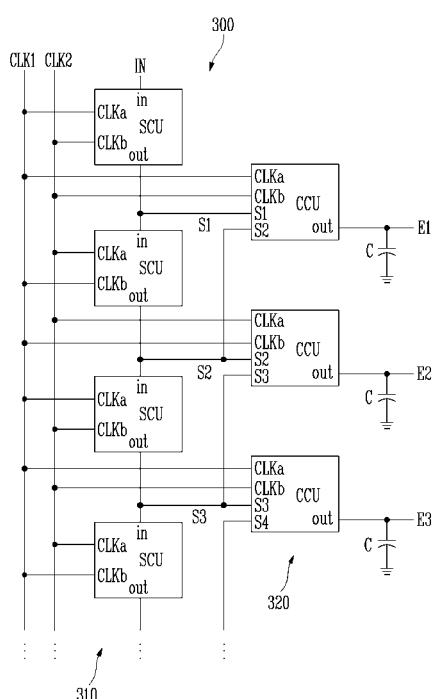

図 3 は、本発明の実施形態による走査駆動回路 3 0 0 の構成を示すブロック図である。

【 0 0 2 6 】

図 3 を参照すれば、走査駆動回路 3 0 0 は走査信号を出力する第 1 走査駆動部 3 1 0 と前記走査信号の入力を受けて発光制御信号を出力する第 2 走査駆動部 3 2 0 とを含む。

【 0 0 2 7 】

第 1 走査駆動部 3 1 0 は、画素回路に供給する走査信号を生成する複数の走査信号生成手段 S C U を含み、複数の走査信号生成手段は互いに直列に配列され、一番目の走査信号生成手段 S C U には最初に入力信号 I N が供給されて二番目以降の走査信号生成手段 S C U の出力信号は、それぞれ後段の走査信号生成手段 S C U に入力信号として供給される。10

【 0 0 2 8 】

また、前記各走査信号生成手段 S C U は、第 1 クロック信号 C L K 1 及び第 2 クロック信号 C L K 2 がそれぞれ供給される第 1 クロック端子 C L K a および第 2 クロック端子 C L K b を具備する。第 1 クロック信号 C L K 1 と第 2 クロック信号 C L K 2 とは位相が 1 / 2 周期異なり、互いにハイレベルになる期間が存在する。望ましくは、第 1 クロック信号 C L K 1 と第 2 クロック信号 C L K 2 とは位相が 1 / 2 周期異なる。また、奇数番目走査信号生成手段（第 1 走査信号生成手段）の第 1 クロック端子 C L K a には第 1 クロック信号 C L K 1 が供給されて、第 2 クロック端子 C L K b には第 2 クロック信号 C L K 2 が供給される。20

【 0 0 2 9 】

これとは反対に、偶数番目走査信号生成手段（第 2 走査信号生成手段）の第 1 クロック端子 C L K a には第 2 クロック信号 C L K 2 が供給されて、第 2 クロック端子 C L K b には第 1 クロック信号 C L K 1 が供給される。

【 0 0 3 0 】

すなわち、最初に入力信号 I N または前段の走査信号生成手段の出力電圧と、第 1 クロック信号 C L K 1 及び第 2 クロック信号 C L K 2との供給を受けた各走査信号生成手段は各走査信号生成手段の出力ラインを通じて順次ローレベルの信号を出力する。30

【 0 0 3 1 】

一方、第 2 走査駆動部 3 2 0 は、画素回路に供給する発光制御信号を生成する複数の発光制御信号生成手段 C C U を含み、各発光制御信号生成手段 C C U は第 1 走査駆動部 3 1 0 から順次に出力される 2 個の走査信号及び前記第 1 クロック信号 C L K 1 及び / または第 2 クロック信号 C L K 2 の入力を受けて一つの発光制御信号を生成する。40

【 0 0 3 2 】

このとき、各発光制御信号生成手段 C C U は、位相が異なる第 1 クロック信号 C L K 1 及び / または第 2 クロック信号 C L K 2 がそれぞれ供給される第 1 クロック端子 C L K a および第 2 クロック端子 C L K b を具備する。また、奇数番目発光制御信号生成手段の第 1 クロック端子 C L K a には第 1 クロック信号 C L K 1 が供給されて、第 2 クロック端子 C L K b には第 2 クロック信号 C L K 2 が供給される。

【 0 0 3 3 】

これとは反対に、偶数番目発光制御信号生成手段の第 1 クロック端子 C L K a には第 2 クロック信号 C L K 2 が供給されて、第 2 クロック端子 C L K b には第 1 クロック信号 C L K 1 が供給される。

【 0 0 3 4 】

一例で、第 2 走査駆動部 3 2 0 の第 1 発光制御信号生成手段 C C U は、第 1 及び第 2 クロック信号と、第 1 走査駆動部 3 1 0 の一番目及び二番目の走査信号生成手段 S C U から出力される走査信号 S 1 , S 2 と、が入力される。

【 0 0 3 5 】

ただし、第 1 クロック信号、第 2 クロック信号は、第 2 走査駆動部 3 2 0 の各発光制御

10

20

30

40

50

信号生成手段にそれぞれ入力されうるだけでなく、少なくとも一つ以上入力されればよい。

**【0036】**

また、第2走査駆動部320の各発光制御信号生成手段CCUからの出力ラインには、図示されたように所定のキャパシタCが具備されることが好ましい。

**【0037】**

そして、第1走査駆動部310から出力される走査信号は、別途のラインを通じて第2走査駆動部320を経ることなく画像表示部100に入力されるように構成することもできる。

**【0038】**

すなわち、本発明による走査駆動回路300は、第2走査駆動部320の出力のみを画像表示部100に提供して発光制御信号を提供するように構成されるだけでなく、第1走査駆動部310から出力される走査信号を別途のラインを通じて画像表示部100に入力されるように構成して走査信号及び発光制御信号を同時に提供することができる。

**【0039】**

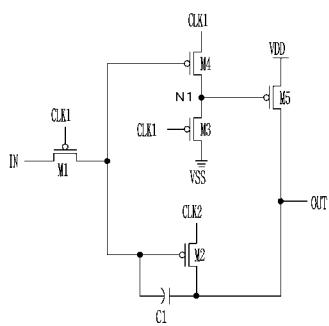

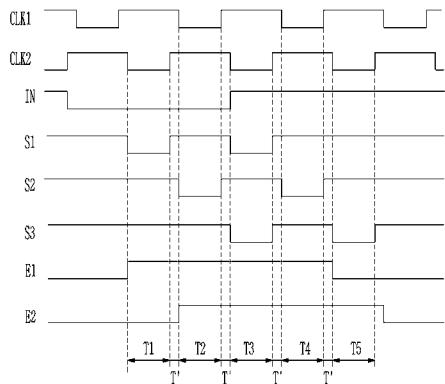

図4は、図3に示された第1走査駆動部310の任意の走査信号生成手段SCUに対する回路図で、一例として一番目走査信号生成手段の回路構成を示し、図5は本発明の実施形態による走査駆動部の入出力信号波形に対するタイミング図である。

**【0040】**

図4及び図5を参照すれば、第1走査駆動部310を構成する走査信号生成手段SCUは、位相が異なる第1クロック信号CLK1および第2クロック信号CLK2が入力され、クロック信号が互いに出力信号のレベルが異なる第1期間の間には、入力信号としての前段の走査信号生成手段の出力電圧または入力信号INを保存するプリチャージ(pre-charge)を遂行し、前記第1期間と反転された位相を持つ第2期間の間に評価を遂行する。結果的に第1走査駆動部310は、一定のパルス(たとえば、ローレベルのパルス)を、前記第1クロック信号CLK1および第2クロック信号CLK2のレベルが同一(たとえば、ハイレベル)となる時間間隔において、順次に出力する。

**【0041】**

すなわち、走査信号生成手段SCUは、前記プリチャージを遂行するプリチャージ期間(第1期間)ではハイレベルの信号を出力して、評価を遂行する評価期間(第2期間)には前記プリチャージ期間に受けた入力にあたる信号を出力する。

**【0042】**

ただし、前記第1走査駆動部を構成する走査信号生成手段の場合、奇数番目走査信号生成手段の評価期間(プリチャージ)期間を偶数番目走査信号生成手段のプリチャージ期間(評価期間)と同じようにする。

**【0043】**

以下、図4に示された第1走査駆動部の第1走査信号生成手段の回路構成を通じてより具体的に走査信号生成手段の動作を説明する。

**【0044】**

ただし、以下では、走査信号生成手段に具備されるトランジスタはPMOS薄膜トランジスタをその例として説明しているが、本発明の実施形態が必ずしもこれに限定されるものではない。

**【0045】**

図4を参照すれば、本発明による第1走査駆動部の奇数番目走査信号生成手段としての一番目走査信号生成手段は、最初に入力信号INの入力を受けて、第1クロック端子にゲート端子が接続された第1PMOSトランジスタM1と、第1PMOSトランジスタM1の出力端にゲート端子が接続されて、第2クロック端子及び出力ラインOUTに接続された第2PMOSトランジスタM2と、前記第1クロック端子にゲート端子が接続されて、第2電源VSS及び第1ノードN1の間に接続された第3PMOSトランジスタM3と、第1PMOSトランジスタM1の出力端にゲート端子が接続されて、第1クロック端子及

び第1ノードの間N1に接続された第4POMSトランジスタM4と、第1ノードN1にゲート端子が接続されて、第1電源VDD及び前記出力ラインOUTの間に接続された第5PMOSトランジスタM5と、が含まれて構成される。

#### 【0046】

また、第1PMOSトランジスタM1の出力端及び出力ラインOUTの間に接続された第1キャパシタC1がさらに含まれて構成される。

#### 【0047】

ここで、図4に示された走査信号生成手段が第1走査駆動部の奇数番目走査信号生成手段の場合には前記第1クロック端子に第1クロック信号CLK1が供給されて、前記第2クロック端子に第2クロック信号CLK2が供給される。

10

#### 【0048】

これとは反対に、図4に示された走査信号生成手段が偶数番目の場合には前記第1クロック端子には第2クロック信号CLK2が供給されて、第2クロック端子には第1クロック信号CLK1が供給される。

#### 【0049】

また、第2電源VSSには別途の負の電源が印加されうるが、図4に示されたように接地GNDされて構成することも可能である。本発明の実施形態では、第2電源VSSは、接地して具現している。

#### 【0050】

このような各走査信号生成手段は、大きく伝達部、反転部、およびバッファー部を含み、前記伝達部は第1PMOSトランジスタM1、第2POMSトランジスタM2、及び第1キャパシタC1で構成されて、前記反転部は第1PMOSトランジスタM1、第3PMOSトランジスタM3、および第4PMOSトランジスタM4で構成されて、前記バッファー部は第5PMOSトランジスタM5で構成される。

20

#### 【0051】

このとき、第1クロック信号CLK1がローレベル、および第2クロック信号CLK2がハイレベルである期間がプリチャージ期間となって、第1クロック信号CLK1がハイレベル、および第2クロック信号CLK2がローレベルである期間が評価期間になる。

#### 【0052】

前記プリチャージ期間ではハイレベルの出力を出し、評価期間には前記プリチャージ期間に受けた入力に応じた信号を出力する。

30

#### 【0053】

ただし、本発明の実施形態の場合、各走査信号生成手段に入力される信号としての第1、第2クロック信号が、図5に示すように、それぞれハイレベルで所定部分オーバーラップされて提供される。

#### 【0054】

これは、前記各走査信号生成手段に入力される一対のクロック信号CLK1、CLK2が互いにハイレベルでオーバーラップされた時間間隔を置いて順次にローレベルの信号を出力するようにし、このように各走査信号生成手段の出力信号間に所定の時間間隔をおくようにするのは、クロック・スキュー(clock skew)または遅延に対するマージンを確保するためである。

40

#### 【0055】

図4及び図5を参照して、第1走査駆動部の奇数番目走査信号生成手段に対する回路の動作をみれば、まず、プリチャージ期間、すなわち、第1クロック信号CLK1がローレベル、および第2クロック信号CLK2がハイレベルに入力される間にはPMOSトランジスタM1、M3がオン(ON)になって、入力信号INまたは前段の走査信号生成手段の出力電圧がそれぞれPMOSトランジスタM2、M4のゲート端子に伝達する。

#### 【0056】

したがって、前記プリチャージ期間には、第1キャパシタC1に入力信号としての前段の走査信号生成手段の出力電圧または入力信号INが保存されて、第1ノードN1には第

50

2 クロック信号 C L K 2 または第 2 電源 V S S によってローレベルの信号が充電されるので、M 5 がオンされてハイレベルの第 1 電源 V D D が出力端 O U T を通じて出力される。すなわち、前記プリチャージ期間で前記走査信号生成手段のバッファー部の出力はハイレベルになる。

#### 【 0 0 5 7 】

また、評価期間の間には M 1 がオフされて入力信号 I N または前走査信号生成手段の出力電圧が遮断され、P M O S トランジスタ M 3 , M 4 もオフされる。

#### 【 0 0 5 8 】

このとき、前記プリチャージ期間の間に入力を受けた信号、すなわち、前段の走査信号生成手段の出力電圧または入力信号 I N がハイレベルの場合には、前記プリチャージ期間の間にフリーチャージされた信号レベルが維持されるので、前記バッファー部は相変らずハイレベルを出力するようになる。

10

#### 【 0 0 5 9 】

一方、前記プリチャージ期間の間に入力を受けた信号、すなわち、前段の走査信号生成手段の出力電圧または入力信号 I N がローレベルの場合には、第 1 キャパシタ C 1 によって保存された前記ローレベル信号によって P M O S トランジスタ M 2 がオンになるが、前記伝達部では P M O S トランジスタ M 2 がオンになることによってローレベルの値を有する第 2 クロック信号 C L K 2 が出力端 O U T を通じて出力される。

20

#### 【 0 0 6 0 】

すなわち、前記評価期間において前記走査信号生成手段は、事前のプリチャージ期間に入力を受けた信号、すなわち、前段の走査信号生成手段の出力電圧または入力信号 I N がローレベルの場合にはローレベルを出力し、ハイレベルの場合にはハイレベルを出力する動作を遂行する。

20

#### 【 0 0 6 1 】

ただし、上述で説明したように、前記走査信号生成手段に入力される信号としての第 1 , 第 2 クロック信号は、図 5 で示されたようにハイレベルで所定間隔オーバーラップされて提供される。

30

#### 【 0 0 6 2 】

第 1 クロック信号 C L K 1 及び第 2 クロック信号 C L K 2 がハイレベルであるとき、その状態になる前がプリチャージ期間なら第 1 クロック信号 C L K 1 によって制御される P M O S トランジスタ M 1 , M 3 がすべてオフになって、C 1 の電圧がそのまま維持されるので事前の状態の出力を維持する。

30

#### 【 0 0 6 3 】

一方、その状態になる前が評価期間なら P M O S トランジスタ M 1 , M 3 がオフになっており、P M O S トランジスタ M 2 は前の状態を維持するが、P M O S トランジスタ M 2 がオフされていればハイレベルの入力を受けたことになるので、結果的に M 5 によってハイレベル出力が維持される。

40

#### 【 0 0 6 4 】

逆に、P M O S トランジスタ M 3 がオンになっていればローレベルの入力を受けたことになるので、M 2 のゲート端子がフローティングされているから C 1 の電圧がそのまま維持され、それによって P M O S トランジスタ M 2 は引き続きオン状態を維持し、出力がハイレベルである第 2 クロック信号が出力されることで結果的にハイレベルが出力される。

40

#### 【 0 0 6 5 】

このように第 1 クロック信号 C L K 1 、第 2 クロック信号 C L K 2 がハイレベルであるとき、前の状態がプリチャージ期間なら前の状態の出力を維持し、評価期間なら出力がハイレベルになるので、第 1 クロック信号 C L K 1 、第 2 クロック信号 C L K 2 のハイレベルがオーバーラップされた間隔ほど、隣接した走査信号生成手段との出力パルスの間に時間間隔を与えることができる。

#### 【 0 0 6 6 】

ただし、図 5 に示されたように第 1 走査駆動部の第 1 の走査信号生成手段に入力される

50

入力信号INが、最初2回のフリーチャージが遂行される期間を含んで印加されるから、これによって前記走査信号生成手段SCUでは、示されたようにそれぞれの走査線または第2走査駆動部の各発光制御信号生成手段CCUに連続的な2回のローレベル走査信号を提供する。

【0067】

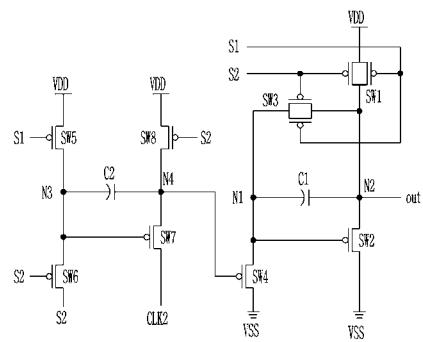

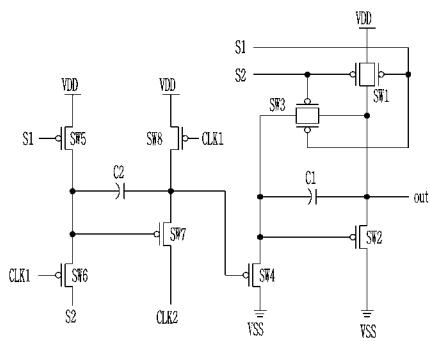

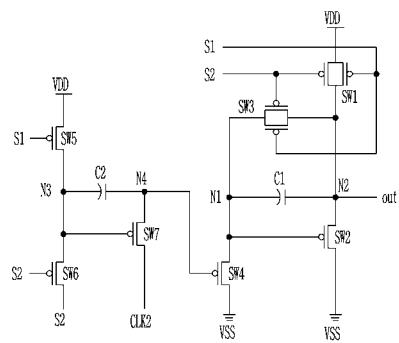

図6は図3に示された第2走査駆動部の第1実施形態による任意発光制御信号生成手段CCUの回路図である。

【0068】

ただし、図6は一例として第2走査駆動部の第1発光制御信号生成手段の回路構成を示しており、前記第2走査駆動部の第1発光制御信号生成手段CCUは、第1クロック信号及び／または第2クロック信号と第1走査駆動部の第1，第2走査信号生成手段から出力される走査信号S1，S2が入力される。

10

【0069】

図5及び図6を参照すれば、前記第2走査駆動部を構成する発光制御信号生成手段CCUは、第1電源VDDと出力端N2との間に接続された第1スイッチング素子SW1と、出力端N2と第2電源VSSとの間に接続された第2スイッチング素子SW2と、第1電極が出力端N2に接続されて、第2電極が第2スイッチング素子SW2のゲート電極に連結された第1ノードN1に接続された第1キャパシタC1と、第1ノードN1と出力端N2及び第1スイッチング素子SW1のゲート電極に接続された第3スイッチング素子SW3と、第1ノードN1と第2電源VSSとの間に接続されてゲート電極がコンバージョン部の出力端に接続された第4スイッチング素子SW4と、を具備する。ここで、第1電源VDDの電圧レベルは、第2電源VSSの電圧レベルより高い。

20

【0070】

また、第1スイッチング素子SW1ないし第4スイッチング素子SW4は、PMOSトランジスタである。また、第1スイッチング素子SW1及び第3スイッチング素子SW3はそれ二つのトランジスタが結合されて具現されているトランスマッシュゲート構造を持つトランジスタに具現されて、それぞれ一つのソースと一つのドレインと二つの第1ゲートおよび第2ゲートを具備する。そして、第2スイッチング素子SW2及び第4スイッチング素子SW4は、一つのトランジスタで具現される。

30

【0071】

第1スイッチング素子SW1のソースは、第1電源VDDに接続されて、ドレインは出力端N2に接続される。第1スイッチング素子SW1の第1ゲート電極には前記第1走査駆動部から出力される第1走査信号S1が伝達され、第2ゲート電極には前記第1走査駆動部から第2走査信号S2が伝達される。このような、第1スイッチング素子SW1は、第1走査信号S1または第2走査信号S2によって第1電圧を出力端N2に供給する第1パスを形成する。

40

【0072】

第2スイッチング素子SW2のゲートは、第1ノードN1に接続されて、ソースは出力端N2に接続されてドレインは第2電源VSSに接続される。このような、第2スイッチング素子SW2は、第1ノードN1、すなわちゲートの電圧によって第2電源VSSを出力端N2に供給する第2パスを形成する。このとき、第1電源VDDの電圧レベルは第2電源VSSの電圧レベルより高い。

40

【0073】

第3スイッチング素子SW3のソースは出力端N2に接続されて、ドレインは第1ノードN1に接続されて第3スイッチング素子SW3の第1ゲートには第1走査信号S1が伝達されて、第2ゲートには第2走査信号S2が伝達される。このような、第3スイッチング素子SW3は、第1走査信号S1または第2走査信号S2によって第1スイッチング素子SW1を経由して供給される第1電源VDDを第1ノードN1に供給する。

【0074】

これによって、第3スイッチング素子SW3はローレベルの第1走査信号S1または第

50

2走査信号S2によってオン状態になって第2スイッチング素子SW2のゲートソース間の電圧を等しくして第2スイッチング素子SW2を通じて形成される第2パスを遮断する役目をする。

【0075】

第4スイッチング素子SW4のソースは、第1ノードN1に接続されて、ドレインは第2電源VSSに接続されて、ゲートにはコンバージョン部の出力端N4に接続される。

【0076】

ここで、前記コンバージョン部は、第1電源VDDと第3ノードN3との間に接続された第5スイッチング素子SW5と、第3ノードN3と第1入力端子との間に接続された第6スイッチング素子SW6と、コンバージョン部出力端N4と第2入力端子との間に接続されて、ゲート電極が第3ノードN3に接続された第7スイッチング素子SW7と、第1電源VDDとコンバージョン部出力端N4との間に接続された第8スイッチング素子SW8と、第3ノードN3とコンバージョン部出力端N4との間に接続された第2キャパシタC2と、が含まれて構成される。

【0077】

ここで、第5スイッチング素子SW5のゲート電極は、第1走査信号S1の入力ラインに接続されて、第6スイッチング素子SW6及び第8スイッチング素子SW8のゲート電極は、第2走査信号S2の入力ラインに接続される。また、前記第1入力端子には第2走査信号S2が入力されて、第2入力端子には第2クロック信号CLK2が入力される。

【0078】

すなわち、第4スイッチング素子SW4は前記コンバージョン部の出力信号にオン・オフが制御される。

【0079】

また、第1キャパシタC1は、出力端N2に接続される第1電極と第1ノードN1に接続される第2電極を持つ。このような、第1キャパシタC1は第4スイッチング素子SW4のスイッチング動作によって第2スイッチング素子SW2のゲートソース間の電圧を保存した後、第2スイッチング素子SW2のゲートソース間の電圧によって第2スイッチング素子SW2をスイッチングさせる役目を果たす。このような、第1キャパシタC1は第4スイッチング素子SW4のスイッチング動作によって第2スイッチング素子SW2のオン状態を維持させて、第2バスが持続的に維持されるようにする。

【0080】

図5及び図6を参照して前記第2走査駆動部の第1発光制御信号生成手段の動作を説明する。

【0081】

第1走査信号S1がローレベルに入力されて、第2走査信号S2がハイレベルに入力される第1区間T1及び第3区間T3と、第1走査信号S1ハイレベルに入力されて、第2走査信号S2がローレベルに入力される第2区間T2及び第4区間T4では、第1スイッチング素子SW1および第3スイッチング素子SW3はオン状態になって、コンバージョン部の出力が前記区間でハイレベルなので第4スイッチング素子SW4はオフ状態になる。

【0082】

したがって、第1電源VDDが第1スイッチング素子SW1を通じて出力端に伝達されて第1スイッチング素子SW1および第3スイッチング素子SW3を通じて第1ノードN1に伝達される。したがって、第1区間T1及び第3区間T3と、第2区間及び第4区間T4から出力端N2には第1電源VDDの電圧レベルが出力される。

【0083】

また、第3スイッチング素子SW3によって第2スイッチング素子SW2にソースとゲートにそれぞれ第1電源VDDが伝達されて第2スイッチング素子SW2のゲートソース間の電圧差はゼロになって、第2スイッチング素子SW2のソースとドレインとの間のパスが遮られ、出力端N2および第2スイッチング素子SW2を通じて第2電源VSSに静

10

20

30

40

50

電流 ( S t a t i c C u r r e n t ) が流れなくなる。

【 0 0 8 4 】

したがって、出力端 N 2 で第 1 電源 V D D の電圧レベルを出力するうちに第 3 スイッチング素子 S W 3 を利用して第 2 スイッチング素子 S W 2 のゲートソース間の電圧レベルの差をゼロにして静電流バスを遮断することで消費電力を減少させる。

【 0 0 8 5 】

また、第 1 走査信号 S 1 及び第 2 走査信号 S 2 がハイレベルに重畠されて印加される区間 T' では、コンバージョン部の出力はハイレベルに維持されるので、結果的に第 1 スイッチング素子 S W 1 及び第 3 スイッチング素子 S W 3 と第 4 スイッチング素子 S W 4 はすべてオフ状態になって前の区間の出力が維持されるので、出力端 N 2 には第 1 電源 V D D の電圧レベルが出力される。 10

【 0 0 8 6 】

引き続いて、第 1 走査信号 S 1 及び第 2 走査信号 S 2 がハイレベルに印加されて、第 2 クロック信号 C L K 2 がローレベルに印加される第 5 区間 T 5 では、コンバージョン部の出力がローレベルなので第 1 スイッチング素子 S W 1 及び第 3 スイッチング素子 S W 3 はオフ状態になって第 4 スイッチング素子 S W 4 はオン状態になる。

【 0 0 8 7 】

第 4 スイッチング素子 S W 4 がオン状態になるとによって、第 1 ノード N 1 の電圧が降下し、第 1 キャパシタ C の第 2 端子と第 1 端子との間、即ち、第 2 スイッチング素子 S W 2 のソースとゲートとの間には第 2 スイッチング素子 S W 2 の閾値電圧の絶対値 ( | V<sub>t h</sub> | ) 以上の電圧が印加される。このように動作して、第 2 スイッチング素子 S W 2 はオン状態になる。 20

【 0 0 8 8 】

その後、第 1 ノード N 1 の電圧が引き続き降下して第 4 スイッチング素子 S W 4 のソースとゲートとの間の電圧が第 4 スイッチング素子 S W 4 の閾値電圧の絶対値以下になれば、第 4 スイッチング素子 S W 4 はオフ状態になる。

【 0 0 8 9 】

第 4 スイッチング素子 S W 4 がオフ状態になれば、キャパシタ C の第 1 端子は、フローティング ( f l o a t i n g ) 状態になって第 1 キャパシタ C 1 に保存された電圧は一定に維持される。 30

【 0 0 9 0 】

したがって、第 1 キャパシタ C 1 の第 2 端子と第 1 端子との間に保存された電圧は、第 2 スイッチング素子 S W 2 の閾値電圧の絶対値 ( | V<sub>t h</sub> | ) 以上の電圧を維持するようになるので、出力端 N 2 の電圧が第 2 電源 V S S の電圧レベルに到達するように第 2 スイッチング素子 S W 2 がオン状態を維持するようにしてプルダウン ( P u l l - D o w n ) になるようとする。

【 0 0 9 1 】

すなわち、本発明の実施形態による第 2 走査駆動回路の発光制御信号生成手段は、第 3 スイッチング素子 S W 3 を利用して第 1 電源 V D D の電圧レベルを出力する間に第 2 スイッチング素子 S W 2 の静電流バスを遮断して電流損失を減少させると同時に、第 1 キャパシタ C 1 を利用して第 2 スイッチング素子 S W 2 のオン状態を維持させてプルダウンされる第 2 電源 V S S の電圧レベルを出力するようになる。 40

【 0 0 9 2 】

結果的に、これはフルスイング ( F u l l S w i n g ) される第 1 電源の電圧レベルと第 2 電源の電圧レベルの出力が可能と同時に PMOS ランジスタの静電流による電流損失を減らして消費電力が減少される。

【 0 0 9 3 】

また、これを通じて出力される発光制御信号は、第 1 電源の電圧レベルと第 2 電源の電圧レベルとの間をフルスイングするようになって画像表示部 100 から発光制御信号の入力を受けて正確な動作ができるようになる。 50

## 【0094】

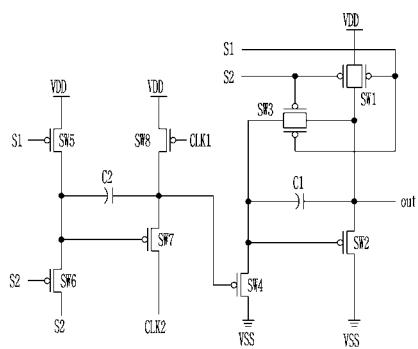

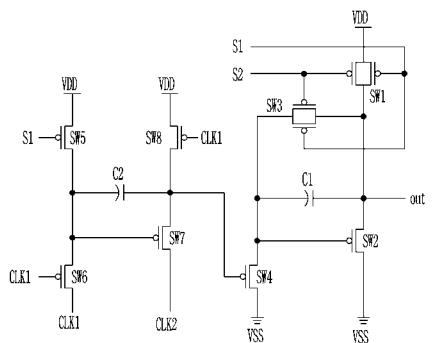

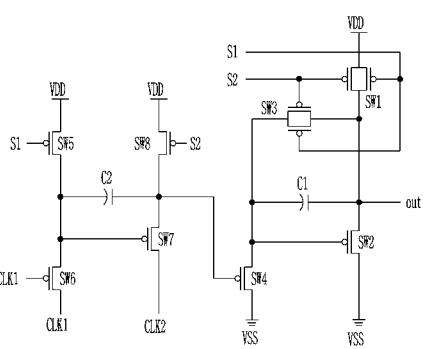

図7Aないし図7Eは、図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。

## 【0095】

ただし、これは図6を通じて説明した発光制御信号生成手段と同じ構成に対しては同じ図面符号を使用し、具体的な構成及び動作の説明は前述と同様であるから略する。

## 【0096】

図7A～図7Eに示された各実施形態はまず、図6に示された第2走査駆動部の発光制御信号生成手段回路構成の中でコンバージョン部に入力される信号が異なる点以外にはその動作及び構成は同じである。

10

## 【0097】

すなわち、前記コンバージョン部は第1電源VDDと第3ノードN3との間に接続された第5スイッチング素子SW5と、第3ノードN3と第1入力端子との間に接続された第6スイッチング素子SW6と、コンバージョン部出力端N4と第2入力端子との間に接続されて、ゲート電極が第3ノードN3に接続された第7スイッチング素子SW7と、第1電源VDDとコンバージョン部出力端N4との間に接続された第8スイッチング素子SW8と、第3ノードN3とコンバージョン部出力端N4との間に接続された第2キャパシタC2が含まれて構成される。

## 【0098】

図7Aの場合、第6スイッチング素子SW6及び第8スイッチング素子SW8のゲート電極が第2走査信号S2入力ラインではない第1クロック信号CLK1入力ラインに接続される。

20

## 【0099】

また、図7Bの場合、第6スイッチング素子SW6のゲート電極は第2走査信号S2入力ラインに接続されて第8スイッチング素子SW8のゲート電極は第1クロック信号CLK1入力ラインに接続される。

## 【0100】

また、図7Cの場合、第6スイッチング素子SW6及び第8スイッチング素子SW8のゲート電極が第1クロック信号CLK1入力ラインに接続されて、第1入力端子に第2走査信号S2ではない第1クロック信号CLK1が入力される。

30

## 【0101】

また、図7Dの場合、第6スイッチング素子SW6のゲート電極は第1クロック信号CLK1の入力ラインに接続されて、第8スイッチング素子SW8のゲート電極は第2走査信号S2の入力ラインに接続されて、第1入力端子には第1クロック信号CLK1が入力される。

## 【0102】

また、図7Eの場合のように第8スイッチング素子SW8が除去されて構成されうるし、このとき第6スイッチング素子のゲート電極、第1入力端子、および第2入力端子に入力される信号は、前述のように多様な信号が入力されうる。

40

## 【0103】

以上添付した図面を参照して本発明について詳細に説明したが、これは例示的なものに過ぎず、当該技術分野における通常の知識を有する者であれば、多様な変形及び均等な他の実施形態が可能であるということを理解することができる。

## 【図面の簡単な説明】

## 【0104】

【図1】本発明の実施形態による有機電界発光表示装置を示す構成図である。

【図2】図1に示された有機電界発光表示装置の各画素領域に具備される画素回路の一実施形態を示す回路図である。

## 【図3】本発明の実施形態による走査駆動回路の構成を示すプロック図である。

【図4】図3に示された第1走査駆動部の任意走査信号生成手段SCUに対する回路図で

50

ある。

【図5】本発明の実施形態による走査駆動部の入出力信号波形に対するタイミング図である。

【図6】図3に示された第2走査駆動部の第1実施形態による任意発光制御信号生成手段CCUの回路図である。

【図7A】図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。

【図7B】図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。

【図7C】図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。 10

【図7D】図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。

【図7E】図3に示された第2走査駆動部の第2ないし第6実施形態による任意発光制御信号生成手段CCUの回路図である。 20

#### 【符号の説明】

##### 【0 1 0 5】

- 1 0 0 画像表示部、

- 1 1 0 画素回路、

- 2 0 0 データ駆動回路、

- 3 0 0 走査駆動回路、

- 3 1 0 第1走査駆動部、

- 3 2 0 第2走査駆動部。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 2 2 E |

| G 0 9 G | 3/20  | 6 2 2 D |

| H 0 5 B | 33/14 | A       |

| H 0 5 B | 33/08 |         |

(74)代理人 100134348

弁理士 長谷川 俊弘

(72)発明者 申 東 蓉

大韓民国ソウル特別市冠岳区奉天1洞969-37

F ターム(参考) 3K107 AA01 BB01 CC14 CC33 EE03 HH00 HH04 HH05

5C080 AA06 BB05 DD05 DD26 EE28 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 扫描驱动电路和使用其的有机电致发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2007279667A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2007-10-25 |

| 申请号            | JP2006277770                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2006-10-11 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 申東蓉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 申 東 蓉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/325 G09G3/20 G09G3/3266 G09G2300/0842 G09G2310/0286 G09G2330/021 G11C19/184                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.A G09G3/20.642.A G09G3/20.622.Q G09G3/20.622.G G09G3/20.624.B<br>G09G3/20.622.E G09G3/20.622.D H05B33/14.A H05B33/08 G09G3/325 G09G3/3266 G09G3/3275<br>G09G3/3283 G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC14 3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH04 3K107/<br>/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD26 5C080/EE28 5C080/FF11 5C080/JJ02<br>5C080/JJ03 5C080/JJ04 5B074/AA10 5B074/CA01 5C380/AA01 5C380/AB06 5C380/BA01 5C380/<br>/BA02 5C380/BA34 5C380/CA08 5C380/CA13 5C380/CB01 5C380/CB11 5C380/CB14 5C380/CB18<br>5C380/CB31 5C380/CB33 5C380/CC13 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC52 5C380/<br>/CC61 5C380/CC63 5C380/CD014 5C380/CF07 5C380/CF22 5C380/CF43 5C380/DA02 5C380/DA06 |         |            |

| 代理人(译)         | 宇谷 胜幸<br>藤田 健                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 优先权            | 1020060031636 2006-04-06 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | <a href="#">JP4533365B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

提供一种用于电流写入型有机电致发光器件的扫描驱动电路。包括用于产生扫描信号的多个扫描信号产生单元SCU的第一扫描驱动器310和包括用于产生发光控制信号的多个发光控制发生器CCU的第二扫描驱动器320，其中所述多个扫描信号发生装置SCU与彼此串联布置，扫描信号发生装置SCU的输入信号或从相邻的扫描信号发生装置SCU中，第一时钟信号产生的扫描信号CLK1和第二时钟信号CLK2，该输入接收产生扫描信号，多个发光控制信号发生装置，CCU被彼此串联布置，每个发光控制信号生成单元CCU包括两个扫描信号发生装置并且，从SCU和第一时钟信号CLK1和/或第二时钟信号CLK2顺序产生两个扫描信号，并产生一个发光控制信号。点域