(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-202209

(P2005-202209A)

(43) 公開日 平成17年7月28日(2005.7.28)

(51) Int.Cl. 7

G09G 3/30

G09G 3/20

H05B 33/14

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611H

5C080

G09G 3/20

622B

G09G 3/20

623B

G09G 3/20

624B

審査請求 有 請求項の数 12 O L (全 33 頁) 最終頁に続く

(21) 出願番号

特願2004-9146 (P2004-9146)

(22) 出願日

平成16年1月16日 (2004.1.16)

(71) 出願人 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100090033

弁理士 荒船 博司

(74) 代理人 100093045

弁理士 荒船 良男

(72) 発明者 白寄 友之

東京都八王子市石川町2951番地5 カ

シオ計算機株式会社八王子研究所内

(72) 発明者 佐藤 和仁

東京都八王子市石川町2951番地5 カ

シオ計算機株式会社八王子研究所内F ターム(参考) 3K007 AB17 BA06 DB03 GA00

5C080 AA06 BB05 DD05 EE29 FF11

JJ02 JJ03 JJ04 JJ05 JJ06

(54) 【発明の名称】表示装置、データ側駆動回路及び表示パネルの駆動方法

## (57) 【要約】

【課題】 高品質な表示を行うことができる表示装置、データ側駆動回路及び表示パネルの駆動方法を提供すること。

【解決手段】 データ側駆動回路7、選択走査ドライバ5及び電源走査ドライバ6によって駆動される有機エレクトロルミネッセンス表示パネル2においては、画素 $P_{i,j}$ がマトリクス状に配列されており、画素 $P_{i,j}$ が有機EL素子 $E_{i,j}$ と画素回路 $D_{i,j}$ とを備える。画素回路 $D_{i,j}$ は選択走査ドライバ5によって選択されると、信号線 $Y_j$ にリセット電圧 $V_R$ が印加される。その後、画素回路 $D_{i,j}$ が選択された状態で、画素回路 $D_{i,j}$ は、信号線 $Y_j$ に流れる階調指定電流の大きさに従ったレベルの電圧をトランジスタ23に保持する。画素回路 $D_{i,j}$ の選択が解除されると、画素回路 $D_{i,j}$ はトランジスタ23の電圧レベルに従った大きさの駆動電流を有機EL素子 $E_{i,j}$ に流す。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、

前記複数の選択走査線を順次選択する選択走査ドライバと、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すデータ側駆動回路と、

前記複数の選択走査線及び前記複数の信号線にそれぞれ接続され、前記選択走査ドライバが前記選択走査線を選択することにより、前記信号線に流れる指定電流の大きさを記憶し、前記記憶した指定電流に従った大きさの駆動電流を前記複数の発光素子にそれぞれ流す複数の画素回路と、を備えることを特徴とする表示装置。10

## 【請求項 2】

前記データ側駆動回路は、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時の前半に前記複数の信号線に対してリセット電圧を印加した状態に切り換える切換部と、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前記切換部がリセット電圧を印加した後から、前記選択走査ドライバが前記複数の選択走査線各々の選択を解除するまでの間に、映像信号に従った大きさの指定電流を前記複数の信号線に流す信号ドライバと、を有することを特徴とする請求項 1 に記載の表示装置。20

## 【請求項 3】

前記複数の画素回路の各々は、

前記選択走査ドライバが前記選択走査線を選択している時に前記信号線に流れる指定電流を取り込んでその指定電流の大きさを電圧のレベルに変換して記憶し、

前記選択走査ドライバが前記選択走査線の選択を解除している時に前記信号線に流れる指定電流を遮断し、前記指定電流に応じて変換された電圧のレベルに従った駆動電流を前記発光素子に流すことを特徴とする請求項 1 又は 2 に記載の表示装置。

## 【請求項 4】

前記発光素子が有機エレクトロルミネッセンス素子であり、前記有機エレクトロルミネッセンス素子の一方の電極が前記画素回路に接続されていることを特徴とする請求項 1 から 3 の何れか一項に記載の表示装置。30

## 【請求項 5】

前記データ側駆動回路により印加するリセット電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧以下に設定されていることを特徴とする請求項 4 に記載の表示装置。

## 【請求項 6】

前記複数の選択走査線に対応して平行な複数の電源走査線が設けられ、

前記選択走査ドライバが前記複数の選択走査線を順次選択するのに同期して、前記複数の電源走査線を順次選択する電源走査ドライバが設けられ、40

前記複数の画素回路の各々は、

ゲートが前記選択走査線に接続され、ドレインとソースのうちの一方が前記信号線に接続された第一トランジスタと、

ゲートが前記選択走査線に接続され、ドレインとソースのうちの一方が前記電源走査線に接続された第二トランジスタと、

ゲートが前記第二トランジスタのドレインとソースのうちの他方に接続され、ドレインとソースとのうちの一方が前記電源走査線に接続され、ドレインとソースのうちの他方が前記第一トランジスタのドレインとソースのうちの他方に接続され、ドレインとソースとのうちの一方が前記有機エレクトロルミネッセンス素子の一方の電極に接続された第三トランジスタと、

前記第三トランジスタのゲート - ソース間の電圧を保持することによって記憶するキャ

50

パシタと、を有することを特徴とする請求項 4 又は 5 に記載の表示装置。

【請求項 7】

前記選択走査ドライバが前記選択走査線を選択して前記第一トランジスタをオンしている時に、前記第一トランジスタが前記電源走査線から前記第三トランジスタのドレイン-ソース間を介して前記信号線に指定電流を流すことによって、前記第三トランジスタが指定電流の大きさをゲート-ソース間電圧のレベルに変換して前記キャパシタが変換された電圧のレベルを記憶し、

前記選択走査ドライバが前記選択走査線の選択を解除して前記第一トランジスタをオフしている時に、前記第三トランジスタが、前記キャパシタによって記憶されたゲート-ソース間電圧のレベルに従った大きさの駆動電流を前記有機エレクトロルミネッセンス素子へ流すことを特徴とする請求項 6 に記載の表示装置。 10

【請求項 8】

前記電源走査ドライバが前記電源走査線を選択している時に前記電源走査線に印加する電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧以下に設定されており、前記電源走査ドライバが前記電源走査線の選択を解除した時に前記電源走査線に印加する電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧を越えるように設定されていることを特徴とする請求項 6 又は 7 に記載の表示装置。

【請求項 9】

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、 20

前記複数の選択走査線を順次選択する選択走査ドライバと、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すデータ側駆動回路と、

前記複数の選択走査線及び前記複数の信号線にそれぞれ接続され、前記選択走査ドライバが前記選択走査線を選択することにより、前記信号線と前記発光素子とを導通させる複数の画素回路と、を備えることを特徴とする表示装置。

【請求項 10】

複数の選択走査線と前記複数の信号線とにそれぞれ接続され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、前記複数の選択走査線を順次選択する選択走査ドライバと、前記複数の発光素子の各々に接続された複数の画素回路と、を備えるアクティブラマトリクス駆動方式の表示装置におけるデータ側駆動回路であって、 30

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すことを特徴とするデータ側駆動回路。

【請求項 11】

前記選択走査ドライバが前記複数の選択走査線を各々選択している時の前半に前記複数の信号線に対してリセット電圧を印加した状態に切り換える切換部と、 40

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前記切換部がリセット電圧を印加した後から、前記選択走査ドライバが前記複数の選択走査線各々の選択を解除するまでの間に、映像信号に従った大きさの指定電流を前記複数の信号線に流す信号ドライバと、を備えることを特徴とする請求項 10 に記載のデータ側駆動回路。

【請求項 12】

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、前記選択走査線及び前記信号線にそれぞれ接続した複数の画素回路と、を備える表示パネルを駆動する方法であって、

前記複数の選択走査線を順次選択し、

前記複数の選択走査線が各々選択されている時のうち前半に、リセット電圧を前記複数 50

の信号線に印加し、

前記複数の選択走査線が各々選択されている時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流し、

前記選択走査線が選択されることにより、前記信号線に流れる指定電流の大きさを記憶し、前記記憶した指定電流の大きさに従った大きさの駆動電流を前記画素回路によって前記発光素子に流すことを特徴とする表示パネルの駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光素子を画素ごとに備える表示パネルを駆動する表示パネルの駆動方法、前記表示パネルを駆動するためのデータ側駆動回路、及び、前記表示パネルと前記データ側駆動回路と選択走査ドライバとを備える表示装置に関する。 10

【背景技術】

【0002】

一般に、液晶ディスプレイにはアクティブマトリクス駆動方式のものと、単純マトリクス駆動方式のものがある。アクティブマトリクス駆動方式の液晶ディスプレイにおいては、単純マトリクス駆動方式の液晶ディスプレイに比較しても高コントラスト及び高精細な画面表示が行われる。アクティブマトリクス駆動方式の液晶ディスプレイにおいては、キャパシタとしても機能する液晶素子と、画素スイッチング素子として機能するトランジスタとが、画素ごとに設けられている。アクティブマトリクス駆動方式では、シフトレジスタである走査ドライバによって走査線が選択されている時に、輝度を表すレベルの電圧がデータドライバによって信号線に印加されると、トランジスタを介して液晶素子に電圧が印加される。走査線の選択が終了してから次にその走査線が選択されるまでの間ににおいてトランジスタがオフになっても、液晶素子がキャパシタとして機能するため、走査線の選択が終了してから次にその走査線が選択されるまでの間、電圧レベルが保持される。以上のように、走査線が選択されている時において液晶素子の光透過率が新たにリフレッシュされて、バックライトの光がリフレッシュされた光透過率で液晶素子を透過することによって、液晶ディスプレイの階調表現が行われる。 20

【0003】

一方、自発光素子である有機EL(Electro Luminescence: エレクトロルミネッセンス)素子を用いた有機エレクトロルミネッセンスディスプレイは、液晶ディスプレイのようにバックライトを必要とせず、薄型化に最適であるとともに、液晶ディスプレイのような視野角の制限もないため、次世代の表示装置として実用化が大きく期待されている。 30

【0004】

高輝度、高コントラスト、高精細といった観点から、有機エレクトロルミネッセンスディスプレイも、液晶ディスプレイと同様にアクティブマトリクス駆動方式の有機エレクトロルミネッセンスディスプレイが開発されている。例えば特許文献1に記載された従来のアクティブマトリクス駆動方式の有機エレクトロルミネッセンスディスプレイにおいては、有機EL素子を駆動するための画素回路(特許文献1においては、有機EL素子駆動回路と称されている。)が画素ごとに設けられている。画素回路は、有機EL素子(2、52)、駆動TFT(5、55)、第1のスイッチング素子(7、57)及びスイッチTFT(10、60)等から構成されている。制御線(4、54)が選択されると、信号ドライバにより駆動TFTのゲートに輝度データとして電圧が印加されることになる。これにより、駆動TFTがオンになり、ゲート電圧のレベルに応じた大きさの駆動電流が電源線から有機EL素子を介して駆動TFTに流れ、有機EL素子が電流の大きさに応じた輝度で発光する。制御線の選択が終了すると、駆動TFTのゲート電圧が第1のスイッチング素子によって保持され、有機EL素子の発光が保持される。その後、スイッチTFTのゲートにブランкиング信号が入力されると、駆動TFTのゲート電圧が下がって駆動TFTがオフし、有機EL素子が消灯して1フレーム期間が終了する。 40

【特許文献1】特開2000-221942号公報(第1図、第5図)

10

20

30

40

50

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

ところで、一般的にトランジスタは、周囲の温度変化によってチャネル抵抗が変化したり、長時間の使用によりチャネル抵抗が変化したりするために、ゲート閾値電圧が経時変化したり、ゲート閾値電圧がトランジスタごとに異なる。従って、従来の信号電圧によって輝度階調制御される電圧制御型アクティブマトリクス駆動方式の有機エレクトロルミネッセンスディスプレイでは、信号線からの信号電圧によって駆動TFTのゲート電圧のレベルを変化させることで有機EL素子に流れる電流の大きさを変化させることを行っても、駆動TFTのゲート電圧のレベルで有機EL素子に流れる電流の大きさを一義的に指定するのは困難である。つまり、複数の画素において同じレベルのゲート電圧を駆動TFTに印加したものとしても、有機EL素子の発光輝度が画素ごとに異なってしまい、表示面内で輝度のバラツキが生じてしまう。また、駆動TFTは経時に劣化してしまうため、初期時と同じゲート電圧を印加しても初期時と同じ電流値の駆動電流にならないので有機EL素子の発光輝度も異なってしまう。

**【0006】**

そこで、本発明は、上記のような問題点を解決しようとしてなされたものであり、高品質な表示を行うことができる表示装置、データ側駆動回路及び表示パネルの駆動方法を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

以上の課題を解決するために、本発明の表示装置は、

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、

前記複数の選択走査線を順次選択する選択走査ドライバと、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すデータ側駆動回路と、

前記複数の選択走査線及び前記複数の信号線にそれぞれ接続され、前記選択走査ドライバが前記選択走査線を選択することにより、前記信号線に流れる指定電流の大きさを記憶し、前記記憶した指定電流に従った大きさの駆動電流を前記複数の発光素子にそれぞれ流す複数の画素回路と、を備えることを特徴とする。

**【0008】**

好ましくは、前記データ側駆動回路は、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時の前半に前記複数の信号線に対してリセット電圧を印加した状態に切り換える切換部と、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前記切換部がリセット電圧を印加した後から、前記選択走査ドライバが前記複数の選択走査線各々の選択を解除するまでの間に、映像信号に従った大きさの指定電流を前記複数の信号線に流す信号ドライバと、を有する。

**【0009】**

好ましくは、前記複数の画素回路の各々は、

前記選択走査ドライバが前記選択走査線を選択している時に前記信号線に流れる指定電流を取り込んでその指定電流の大きさを電圧のレベルに変換して記憶し、

前記選択走査ドライバが前記選択走査線の選択を解除している時に前記信号線に流れる指定電流を遮断し、前記指定電流に応じて変換された電圧のレベルに従った駆動電流を前記発光素子に流す。

**【0010】**

好ましくは、前記発光素子が有機エレクトロルミネッセンス素子であり、前記有機エレ

10

20

30

40

50

クトロルミネッセンス素子の一方の電極が前記画素回路に接続されている。

【0011】

好ましくは、前記データ側駆動回路により印加するリセット電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧以下に設定されている。

【0012】

前記複数の選択走査線に対応して平行な複数の電源走査線が設けられ、

前記選択走査ドライバが前記複数の選択走査線を順次選択するのに同期して、前記複数の電源走査線を順次選択する電源走査ドライバが設けられ、

前記複数の画素回路の各々は、

ゲートが前記選択走査線に接続され、ドレインとソースのうちの一方が前記信号線に接続された第一トランジスタと、

ゲートが前記選択走査線に接続され、ドレインとソースのうちの一方が前記電源走査線に接続された第二トランジスタと、

ゲートが前記第二トランジスタのドレインとソースのうちの他方に接続され、ドレインとソースとのうちの一方が前記電源走査線に接続され、ドレインとソースのうちの他方が前記第一トランジスタのドレインとソースのうちの他方及び前記有機エレクトロルミネッセンス素子の一方の電極に接続された第三トランジスタと、

前記第三トランジスタのゲート - ソース間の電圧を保持することによって記憶するキャパシタと、を有する。

【0013】

好ましくは、前記選択走査ドライバが前記選択走査線を選択して前記第一トランジスタをオンしている時に、前記第一トランジスタが前記電源走査線から前記第三トランジスタのドレイン - ソース間を介して前記信号線に指定電流を流すことによって、前記第三トランジスタが指定電流の大きさをゲート - ソース間電圧のレベルに変換して前記キャパシタが変換された電圧のレベルを記憶し、

前記選択走査ドライバが前記選択走査線の選択を解除して前記第一トランジスタをオフしている時に、前記第三トランジスタが、前記キャパシタによって記憶されたゲート - ソース間電圧のレベルに従った大きさの駆動電流を前記有機エレクトロルミネッセンス素子へ流す。

【0014】

好ましくは、前記電源走査ドライバが前記電源走査線を選択している時に前記電源走査線に印加する電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧以下に設定されており、前記電源走査ドライバが前記電源走査線の選択を解除した時に前記電源走査線に印加する電圧が前記有機エレクトロルミネッセンス素子の他方の電極の電圧を越えるように設定されている。

【0015】

そして、本発明の表示装置は、

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、

前記複数の選択走査線を順次選択する選択走査ドライバと、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すデータ側駆動回路と、

前記複数の選択走査線及び前記複数の信号線にそれぞれ接続され、前記選択走査ドライバが前記選択走査線を選択することにより、前記信号線と前記発光素子とを導通させる複数の画素回路と、を備えることを特徴とする。

【0016】

また、本発明のデータ側駆動回路は、複数の選択走査線と前記複数の信号線とにそれぞれ接続され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、前記複数の

10

20

30

40

50

選択走査線を順次選択する選択走査ドライバと、前記複数の発光素子の各々に接続された複数の画素回路と、を備えるアクティブマトリクス駆動方式の表示装置におけるデータ側駆動回路であって、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前半に、リセット電圧を前記複数の信号線に印加し、前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流すことを特徴とする。

#### 【0017】

好みしくは、前記データ側駆動回路は、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時の前半に前記複数の信号線に対してリセット電圧を印加した状態に切り換える切換部と、

前記選択走査ドライバが前記複数の選択走査線を各々選択している時のうち前記切換部がリセット電圧を印加した後から、前記選択走査ドライバが前記複数の選択走査線各々の選択を解除するまでの間に、映像信号に従った大きさの指定電流を前記複数の信号線に流す信号ドライバと、を備える。

#### 【0018】

また、本発明の表示パネルの駆動方法は、

複数の選択走査線と複数の信号線との各交差部に配置され、流れる電流の大きさに従った輝度で発光する複数の発光素子と、前記選択走査線及び前記信号線にそれぞれ接続した複数の画素回路と、を備える表示パネルを駆動する方法であって、

前記複数の選択走査線を順次選択し、

前記複数の選択走査線が各々選択されている時のうち前半に、リセット電圧を前記複数の信号線に印加し、

前記複数の選択走査線が各々選択されている時のうちリセット電圧を印加した後に、映像信号に従った大きさの指定電流を前記複数の信号線に流し、

前記選択走査線が選択されることにより、前記信号線に流れる指定電流の大きさを記憶し、前記記憶した指定電流の大きさに従った大きさの駆動電流を前記画素回路によって前記発光素子に流すことを特徴とする。

#### 【0019】

本発明では、複数の選択走査線のうち或る選択走査線が選択されている時の前半に、その選択走査線に交差する信号線にリセット電圧が印加されることによって、信号線の寄生容量によって蓄積された電荷を放出することができる。

#### 【発明の効果】

#### 【0020】

本発明によれば、選択期間中に選択走査線の選択によって信号線と発光素子とが導通している間にリセット電圧を印加することで信号線のみならず、発光素子に蓄積された電荷を放出することで正確な電流値の電流を発光素子に流すことができ、高品質な画面表示を行うことができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

以下に、本発明を実施するための最良の形態について図面を用いて説明する。但し、以下に述べる実施形態には、本発明を実施するために技術的に好みしい種々の限定が付されているが、発明の範囲を以下の実施形態及び図示例に限定するものではない。

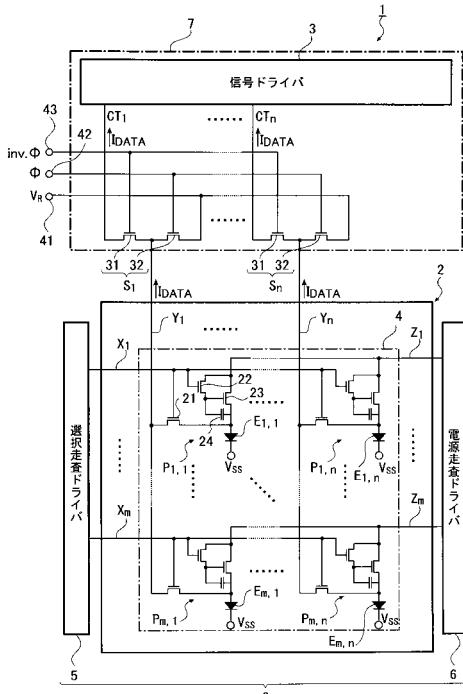

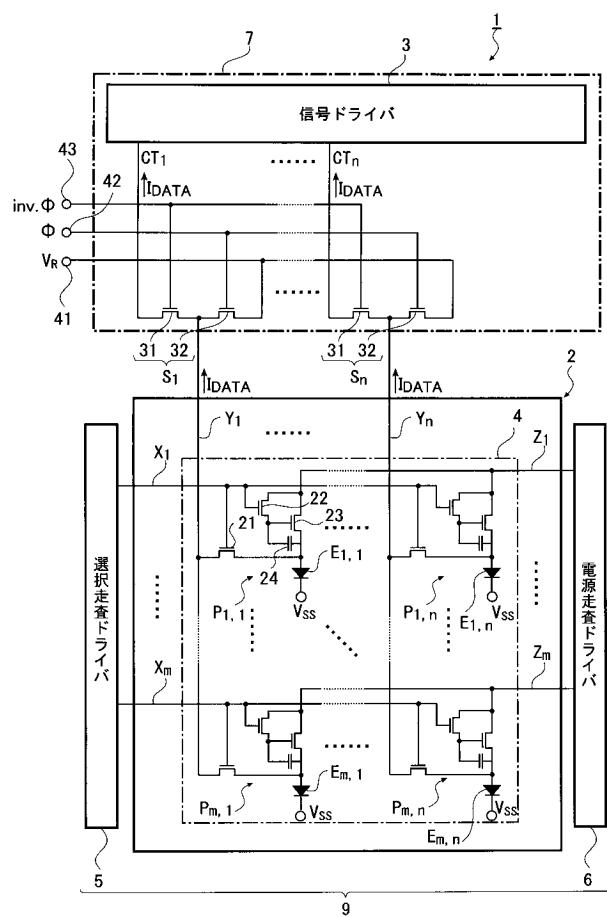

#### 【0022】

#### 〔第1の実施の形態〕

図1は、本発明の有機エレクトロルミネッセンスディスプレイを適用した第1の実施形態における有機エレクトロルミネッセンスディスプレイ1を示した図面である。図1に示されるように、有機エレクトロルミネッセンスディスプレイ1は、基本構成として、m本の選択走査線X<sub>1</sub>～X<sub>m</sub>、m本の電源走査線Z<sub>1</sub>～Z<sub>m</sub>、n本の信号線Y<sub>1</sub>～Y<sub>n</sub>及び画素P<sub>1,1</sub>～P<sub>m,n</sub>等を有する有機エレクトロルミネッセンス表示パネル2と、有機エレクトロルミ

10

20

30

40

50

ネッセンス表示パネル 2 を縦方向に線状走査する走査側駆動回路 9 と、この走査側駆動回路 9 と連動して階調指定電流  $I_{DATA}$  をそれぞれの信号線  $Y_1 \sim Y_n$  に流すデータ側駆動回路 7 と、を備える。ここで、 $m$ 、 $n$  は 2 以上の自然数である。

#### 【0023】

走査側駆動回路 9 は、選択走査線  $X_1 \sim X_m$  を順次選択する選択走査ドライバ 5 と、選択走査ドライバ 5 が選択走査線  $X_1 \sim X_m$  を順次選択することに同期して電源走査線  $Z_1 \sim Z_m$  を順次選択する電源走査ドライバ 6 と、を備える。また、データ側駆動回路 7 は、 $n$  個の電流端子  $CT_1 \sim CT_n$  を有するとともに電流端子  $CT_1 \sim CT_n$  それぞれに階調指定電流  $I_{DATA}$  が流れるようにする信号ドライバ 3 と、電流端子  $CT_1 \sim CT_n$  と信号線  $Y_1 \sim Y_n$  の間に介在した切換部  $S_1 \sim S_n$  と、を備える。

10

#### 【0024】

有機エレクトロルミネッセンス表示パネル 2 は、映像が実質的に表示される表示部 4 が透明基板上に設けられた構造となっている。表示部 4 の周囲に選択走査ドライバ 5、電源走査ドライバ 6、信号ドライバ 3 及び切換部  $S_1 \sim S_n$  が配設されている。選択走査ドライバ 5、電源走査ドライバ 6、信号ドライバ 3 及び切換部  $S_1 \sim S_n$  のうちの少なくとも 1 つの一部又は全体が、前記透明基板上に設けられた状態で有機エレクトロルミネッセンス表示パネル 2 と一緒に設けられても良いし、有機エレクトロルミネッセンス表示パネル 2 とは別にチップ化された状態で有機エレクトロルミネッセンス表示パネル 2 の周囲に設けられても良い。なお、透明基板の変わりに樹脂シート等のような可撓性シートに表示部 4 を設けても良い。

20

#### 【0025】

表示部 4 においては、 $(m \times n)$  個の画素  $P_{1,1} \sim P_{m,n}$  がマトリクス状となって前記透明基板上に設けられており、縦方向つまり列方向に  $m$  個の画素が配列され、横方向つまり行方向に  $n$  個の画素が配列されている。ここで、上から  $i$  番目 (つまり、 $i$  行目) であって左から  $j$  番目 (つまり、 $j$  列目) である画素が画素  $P_{i,j}$  となる。但し、 $i$  は 1 以上  $m$  以下の任意自然数であり、 $j$  は 1 以上  $n$  以下の任意自然数である。従って、

#### 【0026】

また、表示部 4 においては、行方向に延在する  $m$  本の選択走査線  $X_1 \sim X_m$  が互いに平行に配列して前記透明基板上に設けられている。行方向に延在する  $m$  本の電源走査線  $Z_1 \sim Z_m$  が選択走査線  $X_1 \sim X_m$  と対応するように互いに平行に配列して前記透明基板上に設けられている。電源走査線  $Z_k$  ( $1 \leq k \leq m-1$ ) は選択走査線  $X_k$  と選択走査線  $X_{k+1}$  との間に配置され、選択走査線  $X_m$  は電源走査線  $Z_{m-1}$  と電源走査線  $Z_m$  との間に配置されている。また、列方向に延在する  $n$  本の信号線  $Y_1 \sim Y_n$  が互いに平行に配列して前記透明基板上に設けられている。これら選択走査線  $X_1 \sim X_m$ 、電源走査線  $Z_1 \sim Z_m$  及び信号線  $Y_1 \sim Y_n$  は、介在する絶縁膜等によって離間されているので互いに絶縁されている。 $i$  行目の選択走査線  $X_i$  及び電源走査線  $Z_i$  には、行方向に沿って配列された  $n$  個の画素  $P_{i,1} \sim P_{i,n}$  が接続されており、 $j$  列目の信号線  $Y_j$  には、列方向に沿って配列された  $m$  個の画素  $P_{1,j} \sim P_{m,j}$  が接続されており、選択走査線  $X_i$  と信号線  $Y_j$  の交差部に画素  $P_{i,j}$  が配されている。選択走査線  $X_1 \sim X_m$  は選択走査ドライバ 5 のそれぞれの出力端子に接続されており、電源走査線  $Z_1 \sim Z_m$  は電源走査ドライバ 6 のそれぞれの出力端子に接続されている。

30

#### 【0027】

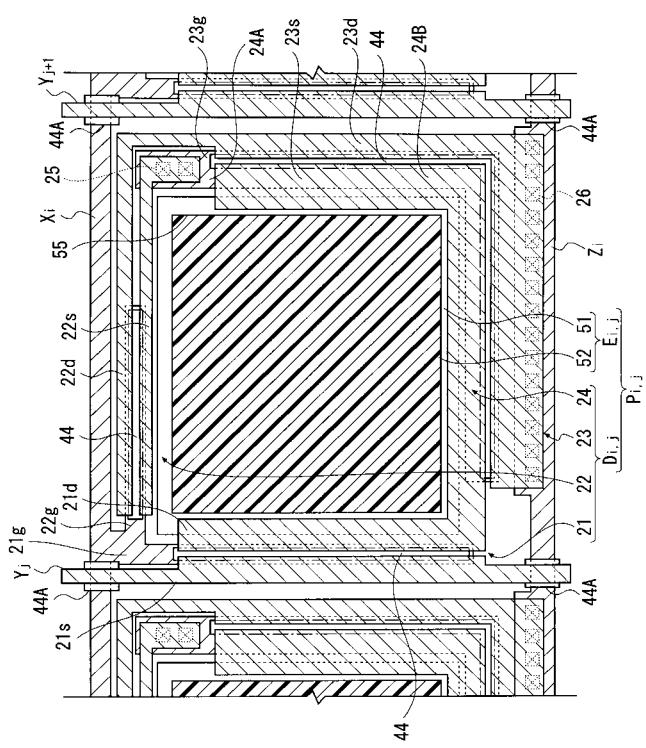

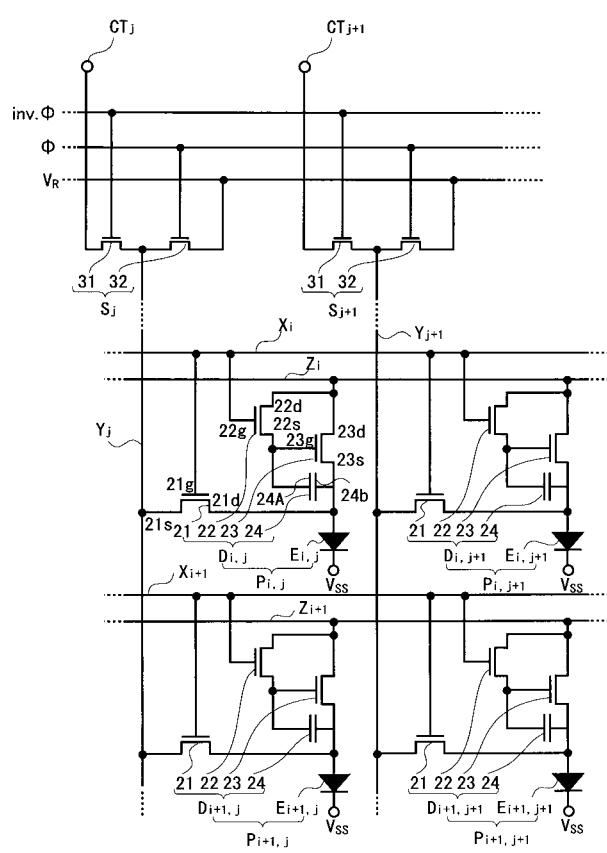

次に、図 2 及び図 3 を用いて画素  $P_{1,1} \sim P_{m,n}$  について説明する。図 2 は画素  $P_{i,j}$  を示した平面図であり、図 3 は隣接する四つの画素  $P_{i,j}$ 、 $P_{i+1,j}$ 、 $P_{i,j+1}$ 、 $P_{i+1,j+1}$  等の等価回路図である。図 2 においては、より理解しやすいように、画素  $P_{i,j}$  中の電極を主に示す。

40

#### 【0028】

画素  $P_{i,j}$  は、電流の大きさに従った輝度で発光する自発光素子としての有機エレクトロルミネッセンス (Electro Luminescence) 素子  $E_{i,j}$  と、有機エレクトロルミネッセンス素子  $E_{i,j}$  の周辺に設けられているとともに有機エレクトロルミネッセンス素子  $E_{i,j}$  を駆動する画素回路  $D_{i,j}$  と、から構成されている。なお、以下では、有機エレクトロルミ

50

ネッセンス素子を有機EL素子と略称する。

【0029】

有機EL素子E<sub>i,j</sub>は、アノードとして機能する画素電極51と、電界により注入された正孔及び電子を輸送し、輸送した正孔と電子を再結合し且つその再結合により生成された励起子により発光する広義の発光層として機能する有機EL層52と、カソードとして機能する共通電極とをこの順に前記透明基板上に積層した積層構造となっている。なお、図2の平面図において、全体を被覆するように共通電極が成膜されているが、画素電極51、有機EL層52及び画素回路D<sub>i,j</sub>等を把握しやすいように、共通電極の図示を省略する。

【0030】

画素電極51は、信号線Y<sub>1</sub>～Y<sub>n</sub>と選択走査線X<sub>1</sub>～X<sub>m</sub>と電源走査線Z<sub>1</sub>～Z<sub>m</sub>に囲まれる各囲繞領域に、画素P<sub>1,1</sub>～P<sub>m,n</sub>ごとにパターニングされている。

【0031】

画素電極51は、透明電極である。つまり、画素電極51は、導電性を有しているとともに、可視光に対して透過性を有している。また、画素電極51は、比較的仕事関数の高いものであり、有機EL層52へ正孔を効率よく注入するものが好ましい。画素電極51としては、例えば、錫ドープ酸化インジウム(ITO)、亜鉛ドープ酸化インジウム、酸化インジウム(Indium oxide)、酸化スズ(SnO<sub>2</sub>)、酸化亜鉛(ZnO)又はカドミウム-錫酸化物(CTO)を主成分としたものがある。

【0032】

各々の画素電極51上に有機EL層52が成膜されている。有機EL層52も画素P<sub>1,1</sub>～P<sub>m,n</sub>ごとにパターニングされている。有機EL層52には、有機化合物である発光材料(蛍光体)が含有されているが、発光材料は高分子系材料であっても良いし、低分子系材料であっても良い。特に、有機EL層52は、画素電極51から順に正孔輸送層、狭義の発光層の順に積層した二層構造である。正孔輸送層は、導電性高分子であるPEDOT(ポリチオフェン)及びドーパントであるPSS(ポリスチレンスルホン酸)からなり、狭義の発光層は、ポリフルオレン系発光材料からなる。なお、有機EL層52は、二層構造の他に、画素電極51から順に正孔輸送層、狭義の発光層、電子輸送層となる三層構造であっても良いし、狭義の発光層からなる一層構造であっても良いし、これらの層構造において適切な層間に電子或いは正孔の注入層が介在した積層構造であっても良いし、その他の積層構造であっても良い。

【0033】

この有機エレクトロルミネッセンス表示パネル2は、フルカラー表示又はマルチカラー表示が可能であり、この場合、画素P<sub>1,1</sub>～P<sub>m,n</sub>の有機EL層52はそれぞれ、例えば赤色、緑色、青色の何れかに発光する機能を有する広義の発光層である。つまり、赤色に発光する有機EL層52、緑色に発光する有機EL層52、青色に発光する有機EL層52が規則正しく配列され、これにより表示部4ではこれらの色が適宜合成された色調で表示が行われる。

【0034】

また、有機EL層52は、電子的に中立な有機化合物であることが望ましく、これにより正孔及び電子が有機EL層52でバランス良く注入され、輸送される。また、電子輸送性の物質が狭義の発光層に適宜混合されていても良いし、正孔輸送性の物質が狭義の発光層に適宜混合されていても良いし、電子輸送性の物質及び正孔輸送性の物質の両方が狭義の発光層に適宜混合されていても良い。また、電子輸送層又は正孔輸送層である電荷輸送層を、電子と正孔を再結合する再結合領域として機能させ、この電荷輸送層に蛍光体を混在させることによって発光させても良い。

【0035】

有機EL層52上に形成されている共通電極は、全ての画素P<sub>1,1</sub>～P<sub>m,n</sub>に共通して形成された電極である。なお、全ての画素P<sub>1,1</sub>～P<sub>m,n</sub>に共通した共通電極の代わりに、各列毎に分割された複数のストライプ形状の電極や各行毎に分割された複数のストライプ形

10

20

30

40

50

状の電極のように複数に分割されていてもよい。有機EL層52は一般的に発光色毎に材料が異なり電流密度に対する発光特性も材料に応じて異なるので、各発光色の輝度バランスを調整するために、有機EL層52の発光色毎に流れる電流値を設定するために発光色が同じ画素同士を互いに接続した画素であってもよい。すなわち相対的に低い電流密度で所定の輝度を発光する第一発光色画素と同じ輝度を発光するために高い電流密度が要求される第二発光色画素には、第一発光色画素よりも大きい各階調電流が流れるようにすることで発光色のバランスを調整することができる。

#### 【0036】

いずれにしても共通電極は、選択走査線 $X_1 \sim X_m$ 、信号線 $Y_1 \sim Y_n$ 、電源走査線 $Z_1 \sim Z_m$ と電気的に絶縁されている。共通電極は、仕事関数の低い材料で形成されており、例えば、インジウム、マグネシウム、カルシウム、リチウム、バリウム、希土類金属の少なくとも一種を含む単体又は合金で形成されている。また、共通電極は、上記各種材料の層が積層された積層構造となっていても良いし、以上の各種材料の層に加えて金属層が堆積した積層構造となっていても良く、具体的には、有機EL層52と接する界面側に設けられた低仕事関数のバリウム層と、バリウム層を被覆するように設けられたアルミニウム層との積層構造や、下層にリチウム層、上層にアルミニウム層が設けられた積層構造が挙げられる。また、画素電極51を透明電極とし、有機EL層52で発する光を画素電極51を介して前記透明基板側から出射させる場合、共通電極は有機EL層52で発する光に対して遮光性を有することが好ましく、有機EL層52で発する光に対して高い反射性を有することがさらに好ましい。

#### 【0037】

以上のように積層構造となる有機EL素子 $E_{i,j}$ では、画素電極51と共通電極との間に順バイアス電圧（画素電極51が共通電極よりも高電位）が印加されると、正孔が画素電極51から有機EL層52に注入され、電子が共通電極から有機EL層52に注入される。そして、有機EL層52で正孔及び電子が輸送されて、有機EL層52にて正孔及び電子が再結合することによって励起子が生成され、励起子が有機EL層52を励起して、有機EL層52で発光する。

#### 【0038】

有機EL素子 $E_{i,j}$ の発光輝度は有機EL素子 $E_{i,j}$ に流れる電流の大きさに依存し、流れる電流が大きくなるにつれて有機EL素子 $E_{i,j}$ の発光輝度も増大する。つまり、有機EL素子 $E_{i,j}$ の劣化を考慮しなければ、有機EL素子 $E_{i,j}$ に流れる電流の大きさが定まると、有機EL素子 $E_{i,j}$ の輝度が一義的に定まる。

#### 【0039】

各画素回路 $D_{1,1} \sim D_{m,n}$ は、三つの薄膜トランジスタ（以下単にトランジスタと記述する。）21, 22, 23と、キャパシタ24と、を備える。

#### 【0040】

トランジスタ21, 22, 23は、ゲート、ドレイン、ソース、半導体層44、不純物半導体層、ゲート絶縁膜等から構成されたNチャネルMOS型の電界効果トランジスタであり、特にアモルファスシリコンを半導体層44（チャネル領域）としたa-Siトランジスタであるが、ポリシリコンを半導体層44としたp-Siトランジスタであってもよい。何れのトランジスタ21, 22, 23もNチャネルの電界効果トランジスタである。トランジスタ21, 22, 23の構造は逆スタガ型であっても良いし、コプラナ型であっても良い。

#### 【0041】

また、トランジスタ21, 22, 23は同一工程で同時に形成されても良いが、この場合、ゲート、ドレイン、ソース、半導体層44、不純物半導体層、ゲート絶縁膜等の組成はトランジスタ21, 22, 23のあいだで同じであり、トランジスタ21, 22, 23の形状、大きさ、寸法、チャネル幅、チャネル長等はトランジスタ21, 22, 23のそれぞれの機能に応じて異なる。以下では、トランジスタ21を第一トランジスタ21と、トランジスタ22を第二トランジスタ22と、トランジスタ23を第三トランジスタ23

10

20

30

40

50

と称する。

【0042】

キャパシタ24は、第三トランジスタ23のゲート23gと接続された電極24Aと、トランジスタ23のソース23sと接続された電極24Bと、これら二つの電極の間に介在するゲート絶縁膜（誘電体膜）と、で構成され、第三トランジスタ23のゲート23gとソース23sとの間に電荷を蓄積する機能を有する。

【0043】

i行目の画素回路D<sub>i,1</sub>~D<sub>i,n</sub>それぞれの第二トランジスタ22においては、ゲート22gがi行目の選択走査線X<sub>i</sub>に接続され、ドレイン22dがi行目の電源走査線Z<sub>i</sub>に接続されている。i行目の画素回路D<sub>i,1</sub>~D<sub>i,n</sub>それぞれの第三トランジスタ23においては、ドレイン23dがコンタクトホール26を介してi行目の電源走査線Z<sub>i</sub>に接続されている。i行目の画素回路D<sub>i,1</sub>~D<sub>i,n</sub>それぞれの第一トランジスタ21においては、ゲート21gがi行目の選択走査線X<sub>i</sub>に接続されている。j列目の画素回路D<sub>1,j</sub>~D<sub>m,j</sub>それぞれの第一トランジスタ21においては、ソース21sがj列目の信号線Y<sub>j</sub>に接続されている。

【0044】

画素P<sub>1,1</sub>~P<sub>m,n</sub>それぞれにおいては、第二トランジスタ22のソース22sが、コンタクトホール25を通じて第三トランジスタ23のゲート23gに接続されるとともにキャパシタ24の一方の電極に接続されている。第三トランジスタ23のソース23sは、キャパシタ24の他方の電極に接続されるとともに第一トランジスタ21のドレイン21dに接続されている。第三トランジスタ23のソース23s、キャパシタ24の他方の電極及び第一トランジスタ21のドレイン21dは何れも画素電極51に接続されている。

【0045】

有機EL素子E<sub>1,1</sub>~E<sub>m,n</sub>の共通電極の電圧は、一定の基準電圧V<sub>ss</sub>に保たれており、本実施形態では、有機EL素子E<sub>1,1</sub>~E<sub>m,n</sub>の共通電極が接地されることで基準電圧V<sub>ss</sub>が0[V]に設定されている。

画素電極51は、信号線Y<sub>1</sub>~Y<sub>n</sub>と選択走査線X<sub>1</sub>~X<sub>m</sub>と電源走査線Z<sub>1</sub>~Z<sub>m</sub>とに囲まれる各囲繞領域に囲まれた画素毎に分割されるようにパターニングされており、且つ各画素回路の三つのトランジスタ21, 22, 23を覆う窒化シリコン又は酸化シリコンを有する層間絶縁膜で周縁を覆われるとともにその層間絶縁膜に設けられたコンタクトホール55により中央上面が露出されている。なお層間絶縁膜は、窒化シリコン又は酸化シリコンの第一層の上にさらにポリイミド等の絶縁膜からなる第二層が設けられていてよい。

選択走査線X<sub>i</sub>と信号線Y<sub>j</sub>との間、並びに電源走査線Z<sub>i</sub>と信号線Y<sub>j</sub>との間には、ゲート絶縁膜に加え、各トランジスタ21~23の半導体層44と同一膜をパターニングして形成された保護膜44Aが設けられている。なお、トランジスタ21、22、23の半導体層44のチャネルとなる表面がパターニングの際に用いられるエッチャントに晒されて荒れないように半導体層44の両端部を除いて窒化シリコン等からなるブロッキング絶縁層を設けてもよく、この場合、選択走査線X<sub>i</sub>と信号線Y<sub>j</sub>との間、並びに電源走査線Z<sub>i</sub>と信号線Y<sub>j</sub>との間にブロッキング絶縁層と同一膜をパターニングして形成された保護膜を設けてもよく、この保護膜及び保護膜44Aを重ね合わせてもよい。

【0046】

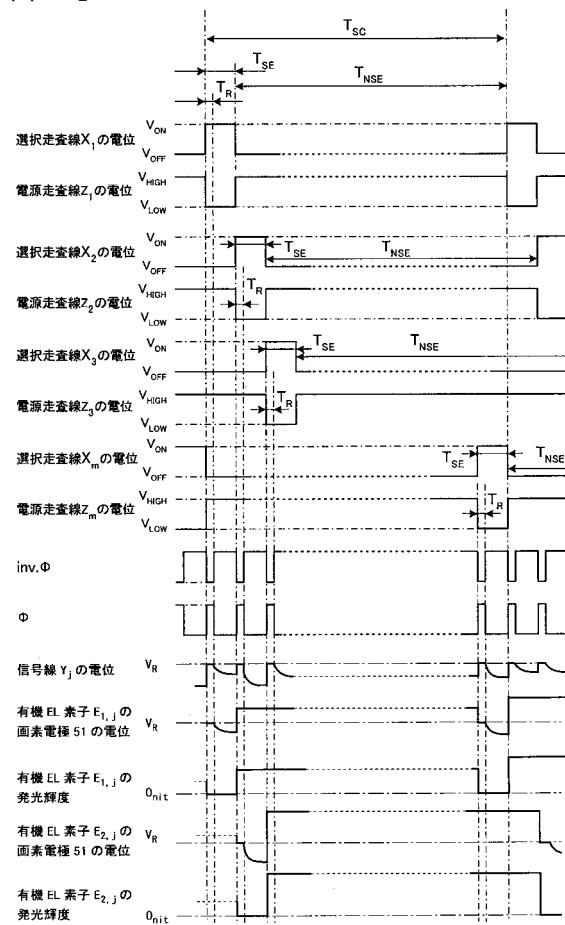

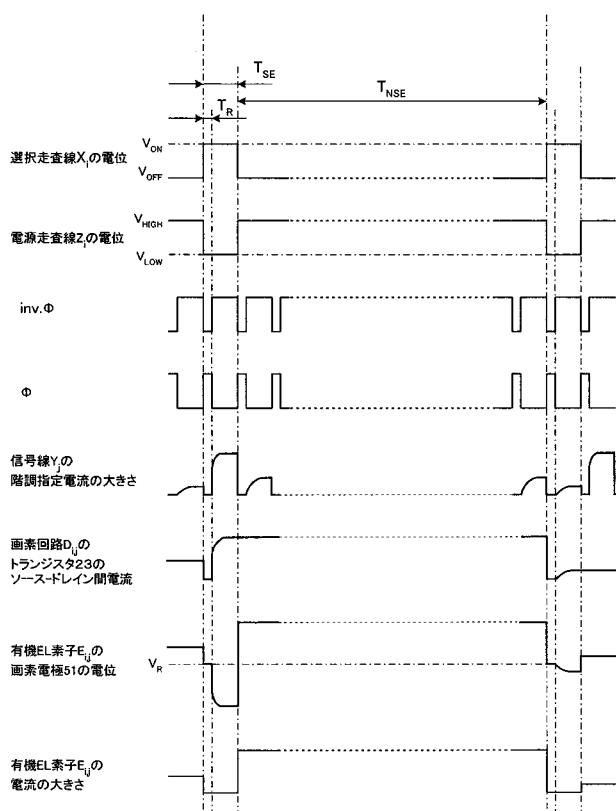

次に、選択走査ドライバ5、電源走査ドライバ6、切換部S<sub>1</sub>~S<sub>n</sub>及び信号ドライバ3について図4を用いて説明する。ここで、図4は、上から順に、選択走査線X<sub>1</sub>の電位、電源走査線Z<sub>2</sub>の電位、選択走査線X<sub>2</sub>の電位、電源走査線Z<sub>2</sub>の電位、選択走査線X<sub>3</sub>の電位、電源走査線Z<sub>3</sub>の電位、選択走査線X<sub>m</sub>の電位、電源走査線Z<sub>m</sub>の電位、切換信号i<sub>n</sub>v<sub>.</sub>のレベル（電圧値）、切換信号v<sub>.</sub>のレベル、信号線Y<sub>j</sub>の電位、有機EL素子E<sub>1,j</sub>の画素電極51の電位、有機EL素子E<sub>1,j</sub>の発光輝度、有機EL素子E<sub>2,j</sub>の画素電極51の電位、有機EL素子E<sub>2,j</sub>の発光輝度を示したタイミングチャートである。図4にお

10

20

30

40

50

いて、横軸は共通の時間を表す。

【0047】

選択走査ドライバ5は、いわゆるシフトレジスタであり、m個のフリップフロップ回路等を直列に接続した構成を有する。つまり、選択走査ドライバ5は、選択走査線X<sub>1</sub>から選択走査線X<sub>m</sub>への順（選択走査線X<sub>m</sub>の次は選択走査線X<sub>1</sub>）に選択信号を順次出力することで、選択走査線X<sub>1</sub>～X<sub>m</sub>を順次選択するものであり、選択走査線X<sub>1</sub>～X<sub>m</sub>にそれぞれ接続された各行の第一トランジスタ21及び第二トランジスタ22を順次選択するものである。

【0048】

詳細には図4に示されるように、選択走査ドライバ5は、選択信号としてハイレベル（オンレベル）のオン電圧V<sub>ON</sub>（基準電圧V<sub>SS</sub>よりも十分に高い。）又は非選択信号としてローレベルのオフ電圧V<sub>OFF</sub>（基準電圧V<sub>SS</sub>以下である。）の何れかのレベルの電圧を選択走査線X<sub>1</sub>～X<sub>m</sub>に個別に印加することによって、選択走査線X<sub>1</sub>～X<sub>m</sub>を順次選択する。

【0049】

即ち、選択走査ドライバ5がオン電圧V<sub>ON</sub>を選択走査線X<sub>i</sub>に印加するように設定されており、これによりi行目の選択走査線X<sub>i</sub>が選択される。選択走査ドライバ5がオン電圧V<sub>ON</sub>をi行目の選択走査線X<sub>i</sub>に印加することによりi行目の選択走査線X<sub>i</sub>が選択されている期間を、i行目の選択期間T<sub>SE</sub>と称する。なお、選択走査ドライバ5がオン電圧V<sub>ON</sub>を選択走査線X<sub>i</sub>に印加している時、選択走査ドライバ5が他の選択走査線X<sub>1</sub>～X<sub>m</sub>（但し、選択走査線X<sub>i</sub>を除く。）にオフ電圧V<sub>OFF</sub>を印加し、これにより選択走査線X<sub>1</sub>～X<sub>m</sub>の選択期間T<sub>SE</sub>は互いに重ならない。

【0050】

選択走査ドライバ5がオン電圧V<sub>ON</sub>をi行目の選択走査線X<sub>i</sub>に印加することにより、i行目の選択走査線X<sub>i</sub>に接続された画素回路D<sub>i,1</sub>～D<sub>i,n</sub>それぞれでは、第一トランジスタ21及び第二トランジスタ22がオン状態になる。第一トランジスタ21がオン状態になることによって信号線Y<sub>1</sub>～Y<sub>n</sub>に流れる電流がそれぞれ画素回路D<sub>i,1</sub>～D<sub>i,n</sub>に流れ得るようになる。

【0051】

一方、i行目の選択走査線X<sub>i</sub>が選択されている選択期間T<sub>SE</sub>の後では、選択走査ドライバ5がオフ電圧V<sub>OFF</sub>を選択走査線X<sub>i</sub>に印加して、選択走査線X<sub>i</sub>の選択を解除する。これにより、i行目の選択走査線X<sub>i</sub>に接続された画素回路D<sub>i,1</sub>～D<sub>i,n</sub>それぞれでは、第一トランジスタ21及び第二トランジスタ22がオフ状態になる。第一トランジスタ21がオフ状態になることで、信号線Y<sub>1</sub>～Y<sub>n</sub>に流れる電流はそれぞれ画素回路D<sub>i,1</sub>～D<sub>i,n</sub>に流れ得ないようになる。なお、選択走査ドライバ5がオフ電圧V<sub>OFF</sub>をi行目の選択走査線X<sub>i</sub>に印加することによりi行目の選択走査線X<sub>i</sub>の選択が解除されている期間を、i行目の非選択期間T<sub>NSE</sub>と称する。ここで、T<sub>SE</sub> + T<sub>NSE</sub> = T<sub>SC</sub>で表される期間、つまりi行目の選択走査線X<sub>i</sub>の選択期間T<sub>SE</sub>の開始時刻からi行目の選択走査線X<sub>i</sub>の次の選択期間T<sub>SE</sub>の開始時刻までの期間がi行目の1フレーム期間である。

【0052】

電源走査ドライバ6は、いわゆるシフトレジスタであり、m個のフリップフロップ回路等を直列に接続した構成を有する。つまり、電源走査ドライバ6は、選択走査ドライバ5に同期して、電源走査線Z<sub>1</sub>から電源走査線Z<sub>m</sub>への順（電源走査線Z<sub>m</sub>の次は電源走査線Z<sub>1</sub>）に選択信号を順次出力することで、電源走査線Z<sub>1</sub>～Z<sub>m</sub>を順次選択するものであり、電源走査線Z<sub>1</sub>～Z<sub>m</sub>にそれぞれ接続された各行の第三トランジスタ23を順次選択するものである。

【0053】

詳細には図4に示されるように、電源走査ドライバ6は、選択信号としてローレベルの階調指定電流用基準電圧V<sub>LOW</sub>（基準電圧V<sub>SS</sub>と等電圧であるか、又は基準電圧V<sub>SS</sub>未満である。）又は非選択信号としてハイレベルの駆動電流用基準電圧V<sub>HIGH</sub>（基準電圧V<sub>SS</sub>よりも高く、且つ階調指定電流用基準電圧V<sub>LOW</sub>よりも高い。）の何れかのレベルの電圧

10

20

30

40

50

を電源走査線  $Z_1 \sim Z_m$  に個別に印加することによって、電源走査線  $Z_1 \sim Z_m$  を順次選択する。

【0054】

即ち、 $i$  行目の選択走査線  $X_i$  が選択される選択期間  $T_{SE}$  では、電源走査ドライバ 6 が階調指定電流用基準電圧  $V_{LOW}$  を  $i$  行目の電源走査線  $Z_i$  に印加するように設定されており、これにより  $i$  行目の電源走査線  $Z_i$  が選択される。なお、電源走査ドライバ 6 が階調指定電流用基準電圧  $V_{LOW}$  を電源走査線  $Z_i$  に印加している時、電源走査ドライバ 6 が他の電源走査線  $Z_1 \sim Z_m$  ( 但し、電源走査線  $Z_i$  を除く。 ) に駆動電流用基準電圧  $V_{HIGH}$  を印加する。

【0055】

一方、 $i$  行目の選択走査線  $X_i$  が選択されていない非選択期間  $T_{NSE}$  では、電源走査ドライバ 6 は、駆動電流用基準電圧  $V_{HIGH}$  を電源走査線  $Z_i$  に印加して、 $i$  行目の電源走査線  $Z_i$  の選択を解除する。駆動電流用基準電圧  $V_{HIGH}$  は基準電圧  $V_{SS}$  よりも高く、トランジスタ 23 がオン状態となっているとともにトランジスタ 21 がオフ状態となつていれば、電源走査線  $Z_i$  から有機 EL 素子  $E_{i,j}$  へと電流が流れる。

【0056】

電源走査ドライバ 6 によって印加される階調指定電流用基準電圧  $V_{LOW}$  は基準電圧  $V_{SS}$  以下に設定されているため、選択期間  $T_{SE}$  中に各画素  $P_{1,1} \sim P_{m,n}$  の第三トランジスタ 23 がオン状態となつても、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  のアノード - カソード間にはゼロ電圧又は逆バイアス電圧が印加されていることになる。従って、選択期間  $T_{SE}$  中では有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に電流が流れないので、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  が発光するこがない。一方、電源走査ドライバ 6 によって印加される駆動電流用基準電圧  $V_{HIGH}$  が基準電圧  $V_{SS}$  より高く、図 5 に示されるように、第三トランジスタ 23 のソース - ドレイン間電圧  $V_{DS}$  が飽和領域になるように設定されている。そのため、非選択期間  $T_{NSE}$  に第三トランジスタ 23 がオン状態となつていれば、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に順バイアス電圧が印加されていることになる。従って、非選択期間  $T_{NSE}$  中では有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に電流が流れ、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  が発光する。

【0057】

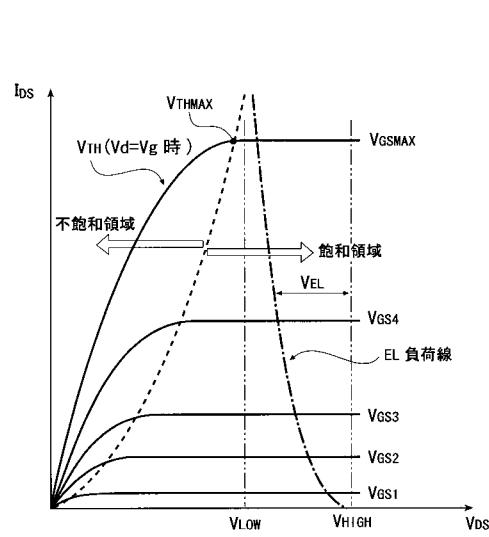

駆動電流用基準電圧  $V_{HIGH}$  について説明する。図 5 は、N チャネル型の電界効果トランジスタの電流 - 電圧特性を表したグラフである。図 5 において、横軸はドレイン - ソース間の電圧のレベルを表し、縦軸はドレイン - ソース間の電流の大きさを表す。図中の不飽和領域 ( ソース - ドレイン間電圧  $V_{DS} <$  ドレイン飽和閾電圧  $V_{TH}$  ) となつてている領域 : ドレイン飽和閾電圧  $V_{TH}$  はゲート - ソース間電圧  $V_{GS}$  の関数であり、ゲート - ソース間電圧  $V_{GS}$  が定まればゲート - ソース間電圧  $V_{GS}$  によってドレイン飽和閾電圧  $V_{TH}$  が一義的に定まる。 ) では、ゲート - ソース間電圧  $V_{GS}$  が一定であると、ソース - ドレイン間電圧  $V_{DS}$  が大きくなるにつれてソース - ドレイン間電流  $I_{DS}$  が大きくなる。更に、図中の飽和領域 ( ソース - ドレイン間電圧  $V_{DS} >$  ドレイン飽和閾電圧  $V_{TH}$  ) では、ゲート - ソース間電圧  $V_{GS}$  が一定であると、ソース - ドレイン間電圧  $V_{DS}$  が大きくなつてもソース - ドレイン間電流  $I_{DS}$  はほぼ一定となる。

【0058】

また、図 5 において、ゲート - ソース間電圧  $V_{GS1} \sim V_{GSMAX}$  は、 $0 [V] < V_{GS1} < V_{GS2} < V_{GS3} < V_{GS4} < V_{GSMAX}$  の関係となつてている。つまり、図 5 から明らかのように、ソース - ドレイン間電圧  $V_{DS}$  が一定の場合、ゲート - ソース間電圧  $V_{GS}$  が大きくなるにつれて、不飽和領域、飽和領域のいずれであつてもドレイン - ソース間電流  $I_{DS}$  が大きくなる。更に、ゲート - ソース間電圧  $V_{GS}$  が大きくなるにつれて、ドレイン飽和閾電圧  $V_{TH}$  が大きくなる。

【0059】

以上のことから、不飽和領域では、ゲート - ソース間電圧  $V_{GS}$  が一定のもとでソース - ドレイン間電圧  $V_{DS}$  がわずかに変わるとソース - ドレイン間電流  $I_{DS}$  が変わつてしまふが、飽和領域では、ゲート - ソース間電圧  $V_{GS}$  によってドレイン - ソース間電流  $I_{DS}$  が一義

10

20

30

40

50

的に定まる。

【0060】

ここで、第三トランジスタ23に最大のゲート-ソース間電圧 $V_{GSMAX}$ が印加されている時のドレイン-ソース間電流 $I_{DS}$ は、最大輝度で発光する有機EL素子 $E_{i,j}$ の画素電極51と共に通電極との間に流れる電流に設定されている。

また、非選択期間に第三トランジスタ23のゲート-ソース間電圧 $V_{GS}$ が最大電圧 $V_{GS MAX}$ であっても、第三トランジスタ23が選択期間 $T_{SE}$ 中に飽和領域を維持するように、下記に示す条件式を満たしている。

$$V_{LOW} = V_{HIGH} - V_E - V_{SS} - V_{THMAX}$$

ここで、 $V_E$ は、発光寿命期間中に有機EL素子 $E_{i,j}$ を最高輝度で発光するのに要するアノード-カソード間の電圧である。 $V_{THMAX}$ は、 $V_{GS MAX}$ 時のトランジスタ23のソース-ドレイン間の飽和閾電圧レベルである。以上の条件式を満たすように駆動電流用基準電圧 $V_{HIGH}$ が設定されている。従って、第三トランジスタ23と直列に接続された有機EL素子 $E_{i,j}$ の分圧により第三トランジスタ23のソース-ドレイン間電圧 $V_{DS}$ が低くなつても、ソース-ドレイン間電圧 $V_{DS}$ が常に飽和状態の範囲内なので、第三トランジスタ23に流れるソース-ドレイン間電流 $I_{DS}$ はゲート-ソース間電圧 $V_{GS}$ により一義的に決まることになる。

【0061】

図1、図3に示されるように、信号ドライバ3の電流端子 $CT_1 \sim CT_n$ には、それぞれ切換部 $S_1 \sim S_n$ を介して、それぞれ信号線 $Y_1 \sim Y_n$ が接続されている。信号ドライバ3には、8bitのデジタル階調映像信号が入力される。信号ドライバ3に取り込まれたデジタル階調映像信号は、信号ドライバ3内のD/Aコンバータによってアナログ変換される。そして、信号ドライバ3は、アナログ変換された映像信号に従った大きさの階調指定電流 $I_{DATA}$ をそれぞれ電流端子 $CT_1 \sim CT_n$ に発生させるものである。信号ドライバ3は、図4に示すように、各行の選択期間 $T_{SE}$ ごとに電流端子 $CT_1 \sim CT_n$ それぞれの階調指定電流 $I_{DATA}$ の大きさを映像信号に従った大きさに制御し、それぞれのリセット期間 $T_R$ が終了してからその選択期間 $T_{SE}$ が終了するまでの間では階調指定電流 $I_{DATA}$ の大きさを一定となるように制御する。ここで、信号ドライバ3は、階調指定電流 $I_{DATA}$ を信号線 $Y_1 \sim Y_n$ からそれぞれの切換部 $S_1 \sim S_n$ を介して、信号ドライバ3のそれぞれの電流端子 $CT_1 \sim CT_n$ に向かって流す。

【0062】

図1、図3に示されるように、切換部 $S_1 \sim S_n$ はそれぞれ信号線 $Y_1 \sim Y_n$ に接続されており、更に信号ドライバ3の電流端子 $CT_1 \sim CT_n$ が切換部 $S_1 \sim S_n$ にそれぞれ接続されている。更に、切換部 $S_1 \sim S_n$ はリセット入力端子41に接続されており、リセット電圧 $V_R$ がリセット入力端子41を介して切換部 $S_1 \sim S_n$ に印加される。また、切換部 $S_1 \sim S_n$ は切換信号入力端子42が接続されており、切換信号 $i_{n,v}$ が切換信号入力端子42を介して切換部 $S_1 \sim S_n$ に入力される。また、切換部 $S_1 \sim S_n$ は切換信号入力端子43が接続されており、切換信号 $i_{n,v}$ を反転した切換信号 $i_{n,v}$ が切換信号入力端子43を介して切換部 $S_1 \sim S_n$ に入力される。ここで、リセット電圧 $V_R$ は一定であり、階調指定電流用基準電圧 $V_{LOW}$ と同じレベル(電圧値)である。詳細には、リセット入力端子41が接地されることでリセット電圧 $V_R$ が0[V]に設定されている。

【0063】

切換部 $S_j$ (切換部 $S_j$ は、 $j$ 列目の信号線 $Y_j$ と $j$ 列目の電流端子 $CT_j$ に介在している。)は、信号ドライバ3による階調指定電流 $I_{DATA}$ を信号線 $Y_j$ に流す状態と、リセット電圧 $V_R$ を信号線 $Y_j$ に印加する状態とを切り換える。つまり、図4に示されるように、切換信号 $i_{n,v}$ がハイレベルであり且つ切換信号 $i_{n,v}$ がローレベルである場合には、切換部 $S_j$ は電流端子 $CT_j$ の電流を遮断するとともにリセット電圧 $V_R$ を信号線 $Y_j$ 及び第一トランジスタ21のドレイン21d、キャパシタ24の電極24B、第三トランジスタ23のソース23s、有機EL素子 $E_{x,j}$ ( $1 \times m$ )の画素電極51に印加して、前の選択期間 $T_{SE}$ 中にこれらに蓄積された電荷を放出する。一方、切換信号 $i_{n,v}$ がローレベルであ

10

20

30

40

50

り且つ切換信号  $i_{nV}$  がハイレベルである場合には、切換部  $S_j$  は電流端子  $CT_j$  の電流を信号線  $Y_j$  に流すとともに信号線  $Y_j$  に対するリセット電圧  $V_R$  の印加を遮断する。

#### 【0064】

ここで、切換信号 及び切換信号  $i_{nV}$  の周期について説明する。図4に示されるように、切換信号 及び切換信号  $i_{nV}$  の周期は、選択期間  $T_{SE}$  と同じである。つまり、選択走査ドライバ5が選択走査線  $X_1 \sim X_m$  のうちの何れかに対してオン電圧  $V_{ON}$  を印加し始める時(つまり、それぞれの行の選択期間  $T_{SE}$  の開始時)に、切換信号 がハイレベルからローレベルになるとともに切換信号  $i_{nV}$  がローレベルからハイレベルになる。そして、選択走査ドライバ5が選択走査線  $X_1 \sim X_m$  のうちの何れかに対してオン電圧  $V_{ON}$  を印加している時(つまり、それぞれの行の選択期間  $T_{SE}$  中に)に、切換信号 がローレベルからハイレベルになるとともに切換信号  $i_{nV}$  がハイレベルからローレベルになる。 $i$  行目の選択走査線  $X_i$  の選択期間  $T_{SE}$  中に切換信号 がハイレベルであり且つ切換信号  $i_{nV}$  がローレベルである期間を  $i$  行目のリセット期間  $T_R$  と称する。

#### 【0065】

切換部  $S_j$  の一例について説明する。切換部  $S_j$  は、Nチャネル型の電界効果トランジスタ31, 32から構成される。トランジスタ31のゲートが切換信号入力端子43に接続され、切換信号  $i_{nV}$  がトランジスタ31のゲートに入力される。また、トランジスタ32のゲートが切換信号入力端子42に接続され、切換信号 がトランジスタ32のゲートに入力される。トランジスタ31のドレインは信号線  $Y_j$  に接続されており、トランジスタ31のソースは電流端子  $CT_j$  に接続されている。トランジスタ32のドレインは信号線  $Y_j$  に接続されている。トランジスタ32のソースはリセット入力端子41に接続され、定電圧であるリセット電圧  $V_R$  がトランジスタ32のソースに印加されている。この構成では、切換信号 がハイレベルであり切換信号  $i_{nV}$  がローレベルである場合に、トランジスタ32がオン状態になり、トランジスタ31がオフ状態になる。一方、切換信号 がローレベルであり且つ切換信号  $i_{nV}$  がハイレベルの場合に、トランジスタ31がオン状態になり、トランジスタ32がオフ状態になる。トランジスタ31及びトランジスタ32は、画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ21～23と同じ工程によって製造されることが可能である。

#### 【0066】

次に、図6～図8を用いて画素回路  $D_{1,1} \sim D_{m,n}$  の機能について説明する。ここで、図6～図8では、電流の流れを矢印で示している。

#### 【0067】

図6は、 $i$  行目の選択期間  $T_{SE}$  のうちリセット期間  $T_R$  における電圧の状態を示した回路図である。図6に示されるように、 $i$  行目のリセット期間  $T_R$  では、選択走査線  $X_i$  にはオン電圧  $V_{ON}$  が選択走査ドライバ5によって印加されるとともに、電源走査線  $Z_i$  には階調指定電流用基準電圧  $V_{LOW}$  が電源走査ドライバ6によって印加されている。更に、 $i$  行目のリセット期間  $T_R$  では、それぞれの信号線  $Y_1 \sim Y_n$  にはリセット電圧  $V_R$  が切換部  $S_1 \sim S_n$  によって印加されている。従って、 $i$  行目のリセット期間  $T_R$  では、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ21がオン状態となっているので、それぞれの有機EL素子  $E_{i,1} \sim E_{i,n}$  の画素電極51、 $i$  行目の第一トランジスタ21のドレイン21d、 $i$  行目のキャパシタ24の電極24B、 $i$  行目の第三トランジスタ23のソース23s及び信号線  $Y_1 \sim Y_n$  の電圧が図4に示すように、リセット電圧  $V_R$  で定常状態となって前の選択期間  $T_{SE}$  中にこれらの寄生容量によって蓄積された電荷を放出するので、引き続き次の選択期間  $T_{SE}$  中に迅速且つ正確に階調指定電流  $I_{DATA}$  を書き込むことができる。また、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第二トランジスタ22及び第三トランジスタ23がオン状態となっているが、電源走査線  $Z_i$  に基準電圧  $V_{SS}$  以下の階調指定電流用基準電圧  $V_{LOW}$  が印加されているので、電源走査線  $Z_i$  から第三トランジスタ23に流れる階調指定電流  $I_{DATA}$  は有機EL素子  $E_{i,1} \sim E_{i,n}$  に流れない。

#### 【0068】

図7は、 $i$  行目の選択期間  $T_{SE}$  のうちリセット期間  $T_R$  後における電流、電圧の状態を

10

20

30

40

50

示した回路図である。図7に示されるように、 $i$ 行目の選択期間 $T_{SE}$ のうちリセット期間 $T_R$ 後では、選択走査線 $X_i$ にはオン電圧 $V_{ON}$ が選択走査ドライバ5によって引き続き印加されているとともに、電源走査線 $Z_i$ には階調指定電流用基準電圧 $V_{LOW}$ が電源走査ドライバ6によって引き続き印加されている。更に、 $i$ 行目の選択期間 $T_{SE}$ のうちリセット期間 $T_R$ 後では、各切換部 $S_1 \sim S_n$ がそれぞれ信号線 $Y_1 \sim Y_n$ からそれぞれ電流端子 $CT_1 \sim CT_n$ に階調指定電流 $I_{DATA}$ を流すように信号ドライバ3によって制御されている。 $i$ 行目の選択期間 $T_{SE}$ では、 $i$ 行目の各画素回路 $D_{i,1} \sim D_{i,n}$ の第二トランジスタ22がオン状態になっている。画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第二トランジスタ22はオン状態となることにより、画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第三トランジスタ23のゲート23gにも電圧が印加され、画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第三トランジスタ23がオン状態となる。更に、画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第一トランジスタ21もオン状態となっているので、画素回路 $D_{i,1} \sim D_{i,n}$ の何れにおいても第一トランジスタ21が電源走査線 $Z_i$ から第三トランジスタ23のドレイン23d及びソース23sを介してそれぞれの信号線 $Y_1 \sim Y_n$ に階調指定電流 $I_{DATA}$ を流す。このとき、信号線 $Y_j$ の電位は図4に示すように階調指定電流 $I_{DATA}$ が定常状態になるまで低下する。また、画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第三トランジスタ23がオン状態となっているが、電源走査線 $Z_i$ にローレベルの階調指定電流用基準電圧 $V_{LOW}$ が印加されているので、電源走査線 $Z_i$ から有機EL素子 $E_{i,1} \sim E_{i,n}$ に電流は流れない。このため、それぞれの信号線 $Y_1 \sim Y_n$ に流れる階調指定電流 $I_{DATA}$ の大きさが第三トランジスタ23のドレイン23d - ソース23s間電流 $I_{DS}$ の大きさに等しくなる。また、第三トランジスタ23のゲート23g - ソース23s間の電圧のレベルが、ドレイン23dからソース23sに流れる階調指定電流 $I_{DATA}$ の大きさに従ったレベルになる。従って、第三トランジスタ23は階調指定電流 $I_{DATA}$ の大きさをゲート23g - ソース23s間の電圧のレベルに変換し、第三トランジスタ23のゲート23g - ソース23s間の電圧のレベルに従った大きさの電荷がキャパシタ24にチャージされる。なお、第三トランジスタ23のゲート23gとドレイン23dとは、第二トランジスタ22を介して接続されており、選択時の第二トランジスタ22のオン抵抗は無視する程度なので第三トランジスタ23のゲート23gに印加された電圧とドレイン23dに印加された電圧はほぼ等しいため、階調指定電流 $I_{DATA}$ は図5に示す波線 $V_{TH}$ の線上を変位する電流 $I_{DS}$ となる。つまり第三トランジスタ23のゲート23gとドレイン23dが等電位の場合、不飽和領域と飽和領域との間の閾値電圧 $V_{TH}$ となるようなソース23s - ドレイン23d間電圧 $V_{DS}$ となる。

#### 【0069】

図8は、 $i$ 行目の非選択期間 $T_{NSE}$ における電流、電圧の状態を示した回路図である。図8に示されるように、 $i$ 行目の非選択期間 $T_{NSE}$ では、選択走査線 $X_i$ にはオフ電圧 $V_{OF}$ が選択走査ドライバ5によって印加されるとともに、電源走査線 $Z_i$ には駆動電流用基準電圧 $V_{HIGH}$ が電源走査ドライバ6によって印加されている。

#### 【0070】

$i$ 行目の非選択期間 $T_{NSE}$ では、画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第一トランジスタ21がオフ状態となっているので、画素回路 $D_{i,1} \sim D_{i,n}$ の何れにおいても第一トランジスタ21がそれぞれの信号線 $Y_1 \sim Y_n$ に流れている階調指定電流 $I_{DATA}$ を遮断し、電源走査線 $Z_i$ から第三トランジスタ23を介してそれぞれの信号線 $Y_1 \sim Y_n$ に電流が流れないようにする。更に、 $i$ 行目の画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第二トランジスタ22がオフ状態となることにより第二トランジスタ22がキャパシタ24にチャージされた電荷を閉じ込める。これにより、第二トランジスタ22は、第三トランジスタ23のゲート23g - ソース23s間の変換された電圧のレベルを保持することで第三トランジスタ23のソース - ドレイン間に流れる電流の電流値を記憶する。ここで、電源走査線 $Z_i$ に、第三トランジスタ23のソース - ドレイン間電圧 $V_{DS}$ が飽和領域を維持するようなハイレベルの駆動電流用基準電圧 $V_{HIGH}$ が印加されるとともに画素回路 $D_{i,1} \sim D_{i,n}$ それぞれの第三トランジスタ23がオン状態となっているので、それぞれの第三トランジスタ23が電源走査線 $Z_i$ からそれぞれの有機EL素子 $E_{i,1} \sim E_{i,n}$ に駆動電流を流し、駆動電流の電

10

20

30

40

50

流値に応じた輝度で有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>が発光する。このときの画素回路D<sub>i,1</sub>～D<sub>i,n</sub>それぞれの第三トランジスタ23のゲート23g-ソース23s間に変換した電圧のレベルは、選択期間T<sub>SE</sub>の後半にそれぞれ信号線Y<sub>1</sub>～Y<sub>n</sub>に階調指定電流I<sub>DATA</sub>が流れたときの電圧のレベルと等しいようにキャパシタ24によって保持されている。

ここで、非選択期間T<sub>NSE</sub>中の有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の分圧V<sub>EL</sub>は、図5に示すように、駆動電流用基準電圧V<sub>HIGH</sub>から、階調指定電流I<sub>DATA</sub>と等しい電流値の駆動電流(図5中のI<sub>DS</sub>に相当。)が流れるときの一点鎖線のEL負荷線上のV<sub>DS</sub>を差し引いたものである。このように、有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の分圧V<sub>EL</sub>は高輝度階調になるほど高くなる傾向を持つ。そして、非選択期間T<sub>NSE</sub>時において、駆動電流用基準電圧V<sub>HIGH</sub>は、有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の最低輝度階調の場合の第三トランジスタのドレイン23d-ソース23s間のオン抵抗V<sub>DS</sub>にそのときの分圧V<sub>EL</sub>を加えた電圧より高く、且つ有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の最高輝度階調の場合の第三トランジスタのドレイン23d-ソース23s間のオン抵抗V<sub>DS</sub>にそのときの分圧V<sub>EL</sub>を加えた電圧より高いように設定されている。また非選択期間T<sub>NSE</sub>中の第三トランジスタ23のソース23sの電位は、選択期間T<sub>SE</sub>中に保持されたゲート23g-ソース23s間の電圧V<sub>GS</sub>が高いほど高くなるが、これにともなってキャパシタ24はソース23sに接続された電極24B側の電荷が変位してしまうが、電極24A側の電荷を等しく変位させてゲート23g-ソース23s間の電圧V<sub>GS</sub>を常に一定にしている。

したがって、図5に示すように、非選択期間T<sub>NSE</sub>中の第三トランジスタ23のドレイン23d-ソース23s間は常に飽和領域電位になり、選択期間T<sub>SE</sub>に保持されたゲート23g-ソース23s間の電荷によって、非選択期間T<sub>NSE</sub>中に有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>に流れる駆動電流の大きさは階調指定電流I<sub>DATA</sub>の大きさに等しい。また図4に示すように、高輝度階調になるほど非選択期間T<sub>NSE</sub>中の有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の画素電極51での電位は高くなり、画素電極51とカソードである共通電極との電位差は大きくなり、有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>に流れるの発光輝度が大きくなる。

以上のように有機EL素子E<sub>i,1</sub>～E<sub>i,n</sub>の発光輝度(単位はnit.)は選択期間T<sub>SE</sub>にそれぞれの画素回路D<sub>i,1</sub>～D<sub>i,n</sub>に流れる階調指定電流I<sub>DATA</sub>の大きさによって一義的に決まる。

#### 【0071】

次に、信号ドライバ3、選択走査ドライバ5、電源走査ドライバ6及び切換部S<sub>1</sub>～S<sub>n</sub>で有機エレクトロルミネッセンス表示パネル2を駆動する方法及び有機エレクトロルミネッセンスディスプレイ1の表示動作について説明する。

#### 【0072】

図4に示されるように、選択走査ドライバ5が、1行目の選択走査線X<sub>1</sub>からm行目の選択走査線X<sub>m</sub>の順(但し、m行目の選択走査線X<sub>m</sub>の次は1行目の選択走査線X<sub>1</sub>)にオン電圧V<sub>ON</sub>を印加して選択していく。選択走査ドライバ5が選択するのに同期して、電源走査ドライバ6が1行目の電源走査線Z<sub>1</sub>からm行目の電源走査線Z<sub>m</sub>の順(但し、m行目の電源走査線Z<sub>m</sub>の次は1行目の電源走査線Z<sub>1</sub>)に階調指定電流用基準電圧V<sub>LOW</sub>を印加して選択していく。それぞれの行の選択期間T<sub>SE</sub>においては、信号ドライバ3が、映像信号に従った大きさの階調指定電流I<sub>DATA</sub>を電流端子C<sub>T1</sub>～C<sub>Tn</sub>に発生させるように制御する。

#### 【0073】

また、それぞれの行の選択期間T<sub>SE</sub>の開始時(前の行の選択期間T<sub>SE</sub>の終了時)に、切換信号i<sub>n</sub>v.がローレベルからハイレベルになるとともに切換信号i<sub>n</sub>v.がハイレベルからローレベルになり、信号線Y<sub>1</sub>～Y<sub>n</sub>に蓄積された電荷及び第一トランジスタ21を介して画素電極51に蓄積された電荷を放出するなりセット電圧V<sub>R</sub>が印加される。それぞれの行の選択期間T<sub>SE</sub>中(それぞれの行のリセット期間T<sub>R</sub>の終了時)に、切換信号i<sub>n</sub>v.がハイレベルからローレベルになるとともに切換信号i<sub>n</sub>v.がローレベルからハイレベルになる。これにより、選択期間T<sub>SE</sub>の前半であるリセット期間T<sub>R</sub>では、切換部S<sub>1</sub>～S<sub>n</sub>がそれぞれの電流端子C<sub>T1</sub>～C<sub>Tn</sub>とそれぞれの信号線Y<sub>1</sub>～Y<sub>n</sub>との間の階調指定電

10

20

30

40

50

流  $I_{DATA}$  の流れを許容するとともにそれぞれの信号線  $Y_1 \sim Y_n$  に対するリセット電圧  $V_R$  の印加を遮断し、選択期間  $T_{SE}$  のうちリセット期間  $T_R$  の後では、切換部  $S_1 \sim S_n$  がそれぞれの電流端子  $CT_1 \sim CT_n$  とそれぞれの信号線  $Y_1 \sim Y_n$  との間の電流の流れを遮断するとともにそれぞれの信号線  $Y_1 \sim Y_n$  に対するリセット電圧  $V_R$  の印加を許容する。

なお、階調指定電流  $I_{DATA}$  は輝度階調が低いほど小さい電流値になり、このときの信号線  $Y_1 \sim Y_n$  及び画素電極 5 1 の電位は階調指定電流用基準電圧  $V_{LOW}$ 、つまりリセット電圧  $V_R$  に近似する。また前回の選択期間  $T_{SE}$  時に大きい電流値の階調指定電流  $I_{DATA}$  が流れていると、信号線  $Y_1 \sim Y_n$  及び第一トランジスタ 2 1 を介して画素電極 5 1 の電位がリセット電圧  $V_R$  より十分低い電位になってしまふ。このため切換部  $S_1 \sim S_n$  を設けないで信号線  $Y_1 \sim Y_n$  及び画素電極 5 1 にリセット電圧を印加しない場合、引き続き低い輝度階調の低い電流値の階調指定電流  $I_{DATA}$  を流そうとすると、前回の選択期間  $T_{SE}$  時の大きい電流値の階調指定電流  $I_{DATA}$  に応じて蓄積された信号線  $Y_1 \sim Y_n$  の電荷及び画素電極 5 1 の電荷のため、第三トランジスタ 2 3 のドレイン 2 3 d - ソース 2 3 s 間を流れる電流の電流値が階調指定電流  $I_{DATA}$  になるまでに時間がかかってしまい、選択期間  $T_{SE}$  中に第三トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間に要求する電位が十分チャージできなくなってしまい、非選択期間  $T_{NSE}$  の駆動電流が階調指定電流  $I_{DATA}$  と異なり正確な階調表示ができなくなる。しかし、リセット期間  $T_R$  にリセット電圧  $V_R$  を印加する切換部  $S_1 \sim S_n$  を設けたので、信号線  $Y_1 \sim Y_n$  に蓄積された電荷及び第一トランジスタ 2 1 を介して画素電極 5 1 に蓄積された電荷を速やかに放出し、迅速に第三トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間の電位を低い輝度階調の低い電流値の階調指定電流  $I_{DATA}$  が流れるような電圧にすることができ、高速表示が可能となり特に動画特性に優れた映像を表示できる。

#### 【0074】

ここで、図 9 は、上から順に、選択走査線  $X_i$  の電位、電源走査線  $Z_i$  の電位、切換信号  $i_{nv.}$ 、切換信号、信号線  $Y_j$  の階調指定電流  $I_{DATA}$  の大きさ、画素回路  $D_{i,j}$  の第三トランジスタ 2 3 に流れる電流の大きさ、有機 EL 素子  $E_{i,j}$  の画素電極 5 1 の電位、有機 EL 素子  $E_{i,j}$  に流れる電流の大きさを示したタイミングチャートである。図 9 において、横軸は共通の時間を表す。

#### 【0075】

図 6、図 9 に示されるように、選択走査ドライバ 5 がオン電圧  $V_{ON}$  を  $i$  行目の選択走査線  $X_i$  に印加している時（つまり、 $i$  行目の選択期間  $T_{SE}$ ）では、他の選択走査線  $X_1 \sim X_m$ （但し、 $X_i$  を除く。）にはオフ電圧  $V_{OFF}$  が印加されている。従って、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の各画素回路  $D_{i,1} \sim D_{i,n}$  の第一トランジスタ 2 1 及び第二トランジスタ 2 2 がオン状態であり、他の行の画素回路  $D_{1,1} \sim D_{m,n}$ （但し、 $D_{i,1} \sim D_{i,n}$  を除く。）の第一トランジスタ 2 1 及び第二トランジスタ 2 2 がオフ状態である。

#### 【0076】

このように  $i$  行目の選択期間  $T_{SE}$  では階調指定電流用基準電圧  $V_{LOW}$  が電源走査線  $Z_i$  に印加されており、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第二トランジスタ 2 2 がオン状態であるので、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 2 3 のゲート 2 3 g にも電圧が印加され、第三トランジスタ 2 3 がオン状態となる。

#### 【0077】

$i$  行目の選択期間  $T_{SE}$  のうち前半のリセット期間  $T_R$  では、切換部  $S_1 \sim S_n$  それぞれのトランジスタ 3 2 がオン状態となることによって、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1 並びにそれぞれの信号線  $Y_1 \sim Y_n$  を介して、リセット入力端子 4 1 までの間が電気的に導通する。この時、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1 並びにそれぞれの信号線  $Y_1 \sim Y_n$  を介して、リセット入力端子 4 1 までの間の電圧が、基準電圧  $V_{SS}$  以下のリセット電圧  $V_R$ （リセット電圧  $V_R =$  階調指定電流用基準電圧  $V_{LOW}$ ）となるので、それぞれの有機 EL 素子  $E_{i,1} \sim E_{i,n}$  の画素電極 5 1 の電圧もリセット電圧  $V_R$  となる。更には、リセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されることによ

10

20

30

40

50

つて、信号線  $Y_1 \sim Y_n$  の寄生容量にチャージされた電荷並びに画素電極 5 1 を含む画素回路  $D_{i,1} \sim D_{i,n}$  の寄生容量にチャージされた電荷が除去され、これらの電位がリセット電圧  $V_R$  となる。そのため、 $i$  行目のリセット期間  $T_R$  の開始後すぐに、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  が消灯する。

#### 【0078】

図 7、図 9 に示されるように、リセット期間  $T_R$  に引き続き選択期間  $T_{SE}$  の後半でも、オン電圧  $V_{ON}$  が  $i$  行目の選択走査線  $X_i$  に印加されているとともに、階調指定電流用基準電圧  $V_{LOW}$  が  $i$  行目の電源走査線  $Z_i$  に印加されている。そのため、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ 2 1、第二トランジスタ 2 2 及び第三トランジスタ 2 3 がオン状態である。選択期間  $T_{SE}$  のうちリセット期間  $T_R$  の後では、切換部  $S_1 \sim S_n$  それぞれのトランジスタ 3 1 がオン状態となることによって切換部  $S_1 \sim S_n$  がそれぞれの電流端子  $CT_1 \sim CT_n$  とそれぞれの信号線  $Y_1 \sim Y_n$  との間の電流の流れを許容するので、電流端子  $CT_1 \sim CT_n$  は  $i$  行目の電源走査線  $Z_i$  に電気的に導通する。この時、信号ドライバ 3 は、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1、それぞれの信号線  $Y_1 \sim Y_n$ 、それぞれの切換部  $S_1 \sim S_n$  を介して、それぞれの電流端子  $CT_1 \sim CT_n$  に向かった階調指定電流  $I_{DATA}$  を流す。そして、 $i$  行目の選択期間  $T_{SE}$  が終了するまでの間、信号ドライバ 3 はそれぞれの信号線  $Y_1 \sim Y_n$  に流す階調指定電流  $I_{DATA}$  の大きさを映像信号に従った大きさで一定となるように制御する。

#### 【0079】

$i$  行目の選択期間  $T_{SE}$  の後半では、階調指定電流  $I_{DATA}$  が電源走査線  $Z_i$  画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 2 3 のドレイン 2 3 d - ソース 2 3 s 間 画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ 2 1 のドレイン 2 1 d - ソース 2 1 s 間 それぞれの信号線  $Y_1 \sim Y_n$  それぞれの切換部  $S_1 \sim S_n$  のトランジスタ 3 1 信号ドライバ 3 のそれぞれの電流端子  $CT_1 \sim CT_n$  に向かって流れることによって、 $i$  行目の選択期間  $T_{SE}$  中に、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1 並びにそれぞれの信号線  $Y_1 \sim Y_n$  を介してそれぞれの電流端子  $CT_1 \sim CT_n$  までの間の電圧が定常状態になる。

#### 【0080】

つまり、 $i$  行目の電源走査線  $Z_i$  からそれぞれの電流端子  $CT_1 \sim CT_n$  までの電圧が定常状態になることによって、第三トランジスタ 2 3 に流れる階調指定電流  $I_{DATA}$  の大きさに従ったレベルの電圧が第三トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間に印加され、第三トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間の電圧のレベルに従った大きさの電荷がキャパシタ 2 4 にチャージされる。これにより、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 2 3 に流れる階調指定電流  $I_{DATA}$  の大きさが、第三トランジスタ 2 3 のゲート 2 3 g - ソース 2 3 s 間の電圧のレベルに変換される。

#### 【0081】

上述したように  $i$  行目のリセット期間  $T_R$  においては、リセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されたので、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1 並びにそれぞれの信号線  $Y_1 \sim Y_n$  を介して、リセット入力端子 4 1 までの間の配線の電位を定常にすることできる。従って、 $i$  行目のリセット期間  $T_R$  の後において、微弱な階調指定電流  $I_{DATA}$  が信号線  $Y_1 \sim Y_n$  に流れる場合であっても、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれのキャパシタ 2 4 に階調指定電流  $I_{DATA}$  に応じた電荷を迅速にチャージすることができる。

#### 【0082】

以上のように、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 2 3 のドレイン 2 3 d - ソース 2 3 s 間に流れる電流の大きさ及びソース 2 3 s - ゲート 2 3 g 間の電圧のレベルも前回のフレーム期間  $T_{SC}$  から上書きされるので、 $i$  行目の選択期間  $T_{SE}$  中において、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のキャパシタ 2 4 にチャージされる電荷の大きさが前回のフレーム期間  $T_{SC}$  から上書きされる。

10

20

30

40

50

## 【0083】

ここで、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 23 から第一トランジスタ 21 を介してそれぞれの信号線  $Y_1 \sim Y_n$  までの間の任意の点での電位は、経時変化するトランジスタ 21, 22, 23 の内部抵抗等に因って変化してしまう。しかしながら、本実施形態では、信号ドライバ 3 が選択期間  $T_{SE}$  中に画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 23 から第一トランジスタ 21 を介してそれぞれの信号線  $Y_1 \sim Y_n$  へと流れる階調指定電流  $I_{DATA}$  を強制的に流しているため、トランジスタ 21, 22, 23 の内部抵抗が経時変化しても、階調指定電流  $I_{DATA}$  の大きさが所望通りとなる。

## 【0084】

また、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  の共通電極が基準電圧  $V_{SS}$  であり、電源走査線  $Z_i$  が基準電圧  $V_{SS}$  と同じ又は基準電圧  $V_{SS}$  よりもローレベルの階調指定電流用基準電圧  $V_{LOW}$  であるため、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には逆バイアス電圧が印加されるから、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には電流が流れず、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  は発光しない。

## 【0085】

続いて、図 8、図 9 に示されるように、 $i$  行目の選択期間  $T_{SE}$  の終了時刻（ $i$  行目の非選択期間  $T_{NSE}$  の開始時刻）では、選択走査ドライバ 5 から選択走査線  $X_i$  に出力される信号がハイレベルのオン電圧  $V_{ON}$  からローレベルのオフ電圧  $V_{OFF}$  になり、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ 21 のゲート 21g 及び第二トランジスタ 22 のゲート 22g に対してオフ電圧  $V_{OFF}$  が選択走査ドライバ 5 によって印加される。

## 【0086】

このため、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ 21 がオフ状態になり、オフ状態の第一トランジスタ 21 によって電流が電源走査線  $Z_i$  からそれぞれの信号線  $Y_1 \sim Y_n$  へ流れないようになる。更に、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の各画素回路  $D_{i,1} \sim D_{i,n}$  の第二トランジスタ 22 がオフ状態になると、直前の  $i$  行目の選択期間  $T_{SE}$  においてキャパシタ 24 にチャージされた電荷が第二トランジスタ 22 によって閉じ込められている。これにより、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、第三トランジスタ 23 は、非選択期間  $T_{NSE}$  中オン状態を維持し続ける。つまり、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、非選択期間  $T_{NSE}$  における第三トランジスタ 23 のゲート 23g - ソース 23s 間の電圧  $V_{GS}$  の大きさがその直前の選択期間  $T_{SE}$  における第三トランジスタ 23 のゲート 23g - ソース 23s 間の電圧  $V_{GS}$  の大きさと等しくなるように、つまり第二トランジスタ 22 によって電極 24A 側の電荷が保持されたキャパシタ 24 が第三トランジスタ 23 のゲート 23g - ソース 23s 間の電圧  $V_{GS}$  を保持する。

## 【0087】

また、 $i$  行目の非選択期間  $T_{NSE}$  では、電源走査ドライバ 6 が  $i$  行目の電源走査線  $Z_i$  に駆動電流用基準電圧  $V_{HIGH}$  を印加している。ここで、非選択期間  $T_{NSE}$  では、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  の共通電極が基準電圧  $V_{SS}$  である上、 $i$  行目の電源走査線  $Z_i$  が基準電圧  $V_{SS}$  より高い駆動電流用基準電圧  $V_{HIGH}$  であり、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第三トランジスタ 23 がオン状態であるため、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には順バイアス電圧が印加される。従って、画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、電源走査線  $Z_i$  からそれぞれの第三トランジスタ 23 を通じてそれぞれの有機 EL 素子  $E_{i,1} \sim E_{i,n}$  へ駆動電流が流れ、それぞれの有機 EL 素子  $E_{i,1} \sim E_{i,n}$  が発光する。

## 【0088】

つまり、 $i$  行目の非選択期間  $T_{NSE}$  中の画素回路  $D_{i,j}$  は、信号線  $Y_j$  と第三トランジスタ 23 との間を第一トランジスタ 21 により電気的に遮断し、キャパシタ 24 の電荷を第二トランジスタ 22 により閉じめることによって選択期間  $T_{SE}$  において変換された第三トランジスタ 23 のゲート 23g - ソース 23s 間の電圧のレベルを保持し、保持されたゲート 23g - ソース 23s 間の電圧のレベルに応じた大きさの駆動電流を第三トランジスタ 23 により有機 EL 素子  $E_{i,j}$  に流す。

10

20

30

40

50

## 【0089】

ここで、 $i$ 行目の選択期間  $T_{SE}$  中にそれぞれの有機EL素子  $E_{i,1} \sim E_{i,n}$  に流れる駆動電流の大きさは、それぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ23に流れる電流の大きさと同じであり、従って、選択期間  $T_{SE}$  においてそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ23に流れる階調指定電流  $I_{DATA}$  の大きさと同じである。上述したように、選択期間  $T_{SE}$  では、それぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ23に流れる階調指定電流  $I_{DATA}$  の大きさは所望通りとなるから、所望通りの大きさの駆動電流をそれぞれの有機EL素子  $E_{i,1} \sim E_{i,n}$  に流すことができ、それぞれの有機EL素子  $E_{i,1} \sim E_{i,n}$  を所望の階調輝度で発光させることができる。

## 【0090】

$i$ 行目の選択期間  $T_{SE}$  が終了した後の( $i+1$ )行目のリセット期間  $T_R$  では、 $i$ 行目のリセット期間  $T_R$  と同様に切換部  $S_1 \sim S_n$  それぞれのトランジスタ31がオフ状態になり、切換部  $S_1 \sim S_n$  それぞれのトランジスタ32がオン状態になる。従って、( $i+1$ )行目のリセット期間  $T_R$  では、何れの信号線  $Y_1 \sim Y_n$  にも階調指定電流  $I_{DATA}$  が流れないと、リセット電圧  $V_R$  が全ての信号線  $Y_1 \sim Y_n$ 、( $i+1$ )行目の画素電極51、( $i+1$ )行目のキャパシタ24の電極24B及び( $i+1$ )行目の第三トランジスタ23のソース23sに印加される。そして、( $i+1$ )行目の選択期間  $T_{SE}$  のうちリセット期間  $T_R$  の後では、 $i$ 行目の場合と同様に、( $i+1$ )行目の選択走査線  $X_{i+1}$  が選択走査ドライバ5によって選択されることによって、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ23及び第一トランジスタ21、それぞれの信号線  $Y_1 \sim Y_n$ 、それぞれの切換部  $S_1 \sim S_n$  を介して、それぞれの電流端子  $CT_1 \sim CT_n$  に向かって階調指定電流  $I_{DATA}$  が流れる。

## 【0091】

以上のように、リセット期間  $T_R$  では、リセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  や画素電極51等に強制的に印加されるので、信号線  $Y_1 \sim Y_n$  等の寄生容量のチャージ量は、小さい電流が流れる時に定常化されるときのチャージ量に近づける。そのため、( $i+1$ )行目のリセット期間  $T_R$  の後において信号線  $Y_1 \sim Y_n$  に流れる電流が微小であっても速やかに定常状態にすることができる。

## 【0092】

以上のように本実施形態では、非選択期間  $T_{NSE}$  において有機EL素子  $E_{1,1} \sim E_{m,n}$  に流れる駆動電流の大きさは、それぞれの選択期間  $T_{SE}$  のうちリセット期間  $T_R$  後において階調指定電流  $I_{DATA}$  の大きさで表されている。従って、例えば、画素回路  $D_{1,1} \sim D_{m,n}$  の間で第三トランジスタ23の特性にバラツキがあったとしても、画素回路  $D_{1,1} \sim D_{m,n}$  の間で階調指定電流  $I_{DATA}$  の大きさが同じであれば、有機EL素子  $E_{1,1} \sim E_{m,n}$  の間で輝度にバラツキが生じない。つまり、本実施形態では、同じレベルの輝度階調信号が画素に出力されても画素の間で輝度が異なってしまうという面内バラツキを抑えることができる。従って、本実施形態の有機エレクトロルミネッセンスディスプレイ1は、高品質な映像表示を行える。

## 【0093】

階調指定電流  $I_{DATA}$  は、発光するそれぞれの有機EL素子  $E_{1,1} \sim E_{m,n}$  の輝度に合わせてそれぞれの有機EL素子  $E_{1,1} \sim E_{m,n}$  に流れる電流の大きさと等しいために極めて微弱である。ここで信号線  $Y_1 \sim Y_n$  の配線容量のために、信号線  $Y_1 \sim Y_n$  に流れる階調指定電流  $I_{DATA}$  に遅延が生じてしまい、選択期間  $T_{SE}$  が短い場合には第三トランジスタ23のゲート-ソース間に階調指定電流  $I_{DATA}$  に応じた電荷をチャージアップできないといった問題を生じていた。しかしながら本実施形態では、それぞれの行のリセット期間  $T_R$  中に信号線  $Y_1 \sim Y_n$  に強制的にリセット電圧  $V_R$  を印加したので、特に階調指定電流  $I_{DATA}$  が微弱であっても、選択期間  $T_{SE}$  が短くても選択期間  $T_{SE}$  内に第三トランジスタ23のゲート-ソース間に階調指定電流  $I_{DATA}$  に応じた電荷をチャージアップすることができる。

## 【0094】

また、本実施形態では、選択期間  $T_{SE}$  中にデータ側駆動回路7によってリセット電圧  $V$

10

20

30

40

50

$R$  が信号線  $Y_1 \sim Y_n$  に印加されている。そのため、第一トランジスタ  $2_1$  が、画素回路  $D_{1,1} \sim D_{m,n}$  にリセット電圧  $V_R$  を取り込むスイッチング素子の機能と、画素回路  $D_{1,1} \sim D_{m,n}$  に階調指定電流  $I_{DATA}$  を取り込むためのスイッチング素子の機能と、を兼ねている。従って、従来（特許文献1）のように画素回路にブランкиング信号を取り込むスイッチ  $TF_T$  を第一トランジスタ  $2_1$  とは別に画素回路  $D_{1,1} \sim D_{m,n}$  に設ける必要がない。ゆえに、画素回路  $D_{1,1} \sim D_{m,n}$  に必要なトランジスタの数が増えず、有機EL素子  $E_{1,1} \sim E_{m,n}$  を画素回路  $D_{1,1} \sim D_{m,n}$  と同一面に作り込む場合、画素  $P_{1,1} \sim P_{m,n}$  の開口率の低下を防止することができる。

## 【0095】

## 〔第2の実施の形態〕

10

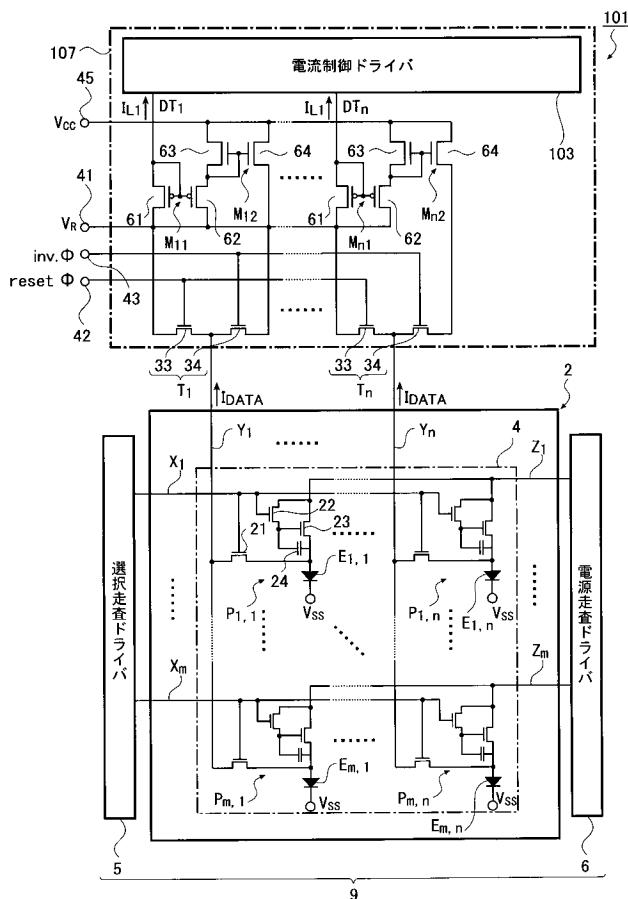

図10は、本発明の有機エレクトロルミネッセンスディスプレイを適用した第2の実施形態における有機エレクトロルミネッセンスディスプレイ101を示した図面である。図10に示すように、有機エレクトロルミネッセンスディスプレイ101において、第1の実施形態の有機エレクトロルミネッセンスディスプレイ1のいずれかの部分と同一の部分に対しては同一の符号を付し、同一の部分についての説明は省略する。

## 【0096】

この有機エレクトロルミネッセンスディスプレイ101も、図1の有機エレクトロルミネッセンスディスプレイ1と同様に、有機エレクトロルミネッセンス表示パネル2と、走査側駆動回路9と、データ側駆動回路107と、を備える。ここで、有機エレクトロルミネッセンス表示パネル2及び走査側駆動回路9は、第1の実施形態における有機エレクトロルミネッセンス表示パネル2及び走査側駆動回路9とそれと同じである。但し、データ側駆動回路107は、第1の実施形態におけるデータ側駆動回路7と異なる。

20

## 【0097】

このデータ側駆動回路107は、 $n$  個の電流端子  $D_{T_1} \sim D_{T_n}$  を有するとともに電流端子  $D_{T_1} \sim D_{T_n}$  それぞれに引抜電流  $I_{L1}$  を流す電流制御ドライバ103と、電流端子  $D_{T_1} \sim D_{T_n}$  に流れる引抜電流  $I_{L1}$  を階調指定電流  $I_{DATA}$  に変換する第1カレントミラー回路  $M_{11} \sim M_{n1}$  及び第2カレントミラー回路  $M_{12} \sim M_{n2}$  と、信号線  $Y_1 \sim Y_n$  と第1カレントミラー回路  $M_{11} \sim M_{n1}$  及び第2カレントミラー回路  $M_{12} \sim M_{n2}$  との間に介在した切換部  $T_1 \sim T_n$  と、を備える。

## 【0098】

30

電流制御ドライバ103には、8bitのデジタル階調映像信号が入力される。電流制御ドライバ103に取り込まれたデジタル階調映像信号は、電流制御ドライバ103内のD/Aコンバータによってアナログ変換される。そして、電流制御ドライバ103は、アナログ変換された映像信号に従った大きさの引抜電流  $I_{L1}$  を電流端子  $D_{T_1} \sim D_{T_n}$  それぞれに発生させるものである。電流制御ドライバ103は、行毎に設けられた第1カレントミラー回路  $M_{11} \sim M_{n1}$  からそれぞれの電流端子  $D_{T_1} \sim D_{T_n}$  に向かって引抜電流  $I_{L1}$  を流し、この引抜電流  $I_{L1}$  にしたがって、各行の第三トランジスタ23から信号線  $Y_1 \sim Y_n$  を介して第2カレントミラー回路  $M_{12} \sim M_{n2}$  に向かって階調指定電流  $I_{DATA}$  を流す。

## 【0099】

電流制御ドライバ103の動作タイミングは、第1の実施形態における信号ドライバ3の動作タイミングと同じである。つまり、電流制御ドライバ103は、各行の選択期間  $T_{SE}$  ごとに電流端子  $D_{T_1} \sim D_{T_n}$  それぞれの引抜電流  $I_{L1}$  の大きさを映像信号に従った大きさに制御し、それぞれのリセット期間  $T_R$  が終了してからその選択期間  $T_{SE}$  が終了するまでの間では引抜電流  $I_{L1}$  の大きさを定常化するように制御する。ここで、電流制御ドライバ103によって流れる引抜電流  $I_{L1}$  は、第1の実施形態における信号ドライバ3階調指定電流  $I_{DATA}$  よりも大きく、電流制御ドライバ103によって流れる引抜電流  $I_{L1}$  と第1の実施形態における信号ドライバ3が流す階調指定電流  $I_{DATA}$  との関係は比例関係にある。

40

## 【0100】

第1カレントミラー回路  $M_{11} \sim M_{n1}$  及び第2カレントミラー回路  $M_{12} \sim M_{n2}$  は、電流端

50

子  $D T_1 \sim D T_n$  に流れる引抜電流  $I_{L1}$  を所定の変換率で階調指定電流  $I_{DATA}$  に変換するものである。第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  は、二つの P チャネル型 MOS 型のトランジスタ 61, 62 から構成されている。トランジスタ 61, 62 は、画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ 21 ~ 23 と同じ工程によって製造されることが可能である。第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  は、二つの N チャネル型 MOS 型のトランジスタ 63, 64 から構成されている。トランジスタ 63, 64 は、部分的に画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ 21 ~ 23 と同じ工程によって製造されることが可能である。

### 【0101】

各第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  において、トランジスタ 61 のゲート、ドレイン及びトランジスタ 62 のゲートが互いにそれぞれの電流端子  $D T_1 \sim D T_n$  と接続されている。そしてトランジスタ 61 のソース及びトランジスタ 62 のソースは、接地電位であるリセット電圧  $V_R$  が出力されているリセット入力端子 41 に接続されている。

各第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  において、トランジスタ 63 のゲート、ドレイン及びトランジスタ 64 のゲートが互いに接続されるとともにトランジスタ 62 のドレインに接続されている。そしてトランジスタ 63 のソース及びトランジスタ 64 のソースは、負電圧  $V_{CC}$  が印加されている定電圧入力端子 45 に接続され、トランジスタ 64 のドレインが後述する切換部  $T_1 \sim T_n$  のトランジスタ 32 のソースと接続されている。また、第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  では、トランジスタ 61 のチャネル抵抗は、トランジスタ 62 のチャネル抵抗より小さい。第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  では、トランジスタ 63 のチャネル抵抗は、トランジスタ 64 のチャネル抵抗より小さい。

切換部  $T_1 \sim T_n$  は、それぞれ 2 つの N チャネル型 MOS トランジスタ 33, 34 を有している。トランジスタ 33 及びトランジスタ 34 は、画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ 21 ~ 23 と同じ工程によって製造されることが可能である。ここで切換部  $T_j$  の一例について説明する。切換部  $T_j$  のトランジスタ 34 のゲートが切換信号入力端子 43 に接続され、切換信号  $i_{nv.}$  がトランジスタ 34 のゲートに入力される。また、トランジスタ 33 のゲートが切換信号入力端子 42 に接続され、切換信号  $i_{nv.}$  がトランジスタ 33 のゲートに入力される。トランジスタ 34 のドレイン及びトランジスタ 33 のドレインは信号線  $Y_j$  に接続されており、トランジスタ 33 のソースは第 1 カレントミラー回路  $M_{11}$  のトランジスタ 61 のソースとともにリセット入力端子 41 に接続されており、トランジスタ 34 のソースは第 2 カレントミラー回路  $M_{12}$  のトランジスタ 64 のドレインに接続されている。

この構成では、切換信号  $i_{nv.}$  がハイレベルであり切換信号  $i_{nv.}$  がローレベルである場合に、トランジスタ 33 がオン状態になり、トランジスタ 34 がオフ状態になる。一方、切換信号  $i_{nv.}$  がローレベルであり且つ切換信号  $i_{nv.}$  がハイレベルの場合に、トランジスタ 34 がオン状態になり、トランジスタ 33 がオフ状態になる。ここで、切換信号及び切換信号  $i_{nv.}$  は、第 1 実施形態の図 4 と同様の波形となる。したがって、各切換部  $T_1 \sim T_n$  は、第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  及び第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  のそれによって引抜電流  $I_{L1}$  の大きさが変調された階調指定電流  $I_{DATA}$  をそれぞれの第三トランジスタ 23 及び信号線  $Y_1 \sim Y_n$  に流す状態と、リセット電圧  $V_R$  をそれぞれの信号線  $Y_1 \sim Y_n$  に印加する状態とを切り換える。

### 【0102】

電流制御ドライバ 103 が電流端子  $D T_j$  に引抜電流  $I_{L1}$  を流すと、第 1 カレントミラー回路  $M_{11}$  において、トランジスタ 62 のドレイン - ソース間を流れる電流は、トランジスタ 61 のチャネル抵抗に対するトランジスタ 62 のチャネル抵抗の比率にトランジスタ 61 のドレイン - ソース間の引抜電流  $I_{L1}$  の大きさを乗じた値となる。そして、第 2 カレントミラー回路  $M_{12}$  において、トランジスタ 64 のドレイン - ソース間を流れる電流は、トランジスタ 63 のチャネル抵抗に対するトランジスタ 64 のチャネル抵抗の比率にトランジスタ 63 のドレイン - ソース間の電流の大きさを乗じた値となる。ここでトランジスタ 63 のドレイン - ソース間の電流の大きさは、トランジスタ 62 のドレイン - ソース間を流れる電流に一致する。したがって、階調指定電流  $I_{DATA}$  は、トランジスタ 63 のチャ

10

20

30

40

50

ネル抵抗に対するトランジスタ 6 4 のチャネル抵抗の比率に、トランジスタ 6 1 のチャネル抵抗に対するトランジスタ 6 2 のチャネル抵抗の比率にトランジスタ 6 1 のドレイン - ソース間の引抜電流  $I_{L1}$  の大きさを乗じた値を、乗じた値になる。

#### 【 0 1 0 3 】

以上のようにして、第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  及び第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  は電流端子  $D T_1 \sim D T_n$  に流れる引抜電流  $I_{L1}$  を階調指定電流  $I_{DATA}$  に変換する。そして、第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  の出力側につまりトランジスタ 6 4 のドレインに階調指定電流  $I_{DATA}$  が流れるので、第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  のトランジスタ 6 4 のドレインが、第 1 の実施形態における信号ドライバ 3 の電流端子  $C T_j$  に相当する。つまり、第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  及び第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  と電流制御ドライバ 103 とを組み合わせた構成が第 1 の実施形態における信号ドライバ 3 に相当する。10

#### 【 0 1 0 4 】

第 1 の実施形態では、リセット電圧  $V_R$  が階調指定電流用基準電圧  $V_{LOW}$  と同じレベルであったが、第 2 の実施形態ではリセット電圧  $V_R$  が 0 [V] に設定されている。したがって、電極  $V_{SS}$  を接地電位に設定すると、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  のアノードである画素電極 5 1 とカソードである共通電極との間の電位差がなくなり画素電極 5 1 に蓄積された電荷を容易に放出することができる。

#### 【 0 1 0 5 】

切換部  $T_1 \sim T_n$  が切換動作を行うために、第 1 の実施形態と同様に切換信号  $i$  が切換信号入力端子 4 2 に入力され、切換信号  $i_{nv}$  が切換信号入力端子 4 3 に入力される。切換信号  $i$  及び切換信号  $i_{nv}$  のタイミングと選択走査ドライバ 5 及び電源走査ドライバ 6 が選択していくタイミングとの関係は、第 1 の実施形態の場合と同様である。また、第 2 の実施形態における選択走査ドライバ 5 及び電源走査ドライバ 6 の動作タイミングは、第 1 の実施形態のそれと同じである。20

#### 【 0 1 0 6 】

そして、第 2 の実施形態においても、 $i$  行目の選択期間  $T_{SE}$  のうち前半のリセット期間  $T_R$  では、切換部  $T_1 \sim T_n$  それぞれのトランジスタ 3 3 がオン状態となることによって、電源走査線  $Z_i$  からそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 及び第一トランジスタ 2 1 並びにそれぞれの信号線  $Y_1 \sim Y_n$  を介して、リセット入力端子 4 1 までの間が電気的に導通する。30

#### 【 0 1 0 7 】

また、 $i$  行目のリセット期間  $T_R$  では、リセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  や画素電極 5 1 に印加されるので、信号線  $Y_1 \sim Y_n$  の寄生容量に蓄積された電荷及び画素電極 5 1 の蓄積容量に蓄積された電荷を迅速に放出することができる。従って、 $i$  行目のリセット期間  $T_R$  の後において、微弱な階調指定電流  $I_{DATA}$  が信号線  $Y_1 \sim Y_n$  に流れる場合であっても、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれのキャパシタ 2 4 に階調指定電流  $I_{DATA}$  に応じた電荷を迅速にチャージすることができる。

#### 【 0 1 0 8 】

また、非選択期間  $T_{NSE}$  において有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に流れる駆動電流の大きさは、それぞれの選択期間  $T_{SE}$  のうちリセット期間  $T_R$  後における階調指定電流  $I_{DATA}$  の大きさで表されている。従って、例えば、画素回路  $D_{1,1} \sim D_{m,n}$  の間で第三トランジスタ 2 3 の特性にバラツキがあったとしても、第三トランジスタ 2 3 に強制的に階調指定電流  $I_{DATA}$  を流すので駆動電流にバラツキが生じることがなく、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  の間で輝度にバラツキが生じない。40

#### 【 0 1 0 9 】

また、第 1 カレントミラー回路  $M_{11} \sim M_{n1}$  及び第 2 カレントミラー回路  $M_{12} \sim M_{n2}$  が設けられることによって、それぞれの信号線  $Y_1 \sim Y_n$  の階調指定電流  $I_{DATA}$  の大きさは、それぞれの電流端子  $D T_1 \sim D T_n$  の引抜電流  $I_{L1}$  に比例するとともに引抜電流  $I_{L1}$  より小さい。従って、電流制御ドライバ 103 等にリーク電流が生じることによって電流端子  $D T$  50

$I_{L1} \sim I_{Ln}$  の引抜電流  $I_{L1}$  が不意に低減しても、信号線  $Y_1 \sim Y_n$  の階調指定電流  $I_{DATA}$  が大幅に低くなることはない。つまり、電流リーアによって電流制御ドライバ 103 の出力が低下しても、信号線  $Y_1 \sim Y_n$  の階調指定電流  $I_{DATA}$  に大きく影響することなく、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  の発光輝度が大きく低減することがない。

そして、第 2 の実施形態では、電流制御ドライバ 103 が有機 EL 素子の発光特性に見合った階調指定電流  $I_{DATA}$  程度の微小電流を発生できなくても十分にデータ側駆動回路 107 が階調指定電流  $I_{DATA}$  を発生することができる。

#### 【0110】

また、第 2 の実施形態でも、選択期間  $T_{SE}$  中にデータ側駆動回路 107 によってリセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されている。そのため、第一トランジスタ 21 が、画素回路  $D_{1,1} \sim D_{m,n}$  にリセット電圧  $V_R$  を取り込むスイッチング素子の機能と、画素回路  $D_{1,1} \sim D_{m,n}$  に階調指定電流  $I_{DATA}$  を取り込むためのスイッチング素子の機能と、を兼ねている。従って、画素回路  $D_{1,1} \sim D_{m,n}$  に必要なトランジスタの数が増えず、有機 EL 素子  $E_{1,1} \sim E_{m,n}$  を画素回路  $D_{1,1} \sim D_{m,n}$  と同一面に作り込む場合、画素  $P_{1,1} \sim P_{m,n}$  の開口率の低下を防止することができる。

#### 【0111】

##### [第 3 の実施の形態]

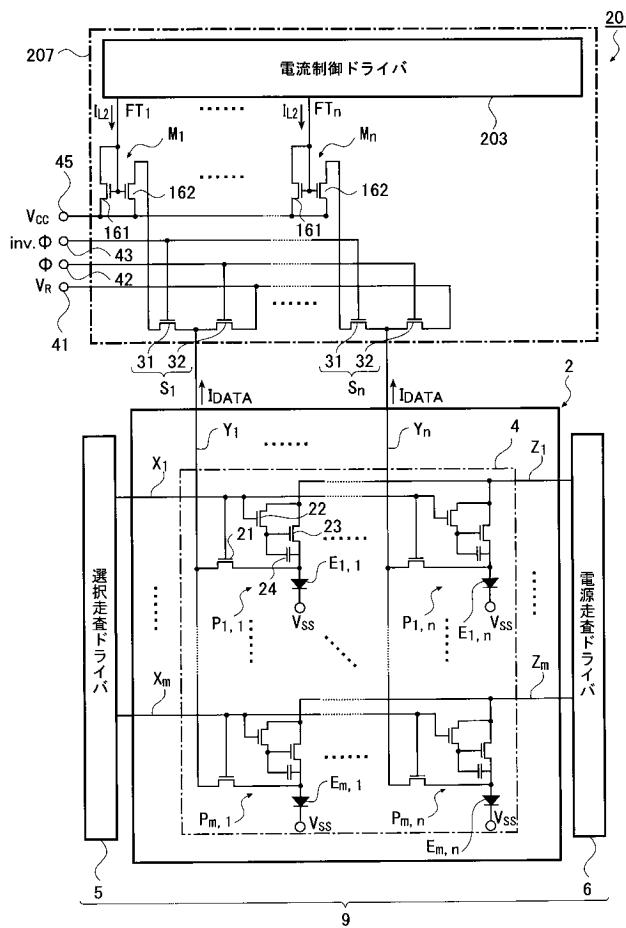

図 11 は、本発明の有機エレクトロルミネッセンスディスプレイを適用した第 3 の実施形態における有機エレクトロルミネッセンスディスプレイ 201 を示した図面である。図 11 に示すように、有機エレクトロルミネッセンスディスプレイ 201 において、第 1 の実施形態の有機エレクトロルミネッセンスディスプレイ 1 のいずれかの部分と同一の部分に対しては同一の符号を付し、同一の部分についての説明は省略する。

#### 【0112】

この有機エレクトロルミネッセンスディスプレイ 201 も、有機エレクトロルミネッセンスディスプレイ 1 と同様に、有機エレクトロルミネッセンス表示パネル 2 と、走査側駆動回路 9 と、データ側駆動回路 207 と、を備える。ここで、有機エレクトロルミネッセンス表示パネル 2 及び走査側駆動回路 9 は、第 1 の実施形態における有機エレクトロルミネッセンス表示パネル 2 及び走査側駆動回路 9 とそれぞれ同じである。但し、データ側駆動回路 207 は、第 1 の実施形態におけるデータ側駆動回路 7 と異なる。

#### 【0113】

このデータ側駆動回路 207 は、 $n$  個の電流端子  $FT_1 \sim FT_n$  を有するとともに電流端子  $FT_1 \sim FT_n$  それぞれに押込電流  $I_{L2}$  を流す電流制御ドライバ 203 と、電流端子  $FT_1 \sim FT_n$  に流れる押込電流  $I_{L2}$  を階調指定電流  $I_{DATA}$  に変換するカレントミラー回路  $M_1 \sim M_n$  と、信号線  $Y_1 \sim Y_n$  とカレントミラー回路  $M_1 \sim M_n$  との間に介在した切換部  $S_1 \sim S_n$  と、を備える。

#### 【0114】

第 2 の実施形態では、電流制御ドライバ 103 がカレントミラー回路  $M_1 \sim M_n$  からそれぞれの電流端子  $DT_1 \sim DT_n$  に向かった引抜電流  $I_{L1}$  を流すのに対して、第 3 の実施形態では、電流制御ドライバ 203 が電流端子  $FT_1 \sim FT_n$  からそれぞれのカレントミラー回路  $M_1 \sim M_n$  に向かった押込電流  $I_{L2}$  を流す。

カレントミラー回路  $M_1 \sim M_n$  は、二つの N チャネル型 MOS トランジスタ 161, 162 とから構成されている。トランジスタ 161 及びトランジスタ 162 は、画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ 21 ~ 23 と同じ工程によって製造されることが可能である。

何れのカレントミラー回路  $M_1 \sim M_n$  においても、トランジスタ 161 のゲートとドレイン及びトランジスタ 162 のゲートが互いに接続され、トランジスタ 161 のソース及びトランジスタ 162 のソースが定電圧入力端子 45 に接続されている。定電圧入力端子 45 には、定電圧  $V_{cc}$  が印加されている。定電圧  $V_{cc}$  は、階調指定電流用基準電圧  $V_{LOW}$  及び基準電圧  $V_{SS}$  よりも低レベルである。なお、第 1 の実施形態と同様に基準電圧  $V_{SS}$  又は階調指定電流用基準電圧  $V_{LOW}$  が 0 [V] である場合、定電圧  $V_{cc}$  は負電位である。

切換部  $S_j$  の一例について説明する。切換部  $S_j$  は、N チャネル型の電界効果トランジス

10

20

30

40

50

タ31, 32から構成される。トランジスタ31のゲートが切換信号入力端子43に接続され、切換信号  $i_{nv.}$  がトランジスタ31のゲートに入力される。また、トランジスタ32のゲートが切換信号入力端子42に接続され、切換信号  $i_{nv.}$  がトランジスタ32のゲートに入力される。トランジスタ31のドレインは信号線  $Y_j$  に接続されており、トランジスタ31のソースはトランジスタ162のドレインに接続されている。トランジスタ32のドレインは信号線  $Y_j$  に接続されている。トランジスタ32のソースはリセット入力端子41に接続され、定電圧であるリセット電圧  $V_R$  がトランジスタ32のソースに印加されている。この構成では、切換信号  $i_{nv.}$  がハイレベルであり切換信号  $i_{nv.}$  がローレベルである場合に、トランジスタ32がオン状態になり、トランジスタ31がオフ状態になる。一方、切換信号  $i_{nv.}$  がローレベルであり且つ切換信号  $i_{nv.}$  がハイレベルの場合に、トランジスタ31がオン状態になり、トランジスタ32がオフ状態になる。トランジスタ31及びトランジスタ32は、画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ21～23と同じ工程によって製造されることが可能である。リセット電圧  $V_R$  は、信号線  $Y_1 \sim Y_n$  の寄生容量に蓄積された電荷や画素電極51の寄生容量によって蓄積された電荷等を完全に放出するために0[V]であることが好ましい。

そして、電流制御ドライバ203は、各行の選択期間  $T_{SE}$  ごとに電流端子  $FT_1 \sim FT_n$  それぞれの押込電流  $I_{L2}$  の大きさを映像信号に従った大きさに制御し、それぞれのリセット期間  $T_R$  が終了してからその選択期間  $T_{SE}$  が終了するまでの間では押込電流  $I_{L2}$  の大きさを一定となるように制御する。ここで、電流制御ドライバ203が流す押込電流  $I_{L2}$  は、第1の実施形態における信号ドライバ3が流す階調指定電流  $I_{DATA}$  よりも大きく、電流制御ドライバ203が流す押込電流  $I_{L2}$  と第1の実施形態における信号ドライバ3が流す階調指定電流  $I_{DATA}$  との関係は比例関係にある。

#### 【0115】

トランジスタ161のチャネル抵抗はトランジスタ162のチャネル抵抗よりも小さい。そのため、カレントミラー回路  $M_1 \sim M_n$  は、それぞれの電流端子  $FT_1 \sim FT_n$  に流れる押込電流  $I_{L2}$  を階調指定電流  $I_{DATA}$  に変換する。ここで、階調指定電流  $I_{DATA}$  の大きさは、実質的に、トランジスタ161のチャネル抵抗に対するトランジスタ162のチャネル抵抗の比率にトランジスタ161のドレイン-ソース間の押込電流  $I_{L2}$  の大きさを乗じた値となる。そして、カレントミラー回路  $M_1 \sim M_n$  の出力側につまりトランジスタ162のドレインに階調指定電流  $I_{DATA}$  が流れるので、カレントミラー回路  $M_1 \sim M_n$  のトランジスタ162のドレインが、第1の実施形態における信号ドライバ3の電流端子  $CT_1 \sim CT_n$  にそれ相応する。つまり、カレントミラー回路  $M_1 \sim M_n$  と電流制御ドライバ203とを組み合わせた構成が第1の実施形態における信号ドライバ3に相当する。

#### 【0116】

本実施形態の切換信号  $i_{nv.}$  及び切換信号  $i_{nv.}$  のタイミングと選択走査ドライバ5及び電源走査ドライバ6が選択していくタイミングとの関係は、第1の実施形態の場合と同様である。また、本実施形態における選択走査ドライバ5及び電源走査ドライバ6の動作タイミングは、第1の実施形態のそれと同じである。従って、第3の実施形態においても、 $i$ 行目のリセット期間  $T_R$  では、画素回路  $D_{i,1} \sim D_{i,n}$  それぞれの第一トランジスタ21がオン状態となっているので、それぞれの有機EL素子  $E_{i,1} \sim E_{i,n}$  の画素電極51、 $i$ 行目の第一トランジスタ21のドレイン21d、 $i$ 行目のキャパシタ24の電極24B、 $i$ 行目の第三トランジスタ23のソース23s及び信号線  $Y_1 \sim Y_n$  の電圧が図4に示すようにリセット電圧  $V_R$  で定常状態となって前の選択期間  $T_{SE}$  中にこれらの寄生容量によって蓄積された電荷を放出するので、引き続き次の選択期間  $T_{SE}$  中に迅速且つ正確に階調指定電流  $I_{DATA}$  を書き込むことができる。

#### 【0117】

また、第3の実施形態でも、選択期間  $T_{SE}$  中にデータ側駆動回路207によってリセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されている。そのため、第一トランジスタ21が、画素回路  $D_{1,1} \sim D_{m,n}$  にリセット電圧  $V_R$  を取り込むスイッチング素子の機能と、画素回路  $D_{1,1} \sim D_{m,n}$  に階調指定電流  $I_{DATA}$  を取り込むためのスイッチング素子の機能と、を兼ね

10

20

30

40

50

ている。従って、画素回路  $D_{1,1} \sim D_{m,n}$  に必要なトランジスタの数が増えず、有機 E-L 素子  $E_{1,1} \sim E_{m,n}$  を画素回路  $D_{1,1} \sim D_{m,n}$  と同一面に作り込む場合、画素  $P_{1,1} \sim P_{m,n}$  の開口率の低下を防止することができる。

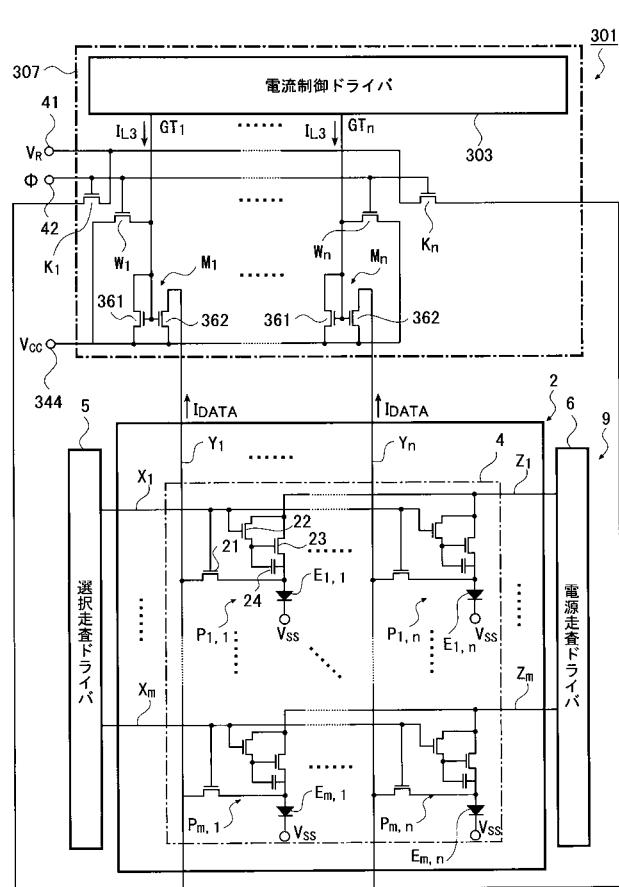

### 【0118】

#### [第4の実施の形態]

図12は、本発明の有機エレクトロルミネッセンスディスプレイを適用した第4の実施形態における有機エレクトロルミネッセンスディスプレイ301を示した図面である。図12に示すように、有機エレクトロルミネッセンスディスプレイ301において、第1の実施形態の有機エレクトロルミネッセンスディスプレイ1のいずれかの部分と同一の部分に対しては同一の符号を付し、同一の部分についての説明は省略する。

10

### 【0119】

この有機エレクトロルミネッセンスディスプレイ301も、有機エレクトロルミネッセンスディスプレイ1と同様に、有機エレクトロルミネッセンス表示パネル2と、走査側駆動回路9と、データ側駆動回路307と、を備える。ここで、有機エレクトロルミネッセンス表示パネル2及び走査側駆動回路9は、第3の実施形態における有機エレクトロルミネッセンス表示パネル2及び走査側駆動回路9とそれぞれ同じである。但し、データ側駆動回路307は、第1の実施形態におけるデータ側駆動回路7と異なる。

### 【0120】

このデータ側駆動回路307は、電流制御ドライバ303と、カレントミラー回路  $M_1 \sim M_n$  と、スイッチング素子  $K_1 \sim K_n$  と、切換部としてのスイッチング素子  $W_1 \sim W_n$  と、を備える。

20

### 【0121】

電流制御ドライバ303は、 $n$  個の電流端子  $G T_1 \sim G T_n$  を有する。電流制御ドライバ303には、8 bit のデジタル階調映像信号が入力される。電流制御ドライバ303に取り込まれたデジタル階調映像信号は、電流制御ドライバ303内のD/Aコンバータによってアナログ変換される。そして、電流制御ドライバ303は、アナログ変換された映像信号に従った大きさの押込電流  $I_{L3}$  を電流端子  $G T_1 \sim G T_n$  それぞれに発生させる。そして、電流制御ドライバ303は、各行の選択期間  $T_{SE}$  ごとに電流端子  $G T_1 \sim G T_n$  それぞれの押込電流  $I_{L3}$  の大きさを映像信号に従った大きさに制御し、それぞれのリセット期間  $T_R$  が終了してからその選択期間  $T_{SE}$  が終了するまでの間では押込電流の大きさを一定となるように制御する。ここで、電流制御ドライバ303が流す押込電流  $I_{L3}$  は、第1の実施形態における信号ドライバ3が流す階調指定電流  $I_{DATA}$  よりも大きく、電流制御ドライバ303が流す押込電流  $I_{L3}$  と後述するトランジスタ362に流れる階調指定電流  $I_{DATA}$  との関係は比例関係にある。

30

### 【0122】

カレントミラー回路  $M_1 \sim M_n$  は、それぞれの電流端子  $G T_1 \sim G T_n$  に流れる押込電流  $I_{L3}$  を階調指定電流  $I_{DATA}$  に変換するものである。何れのカレントミラー回路  $M_1 \sim M_n$  も二つのトランジスタ361, 362を有する。カレントミラー回路  $M_j$  においては、トランジスタ361のゲートがトランジスタ362のゲートに接続され、トランジスタ361のドレインが電流端子  $G T_j$  に接続されとともにトランジスタ362のゲート及びトランジスタ361のゲートに接続されている。トランジスタ362のドレインは信号線  $Y_j$  に接続されている。トランジスタ361のソース及びトランジスタ362のソースは共通の電圧端子344に接続されている。電圧端子344には、定電圧  $V_{cc}$  が印加されている。定電圧  $V_{cc}$  は、階調指定電流用基準電圧  $V_{LOW}$  及び基準電圧  $V_{SS}$  よりも低レベルである。なお、第1の実施形態と同様に基準電圧  $V_{SS}$  又は階調指定電流用基準電圧  $V_{LOW}$  が0[V]である場合、定電圧  $V_{cc}$  は負電位である。

40

### 【0123】

ここで、階調指定電流  $I_{DATA}$  の大きさは、実質的に、トランジスタ361のチャネル抵抗に対するトランジスタ362のチャネル抵抗の比率にトランジスタ361のドレイン-ソース間の押込電流  $I_{L3}$  の大きさを乗じた値となる。つまり、カレントミラー回路  $M_1 \sim$

50

$M_n$  と電流制御ドライバ 303 とを組み合わせた構成が信号ドライバに相当する。

【0124】

何れのスイッチング素子  $W_1 \sim W_n$  のドレインがそれぞれの電流端子  $G T_1 \sim G T_n$  及びそれぞれのカレントミラー回路  $M_1 \sim M_n$  のトランジスタ 361 のドレイン及びゲートに接続されている。スイッチング素子  $W_1 \sim W_n$  のソースが電圧端子 344 に接続されている。スイッチング素子  $W_1 \sim W_n$  のゲートは切換信号入力端子 42 に接続されている。スイッチング素子  $W_1 \sim W_n$  は、それぞれのカレントミラー回路  $M_1 \sim M_n$  のトランジスタ 361 のドレインに対して定電圧  $V_{cc}$  の印加の切換を行うものである。なお、スイッチング素子  $W_1 \sim W_n$  が電流制御ドライバ 303 に内蔵されていても良い。

【0125】

本実施形態の切換信号のタイミングと選択走査ドライバ 5 及び電源走査ドライバ 6 が選択していくタイミングとの関係は、第 1 の実施形態の場合と同様である。

【0126】

従って、 $i$  行目の選択期間  $T_{SE}$  のうち前半のリセット期間  $T_R$  では、トランジスタ  $W_1 \sim W_n$  がオン状態となることによって、トランジスタ 361 のソースとドレインが等電位になる。そのため、選択期間  $T_{SE}$  のうちリセット期間  $T_R$  の後において、信号線  $Y_1 \sim Y_n$  に対するカレントミラー回路  $M_1 \sim M_n$  の寄生容量の影響を除くことができる。

【0127】

何れのスイッチング素子  $K_1 \sim K_n$  においても、ドレインとソースのうちの一方がリセット入力端子 41 に接続され、ドレインとソースのうちの他方がそれぞれの信号線  $Y_1 \sim Y_n$  に接続され、ゲートが切換信号入力端子 42 に接続されている。スイッチング素子  $K_1 \sim K_n$  は、信号線  $Y_1 \sim Y_n$  に対してリセット電圧  $V_R$  の印加の切換を行うものである。ここで、リセット電圧  $V_R$  は 0 [V] に設定されている。なお、信号線  $Y_1 \sim Y_n$  とトランジスタ 362 との接続部の反対側において、スイッチング素子  $K_1 \sim K_n$  のドレインとソースのうちの他方が信号線  $Y_1 \sim Y_n$  に接続されており、スイッチング素子  $K_1 \sim K_n$  が有機エレクトロルミネッセンス表示パネル 2 に形成されていても良い。

【0128】

そして、 $i$  行目の選択期間  $T_{SE}$  のうち前半のリセット期間  $T_R$  では、スイッチング素子  $K_1 \sim K_n$  がオン状態となることによって、画素電極 51 並びにそれぞれの信号線  $Y_1 \sim Y_n$  が、リセット入力端子 41 に電気的に導通して接地されたリセット電圧  $V_R$  が印加されているため、 $i$  行目のリセット期間  $T_R$  の開始してすぐに、信号線  $Y_1 \sim Y_n$  の寄生容量に蓄積された電荷、画素電極 51 の寄生容量に蓄積された電荷、キャパシタ 24 の電極 24B の寄生容量に蓄積された電荷、及び第 2 トランジスタ 23 のソースの寄生容量に蓄積された電荷を除去する。そのため、正確且つ迅速に微小電流値の階調指定電流  $I_{DATA}$  を流すことができる。リセット期間  $T_R$  後には、スイッチング素子  $K_1 \sim K_n$  及びスイッチング素子  $W_1 \sim W_n$  がオフ状態になり、電流制御ドライバ 303 の電流端子  $G T_1 \sim G T_n$  に階調に応じた電流値の電流が流れ、カレントミラー回路  $M_1 \sim M_n$  によって変調された階調指定電流  $I_{DATA}$  が信号線  $Y_1 \sim Y_n$  及び第三トランジスタ 23 に流れることになる。

【0129】

また、第 4 の実施形態でも、選択期間  $T_{SE}$  中にデータ側駆動回路 307 によってリセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されている。そのため、第一トランジスタ 21 が、画素回路  $D_{1,1} \sim D_{m,n}$  にリセット電圧  $V_R$  を取り込むスイッチング素子の機能と、画素回路  $D_{1,1} \sim D_{m,n}$  に階調指定電流  $I_{DATA}$  を取り込むためのスイッチング素子の機能と、を兼ねている。従って、画素回路  $D_{1,1} \sim D_{m,n}$  に必要なトランジスタの数が増えず、有機 E-L 素子  $E_{1,1} \sim E_{m,n}$  を画素回路  $D_{1,1} \sim D_{m,n}$  と同一面に作り込む場合、画素  $P_{1,1} \sim P_{m,n}$  の開口率の低下を防止することができる。

【0130】

なお、本発明は、上記実施の形態に限定されることなく、本発明の趣旨を逸脱しない範囲において、種々の改良並びに設計の変更を行っても良い。

例えば、上記各実施の形態では発光素子として有機 E-L 素子を用いているが、整流性の

ある他の発光素子を用いても良い。つまり、逆バイアス電圧が印加された場合には電流が流れないとともに順バイアス電圧が印加された場合には電流が流れるような発光素子であって、流れる電流の大きさに従った輝度で発光する発光素子であっても良い。整流性のある発光素子としては、例えばLED (Light Emitting Diode) 素子が挙げられる。

また電源走査ドライバ6の階調指定電流用基準電圧V<sub>LOW</sub>は、選択期間T<sub>SE</sub>中に有機EL素子に階調指定電流I<sub>DATA</sub>の一部又は全部が流れなければ、図4に示す最高輝度階調時のEL負荷線よりも右側に位置してもよい。

【図面の簡単な説明】

【0131】

【図1】本発明を適用した第1の実施形態における有機エレクトロルミネッセンスディスプレイ1のプロック図である。 10

【図2】有機エレクトロルミネッセンスディスプレイ1の画素P<sub>i,j</sub>の平面図である。

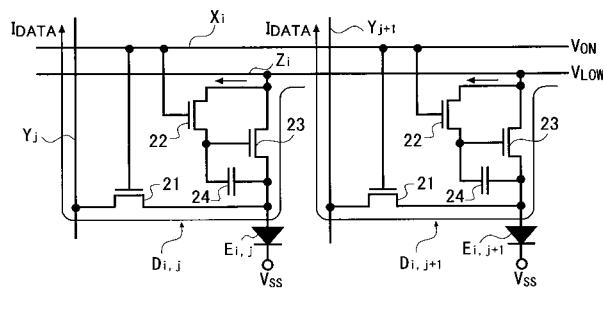

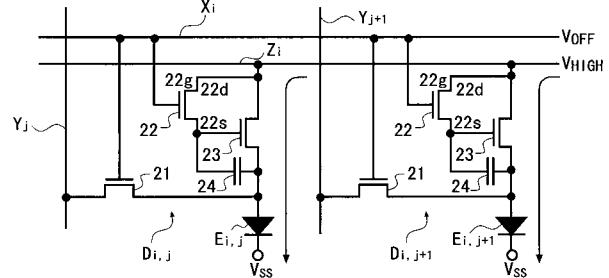

【図3】有機エレクトロルミネッセンスディスプレイ1の隣接する四つの画素P<sub>i,j</sub>, P<sub>i+1,j</sub>, P<sub>i,j+1</sub>, P<sub>i+1,j+1</sub>の等価回路図である。

【図4】有機エレクトロルミネッセンスディスプレイ1における信号のレベルを示したタイミングチャート。 20

【図5】Nチャネル型の電界効果トランジスタの電流-電圧特性を表したグラフである。

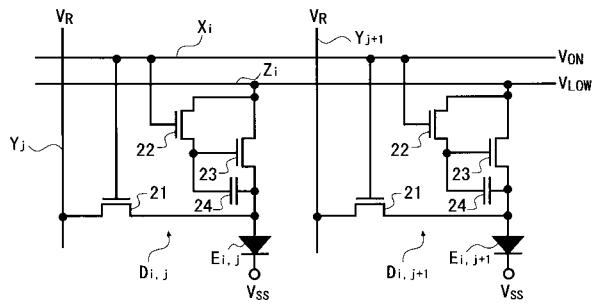

【図6】i行目の隣り合う二つの画素P<sub>i,j</sub>, P<sub>i,j+1</sub>の等価回路図とともに、i行目のリセット期間T<sub>R</sub>の電流、電圧の状態を示した図である。 30

【図7】i行目の隣り合う二つの画素P<sub>i,j</sub>, P<sub>i,j+1</sub>の等価回路図とともに、i行目の選択期間T<sub>SE</sub>のうちリセット期間T<sub>R</sub>の後の電流、電圧の状態を示した図である。

【図8】i行目の隣り合う二つの画素P<sub>i,j</sub>, P<sub>i,j+1</sub>の等価回路図とともに、i行目の非選択期間T<sub>NSE</sub>の電流、電圧の状態を示した図である。

【図9】画素P<sub>i,j</sub>に関連する電流、電圧のレベルを示したタイミングチャートである。

【図10】本発明を適用した第2の実施形態における有機エレクトロルミネッセンスディスプレイ101のプロック図である。 30

【図11】本発明を適用した第3の実施形態における有機エレクトロルミネッセンスディスプレイ201のプロック図である。

【図12】本発明を適用した第4の実施形態における有機エレクトロルミネッセンスディスプレイ301のプロック図である。 40

【符号の説明】

【0132】

1、101、201、301 ... 有機エレクトロルミネッセンスディスプレイ(表示装置)

2 ... 有機エレクトロルミネッセンス表示パネル(表示パネル)

3 ... 信号ドライバ

5 ... 選択走査ドライバ

6 ... 電源走査ドライバ

7、107、207、307 ... データ側駆動回路

21 ... 第一トランジスタ

22 ... 第二トランジスタ

23 ... 第三トランジスタ

E<sub>1,1</sub> ~ E<sub>m,n</sub> ... 有機EL素子(発光素子)

K<sub>1</sub> ~ K<sub>n</sub> ... スイッチング素子(切換部)

S<sub>1</sub> ~ S<sub>n</sub> ... 切換部

Y<sub>1</sub> ~ Y<sub>n</sub> ... 信号線

X<sub>1</sub> ~ X<sub>n</sub> ... 選択走査線

Z<sub>1</sub> ~ Z<sub>n</sub> ... 電源走査線

P<sub>1,1</sub> ~ P<sub>m,n</sub> ... 画素

D<sub>1,1</sub> ~ D<sub>m,n</sub> ... 画素回路

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

## フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/20 6 4 2 A

H 0 5 B 33/14 A

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，数据侧驱动电路和驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005202209A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2005-07-28 |

| 申请号            | JP2004009146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2004-01-16 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 白寄友之<br>佐藤和仁                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 白寄 友之<br>佐藤 和仁                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/325 G09G2300/0417 G09G2300/0842 G09G2300/0866 G09G2310/0248 G09G2310/0256<br>G09G2320/0223 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.622.B G09G3/20.623.B G09G3/20.624.B G09G3/20.642.A<br>H05B33/14.A G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD05 5C080<br>/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 3K107/AA01 3K107<br>/BB01 3K107/CC31 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AA03 5C380/AB06<br>5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB34 5C380/BA13 5C380/BA19 5C380/BA38 5C380<br>/BA39 5C380/BA40 5C380/BB02 5C380/BB15 5C380/BB16 5C380/BB22 5C380/BC18 5C380/BD02<br>5C380/BD05 5C380/CA04 5C380/CA08 5C380/CA13 5C380/CA30 5C380/CA34 5C380/CA49 5C380<br>/CA53 5C380/CB01 5C380/CB16 5C380/CB20 5C380/CB26 5C380/CC13 5C380/CC27 5C380/CC30<br>5C380/CC33 5C380/CC41 5C380/CC52 5C380/CC62 5C380/CD013 5C380/CE05 5C380/CF26 5C380<br>/DA02 5C380/DA06 5C380/DA47 5C380/HA13 |         |            |

| 其他公开文献         | JP4203656B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

## 摘要(译)

解决的问题：提供一种能够执行高质量显示的显示装置，数据侧驱动电路和显示面板驱动方法。在由数据侧驱动电路7驱动的有机电致发光显示面板2中，选择扫描驱动器5和电源扫描驱动器6以矩阵形式布置像素P我，并且布置像素P我。)包括有机EL元件E我和像素电路D我。当通过选择性扫描驱动器5选择像素电路D我时，将复位电压V[R施加到信号线Y<sub>J</sub>。之后，在选择了像素电路D我的状态下，像素电路D我保持与在晶体管23中的信号线Y<sub>J</sub>中流动的灰度指定电流的大小对应的电平的电压。。。当解除对像素电路D我的选择时，像素电路D我将具有根据晶体管23的电压电平的大小的驱动电流提供给有机EL元件E我。[选型图1图

1