(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-148750

(P2005-148750A)

(43) 公開日 平成17年6月9日(2005.6.9)

(51) Int.Cl.<sup>7</sup>

**G09G 3/30**

**G09G 3/20**

**G09G 3/22**

**G09G 3/28**

**H05B 33/14**

F 1

G09G 3/30 J 3K007

G09G 3/20 611F 5C080

G09G 3/20 611J

G09G 3/20 621A

G09G 3/20 621J

テーマコード(参考)

審査請求有 請求項の数 44 O L (全 30 頁) 最終頁に続く

(21) 出願番号

特願2004-330894 (P2004-330894)

(22) 出願日

平成16年11月15日 (2004.11.15)

(31) 優先権主張番号

2003-080739

(32) 優先日

平成15年11月14日 (2003.11.14)

(33) 優先権主張国

韓国 (KR)

(71) 出願人 590002817

三星エスディアイ株式会社

大韓民国京畿道水原市靈通区▲しん▼洞5

75番地

(74) 代理人 100095957

弁理士 龟谷 美明

(74) 代理人 100096389

弁理士 金本 哲男

(72) 発明者 郭 源奎

大韓民国京畿道城南市盆唐区九美洞88番

地 カチ住公アパート207-903

F ターム(参考) 3K007 AB02 AB17 AB18 BA06 DB03

GA00

最終頁に続く

(54) 【発明の名称】表示装置のピクセル回路、表示装置、及びその駆動方法

## (57) 【要約】

【課題】 高精細化、開口率、収率を向上させ、R C ディレイ及び電圧降下を防止し、画素構成及び配線を単純化することができる表示装置のピクセル回路及びその駆動方法を提供する。

【解決手段】 有機電界発光表示装置は、所定区間ごとに所定の色を具現する表示装置のピクセル回路において、所定区間内でそれぞれ一つの色を放出する複数の発光素子(E L 1\_R, E L 1\_G, E L 1\_B)と、これらの発光素子に共通連結されて、各発光素子を駆動するための能動素子(540, 550)を備えている。能動素子は所定区間内で所定期間ごとに各発光素子を順次に駆動し、これによって各発光素子は、所定期間ごとに順次に発光する。

【選択図】 図10

**【特許請求の範囲】****【請求項 1】**

所定区間ごとに所定の色を具現する表示装置のピクセル回路であって，

前記所定区間内で発光する複数の発光素子と，

前記複数の発光素子に共通接続され，前記複数の発光素子を駆動する能動素子と，

を具備し，

前記能動素子は，前記所定区間内の所定期間ごとに，前記複数の発光素子を順に駆動させ，

前記複数の発光素子は，前記所定期間ごとに発光することを特徴とする，表示装置のピクセル回路。

10

**【請求項 2】**

前記所定区間は，一つのフレームであり，前記所定期間は，サブフレームであり，

前記フレームは，複数のサブフレームで構成され，

前記複数の発光素子は，前記サブフレームごとに，順に駆動されることを特徴とする，

請求項 1 に記載の表示装置のピクセル回路。

**【請求項 3】**

前記複数の発光素子のうち少なくとも一つの発光素子は，前記複数のサブフレームのうち二つ以上のサブフレームにおいて発光することを特徴とする，請求項 2 に記載の表示装置のピクセル回路。

**【請求項 4】**

前記複数のサブフレームのうちいずれかのサブフレームでは二つ以上の前記発光素子が発光することを特徴とする，請求項 2 または 3 に記載の表示装置のピクセル回路。

20

**【請求項 5】**

前記複数の発光素子の各発光時間を調節して，全体のホワイトバランスを調節することを特徴とする，請求項 1 ~ 4 のいずれかに記載の表示装置のピクセル回路。

**【請求項 6】**

前記各発光素子は，発光ダイオードまたはプラズマ発光素子であることを特徴とする，請求項 1 ~ 5 のいずれかに記載の表示装置のピクセル回路。

**【請求項 7】**

前記各発光素子は，電界発光素子であることを特徴とする，請求項 1 ~ 5 のいずれかに記載の表示装置のピクセル回路。

30

**【請求項 8】**

前記複数の発光素子の各第 1 電極は，前記能動素子に接続され，前記複数の発光素子の各第 2 電極は，接地されることを特徴とする，請求項 1 ~ 7 のいずれかに記載の表示装置のピクセル回路。

**【請求項 9】**

前記複数の発光素子は，ストライプタイプまたはデルタタイプに配列されることを特徴とする，請求項 1 ~ 8 のいずれかに記載の表示装置のピクセル回路。

**【請求項 10】**

前記能動素子は，前記複数の発光素子を駆動するための一つ以上のスイッチング素子で構成されることを特徴とする，請求項 1 ~ 9 のいずれかに記載の表示装置のピクセル回路。

40

**【請求項 11】**

前記スイッチング素子は，トランジスタ，薄膜ダイオード，ダイオード，または T R S で構成されることを特徴とする，請求項 10 に記載の表示装置のピクセル回路。

**【請求項 12】**

赤色電界発光素子と，

緑色電界発光素子と，

青色電界発光素子と，

データ信号を伝達する 1 または 2 以上のスイッチングトランジスタと，

50

少なくとも 2 つの発光制御信号によってオン / オフ制御され、前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子が共通接続され、前記データ信号によって、前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子を発光させる 1 または 2 以上の駆動トランジスタと、

前記データ信号を貯蔵する貯蔵素子と、

を具備することを特徴とする、表示装置のピクセル回路。

**【請求項 13】**

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子は、一つのフレームを構成する複数のサブフレームそれぞれにおいて、順に駆動されることを特徴とする、表示装置のピクセル回路。 10

**【請求項 14】**

前記複数のサブフレームのうちいずれかのサブフレームでは、前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子のうちの少なくとも二つが駆動されることを特徴とする、請求項 13 に記載の表示装置のピクセル回路。

**【請求項 15】**

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子の各発光時間を調節して、全体のホワイトバランスを調節することを特徴とする、請求項 12 ~ 14 のいずれかに記載の表示装置のピクセル回路。 20

**【請求項 16】**

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子の各第 1 電極は、前記駆動トランジスタに共通接続され、前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子の第 2 電極は、接地されることを特徴とする、請求項 12 ~ 15 のいずれかに記載の表示装置のピクセル回路。 20

**【請求項 17】**

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子は、ストライプタイプまたはデルタタイプで配列されることを特徴とする、請求項 12 ~ 16 のいずれかに記載の表示装置のピクセル回路。 20

**【請求項 18】**

赤色電界発光素子と、

緑色電界発光素子と、

青色電界発光素子と、

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子が共通接続され、前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子を駆動する駆動手段と、

前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子の駆動を制御する制御手段と、

を含むことを特徴とする、表示装置のピクセル回路。 30

**【請求項 19】**

前記駆動手段は、

データ信号をスイッチングする 1 または 2 以上のスイッチングトランジスタと、

前記データ信号に対応する駆動電流を前記赤色電界発光素子、前記緑色電界発光素子、及び前記青色電界発光素子に供給する 1 または 2 以上の駆動トランジスタと、

前記データ信号を貯蔵するキャパシタと、

を含むことを特徴とする、請求項 18 に記載の表示装置のピクセル回路。 40

**【請求項 20】**

前記駆動手段は、前記駆動トランジスタのスレッショルド電圧を補償するためのスレッショルド電圧補償手段をさらに含むことを特徴とする、請求項 19 に記載の表示装置のピクセル回路。 50

**【請求項 21】**

前記駆動トランジスタとキャパシタには、共通の電源ラインを通じて同一の電源電圧が

供給される，または，個別の電源ラインを通じて同一若しくは別個の電源電圧が供給されることを特徴とする，請求項19または20に記載の表示装置のピクセル回路。

#### 【請求項22】

前記制御手段は，

発光制御信号に応じて前記駆動トランジスタが出力する駆動電流を前記赤色電界発光素子に与える第1制御手段と，

前記発光制御信号に応じて前記駆動トランジスタが出力する駆動電流を前記緑色電界発光素子に与える第2制御手段と，

前記発光制御信号に応じて前記駆動トランジスタが出力する駆動電流を前記青色電界発光素子に与える第3制御手段と，

を含むことを特徴とする，請求項18～21のいずれかに記載の表示装置のピクセル回路。

#### 【請求項23】

前記発光制御信号は，第1発光制御信号と第2発光制御信号を含み，

前記第1制御手段は，前記駆動手段と前記赤色電界発光素子との間に直列に接続され，前記第1発光制御信号と前記第2発光制御信号によってオン／オフ制御される少なくとも2つのトランジスタで構成され，

前記第2制御手段は，前記駆動手段と前記緑色電界発光素子との間に直列に接続され，前記第1発光制御信号と前記第2発光制御信号によってオン／オフ制御される少なくとも2つのトランジスタで構成され，

前記第3制御手段は，前記駆動手段と前記青色電界発光素子との間に直列に接続され，前記第1発光制御信号と前記第2発光制御信号によってオン／オフ制御される少なくとも2つのトランジスタで構成されたことを特徴とする，請求項22に記載の発光表示装置のピクセル回路。

#### 【請求項24】

前記発光制御信号のアクティブオン時間を調整することによって，全体のホワイトバランスを調節することを特徴とする，請求項22または請求項23に記載の発光表示装置のピクセル回路。

#### 【請求項25】

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子は，ストライプタイプまたはデルタタイプで配列されることを特徴とする，請求項18～24のいずれかに記載の表示装置のピクセル回路。

#### 【請求項26】

制御端がゲートラインに接続され，第1電源端がデータラインに接続された第1トランジスタと，

制御端が前記第1トランジスタの第2電源端に接続され，第1電源端が電源ラインに接続された第2トランジスタと，

前記第2トランジスタの制御端と前記電源ラインとの間に接続されたキャパシタと，

第1電源端が前記第2トランジスタの第2電源端に接続され，制御端が第1発光制御信号の伝送ラインに接続された第3トランジスタと，

第1電源端が前記第3トランジスタの第2電源端に接続され，制御端が第2発光制御信号の伝送ラインに接続された第4トランジスタと，

第1電源端が前記第2トランジスタの第2電源端に接続され，制御端が第1発光制御信号の伝送ラインに接続された第5トランジスタと，

第1電源端が前記第5トランジスタの第2電源端に接続され，制御端が第2発光制御信号の伝送ラインに接続された第6トランジスタと，

第1電源端が前記第2トランジスタの第2電源端に接続され，制御端が第1発光制御信号の伝送ラインに接続された第7トランジスタと，

第1電源端が前記第7トランジスタの第2電源端に接続され，制御端が第2発光制御信号の伝送ラインに接続された第8トランジスタと，

10

20

30

40

50

第1電極が前記第4トランジスタの第2電源端に接続され，第2電極が接地された赤色電界発光素子と，

第1電極が前記第6トランジスタの第2電源端に接続され，第2電極が接地された緑色電界発光素子と，

第1電極が前記第8トランジスタの第2電源端に接続され，第2電極が接地された青色電界発光素子と，

を含むことを特徴とする，表示装置のピクセル回路。

#### 【請求項27】

所定区間内でそれぞれ一つの色を放出する複数の発光素子を備える複数の画素を含み，

前記複数の発光素子は，前記所定区間内で時分割的に順次駆動され一つの色を放出して

10 前記各画素は，前記所定区間内で所定の色を具現することを特徴とする，表示装置。

#### 【請求項28】

前記所定区間は，一つのフレームであり，

前記フレームは，複数のサブフレームで構成され，

前記複数の発光素子は，前記サブフレームごとに，順次駆動されることを特徴とする，

請求項27に記載の表示装置。

#### 【請求項29】

前記複数の発光素子のうち少なくとも一つの発光素子は，前記複数のサブフレームのうち二つ以上のサブフレームにおいて発光する，及び／又は，前記複数のサブフレームのうちいずれかのサブフレームでは二つ以上の発光素子が発光することを特徴とする，請求項

20 27または28に記載の表示装置。

#### 【請求項30】

前記複数の発光素子の各発光時間を調節して，全体のホワイトバランスを調節することを特徴とする，請求項27～29のいずれかに記載の表示装置。

#### 【請求項31】

所定区間ににおいて，それぞれ発光する複数の発光素子を備える複数の画素を含み，

前記複数の発光素子は，前記所定区間に設定された複数の所定期間ににおいて一つずつ発光して，前記各画素は，前記所定区間内で所定の色を具現することを特徴とする，表示装置。

#### 【請求項32】

前記所定区間は，一つのフレームであり，前記所定期間は，サブフレームであり，

前記1フレームは，複数のサブフレームで構成され，

前記複数の発光素子は，前記サブフレームごとに，順に駆動されることを特徴とする，

請求項31に記載の表示装置。

#### 【請求項33】

前記複数の発光素子のうち少なくとも一つの発光素子は，前記複数のサブフレームのうち二つ以上のサブフレームにおいて発光することを特徴とする，請求項31または32に記載の表示装置。

#### 【請求項34】

前記複数の発光素子の各発光時間を調節して，全体のホワイトバランスを調節することを特徴とする，請求項31～33のいずれかに記載の表示装置。

#### 【請求項35】

一方の電極が接地されている赤色電界発光素子と，

一方の電極が接地されている緑色電界発光素子と，

一方の電極が接地されている青色電界発光素子と，

前記赤色電界発光素子の他方の電極，前記緑色電界発光素子の他方の電極，及び前記青色電界発光素子の他方の電極が共通接続され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を駆動する少なくとも一つのトランジスタと，

を具備する複数の画素を含むことを特徴とする，表示装置。

#### 【請求項36】

10

20

30

40

50

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子は，少なくとも三つのサブフレームで構成されるフレーム内において，前記各サブフレームごと順に駆動されることを特徴とする，表示装置。

**【請求項 3 7】**

前記各画素は，ストライプタイプまたはデルタタイプで配列されることを特徴とする，請求項 3 5 または 3 6 に記載の表示装置。

**【請求項 3 8】**

複数のゲートラインと，

複数のデータラインと，

複数の電源ラインと，

前記複数のゲートライン，前記複数のデータライン，及び前記複数の電源ラインのうち，対応する一つ以上のゲートライン，データライン，及び電源ラインに接続される複数の画素と，

を含み，

前記各画素は，

赤色電界発光素子と，

緑色電界発光素子と，

青色電界発光素子と，

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子が共通接続され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を駆動する少なくとも一つのトランジスタと，

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子と，前記トランジスタとの間に配置され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を，複数のサブフレームで構成される一つのフレーム内で前記サブフレームごとに順に発光するように制御する発光制御用トランジスタと，

を含むことを特徴とする，表示装置。

**【請求項 3 9】**

複数のゲートラインと，

複数のデータラインと，

複数の電源ラインと，

前記複数のゲートライン，前記複数のデータライン，及び前記複数の電源ラインのうち，対応する一つのゲートライン，データライン，及び電源ラインに接続される複数の画素と，

を含み，

前記各画素は，

制御端が前記ゲートラインに接続され，第 1 電源端が前記データラインに接続された第 1 トランジスタと，

制御端が前記第 1 トランジスタの第 2 電源端に接続され，第 1 電源端が電源ラインに接続された第 2 トランジスタと，

前記第 2 トランジスタの制御端と前記電源ラインとの間に接続されたキャパシタと，

第 1 電源端が前記第 2 トランジスタの第 2 電源端に接続され，制御端が第 1 発光制御信号の伝送ラインに接続された第 3 トランジスタと，

第 1 電源端が前記第 3 トランジスタの第 2 電源端に接続され，制御端が第 2 発光制御信号の伝送ラインに接続された第 4 トランジスタと，

第 1 電源端が前記第 2 薄膜トランジスタの第 2 電源端に接続され，制御端が第 1 発光制御信号の伝送ラインに接続された第 5 トランジスタと，

第 1 電源端が前記第 5 トランジスタの第 2 電源端に接続され，制御端が第 2 発光制御信号の伝送ラインに接続された第 6 トランジスタと，

第 1 電源端が前記第 2 トランジスタの第 2 電源端に接続され，制御端が第 1 発光制御信号の伝送ラインに接続された第 7 トランジスタと，

10

20

30

40

50

第1電源端が前記第7トランジスタの第2電源端に接続され，制御端が第2発光制御信号の伝送ラインに接続された第8トランジスタと，

第1電極が前記第4トランジスタの第2電源端に接続され，第2電極が接地された赤色電界発光素子と，

第1電極が前記第6トランジスタの第2電源端に接続され，第2電極が接地された緑色電界発光素子と，

第1電極が前記第8トランジスタの第2電源端に接続され，第2電極が接地された青色電界発光素子と，

を含むことを特徴とする，表示装置。

#### 【請求項40】

複数のゲートライン，複数のデータライン，複数の発光制御ライン，及び複数の電源ライン，並びに，前記複数のゲートライン，前記複数のデータライン，前記複数の発光制御ライン，及び前記複数の電源ラインのうち，対応する一つ以上のゲートライン，データライン，発光制御ライン，及び電源ラインにそれぞれ接続される複数の画素を具備する画素部と，

前記複数のゲートラインを通じてスキャン信号を供給する少なくとも一つのゲートライン駆動回路と，

前記複数のデータラインを通じてデータ信号を供給する少なくとも一つのデータライン駆動回路と，

前記複数の発光制御ラインを通じて発光制御信号を供給する少なくとも一つの発光制御信号発生回路と，

を具備し，

前記各画素は，

赤色電界発光素子と，

緑色電界発光素子と，

青色電界発光素子と，

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子が共通接続され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を駆動する少なくとも一つのトランジスタと，

前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子と，前記トランジスタとの間に配置され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を，複数のサブフレームで構成される一つのフレーム内で前記サブフレームごとに順に発光するように制御する発光制御用トランジスタと，

を含むことを特徴とする，表示装置。

#### 【請求項41】

前記ゲートライン駆動回路，前記データライン駆動回路，及び前記発光制御信号発生回路は，冗長機能を有することを特徴とする，請求項40に記載の表示装置。

#### 【請求項42】

複数のゲートライン，複数のデータライン，及び複数の電源ラインと，

前記複数のゲートライン，前記複数のデータライン，及び前記複数の電源ラインのうち，対応する一つのゲートライン，データライン，及び電源ラインにそれぞれ接続され，それぞれ少なくとも赤色電界発光素子，緑色電界発光素子，及び青色電界発光素子を備えた複数の画素と，

を含む表示装置の駆動方法であって，

所定区間を構成する複数の所定期間ごとに，一のデータラインを通じて前記各画素にデータ信号が順に提供され，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子が時分割的に順に駆動されることによって，前記所定区間内で所定の色を表現することを特徴とする，表示装置の駆動方法。

#### 【請求項43】

複数のゲートライン，複数のデータライン，及び複数の電源ラインと，

10

20

30

40

50

前記複数のゲートライン，前記複数のデータライン，及び前記複数の電源ラインのうち，対応する一つのゲートライン，データライン，及び電源ラインにそれぞれ接続され，それぞれ少なくとも赤色電界発光素子，緑色電界発光素子，及び青色電界発光素子を備えた複数の画素と，

を含む表示装置の駆動方法であつて，

前記複数のゲートラインのうち，一のゲートラインに対して，所定区間内の所定期間にごとにスキャン信号を与えること，

前記スキャン信号が前記一のゲートラインに与えられるたびに，前記複数のデータラインのうち，一のデータラインに対して，データ信号を与えて，駆動電流を発生させること，

10 発光制御信号に応じて，前記一のゲートラインに接続された画素に含まれる赤色電界発光素子，緑色電界発光素子，及び青色電界発光素子に対して前記駆動電流を与えて，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子を駆動すること，を特徴とする，表示装置の駆動方法。

#### 【請求項 4 4】

前記所定区間は，三つの所定期間を含み，

前記三つの所定期間ににおいて，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子は一つずつ発光し，

前記所定区間ににおいて，前記赤色電界発光素子，前記緑色電界発光素子，及び前記青色電界発光素子は，順に発光することを特徴とする，請求項 4 2 または 4 3 に記載の表示装置の駆動方法。20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は，表示装置のピクセル回路，表示装置，及びその駆動方法に関する。

##### 【背景技術】

##### 【0 0 0 2】

最近，携帯用情報機器には，軽量，薄型などの特性に優れた液晶表示装置（LCD）や有機電界発光表示装置（OLED：Organic Light Emission Diode）などがよく使用されている。有機電界発光表示装置は，液晶表示装置に比べて輝度特性及び視野角特性が優れているため次世代平板表示装置として注目を浴びている。30

##### 【0 0 0 3】

通常，アクティブマトリクス有機電界発光表示装置において，一つの画素は，R，G，B 単位画素で構成されており，各 R，G，B 単位画素は，EL 素子を有する。各 EL 素子は，アノード電極とカソード電極との間に各 R，G，B 有機発光層を備えている。そして，アノード電極とカソード電極に印加される電圧により，R，G，B 有機発光層から光が出射される。

##### 【0 0 0 4】

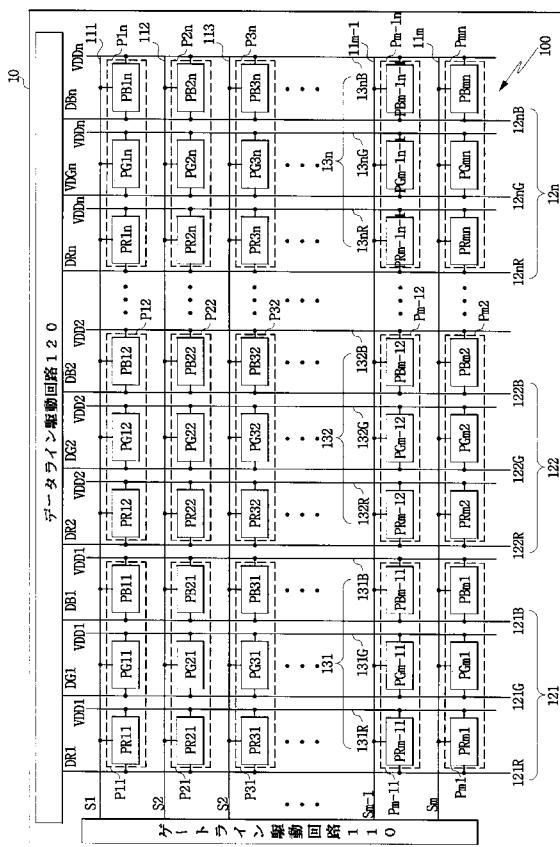

図 1 は，従来のアクティブマトリクス有機電界発光表示装置 10 の構成を示している。

##### 【0 0 0 5】

従来のアクティブマトリクス有機電界発光表示装置 10 は，画素部 100，ゲートライン駆動回路 110，データライン駆動回路 120，及び制御部（図示せず）を備える。画素部 100 は，ゲートライン駆動回路 110 からスキャン信号 S<sub>1</sub> ~ S<sub>m</sub> が提供される多数のゲートライン 111 ~ 11m と，データライン駆動回路 120 からデータ信号 D<sub>R1</sub>，D<sub>G1</sub>，D<sub>B1</sub>，…，D<sub>Rn</sub>，D<sub>Gn</sub>，D<sub>Bn</sub> を提供するための多数のデータライン 121 ~ 12n，及び電源電圧 V<sub>DD1</sub> ~ V<sub>DDn</sub> を提供する多数の電源ライン 131 ~ 13n を備える。40

##### 【0 0 0 6】

画素部 100 には，多数のゲートライン 111 ~ 11m，多数のデータライン 121 ~ 12n，及び多数の電源ライン 131 ~ 13n に連結される多数の画素 P<sub>11</sub> ~ P<sub>mn</sub> が

マトリクス形態で配列されている。各画素 P<sub>11</sub> ~ P<sub>m n</sub> は、三つの単位画素、つまり R, G, B 単位画素 P<sub>R11</sub>, P<sub>G11</sub>, P<sub>B11</sub>, ..., P<sub>Rmn</sub>, P<sub>Gmn</sub>, P<sub>Bmn</sub> で構成されており、多数のゲートライン、データライン、及び電源供給ラインのうち、対応する一つのゲートライン、データライン、及び電源供給ラインにそれぞれ接続されている。

#### 【 0 0 0 7 】

例えば、画素 P<sub>11</sub> は、R 単位画素 P<sub>R11</sub>, G 単位画素 P<sub>G11</sub>, B 単位画素 P<sub>B11</sub> を備え、多数のゲートライン 111 ~ 11m の中の第 1 スキャン信号 S<sub>1</sub> を提供する第 1 ゲートライン 111, 多数のデータライン 121 ~ 12n の中の第 1 データライン 121, そして多数の電源ライン 131 ~ 13n の中の第 1 電源ライン 131 に接続されている。10

#### 【 0 0 0 8 】

すなわち、画素 P<sub>11</sub> に備えられた R 単位画素 P<sub>R11</sub> は、第 1 ゲートライン 111 と、第 1 データライン 121 の中の R データ信号 D<sub>R1</sub> が提供される R データライン 121 R, 及び第 1 電源ライン 131 の中の R 電源ライン 131 R に接続されている。また、画素 P<sub>11</sub> に備えられた G 単位画素 P<sub>G11</sub> は、第 1 ゲートライン 111 と、第 1 データライン 121 の中の G データ信号 D<sub>G1</sub> が提供される G データライン 121 G, 及び第 1 電源ライン 131 の中の G 電源ライン 131 G に接続されている。また、画素 P<sub>11</sub> に備えられた B 単位画素 P<sub>B11</sub> は、第 1 ゲートライン 111 と、第 1 データライン 121 の中の B データ信号 D<sub>B1</sub> が提供される B データライン 121 B, 及び第 1 電源ライン 131 の中の B 電源ライン 131 B に接続されている。20

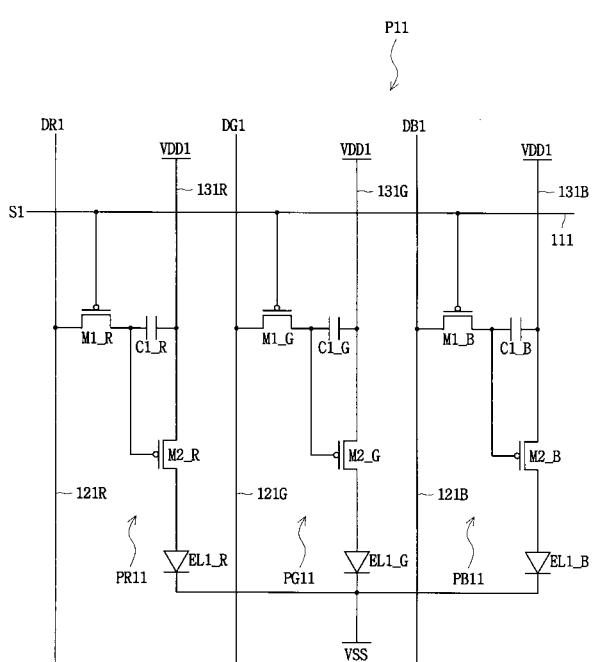

#### 【 0 0 0 9 】

図 2 は、従来の有機電界発光表示装置 10 が備えるピクセル回路を示したものである。このピクセル回路とは、図 1 に示した R, G, B 単位画素で構成される一つの画素 P<sub>11</sub> の回路に対応するものである。

#### 【 0 0 1 0 】

画素 P<sub>11</sub> を構成する R, G, B 単位画素 P<sub>R11</sub>, P<sub>G11</sub>, P<sub>B11</sub> のうち、R 単位画素 P<sub>R11</sub> は、第 1 ゲートライン 111 から印加されるスキャン信号 S<sub>1</sub> がゲートに提供され、ソースに R データライン 121 R からデータ信号 D<sub>R1</sub> が提供されるスイッチングトランジスタ M<sub>1\_R</sub> と、このスイッチングトランジスタ M<sub>1\_R</sub> のドレインにゲートが接続され、ソースに電源ライン 131 R から電源電圧 V<sub>DD1</sub> が提供される駆動トランジスタ M<sub>2\_R</sub> と、この駆動トランジスタ M<sub>2\_R</sub> のゲートとソースに接続されたキャパシタ C<sub>1\_R</sub> と、駆動トランジスタ M<sub>2\_R</sub> のドレインにアノードが接続され、カソードが接地電圧 V<sub>SS</sub> に接続された R-E<sub>L</sub> 素子 E<sub>L1\_R</sub> で構成される。30

#### 【 0 0 1 1 】

また、画素 P<sub>11</sub> を構成する G 単位画素 P<sub>G11</sub> は、第 1 ゲートライン 111 から印加されるスキャン信号 S<sub>1</sub> がゲートに提供され、ソースに G データライン 121 G からデータ信号 D<sub>G1</sub> が提供されるスイッチングトランジスタ M<sub>1\_G</sub> と、このスイッチングトランジスタ M<sub>1\_G</sub> のドレインにゲートが連結され、ソースに電源ライン 131 G から電源電圧 V<sub>DD1</sub> が提供される駆動トランジスタ M<sub>2\_G</sub> と、この駆動トランジスタ M<sub>2\_G</sub> のゲートとソースに連結されたキャパシタ C<sub>1\_G</sub> と、駆動トランジスタ M<sub>2\_G</sub> のドレインにアノードが連結され、カソードが接地電圧 V<sub>SS</sub> に連結された G-E<sub>L</sub> 素子 E<sub>L1\_G</sub> で構成される。40

#### 【 0 0 1 2 】

また、画素 P<sub>11</sub> を構成する B 単位画素 P<sub>B11</sub> は、第 1 ゲートライン 111 から印加されるスキャン信号 S<sub>1</sub> がゲートに提供され、ソースに B データライン 121 B からデータ信号 D<sub>B1</sub> が提供されるスイッチングトランジスタ M<sub>1\_B</sub> と、このスイッチングトランジスタ M<sub>1\_B</sub> のドレインにゲートが連結され、ソースに電源ライン 131 B から電源電圧 V<sub>DD1</sub> が提供される駆動トランジスタ M<sub>2\_B</sub> と、この駆動トランジスタ M<sub>2\_B</sub> のゲートとソースに連結されたキャパシタ C<sub>1\_B</sub> と、駆動トランジスタ M<sub>2\_B</sub> のドレインにアノードが連結され、カソードが接地電圧 V<sub>SS</sub> に連結された G-E<sub>L</sub> 素子 E<sub>L1\_B</sub> で構成される。50

インにアノードが連結され、カソードが接地電圧VSSに連結されたB-EL素子EL1\_Bで構成される。

#### 【0013】

このピクセル回路の動作は次の通りである。ゲートライン111にスキャン信号S1が印加されると、画素P11を構成するR,G,B単位画素のスイッチングトランジスタM1\_R,M1\_G,M1\_Bが駆動し、R,G,Bデータライン121R,121G,121BからR,G,BデータDR1,DG1,DB1が駆動トランジスタM2\_R,M2\_G,M2\_Bのゲートにそれぞれ入力される。

#### 【0014】

駆動トランジスタM2\_R,M2\_G,M2\_Bは、ゲートに印加されるデータ信号DR1,DG1,DB1とR,G,B電源ライン131R,131G,131Bからそれぞれ提供される電源電圧VDD1との差に相応する駆動電流をEL素子EL1\_R,EL1\_G,EL1\_Bに提供する。各EL素子EL1\_R,EL1\_G,EL1\_Bは、駆動トランジスタM2\_R,M2\_G,M2\_Bを通じて印加される駆動電流により動作する。このようにして画素P11が駆動する。キャパシタC1\_R,C1\_G,C1\_Bは、各R,G,Bデータライン121R,121G,121Bに入力されたデータ信号DR1,DG1,DB1を貯蔵するための手段である。

#### 【0015】

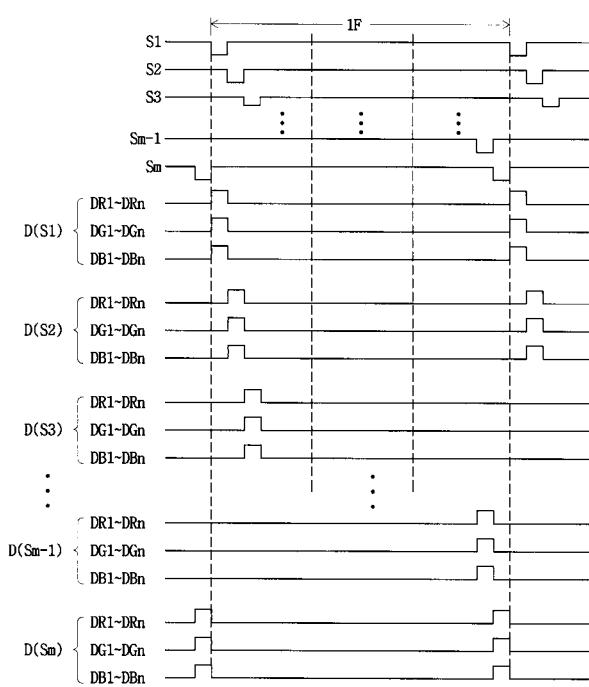

次に、以上のような構成を有する従来の有機電界発光表示装置10の動作を、図3の駆動波形図を参照しながら説明する。

#### 【0016】

まず、第1ゲートライン111にスキャン信号S1が印加されると、第1ゲートライン111が駆動し、第1ゲートライン111に接続された画素P11～P1nが駆動する。

#### 【0017】

つまり、第1ゲートライン111に印加されるスキャン信号S1によって、第1ゲートライン111に接続された画素P11～P1nのR,G,B単位画素PR11～PR1n,PG11～PG1n,PB11～PB1nのスイッチングトランジスタが駆動する。スイッチングトランジスタの駆動により、第1～nデータライン121～12nを構成するR,G,Bデータライン121R～12nR,121G～12nG,121B～12nBからR,G,Bデータ信号D(S1)DR1～DRn,DG1～DGn,DB1～DBnがR,G,B単位画素の駆動トランジスタのゲートに同時にそれぞれ入力される。

#### 【0018】

R,G,B単位画素の駆動トランジスタは、R,G,Bデータライン121R～12nR,121G～12nG,121B～12nBにそれぞれ印加されるR,G,Bデータ信号D(S1)DR1～DRn,DG1～DGn,DB1～DBnに対応する駆動電流をR,G,B-EL素子に提供する。したがって、第1ゲートライン111に接続された画素P11～P1nのR,G,B単位画素PR11～PR1n,PG11～PG1n,PB11～PB1nを構成する各EL素子は、第1ゲートライン111にスキャン信号S1が印加されると、同時に駆動する。

#### 【0019】

これと同様に、第2ゲートライン112を駆動するためのスキャン信号S2が印加されると、第2ゲートライン112に接続された画素P21～P2nのR,G,B単位画素PR21～PR2n,PG21～PG2n,PB21～PB2nには、第1～nデータライン121～12nを構成するR,G,Bデータライン121R～12nR,121G～12nG,121B～12nBからデータ信号D(S2)DR1～DRn,DG1～DGn,DB1～DBnが印加される。

#### 【0020】

この結果、第2ゲートライン112に接続された画素P21～P2nのR,G,B単位画素PR21～PR2n,PG21～PG2n,PB21～PB2nを構成するEL素子が、データ信号D(S2)DR1～DRn,DG1～DGn,DB1～DBnに対応する

10

20

30

40

50

駆動電流によって同時に駆動する。

#### 【0021】

このような動作を繰り返し、最終的にm番目のゲートライン11mにスキャン信号S<sub>m</sub>が印加されると、R，G，Bデータライン121R～12nR，121G～12nG，121B～12nBに印加されるR，G，Bデータ信号D(S<sub>m</sub>)DR1～DRn，DG1～DGn，DB1～DBnにより、m番目のゲートライン11mに接続された画素P<sub>m1</sub>～P<sub>m n</sub>のR，G，B単位画素PR<sub>m1</sub>～PR<sub>m n</sub>，PG<sub>m1</sub>～PG<sub>m n</sub>，PB<sub>m1</sub>～PB<sub>m n</sub>を構成するEL素子が同時に駆動する。

#### 【0022】

したがって、第1ゲートライン111から第mゲートライン11mにまで、順々にスキャン信号S<sub>1</sub>～S<sub>m</sub>が印加されると、各ゲートライン111～11mに接続された画素P<sub>11</sub>～P<sub>1n</sub>，…，P<sub>m1</sub>～P<sub>m n</sub>が順に駆動し、第1フレーム1Fの間、画素を駆動して、画像が表示されるようになる。10

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0023】

しかし、上述したように、従来の有機電界発光表示装置は、各画素が三つのR，G，B単位画素で構成されており、各R，G，B単位画素は、R，G，B-EL素子を駆動させるための駆動素子、すなわち、スイッチング薄膜トランジスタ、駆動薄膜トランジスタ、及びキャパシタを備えている。さらに、従来の有機電界発光表示装置には、各R，G，B単位画素に備えられた駆動素子に対してデータ信号と共通電源(ELVDD)を提供するためのデータライン及び共通電源ラインが単位画素別に配列される。20

#### 【0024】

すなわち、従来の有機電界発光表示装置によれば、各画素に3本のデータラインと3本の電源ラインが配置され、また、6個のトランジスタ(3個のスイッチング薄膜トランジスタと3個の駆動薄膜トランジスタ)と3個のキャパシタが要求されていた。しかも、各画素が発光制御信号によってコントロールされる場合には、発光制御信号を提供するための別途の発光制御ラインが必要であるため、R，G，B単位画素毎に少なくとも4本の信号ラインが要求される。このように、各画素に多数の配線と多数の素子が配列されると、回路構成が複雑となり、欠陥も発生しやすくなる。また、収率(製造歩留まり)が低下するという問題点がある。しかも、回路構成が複雑化して、信号ラインの本数が増加した場合や信号ラインが長くなった場合には、信号の伝送遅延(RCディレイ)や信号の電流電圧レベルの低下が起こり得る。30

#### 【0025】

また、近年では、表示装置が更に高精細化され、各画素の面積が減少している。このため、一つの画素に多くの回路要素を配列することは困難となっている。加えて、開口率が減少するという問題点がある。

#### 【0026】

そこで、本発明は、このような問題に鑑みてなされたもので、その目的は、高精細化に適した表示装置のピクセル回路、表示装置、及びその駆動方法を提供することにある。40

#### 【0027】

本発明の他の目的は、開口率及び収率を向上させることができる表示装置のピクセル回路、表示装置、及びその駆動方法を提供することにある。

#### 【0028】

本発明のもう一つの他の目的は、RCディレイ及び電圧降下を防ぐことができる表示装置のピクセル回路、表示装置、及びその駆動方法を提供することにある。

#### 【0029】

本発明のまたもう一つの他の目的は、画素構成及び配線を単純化することができる表示装置のピクセル回路、表示装置、及びその駆動方法を提供することにある。

#### 【課題を解決するための手段】

## 【 0 0 3 0 】

上記課題を解決するために、本発明の第1の観点によれば、所定区間ごとに所定の色を具現する表示装置のピクセル回路において、所定区間内でそれぞれ一つの色を放出する、少なくとも2個以上の発光素子と、少なくとも2個以上の発光素子に共通連結されて、少なくとも2個以上の発光素子を駆動するための能動素子を備え、能動素子は、所定区間内で所定期間ごとに少なくとも2個以上の発光素子を順に駆動し、少なくとも2個以上の発光素子は、所定期間ごとに順次に該当する一つの色を放出して所定区間で所定の色を具現する表示装置のピクセル回路が提供される。

## 【 0 0 3 1 】

所定区間は1フレームであり、所定期間はサブフレームであるため、1フレームは、少なくとも3個以上のサブフレームに分けられて、少なくとも2個以上の発光素子は、1フレーム内で各サブフレームごとに順に駆動し、残ったもので少なくとも一つのサブフレームでは、少なくとも2個以上の発光素子のうち、一つが再び駆動されるか、または少なくとも二つの発光素子が同時に駆動されて明るさを調節する。残ったもので少なくとも一つのサブフレームは、多数のサブフレームのうち、任意的に選択される。10

## 【 0 0 3 2 】

少なくとも二つの発光素子の発光時間を調節してホワイトバランスを調節する。発光素子はF E D、またはP D Pであるか、または発光素子はR、G、BまたはホワイトE L素子であり、少なくとも二つ以上のE L素子は第1電極が能動素子に共通連結され、第2電極が接地電圧に共通連結される。発光素子はストライプタイプまたはデルタタイプで配列される。20

## 【 0 0 3 3 】

能動素子は発光素子を駆動するための少なくとも一つ以上のスイッチング素子で構成され、能動素子を構成するスイッチング素子は薄膜トランジスタ、薄膜ダイオード、ダイオード、またはT R S (Triode Rectifier Switch : 3整流スイッチ)で構成される。

## 【 0 0 3 4 】

また、上記課題を解決するために、本発明の第2の観点によれば、R、G、B-E L素子(赤色電界発光素子、緑色電界発光素子、青色電界発光素子)と、R、G、Bデータ信号(赤色データ信号、緑色データ信号、青赤色データ信号)を順に伝達するための一つまたはそれ以上のスイッチングトランジスタと、R、G、Bデータ信号によりR、G、B-E L素子を順に駆動するための一つまたはそれ以上の駆動トランジスタと、R、G、Bデータ信号を貯蔵するための貯蔵素子と、を備え、R、G、B-E L素子は駆動トランジスタに共通連結され、2つの発光制御信号により駆動トランジスタから順に伝達されるR、G、Bデータ信号に相応して順に発光する表示装置のピクセル回路が提供される。30

## 【 0 0 3 5 】

また、上記課題を解決するために、本発明の第3の観点によれば、R、G、B-E L素子と、R、G、B-E L素子に共通連結されて、R、G、B-E L素子を駆動するための駆動手段と、R、G、B-E L素子の駆動を順に制御するための制御手段と、を有する有機電界発光表示装置のピクセル回路が提供される。駆動手段は少なくともデータ信号をスイッチングするための一つ、またはそれ以上のスイッチングトランジスタと、データ信号に相応する駆動電流をR、G、B-E L素子として提供するための一つ、またはそれ以上の駆動トランジスタと、データ信号を貯蔵するためのキャパシタと、を有する。駆動手段は駆動トランジスタのスレッショルド電圧を補償するためのスレッショルド電圧補償手段をさらに有する。駆動トランジスタとキャパシタには、共通の電源ラインを通じて同一な電源電圧を提供するか、または個別の電源ラインを通じて同一な電源電圧を個別的に提供する。40

## 【 0 0 3 6 】

制御手段は、該当する発光制御信号(第1発光制御信号と第2発光制御信号を含む)によって駆動トランジスタからR、G、B-E L素子に駆動電流が提供されるのを制御して50

， R , G , B - E L 素子の発光を順に制御する第 1 制御手段，第 2 制御手段，及び第 3 制御手段で成り立つ。第 1 制御手段は，駆動手段と赤色電界発光素子（R - E L 素子）との間に直列に接続され，第 1 発光制御信号と第 2 発光制御信号によってオン／オフ制御される少なくとも 2 つのトランジスタで構成されている。また，第 2 制御手段は，駆動手段と緑色電界発光素子（G - E L 素子）との間に直列に接続され，第 1 発光制御信号と第 2 発光制御信号によってオン／オフ制御される少なくとも 2 つのトランジスタで構成されている。また，第 3 制御手段は，駆動手段と青色電界発光素子（B - E L 素子）との間に直列に接続され，第 1 発光制御信号と第 2 発光制御信号によってオン／オフ制御される少なくとも 2 つのトランジスタで構成されている。制御手段に印加される該当発光制御信号のアクティブオン時間を調節して該当する E L 素子に駆動電流が印加される時間を調節し，全体のホワイトバランスを調節する。

#### 【 0 0 3 7 】

また，上記課題を解決するために，本発明の第 4 の観点によれば，ゲート（制御端）がゲートラインに連結され，ソース／ドレイン（第 1 電源端）がデータラインに連結された第 1 薄膜トランジスタと，第 1 薄膜トランジスタのドレイン／ソース（第 1 電源端）にゲート（制御端）が連結され，ソース／ドレイン（第 1 電源端）に電源ラインが連結された第 2 薄膜トランジスタと，第 2 薄膜トランジスタのゲート（制御端）とソース／ドレイン（第 1 電源端）に連結されたキャパシタと，第 2 薄膜トランジスタのドレイン／ソース（第 2 電源端）にソース／ドレイン（第 1 電源端）が連結され，ゲート（制御端）に第 1 発光制御信号が印加される第 3 薄膜トランジスタと，第 3 薄膜トランジスタのドレイン／ソース（第 2 電源端）にドレイン／ソース（第 1 電源端）が連結され，ゲート（制御端）に第 2 発光制御信号が印加される第 4 薄膜トランジスタと，第 2 薄膜トランジスタのドレイン／ソース（第 2 電源端）にドレイン／ソース（第 1 電源端）が連結され，ゲート（制御端）に第 1 発光制御信号が印加される第 5 薄膜トランジスタと，第 5 薄膜トランジスタのソース／ドレイン（第 2 電源端）にソース／ドレイン（第 1 電源端）が連結され，ゲート（制御端）に第 2 発光制御信号が印加される第 6 薄膜トランジスタと，第 2 薄膜トランジスタのドレイン／ソース（第 2 電源端）にドレイン／ソース（第 1 電源端）が連結され，ゲート（制御端）に第 1 発光制御信号が印加される第 7 薄膜トランジスタと，第 7 薄膜トランジスタのソース／ドレイン（第 2 電源端）にドレイン／ソース（第 1 電源端）が連結され，ゲート（制御端）に第 2 発光制御信号が印加される第 8 薄膜トランジスタと，第 1 電極が第 4 トランジスタの第 2 電源端に接続され，第 2 電極が接地された赤色電界発光素子と，第 1 電極が第 6 トランジスタの第 2 電源端に接続され，第 2 電極が接地された緑色電界発光素子と，第 1 電極が第 8 トランジスタの第 2 電源端に接続され，第 2 電極が接地された青色電界発光素子と，を有する有機電界発光表示装置のピクセル回路が提供される。

#### 【 0 0 3 8 】

また，上記課題を解決するために，本発明の第 5 の観点によれば，それぞれ所定区間にごとに所定の色を具現し，所定区間内でそれぞれ一つの色を放出する少なくとも二つ以上の発光素子を備える多数の画素を含み，少なくとも二つ以上の発光素子は所定区間内で時分割的に順に駆動されて一つの色を放出して，各画素は所定区間内で所定の色を具現する表示装置が提供される。

#### 【 0 0 3 9 】

また，上記課題を解決するために，本発明の第 6 の観点によれば，それぞれ所定区間にごとに所定の色を具現し，所定区間内でそれぞれ一つの色を放出する少なくとも二つ以上の発光素子を備える多数の画素を含み，少なくとも二つ以上の発光素子は所定期間の間に一つだけ発光して，所定区間の間少なくとも二つ以上の発光素子が順に一つの色を放出することによって，各画素は所定区間の間所定の色を具現する表示装置が提供される。

#### 【 0 0 4 0 】

また，上記課題を解決するために，本発明の第 7 の観点によれば，R , G , B - E L 素子と，R , G , B - E L 素子に連結されて R , G , B 発光素子を駆動するための少なくと

10

20

30

40

50

も一つの薄膜トランジスタを備える多数の画素と，を含み，各画素のR，G，B-E-L素子は，第1電極が少なくとも一つの薄膜トランジスタに共通連結され，第2電極が接地に共通連結されるうえ，各画素は少なくとも一つの薄膜トランジスタによってR，G，B-E-L素子が順に発光する表示装置が提供される。

#### 【0041】

また，上記課題を解決するために，本発明の第8の観点によれば，多数のゲートライン，多数のデータライン及び多数の電源ラインと，多数のゲートライン，データライン及び電源ラインのうち，該当する一つのゲートライン，データライン及び電源ラインにそれぞれ連結される多数の画素を含め，各画素はR，G，B-E-L素子と，R，G，B-E-L素子に共通連結されて，R，G，B-E-L素子を順に駆動するための少なくとも一つ以上の薄膜トランジスタと，薄膜トランジスタとR，G，B-E-L素子の間にそれぞれ連結され，R，G，B-E-L素子が多数のサブフレームで構成される一つのフレーム内で各サブフレームごとに順に発光するように制御するR，G，B発光制御用薄膜トランジスタと，を有する平板表示装置が提供される。

#### 【0042】

また，上記課題を解決するために，本発明の第9の観点によれば，多数のゲートライン，多数のデータライン及び多数の電源ラインと，多数のゲートライン，データライン及び電源ラインのうち，該当する一つのゲートライン，データライン及び電源ラインにそれぞれ連結される多数の画素を含め，各画素は，ゲートがゲートラインに連結され，ソースがデータラインに連結された第1薄膜トランジスタと，第1薄膜トランジスタのドレインにゲートが連結され，ソースに電源ラインが連結された第2薄膜トランジスタと，第2薄膜トランジスタのゲートとソースに連結されたキャパシタと，第2薄膜トランジスタのドレインにソースが連結され，ゲートに第1発光制御信号が印加される第3薄膜トランジスタと，第3薄膜トランジスタのドレインにドレインが連結され，ゲートに第2発光制御信号が印加される第4薄膜トランジスタと，第2薄膜トランジスタのドレインにドレインが連結され，ゲートに第1発光制御信号が印加される第5薄膜トランジスタと，第5薄膜トランジスタのソースにソースが連結され，ゲートに第2発光制御信号が印加される第6薄膜トランジスタと，第2薄膜トランジスタのドレインにドレインが連結され，ゲートに第1発光制御信号が印加される第7薄膜トランジスタと，第7薄膜トランジスタのソースにドレインが連結され，ゲートに第2発光制御信号が印加される第8薄膜トランジスタと，第1電極が第4トランジスタの第2電源端に接続され，第2電極が接地された赤色電界発光素子と，第1電極が第6トランジスタの第2電源端に接続され，第2電極が接地された緑色電界発光素子と，第1電極が第8トランジスタの第2電源端に接続され，第2電極が接地された青色電界発光素子と，を有する平板表示装置が提供される。

#### 【0043】

また，上記課題を解決するために，本発明の第10の観点によれば，多数のゲートライン，多数のデータライン，多数の発光制御ライン及び多数の電源ラインと，多数のゲートライン，データライン，発光制御ライン及び電源ラインのうち，該当する一つのゲートライン，データライン，発光制御ライン及び電源ラインにそれぞれ連結される多数の画素を備える画素部と，多数のゲートラインに多数のスキャン信号を提供するための少なくとも一つのゲートライン駆動回路と，多数のデータラインにR，G，Bデータ信号を順に提供するための少なくとも一つのデータライン駆動回路と，多数の発光制御ラインに発光制御信号を提供するための少なくとも一つの発光制御信号発生回路を備え，各画素はR，G，B-E-L素子と，R，G，B-E-L素子に共通連結されて，R，G，B-E-L素子を順に駆動するための少なくとも一つ以上の薄膜トランジスタと，薄膜トランジスタとR，G，B-E-L素子間にそれぞれ連結されて，R，G，B-E-L素子が多数のサブフレームで構成される一つのフレーム内で各サブフレームごとに順に発光するように制御するR，G，B発光制御用薄膜トランジスタと，を有する平板表示装置が提供される。

#### 【0044】

また，上記課題を解決するために，本発明の第11の観点によれば，多数のゲートライ

10

20

30

40

50

ン，多数のデータライン及び多数の電源ラインと，多数のゲートライン，データライン及び電源ラインのうち，該当する一つのゲートライン，データライン及び電源ラインにそれぞれ連結された多数の画素を含め，各画素は少なくともR，G，B発光素子を備える平板表示装置を駆動する方法において，各画素には所定区間内で所定期間ごとに同一なデータラインを通じてR，G，Bデータが順に提供されて，R，G，B発光素子が時分割的に順に駆動されることによって，所定区間内で所定の色を具現する平板表示装置の駆動方法が提供される。

#### 【0045】

また，上記課題を解決するために，本発明の第12の観点によれば，多数のゲートライン，多数のデータライン及び多数の電源ラインと，多数のゲートライン，データライン及び電源ラインのうち，該当する一つのゲートライン，データライン及び電源ラインにそれぞれ連結された多数の画素を含め，各画素は少なくともR，G，B発光素子を備える平板表示装置を駆動する方法において，多数のゲートラインのうち，該当する一つのゲートラインに所定期間ごとにスキャン信号を発生し，スキャン信号が発生するたびに多数のデータラインのうち，該当する一つのデータラインにR，G，Bデータを順に印加してR，G，B駆動電流を発生させ，発光制御信号に該当する一つのゲートラインに連結された画素のR，G，B発光素子を順に駆動して所定区間内で所定の色を具現する平板表示装置の駆動方法が提供される。

#### 【発明の効果】

#### 【0046】

本発明によれば，表示画像の高精細化が可能となる。また，開口率及び収率を向上させるとともに，画素構成及び配線を単純化することができる。さらに，伝送信号のディレイ及び電流電圧降下を防ぐことができる。

#### 【発明を実施するための最良の形態】

#### 【0047】

以下に添付図面を参照しながら，本発明の好適な実施の形態について詳細に説明する。なお，本明細書及び図面において，実質的に同一の機能構成を有する構成要素については，同一の符号を付することにより重複説明を省略する。

#### 【0048】

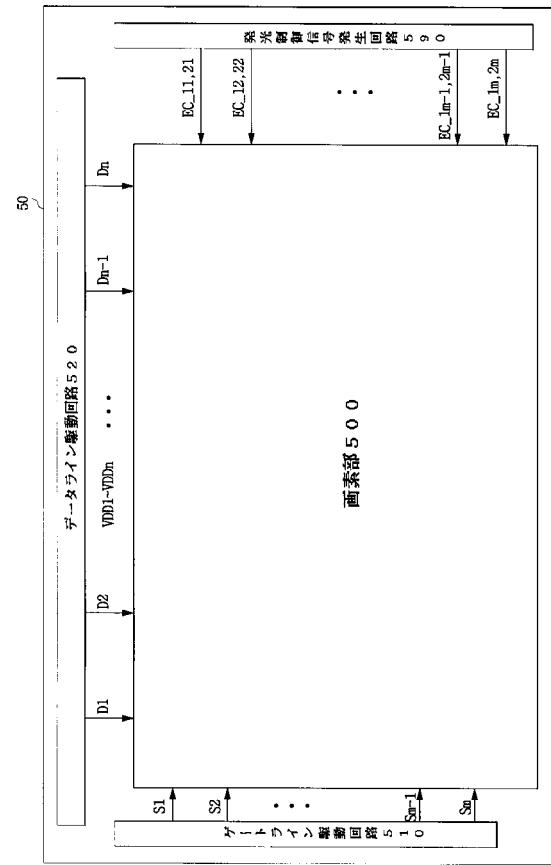

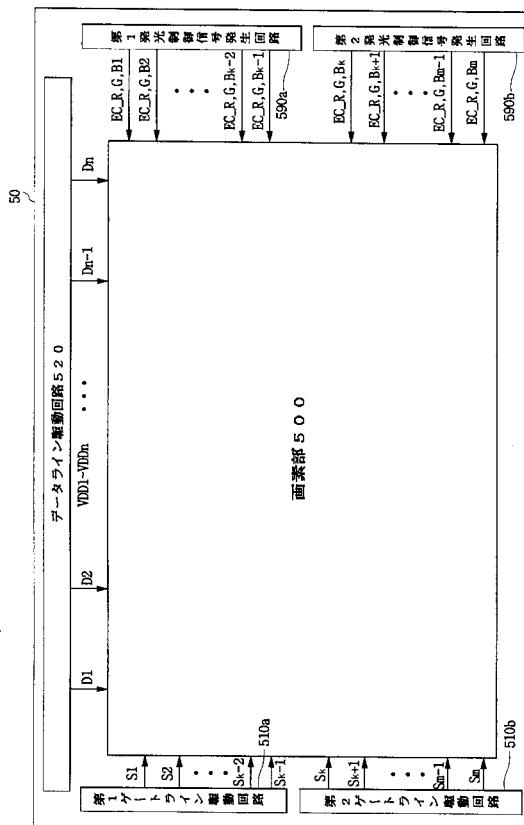

図4は，本発明の第1の実施の形態に係る有機電界発光表示装置50の構成を示すブロック図である。

#### 【0049】

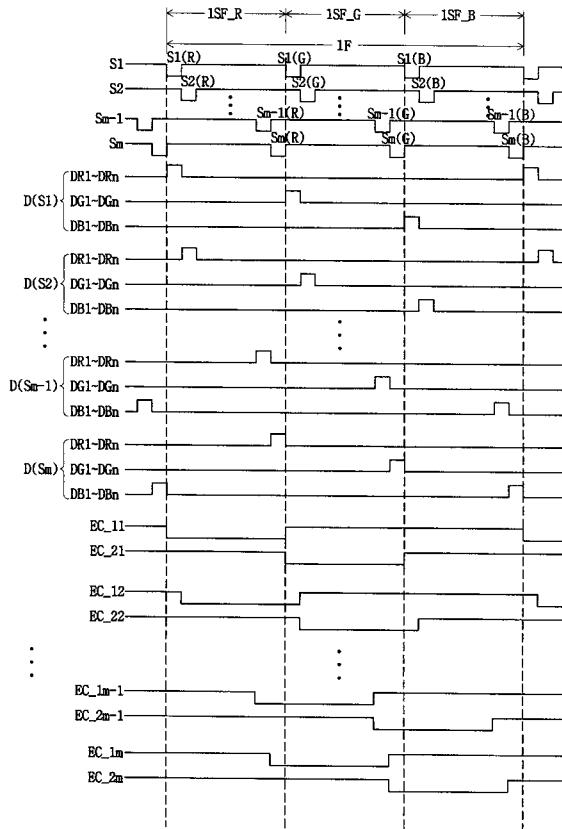

有機電界発光表示装置50は，画素部500，ゲートライン駆動回路510，データライン駆動回路520，及び発光制御信号発生回路590を備える。ゲートライン駆動回路510は，画素部500のゲートラインに対して，スキャン信号S1～Smを一つのフレームの間，順に供給する。データライン駆動回路520は，画素部500のデータラインに対して，R，G，Bデータ信号D1～Dnを一つのフレームの間，スキャン信号が印加されるごとに順に提供する。発光制御信号発生回路590は，画素部500の発光制御ライン591～59mに対して，R，G，B-EL素子の発光を制御するための発光制御信号EC\_11，EC\_21～EC\_1m，EC\_2mを一つのフレームの間，スキャン信号が印加されるごとに順に供給する。

#### 【0050】

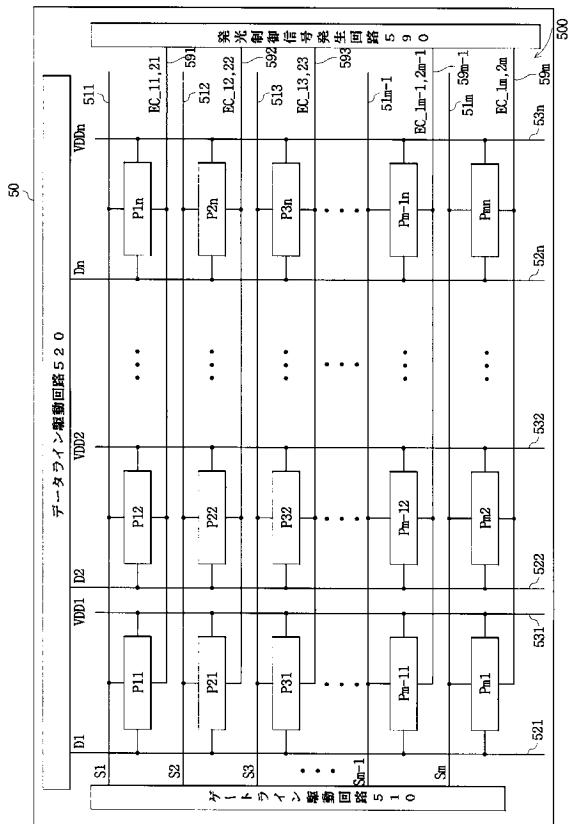

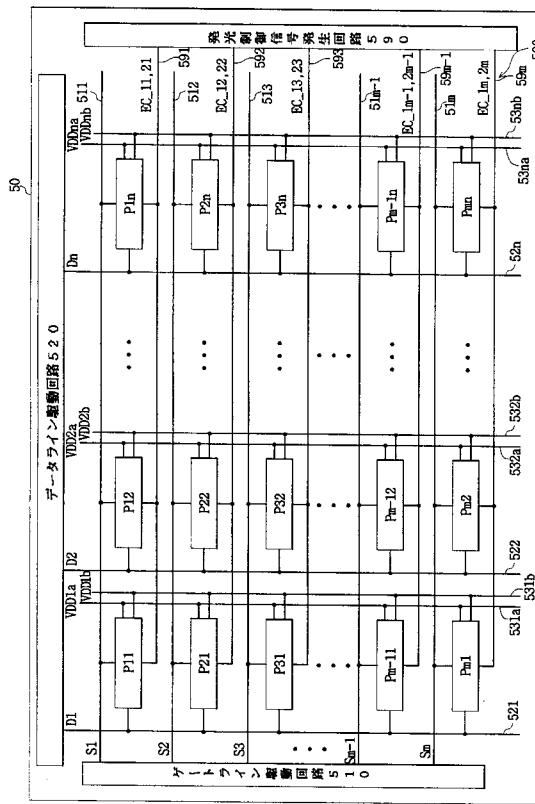

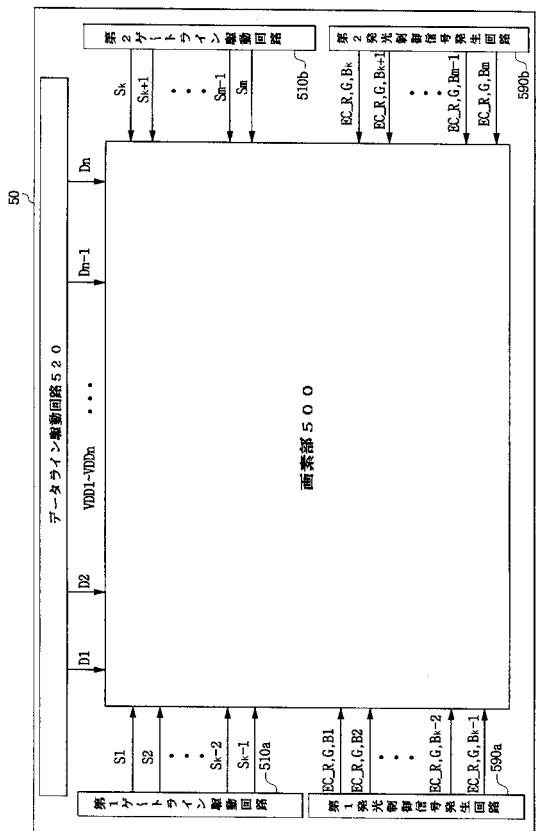

図5は，画素部500の構成の一例を示したブロック図である。

#### 【0051】

画素部500は，ゲートライン駆動回路510からスキャン信号S1～Smがそれぞれ提供される多数のゲートライン511～51mと，データライン駆動回路520からデータ信号D1～Dnがそれぞれ提供される多数のデータライン521～52nと，発光制御信号発生回路590から発光制御信号EC\_11，EC\_21～EC\_1m，EC\_2mがそれぞれ提供される多数の発光制御ライン591～59mと，電源(図示せず)から電源電圧VDD1～VDDnが提供される多数の電源ライン531a，531b～531na

10

20

30

40

50

, 53nbを備える。

#### 【0052】

画素部500は、多数のゲートライン511～51m、多数のデータライン521～52n、多数の発光制御ライン591～59m、及び多数の電源ライン531a、531b～53na、53nbに接続され、マトリクス形態に配列される多数の画素P11～Pmnをさらに含む。各画素P11～Pmnは、多数のゲートライン511～51mの中の対応する一つのゲートラインに接続され、多数のデータライン521～52nの中の対応する一つのデータラインに接続され、多数の発光制御ライン591～59mの中の対応する一つの発光制御ラインに接続され、多数の電源ライン531a、531b～53na、53nbの中の対応する一つの電源ラインに接続されている。

10

#### 【0053】

例えば、画素P11は、多数のゲートライン511～51mのうち、第1スキャン信号S1を提供する第1ゲートライン511に接続され、多数のデータライン521～52nのうち、第1データ信号D1を提供する第1データライン521に接続され、多数の発光制御ライン591～59mのうち、第1発光制御信号EC\_11、第2発光制御信号EC\_21が伝送される発光制御ライン591に接続され、多数の電源ライン531a、531b～53na、53nbのうち、第1電源ライン531a、531bに接続されている。

#### 【0054】

したがって、それぞれの画素P11～Pmnには、対応するスキャンラインを通じて対応するスキャン信号が印加され、対応するデータラインを通じて対応するR、G、Bデータ信号が順に提供されるうえ、対応する発光制御ラインを通じて対応する発光制御信号が順に提供され、対応する電源ラインを通じて対応する電源電圧が印加される。故に、各画素は、対応するスキャン信号が印加されることに対応するR、G、Bデータ信号が順に印加され、発光制御信号によりR、G、B-EL素子が順に駆動されてR、G、Bデータ信号に相応な光を順に出射する。この結果、一つのフレームの間、所定の色、つまり、画像が表示されるようになる。

20

#### 【0055】

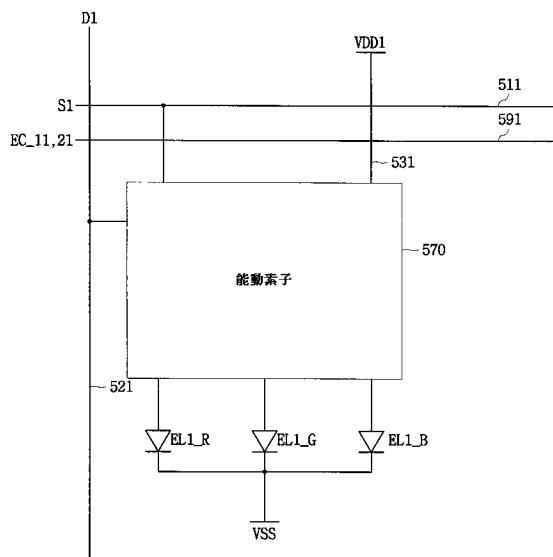

図7は、本発明の第1の実施の形態に係る順次駆動方式の有機電界発光表示装置に備えられた一つの画素に対応するピクセル回路を概念的に示したものである。図7は、多数の画素のうち、代表的に一つの画素P11の構成を示している。

30

#### 【0056】

図7に示したように、画素P11は、第1ゲートライン511、第1データライン521、第1発光制御ライン591、及び第1共通電源ライン531に接続された能動素子570と、能動素子570と接地VSSの間に並列接続されるR、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bを備える。三つのR、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bは、第1電極、例えばアノード電極が能動素子570にそれぞれ接続され、第2電極、例えばカソード電極が接地電圧VSSに共通接続される。

#### 【0057】

このような構成を有するピクセル回路は、三つのR、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bが一つ能動素子570を共有するため、1フレームの間に画素P11が所定の色を表示するためには、R、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bが順に駆動しなければならない。そこで、一つのフレームを三つのサブフレームに分割し、サブフレームごとにR、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bを駆動させる。これによって、1フレームの間、R、G、B-EL素子EL1\_R、EL1\_G、EL1\_Bが時分割的に順に駆動し、画素P11が所定の色を具現する。

40

#### 【0058】

まず、第1サブフレームにおいて、ゲートライン511にスキャン信号S1が印加され、データライン521にデータD1としてRデータDR1が印加されると、能動素子570は、発光制御信号発生回路590が発光制御ライン591に出力する発光制御信号EC

50

—11, EC\_21に応じてR-EL素子EL1\_Rを駆動させ, Rデータに相応なR色(赤色)を発光する。

#### 【0059】

次に, 第2サブフレームにおいて, ゲートライン511にスキャン信号S1が印加され, データライン521にデータD1としてGデータDG1が印加されると, 能動素子570は, 発光制御信号発生回路590が発光制御ライン591に出力する発光制御信号EC\_11, EC\_21に応じてG-EL素子EL1\_Gを駆動させ, Gデータに相応なG色(緑色)を発光する。

#### 【0060】

最後に, 第3サブフレームにおいて, ゲートライン511にスキャン信号S1が印加され, データライン521にデータD1としてGデータDB1が印加されると, 能動素子570は, 発光制御信号発生回路590が発光制御ライン591に出力する発光制御信号EC\_11, EC\_21に応じてB-EL素子EL\_Bを駆動させ, Bデータに相応なB色(青色)を発光する。このように, 1フレームの間にR, G, B-EL素子が時分割的に順に駆動される。そして, 各画素が所定の色を発光して画像が表示されるようになる。

#### 【0061】

本実施の形態では, 1フレームを3サブフレームに分割し, 各サブフレームにおいて, R, G, B-EL素子が順に駆動してR, G, B色を発光し, 所定の色を具現する。この他, 色度, 明るさ, または輝度等を調整するために, R, G, B-EL素子, またはR, G, B, W(White)-EL素子の発光順を任意的に変更する, または1フレームを3サブフレーム以上に分割して他のサブフレームでR, G, B, W色のうち, 少なくとも一つをさらに発光させることもできる。例えば, 1フレームを4サブフレームに分割して, RRGB, RGGB, RGBB, RGBWのように余分の1サブフレームの間にR, G, B, またはWのうち, 一つの色をさらに発光させることもできる。そして, 余分に発光させる色は, 多数のサブフレームのうち, 適当なサブフレームにおいて発光される。このとき, 余分のサブフレームにおいてR, G, B, Wの色のうち, 一つをさらに発光させるために, R, G, B, W-EL素子のうち, 一つのEL素子を駆動させるか, またはこれらの中で少なくとも二つのEL素子を駆動させることもできる。

#### 【0062】

また, 本実施の形態では, 1フレームを3サブフレームに分割し, 各サブフレームにおいてR, G, B-EL素子が順に駆動されるが, 各EL素子の駆動方法についてはこれに限定されない。例えば, 1フレームを4以上のサブフレームに分割して, R, G, B, Wを時分割的に順に駆動させる, またはR, G, B, Wのうち, 少なくとも二つの色を各サブフレームにおいて時分割的に順に駆動させるようにしてもよい。

#### 【0063】

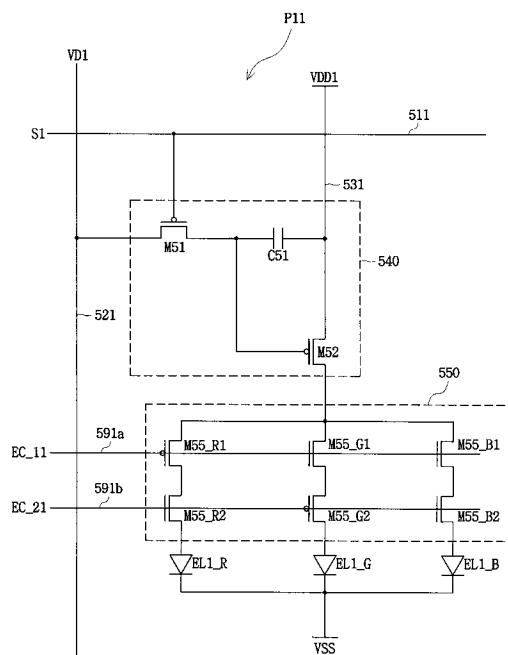

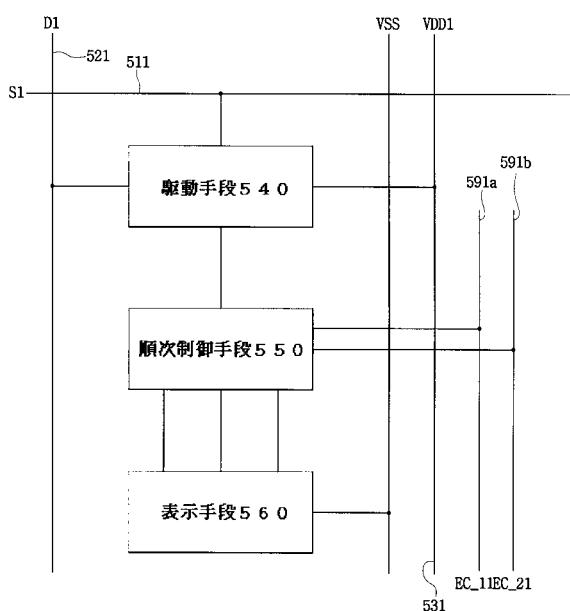

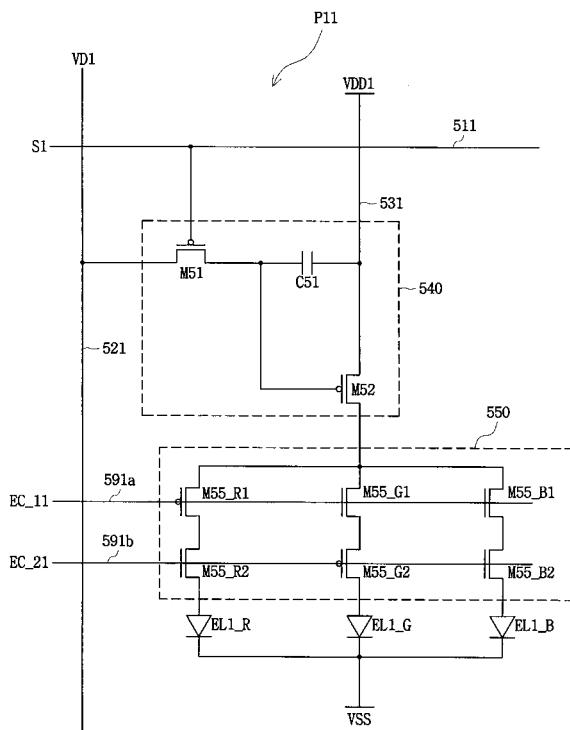

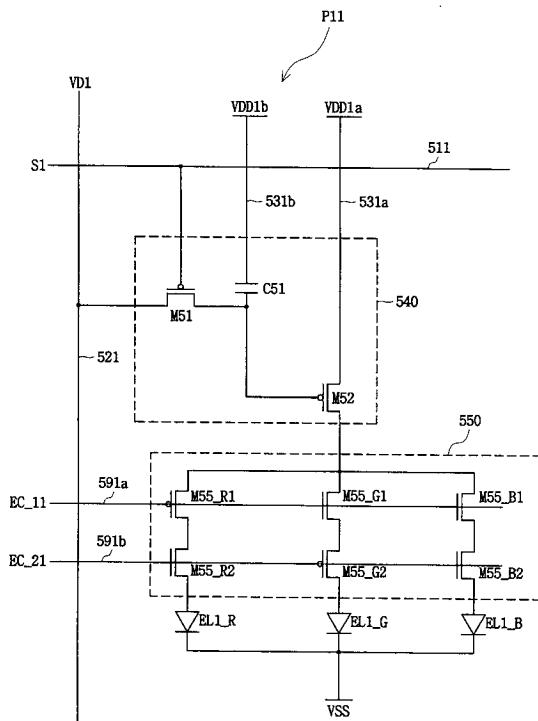

図8は, 本実施の形態に係る順次駆動方式の有機電界発光表示装置が備えるピクセル回路の構成例を示したブロック図である。図10は, 図8のピクセル回路の具体例を示している。図8及び図10に示したピクセル回路は, R, G, B-EL素子EL1\_R, EL1\_G, EL1\_Bを1フレームの間に時分割的に順次駆動させる。

#### 【0064】

図8及び図10に示したように, 画素P11は, 一つのゲートライン511, データライン521, 二つの発光制御ライン591a, 591b, 及び電源供給ライン531, 並びに, 各ラインを通じて入力される信号によって順に駆動される表示手段560を備える。表示手段560は, 光を自ら放出する発光素子で構成され, 発光素子はR, G, Bの色を発光するR, G, B-EL素子EL1\_R, EL1\_G, EL1\_Bを備える。

#### 【0065】

また, 画素P11は, R, G, B-EL素子EL1\_R, EL1\_G, EL1\_Bを時分割的に順に駆動するための能動素子570をさらに備える(図7参照)。

#### 【0066】

能動素子570は, 駆動手段540と順次制御手段550を備えている。駆動手段54

10

20

30

40

50

0は、スキャン信号S1が印加されるたびにR,G,Bデータ信号D1(DR1,DG1,DB1)に対応する駆動電流を出力する。順次制御手段550は、発光制御信号EC\_11,EC\_21に応じて、駆動手段540から出力された駆動電流を順に表示手段560に備えられたR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bに供給する。

#### 【0067】

図10に示したように、駆動手段540は、ゲートにゲートライン511からスキャン信号S1が提供され、ソースにデータライン521からR,G,Bデータ信号DR1,DG1,DB1が順に提供されるスイッチングトランジスタM51(第1トランジスタ)と、スイッチングトランジスタM51のドレインにゲートが接続され、ソースに電源電圧ライン531から電源電圧VDD1が提供され、ドレインが順次制御手段550に接続される駆動トランジスタM52(第2トランジスタ)，及び駆動トランジスタM52のゲートとソースの間に接続されたキャパシタC51(貯蔵素子)で構成される。

#### 【0068】

本実施の形態では、駆動手段540は、二つの薄膜トランジスタ(スイッチングトランジスタと駆動トランジスタ)と、一つのキャパシタで構成されているが、表示手段560を構成する発光素子を駆動することができるその他の回路構成を採用することが可能である。また、表示手段560の発光素子を駆動する駆動特性を向上させることができるすべての手段、例えばスレッショルド電圧補償手段等を追加することも好ましい。

#### 【0069】

また、駆動手段540は、Pチャネル型薄膜トランジスタのみで構成されているが、Nチャネル型薄膜トランジスタで構成してもよい。Nチャネル型薄膜トランジスタとPチャネル型薄膜トランジスタを混在させることも可能である。またさらに、各薄膜トランジスタは、デプレーションモード(depletion mode)であってもよいし、エンハンスマントモード(enhancement mode)であってもよい。また、駆動手段540を薄膜トランジスタで構成する代わりに、薄膜ダイオード(TFD:Thin Film Diode)，ダイオード，TRSのような各種スイッチング素子を使用することができる。

#### 【0070】

順次制御手段550は、駆動手段540と表示手段560の間に接続されており、発光制御信号発生回路590から発光制御ライン591a,591bを通じて提供される第1発光制御信号EC\_11及び第2発光制御信号EC\_21に応じて、表示手段560のR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bを順に駆動する。

#### 【0071】

図10に示したように、順次制御手段550は、駆動手段540に属する駆動トランジスタM52のドレインとR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bのアノードとの間に接続されており、発光制御信号EC\_11,EC\_21応じてR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bの駆動を順に制御する第1制御手段、第2制御手段、及び3制御手段を備える。

#### 【0072】

本実施の形態では、順次制御手段550が二つの発光制御制御信号EC\_11,EC\_21だけを利用してR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bを順に制御する。

#### 【0073】

すなわち、第1制御手段は、Pチャネル型のトランジスタ(FET:Field-Effect Transistor)M55\_R1(第3トランジスタ)とNチャネル型のトランジスタM55\_R2(第4トランジスタ)から構成されている。トランジスタM55\_R1は、第1発光制御信号EC\_11によってオン/オフ制御され、駆動トランジスタM52を通じて入力されるRデータ信号をトランジスタM55\_R2に与える。トランジスタM55\_R2は、第2発光制御信号EC\_21によってオン/オフ制御され、トランジスタM55\_R1を介して入力されるRデータ信号をR-EL素子EL1\_Rに与え

10

20

30

40

50

て，R-E L素子E L 1\_Rを駆動する。具体的には，トランジスタM 5 5\_R 1のゲートは第1発光制御信号E C\_1 1の伝送ラインに接続されており，トランジスタM 5 5\_R 2のゲートは第2発光制御信号E C\_2 1が接続されており，トランジスタM 5 5\_R 1のソースは駆動トランジスタM 5 2のドレインに接続されており，トランジスタM 5 5\_R 2のドレインはトランジスタM 5 5\_R 1のドレインに接続されており，トランジスタM 5 5\_R 2のソースはR-E L素子E L 1\_Rのアノードに接続されている。

#### 【0074】

第2制御手段は，Nチャネル型のトランジスタM 5 5\_G 1（第5トランジスタ）とPチャネル型のトランジスタM 5 5\_G 2（第6トランジスタ）から構成されている。トランジスタM 5 5\_G 1は，第1発光制御信号E C\_1 1によってオン／オフ制御され，駆動トランジスタM 5 2を通じて入力されるGデータ信号をトランジスタM 5 5\_G 2に与える。トランジスタM 5 5\_G 2は，第2発光制御信号E C\_2 1によってオン／オフ制御され，トランジスタM 5 5\_G 1を介して入力されるGデータ信号をG-E L素子E L 1\_Gに与えて，G-E L素子E L 1\_Rを駆動する。具体的には，トランジスタM 5 5\_G 1のゲートは第1発光制御信号E C\_1 1の伝送ラインに接続されており，トランジスタM 5 5\_G 2のゲートは第2発光制御信号E C\_2 1が接続されており，トランジスタM 5 5\_G 1のドレインは駆動トランジスタM 5 2のドレインに接続されており，トランジスタM 5 5\_G 2のソースはトランジスタM 5 5\_G 1のソースに接続されており，トランジスタM 5 5\_G 2のドレインはG-E L素子E L 1\_Gのアノードに接続されている。

10

20

#### 【0075】

第3制御手段は，Nチャネル型のトランジスタM 5 5\_B 1（第7トランジスタ）とNチャネル型のトランジスタM 5 5\_B 2（第8トランジスタ）から構成されている。トランジスタM 5 5\_B 1は，第1発光制御信号E C\_1 1によってオン／オフ制御され，駆動トランジスタM 5 2を通じて入力されるBデータ信号をトランジスタM 5 5\_B 2に与える。トランジスタM 5 5\_B 2は，第2発光制御信号E C\_2 1によってオン／オフ制御され，トランジスタM 5 5\_B 1を介して入力されるBデータ信号をB-E L素子E L 1\_Bに与えて，B-E L素子E L 1\_Bを駆動する。具体的には，トランジスタM 5 5\_B 1のゲートは第1発光制御信号E C\_1 1の伝送ラインに接続されており，トランジスタM 5 5\_B 2のゲートは第2発光制御信号E C\_2 1が接続されており，トランジスタM 5 5\_B 1のドレインは駆動トランジスタM 5 2のドレインに接続されており，トランジスタM 5 5\_B 2のドレインはトランジスタM 5 5\_B 1のソースに接続されており，トランジスタM 5 5\_B 2のソースはB-E L素子E L 1\_Bのアノードに接続されている。

30

#### 【0076】

順次制御手段550は，Pチャネル型薄膜トランジスタとNチャネル型薄膜トランジスタの組み合わせで構成されているが，Pチャネル型薄膜トランジスタのみ，または，Nチャネル型薄膜トランジスタのみで構成してもよい。Nチャネル型薄膜トランジスタとPチャネル型薄膜トランジスタを異なる組み合わせとすることも可能である。また，各薄膜トランジスタは，デブリーションモードであってもよいし，エンハンスマントモードであってもよい。また，順次制御手段550を薄膜トランジスタで構成する代わりに，薄膜ダイオード，ダイオード，TRSのような各種スイッチング素子を使用することができる。そして，R，G，B-E L素子を順に駆動する多様な形態でこれらのスイッチング素子が回路構成される。

40

#### 【0077】

本実施の形態では，一つの能動素子によって順次駆動される発光素子としてR，G，B-E L素子が採用されているが，この他，FED(Field Emission Display)，PDP(Plasma Display Panel)のような発光素子を採用することも可能である。

#### 【0078】

50

本実施の形態に係る有機電界発光表示装置のピクセル回路の順次駆動方式を説明するところのようである。

#### 【0079】

従来は、図3に示したように、多数のゲートラインに対して、ゲートライン駆動回路110から一つのスキャン信号S1～Smがそれぞれ順に印加される。そして、1フレームの間にm個のスキャン信号が印加され、各スキャン信号S1～Smが印加されるたびにデータライン駆動回路120からR,G,B,データ信号DR1～DRn,DG1～DGn,DB1～DBnが同時にR,G,Bデータラインに印加される。これによって画素が駆動する。

#### 【0080】

これに対して、本実施の形態によれば、1フレームが3サブフレームに分割され、各サブフレームにおいて、各ゲートラインにゲートライン駆動回路510からスキャン信号がそれぞれ印加される。このため、1フレームの間に、3m個のスキャン信号が印加される。第1画素については、まず、第1サブフレームにおいて、第1ゲートライン511にスキャン信号S1が印加され、スイッチングトランジスタM51がターンオンしてデータライン521からRデータ信号DR1が駆動トランジスタM52に提供される。このとき、順次制御手段550において、論理的低レベル（以下、「Lレベル」という）の第1発光制御信号EC\_11と論理的高レベル（以下、「Hレベル」という）の第2発光制御信号EC\_21に応じて第1制御手段であるトランジスタM55\_R1とトランジスタM55\_R2がターンオンしているため、Rデータ信号DR1がR-EL素子EL1\_Rに供給され、R-EL素子EL1\_Rが駆動する。10

#### 【0081】

次に、第2サブフレームにおいて、第1ゲートライン511にスキャン信号S1が印加され、データライン521からGデータ信号DG1が駆動トランジスタM52に提供される。このとき、順次制御手段550において、Hレベルの第2発光制御信号EC\_11とLレベルの第2発光制御信号EC\_21に応じて第2制御手段であるトランジスタM55\_G1とトランジスタM55\_G2がターンオンしているため、Gデータ信号DG1がG-EL素子EL1\_Gに供給され、G-EL素子EL1\_Gが駆動する。20

#### 【0082】

最後に、第3サブフレームにおいて、第1ゲートライン511にスキャン信号S1が印加され、データライン521からBデータ信号DB1が駆動トランジスタM52に提供される。このとき、順次制御手段550において、Hレベルの第3発光制御信号EC\_11とHレベルの第2発光制御信号EC\_21に応じて第3制御手段であるトランジスタM55\_B1とトランジスタM55\_B2がターンオンしているため、Bデータ信号DB1がB-EL素子EL1\_Bに供給され、B-EL素子EL1\_Bが駆動する。30

#### 【0083】

このように、1フレームを構成する各サブフレームにおいて、スキャン信号S1～Smが印加されると、その度に各データラインにRデータ信号DR1～DRn,Gデータ信号DG1～DGn,Bデータ信号DB1～DBnが順に印加される。この結果、画素P11～PmnのR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bは、能動素子570を共有することになる。したがって、各画素P11～Pmnにおいて、一つのゲートライン、一つのデータライン、そして、一つの電源供給ラインだけが必要となり、回路構成の単純化が実現する。また、二つの発光制御ラインだけが必要となるため、ピクセル回路の配線がさらに単純化され、R,G,B-EL素子の発光をさらに簡単に制御できる。40

#### 【0084】

このように、本実施の形態に係るピクセル回路は、画素P11～Pmnそれぞれに属するR,G,B-EL素子EL1\_R,EL1\_G,EL1\_Bは、能動素子570を共有することになる。したがって、各画素P11～Pmnにおいて、一つのゲートライン、一つのデータライン、そして、一つの電源供給ラインだけが必要となり、回路構成の単純化が実現する。また、二つの発光制御ラインだけが必要となるため、ピクセル回路の配線がさらに単純化され、R,G,B-EL素子の発光をさらに簡単に制御できる。

#### 【0085】

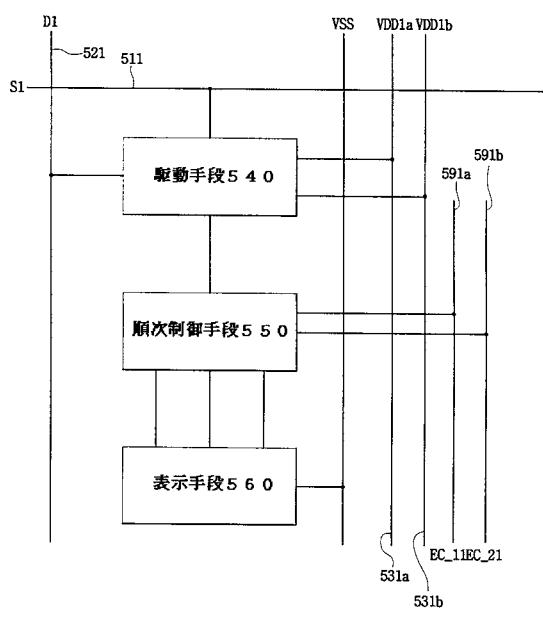

図6は、本発明の第1の実施の形態に係る有機電界発光表示装置が備える画素部の他の

50

例を示したブロック図である。図9は、図6に示した順次駆動方式の有機電界発光表示装置のピクセル回路の、また他のブロック構成を示したものであり、図11は、図9のピクセル回路の詳細回路の例を示したものである。図6、図9、及び図11に示すピクセル回路は、図5、図8、及び図10のピクセル回路に類似している。相違点としては、図6、図9、及び図11に示したピクセル回路では、駆動手段540のキャパシタC51と駆動トランジスタM52のソースに対して、同じ電源ライン531を通じて同じ電源電圧VD D1が提供されたが、図5、図8、及び図10に示したピクセル回路には、個別の電源ラインが備えられており、キャパシタC51には電源ライン531bを通じて電源電圧VD D1bが提供され、駆動トランジスタM52のソースには電源ライン531aを通じて電源電圧VDD1aが提供される。このように、キャパシタC51に供給される電源ラインと駆動トランジスタに供給される電源ラインを分離することによって、キャパシタC51にデータ信号をより安定的に貯蔵できるようになる。

10

## 【0086】

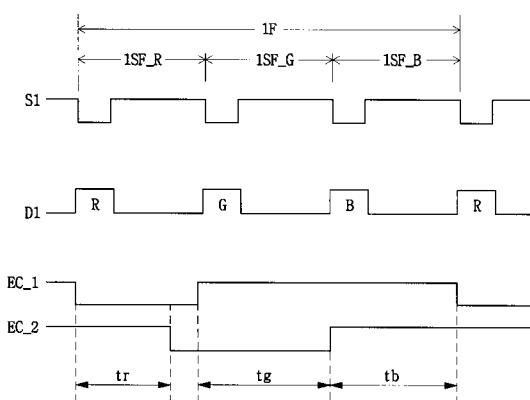

次に、前述したような構成を有する本発明の第1の実施の形態に係る有機電界発光表示装置を時分割的に順次駆動する方法について、図12の駆動波形図を参照しながら詳しく説明する。

## 【0087】

まず、第1フレーム1Fの第1サブフレーム1SF\_Rにおいて、ゲートライン駆動回路510から第1ゲートライン511にスキャン信号S1(R)が印加されると、第1ゲートライン511が活性化し、データライン駆動回路520からデータ信号D1～DnとしてRデータ信号DR1～DRnが第1ゲートライン511に接続された画素P11～P1nの駆動トランジスタM52のゲートに提供される。このとき、発光制御信号発生回路590から発光制御ライン591a、591bを通って、第1ゲートライン511に接続された画素P11～P1nのR-EL素子EL\_Rを制御するためのLレベルの第1発光制御信号EC\_11とHレベルの第2発光制御信号EC\_21が順次制御手段550に印加され、トランジスタM55\_R1とトランジスタM55\_R2がターンオンする。これによって、Rデータ信号DR1～DRnに応じた駆動電流がR-EL素子に提供され、R-EL素子が駆動する。

20

## 【0088】

続いて、第1フレーム1Fの第2サブフレーム1SF\_Gにおいて、第1ゲートライン511に二つ目のスキャン信号S1(G)が印加されると、データライン521～52nに流れるGデータ信号DG1～DGnが駆動トランジスタM52のゲートに提供される。このとき、発光制御信号発生回路590から発光制御ライン591a、591bを通って、第1ゲートライン511に接続された画素P11～P1nのG-EL素子EL\_Gを制御するためのHレベルの第1発光制御信号EC\_11とLレベルの第2発光制御信号EC\_21が順次制御手段550に印加され、トランジスタM55\_G1とトランジスタM55\_G2がターンオンする。これによって、Gデータ信号DG1～DGnに応じた駆動電流がG-EL素子に提供され、G-EL素子が駆動する。

30

## 【0089】

そして、第1フレーム1Fの第3サブフレーム1SF\_Bにおいて、第1ゲートライン511に三つ目のスキャン信号S1(B)が印加されると、データライン521～52nに流れるBデータ信号DB1～DBnが駆動トランジスタM52のゲートに提供される。このとき、発光制御信号発生回路590から発光制御ライン591a、591bを通って、第1ゲートライン511に接続された画素P11～P1nのB-EL素子EL\_Bを制御するためのHレベルの第1発光制御信号EC\_11とHLレベルの第2発光制御信号EC\_21が順次制御手段550に印加され、トランジスタM55\_B1とトランジスタM55\_B2がターンオンする。これによって、Bデータ信号DB1～DBnに応じた駆動電流がB-EL素子に提供され、B-EL素子が駆動する。

40

## 【0090】

同様に、第1フレーム1Fの各サブフレームにおいて、第2ゲートライン512にスキ

50

ヤン信号 S 2 が印加されると、前述のようにデータライン 521～52n に R, G, B データ信号 DR1～DRn, DG1～DGl, DB1～DBn が順次印加される。また、発光制御信号発生回路 590 から発光制御ライン 591a, 591b を通って、第 2 ゲートライン 512 に接続された画素 P21～P2n の R, G, B - EL 素子を制御するための第 1 発光制御信号 EC\_12, 第 2 発光制御信号 EC\_22 が順次制御手段 550 に順次入力される。これによって、トランジスタ M55\_R1 とトランジスタ M55\_R2, トランジスタ M55\_G1 とトランジスタ M55\_G2, トランジスタ M55\_B1 とトランジスタ M55\_B2 が順次ターンオンし、R, G, B データ信号 DR1～DRn, DG1～DGl, DB1～DBn に応じた駆動電流が R, G, B - EL 素子に順次提供され、R, G, B - EL 素子が駆動する。

10

## 【0091】

このような動作は、第 1 フレーム 1F の各サブフレームにおいて、第 m ゲートライン 51m まで繰り返し行われる。第 m ゲートライン 51m にスキャン信号 Sm が印加されると、データライン 521～52n に R, G, B データ信号 DR1～DRn, DG1～DGl, DB1～DBn が順次印加される。また、発光制御信号発生回路 590 から発光制御ライン 59ma, 59mb を通って、第 m ゲートライン 51m に接続された画素 Pm1～Pmn の R, G, B - EL 素子を制御するための第 1 発光制御信号 EC\_1m, 第 2 発光制御信号 EC\_2m が順次制御手段 550 に順次入力される。これによって、トランジスタ M55\_R1 とトランジスタ M55\_R2, トランジスタ M55\_G1 とトランジスタ M55\_G2, トランジスタ M55\_B1 とトランジスタ M55\_B2 が順次ターンオンし、R, G, B データ信号 DR1～DRn, DG1～DGl, DB1～DBn に応じた駆動電流が R, G, B - EL 素子に順次提供され、R, G, B - EL 素子が駆動する。

20

## 【0092】

以上のように、本実施の形態にかかる有機電界発光表示装置の駆動方法によれば、1つのフレームは3つのサブフレームに分割され、各サブフレームにおいて、R, G, B - EL 素子を順次駆動させることによって画素が表示されるようになる。このとき、R, G, B - EL 素子は順に駆動されるが、R, G, B - EL 素子の順次駆動サイクルを短く調整すれば、人間の目には R, G, B - EL 素子があたかも同時に駆動されているように認識される。つまり、各画素はちらつくことなく正常に画像表示される。

30

## 【0093】

また、本発明の第 1 の実施の形態に係る有機電界発光表示装置によれば、R, G, B - EL 素子の発光時間を調節してホワイトバランスを調節できる。R, G, B - EL 素子の発光時間を調節するためには、図 10 及び図 11 の順次制御手段 550 のトランジスタ M55\_R1 とトランジスタ M55\_R2, トランジスタ M55\_G1 とトランジスタ M55\_G2, トランジスタ M55\_B1 とトランジスタ M55\_B2 の各ターンオン時間を調節すればよい。

40

## 【0094】

具体的には、図 13 に示したように、各サブフレームにおいて、発光制御信号発生手段 590 が出力する第 1 発光制御信号 EC\_11 と第 2 発光制御信号 EC\_21 の論理レベルの組み合わせの時間を調節する。この時間に応じて順次制御手段 550 のトランジスタ M55\_R1 とトランジスタ M55\_R2, トランジスタ M55\_G1 とトランジスタ M55\_G2, トランジスタ M55\_B1 とトランジスタ M55\_B2 のターンオン時間 tr, tg, tb が決定される。

40

## 【0095】

本実施の形態では、二つの発光制御信号、すなわち第 1 発光制御信号 EC\_11 と第 2 発光制御信号 EC\_21 によって、R, G, B - EL 素子の順次発光が制御される。例えば図 13 に示したように、R, G, B - EL 素子のうち、R - EL 素子のターンオン時間 tr (発光時間) と G - EL 素子のターンオン時間 tg (発光時間) を定常状態から変更することによってホワイトバランスを調節することが可能となる。このように、R - EL 素子のターンオン時間 tr, G - EL 素子のターンオン時間 tg, 及び B - EL 素子のターンオン時間 tb が決定される。

50

ーンオン時間  $t_b$  を適宜調節すれば、最適なホワイトバランスを得ることができる。

【0096】

本実施の形態によれば、前述したように R, G, B 発光時間を調整してホワイトバランスを調整するだけでなく、図 13 のように、R, G, B 発光時間を 1 次に調整してホワイトバランスを調整した上で、明るさを最適化するために、R, G, B 発光時間をさらに調整するようにしてもよい。

【0097】

以上のように、本発明の第 1 の実施の形態によれば、R, G, B - E L 素子が駆動薄膜トランジスタとスイッチング薄膜トランジスタを共有して時分割的に駆動するため、高精細化が可能であり、素子数及び配線数を減少させ開口率及び収率を向上することができる。また、本実施の形態は、順次駆動方式を採用しているため、RC ディレイ及び電圧降下 (IR drop) を防止することも可能となる。

【0098】

しかも、本実施の形態によれば、各 R, G, B - E L 素子は、2 つの発光制御信号によって駆動制御される。このため、回路構成の一層の簡素化が実現する。

【0099】

(第 2 の実施の形態)

図 14 は、本発明の第 2 の実施の形態に係る有機電界発光表示装置の構成を示すブロック図である。図 14 に示した第 2 の実施の形態に係る有機電界発光表示装置は、図 4 に示した第 1 の実施の形態に係る有機電界発光表示装置に対して、ゲートライン駆動回路 510 が二つのゲートライン駆動回路 510a, 510b に置き換えられ、発光制御信号発生回路 590 が二つの発光制御信号発生回路 590a, 590b に置き換えられた構成を有する。

【0100】

すなわち、本実施の形態にかかる有機電界発光表示装置は、多数のゲートライン 511 ~ 51n のうち、第 1 ゲートライン駆動回路 510a から一のゲートライン群にスキャン信号が提供され、第 2 ゲートライン駆動回路 510b から他のゲートライン群にスキャン信号が提供されるように構成されている。このとき、ゲートライン 511 ~ 51n のうち、上段にレイアウトされているゲートラインには第 1 ゲートライン駆動回路 510a からスキャン信号 S1 ~ Sk-1 (1 < k < m) が印加され、下段にレイアウトされているゲートラインには第 2 ゲートライン駆動回路 510b からスキャン信号 Sk ~ Sm が順に印加されるように構成することが可能である。また、偶数番目にレイアウトされているゲートラインには第 1 ゲートライン駆動回路 510a からスキャン信号が印加され、奇数番目にレイアウトされているゲートラインには第 2 ゲートライン駆動回路 510b からスキャン信号が印加されるように構成することも好ましい。これによって、画素部に配列されるゲートラインの密度を減少させることができる。また、第 1 ゲートライン駆動回路 510a 及び第 2 ゲートライン駆動回路 510b から同時にゲートラインにスキャン信号を供給することによって信号の伝送遅延を防止することが可能となる。さらに、第 1 ゲートライン駆動回路 510a と第 2 ゲートライン駆動回路 510b を備えることによって、冗長性を高めることも可能となる。すなわち、第 1 ゲートライン駆動回路 510a と第 2 ゲートライン駆動回路 510b のうち一方が故障しても他方によって冗長救済することができる。

【0101】

また、本実施の形態にかかる有機電界発光表示装置は、多数の発光制御ライン 591 ~ 59n のうち、第 1 発光制御信号発生回路 590a から一の発光制御ライン群に発光制御信号が提供され、第 2 発光制御信号発生回路 590b から他の発光制御ライン群に発光制御信号が提供されるように構成されている。このとき、発光制御信号ライン 591 ~ 59n のうち、上段にレイアウトされている発光制御ラインには第 1 発光制御信号発生回路 590a から発光制御信号が印加され、下段にレイアウトされている発光制御ラインには第 2 発光制御信号発生回路 590b から発光制御信号が順に印加されるように構成すること

10

20

30

40

50

が可能である。また、偶数番目にレイアウトされている発光制御ラインには第1発光制御信号発生回路590aから発光制御信号が印加され、奇数番目にレイアウトされている発光制御ラインには第2発光制御信号発生回路590bから発光制御信号が印加されるよう構成することも好ましい。これによって、画素部に配列される発光制御ラインの密度を減少させることができる。また、第1発光制御信号発生回路590a及び第2発光制御信号発生回路590bから同時に発光制御ラインに発光制御信号を供給することによって信号の伝送遅延を防止することが可能となる。さらに、第1発光制御信号発生回路590aと第2発光制御信号発生回路590bを備えることによって、冗長性を高めることも可能となる。すなわち、第1発光制御信号発生回路590aと第2発光制御信号発生回路590bのうち一方が故障しても他方によって冗長救済することができる。

10

#### 【0102】

##### (第3の実施の形態)

図15は、本発明の第3の実施の形態に係る有機電界発光表示装置の構成を示すブロック図である。図15に示した第3の実施の形態に係る有機電界発光表示装置は、図14に示した第2の実施の形態に係る有機電界発光表示装置に対して、二つのゲートライン駆動回路510a, 510bと二つの発光制御信号発生回路590a, 590bのレイアウト位置が相違している。このように、ゲートライン駆動回路や発光制御信号発生回路を2以上に分割することによって、基板上のレイアウト位置の自由度が高まる。これは、有機電界発光表示装置の小型化にも有利である。

20

#### 【0103】

なお、本発明の第2の実施の形態及び第3の実施の形態では、ゲートライン駆動回路と発光制御信号発生回路が二つ（またはそれ以上）に分割され、各回路が多段に配列されているが、データライン駆動回路を複数備えて各データライン駆動回路を多段に配列することもできる。

#### 【0104】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

30

#### 【産業上の利用可能性】

#### 【0105】

本発明は、EL表示装置、FED(Field Emission Display)、PDP(Plasma Display Panel)のような発光素子を採用する表示装置に適用可能である。

#### 【図面の簡単な説明】

#### 【0106】

【図1】一般的な有機電界発光表示装置を示す構成図である。

【図2】図1の有機電界発光表示装置のピクセル回路を示す構成図である。

【図3】図1の有機電界発光表示装置の動作波形図である。

【図4】本発明の第1の実施の形態に係る有機電界発光表示装置を示すブロック構成図である。

40

【図5】図4の有機電界発光表示装置の画素部の構成例を示す図である。

【図6】図4の有機電界発光表示装置の画素部の他の構成例を示す図である。

【図7】同実施の形態に係る有機電界発光表示装置のピクセル回路を示す概略図である。

【図8】図5の有機電界発光表示装置のピクセル回路を示すブロック構成図である。

【図9】図6の有機電界発光表示装置のピクセル回路を示すブロック構成図である。

【図10】図8の有機電界発光表示装置のピクセル回路を示す詳細回路図である。

【図11】図9の有機電界発光表示装置のピクセル回路を示す詳細回路図である。

【図12】同実施の形態に係る有機電界発光表示装置のピクセル回路の駆動波形を示す図である。

50

【図13】同実施の形態に係る有機電界発光表示装置におけるホワイトバランスの具現例を説明するための駆動波形を示す図である。

【図14】本発明の第2の実施の形態に係る有機電界発光表示装置のブロック構成図である。

【図15】本発明の第3の実施の形態に係る有機電界発光表示装置のブロック構成図である。

### 【符号の説明】

#### 【0107】

500：画素部

510, 510a, 510b：ゲートライン駆動回路

511～51m：ゲートライン

520：データライン駆動回路

521～52n：データライン

531～53n：電源ライン

540：駆動手段

550：順次制御手段

570：能動素子

590, 590a, 590b：発光制御信号発生回路

P11～Pmn：画素

EC\_11：第1発光制御信号

EC\_21：第2発光制御信号

EL1\_R：R-EEL素子

EL1\_G：G-EEL素子

EL1\_B：B-EEL素子

10

20

【図1】

【図2】

【 図 3 】

【 図 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【図13】

【 図 1 4 】

【図15】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

| F I           | テーマコード(参考) |

|---------------|------------|

| G 0 9 G 3/20  | 6 2 4 B    |

| G 0 9 G 3/20  | 6 4 1 E    |

| G 0 9 G 3/20  | 6 4 2 K    |

| G 0 9 G 3/20  | 6 4 2 L    |

| G 0 9 G 3/22  | E          |

| H 0 5 B 33/14 | A          |

| G 0 9 G 3/28  | H          |

F ターム(参考) 5C080 AA05 AA06 AA08 AA18 BB05 CC03 DD05 DD08 DD23 DD28

EE29 EE30 FF11 HH09 JJ02 JJ03 JJ04 KK07

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的像素电路，显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2005148750A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2005-06-09 |

| 申请号            | JP2004330894                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2004-11-15 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 郭源奎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 郭 源奎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/22 G09G3/291 G09G3/296 G09G3/30 G09G3/32 G09G3/28 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G3/2022 G09G3/3233 G09G2300/0465 G09G2300/0814 G09G2300/0842 G09G2300/0861<br>G09G2300/0866 G09G2310/0235 G09G2310/06 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.F G09G3/20.611.J G09G3/20.621.A G09G3/20.621.J G09G3/20.624.B<br>G09G3/20.641.E G09G3/20.642.K G09G3/20.642.L G09G3/22.E H05B33/14.A G09G3/28.H G09G3<br>/296 G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB17 3K007/AB18 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA05 5C080<br>/AA06 5C080/AA08 5C080/AA18 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD08 5C080/DD23<br>5C080/DD28 5C080/EE29 5C080/EE30 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080<br>/JJ04 5C080/KK07 3K107/AA01 3K107/BB01 3K107/CC08 3K107/CC35 3K107/CC36 3K107/CC45<br>3K107/DD39 3K107/EE04 3K107/EE07 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380<br>/AB34 5C380/AB36 5C380/AB41 5C380/AB46 5C380/AC12 5C380/BA12 5C380/BA13 5C380/BA19<br>5C380/BA20 5C380/BA27 5C380/BA29 5C380/BA39 5C380/BB12 5C380/BB14 5C380/BB22 5C380<br>/CA08 5C380/CA12 5C380/CA53 5C380/CB01 5C380/CB02 5C380/CB18 5C380/CB24 5C380/CB25<br>5C380/CB26 5C380/CB31 5C380/CC03 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380<br>/CC41 5C380/CC53 5C380/CC59 5C380/CC61 5C380/CC64 5C380/CD014 5C380/CF54 5C380/DA02<br>5C380/DA10 5C380/DA19 5C380/DA35 5C580/BB21 5C580/BB27 5C580/CA06 5C580/CB01 5C580<br>/CB10 |         |            |

| 优先权            | 1020030080739 2003-11-14 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP4209832B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

提供一种显示装置的像素电路及其驱动方法，其可以实现高清晰度，提高开口率，提高成品率，防止RC延迟和电压降以及简化像素配置和布线。有机发光显示装置包括多个发光装置 ( EL1\_R , EL1\_G , EL1\_B )，每个发光装置在显示装置的像素电路中的预定区段中发射一种颜色，该像素装置在每个预定区段中实现预定颜色。有源元件 ( 540、550 ) 通常连接到这些发光元件以驱动每个发光元件。有源元件在预定区间内的每个预定时间段内依次驱动每个发光元件，从而每个发光元件在每个预定时间段内依次发光。[选择图]图10