(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-506924

(P2004-506924A)

(43) 公表日 平成16年3月4日(2004.3.4)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611D

5C080

G09G 3/20

621M

G09G 3/20

623V

G09G 3/20

680G

審査請求 未請求 予備審査請求 未請求 (全 31 頁) 最終頁に続く

(21) 出願番号

特願2001-534130(P2001-534130)

(86) (22) 出願日

平成12年9月27日(2000.9.27)

(85) 翻訳文提出日

平成13年6月25日(2001.6.25)

(86) 國際出願番号

PCT/EP2000/009504

(87) 國際公開番号

W02001/031624

(87) 國際公開日

平成13年5月3日(2001.5.3)

(31) 優先権主張番号

9925060.7

(32) 優先日

平成11年10月23日(1999.10.23)

(33) 優先権主張國

イギリス(GB)

(81) 指定国

EP(AT, BE, CH, CY, DE, DK, ES, FI, FR,

GB, GR, IE, IT, LU, MC, NL, PT, SE), JP, KR

(71) 出願人

590000248 コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

Koninklijke Philips Electronics N. V.

オランダ国 5621 ペーー アイン

ドーフェン フルーネヴァウツウェッハ

1

Groenewoudseweg 1, 5

621 BA Eindhoven, The Netherlands

(74) 代理人

100072051

弁理士 杉村 興作

最終頁に続く

(54) 【発明の名称】アクティブマトリックス電界発光表示装置

## (57) 【要約】

アクティブマトリックス電界発光(E L)表示装置は、基板(25)上に、E L表示素子(20)と、駆動周期においてこの素子を流れる電流を前のアドレス周期において印加されたデータ信号に基づいて制御する駆動装置(22)とを各々具える画素(10)のアレイと、前記画素にアドレス導体(12, 14)を経て接続され、前記画素の行を選択し、データ信号を前記選択された行の画素の各自に個々の行アドレス周期において供給する駆動回路(16, 18)とを有する。前記データ信号を、駆動I C(40)によって供給する。必要なI Cの数を減らすために、多重化回路(45)を、前記基板(25)上に前記画素アレイと共に集積し、前記駆動I Cの出力部(41)と、前記アドレス導体(14)の1つの組との間に接続し、個々の駆動I C出力部からのデータ信号を個々の関連する複数のアドレス導体に1行アドレス周期において順次に印加するように動作可能とする。選択された行の画素の表示素子を、前記行アドレス周期において動作しないようにし、望ましくないクロストークの影響を回避する。行選択信号を、前記基板上に集積さ

**【特許請求の範囲】****【請求項 1】**

基板において搭載された画素の行及び列アレイを具え、各画素が電界発光表示素子と、駆動周期において前記表示素子を通る電流を前の行アドレス周期において印加されたデータ信号に基づいて制御する駆動装置とを具え、前記表示素子を前記駆動素子を経て1行の列に共通の電流ラインに接続し、周辺駆動回路を前記画素アレイに接続し、この駆動回路が、データ信号を発生すると共に画素の各々の行に個々の行アドレス周期において前記画素のアレイに接続されたアドレス導体の組を経て印加し、複数の出力部を有する少なくとも1つの駆動ICを具える、アクティブマトリックス電界発光表示装置において、前記少なくとも1つの駆動ICを前記アドレス導体の組に多重化回路を経て接続し、前記多重化回路が、前記基板において集積され、データ信号を前記駆動ICの各々の出力部から前記組における各々の複数のアドレス導体に前記行アドレス周期において順次に印加するように動作可能であり、前記駆動回路を、1行の画素の前記表示素子を流れる電流をその個々の行アドレス周期中に妨げるように配置したことを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 2】**

請求項1に記載のアクティブマトリックス電界発光表示装置において、前記1組のアドレス導体をグループにおいて編成し、各グループを個々の駆動IC出力部に関連付け、前記多重化回路が、データ信号を出力部からその関連するグループのアドレス導体の各々に同じ周期において供給するように動作可能なスイッチング装置を具えることを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 3】**

請求項2に記載のアクティブマトリックス電界発光表示装置において、前記画素の駆動装置と、前記多重化回路のスイッチング装置とが、すべて、p又はnチャネルTFTのいずれかを具えることを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 4】**

請求項2に記載のアクティブマトリックス電界発光表示装置において、前記画素の駆動装置と、前記多重化回路のスイッチング装置とが、p及びnチャネルTFTの双方を具えることを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 5】**

請求項4に記載のアクティブマトリックス電界発光表示装置において、前記周辺駆動回路が、前記基板上に集積され、p及びnチャネルTFTを具えるシフトレジスタ回路をさらに含むことを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 6】**

請求項1ないし5のいずれか1項に記載のアクティブマトリックス電界発光表示装置において、前記駆動回路を、前記列電流ラインに印加される電位を個々の前記行アドレス周期の間切り替えるように配置したことを特徴とするアクティブマトリックス電界発光表示装置。

**【請求項 7】**

請求項1ないし5のいずれか1項に記載のアクティブマトリックス電界発光表示装置において、1個の画素の前記表示素子をその関連する電流ラインにスイッチング装置を経て接続し、前記駆動回路を、前記スイッチング装置が前記表示素子を前記電流ラインから前記行アドレス周期の持続時間の間絶縁するように動作するように配置したことを特徴とするアクティブマトリックス電界発光表示装置。

**【発明の詳細な説明】****【0001】**

本発明は、電界発光表示素子のアレイを具えるアクティブマトリックス電界発光表示装置に関する。

**【0002】**

電界発光表示素子を用いるマトリックス表示装置は、よく知られている。前記表示素子は

、例えば、ポリマ材料を使用する有機薄膜電界発光素子、又は、他に、慣例的な I II - V 半導体混合物を使用する発光ダイオード( L E D )を具えててもよい。有機電界発光材料、特にポリマ材料における最近の開発は、特にビデオ表示装置に使用するこれらの能力を証明した。これらの材料は、代表的に、1対の電極の間に挟まれた電界発光材料、例えば、半導体複合ポリマの1つ以上の層を具え、前記電極の一方を透明とし、他方を、ホール又は電子を前記ポリマ層に注入するのに適した材料とする。前記ポリマ材料を、C V D プロセスを使用して、又は、簡単に、可溶性複合ポリマの溶液を使用するスピンドルティング技術によって形成することができる。

#### 【 0 0 0 3 】

有機電界発光材料は、ダイオード様 I - V 特性を示し、その結果、これらは、表示機能及びスイッチング機能の双方を与えることができ、したがって、パッシブ型ディスプレイにおいて使用することができる。10

#### 【 0 0 0 4 】

しかしながら、本発明は、各々の画素が表示素子と前記表示素子を通る電流を制御する駆動装置とを具えるアクティブマトリックス表示装置に関する。アクティブマトリックス表示装置の例は、欧州特許出願公開明細書第 0 6 5 3 7 4 1 号及び第 0 7 1 7 4 4 6 号において記載されている。表示素子が容量性であり、したがって、実質上電流を受け取らず、駆動(データ)信号電圧を全フレーム時間の間キャパシタンスにおいて格納することができるアクティブマトリックス液晶表示装置と異なり、電界発光表示素子は連続的に電流を通し、光を発生する必要がある。通常、T F T (薄膜トランジスタ)を具える画素の駆動装置は、前記表示素子を通過する電流を制御する責任を負う。前記表示素子の輝度は、該表示素子を通過する電流に依存する。ある画素に関するアドレス周期中、前記表示素子からの必要な出力を決定する駆動(データ)信号を、前記画素に印加し、接続されると共に前記電流制御駆動装置の動作を制御する格納キャパシタにおいて対応する電圧として格納し、前記キャパシタにおいて格納された電圧は、前記画素が再びアドレスされるまでフレーム周期に対応する次の駆動周期中に前記表示素子を通る電流を供給することにおいて前記駆動装置の動作を保持するように働く。20

#### 【 0 0 0 5 】

代表的に、前記画素を行及び列アドレス導体の組に接続し、前記導体の組を通じて選択(走査)信号及びアナログ電圧データ信号を周辺駆動回路によって供給し、画素の各々の行をその関連する行導体に印加された選択信号によって個々の行アドレス周期において選択し、前記選択された行の画素に関する前記データ信号を前記列導体を経て印加する。前記データ信号を、シリコン集積回路( I C )チップを具える列駆動回路によって供給することができる。各チップは、制限された数の個々の間隔を置いた出力接点を有する。各列導体を個々のチップ出力部に接続し、したがって、多数のチップを通常は必要とする。例えば、1行において 8 0 0 画素が存在し、1チップが 1 0 0 出力を供給できる場合、8チップが、関係する 8 0 0 行導体を供給するのに必要である。30

#### 【 0 0 0 6 】

個々の行又は列におけるすべての画素の電界発光表示素子を、これらの関係する駆動装置を経て共通電流ラインに接続する。前記画素の格納キャパシタもこれらの共通ラインに接続し、前記電流ラインのこのような共有は、動作において一種のクロストークを生じる影響を有する電圧低下がこれらのラインに沿って生じる恐れがある他の問題に至る。40

#### 【 0 0 0 7 】

本発明の目的は、改善されたアクティブマトリックス電界発光表示装置を提供することである。

#### 【 0 0 0 8 】

本発明によれば、基板において搭載された画素の行及び列アレイを具え、各画素が電界発光表示素子と、駆動周期において前記表示素子を通る電流を前の行アドレス周期において印加されたデータ信号に基づいて制御する駆動装置とを具え、前記表示素子を前記駆動素子を経て1行の列に共通の電流ラインに接続し、周辺駆動回路を前記画素アレイに接続し50

、この駆動回路が、データ信号を発生すると共に画素の各々の行に個々の行アドレス周期において前記画素のアレイに接続されたアドレス導体の組を経て印加し、複数の出力部を有する少なくとも1つの駆動ICを具える、アクティブマトリックス電界発光表示装置において、前記少なくとも1つの駆動ICを前記アドレス導体の組に多重化回路を経て接続し、前記多重化回路が、前記基板において集積され、データ信号を前記駆動ICの各々の出力部から前記組における各々の複数のアドレス導体に前記行アドレス周期において順次に印加するように動作可能であり、前記駆動回路を、1行の画素の前記表示素子を流れる電流をその個々の行アドレス周期中に妨げるように配置したことを特徴とするアクティブマトリックス電界発光表示装置が提供される。

## 【0009】

10

このように動作可能な前記装置基板上における多重化回路の集積によって、より少ない回路しか所定の数の列の画素を有する装置には必要なくなるため、重大な費用節約が可能である。例えば、個々の駆動IC出力によって供給されるアドレス導体の各グループが4つのアドレス導体を有する4:1の多重化比に関して、必要な前記駆動ICの費用は、単一のIC出力部が個々の単一のアドレス導体に占有的に接続される場合と比較して75%減少する。前記画素を製造するのに用いられる同じ薄膜製造技術を使用して、前記集積多重化回路は、わずかな追加の費用において、又は追加の費用無しで与えられ、共通薄膜層を使用すると共にTFT及び導体ラインのような同様の薄膜回路素子を有する前記画素の薄膜素子と同時に形成することができる。前記多重化回路において使用する多重化スイッチを、好適には、前記画素アレイにおいて使用するのと同じ形式のもの、例えば、p又はn型ポリシリコンTFTとする。したがって、前記画素アレイ及び多重化回路を形成する前記装置基板上の薄膜回路網を、種々の導体層、絶縁層及び半導体層の堆積及びパターン化を含む標準的な薄膜技術を使用して製造することができる。同じ形式のスイッチング装置、例えばp又はnチャネルシリコンのいずれかを使用する前記画素回路及び集積多重化回路に関して、前記アレイと前記多重化回路の一連の製造は、重大に簡単になり、代表的に、p及びチャネル(COMS)TFTの双方を製造するのに通常必要とされるような9又は10マスクプロセスより、5又は6マスクプロセスのみを必要とするようになる。

20

## 【0010】

30

しかしながら、p及びn型TFTの双方を使用することができ、これはCMOS回路を必要とするシフトレジスタのような回路網を前記駆動基板において同様に集積することを可能にする。シフトレジスタを、前記列駆動回路において、及び/又は、前記行駆動(選択)回路において使用することができる。拡張集積を可能にすることにおけるp及びn(CMOS)装置の双方を使用することの利益は、より複雑化された(より多いマスク総数)製造プロセスの必要なものに関して考慮する必要がある。

## 【0011】

40

各行の画素を、これらのデータ信号で個々の行アドレス周期においてアドレスし、この周期中、前記多重化回路は動作し、データ信号を時分割様式において前記行における各グループの画素に順次に供給する。前記表示素子をこれらのアドレスの周期中に流れる電流を防ぐことによって、固有抵抗によってこれらの共有電流ラインにおいて生じる電圧降下によって生じるクロストーク効果に関する問題は回避される。このような防止を、前記表示素子を、単に個々の画素がアドレスされる部分ではなく完全な全体的な行アドレス周期中にゼロ又は逆バイアスすることを保証することによって成し遂げることができる。この目的のため、前記共通電流ラインに印加される電位を切り替えてよく、又は、他のTFTのようなスイッチング装置を、前記表示素子を前記電流ラインから前記行アドレス周期の持続期間中に遮断するように動作可能にする。

## 【0012】

本発明によるアクティブマトリックス電界発光表示装置の位置実施形態を、ここで、例として、添付した図面の参照と共に説明する。

## 【0013】

図面は単に図式的なものである。同じ参照符を、これらの図面を通じて、同じ又は同様の

50

部分を示すために使用した。

【0014】

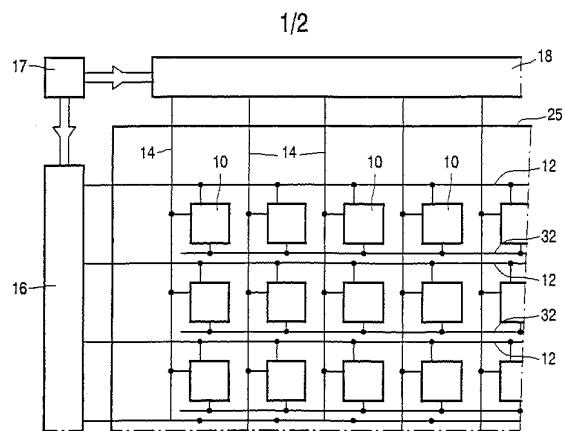

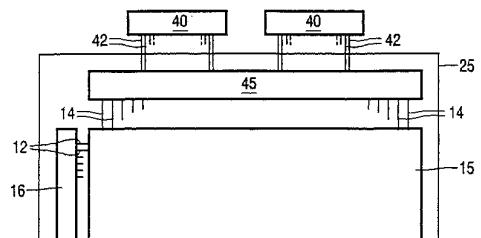

図1を参照し、アクティブマトリックス電界発光表示素子は、基板25上に搭載されたブロック10によって示される規則正しく間隔を置いた画素の行及び列マトリックスアレイを有するパネルを具え、前記画素の各々は、電界発光表示素子と、この表示素子を通る電流を制御する関連する駆動装置とを具え、前記基板上に搭載された行(選択)及び列(データ)アドレス導体すなわちラインの交差する組の間の交点において位置する。簡単にするために、いくつかの画素のみを示す。画素10を、前記アドレス導体の組を経て周辺駆動回路によってアドレスし、前記周辺駆動回路は、前記パネルに接続された出力部を有し、前記行導体に順次に供給される走査信号を発生する行走査駆動回路16と、前記列導体に供給されるデータ信号を発生し、個々の画素表示素子からの表示出力を規定する列データ駆動回路18と、回路16及び18の動作を制御するタイミング及び制御ユニット17とを具える。10

【0015】

画素の各行を、回路16によって関連する行導体12に印加される選択信号によって、前記行の画素が、回路18によって前記列導体に並列に供給される個々のデータ信号にしたがって個々の駆動信号でロードされるようにアドレスする。各行がアドレスされると、前記データ信号は回路18によって適切な同期において供給される。

【0016】

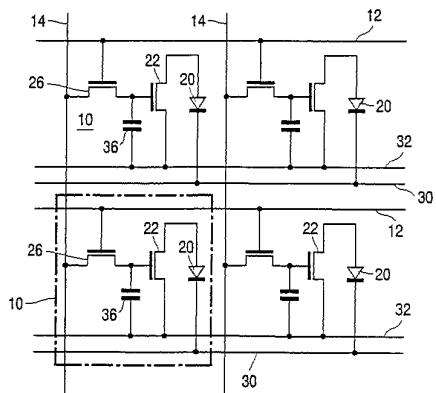

図2は、この既知の装置におけるいくつかの代表的な画素の回路を示す。各画素10は、ここではダイオード素子として表され、1つ以上の有機電界発光材料の活性層を挟んだ1対の電極を有する発光有機電界発光表示素子20を含む。この特定の実施形態において、前記材料は、低モル重量材料のような他の有機電界発光材料を使用できるとしても、ポリマLED材料を有する。前記アレイの表示素子を、関連するアクティブマトリックス回路網と共に、前記基板の一方の側において搭載する。前記表示素子のカソード又はアノードのいずれか一方を、透明導電材料で形成する。前記基板を、ガラスのような透明絶縁性のものとし、前記基板に最も近い個々の表示素子の電極は、ITOのような透明導電性材料から成ってもよく、前記電界発光層によって発生された光がこれらの電極を通過し、前記基板の他方の側におけるビューワに見えるようにすることができる。代わりに、前記光出力を、前記パネルの上部から見ることができ、この場合における表示素子アノードは、前記アレイにおけるすべての表示素子に共通の供給ラインを構成する連続ITO層の部分を有する。前記表示素子のカソードは、カルシウム又はマグネシウム銀合金のような低仕事関数を有する金属を有する。使用することができる好適な有機複合ポリマの例は、欧州特許出願公開明細書第0717446号において記載されている。前記画素のアレイ及びアドレス導体の組を、AMLCDに使用されるのと同様の標準的な薄膜プロセス技術を使用して製造し、このプロセス技術は、種々の導体層、絶縁層及び半導体層の堆積及びパターン化を含む。このような製造の例は、上述した欧州特許出願公開明細書第0717446号において記載されている。2030

【0017】

各画素10は、表示素子20の動作を前記画素に印加されたデータ信号電圧に基づいて制御するTFT22の形態における駆動装置を含む。ある画素に関する前記信号電圧を、画素の個々の列の間で共有される列導体14を経て供給する。列導体14を、アドレスTFT26を経て電流制御駆動トランジスタ22のゲートに結合する。ある行の画素のアドレスTFT26に関するゲートを、共通行導体12と一緒に結合する。40

【0018】

画素10の各行は、すべての画素に共通の連続電極として通常設けられる共通電圧供給ライン30と、個々の共通電力ライン32とを共有する。表示素子20及び駆動装置22を、電圧供給ライン30と共に電流ライン20との間に直列に接続し、共通電流ライン20は、供給ライン30に関して正電位であり、表示素子20を通る電流に関する電流ドレンとして作用する。表示素子20を流れる電流のレベルを、スイッチング装置22によっ50

て制御し、このレベルは、列導体 14 に供給される前記データ信号によって決定される格納された制御信号に応じるトランジスタ 22 におけるゲート電圧の関数である。

【 0 0 1 9 】

画素の行を、選択パルスを行導体 12 に印加する行駆動回路 16 によって選択し、前記選択パルスは、画素の個々の行に関するアドレス TFT 26 をスイッチオンし、その持続時間は、前記行アドレス周期を決定する。ビデオ情報から得られる電圧レベル（データ信号）を、列導体 14 に駆動回路 18 によって印加し、アドレス TFT 26 によって駆動トランジスタ 22 のゲートに移動する。画素の行が行導体 12 を経てアドレスされていない期間中、アドレストランジスタ 26 はターンオフするが、駆動トランジスタ 22 のゲートにおける電圧を、この次の駆動周期中に前記表示素子の動作を保持するように、駆動トランジスタ 22 と共に電流ライン 32 との間に接続された画素格納キャパシタ 36 によって保持する。駆動トランジスタ 22 のゲートと共に電流ライン 32 との間の電圧は、画素 10 の表示素子 20 を通過する電流を決定する。このように、前記表示素子を通過する電流は、駆動トランジスタ 22 のゲート - ソース電圧の関数である（n チャネル型トランジスタ 22 のソースを共通電流ライン 32 に接続し、トランジスタ 22 のドレインを表示素子 20 に接続する）。この電流は、前記画素の光出力レベル（グレイスケール）を制御する。

【 0 0 2 0 】

スイッチングトランジスタ 22 を、飽和状態において動作し、前記ゲート - ソース電圧が、前記ドレイン - ソース電圧にかかわりなく前記トランジスタを通る電流を管理するようする。したがって、前記ドレイン電圧のわずかな変化は、表示素子 20 を通る電流に影響を与えない。電圧供給ライン 30 における電圧は、したがって、前記画素の正確な動作に対して決定的ではない。

【 0 0 2 1 】

画素の各行を、個々の行アドレス周期において、各行の画素にこれらの駆動信号を順次にロードするようにアドレスし、前記画素を、これらが次にアドレスされるまで、次の駆動（フレーム）周期の間、所望の出力を与えるように設定する。

【 0 0 2 2 】

前記データ信号を、アドレス導体 14 の組に、複数の外部シリコン集積回路駆動回路 IC によって共通に供給し、これらの IC の各々が、導体 14 の個々の 1 つに各々接続された多数の別個の出力端子を有する。このように、各導体 14 は、個々の占有的で専用の関連する出力端子を必要とする。前記組において数 C の導体 14 が存在し、各駆動 IC が数 n の出力部を有する（C > > n とする）場合、数 C / n の駆動 IC を必要とする。代表的に、したがって少なくともいくつかの駆動 IC が必要であり、各 IC 出力部 / 行導体に関して 1 つである、これらとパネル薄膜回路網との間の個々の接続部の数は、相当になり、例えば、代表的なビデオ / データグラフィックディスプレイに関して 800 以上になる。

【 0 0 2 3 】

本発明の一態様によれば、多重化を利用し、必要な駆動 IC の数を減少する。駆動 IC 出力を、複数の列導体に渡って各々多重化する。各駆動 IC 出力部を使用し、個々の複数の列導体に関する前記データ信号を供給するため、前記出力部、したがって駆動 IC の合計数を、相當に減少することができる。例えば、4 : 1 の多重化比に関して、以前に必要だった駆動 IC 出力部の数の 4 分の 1 のみが必要であり、結果として、前駆駆動 IC に関して 75 % の費用節約になる。前記多重化回路を、前記基板上に集積し、すなわち、前記基板上に、薄膜技術を使用する前記画素アレイと同様に集積する。このような回路を、同様の薄膜回路素子を与える共通の堆積層を使用して前記画素アレイと同時に容易に製造することができる。

【 0 0 2 4 】

図 3 は、本発明による表示装置の位置実施形態における基本的な配置を図式的に示す。基板 25 において搭載された画素アレイを、ここでは一般的に 15 において示す。その出力部において前記画素に関するデータ信号を発生し、供給するこの例において 2 個である多数の駆動 IC チップ 40 を、基板 25 に外部的に設け、前記データ信号を供給するこれら

10

20

30

40

50

の個々の出力端子を、基板 25において集積された多重化回路 45の入力部に接続する。駆動 I Cが数 100の出力部を有するとし、例えば、前記アレイにおいて前記画素の数 800の列が存在し、回路 45の多重化比を 4:1とし、各 I C出力部が 4つの列に関するデータ信号を供給するようにした場合、2 個の駆動 I Cのみを使用する。ビデオ情報を、I C 40に一般的に慣例的な方法において、例えばディジタル形態において供給し、前記 I Cは、これらが関連する前記列に関するアナログ電圧データ信号を発生し、これらの信号を関連する出力部 42に供給するように動作する。

#### 【0025】

チップ 40を、前記装置において設け、例えば、他の種類のフラットパネルディスプレイの製造において既知の COG 又はタブボンディング技術を使用して、基板 25における薄膜回路網に相互接続することができる

10

#### 【0026】

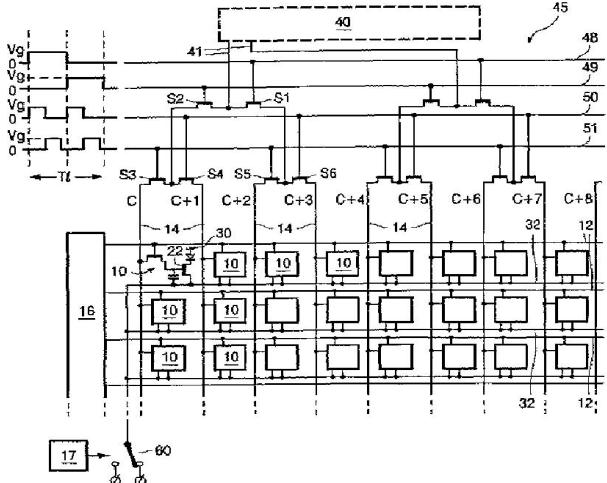

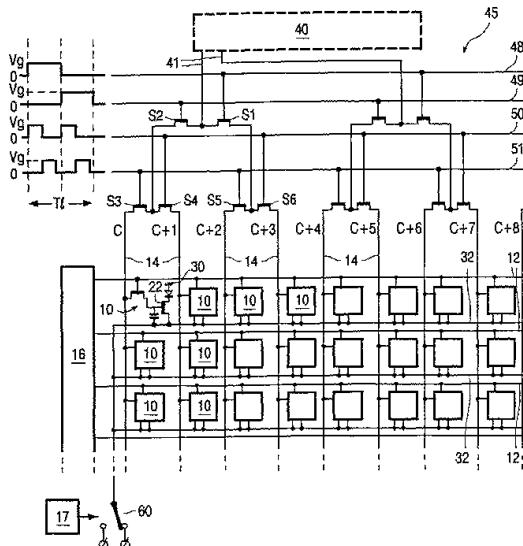

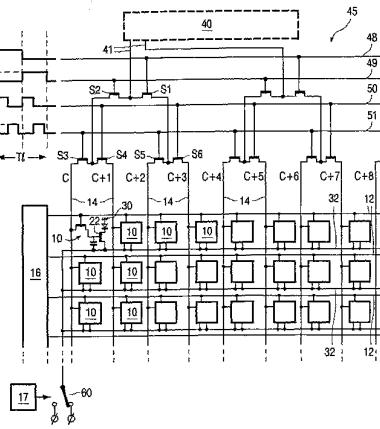

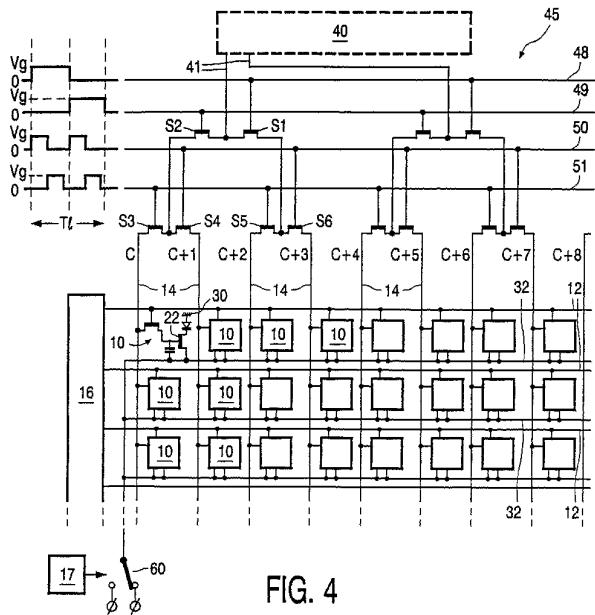

図 4 は、多重化回路 45 の特徴をより詳細に示す。この図は、前記装置のいくつかの代表的な画素と、多重化回路 45 の関連する部分とを、この回路の動作においてタイミング及び制御ユニット 17 によって印加される波形例と共に示す。前記画素回路は、他の既知の種類の画素回路を同様に使用することができるとしても、図 2 のものと同様である。

#### 【0027】

画素 10 の列及びこれらの列導体 14 を、4 のグループに編成し、図 4 に示す数 8 の連続する列導体 Cないし C+7 は、2 つのこのようなグループを構成する。列の各グループは、同じ個々の駆動 I C 41 を共有し、これら 4 列における画素に関する前記データ信号を 1 つの出力部 41 によって供給する。

20

#### 【0028】

多重化回路 45 は、4 つの制御信号バスライン 48、49、50 及び 51 の組を具える。4 列の各グループを、これらのバスラインに、TFT から成り、S1ないし S6 とラベル付けされた 6 個のマルチプレクサスイッチを経て接続する。例えば、列導体 Cないし C+1 から成る第 1 グループを取り上げると、これらの列導体を、各々、TFTS3ないし S6 に接続し、S3 及び S5 のゲートをバスライン 51 に接続し、S4 及び S6 のゲートをバスライン 50 に接続する。データ信号を、TFTS3 及び S4 の対と、TFTS5 及び S6 の対とに、各々、TFTS2 及び S1 を経て供給し、これらの TFTS2 及び S1 のゲートを、各々、バスライン 49 及び 48 に接続する。

30

#### 【0029】

あるグループの TFT を、前記バスラインに供給される制御（ゲート）信号によって、時分割方式において、1 行アドレス周期において特定の順序において動作するように配置し、他のグループの各々における対応する TFT を、前記制御信号によって同時に動作する。これらのバスラインに関する制御信号波形例を、これらの各々のラインの隣に示し、これらの波形は、前記 TFT をターンオンするのに有効なパルス信号を具える。

#### 【0030】

1 行の画素にこれらのデータ信号を供給すべき T<sub>L</sub> によって示す行アドレス周期の最初の半分において、前記行アドレス周期の約半分以下を占めるゲートパルス信号をバスライン 48 に供給し、TFTS1 をターンオンする。この信号の適用の持続時間中、各々が前記行アドレス周期の 4 分の 1 よりわずかに短い期間を占めるゲート信号を連続的に、時間において分離して、バスライン 50 及び 51 に供給し、TFTS6 及び S5 を連続的にターンオンする。TFTS6 をターンオンしている間、列導体 C+3 に関するデータ信号を、前記駆動 I C の関連する出力部 41 において供給し、TFTS1 及び TFTS6 を経てこの列に供給する。同様に、TFTS5 がターンオンしている間、前記駆動 I C を、列導体 C+2 に接続された画素に関するデータ信号を供給するように配置し、このデータ信号を、TFTS1 及び S5 を経てこの列導体に供給する。その後、バスライン 48 及び 51 に印加される前記選択パルス信号の停止に応じて、これらのラインの電位は、低レベルに低下し、TFTS5 及び S1 をターンオフし、選択（ゲート）信号をバスライン 49 に印加し、TFTS2 を、再び前記行アドレス周期の約半分（より後の半分）の間、ターンオン

40

50

する。前記行アドレス周期のこの後半の半分中、TFTS4及びS3は、バスライン50及び51における制御信号によって、前記行アドレス周期の4分の1よりわずかに短い期間中、各々ターンオンし、列導体C+1及びCを出力部41にTFTS2を経て接続するようとする。各TFTS4及びS3がターンオンしている間、列C及びC+1における画素に関する適切なデータ信号を駆動IC40によってその出力部41に供給する。

#### 【0031】

このように、4個のグループにおける画素の各々に個々のデータ信号を、前記行アドレス周期の約4分の1を占める個々の行アドレスサブ周期において供給する。ある行のすべての他のグループにおける対応する画素、例えば、列導体C+4ないしC+7に関する画素を、同じ周期において、これらの個々の関連する駆動IC出力部41からのこれらの個々のデータ信号によってアドレスし、例えば、データ信号を、同時に列C+7及びC+3に供給し、データ信号を、同時に列C+4及びCに供給する、等である。したがって、前記チップは、これらの出力部の各々において、これらが各々の行アドレス周期において関係する前記列に関する別個のデータ信号の連続を供給する。

#### 【0032】

図4において示す特定の配置は、比較的簡単であり、もちろん、1グループにおける列導体の数と、したがって、多重化比とを変化させることができる。例えば、各グループは、8本の列導体を具えてよく、結果として、必要な駆動ICの数がさらに大きく減少するが、1グループにおける各画素にそのデータ信号を供給することを可能とする時間も当然減少する。

#### 【0033】

前記多重化回路を、前記グループにおける列導体を連続する隣接した列導体とする必要がない異なったグループ化配置を与えるように設計することもできる。例えば、あるグループの列導体が、すべて第3列導体を具え、あるグループが、列導体C、C+3及びC+6を具え、他のグループが、C+1、C+4及びC+7を具え、第3グループが、C+2、C+5及びC+8を具えるようにしてもよい。

#### 【0034】

前記画素TFT及び多重化TFTのすべては、低温度ポリシリコンTFTを具える。多重化スイッチS1ないしS6に使用するTFTを、画素10において使用するTFTと同じ形式のもの、例えば、n又はpチャネルTFTのいずれか(NMOS又はPMOS)とする。前記画素アレイ及び集積多重化回路の形成は、CMOS回路を必要とする状況と比較して簡単になり、CMOS回路を形成するのに代表的に必要な9ないし10マスク処理と異なり、5又は6マスクプロセスのみを必要とする。

#### 【0035】

既知の種類の画素回路について、ある列の画素のアドレス中、前記画素の駆動TFT22を、前記格納キャパシタンスを充電している間、ターンオンすることができる。前記画素の格納キャパシタンスにおいて格納された電圧における誤差を生じる、画素のある行に関する電流ライン32に沿ってこの行のアドレス中に生じる電圧降下による望ましくないクロストークの影響を回避するために、前記行の表示素子を通じて流れる電流を、これらがアドレスされている間、故意に妨げる。実際には、表示素子ブランкиング期間を導入する。結果として、前記電流ライン電位は、あるレベルに固定されたままであり、前記画素格納キャパシタは、すべて確実に個々の所望のレベルに充電されるようになる。より特に、前記電流ラインを、関連する前記画素が実際にアドレスされている全体の周期中ではなく、ある行における前記グループの各々の画素がアドレスされている間、すなわち、完全な行アドレス周期中、前記表示素子をゼロ又は逆バイアスするのを保証するのに好適な適切な電位において保持する。このようなバイアスを、図4において60において示し、前記行選択信号との同期において適切にタイミング及び制御ユニット17によって供給される制御信号によって制御されたすべての前記電流ラインに接続されたスイッチング装置にもかかわらず、前記行アドレス周期の持続時間中、前記駆動段階、すなわち、連続するアドレス段階間のフレーム周期中に必要なレベルと、所望のレベル、例えば共通電極30と

10

20

30

40

50

同じ電位との間で切り替えることによって、便利に成し遂げる。代わりに、共通電極 30 の電位を、電流ライン 32 の電位に切り替え、同様の効果を生じることができる。このような場合において、スイッチング装置 60 を、共通電極 30 に接続する。

#### 【0036】

代わりに、各画素に、その表示素子に直列に、例えば、駆動 TFT 22 と電流供給ライン 32 との間に接続された追加の TFT スイッチを設けてもよく、この動作を、個々の行アドレス導体 12 に印加される前記選択信号によって制御し、前記表示素子を前記行アドレス周期中に流れる電流を防止する。

#### 【0037】

前記多重化列駆動の結果として、個々のデータ信号を得る前記駆動 IC に供給されるビデオ情報を、通常に使用されるのとは異なった順序に配列する必要がある。データは、通常、以下の順序、C, C + 1, C + 2, . . . , C + 7 等において到着する。4 : 1 多重化を使用する場合、適切に再整理し、以下の順序、C, C + 4, C + 8, . . . , C + 1, C + 5, C + 9, . . . , C + 2, C + 6, C + 10, . . . , C + 3, C + 7, C + 11, . . . 等において到着する。

#### 【0038】

シフトレジスタ回路を具える行駆動回路 16 を、図 3 において示すように、基板 25 において集積してもよく、画素アレイ 15 及び多重化回路 45 と同時に形成してもよい。前記列駆動配置のように、前記行選択回路は、同様に多重化を使用し、同様に利益を得てもよい。上述したように、前記画素回路及び集積多重化回路 45 において使用した TFT をすべて同じ形式のもの、すなわち、p 又は n チャネル TFT のいずれかにすることが好適であるにもかかわらず、前記装置は双方の形式を使用できることは想像される。これは、シフトレジスタのような CMOS 回路網を必要とする回路も基板 25 において完全に集積することを可能にする。シフトレジスタを、前記列駆動回路、又は、上述したように前記行駆動（選択）回路の一部として使用することができる。

#### 【0039】

特定の画素回路を上述した実施形態において使用したが、当業者には明らかのように、アクティブマトリックスアドレッシングに好適な他の種類の画素回路を使用できることは認識されるであろう。

#### 【0040】

本開示を読むことによって、他の変形が当業者には明らかであろう。このような変形は、アクティブマトリックス電界発光表示装置及びその構成部品の分野において既知であり、すでにここに記載した特徴の代わり又はこれらに追加して使用することができる他の特徴を含むことができる。

#### 【図面の簡単な説明】

【図 1】画素のアレイを具える既知のアクティブマトリックス電界発光表示装置の単純化した図式的な図である。

【図 2】図 1 のアクティブマトリックス電界発光表示装置のいくつかの代表的な画素の等価回路を示す。

#### 【図 3】列駆動回路網を含む本発明による表示装置の一実施形態の一部を図式的に示す。

【図 4】図 3 のアクティブマトリックス電界発光表示装置の実施形態におけるいくつかの代表的な画素と列駆動回路網の関連する部分とを、前記装置の動作において存在する多重化駆動波形と共に示す。

10

20

30

40

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

3 May 2001 (03.05.2001)

PCT

(10) International Publication Number

**WO 01/31624 A1**

(51) International Patent Classification: G09G 3/32 (74) Agent: WILLIAMSON, Paul, L.; Internationaal Octrooiagentschap B.V., Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

(21) International Application Number: PCT/EP00/09504

(22) International Filing Date:

27 September 2000 (27.09.2000)

(81) Designated States (national): JP, KR.

(25) Filing Language: English

(84) Designated States (regional): European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(26) Publication Language: English

(30) Priority Data:

9925060.7 23 October 1999 (23.10.1999) GBPublished:

— With international search report.

— Before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments.

(71) Applicant: KONINKLIJKE PHILIPS ELECTRONICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven (NL).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(72) Inventor: BATTERSBY, Stephen, J.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

(54) Title: ACTIVE MATRIX ELECTROLUMINESCENT DISPLAY DEVICE

**WO 01/31624 A1**

**(57) Abstract:** An active matrix electroluminescent (EL) display device has an array of pixels (10) on a substrate (25) each comprising an EL display element (20) and a driving device (22) controlling drive current therethrough in a drive period based on a data signal applied in a preceding address period, and a drive circuit (16, 18) connected to the pixels via sets of address conductors (12, 14) for selecting the rows of pixels and supplying data signals to each selected row of pixels in a respective row address period. The data signals are provided by drive ICs (40). To reduce the number of ICs required, a multiplexing circuit (45) is integrated with the pixel array on the substrate (25) and connected between the drive IC outputs (41) and one set of address conductors (14) and is operable to apply data signals from an individual drive IC output to a respective associated plurality of address conductors in sequence in a row address period. The display elements of a selected row of pixels are prevented from operating in the row address period to avoid unwanted cross-talk effects. Row selection signals may similarly be supplied by a multiplexing circuit (16) integrated on the substrate.

## ACTIVE MATRIX ELECTROLUMINESCENT DISPLAY DEVICE

5

This invention relates to active matrix electroluminescent display devices comprising an array of electroluminescent display pixels.

Matrix display devices employing electroluminescent, light-emitting, 10 display elements are well known. The display elements may comprise organic thin film electroluminescent elements, for example using polymer materials, or else light emitting diodes (LEDs) using traditional III-V semiconductor compounds. Recent developments in organic electroluminescent materials, particularly polymer materials, have demonstrated their ability to be used 15 practically for video display devices. These materials typically comprise one or more layers of an electroluminescent material, for example a semiconducting conjugated polymer, sandwiched between a pair of electrodes, one of which is transparent and the other of which is of a material suitable for injecting holes or electrons into the polymer layer. The polymer material can be fabricated using 20 a CVD process, or simply by a spin coating technique using a solution of a soluble conjugated polymer.

Organic electroluminescent materials exhibit diode-like I-V properties, so that they are capable of providing both a display function and a switching function, and can therefore be used in passive type displays.

25 However, the invention is concerned with active matrix display devices, with each pixel comprising a display element and a driving device for controlling the current through the display elements. Examples of an active matrix electroluminescent display are described in EP-A-0653741 and EP-A-0717446. Unlike active matrix liquid crystal display devices in which display 30 elements are capacitive and therefore take virtually no current and allow a drive (data) signal voltage to be stored on the capacitance for the whole frame time electroluminescent display elements need to continuously pass current to

generate light. A driving device of a pixel, usually comprising a TFT (thin film transistor), is responsible for controlling the current through the display element. The brightness of the display element is dependent to the current flowing through it. During an address period for a pixel, a drive (data) signal determining the required output from the display element is applied to the pixel and stored as a corresponding voltage on a storage capacitor which is connected to, and controls the operation of, the current controlling drive device with the voltage stored on the capacitor serving to maintain operation of the driving device in supplying current through the display element during the subsequent drive period, corresponding to a frame period, until the pixel is addressed again.

Typically, the pixels are connected to sets of row and column address conductors through which selection, (scanning), signals and analogue voltage data signals respectively are supplied by a peripheral drive circuit, each row of pixels being selected in turn in a respective row address period by means of a selection signal applied to its associated row conductor and with the data signals for the pixels of the selected row being applied via the column conductors. The data signals can be provided by a column driver circuit comprising silicon integrated circuits (IC) chips. Each chip has a limited number of individual, spaced, output contacts. Each column conductor is connected to a respective chip output and consequently a large number of chips would normally be required. For example, if there are 800 pixels in a row and a chip is capable of providing 100 outputs then 8 chips are needed to supply the 800 column conductors involved.

The electroluminescent display elements of all the pixels in a respective row, or column, are connected, through their associated drive devices to a common current line. The storage capacitors of the pixels are also connected to these common lines and such sharing of the current lines leads to a further problem in that voltage drops can occur along these lines in operation which has the effect of producing a kind of cross-talk.

It is an object of the present invention to provide an improved active matrix electroluminescent display device.

According to the present invention there is provided an active matrix electroluminescent display device comprising a row and column array of pixels carried on a substrate, each pixel comprising an electroluminescent display element and a driving device for controlling current through the display element in a drive period based on a data signal applied in a preceding row address period, the display element being connected via the driving device to a current line common to a row of pixels, and a peripheral drive circuit connected to the pixel array which drive circuit generates and applies data signals to each row of pixels in respective row address periods via a set of address conductors connected to the array of pixels and comprises at least one drive IC having a plurality of outputs, which is characterised in that the at least one drive IC is connected to the set of address conductors through a multiplexing circuit which is integrated on the substrate and is operable to apply data signals from each output of the drive IC to a respective plurality of address conductors in the set in sequence in the row address period, and in that the drive circuit is arranged to prevent current flowing through the display elements of a row of pixels during its respective row address period.

Through the integration of a multiplexing circuit on the device substrate operable in this manner, considerable cost savings are possible as fewer drive ICs are required for a device having a given number of columns of pixels. With a multiplexing ratio of 4:1 for example, wherein each group of address conductors supplied by a respective drive IC output comprises four address conductors, the cost of the drive ICs needed is reduced by 75% in comparison to the case in which a single IC output is connected exclusively to a respective single address conductor. Using the same thin film fabrication technology employed for fabricating the pixels the integrated multiplexing circuit is provided at little or no additional expense and can be formed at the same time as the thin film elements of the pixels using common thin film layers and comprising similar thin film circuit elements such as TFTs and conductor lines. Multiplexing switches used in the multiplexing circuit are preferably of the

same type as used in the pixel array, for example p or n type polysilicon TFTs. Consequently it is possible to produce the thin film circuitry on the device substrate forming the pixel array and the multiplexing circuit using standard thin film technology involving the deposition and patterning of various conductive, dielectric and semiconductive layers. With the pixel circuits and the integrated multiplexer circuit using the same type of switching device, e.g. either p or n channel polysilicon TFTs, fabrication of the array together with the multiplexing circuit is considerable simplified, typically requiring only 5 or 6 mask processes rather than 9 or 10 mask processes as normally required to produce both p and n channel (CMOS) TFTs.

10 However, both p and n channel type TFTs could be used which would enable circuitry such as shift registers requiring CMOS circuits to be integrated as well on the device substrate. Shift registers could be used in the column drive circuit and/or in the row drive (selection) circuit. The benefits of using 15 both p and n (CMOS) devices in allowing extended integration would need to be considered in relation to the more complicated (higher mask count) fabrication processes necessary.

10 The pixels of each row are addressed with their data signals in a respective row address period during which the multiplexing circuit operates to 20 supply data signals in time division manner to the pixels of each group in the row in sequence. By preventing current flowing through the display elements during the period of their addressing then problems with cross-talk effect caused by voltage drops occurring in their shared current line due to inherent resistance are avoided. Such prevention can be accomplished by ensuring 25 that the display elements are zero or reversed biased during the full, entire, row address period rather than merely the portion thereof in which individual pixels are addressed. To this end, the potential applied to the common current line may be switched or a switching device, e.g. another TFT, may be connected in series with the display element of each pixel that is operable to 30 disconnect the display element from the current line for the duration of the row address period.

An embodiment of an active matrix electroluminescent display device in accordance with the present invention will now be described, by way of example, with reference to the accompanying drawings, in which:-

5 Figure 1 is a simplified schematic diagram of a known active matrix electroluminescent display device comprising an array of pixels;

Figure 2 shows the equivalent circuit of a few typical pixels of the active matrix electroluminescent display device of Figure 1;

10 Figure 3 shows schematically a part of an embodiment of display device according to the present invention including its column drive circuitry; and

Figure 4 shows a few typical pixels and associated part of the column drive circuitry in the embodiment of active matrix electroluminescent display device of Figure 3 together with multiplexing drive waveforms present in operation of the device.

15 The Figures are merely schematic. The same reference numbers are used throughout the Figures to denote the same or similar parts.

Referring to Figure 1, the active matrix electroluminescent display device comprises a panel having a row and column matrix array of regularly-spaced pixels, denoted by the blocks 10 carried on a substrate 25, each comprising an electroluminescent display element and an associated driving device controlling the current through the display element, and which are located at the intersections between crossing sets of row (selection) and column (data) address conductors, or lines, 12 and 14 also carried on the substrate. Only a few pixels are shown for simplicity. The pixels 10 are addressed via the sets of address conductors by a peripheral drive circuit having outputs connected to the panel and comprising a row, scanning, driver circuit 16 generating scanning signals supplied to the row conductors in sequence and a column, data, driver circuit 18 generating data signals supplied to the column conductors and defining the display outputs from the individual pixel display elements, and a timing and control unit 17 for controlling the operation of the circuits 16 and 18.

Each row of pixels is addressed in turn by means of a selection signal applied by the circuit 16 to the relevant row conductor 12 so as to load the pixels of the row with respective drive signals according to the respective data signals supplied in parallel by the circuit 18 to the column conductors. As each 5 row is addressed, the data signals are supplied by the circuit 18 in appropriate synchronisation.

Figure 2 illustrates the circuit of a few, typical, pixels in this known device. Each pixel, 10, includes a light emitting organic electroluminescent display element 20, represented here as a diode element (LED), and 10 comprising a pair of electrodes between which one or more active layers of organic electroluminescent material is sandwiched. In this particular embodiment the material comprises a polymer LED material, although other organic electroluminescent materials, such as low molecular weight materials, could be used. The display elements of the array are carried together with the 15 associated active matrix circuitry on one side of the substrate. Either the cathodes or the anodes of the display elements are formed of transparent conductive material. The substrate is of transparent insulating such as glass and the electrodes of the individual display elements 20 closest to the substrate can consist of a transparent conductive material such as ITO so that 20 light generated by the electroluminescent layer is transmitted through these electrodes and the substrate so as to be visible to a viewer at the other side of the substrate. Alternatively, the light output could be viewed from above the panel and the display element anodes in this case would comprise parts of a continuous ITO layer constituting a supply line common to all display elements 25 in the array. The cathodes of the display elements comprise a metal having a low work-function such as calcium or magnesium silver alloy. Examples of suitable organic conjugated polymer materials which can be used are described in WO 96/36959. Examples of other, low molecular weight, organic materials are described in EP-A-0717446. The array of pixels and sets of 30 address conductors are fabricated using standard thin film processing technology, similar to that used for AMLCDs, which involves the deposition and patterning of various conductive, insulating and semi-conductive layers.

Examples of such fabrication are described in the aforementioned EP-A-0717446.

Each pixel 10 includes a drive device in the form of a TFT 22 which controls the operation of the display element 20 based on a data signal voltage applied to the pixel. The signal voltage for a pixel is supplied via a column conductor 14 which is shared between a respective column of pixels. The column conductor 14 is coupled to the gate of the current-controlling drive transistor 22 through an address TFT 26. The gates for the address TFTs 26 of a row of pixels are coupled together to a common row conductor 12.

10 Each row of pixels 10 also shares a common voltage supply line 30, usually provided as a continuous electrode common to all pixels, and a respective common current line 32. The display element 20 and the drive device 22 are connected in series between the voltage supply line 30 and the common current line 32, which is at a positive potential with respect to the supply line 30 and acts as a current drain for the current flowing through the display element 20. The level of current flowing through the display element 20 is controlled by the switching device 22 and is a function of the gate voltage on the transistor 22, which is dependent upon a stored control signal determined by the data signal supplied to the column conductor 14.

20 A row of pixels is selected by the row driver circuit 16 applying a selection pulse to the row conductor 12 which switches on the address TFTs 26 for the respective row of pixels and whose duration determines the row address period. A voltage level (data signal) derived from the video information is applied to the column conductor 14 by the driver circuit 18 and is transferred by the address TFT 26 to the gate of the drive transistor 22. During the periods when a row of pixels is not being addressed via the row conductor 12 the address transistor 26 is turned off, but the voltage on the gate of the drive transistor 22 is maintained by a pixel storage capacitor 36 which is connected between the gate of the drive transistor 22 and the common current line 32 so as to maintain the operation of the display element during this subsequent drive period. The voltage between the gate of the drive transistor 22 and the common current line 32 determines the current passing

through the display element 20 of the pixel 10. Thus, the current flowing through the display element is a function of the gate-source voltage of the drive transistor 22 (the source of the n-channel type transistor 22 being connected to the common current line 32, and the drain of the transistor 22 being connected to the display element 20). This current in turn controls the light output level (grey-scale) of the pixel.

The switching transistor 22 is arranged to operate in saturation, so that the gate-source voltage governs the current flowing through the transistor, irrespectively of the drain-source voltage. Consequently, slight variations of 10 the drain voltage do not affect the current flowing through the display element 20. The voltage on the voltage supply line 30 is therefore not critical to the correct operation of the pixels.

Each row of pixels is addressed in turn in respective row address periods so as to load the pixels of each row in sequence with their drive 15 signals and set the pixels to provide desired outputs for the subsequent drive (frame) period until they are next addressed.

The data signals are commonly supplied to the set of address conductors 14 by a plurality of external, silicon integrated circuit, drive circuit ICs each of which has a number of discrete output terminals that are each 20 connected to a respective one of the conductors 14. Thus, each conductor 14 requires a respective exclusive, and dedicated, associated output terminal. If there are C conductors 14 in the set and each drive IC has n outputs, (and assuming  $C \gg n$ ), then  $C/n$  drive ICs are required. Typically, at least several 25 drive ICs are therefore needed and the number of individual connections between these and the panel thin film circuitry, one for each IC output/column conductor, is considerable, for example 800 or more for a typical video/datagraphic display.

In accordance with an aspect of the present invention multiplexing is utilised to reduce the number of drive ICs required. The drive IC outputs are 30 each multiplexed over a plurality of column conductors. As each drive IC output is then used to provide the data signals for a respective plurality of

column conductors, the total number of outputs, and hence drive ICs, can be considerably reduced. For example, with a multiplexing ratio of 4:1 then only one quarter of the number of drive IC outputs previously required is needed, resulting in a cost saving of 75% for the drive ICs. The multiplexing circuit is integrated on the substrate, that is, fabricated on the substrate in similar manner to the pixel array using thin film technology. Such a circuit can readily be fabricated simultaneously with the pixel array using common deposited layers providing similar thin film circuit elements.

Figure 3 illustrates schematically the basic arrangement in an embodiment of display device according to the invention. The pixel array carried on the substrate 25 is depicted generally here at 15. A number of drive IC chips 40, two in this example, are provided externally to the substrate 25, for generating and supplying data signals for the pixels at outputs thereof, with their individual output terminals, 41, from which the data signals are supplied, connected to inputs of a multiplexing circuit 45 integrated on the substrate 25. Assuming a drive IC has 100 outputs and, for example, there are 800 columns of pixels in the array and the multiplexing ratio of the circuit 45 is 4:1 so that each IC output provides the data signals for four columns, then only two drive ICs are used. Video information is supplied to the ICs 40 in generally conventional manner, for example in digital form, and the ICs operate to generate the analogue voltage data signals for the columns with which they are associated and to supply such to the relevant outputs 42.

The chips 40 can be provided in the device and interconnected with the thin film circuitry on the substrate 25 using, for example, COG or tab bonding technology known in the fabrication of other kinds of flat panel displays.

Figure 4 illustrates in greater detail the nature of the multiplexing circuit 45. The figure shows a few typical pixels of the device and the associated part of the multiplexing circuit 45, together with example waveforms applied by the timing and control unit 17 in operation of this circuit. The pixel circuits are similar to those of Figure 2, though other known kinds of pixels circuits could be used as well.

The columns of pixels 10 and their column conductors 14 are organised into groups of four, the eight consecutive column conductors, C to C+7, shown in Figure 4 constituting two such groups. Each group of columns share the same, and respective, drive IC output 41, with the data signals for the pixels in

5 these four columns being supplied by the one output 41.

The multiplexing circuit 45 comprises a set of four control signal bus lines, 48, 49, 50 and 51. Each group of four columns is connected to these bus lines via six multiplexer switches, comprising TFTs, labelled S1 to S6. Taking, for example, the first group comprising column conductors C to C+3,

10 then these column conductors are connected respectively to the TFTs S3 to S6 with the gates of S3 and S5 being connected to the bus line 51 and the gates of S4 and S6 being connected to the bus line 50. Data signals are supplied to the pair of TFTs S3 and S4 and the pair of TFTs S5 and S6 respectively via the TFTs S2 and S1 whose gates are connected respectively

15 to the bus lines 49 and 48.

The TFTs of a group are arranged to be operated in time division manner and in particular sequence in a row address period by means of control (gating) signals supplied to the bus lines, the corresponding TFTs in each of the other groups being operated simultaneously by the control signals.

20 Example control signal waveforms for these bus lines are depicted adjacent their respective lines and comprise pulse signals effective to turn the TFTs on.

In the first half of a row address period, denoted by  $T_L$ , in which the pixels of a row are to be supplied with their data signals, a gating pulse signal occupying approximately one half of the row address period or less is supplied

25 to the bus line 48 turning on TFT S1. During the duration of the application of this signal, gating signals are supplied in succession and separated in time, each occupying slightly less than one quarter of the row address period, to the bus lines 50 and 51 to turn on the TFTs S6 and S5 in succession. While TFT S6 is turned on a data signal for column conductor C+3 is supplied at the

30 associated output 41 of the drive IC and fed via the TFT S1 and TFT S6 to that column. Similarly, while the TFT S5 is turned on, the drive IC is arranged to provide a data signal for the pixel connected to column conductor C+2 which is

fed to that column conductor via TFTs S1 and S5. Thereafter, upon termination of the selection pulse signals applied to the bus lines 48 and 51 the potential of these lines drops to a low level, turning off the TFTs S5 and S1 and a selection (gating) signal is applied to the bus line 49 to turn on the TFT S2 for again approximately one half (the latter half) of the row address period. During this latter half of the row address period the TFTs S4 and S3 are similarly each turned on for slightly less than a quarter of the row address period in sequence by control signals on the bus lines 50 and 51 respectively so as to connect the column conductors C+1 and C in turn with the output 41 via the TFT S2. Whilst each TFT S4 and S3 is turned on, the appropriate data signals for the pixels in columns C and C+1 are supplied by the drive IC 40 to its output 41.

Thus each of the pixels in the group of four is supplied with a respective data signal in a respective row address sub-period, occupying approximately one quarter of the row address period. Corresponding pixels in all the other groups of a row, for example those associated with the column conductors C+4 to C+7, are addressed with their respective data signals, from their respective associated drive IC output 41, in the same period, with, for example, data signals being supplied simultaneously to columns C+7 and C+3, and data signals being supplied simultaneously to columns C+4 and C, etc. The chips therefore provide at each of their outputs a succession of discrete data signals for the columns with which they are associated in each row address period.

The particular arrangement shown in Figure 4 is relatively simple and, of course, the number of column conductors in a group, and hence the multiplexing ratio, can be varied. For example, each group may comprise eight column conductors, resulting in an even greater reduction of the number of drive ICs required, but with a consequential reduction in the time allowed to supply each pixel in a group with its data signal.

It is also possible for the multiplexing circuit to be designed to provide different grouping arrangements such that the column conductors in the group are not necessarily consecutive, adjacent column conductors. For example,

the column conductors of one group may comprise every third column conductor so that one group comprises column conductors C, C+3, and C+6, another group comprises C+1, C+4, and C+7, and a third group comprises C+2, C+5, and C+8.

5       The pixel TFTs and the multiplexing TFTs all comprise low temperature polysilicon TFTs. The TFTs used for the multiplexing switches S1 to S6 are of the same type as those used in the pixels 10, for example either n or p channel TFTs, (NMOS or PMOS). Fabrication of the pixel array and the integrated multiplexing circuit is then simplified compared with a situation

10      requiring a CMOS circuit, with only 5 or 6 mask processes being required for the circuit fabrication unlike the 9 to 10 mask processes typically needed to form a CMOS circuit.

With the known kind of pixel circuit then during the addressing of a row of pixels, the drive TFTs 22 of the pixels can be turned on while the storage capacitor is charging. In order to avoid unwanted cross-talk effects due to voltage drops occurring along the current line 32 associated with a row of pixels during addressing of that row causing errors in the voltage stored on the storage capacitors of the pixels, and thus the cross-talk effect, then current flow through the display elements of the row is deliberately prevented while

15      they are being addressed. In effect, a display element blanking period is introduced. As a consequence, the current line potential remains fixed at a certain level so that the pixel storage capacitors are all charged reliably to a respective desired level. More particularly, the current line is held at an appropriate potential, suitable to ensure that the display elements are zero or

20      reverse biased, not just for the time in which the pixel concerned is actually being addressed but for the entire period during which the pixels of each of the groups in a row is being addressed, i.e. for the complete row address period. Such biasing is conveniently accomplished by switching the potential of the current line 32 between the level required during the driving phase, i.e the

25      frame period between consecutive addressing phases, to the required level, for example the same potential as the common electrode 30, for the duration of the row addressing period though a switching device, shown at 60 in Figure

30

4 and connected to all the current lines controlled by a control signal supplied by the timing and control unit 17 appropriately in synchronisation with the row selection signals. Instead, the potential of the common electrode 30 could be switched to the potential of the current line 32 to similar effect. In such case,

5 the switching device 60 would be connected to the common electrode 30.

Alternatively, each pixel may be provided with an additional TFT switch connected in series with its display element, for example between the drive TFT 22 and the current supply line 32, whose operation is controlled by the selection signal applied to the relevant row address conductor 12 to prevent

10 current flowing through the display element during the row address period

As a consequence of the multiplexing column drive, the video information supplied to the drive ICs from which the individual data signals are derived will need to be sequenced differently to that normally used. Data would normally arrive in the following order: C, C+1, C+2, ... C+7, etc. When

15 using 4:1 multiplexing it is appropriately re-ordered to arrive in the following sequence: C, C+4, C+8, ..., C+1, C+5, C+9, ..., C+2, C+6, C+10 ... C+3, C+7, C+11, ... etc.

The row drive circuit 16, comprising a shift register circuit, may also be integrated on the substrate 25 and fabricated simultaneously with the pixel array 15 and the multiplexing circuit 45, as shown in Figure 3. Like the column drive arrangement, the row selection circuit may similarly use multiplexing to similar benefit. Although as previously mentioned it is preferred that the TFTs used in the pixel circuits and the integrated multiplexing circuit 45 are all of the same type, i.e. either p or n channel TFTs, it is envisaged that the device could

20 use both types. This would enable circuits requiring CMOS circuitry such as shift registers also to be fully integrated on the substrate 25. A shift register circuit can be used as part of the column drive circuit or, as previously mentioned, the row drive (selection) circuit.

Although a particular pixel circuit is used in the above-described

25 embodiment, it will be appreciated that other kinds of pixel circuits suitable for active matrix addressing could be used, as will be apparent to persons skilled in the art.

From reading the present disclosure, other modifications will be apparent to persons skilled in the art. Such modifications may involve other features which are already known in the field of active matrix electroluminescent display devices and component parts thereof and which

5 may be used instead of or in addition to features already described herein.

## CLAIMS

1. An active matrix electroluminescent display device comprising a row and column array of pixels carried on a substrate, each pixel comprising

5 an electroluminescent display element and a driving device for controlling current through the display element in a drive period based on a data signal applied in a preceding row address period, the display element being connected via the driving device to a current line common to a row of pixels, and a peripheral drive circuit connected to the pixel array which drive circuit

10 generates and applies data signals to each row of pixels in respective row address periods via a set of address conductors connected to the array of pixels and comprises at least one drive IC having a plurality of outputs, characterised in that the at least one drive IC is connected to the set of address conductors through a multiplexing circuit which is integrated on the

15 substrate and is operable to apply data signals from each output of the drive IC to a respective plurality of address conductors in the set in sequence in the row address period, and in that the drive circuit is arranged to prevent current flowing through the display elements of a row of pixels during its respective row address period.

20

2. An active matrix electroluminescent display device according to Claim 1, characterised in that the address conductors of the one set are organised in groups with each group being associated with a respective drive IC output, the multiplexing circuit comprising switching devices operable to supply data signals from an output to each of the address conductors of its

25 associated group in turn in the same period.

3. An active matrix electroluminescent display device according to Claim 2, characterised in that the drive devices of the pixels and the switching devices of the multiplexing circuit all comprise either p or n channel TFTs.

30

4. An active matrix electroluminescent display device according to Claim 2, characterised in that the drive devices of the pixels and the switching devices of the multiplexing comprise both p and n channel TFTs.

5 5. An active matrix electroluminescent display device according to Claim 4, characterised in that the peripheral drive circuit further includes a shift register circuit integrated on the substrate and comprising p and n channel TFTs.

10 6. An active matrix electroluminescent display device according to any one of the preceding claims, characterised in that drive circuit is arranged to switch the potential applied to the common current line for the respective row address period.

15 7. An active matrix electroluminescent display device according to any one of Claims 1 to 5, characterised in that the display element of a pixel is connected to its associated current line through a switching device and in that the drive circuit is arranged to operate the switching device to isolate the display element from the current line for the duration of the row address period.

20

WO 01/31624

PCT/EP00/09504

FIG. 1

FIG. 2

WO 01/31624

PCT/EP00/09504

2/2

FIG. 3

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                          |                                                                                                                                                                     | In International Application No<br>PCT/EP 00/09504                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G09G/32                                                                                                                                                                                                                                 |                                                                                                                                                                     |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                    |                                                                                                                                                                     |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G09G                                                                                                                                                        |                                                                                                                                                                     |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                        |                                                                                                                                                                     |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)                                                                                                                                                           |                                                                                                                                                                     |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                               |                                                                                                                                                                     |                                                                                |

| Category *                                                                                                                                                                                                                                                                           | Citation of document, with indication, where appropriate, of the relevant passages                                                                                  | Relevant to claim No.                                                          |

| X<br>A                                                                                                                                                                                                                                                                               | US 5 952 789 A (STEWART ET AL)<br>14 September 1999 (1999-09-14)<br>abstract<br>column 2, line 12 - line 26<br>column 5, line 2 - line 63; figures 2,3<br>----      | 1,6,7<br>2-5                                                                   |

| A                                                                                                                                                                                                                                                                                    | WO 99 38148 A (FED CORP.)<br>29 July 1999 (1999-07-29)<br>abstract<br>page 3, line 21 -page 4, line 7<br>page 11, line 25 -page 12, line 14;<br>figures 6-8<br>---- | 1-7                                                                            |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                  |                                                                                                                                                                     | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents:                                                                                                                                                                                                                                             |                                                                                                                                                                     |                                                                                |

| *A* document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                                                             |                                                                                                                                                                     |                                                                                |

| *E* earlier document but published on or after the international filing date                                                                                                                                                                                                         |                                                                                                                                                                     |                                                                                |

| *L* document which may throw doubt on the novelty of claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                                                         |                                                                                                                                                                     |                                                                                |

| *O* document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                                                         |                                                                                                                                                                     |                                                                                |

| *P* document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                               |                                                                                                                                                                     |                                                                                |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                                                                  |                                                                                                                                                                     |                                                                                |

| *X* document of particular relevance, the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                                                         |                                                                                                                                                                     |                                                                                |

| *Y* document of particular relevance: the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken together with one or more other such documents, such combination being obvious to a person skilled in the art |                                                                                                                                                                     |                                                                                |

| *Z* document member of the same patent family                                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                |

| Date of the actual completion of the international search<br><br>7 March 2001                                                                                                                                                                                                        | Date of mailing of the international search report<br><br>14/03/2001                                                                                                |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5816 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040 Tx. 31 651 epo nl<br>Fax: (+31-70) 340-3016                                                                                                 | Authorized officer<br><br>O'Reilly, D                                                                                                                               |                                                                                |

Form PCT/ISA/210 (second sheet) (July 1992)

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/EP 00/09504

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 5952789 A                           | 14-09-1999       | JP 10319908 A           | 04-12-1998       |

| WO 9938148 A                           | 29-07-1999       | EP 1055218 A            | 29-11-2000       |

Form PCT/ISA/210 (patent family annex) (July 1992)

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 05 B 33/14

A

(72)発明者 スティーヴン イエー バッタースピー

オランダ国 5656 アーアー アインドーフェン プロフ ホルストラーン 6

Fターム(参考) 3K007 DB03 GA00

5C080 AA06 AA07 BB05 BB06 DD05 DD10 DD23 DD25 DD27 EE29

FF03 FF11 HH09 HH13 JJ02 JJ03 JJ04

## 【要約の続き】

れた多重化回路(16)によって同様に供給してもよい。

|                |                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵电致发光显示装置                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2004506924A</a>                                                                                                                                                                                    | 公开(公告)日 | 2004-03-04 |

| 申请号            | JP2001534130                                                                                                                                                                                                     | 申请日     | 2000-09-27 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 皇家飞利浦电子股份有限公司的Vie                                                                                                                                                                                                |         |            |

| [标]发明人         | スティーヴン イエ バッタースビー                                                                                                                                                                                                |         |            |

| 发明人            | スティーヴン イエ バッタースビー                                                                                                                                                                                                |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3233 G09G3/3291 G09G2300/0408 G09G2300/0842 G09G2300/0866 G09G2310/0205 G09G2310/0297 G09G2320/0209 G09G2320/0223                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.D G09G3/20.621.M G09G3/20.623.V G09G3/20.680.G H05B33/14.A                                                                                                                               |         |            |

| F-TERM分类号      | 3K007/DB03 3K007/GA00 5C080/AA06 5C080/AA07 5C080/BB05 5C080/BB06 5C080/DD05 5C080/DD10 5C080/DD23 5C080/DD25 5C080/DD27 5C080/EE29 5C080/FF03 5C080/FF11 5C080/HH09 5C080/HH13 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |

| 优先权            | 1999025060 1999-10-23 GB                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                        |         |            |

## 摘要(译)

的有源矩阵电致发光(EL)显示装置包括，基板(25)，EL显示装置(20)是基于在寻址周期之前流过的电流在驱动期间所述元件所施加的数据信号来控制上像素阵列，每个像素包括地址导体和驱动装置，14)用于选择一行所述像素并在单个行地址周期中向所述所选行的每个像素提供数据信号。数据信号由驱动IC(40)提供。为了减少所需IC的数量，多路复用电路(45)与基板(25)上的像素阵列，驱动IC的输出部分(41)和输出部分集成在一起。一组并且可操作以在一个行寻址周期中将来自各个驱动IC输出的数据信号顺序地施加到各个相关联的多个地址导线。防止所选行的像素的显示元件在行寻址周期中操作，并且避免了不期望的串扰的影响。行选择信号同样可以由集成在所述基板上的多路复用电路(16)提供。