(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3861996号

(P3861996)

(45) 発行日 平成18年12月27日(2006.12.27)

(24) 登録日 平成18年10月6日(2006.10.6)

(51) Int.CI.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b>  | <b>K</b>    |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>624B</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>641D</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>642D</b> |

|             |              |                  | <b>H05B</b> | <b>33/14</b> | <b>A</b>    |

請求項の数 18 (全 17 頁)

(21) 出願番号 特願2001-391148 (P2001-391148)

(22) 出願日 平成13年12月25日 (2001.12.25)

(65) 公開番号 特開2002-258798 (P2002-258798A)

(43) 公開日 平成14年9月11日 (2002.9.11)

審査請求日 平成13年12月25日 (2001.12.25)

(31) 優先権主張番号 2000-81417

(32) 優先日 平成12年12月23日 (2000.12.23)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 599127667

エルジー フィリップス エルシーティー

カンパニー リミテッド

大韓民国 ソウル, ヨンドンポーク,

ヨイドードン 20

(74) 代理人 100109726

弁理士 園田 吉隆

(74) 代理人 100101199

弁理士 小林 義教

(72) 発明者 ベ, スン ジョン

大韓民国 キョンギードー, スンナム-

シ, ブンダン-ク, ケムゴクードン,

チュンソル ヴィレッジ 104-70

3

最終頁に続く

(54) 【発明の名称】エレクトロ・ルミネッセンス・パネル

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲートラインと、前記ゲートラインと交差するデータラインと、前記ゲートラインとデータラインの交差部に設置されたエレクトロ・ルミネッセンス・セルとを具備するエレクトロ・ルミネッセンス・パネルにおいて、

前記第1ゲートラインと前記データラインの交差部に設置されてエレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル駆動回路であって、

エレクトロ・ルミネッセンス・セルに電圧を印加する電源と、

前記電源と前記データライン間に接続され、ゲート電極とドレイン電極とが結線された第1PMOS薄膜トランジスタと、

前記電源と前記エレクトロ・ルミネッセンス・セルの間に接続された第2PMOS薄膜トランジスタと、

前記第1PMOS薄膜トランジスタのゲート電極と接続されたドレイン電極と、前記第2PMOS薄膜トランジスタのゲート電極と接続されたソース電極とを有し、スイッチの役割をする第3PMOS薄膜トランジスタと、

前記第2PMOS薄膜トランジスタのゲート電極と前記電源の間に接続されたキャパシタとを具備した第1エレクトロ・ルミネッセンス・セル駆動回路と、

前記第1ゲートラインを除いたゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・

10

20

セル駆動回路であつて、

エレクトロ・ルミネッセンス・セルに電圧を印加する電源と、

前記電源と前記エレクトロ・ルミネッセンス・セル間に接続された第4PMOS薄膜トランジスタと、

前記データラインと接続されたドレイン電極と、前記第4PMOSのゲート電極と接続されたソース電極とを有し、スイッチの役割をする第5PMOS薄膜トランジスタと、

前記第4PMOS薄膜トランジスタのゲート電極と前記電源と接続されるキャパシタとを具備した第2エレクトロ・ルミネッセンス・セル駆動回路と、

を具備することを特徴とするエレクトロ・ルミネッセンス・パネル。

【請求項2】

ガラス基板の上に相互に交差するように配置されたゲートラインとデータラインとの交差部に設置されてゲートラインでのゲート信号がイネーブルされる際に駆動されて前記データラインでの画素信号の大きさに対応する光を発生する第1及び第2画素を有するエレクトロ・ルミネッセンス・パネルにおいて、

第1及び第2画素それぞれは、第1ゲートラインとデータラインの交差部に設置され、

第1画素はエレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル駆動回路を具備し、

第2画素は前記第1ゲートラインを除いたゲートラインと前記データラインの交差部に設置されてエレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路を具備し、

第1エレクトロ・ルミネッセンス・セル駆動回路は、基底電圧ラインに接続された有機発光ダイオードと、前記第1ゲートラインと前記データラインの交差部に設置された少なくとも3つの薄膜トランジスタを有する補償回路とを具備し、

前記補償回路は、

電圧供給ラインに電流ミラーを形成するために接続された第1及び第2PMOS薄膜トランジスタと、

第1PMOS薄膜トランジスタのゲート電極と接続されたドレイン電極と、第2PMOS薄膜トランジスタのゲート電極と接続されたソース電極とを有する第3PMOS薄膜トランジスタと、

前記第2PMOS薄膜トランジスタのゲート電極と前記電圧供給ラインの間に接続された第1キャパシタとを具備し、

第1PMOS薄膜トランジスタは、第1データラインに接続されたドレイン電極とゲート電極とが結線され、

前記第2エレクトロ・ルミネッセンス・セル駆動回路は基底電圧ラインに接続された有機発光ダイオードと、前記第1ゲートラインを除いたゲートラインと前記データラインの交差部に設置された二つの薄膜トランジスタを有するセル駆動回路とを具備して、前記有機発光ダイオードは前記セル駆動回路から印加された電流の大きさに対応する光を放出し、

前記第2エレクトロ・ルミネッセンス・セル駆動回路は、

前記有機発光ダイオードと前記電圧供給ラインの間に接続された第4PMOS薄膜トランジスタと、

前記第4PMOS薄膜トランジスタの前記ゲート電極と接続されたソース電極と、前記データラインと接続されたドレイン電極とを有し、スイッチとしての役割をする第5PMOS薄膜トランジスタと、

前記第4PMOS薄膜トランジスタの前記ゲート電極と前記電圧供給ラインの間に接続された第2キャパシタとを具備することを特徴とするエレクトロ・ルミネッセンス・パネル。

【請求項3】

前記ゲートラインに接続されて前記ゲートラインを順次駆動するためのゲートドライバと、前記データラインに接続されて前記第1及び第2画素に画素信号を印加するデータド

10

20

30

40

50

ライバとを具備することを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 4】

前記有機発光ダイオードは、前記補償回路から供給された電流に対応する光を放出することを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 5】

前記第 1 エレクトロ・ルミネッセンス・セル駆動回路は、前記ゲートラインでのゲート信号がイネーブルされる間に、第 1 PMOS 薄膜トランジスタと第 2 PMOS 薄膜トランジスタが同時に駆動し、データライン上を流れる電流と所定比の電流信号が前記有機発光ダイオードに供給されることを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。10

【請求項 6】

第 1 キャパシタは、前記電圧供給ラインが前記データラインに接続される際にデータラインでの電流信号を充電して、充電された電流信号を前記第 2 PMOS 薄膜トランジスタの前記ゲート電極に供給することを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 7】

前記第 2 PMOS 薄膜トランジスタは、有機発光ダイオードに電流を供給するために前記供給電圧 (VDD) から充電された第 1 キャパシタの電圧によりターン・オンされることを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。20

【請求項 8】

前記第 3 PMOS 薄膜トランジスタは、前記第 1 及び第 2 PMOS 薄膜トランジスタに対してスイッチとして作用することを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 9】

前記第 1 及び第 2 PMOS 薄膜トランジスタは、前記第 3 PMOS 薄膜トランジスタがターン・オンされる際に電流ミラーになり、前記ミラーは、前記第 1 PMOS 薄膜トランジスタを通して前記第 1 データラインに流れる一定電流の大きさと、前記第 2 PMOS 薄膜トランジスタを通して前記有機発光ダイオードに流れる電流の大きさとが同一となるように構成されることを特徴とする請求項 8 記載のエレクトロ・ルミネッセンス・パネル。30

【請求項 10】

前記有機発光ダイオードに供給される電流は、前記第 1 キャパシタの充電電圧によって前記第 2 PMOS 薄膜トランジスタがターン・オンされた時間の間、供給されることを特徴とする請求項 9 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 11】

前記第 2 エレクトロ・ルミネッセンス・セル駆動回路は、前記ゲートラインでのゲート信号がイネーブルされる際に第 1 エレクトロ・ルミネッセンス・セル駆動回路の第 1 PMOS 薄膜トランジスタを通して第 1 データラインに供給される所定の電流 (ID) によって、これと同一の大きさの電流信号が前記有機発光ダイオードに供給されることを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。40

【請求項 12】

前記第 2 キャパシタは、前記電圧供給ラインが前記データラインに接続される際に前記データラインの電流信号を充電して、充電された電流信号を前記第 4 PMOS 薄膜トランジスタの前記ゲート電極に供給することを特徴とする請求項 2 記載のエレクトロ・ルミネッセンス・パネル。

【請求項 13】

前記第 4 PMOS 薄膜トランジスタは、有機発光ダイオードに電流を供給するために前記供給電圧 (VDD) から充電された第 2 キャパシタの電圧によりターン・オンされることを特徴とする請求項 12 記載のエレクトロ・ルミネッセンス・パネル。50

**【請求項 14】**

前記第5 PMOS薄膜トランジスタは、前記第4 PMOS薄膜トランジスタに対してスイッチとしての役割をすることを特徴とする請求項2記載のエレクトロ・ルミネッセンス・パネル。

**【請求項 15】**

前記第4 PMOS薄膜トランジスタは、前記第5 PMOS薄膜トランジスタがターン・オンされる際に、前記第1エレクトロ・ルミネッセンス駆動回路の前記第1 PMOS薄膜トランジスタと共に電流ミラーを形成することを特徴とする請求項14記載のエレクトロ・ルミネッセンス・パネル。

**【請求項 16】**

前記第1 PMOS薄膜トランジスタは、第1 PMOS薄膜トランジスタを通して前記第1データラインに一定の大きさの電流が流れるようにターン・オンされて、前記第1データラインに流れる電流の大きさと同一の電流が前記第4 PMOS薄膜トランジスタを通して前記有機発光ダイオードに供給されることを特徴とする請求項15記載のエレクトロ・ルミネッセンス・パネル。

**【請求項 17】**

前記有機発光ダイオードに供給される電流は、前記第2キャパシタの充電電圧によって前記第4 PMOS薄膜トランジスタがターン・オンされた時間の間、供給されることを特徴とする請求項16記載のエレクトロ・ルミネッセンス・パネル。

**【請求項 18】**

ゲートラインと、前記ゲートラインと交差するデータラインと、前記ゲートラインとデータラインの交差部に設置されたエレクトロ・ルミネッセンス・セルとを具備するエレクトロ・ルミネッセンス・パネルの製造方法であって、

当該製造方法は、前記第1ゲートラインと前記データラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル駆動回路を形成する過程と、前記第1ゲートラインを除いたゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路を形成する過程とを含み、

前記第1エレクトロ・ルミネッセンス・セルの駆動回路を形成する過程は、

第1エレクトロ・ルミネッセンス・セルに電圧を印加する電源を形成する過程と、

前記電源と前記データラインの間に接続され、ゲート電極とドレイン電極とが結線された第1 PMOS薄膜トランジスタを形成する過程と、

前記電源と前記エレクトロ・ルミネッセンス・セルの間に接続された第2 PMOS薄膜トランジスタを形成する過程と、

前記第1 PMOS薄膜トランジスタのゲート電極と接続されたドレイン電極と、前記第2 PMOS薄膜トランジスタのゲート電極と接続されたソース電極とを有し、スイッチとしての役割をする第3 PMOS薄膜トランジスタを形成する過程と、

前記第2 PMOS薄膜トランジスタのゲート電極と前記電源の間に接続されたキャパシタを形成する過程とを含み、

前記第2エレクトロ・ルミネッセンス・セルの駆動回路を形成する過程は、

前記エレクトロ・ルミネッセンス・セルに電圧を印加する電源を形成する過程と、

前記電源と前記エレクトロ・ルミネッセンス・セル間に接続された第4 PMOS薄膜トランジスタを形成する過程と、

前記データラインと接続されたドレイン電極と、前記第4 PMOSのゲート電極と接続されたソース電極とを有し、スイッチの役割をする第5 PMOS薄膜トランジスタを形成する過程と、

前記第4 PMOS薄膜トランジスタの前記ゲート電極と前記電源の間に接続されたキャパシタを設ける過程と、

を含むことを特徴とするエレクトロ・ルミネッセンス・パネルの製造方法。

**【発明の詳細な説明】**

10

20

30

40

50

**【0001】****【発明の属する技術分野】**

本発明はエレクトロ・ルミネッセンス・パネルに関し、特に輝度を向上させたエレクトロ・ルミネッセンス・パネルに関するものである。

**【0002】****【従来の技術】**

最近、陰極線管の短所である重さと厚さを低減する平板表示装置が開発されている。このような平板表示装置は液晶表示装置、電界放出表示装置、プラズマディスプレーパネル及びエレクトロ・ルミネッセンス（以下“EL”という）パネルがある。

**【0003】**

10 このような平板表示装置の表示品質を高めて大画面化を試みる研究が活発に行われている。ELパネルは自ら発光する自発光素子である。ELパネルは電子及び正孔のキャリアーを利用して蛍光物質を励起することでビデオ映像を表示する。ELパネルは直流低電圧の駆動が可能で応答速度が速いという長所がある。

**【0004】**

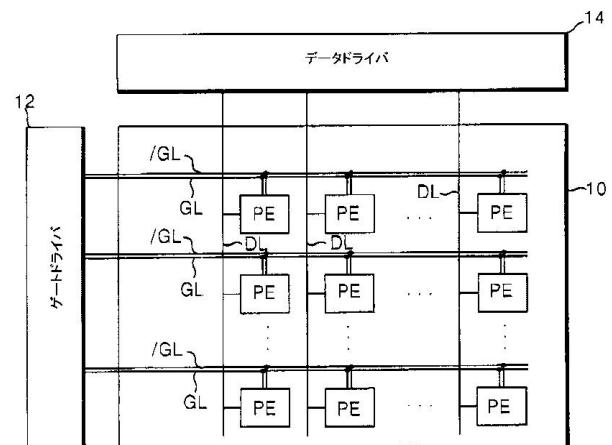

図1に示すように、従来のELパネルはガラス基板（10）上に互いに交差するゲートラインのペア（GL、/GL）及びデータライン（DL）と、ゲートラインのペア（GL、/GL）とデータライン（DL）の交差部それぞれに配列された画素素子（PE）とを具備する。

**【0005】**

20 画素素子（PE）それぞれはゲートラインのペア（GL、/GL）のゲート信号がイネーブル（Enable）される時、駆動されてデータライン（DL）上の画素信号の大きさに対応した光を発生する。

**【0006】**

このような画素素子（PE）を駆動するために、ゲートドライバ（12）はゲートラインのペア（GL、/GL）に接続されることと共にデータドライバ（14）はデータライン（DL）に接続される。

**【0007】**

ゲートドライバ（12）はゲートラインのペア（GL、/GL）を順次駆動する。データドライバ（14）はデータライン（DL）を通して画素（PE）に画素信号を供給する。

**【0008】**

30 このように、ゲートドライバ（12）及びデータドライバ（14）によって駆動される画素素子（PE）は基底電圧ライン（GND）に接続されたELセル（Organic Light Emitting Diode：OLED）と、このELセル（OLED）を駆動するためのセル駆動回路（16）で構成される。

**【0009】**

ELセル（OLED）はセル駆動回路（16）から供給される電流の大きさに対応した光を放出する。

**【0010】**

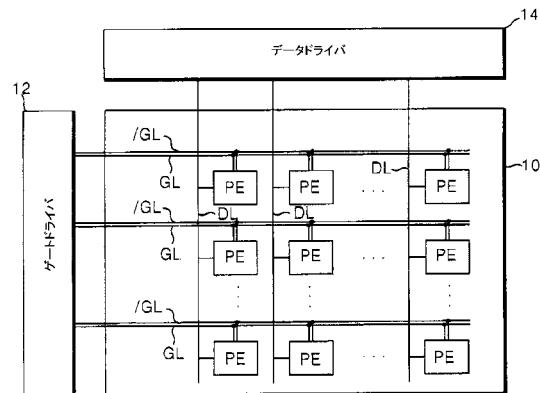

40 図2に示すように、セル駆動回路（16）はELセル（OLED）と第1及び第2ノード（N1、N2）の間に接続された第1PMOS薄膜トランジスタ（以下“TFT”という）（MP1）と、第2ノード及びELセル（OLED）の間に接続された第2PMOS TFT（MP2）と、第1及び第2ノード（N1、N2）の間に接続されたキャパシタ（C1）とを具備する。

**【0011】**

キャパシタ（C1）はデータライン（DL）から画素信号が印加される時、画素信号の電圧を充電してその充電された画素電圧を第1PMOS TFT（MP1）のゲート電極に供給する。

**【0012】**

第1PMOS TFT（MP1）はキャパシタ（C1）に充電された画素電圧によってタ 50

ーン・オンされることで、電圧供給ライン（VDDL）からの供給電圧（VDD）を第1ノード（N1）を経由してELセル（OLED）に供給する。この時、第1PMOS TFT（MP1）は画素信号の電圧レベルによって自分のチャンネル幅を変化させELセル（OLED）に供給される電流量を調節する。これによって、ELセル（OLED）は第1PMOS TFT（MP1）から印加される電流量に対応する光を発生する。

#### 【0013】

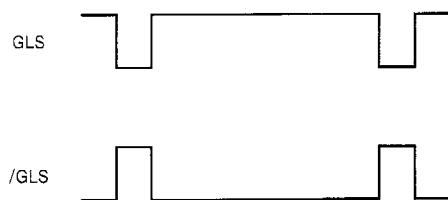

第2PMOS TFT（MP2）はゲートライン（GL）から図3に図示したようにゲート信号（GLS）に応答して第2ノード（N2）をELセル（OLED）に選択的に接続する。

#### 【0014】

これを詳細に説明すると、第2PMOS TFT（MP2）はゲート信号（GLS）がロー論理でイネーブルされる期間に第2ノード（N2）をELセル（OLED）に接続させ画素信号がキャパシタ（C1）に充電される。換言すれば、第2PMOS TFT（MP2）はゲートライン（GL）上のゲート信号（GLS）がイネーブルされる期間にキャパシタ（C1）の電流通路を形成する。

#### 【0015】

キャパシタ（C1）はゲート信号（GLS）がイネーブルされる期間に画素信号を充電して第1PMOS TFT（MP1）のゲート電極上の電圧がドレーン電極上の電圧より充電された画素信号の電圧レベルほど低くする。これによって、第1PMOS TFT（MP1）は画素信号の電圧レベルによってチャンネル幅を調節して第1ノード（N1）からELセル（OLED）の方に流れる電流量を調節する。

#### 【0016】

また、セル駆動回路（16）はゲートライン（GL）上のゲート信号（GLS）に応答する第3PMOS TFT（MP3）と、ゲート反転ライン（/GL）からの反転されたゲート信号（/GLS）に応答する第4PMOS TFT（MP4）とをさらに具備する。

#### 【0017】

第3PMOS TFT（MP3）はロー論理のゲート信号（GLS）がゲートライン（GL）から供給される期間にターン・オンされて第1ノード（N1）に接続されたキャパシタ（C1）及び第1PMOS TFT（MP1）のドレーン電極がデータライン（DL）に接続される。これを詳細に説明すると、第3PMOS TFT（MP3）はロー論理のゲート信号（GLS）に応答してデータライン（DL）上の画素信号を第1ノード（N1）の方に転送される役割をする。結果的に、第3PMOS TFT（MP3）はゲートライン（GL）上のゲート信号（GLS）がロー論理を維持する期間にターン・オンされて画素信号が第1及び第2ノード（N1、N2）の間に接続されたキャパシタ（C1）に充電される。

#### 【0018】

第4PMOS TFT（MP4）はゲート反転ライン（/GL）からロー論理の反転されたゲート信号（/GLS）が自分のゲートの方に供給される期間にターン・オンされてキャパシタ（C1）及び第1PMOS TFT（MP1）のドレーン電極が接続された第1ノード（N1）を電圧供給ライン（VDDL）に接続する。この第4PMOS TFT（MP4）がターン・オンされた期間に電圧供給ライン（VDDL）上の供給電圧（VDD）は第1ノード（N1）及び第1PMOS TFT（MP1）を経由してELセル（OLED）に供給されることで、ELセル（OLED）は画素信号の電圧レベルに対応する光を発生する。

#### 【0019】

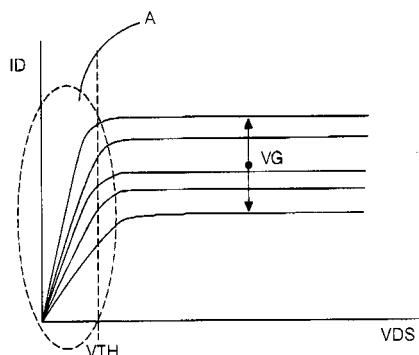

このような、ELパネルはELセル（OLED）を利用して光を発生するのに必要な電流をPMOS TFTから供給されて動作するが、このようなPMOS TFTの特性は図4のようである。

#### 【0020】

図4に示すように、PMOS TFTの特性はゲート電極に供給されるゲート電圧（VG 50

) 値によってドレーン電極及びソース電極間の電圧 (VDS) とドレーン電流 (ID) が異なる。特にELパネルは供給される電流の大きさに発光する量が異なるために電流の調節が何より重要である。

**【0021】**

ELセル (OLED) に供給される電流は、A部分に示すようにPMOS TFTのゲート電圧 (VTH) はドレーン電極及びソース電極間の電圧 (VDS) 变化に大きく影響する。この結果、ELパネルに表示されるビデオ映像に縦及び横の縞模様が発生する問題点が発生する。

**【0022】**

【発明が解決しようとする課題】

従って、本発明の目的は輝度を向上することができるようとしたエレクトロ・ルミネッセンス・パネルを提供することにある。

**【0023】**

【課題を解決するための手段】

前記の目的を達成するために、本発明によるエレクトロ・ルミネッセンス・パネルはゲートラインと、前記ゲートラインと交差するデータラインと、前記ゲートラインとデータラインの交差部に設置されたエレクトロ・ルミネッセンス・セル (OLED) とを具備するエレクトロ・ルミネッセンス・パネルにおいて、前記第1ゲートラインと前記データラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル駆動回路と、前記第1ゲートラインを除いたゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路とを具備する。

**【0024】**

前記第1エレクトロ・ルミネッセンス・セルの駆動回路はエレクトロ・ルミネッセンス・セルに電源を供給する電源と、前記電源と前記データラインの間に接続された第1PMOS薄膜トランジスタと、前記電源と前記エレクトロ・ルミネッセンス・セルの間に接続された第2PMOS薄膜トランジスタと、前記第1及び前記第2PMOS薄膜トランジスタのゲート電極の間に接続されてスイッチの役割をする第3PMOS薄膜トランジスタと、前記第2PMOS薄膜トランジスタのゲート電極と前記電源の間に接続されたキャパシタとを具備する。

**【0025】**

前記第1PMOS薄膜トランジスタと前記第2PMOS薄膜トランジスタの幅と長さの比率により前記第2PMOS薄膜トランジスタに流れる電流を調整することを特徴とする。

**【0026】**

前記第2エレクトロ・ルミネッセンス・セルの駆動回路はエレクトロ・ルミネッセンス・セルに電源を供給する電源と、前記電源と前記エレクトロ・ルミネッセンス・セル間に接続された第4PMOS薄膜トランジスタと、前記データライン及び前記第4PMOSのゲート電極の間に接続されてスイッチの役割をする第5PMOS薄膜トランジスタと、前記第4トランジスタのゲート電極と前記電源と接続されるキャパシタとを具備する。

**【0027】**

前記第1PMOS薄膜トランジスタ及び前記第4PMOS薄膜トランジスタの幅と長さの比率によって前記第4PMOS薄膜トランジスタに流れる電流を調整することを特徴とする。

**【0028】**

本発明によるエレクトロ・ルミネッセンス・パネルは第1ゲートラインとゲートラインの交差部に設置されてエレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル回路と、前記第1ゲートラインを除いたゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路とを具備する。

**【0029】**

10

20

30

40

50

前記第1エレクトロ・ルミネッセンス・セルの駆動回路はエレクトロ・ルミネッセンス・セルに電源を供給する電源と、前記電源と前記データラインの間に接続された第1PMOS薄膜トランジスタと、前記電源と前記エレクトロ・ルミネッセンス・セルの間に接続された第2PMOS薄膜トランジスタと、前記第1及び第2PMOS薄膜トランジスタの前記ゲート電極の間に接続されてスイッチの役割をする第3PMOS薄膜トランジスタと、前記第2PMOS薄膜トランジスタの前記ゲート電極と前記電源の間に接続されたキャパシタとを具備する。

## 【0030】

前記第2エレクトロ・ルミネッセンス・セルの駆動回路はエレクトロ・ルミネッセンス・セルに電源を供給する電源と、前記電源と前記データラインの間に接続された第4PMOS薄膜トランジスタと、前記データラインと前記第4PMOS薄膜トランジスタの前記ゲート電極の間に接続されてスイッチの役割をする第5PMOS薄膜トランジスタと、前記第4PMOS薄膜トランジスタの前記ゲート電極と前記電源の間に接続されたキャパシタとを具備する。

## 【0031】

ガラス基板の上に相互交差されるように配置された前記ゲートラインと前記データラインの交差部に設置されて前記ゲートラインでのゲート信号がイネーブルされる際に駆動されて前記データラインでの画素信号の大きさに対応する光を発生する第1及び第2画素とを具備する。

## 【0032】

前記ゲートラインに接続されて前記ゲートラインを順次駆動するためのゲートドライバと、前記データラインに接続されて前記第1及び第2画素に画素信号を印加するデータドライバとを具備する。

## 【0033】

前記ゲートドライバと前記データドライバで駆動される前記第1及び第2画素それぞれは、第1ゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル回路と、前記第1ゲートラインを除いたゲートラインと前記データラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路とを具備する。

## 【0034】

前記第1エレクトロ・ルミネッセンス・セル駆動回路は、基底電圧ラインに接続された有機発光ダイオードと、前記第1ゲートラインと前記データラインの交差部に設置された少なくとも3つの薄膜トランジスタを有する補償回路とを具備することを特徴とする。

## 【0035】

前記有機発光ダイオードは、前記補償回路から印加された電流の大きさに対応する光を放出することを特徴とする。

## 【0036】

前記第1エレクトロ・ルミネッセンス・セル駆動回路は、前記ゲートラインでゲート信号がイネーブルされる期間に、前記データラインでの逆方向の電流量を変化させる順方向の電流信号を前記有機発光ダイオードに印加することを特徴とする。

## 【0037】

前記補償回路は、電圧供給ラインに電流ミラーを形成するために接続された第1及び第2PMOS薄膜トランジスタと、第1及び第2PMOS薄膜トランジスタの前記ゲート電極の間に接続された第3PMOS薄膜トランジスタと、前記第2PMOS薄膜トランジスタと前記電圧供給ラインの間に接続された第1キャパシタとを具備する。

## 【0038】

前記第1キャパシタは、前記電圧供給ラインが前記データラインに接続される際に前記データラインでの電流信号を充電して、充電された電流信号を前記第2PMOS薄膜トランジスタの前記ゲート電極に印加することを特徴とする。

10

20

30

40

50

**【0039】**

前記第2PMOS薄膜トランジスタは、前記電圧供給ラインでの供給電圧が有機発光ダイオードに印加されて充電された第1キャパシタの充電電流によりターン・オンされることを特徴とする。

**【0040】**

前記第3PMOS薄膜トランジスタは、前記第1及び第2PMOS薄膜トランジスタに対してスイッチとしての役割をすることを特徴とする。

**【0041】**

前記第1及び第2PMOS薄膜トランジスタは、前記第3PMOS薄膜トランジスタがターン・オンされる際に、電流ミラーになり、前記ミラーは前記第1PMOS薄膜トランジスタを通して、前記第1データラインに流れる一定の大きさの電流と前記第2PMOS薄膜トランジスタを通して前記有機発光ダイオードに印加されて第1データラインに流れる電流の大きさと同一の電流で構成されることを特徴とする。10

**【0042】**

前記有機発光ダイオードに印加される電流は、前記第1キャパシタから発生した維持時間の間に供給されることを特徴とする。

**【0043】**

前記第1データラインに流れる電流と前記有機発光ダイオードに印加される電流は、前記第1PMOS薄膜トランジスタと第2PMOS薄膜トランジスタの幅と長さの比率により決定されることを特徴とする。20

**【0044】**

前記第1PMOS薄膜トランジスタと第2PMOS薄膜トランジスタは、ゲート電圧により影響を受けることなく前記第2PMOS薄膜トランジスタに流れる電流を調節することを特徴とする。

**【0045】**

前記第2エレクトロ・ルミネッセンス・セル駆動回路は、基底電圧ラインに接続されたエレクトロ・ルミネッセンス・セル有機発光ダイオードと、前記第1ゲートラインを除いたゲートラインと前記データラインの交差部に設置された二つの薄膜トランジスタを有するセル駆動回路とを具備して、前記有機発光ダイオードは前記セル駆動回路から印加された電流の大きさに対応する光を放出することを特徴とする。30

**【0046】**

前記セル駆動回路は、前記ゲートラインでのゲート信号がイネーブルされる際に前記データラインでの逆方向の電流量により変動する順方向の電流信号を前記有機発光ダイオードに印加することを特徴とする。

**【0047】**

前記セル駆動回路は、前記有機発光ダイオードと前記電圧供給ラインの間に接続された第4PMOS薄膜トランジスタと、前記第4PMOS薄膜トランジスタの前記ゲート電極と前記データラインの間に接続されてスイッチとしての役割をする第5PMOS薄膜トランジスタと、前記第4PMOS薄膜トランジスタの前記ゲート電極と前記電圧供給ラインの間に接続された第2キャパシタとを具備する。40

**【0048】**

前記第2キャパシタは、前記電圧供給ラインが前記データラインに接続される際に前記データラインでの電流信号を充電して、充電された電流信号を前記第4PMOS薄膜トランジスタの前記ゲート電極に印加することを特徴とする。

**【0049】**

前記第4PMOS薄膜トランジスタは、前記電圧供給ラインでの供給電圧が有機発光ダイオードに印加されて充電された第2キャパシタの充電電流によりターン・オンされることを特徴とする。

**【0050】**

前記第5PMOS薄膜トランジスタは前記第4PMOS薄膜トランジスタに対してスイッ50

チとしての役割をすることを特徴とする。

【0051】

前記第5PMOS薄膜トランジスタがターン・オンされる際に、前記第4PMOS薄膜トランジスタは前記第1エレクトロ・ルミネッセンス駆動回路の前記第1PMOS薄膜トランジスタと共に電流ミラーを形成することを特徴とする。

【0052】

前記第1PMOS薄膜トランジスタがターン・オンされて第1PMOS薄膜トランジスタを通して前記第1データラインに一定の大きさの電流が流れることで、前記第1データラインに流れる電流の大きさと同一の電流が前記第4PMOS薄膜トランジスタを通して前記有機発光ダイオードに印加することを特徴とする。 10

【0053】

前記有機発光ダイオードに印加される電流は前記第2キャパシタから発生した維持時間の間に供給されることを特徴とする。

【0054】

前記第1データラインに流れる電流と前記有機発光ダイオードに印加される電流は前記第1PMOS薄膜トランジスタと前記第4PMOS薄膜トランジスタの幅と長さの比率により決定されることを特徴とする。

【0055】

前記第1PMOS薄膜トランジスタと第4PMOS薄膜トランジスタはゲート電圧により影響を受けることなく前記第4PMOS薄膜トランジスタに流れる電流を調節することを特徴とする。 20

【0056】

本発明によるエレクトロ・ルミネッセンス・パネルの製造方法はゲートラインと、前記ゲートラインと交差するデータラインと、前記ゲートラインとデータラインの交差部に設置されたエレクトロ・ルミネッセンス・セルとを具備するエレクトロ・ルミネッセンス・パネルの製造方法において、前記第1ゲートラインと前記データラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第1エレクトロ・ルミネッセンス・セル駆動回路を形成する過程と、前記第1ゲートラインを除いたゲートラインとデータラインの交差部に設置されて前記エレクトロ・ルミネッセンス・セルを駆動するための第2エレクトロ・ルミネッセンス・セル駆動回路を形成する過程とを具備する。 30

【0057】

前記第1エレクトロ・ルミネッセンス・セルの駆動回路を形成する過程はエレクトロ・ルミネッセンス・セルに電源を供給するための電源を形成する過程と、前記電源と前記データラインの間に接続された第1PMOS薄膜トランジスタを形成する過程と、前記電源と前記エレクトロ・ルミネッセンス・セルの間に接続された第2PMOS薄膜トランジスタを形成する過程と、前記第1及び前記第2PMOS薄膜トランジスタのゲート電極の間に接続されてスイッチとしての役割をする第3PMOS薄膜トランジスタを形成する過程と、前記第2PMOS薄膜トランジスタのゲート電極と前記電源の間に接続されたキャパシタを形成する過程とを具備する。

【0058】

前記第2PMOS薄膜トランジスタに流れる電流は前記第1PMOS薄膜トランジスタと前記第2PMOS薄膜トランジスタの幅と長さの比率により前記第2PMOS薄膜トランジスタに流れる電流を調整することを特徴とする。 40

【0059】

前記第2エレクトロ・ルミネッセンス・セルの駆動回路を形成する過程は前記エレクトロ・ルミネッセンス・セルに電源を供給する電源を形成する過程と、前記電源と前記エレクトロ・ルミネッセンス・セル間に接続された第4PMOS薄膜トランジスタを形成する過程と、前記データライン及び前記第4PMOSのゲート電極の間に接続されてスイッチの役割をする第5PMOS薄膜トランジスタを形成する過程と、前記第4PMOS薄膜トランジスタの前記ゲート電極と前記電源の間に接続されたキャパシタとを具備する。 50

**【0060】**

前記第4PMOS薄膜トランジスタに流れる電流は前記第1PMOS薄膜トランジスタと前記第4PMOS薄膜トランジスタの幅と長さの比率により調整することを特徴とする。

**【0061】****【作用】**

本発明によるエレクトロ・ルミネッセンス・パネルは、一つのゲートラインに一つの補償回路を構成することで各ピクセル別で補償回路を適用したエレクトロ・ルミネッセンス・パネルより開口率を大きく向上することができる長所と共に画素セル上に発生する縞模様を除去することができる。また、従来の四つのTFT構造であったものを、二つのTFT構造にまでTFT数を減少することで開口率が大きく向上する長所がある。

10

**【0062】****【発明の実施態様】**

前記目的以外に本発明の異なる目的及び利点は添付の図面を参照した本発明の好ましい実施例に対する説明を通して明らかになるはずである。

**【0063】**

以下、本発明の実施例を、添付した図5乃至図8を参照して詳細に説明する。

**【0064】**

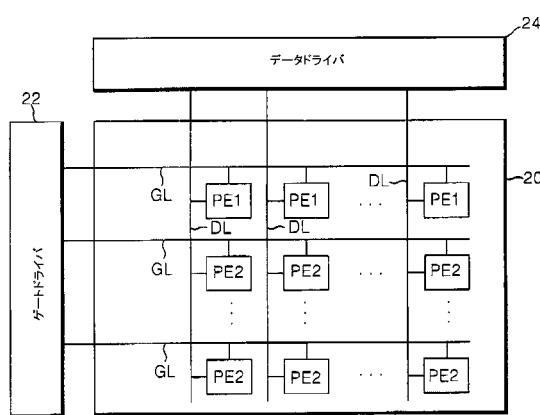

図5に示すように、本発明によるELパネルはガラス基板(20)上に互いに交差するゲートライン(GL)及びデータライン(DL)と、ゲートライン(GL)とデータライン(DL)の交差部のそれぞれに配列された第1及び第2画素素子(PE1、PE2)とを具備する。

20

**【0065】**

第1及び第2画素素子(PE1、PE2)それぞれはゲートライン(GL)のゲート信号がイネーブルされる時に駆動されてデータライン(DL)上の画素信号の大きさに対応した光を発生する。

**【0066】**

このような第1及び第2画素素子(PE1、PE2)を駆動するために、ゲートドライバ(22)はゲートライン(GL)に接続されることと共にデータドライバ(24)はデータライン(DL)に接続される。

**【0067】**

30

ゲートドライバ(22)はゲートライン(GL)を順次駆動する。データドライバ(24)はデータライン(DL)を通して第1及び第2画素素子(PE1、PE2)に画素信号を供給する。

**【0068】**

このように、ゲートドライバ(22)及びデータドライバ(24)によって駆動される第1及び第2画素素子(PE1、PE2)それぞれは第1ゲートライン(GL1)とデータライン(DL)の交差部に設置されてELパネルを駆動する第1ELセル駆動回路(PE1)と、第1ゲートライン(GL1)を除いたゲートライン(GL1乃至GLn)とデータライン(DL)の交差部に設置されてELパネルを駆動する第2ELセル駆動回路(PE2)で分けられる。

40

**【0069】**

第1ELセル駆動回路(PE1)はゲートライン(GL)上のゲート信号がイネーブルされる期間にデータライン(DL)上の逆方向の電流量によって変化する正方向の電流信号をELセル(OLED)に供給する。

**【0070】**

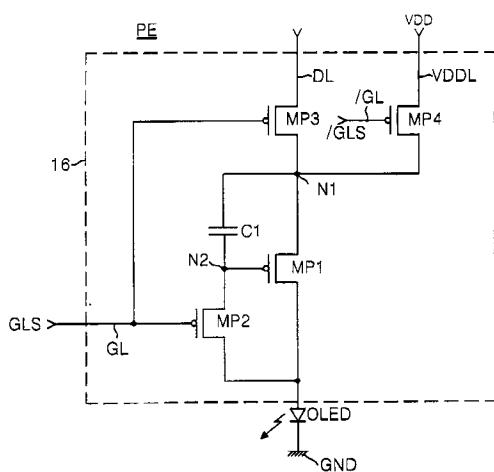

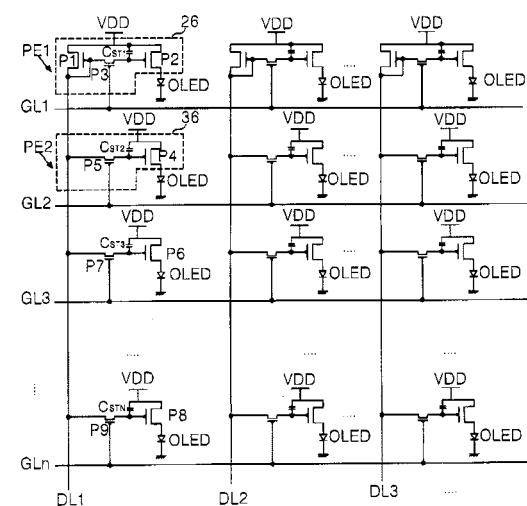

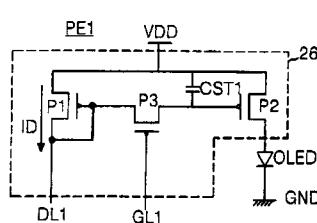

このために、第1ELセル駆動回路(PE1)は図6のように基底電圧ライン(GND)に接続されたELセル(Organic Light Emitting Diode: OLED)と、第1ゲートライン(GL1)とそれぞれのデータラインの交差部に三つの薄膜トランジスタ(以下“TFT”という)を含めて設置される補償回路部(26)で構成される。

**【0071】**

50

E Lセル(OLED)は補償回路部(26)から供給される電流の大きさに対応した光を放出する。

#### 【0072】

補償回路部(26)は電圧供給ライン(VDD)に電流ミラー(Current Mirror)を形成するように接続された第1及び第2PMOS TFT(P1、P2)と、これらの第1及び第2PMOS TFT(P1、P2)のゲート電極の間に接続されてスイッチ役割をする第3PMOS TFT(P3)と、第2PMOSTFT(P2)と電圧供給ライン(VDD)の間に接続されたキャパシタ(CST1)とを具備する。

#### 【0073】

キャパシタ(CST1)は電圧供給ライン(VDD)がデータライン(DL)に接続される時にデータライン(DL)上の電流信号を充電して、その充電された電流信号を第2PMOS TFT(P2)のゲート電極に供給する役割をする。 10

#### 【0074】

第2PMOS TFT(P2)はキャパシタ(CST1)に充電された電流信号によってターン・オンされることで電圧供給ライン(VDD)上の供給電圧(VDD)をE Lセル(OLED)に供給する。

#### 【0075】

第3PMOS TFT(P3)は第1及び第2PMOS TFT(P1、P2)をスイッチングする役割をすることで、この第3PMOS TFT(P3)がターン・オンすると、第1及び第2PMOS TFT(P1、P2)は電流ミラーの回路になる。これによって、第1PMOS TFT(P1)がターン・オンされて、この第1PMOS TFT(P1)を通して第1データライン(DL1)に一定の大きさを有する電流(ID)が流れることと共にE Lセル(OLED)には第1データライン(DL1)に流れる電流(ID)の量ほどの電流が第2PMOS TFT(P2)を通して供給される。 20

#### 【0076】

この時、E Lセル(OLED)に供給される電流はキャパシタ(CST1)によるホルディングタイムの間に供給される。このような、第1データライン(DL1)に流れる電流(ID)及びE Lセル(OLED)に供給される電流は第1PMOS TFT(P1)と第2PMOS TFT(P2)の幅と長さの比率によって決定される。即ち、第1PMOS TFT(P1)と第2PMOS TFT(P2)の幅と長さの比率が同じであると同じ大きさの電流(ID)が第1データライン(DL1)及びE Lセル(OLED)に流れる。 30

#### 【0077】

反対に、第1PMOS TFT(P1)と第2PMOS TFT(P2)の間の幅と長さの比率が1:Kであると、第2PMOS TFT(P2)へ流れる電流は第1PMOS TFT(P1)へ流れる電流よりK×電流(ID)の大きさを有する。

#### 【0078】

従って、第1PMOS TFT(P1)と第2PMOS TFT(P2)はゲート電圧(VHT)の影響を受けずに第2PMOS TFT(P2)へ流れる電流を調整することが可能となる。即ち、ゲート電圧(VHT)に関係なくE Lセル(OLED)に供給される電流の大きさを制御することができる。 40

#### 【0079】

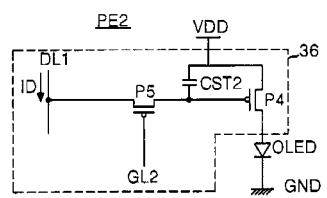

一方、第2E Lセル駆動回路(PE2)は図8のように基底電圧ライン(GND)に接続されたE Lセル(OLED)と、第1ゲートライン(GL1)を除いたデータライン(GL1乃至GLn)とそれぞれのデータラインの交差部に二つの薄膜トランジスタ(TFT)を含めて設置される補償回路部(36)で構成される。

#### 【0080】

E Lセル(OLED)はセル駆動回路(36)から供給される電流の大きさに対応した光を放出する。

#### 【0081】

10

20

30

40

50

セル駆動回路(36)はゲートライン(GL)上のゲート信号がイネーブルされた期間にデータライン(DL)上の逆方向の電流量によって変化する正方向の電流信号をELセル(LED)に供給する。

#### 【0082】

このために、セル駆動回路(36)はELセル(LED)と電圧供給ライン(VDD)の間に接続された第4PMOS TFT(P4)と、第4PMOS TFT(P4)のゲート電極とデータ電極の間に接続されてスイッチ役割をする第5PMOS TFT(P5)と、第4PMOS TFT(P4)のゲート電極と電圧供給ライン(VDD)の間に接続されたキャパシタ(CST2)とを具備する。

#### 【0083】

キャパシタ(CST2)は電圧供給ライン(VDD)がデータライン(DL)に接続される時にデータライン(DL)上の電流信号を充電して、その充電された電流信号を第4PMOS TFT(P4)のゲート電極に供給する役割をする。

#### 【0084】

第4PMOS TFT(P4)はキャパシタ(CST2)に充電された電流信号によってターン・オンされて、電圧供給ライン(VDD)上の供給電圧(VDD)をELセル(LED)に供給する。

#### 【0085】

第5PMOS TFT(P5)は、第4PMOS TFT(P4)をスイッチングする役割をして、この第5PMOS TFT(P5)をターン・オンすると、第4PMOS TFT(P4)が、上述した第1ELセル駆動回路(PE1)の第1PMOS TFT(P1)の電流ミラー回路になる。

10

#### 【0086】

これによって、第4PMOS TFT(P4)がターン・オンされて、この第1PMOS TFT(P1)を通して第1データライン(DL1)に一定の大きさを有する電流(ID)が流れることによって、ELセル(LED)には第1データライン(DL1)に流れる電流(ID)の量と同じ電流が第4PMOS TFT(P4)を通して供給される。

#### 【0087】

この時、ELセル(LED)に供給される電流はキャパシタ(CST2)によるホルディングタイムの間に供給される。このような、第1データライン(DL1)に流れる電流(ID)及びELセル(LED)に供給される電流は第1PMOS TFT(P1)と第4PMOS TFT(P4)の幅と長さの比率によって決定される。

20

#### 【0088】

即ち、第1PMOS TFT(P1)と第4PMOS TFT(P4)の幅と長さの比率が同じであれば、同じ大きさの電流(ID)が第1データライン(DL1)及びELセル(LED)に流れる。

#### 【0089】

反対に、第1PMOS TFT(P1)と第4PMOS TFT(P4)の幅と長さの比率が1:Kであれば、第4PMOS TFT(P4)へ流れる電流は第1PMOS TFT(P1)へ流れる電流よりK×電流(ID)の大きさを有する。

30

#### 【0090】

従って、第1PMOS TFT(P1)と第4PMOS TFT(P4)はゲート電圧(VHT)の影響を受けずに第4PMOS TFT(P4)へ流れる電流を調整することが可能となる。即ち、ゲート電圧(VHT)に関係なくELセル(LED)に供給される電流の大きさを制御することができる。

40

#### 【0091】

#### 【発明の効果】

上述のように、本発明によるエレクトロ・ルミネッセンス・パネルは一つのゲートラインに一つの補償回路を構成することで各ピクセル別で補償回路を適用したエレクトロ・ルミネッセンス・パネルより開口率を大きく向上することができると共に画素セル上に発生さ

50

れる縞模様を除去することができる。また、従来の四つのTFT構造であったものを、2つのTFT構造にまで TFT 数を減少することで開口率が大きく向上することができる長所がある。

#### 【0092】

以上説明した内容を通して当業者であれば本発明の技術思想を一脱しない範囲で多様な変更及び修正の可能であることが分かる。従って、本発明の技術的な範囲は明細書の詳細な説明に記載された内容に限らず特許請求の範囲によって定めなければならない。

#### 【図面の簡単な説明】

【図1】 図1は従来のエレクトロ・ルミネッセンス・パネルを概略的に表すブロック図である。

10

【図2】 図2は図1に図示された画素素子を詳細に表す回路図である。

【図3】 図3は図1に図示された画素素子に供給されるゲート信号を表す信号波形図である。

【図4】 図4は薄膜トランジスタの特性を表すグラフィックである。

【図5】 図5は本発明によるエレクトロ・ルミネッセンス・パネルを概略的に表すブロック図である。

【図6】 図6は図5に図示されたエレクトロ・ルミネッセンス・パネルを表す等価的な回路図である。

【図7】 図7は図6に図示された第1ELセル駆動回路(P E1)を表す回路図である。

20

【図8】 図8は図6に図示された第2ELセル駆動回路(P E2)を表す回路図である。

#### 【符号の説明】

12、22：ゲートドライバ

14、24：データドライバ

16、26、36：セル駆動回路

P E：画素素子

P E1、P E2：第1及び第2ELセル駆動回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 リー, ハン サン

大韓民国 ソウル, カンアク - ク, シンリム 1 - ドン 1608 - 9, 202

(72)発明者 パク, ジヨン キュ-

大韓民国 ソウル, カンアク - ク, シンリム 1 - ドン 1630 - 17, 101

(72)発明者 アン, テ ジヨン

大韓民国 ソウル, スンドン - ク, ヘンダン 1 - ドン 102 - 8

審査官 西島 篤宏

(56)参考文献 特開平11 - 282419 (JP, A)

特開2000 - 221942 (JP, A)

特開2002 - 221917 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00- 3/38

H01L 51/50

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光板                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP3861996B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2006-12-27 |

| 申请号            | JP2001391148                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2001-12-25 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | Eruji 飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | Eruji 飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | ペスンジョン<br>リーハンサン<br>パクジョンキュー<br>アンテジョン                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | ペ, ソン ジョン<br>リー, ハン サン<br>パク, ジョン キュー<br>アン, テ ジョン                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3241 G09G3/3233 G09G3/3283 G09G2300/0465 G09G2300/08 G09G2300/0842                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.K G09G3/20.624.B G09G3/20.641.D G09G3/20.642.D H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 3K007/DB03 3K007/GA00 3K107/AA01 3K107/BB01 3K107/CC02 3K107/EE03 3K107/GG00 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD30 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AC04 5C380/BA05 5C380/BB01 5C380/BB22 5C380/CA08 5C380/CB01 5C380/CB37 5C380/CC02 5C380/CC14 5C380/CC15 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC62 5C380/CC63 5C380/CD012 5C380/CD013 5C380/CD014 5C380/CE01 5C380/HA13 |         |            |

| 优先权            | 1020000081417 2000-12-23 KR                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | <a href="#">JP2002258798A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

要解决的问题：改善电致发光面板的亮度。解决方案：该面板具有第一电致发光单元驱动电路和第二电致发光单元驱动电路，第一电致发光单元驱动电路驱动电致发光单元，第一电致发光单元驱动电路设置在第一栅极线和数据线的交叉处，第二电致发光单元驱动电路驱动电致发光单元并且布置在除第一栅极线和数据线之外的栅极线的交叉点。

## 【 图 1 】