(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-225140

(P2013-225140A)

(43) 公開日 平成25年10月31日(2013.10.31)

|                   |           |                      |

|-------------------|-----------|----------------------|

| (51) Int.Cl.      | F 1       | テーマコード (参考)          |

| <b>G09G 3/30</b>  | (2006.01) | GO9G 3/30 J 3K107    |

| <b>G09G 3/20</b>  | (2006.01) | GO9G 3/20 670J 5C080 |

| <b>H01L 51/50</b> | (2006.01) | GO9G 3/20 611H 5C380 |

|                   |           | GO9G 3/20 611A       |

|                   |           | HO5B 33/14 A         |

審査請求 有 請求項の数 8 O L (全 21 頁)

|              |                                     |            |                                                                         |

|--------------|-------------------------------------|------------|-------------------------------------------------------------------------|

| (21) 出願番号    | 特願2013-117384 (P2013-117384)        | (71) 出願人   | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号                              |

| (22) 出願日     | 平成25年6月3日 (2013.6.3)                | (74) 代理人   | 100126240<br>弁理士 阿部 琢磨                                                  |

| (62) 分割の表示   | 特願2007-178825 (P2007-178825)<br>の分割 | (74) 代理人   | 100124442<br>弁理士 黒岩 創吾                                                  |

| 原出願日         | 平成19年7月6日 (2007.7.6)                | (72) 発明者   | 安部 勝美<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内                                 |

| (31) 優先権主張番号 | 特願2006-240257 (P2006-240257)        | F ターム (参考) | 3K107 AA01 BB01 CC02 CC21 CC33<br>EE03 HH04 HH05                        |

| (32) 優先日     | 平成18年9月5日 (2006.9.5)                |            | 5C080 AA06 BB05 CC06 DD02 DD05<br>DD26 DD27 DD29 FF11 JJ02<br>JJ03 JJ04 |

| (33) 優先権主張国  | 日本国 (JP)                            |            |                                                                         |

最終頁に続く

(54) 【発明の名称】発光表示デバイス

## (57) 【要約】

【課題】 印加電圧による薄膜トランジスタの特性シフトによる影響を抑えることが可能であり、大型・高精細の発光表示デバイスに適用可能であり、単極性の薄膜トランジスタのみで構成される駆動回路を用いた発光表示デバイスを提供する。

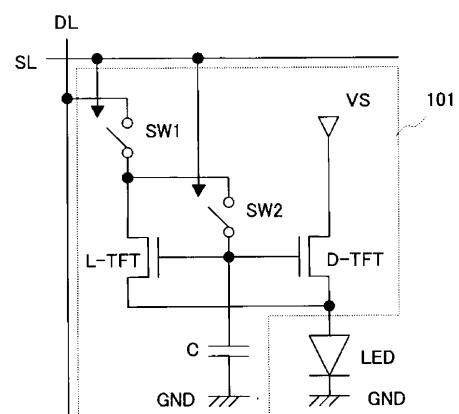

【解決手段】 発光表示デバイスは、画素内に有機EL素子LEDとこれを駆動するための駆動回路101とを有する。駆動回路101は、電流書き込み期間に、TFT3～5を同時に導通し、TFT3を介して接地線GNDとLEDの一端とを同一電圧にする。そして、TFT4、5を介してデータ線DLからの電流をカレントミラー回路を構成するL-TFT及びD-TFTに供給し、L-TFT及びD-TFTのゲート-ソース間電圧として容量Cに保持する。さらに、LED駆動期間に、TFT3～5を同時に遮断し、容量Cの保持電圧に従いD-TFTのソース-ドレイン間の電流をLEDに供給する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

マトリックス状に配列した複数の画素の各々に、発光素子と、前記発光素子を駆動するための駆動回路とを有する発光表示デバイスであって、

前記駆動回路は、

ゲート端子同士及びソース端子同士が各々接続され、前記ソース端子が前記発光素子の一端に接続され、同一極性である第一及び第二の薄膜トランジスタと、

一端が前記第一及び第二の薄膜トランジスタのソース端子及び前記発光素子の一端に接続され、他端が前記発光素子の動作電圧以下の電圧が印加される第一の配線に接続される第一のスイッチと、

一端が前記第一の薄膜トランジスタのドレイン端子に接続され、他端が第二の配線に接続される第二のスイッチと、

一端が前記第一及び第二の薄膜トランジスタのゲート端子に接続され、他端が前記第二の配線または前記第一の薄膜トランジスタのドレイン端子に接続される第三のスイッチと、

一端が第二の薄膜トランジスタのドレイン端子に接続され、他端が第三の配線に接続される第四のスイッチと、

一端が前記第一及び第二の薄膜トランジスタのゲート端子に接続され、他端が前記第一及び第二の薄膜トランジスタのソース端子に接続される容量と、

を備え、

前記第一ないし第四のスイッチの各々は、ソース端子とドレイン端子をスイッチの両端子とする薄膜トランジスタで構成されており、前記第一ないし第三のスイッチを構成する薄膜トランジスタのゲートが共通の第一の走査線に接続され、前記第四のスイッチを構成する薄膜トランジスタのゲート端子が、前記第一の走査線とは異なる第二の走査線に接続されることを特徴とする発光表示デバイス。

## 【請求項 2】

前記駆動回路は、

第一の期間に、前記第一のスイッチをオンさせて前記第一の配線と前記発光素子の一端とを電気的に接続し、前記第四のスイッチをオフにして前記第二の薄膜トランジスタのドレイン端子 - ソース端子間の電流を遮断し、かつ前記第二と第三のスイッチをオンさせて前記発光素子の駆動信号を供給する第二の配線と前記第一の薄膜トランジスタのドレイン端子及び前記第一及び第二の薄膜トランジスタのゲート端子とを電気的に接続して、前記第二の配線から前記第一の薄膜トランジスタのドレイン端子 - ソース端子間に流れる電流により決まる前記第二の薄膜トランジスタのゲート端子 - ソース端子間の電圧を前記容量に保持し、

第二の期間に、前記第一ないし第三のスイッチをオフにし、前記第四のスイッチをオンさせて、前記容量の保持電圧に従い前記第二の薄膜トランジスタのドレイン端子 - ソース端子間に流れる電流を前記発光素子に供給し、

第三の期間に、前記第一ないし第四のスイッチをオフにして、前記発光素子に流れる電流を遮断することを特徴とする請求項 1 に記載の発光表示デバイス。

## 【請求項 3】

前記第一の薄膜トランジスタのチャネル幅をチャネル長で割った値が、前記第二の薄膜トランジスタのチャネル幅をチャネル長で割った値と同じ、あるいは、前記第一の薄膜トランジスタのチャネル幅をチャネル長で割った値が、前記第二の薄膜トランジスタのチャネル幅をチャネル長で割った値より大きいことを特徴とする請求項 1 または 2 に記載の発光表示デバイス。

## 【請求項 4】

前記容量の容量値は、前記第一の薄膜トランジスタのチャネル容量と、ゲート - ドレインオーバーラップ容量と、前記第二の薄膜トランジスタのチャネル容量と、ゲート - ドレインオーバーラップ容量とを加えた全容量値の 3 倍以上であることを特徴とする請求項 1

10

20

30

40

50

ないし 3 のいずれか 1 項に記載の発光表示デバイス。

【請求項 5】

前記第一及び第二の薄膜トランジスタが p 型薄膜トランジスタで構成され、前記発光素子のカソード端子が、前記第一及び第二の p 型薄膜トランジスタのソース端子に接続されることを特徴とする請求項 1 ないし 4 のいずれか 1 項に記載の発光表示デバイス。

【請求項 6】

前記第一及び第二の薄膜トランジスタが n 型薄膜トランジスタで構成され、前記発光素子のアノード端子が、前記第一及び第二の n 型薄膜トランジスタのソース端子に接続されることを特徴とする請求項 1 ないし 4 のいずれか 1 項に記載の発光表示デバイス。

【請求項 7】

前記駆動回路の n 型薄膜トランジスタが、キャリア密度が  $10^{18}$  [ cm<sup>-3</sup> ] 以下であるアモルファス金属酸化物から構成される n 型半導体膜を n 型薄膜トランジスタのチャネル膜として用い、移動度が 1 [ cm<sup>2</sup> / V s ] 以上、かつ、オンオフ比が  $10^6$  以上であることを特徴とする請求項 6 に記載の発光表示デバイス。

10

【請求項 8】

前記発光素子が有機 E L 素子であることを特徴とする請求項 1 ないし 7 のいずれか 1 項に記載の発光表示デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、供給される電流に従って機能を果たす電流負荷デバイスに関し、特に電流負荷として発光素子を用いた発光表示デバイスに関する。特に、本発明は、発光素子としての有機エレクトロルミネッセンス (Electro-Luminescence、以下 E L ) 素子と、有機 E L 素子に電流を供給するための駆動回路とで構成される画素をマトリックス状に複数備えた発光表示デバイスに関する。

20

【背景技術】

【0002】

有機 E L 素子は、発光ダイオード (LED : Light Emission Diode) と同様に電流を流すことで発光する発光素子であり、OLED (Organic LED) とも呼ばれる。この有機 E L 素子とその駆動回路とで構成される画素をマトリックス状に複数備えた発光表示デバイスとして、アクティブマトリックス (Active-Matrix、以下 AM ) 型有機 E L ディスプレイが検討されている。

30

【0003】

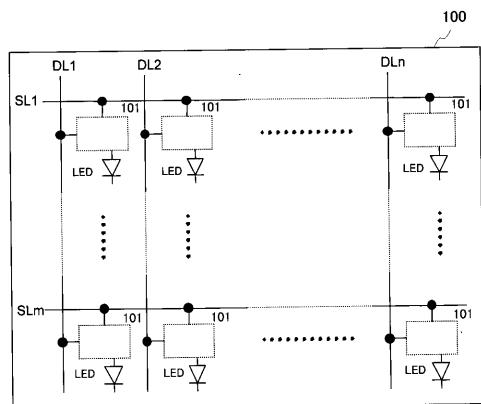

図 6 は、AM 型有機 E L ディスプレイの画素の構成例を示す。同図において、LED は有機 E L 素子、101 は駆動回路、DL はデータ線、SL は走査線を示す。図 7 は、その画素をマトリックス状 (n 列 × m 行) に複数配列した AM 型有機 E L ディスプレイの構成例をそれぞれ示す。同図において、SL (1) 、…、SL (m) は、1 ~ m 番目の行毎に配置される走査線、DL (1) 、…、DL (n) は、1 ~ n 番目の列毎に配置されるデータ線をそれぞれ示す。同図に示す AM 型有機 E L ディスプレイ 100 は、画素毎に、各列の走査線 SL の信号 (H レベル、L レベル) により、各行のデータ線 DL を介して駆動回路 101 から有機 E L 素子 LED へ供給する電圧、電流、時間等を制御する。こうすることで、有機 E L 素子 LED の輝度を調節し、階調表示を行う。

40

【0004】

このような AM 型有機 E L ディスプレイにおいては、有機 E L 素子の電圧 - 輝度特性が経時変化する場合、表示品質に影響を与える。これは、駆動回路の構成要素である薄膜トランジスタ (Thin-Film-Transistor、以下 TFT) の特性にばらつきがある場合や、印加される電気的ストレスにより TFT の特性が変化する場合も同様である。従って、ムラのない高品質な表示を実現するには、有機 E L 素子特性の経時変化や TFT の特性ばらつき・変化の影響を受けにくい駆動回路・駆動方法の開発が必要である。

50

## 【0005】

(従来例1)

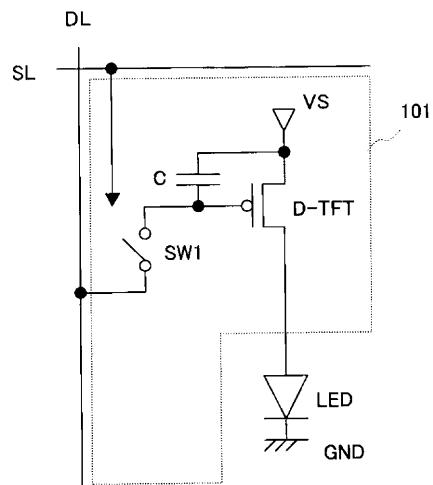

図8は、第一の従来例として、最も簡単な駆動回路を示す。同図において、LEDは有機EL素子、101は駆動回路、DLはデータ線、SLは走査線、VSは電源線、GNDは接地線、D-TFTは駆動用のp型TFT、Cは容量を示す。SW1はスイッチ(スイッチング素子)を示し、走査線SLの信号によりオンオフ動作が制御される。

## 【0006】

本従来例では、走査線SLの信号によりスイッチSW1をONにし、駆動回路101内のTFT(D-TFT)のゲート端子にスイッチSW1を介してデータ線DLからの電圧を印加し、ゲート端子-ソース端子間の電圧を容量Cに保持する。TFTは、ゲート端子に印加した電圧に従って、有機EL素子LEDに電流を供給する。本従来例において、TFTに特性ばらつきがあると、有機EL素子LEDに供給する電流がばらつき、表示ムラが見える。従来、このような課題を解決するための駆動回路がいくつか提案されている。以下、その駆動回路の従来例について説明する。

10

## 【0007】

(従来例2)

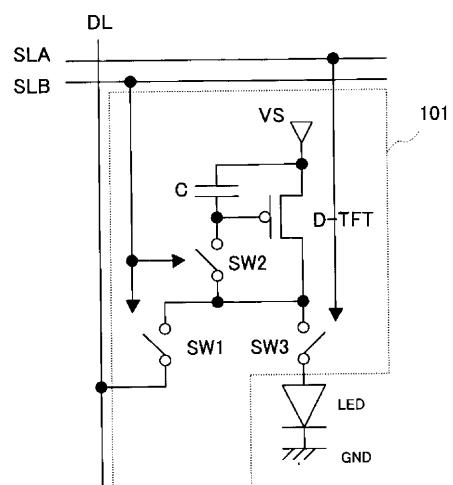

図9は、第二の従来例として、特許文献1に開示されている駆動回路を示す。同図において、LEDは有機EL素子、101は駆動回路、DLはデータ線、SLA、SLBは走査線、VSは電源線、GNDは接地線、D-TFTは駆動用のp型TFT、Cは容量を示す。SW1、SW2、SW3はスイッチ(スイッチング素子)を示し、走査線SLの信号によりオンオフ動作が制御される。

20

## 【0008】

本従来例では、走査線SLAの信号によりスイッチSW1、SW2をONにし、駆動回路101内のゲート端子-ドレイン端子間がスイッチSW2を介して短絡したTFT(D-TFT)に、スイッチSW1を介して外部(データ線DL)から電流を供給する。こうすることで、TFTのゲート端子の電圧を、TFTのしきい値と移動度に応じて、外部からの電流が流れる電圧とすることができます。引き続き、電流経路を有機EL素子LEDに向けると、TFTのゲート端子-ソース端子間電圧が外部からの電流が流れる電圧と同じである。このため、走査線SLBの信号によりスイッチSW3をONにすると、TFTは、電流源として、外部からの電流と同じ大きさの電流をスイッチSW3を介して有機EL素子LEDに流すことができる。従って、外部からの電流にばらつきがなければ、本従来例は、TFTの特性ばらつきに関わらず、有機EL素子に一定の電流を流すことができ、ムラのない表示が可能となる。

30

## 【0009】

(従来例3)

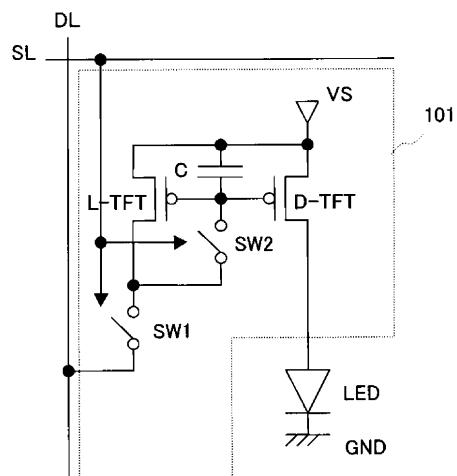

図10は、第三の従来例として、特許文献2に開示されている駆動回路を示す。同図において、LEDは有機EL素子、101は駆動回路、DLはデータ線、SLは走査線、VSは電源線、GNDは接地線、L-TFT及びD-TFTはカレントミラーを構成する一対のp型TFT、Cは容量を示す。SW1、SW2は、スイッチ(スイッチング素子)を示し、走査線SLの信号によりオンオフ動作が制御される。

40

## 【0010】

本従来例は、2つのTFT(L-TFT、D-TFT)がカレントミラーを構成している。これによれば、走査線SLの信号によりスイッチSW1、SW2をONにし、カレントミラーレ回路内の方のTFT(L-TFT)のゲート端子とドレイン端子をスイッチSW2を介して短絡し、外部(データ線DL)からスイッチSW1を介して電流を供給する。すると、L-TFTのゲート端子の電圧は、外部からの電流を流すような電圧とすることができます。これに伴い、カレントミラーレ回路の他方のTFT(D-TFT)は、電圧に従い、有機EL素子LEDに電流を供給する。カレントミラーレ回路を構成する2つのTFTは近接し、その間の特性ばらつきが小さいため、有機EL素子LEDに供給する電流は、外部からの電流と、L-TFTとD-TFTの電流能力比により決定される。従って、

50

外部からの電流にばらつきがなければ、本従来例は、TFTの特性ばらつきに関わらず、有機EL素子LEDに一定の電流を流すことができ、ムラのない表示が可能となる。

【0011】

上述の回路には多結晶シリコン (polycrystalline-Si、以下p-Si)、非晶質シリコン (amorphous-Si、以下a-Si)、有機半導体 (Organic Semiconductor、OS) 等をチャネル層とするTFTが検討されている。p-Si TFTは、移動度が高く、動作電圧を低くできるが、製造コストが高くなる。一方、a-SiやOS TFTは、製造ステップ数が少なく、コストを安価にできるが、p-Si TFTに比べ移動度が低いために、動作電圧が高く、消費電力が大きい。また、酸化亜鉛 (ZnO) などの金属酸化物半導体をチャネル層として用いるTFTも、近年、開発が進められており、a-SiやOSよりも高い移動度が報告されている。

10

【0012】

a-Si、OS、金属酸化物半導体をチャネル層とするTFTは、n型TFTとp型TFTを同一基板上に形成する相補型TFTとすることは難しい。例えば、a-Siや金属酸化物では高移動度のp型半導体というのが得られておらず、p型TFTの形成が困難である。また、OSでは、高移動度のn型半導体とp型半導体の材料が異なるために、工程が2倍となり、安価な製造が難しくなる。従って、これらのTFTを用いた駆動回路は、n型あるいはp型のTFTのみで構成する必要がある。

20

【0013】

また、a-Si、OS、金属酸化物をチャネル層とするTFTは、ゲート端子-ソース端子間に印加される電圧によって、電流-電圧特性がシフトすることが知られている。

【0014】

上記の中で、a-Si TFTは、AM型液晶ディスプレイ (Liquid Crystal Display、以下LCD) の画素に用いられており、対角サイズが数十インチの生産技術が確立されている。このため、a-Si TFTは、対角サイズが10インチ以上である大型のAM型有機ELディスプレイの駆動回路向けTFTとして有望視され、技術開発が進められている（後述の図11に示す第四の従来例参照）。

30

【0015】

一方、有機EL素子は、一般に、アノード電極とカソード電極の間に、少なくとも有機材料による発光層が挟まれた構造を有し、有機材料が熱や電磁波、水分などの影響を受け特性変化を起こしやすい。このため、有機EL素子を用いた発光表示デバイスは、駆動回路やアノード電極作成後に、有機材料発光層を形成し、ダメージの少ない真空蒸着などによりカソード電極を作成するという製造過程が好ましい。

【0016】

これに従い、AM型有機ELディスプレイを、n型TFTで構成される駆動回路と、下からアノード電極、有機発光層、カソード電極という順で形成される有機EL素子と、により画素を構成する場合を考える。この場合、特許文献1、2の機能は、p型TFTをn型TFTに置き換えるだけでは実現できない。なぜなら、特許文献1、2においては、p型TFTのソース端子電圧は電源により固定され、ゲート端子電圧は外部からの電流によって決められる。このため、有機EL素子駆動時には、ゲート端子とソース端子間の電圧差が固定されており、有機EL素子に対し、定電流源として機能している。ここで、p型TFTをn型TFTに置き換えると、ゲート端子-ドレイン端子間が固定されることになるため、定電流源として機能しなくなる。また、前述の通り、印加電圧による特性シフトが生じるため、その影響を抑えることが必要となる。

40

【0017】

（従来例4）

第四の従来例は、a-Si TFTを用いた駆動回路による上記課題を解決するための従来技術である。図11は、第四の従来例として、非特許文献1、2に開示されている駆動回路を示す。同図において、LEDは有機EL素子、101は駆動回路、DLはデータ線、SLは走査線、VSは電源線、GNDは接地線、L-TFT及びD-TFTはカレン

50

トミラー回路を構成する一対のn型TFT、Cは容量を示す。SW1、SW2はスイッチ(スイッチング素子)を示し、走査線SLの信号によりオンオフ動作が制御される。

【0018】

本従来例は、特許文献2のカレントミラー回路を応用したものである。これによれば、走査線SLの信号によりスイッチSW1、SW2をONにし、L-TFTのゲート端子とドレイン端子をスイッチSW2を介して接続し、スイッチSW1を介して外部(データ線DL)から電流を供給する。すると、供給された電流は、L-TFTのドレイン端子からソース端子、さらに有機EL素子LEDに流れる。従って、L-TFTのゲート端子とソース端子の電圧は、共に、外部からの電流を流すような電圧となる。さらに、D-TFTは、L-TFTとゲート端子とソース端子が各々共通であるため、L-TFTのゲート端子電圧、ソース端子電圧に従い、有機EL素子LEDに電流を供給する。このゲート端子電圧を容量Cにより保持することで、外部から電流が停止した期間でも、D-TFTは、外部から電流が供給される期間と同じ電流を有機EL素子LEDに供給できる。

【0019】

さらに、動作時にはD-TFTとL-TFTは、ゲート・ソースの各端子にそれぞれ同じ電圧が印加され、これらのTFTの特性シフトは同等となる。この時、D-TFTとL-TFTとの電流能力比は保持される。この場合、特性シフトが生じてもこれらのTFTに流れる電流は、特性シフト前と同等とすることができます。

【0020】

ただし、本従来例では、L-TFTは、D-TFTに比べ、電流を流す能力が十分に低い必要がある。なぜなら、有機EL素子には、外部から電流が供給されている期間にはL-TFTとD-TFTから電流が供給される一方、外部からの電流が停止する期間にはD-TFTのみから電流が供給される。従って、両期間において、有機ELの電流能力によって決まるL-TFTとD-TFTのソース電圧は、L-TFTの電流値が大きい場合には一致しない。この場合、外部から電流が供給されている期間で設定した電流を、外部からの電流が停止する期間に流すことができなくなる。結果として、外部からL-TFTに供給される電流は、D-TFTが有機EL素子に供給する電流に比べ、小さくする必要がある。

【0021】

一方、近年、有機EL素子の電流・輝度特性の向上が進み、有機EL素子への供給電流が低下している。また、有機ELディスプレイは、より大型・高精細のものが求められており、配線負荷が増大する傾向にある。従って、従来技術において、特に、低階調に相当する低い電流を外部から供給する場合、配線負荷を充電するための時間が長くなる。この時、駆動回路内のTFTのゲートを、TFTのしきい値と移動度に応じて、外部からの電流が流れる電圧とする動作に時間がかかるようになり、高精細、大画面の表示装置に適用することが難しくなる。これを回避するためには、外部からの電流を大きくする手段が考えられるが、この手段は、前述の通り、第四の従来例には適用できない。

【先行技術文献】

【特許文献】

【0022】

【特許文献1】特表2002-517806号公報

【特許文献2】特開2001-147659号公報

【非特許文献】

【0023】

【非特許文献1】A.Nathan et al., SID 05 DIGEST, P-26, Fig. 3

【非特許文献2】A.Nathan et al., SID 06 DIGEST, 46.1, Fig. 1

【発明の概要】

【発明が解決しようとする課題】

10

20

30

40

50

## 【0024】

本発明は、印加電圧による薄膜トランジスタの特性シフトによる影響を抑えることが可能であり、大型・高精細の発光表示デバイスに適用可能であり、単極性の薄膜トランジスタのみで構成される駆動回路を用いた発光表示デバイスを提供することを目的とする。

## 【課題を解決するための手段】

## 【0025】

上記目的を達成するため、本発明に係る第一の発光表示デバイスは、マトリックス状に配列した複数の画素の各々に、発光素子と、前記発光素子を駆動するための駆動回路とを有する。駆動回路は、第一及び第二の薄膜トランジスタ、第一ないし第四のスイッチ、容量を有する。

10

## 【0026】

第一及び第二の薄膜トランジスタは、ゲート端子同士及びソース端子同士が各々接続され、ソース端子が発光素子の一端に接続され、同一極性である。

## 【0027】

更に、容量は、一端が第一及び第二の薄膜トランジスタのゲート端子に接続され、他端が第一及び第二の薄膜トランジスタのソース端子に接続される。

20

## 【0028】

第一のスイッチは、一端が前記第一及び第二の薄膜トランジスタのソース端子及び発光素子の一端に接続され、他端が発光素子の動作電圧以下の電圧が印加される第一の配線に接続される。

## 【0029】

第二のスイッチは、一端が第一の薄膜トランジスタのドレイン端子に接続され、他端が第二の配線に接続される。

## 【0030】

第三のスイッチは、一端が第一及び第二の薄膜トランジスタのゲート端子に接続され、他端が第二の配線または第一の薄膜トランジスタのドレイン端子に接続される。

30

## 【0031】

第四のスイッチは、一端が第二の薄膜トランジスタのドレイン端子に接続され、他端が第三の配線に接続される。

## 【0032】

第一ないし第四のスイッチの各々は、ソース端子とドレイン端子をスイッチの両端子とする薄膜トランジスタで構成されており、第一ないし第三のスイッチを構成する薄膜トランジスタのゲートが共通の第一の走査線に接続され、第四のスイッチを構成する薄膜トランジスタのゲート端子が、第一の走査線とは異なる第二の走査線に接続される。

40

## 【発明の効果】

## 【0033】

本発明によれば、各画素に、同一極性の一対の薄膜トランジスタから構成されるカレントミラー回路を備えた駆動回路が設けられる。一対の薄膜トランジスタは、互いに共通なソース端子が、発光素子の一端に接続され、かつ、第一の配線に第一のスイッチを経由して接続されると共に、ゲート端子とソース端子間には容量が設けられる。こうすることで、印加電圧による薄膜トランジスタの特性シフトによる影響を抑えることが可能であり、大型・高精細の発光表示デバイスに適用可能であり、単極性の薄膜トランジスタのみで構成される駆動回路を用いた発光表示デバイスを提供することができる。

## 【図面の簡単な説明】

## 【0034】

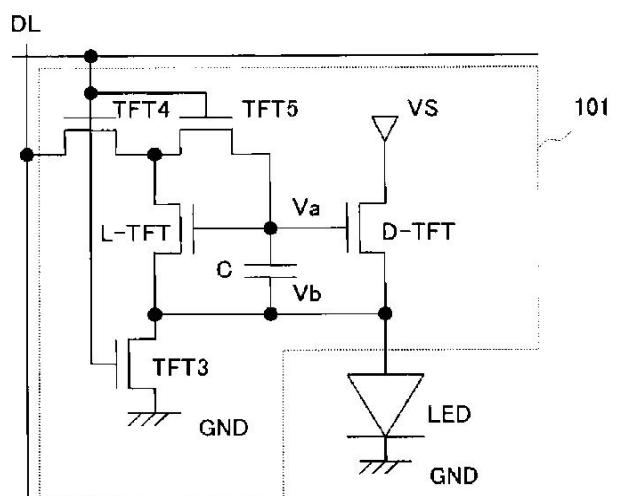

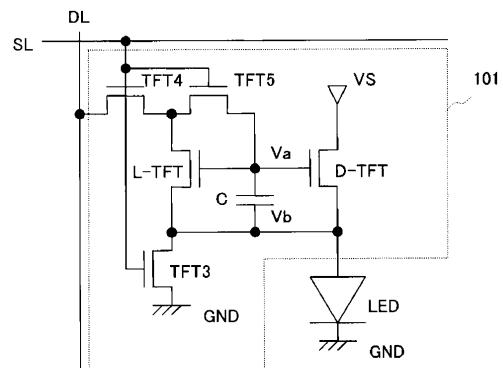

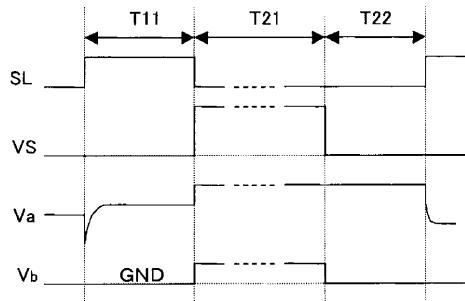

【図1】本発明の第一の実施例に係る発光表示デバイスの画素の構成を示す回路図である。

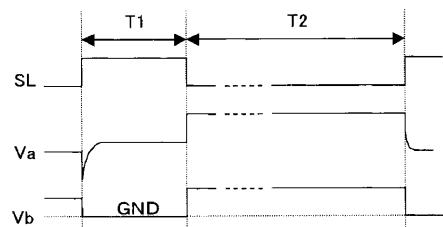

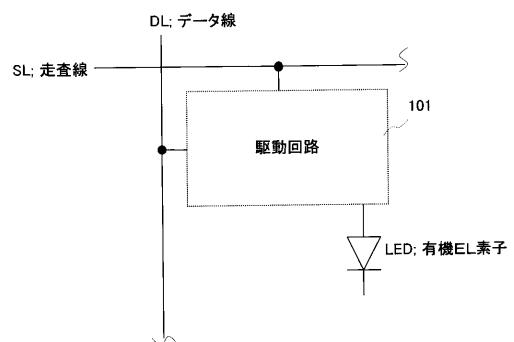

【図2】本発明の第一の実施例に係る発光表示デバイスの動作を説明するタイミングチャートである。

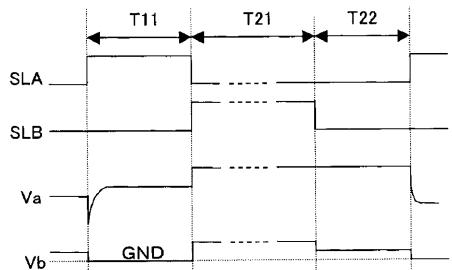

【図3】本発明の第二の実施例に係る発光表示デバイスの動作を説明するタイミングチャ

50

ートである。

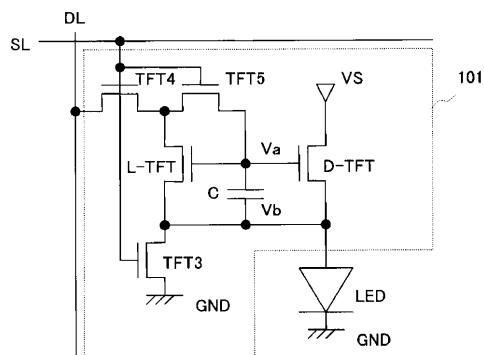

【図4】本発明の第三の実施例に係る発光表示デバイスの画素の構成を示す回路図である。

【図5】本発明の第三の実施例に係る発光表示デバイスの動作を説明するタイミングチャートである。

【図6】画素の構成を示す図である。

【図7】有機EL表示装置の構成を示す図である。

【図8】第一の従来例の画素の構成を示す回路図である。

【図9】第二の従来例の画素の構成を示す回路図である。

【図10】第三の従来例の画素の構成を示す回路図である。

【図11】第四の従来例の画素の構成を示す回路図である。

【発明を実施するための形態】

【0035】

以下、本発明の実施の形態について、図面を参照して説明する。

【0036】

本実施の形態は、有機EL素子を用いる発光表示デバイスについて説明するが、本発明は有機EL素子以外の供給される電流により発光する発光表示デバイスや、供給される電流により任意の機能を示す一般的な電流負荷を用いる電流負荷デバイスにも適用できる。また、本実施の形態は、n型TFTについて説明しているが、以下の説明において、n型TFTの代わりにp型TFTを用い、有機EL素子のアノード端子をカソード端子とすれば、同様に適用できる。

【0037】

本実施の形態の発光表示デバイスは、画素に、供給される電流により輝度が決まる有機EL素子と、この有機EL素子に一定の電流を供給する駆動回路とを少なくとも備える。

【0038】

有機EL素子は、前述のようにOLEDとも呼ばれ、高輝度発光が可能な面状の自発光が得られるものである。この有機EL素子は、アノード電極及びカソード電極間に発光層となる有機層をその機能に応じて積層し、その有機層の機能積層数を増やすことにより、低電圧で高効率な発光を可能としている。有機EL素子の基本となる素子構成は、アノード電極及びカソード電極間に有機層から成るEL発光層及び正孔輸送層を備え、アノード電極/正孔輸送層/EL発光層/カソード電極の積層構造から成る。このような発光素子として有機EL素子を用いた発光表示デバイスでは、発光層内への正孔と電子の注入により発光輝度が制御される。なお、有機EL素子については、公知事項であるため、その詳細については省略する。

【0039】

本実施の形態に係る発光表示デバイスを図1及び図2を用いて説明する。

【0040】

本実施の形態に係る発光表示デバイスは、画素内に、発光素子と、その発光素子を駆動するための駆動回路101とを有する。駆動回路101は、第一の薄膜トランジスタL-TFT、及び第二の薄膜トランジスタD-TFT、第一のスイッチTFT3、容量C、及び第一の配線GNDを有する。

【0041】

第一及び第二の薄膜トランジスタ(L-TFT、D-TFT)は、ゲート端子同士及びソース端子同士が各々接続されており、ソース端子は発光素子の一端(アノード端子)に接続されている。ここで、第一及び第二の薄膜トランジスタ(L-TFT、D-TFT)は同一極性である。

【0042】

更に、第一のスイッチTFT3は、一端が前記第一及び第二の薄膜トランジスタ(L-TFT、D-TFT)のソース端子及び発光素子の一端(アノード端子)に接続され、他端が第一の配線GNDに接続される。

10

20

30

40

50

## 【0043】

更に、容量Cは、一端が第一及び第二の薄膜トランジスタ(L-TFT、D-TFT)のゲート端子に接続され、他端が第一及び第二の薄膜トランジスタのソース端子に接続される。第二の配線DLは、発光素子の駆動信号を供給する。

## 【0044】

そして、本実施の形態に係る駆動回路は、駆動信号を書き込む第一の期間(図2のT1)と、第一の期間後、発光素子を駆動する第二の期間(図2のT2)とを少なくとも有する。

## 【0045】

第一の期間(T1)において、駆動回路は第一のスイッチTFT3を介して第一の配線と発光素子の一端(アノード端子)とを同一電圧にする。また、第一の期間(T1)において、駆動回路は、第二の配線DLと第一の薄膜トランジスタのドレイン端子及び第一及び第二の薄膜トランジスタのゲート端子とを電気的に接続し第二の配線から第一の薄膜トランジスタに電流を供給する。第一の期間(T1)は、上記動作を行う期間を含む。

10

## 【0046】

ここで、第二の配線と、第一の薄膜トランジスタのドレイン端子及び第一及び第二の薄膜トランジスタのゲート端子との接続には、図1のように第二のスイッチTFT4と第三のスイッチTFT5を用いてもよい。

## 【0047】

つまり、一端が第二の配線に接続され、他端がL-TFTのドレイン端子に接続される第二のスイッチTFT4と、一端がL-TFTのドレイン端子に接続され、他端がL-TFTのゲート端子に接続される第三のスイッチTFT5を用いてもよい。

20

## 【0048】

またこの場合、第三のスイッチTFT5のドレイン端子を、第二の配線DLと直接接続する構成としてもよい。

## 【0049】

第二の期間(T2)は、第二の配線と第一の薄膜トランジスタとの接続、第二の配線と第二の薄膜トランジスタとの接続、並びに第一のスイッチを遮断する期間を含む。

## 【0050】

上記第一の期間及び第二の期間の動作により、駆動回路は以下のようない動作をする。

30

## 【0051】

第一の期間(T1)に、駆動回路は、第一のスイッチTFT3を介して第一の配線と発光素子の一端とを同一電圧にする。更に、駆動回路は第二の配線DLからの電流を第一の薄膜トランジスタのドレイン端子及び第一及び第二の薄膜トランジスタのゲート端子に供給する。これにより、第一の薄膜トランジスタのドレイン端子-ソース端子に流れる電流で決まる第二の薄膜トランジスタのゲート端子-ソース端子間の電圧を容量Cに保持することができる。

## 【0052】

また、第二の期間(T2)に、駆動回路は、容量の保持電圧に従い第二の薄膜トランジスタのソース端子-ドレイン端子間を流れる電流を発光素子に供給する。この場合、容量の保持電圧は、VaとVbの電位差である。また、発光素子に供給する電流は、電源線VSから供給される。

40

## 【0053】

より好ましくは、本実施の形態の発光表示デバイスは、L-TFTのチャネル幅をチャネル長で割った値(W/L)が、D-TFTのW/Lと同じ、あるいは、L-TFTのW/LがD-TFTのW/Lより大きい。これにより、カレントミラー回路を構成する一対のL-TFT及びD-TFTのサイズ比を規定することができる。

## 【0054】

より好ましくは、本実施の形態の発光表示デバイスは、容量の容量値は、L-TFTのチャネル容量と、ゲート-ドレインオーバーラップ容量と、D-TFTのチャネル容量と

50

、ゲート - ドレインオーバーラップ容量とを加えた全容量値の 3 倍以上である。これにより、容量のサイズを規定することができる。

【 0 0 5 5 】

より好ましくは、本実施の形態の発光表示デバイスは、第一の配線の電圧が、有機 E L 素子の動作電圧以下である。これにより、電流書き込み時の有機 E L 素子への駆動電流をシャットアウトすることができる。

【 0 0 5 6 】

より好ましくは、本実施の形態の発光表示デバイスは、少なくとも第一から第三のスイッチが導通する期間 ( O N 期間 : 第一の期間 ) において、D - T F T のソースとドレイン間に電流を流さない駆動回路を備える。これにより、電流書き込み時の有機 E L 素子への駆動電流をシャットアウトすることができる。

10

【 0 0 5 7 】

より好ましくは、本実施の形態の発光表示デバイスは、D - T F T のソースとドレイン間に電流を流さない駆動回路として、第一から第三のスイッチが O N である期間において、D - T F T のドレイン端子電圧を、第一の配線の電圧と同電位とする回路を備える。これにより、電源電圧変動による有機 E L 素子への駆動電流をシャットアウトする。あるいは、D - T F T のドレイン端子と、第四の配線との間に第四のスイッチを備え、第四のスイッチは、少なくとも、第一から第三のスイッチが O N である期間、遮断、すなわち O F F する駆動回路 ( 電流遮断器 ) を備える。この第四のスイッチにより、有機 E L 素子への駆動電流をシャットアウトすることができる。

20

【 0 0 5 8 】

より好ましくは、本実施の形態の発光表示デバイスは、第一から第三のスイッチが遮断する期間 ( O F F 期間 : 第二の期間 ) の少なくとも一部において、D - T F T のソースとドレイン間に電流を流さない期間 ( 第三の期間 ) を設ける駆動回路を備える。この駆動回路は、電源電圧の変動、あるいは、第四のスイッチを用いたものであることを特徴とする。これにより、第三の期間における有機 E L 素子への駆動電流をシャットアウトすることができる。

30

【 0 0 5 9 】

より好ましくは、本実施の形態の発光表示デバイスは、第一から第三のスイッチが、L - T F T 、 D - T F T と同一構造の n 型 T F T ( 以下では第三から第五の n 型 T F T とする ) で構成される。第三から第五の n 型 T F T は、ソース端子あるいはドレイン端子の一端がスイッチの一端として機能し、ソース端子あるいはドレイン端子の他端がスイッチの他端として機能する。これにより、第一から第三のスイッチを L - T F T 及び D - T F T と同一構造の T F T で構成することができる。

【 0 0 6 0 】

より好ましくは、本実施の形態の発光表示デバイスは、第三から第五の n 型 T F T のゲート端子が、第三の配線と接続していることを特徴とする。これにより、スイッチを構成する T F T を共通制御することができる。

30

【 0 0 6 1 】

より好ましくは、本実施の形態の発光表示デバイスは、第四のスイッチが、L - T F T 、 D - T F T 、第三から第五の n 型 T F T と同一構造の n 型 T F T ( 以下では第六の n 型 T F T とする ) で構成される。第六の n 型 T F T は、ソース端子あるいはドレイン端子の一端がスイッチの一端として機能し、ソース端子あるいはドレイン端子の他端がスイッチの他端として機能する。これにより、第四のスイッチを L - T F T 、 D - T F T 、第一から第三のスイッチと同一構造の T F T で構成する。

40

【 0 0 6 2 】

より好ましくは、本実施の形態の発光表示デバイスは、駆動回路を構成する T F T が、キャリア密度が 1 0 1 8 [ c m - 3 ] 以下であるアモルファス金属酸化物 n 型半導体膜を n 型 T F T のチャネル膜として用い構成される。当該膜は移動度が 1 [ c m 2 / V s ] 以上、かつ、オンオフ比が 1 0 6 以上である。これにより、駆動回路を構成する T F T とし

50

て、酸化物半導体をチャネル膜として用いたTFTを用いることができる。

【0063】

より好ましくは、本実施の形態の発光表示デバイスは、駆動回路が、前記いずれかの駆動回路であって、基板上にマトリックス状に複数配置されている。

【0064】

本実施の形態の駆動回路によれば、外部から電流が供給されカレントミラー回路を構成する一対のn型TFT (L-TFTとD-TFT) に流す電流を設定する期間では、有機EL素子のカソード端子とアノード端子間の電圧が動作電圧以下となり電流が流れない。さらに、外部から供給される電流が流れるゲート端子 - ソース端子間電圧がL-TFTとD-TFTで保持される。従って、D-TFTは、飽和領域で動作する限り、定電流源として機能する。しかも、容量は、オーバーラップ容量などの寄生容量に比べ十分大きいため、ソース端子、ドレイン端子等の電圧が変動しても、寄生容量の効果を無視できる。

10

【0065】

また、本実施の形態によれば、有機EL素子に電流を供給する期間では、L-TFTのドレイン端子とソース端子は、D-TFTのソース端子と同電圧となり、L-TFTとD-TFTのゲート端子とソース端子間は同電圧となる。従って、印加電圧による特性変化を、L-TFTとD-TFTで同程度にすることができる。

【0066】

また、本実施の形態によれば、L-TFTの電流能力をD-TFTの電流能力よりも大きくすることで、外部よりL-TFTに供給する電流を、D-TFTが有機EL素子に供給する電流よりも大きくすることができます。従って、大型・高精細のディスプレイにも適用可能となる。さらに、本実施の形態によれば、前記の通り、電流を設定する期間において、有機EL素子には電流を流さないため、外部より供給する電流が大きくても、大きな電流が有機EL素子に流れる事が無い。このため、電流設定期間における、大電流による有機EL素子の劣化を抑えられ、電流設定時に必要な電圧を高くする必要が無い。

20

【0067】

また、本実施の形態によれば、外部から電流が供給し、カレントミラーナ型TFT (L-TFTとD-TFT) に流す電流を設定する期間において、D-TFTに流れる電流を停止することができる。さらに、本機能を、有機EL素子に電流を供給する、すなわち有機EL素子が発光する期間の前後、あるいは、その期間の前のみ、又はその期間の後のみに用いれば、D-TFTに電流を流さず、有機EL素子の発光を停止する期間を設けることができる。このように発光が停止する期間を設けると、発光が停止する期間を設けない場合と同じ時間平均輝度を実現するためには、有機EL素子に供給する電流を増加することになる。この場合、外部から供給する電流を増加することに相当し、従って、大型・高精細のディスプレイにも適用可能となる。しかも、発光を停止する期間を設けることで、CRT (Cathode Ray Tube) と動作が近くなり、残像が少ない高品質な動画表示が実現できる。

30

【0068】

また、本実施の形態によれば、n型TFTとして、キャリア密度が1018 [cm<sup>-3</sup>] 以下、かつ電界効果移動度が1 [cm<sup>2</sup>/Vs] 以上であるアモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、a-SiやOS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、高精細、大画面化が可能となる。

40

【0069】

以上説明したように、本実施の形態によれば、有機EL素子を用いた発光表示デバイスにおいて、駆動回路上に、下から、アノード電極、有機材料発光層、カソード電極という順に積層されている有機EL素子向けに駆動回路を提供することができる。この駆動回路は、a-Si、OS、金属酸化物半導体をチャネル層とするn型TFTにより構成することができる。また、印加電圧によるTFTの特性シフトによる影響を抑えることが可能な駆動回路を提供することができる。さらに、大型・高精細の発光表示デバイスに適用可能

50

な駆動回路を提供することができる。

【0070】

以下、有機EL素子を用いた発光表示デバイスの種々の実施例について説明するが、本発明は、有機EL素子に限定されるものではなく、他の電流負荷にも適用できる。さらに、以下では、アモルファス金属酸化物半導体をチャネル層としたn型TFTを用いるものとするが、a-Si TFTやOS TFTにも適用できる。さらに、他の半導体材料をチャネル層とする、n型TFTのみで構成される場合にも適用可能である。

【実施例1】

【0071】

まず、本発明の第一の実施例について説明する。

10

【0072】

本実施例の構成を図1に示す。同図に示す発光表示デバイスは、有機EL表示装置(AM型有機ELディスプレイ)の各画素において、カソード端子が接地線GNDに接続(接地)している有機EL素子LEDと、この有機EL素子LEDを駆動する駆動回路101とを備える。

【0073】

有機EL素子LEDは、下から、アノード電極、有機材料発光層、及びカソード電極という順に積層されている。

【0074】

駆動回路101は、第一のn型TFT(以下L-TFT)、第二のn型TFT(以下D-TFT)、第三のn型TFT(以下TFT3)、第四のn型TFT(以下TFT4)、第五のn型TFT(以下TFT5)、及び容量Cを有する。L-TFTとD-TFTは、カレントミラー回路を構成するn型TFT(n型カレントミラーティア)から構成され、TFT3、TFT4、及びTFT5は、スイッチ(スイッチング素子)を構成するn型TFT(n型スイッチングティア)から構成される。

20

【0075】

この駆動回路101には、画素の表示階調に相当する電流をL-TFTに供給するデータ線DLと、TFT3、TFT4、TFT5の各ゲート端子に接続される走査線SLと、電源線VSと、接地線GNDとの各配線が配置されている。接地線GNDは、本発明の第一の配線、データ線DLは本発明の第二の配線、電源線VSは本発明の第三の配線、走査線SLは本発明の第四の配線にそれぞれ対応する。

30

【0076】

L-TFTは、ソース端子が有機EL素子LEDのアノード端子に接続され、ゲート端子が容量Cの一端に接続されている。L-TFTは、本発明のカレントミラー回路を構成する第一の薄膜トランジスタに対応する。

【0077】

D-TFTは、ソース端子が有機EL素子LEDのアノード端子に接続され、ゲート端子が容量Cの一端に接続され、ドレイン端子が電源線VSに接続されている。D-TFTは、本発明のカレントミラー回路を構成する第二の薄膜トランジスタに対応する。

40

【0078】

TFT3は、ソース/ドレイン端子の一端が有機EL素子LEDのアノード端子に接続され、ソース/ドレイン端子の他端が接地線GNDに接続(接地)されている。TFT3は、本発明の第一のスイッチに対応する。

【0079】

TFT4は、ソース端子/ドレイン端子の一端がデータ線DLに接続され、ソース端子/ドレイン端子の他端がL-TFTのドレイン端子に接続されている。TFT4は、本発明の第二のスイッチに対応する。

【0080】

TFT5は、ソース端子/ドレイン端子の一端がL-TFTのドレイン端子に接続され、ソース端子/ドレイン端子の他端がL-TFTのゲート端子と接続されている。TFT

50

5は、本発明の第三のスイッチに対応する。

【0081】

容量Cは、一端がL-TFTとD-TFTのゲート端子に接続され、他端がL-TFTとD-TFTのソース端子に接続されている。また、容量Cの他端は、有機EL素子LEDのアノード端子に接続されている。

【0082】

ここで、電源線VSの電圧は、後述する電流書き込み期間で書き込む電流が、D-TFTと有機EL素子LEDに流れた場合でも、D-TFTが飽和領域で動作する電圧VDとする。

【0083】

また、L-TFTの電流能力は、D-TFTの4倍であるとする。これは、L-TFTとD-TFTのチャネル長と同じとし、L-TFTのチャネル幅をD-TFTのチャネル幅の4倍とすることで実現できる。

【0084】

さらに、容量Cの容量値は、L-TFTやD-TFTに関するオーバーラップ容量などの寄生容量の総和に比べ、3倍以上とする。

【0085】

次に、図2に示すタイミングチャートを参照して、本実施例の動作を説明する。

【0086】

まず、走査線SLの信号をHレベルとする期間（電流書き込み期間：第一の期間）T1において、TFT3、TFT4、TFT5がONになる。本期間T1において、TFT3のONにより、L-TFT及びD-TFTのソース端子の電圧、有機EL素子LEDのアノード端子の電圧Vbは、TFT3を介して共に接地線GNDの電圧と同電位となる。一方、TFT4、TFT5のONにより、データ線DLから、有機EL素子LEDに供給したい電流の4倍の電流がTFT4を介してL-TFTのドレイン端子に供給される。これにより、ゲート端子の電圧Vaは、L-TFTのドレイン端子-ソース端子間に有機EL素子LEDに供給したい電流の4倍の電流が流れるような電圧に設定される。同時に、D-TFTのドレイン端子-ソース端子間には、データ線DLからの電流の1/4、つまり、有機EL素子LEDに供給したい電流が流れる。一方、有機EL素子LEDのアノード端子の電圧Vbが接地線GNDの電圧と同電位であるため、D-TFTに流れる電流は、有機EL素子LEDに流れず、全てTFT3を介して接地線GNDに向け流れる。

【0087】

次に、走査線SLの信号をLレベルとする期間（LED駆動期間＝発光期間に相当：第二の期間）T2において、TFT3、TFT4、TFT5がOFFになる。本期間T2において、容量Cにより、D-TFTのゲート端子-ソース端子間の電圧差は、電流書き込み期間T1に設定された電圧差となる。つまり、D-TFTは、飽和動作を行う限り、D-TFTから有機EL素子LEDに向けて電流書き込み期間T1に設定された電流を供給する電流源となる。従って、D-TFTのソース端子電圧は、電流書き込み期間T1に設定された電流を有機EL素子LEDに流すようなアノード端子電圧となる。そして、D-TFTのゲート端子電圧は、有機EL素子LEDのアノード端子電圧に電流書き込み期間T1に設定されるゲート端子-ソース端子間の電圧差を加えた電圧となる。その結果、有機EL素子LEDは供給された電流に従って発光する。

【0088】

一方、L-TFTのゲート端子は、D-TFTのゲート端子と同一電圧であるので、L-TFTのソース端子、ドレイン端子の電圧は、D-TFTのソース端子と同電圧となる。

【0089】

以後、有機ELディスプレイでは、各ラインに上記動作を繰り返すことで、ディスプレイの表示を行う。

【0090】

10

20

30

40

50

従って、本実施例によれば、データ線からL-TFTに電流を供給する電流書き込み期間では、有機EL素子LEDのカソード端子とアノード端子が同電圧となり、電流が流れない。さらに、データ線から供給される電流が流れるゲート端子・ソース端子間電圧がL-TFTとD-TFTで容量Cにより保持される。LED駆動期間になつても、D-TFTは、飽和領域で動作する限り、定電流源として機能する。しかも、容量Cは、L-TFTやD-TFTに関するオーバーラップ容量などの寄生容量の総和に比べ十分大きいため、ソース端子、ドレイン端子等の電圧が変動しても、寄生容量の効果を無視できる。

#### 【0091】

また、本実施例によれば、LED駆動期間では、L-TFTのドレイン端子とソース端子は、D-TFTのソース端子と同電圧となり、L-TFTとD-TFTのゲート端子とソース端子間は同電圧となる。従って、印加電圧による特性変化を、L-TFTとD-TFTで同程度にすることができる。このため、L-TFTとD-TFTの電流能力比の変化が現れず、データ線から電流を書き込む限り、L-TFTとD-TFTの特性変化の影響を抑えることができる。

10

#### 【0092】

また、本実施例によれば、L-TFTの電流能力をD-TFTの電流能力よりも大きくすることで、データ線よりL-TFTに供給する電流を、D-TFTが有機EL素子LEDに供給する電流よりも大きくすることができます。従って、電流書き込み期間が短縮でき、大型・高精細のディスプレイにも適用可能となる。

20

#### 【0093】

また、本実施例によれば、電流書き込み期間において、有機EL素子には電流を流さないため、上記のように、外部より供給する電流が大きくても、大きな電流が有機EL素子に流れる事が無い。この場合、有機EL素子の劣化を抑えることができ、かつ、有機EL素子のアノード端子電圧上昇を補償するためにデータ線の電圧を高くする必要が無い。

30

#### 【0094】

さらに、本実施例によれば、L-TFT、D-TFTとして、キャリア密度が1018 [cm<sup>-3</sup>]以下、かつ電界効果移動度が1 [cm<sup>2</sup>/Vs]以上であるアモルファス金属酸化物半導体層をチャネル層としたn型TFTを用いる。これにより、a-SiやOS-TFTで構成した場合よりも、消費電力が少なく、室温形成が可能なTFTにより発光表示デバイスが作成できる。さらに、移動度が高いため、高精細、大画面化が可能となる。

30

#### 【実施例2】

#### 【0095】

次に、本発明の第二の実施例について説明する。本実施例に係る発光表示デバイスの素子構成は、第一の実施例と同一である。ただし、本実施例は、電源線VSの電圧を変動することを特徴としている。

#### 【0096】

以下、図3に示すタイミングチャートを参照して、本実施例の動作を説明する。

#### 【0097】

まず、走査線SLの信号をHレベル、電源線VSの電圧を接地線GNDの電圧と同電位（以下GND）とする期間（電流書き込み期間）T11において、TFT3、TFT4、TFT5がONになる。本期間T11では、TFT3のONにより、L-TFT、D-TFTのソース端子の電圧、有機EL素子LEDのアノード端子の電圧Vbは、共にTFT3を介して接地線GNDの電圧と同電位となる。一方、TFT4、TFT5のONにより、データ線DLから、有機EL素子LEDに供給したい電流の16倍の電流がL-TFTのドレイン端子に供給される。これにより、ゲート端子の電圧Vaは、L-TFTのドレイン端子・ソース端子間に有機EL素子LEDに供給したい電流の16倍の電流が流れるような電圧に設定される。一方、電源線VSの電圧がGNDであるため、D-TFTのドレイン端子・ソース端子間に電流が流れない。また、有機EL素子LEDのアノード端子の電圧Vbが接地線GNDの電圧と同電位であるため、有機EL素子LEDにも電流が流れない。

40

50

## 【0098】

引き続き、走査線 S-L の信号を L レベル、電源線 V-S の電圧を V-D とする期間 (LED 駆動期間 = 発光期間に相当) T-2-1 を設ける。ただし、本期間 T-2-1 を第一の実施例の LED 駆動期間 T-2 の 1/4 とする。本期間 T-2-1 において、TFT-3、TFT-4、TFT-5 が OFF になる。さらに、容量 C により、D-TFT のゲート端子 - ソース端子間の電圧差は、電流書き込み期間 T-1-1 に設定された電圧差となる。つまり、D-TFT は、飽和動作を行う限り、D-TFT から有機 EL 素子 LED に向けて電流書き込み期間 T-1-1 に設定された電流、すなわち有機 EL 素子 LED に供給したい電流の 4 倍を供給する電流源となる。従って、D-TFT のソース端子電圧は、電流書き込み期間 T-1-1 に設定された電流を有機 EL 素子 LED に流すようなアノード端子電圧となる。そして、D-TFT のゲート端子電圧は、有機 EL 素子 LED のアノード端子電圧に電流書き込み期間 T-1-1 に設定されるゲート端子 - ソース端子間の電圧差を加えた電圧となる。その結果、有機 EL 素子 LED は供給された電流に従って発光する。

10

## 【0099】

さらに、走査線 S-L の信号を L レベル、電源線 V-S の電圧を GND とする期間 (黒表示期間) T-2-2 を設ける。本期間 T-2-2 において、D-TFT から電流が流れず、有機 EL 素子 LED は発光しない。

20

## 【0100】

以後、有機 EL ディスプレイでは、各ラインに上記動作を繰り返すことで、ディスプレイの表示を行う。

## 【0101】

従って、本実施例は、第一の実施例と同じ効果が得られる。また、本実施例において、黒表示期間を設け、LED 駆動期間を第一の実施例の 1/4 とし、かつ、有機 EL 素子 LED に流れる電流を 4 倍としている。これにより、時間平均の輝度が、第一の実施例とほぼ同一とすることができる。その一方、データ線から供給される電流は、第一の実施例の 4 倍となるため、電流書き込み期間がより短縮でき、第一の実施例よりもさらに大型・高精細のディスプレイにも適用可能となる。

## 【実施例 3】

## 【0102】

次に、本発明の第三の実施例について説明する。

30

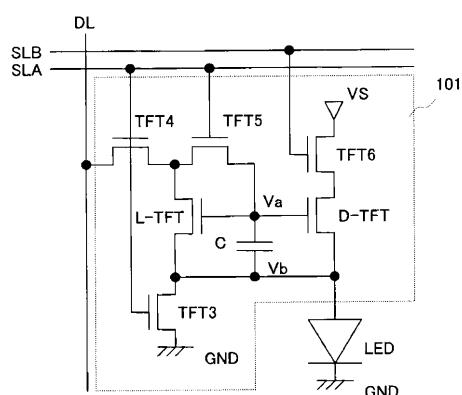

## 【0103】

本実施例の構成を図 4 に示す。同図に示す発光表示デバイスは、有機 EL 表示装置 (AM 型有機 EL ディスプレイ) の各画素において、カソード端子が接地線 GND に接続 (接地) している有機 EL 素子 LED と、この有機 EL 素子 LED を駆動する駆動回路 101 とを備える。

## 【0104】

有機 EL 素子 LED は、下から、アノード電極、有機材料発光層、及びカソード電極という順に積層されている。

## 【0105】

駆動回路 101 は、第一の n 型 TFT (以下 L-TFT)、第二の n 型 TFT (以下 D-TFT)、第三の n 型 TFT (以下 TFT-3)、第四の n 型 TFT (以下 TFT-4)、第五の n 型 TFT (以下 TFT-5) を有する。更に、駆動回路 101 は第六の n 型 TFT (第六の薄膜トランジスタ、以下 TFT-6)、及び容量 C を有する。L-TFT と D-TFT は、カレントミラー回路を構成する n 型 TFT (n 型カレントミラーティFT) から構成され、TFT-3、TFT-4、TFT-5、及び TFT-6 は、スイッチング素子 (スイッチ) を構成する n 型 TFT (n 型スイッチング TFT) から構成される。

40

## 【0106】

この駆動回路 101 には、画素の表示階調に相当する電流を L-TFT に供給するデータ線 DL と、TFT-3、TFT-4、TFT-5 の各ゲート端子に接続する第一の走査線 S-L-A が配置されている。更に、この駆動回路 101 には、TFT-6 のゲート端子に接続する

50

第二の走査線 S L B と、電源線 V S と、接地線 G N D との各配線が配置されている。接地線 G N D は、本発明の第一の配線、データ線 D L は本発明の第二の配線、電源線 V S は本発明の第三の配線、第一の走査線 S L A 及び第二の走査線 S L B は本発明の第四の配線にそれぞれ対応する。

【 0 1 0 7 】

L - T F T は、ソース端子が有機 E L 素子 L E D のアノード端子に接続され、ゲート端子が容量 C の一端に接続されている。L - T F T は、本発明のカレントミラー回路を構成する第一の薄膜トランジスタに対応する。

【 0 1 0 8 】

D - T F T は、ソース端子が有機 E L 素子 L E D のアノード端子に接続され、ゲート端子が容量 C 1 の一端に接続されている。D - T F T は、本発明のカレントミラー回路を構成する第二の薄膜トランジスタに対応する。

【 0 1 0 9 】

T F T 3 は、ソース端子 / ドレイン端子の一端が有機 E L 素子 L E D のアノード端子に接続され、ソース / ドレイン端子の他端が接地線 G N D に接続（接地）されている。T F T 3 は、本発明の第一のスイッチに対応する。

【 0 1 1 0 】

T F T 4 は、ソース端子 / ドレイン端子の一端がデータ線 D L に接続され、ソース端子 / ドレイン端子の他端が L - T F T のドレイン端子に接続されている。T F T 4 は、本発明の第二のスイッチに対応する。

【 0 1 1 1 】

T F T 5 は、ソース端子 / ドレイン端子の一端が L - T F T のドレイン端子に接続され、ソース端子 / ドレイン端子の他端が前記 L - T F T のゲート端子に接続されている。T F T 5 は、本発明の第三のスイッチに対応する。

【 0 1 1 2 】

T F T 6 は、ソース端子 / ドレイン端子の一端が D - T F T のドレイン端子に接続され、ソース端子 / ドレイン端子の他端が電源線 V S に接続されている。T F T 6 は、本発明の第四のスイッチに対応する。

【 0 1 1 3 】

容量 C は、一端が L - T F T と D - T F T のゲート端子に接続され、他端が L - T F T と D - T F T のソース端子に接続されている。また、容量 C の他端は、有機 E L 素子 L E D のアノード端子に接続されている。

【 0 1 1 4 】

ここで、電源線 V S の電圧は、後述する電流書き込み期間で書き込む電流が、D - T F T と有機 E L 素子 L E D に流れた場合でも、D - T F T が飽和領域で動作する電圧 V D とする。

【 0 1 1 5 】

また、L - T F T の電流能力は、D - T F T の 4 倍であるとする。これは、L - T F T と D - T F T のチャネル長を同じとし、L - T F T のチャネル幅を D - T F T のチャネル幅の 4 倍とすることで実現できる。

【 0 1 1 6 】

さらに、容量 C の容量値は、L - T F T や D - T F T に関するオーバーラップ容量などの寄生容量の総和に比べ、3 倍以上とする。

【 0 1 1 7 】

次に、図 5 に示すタイミングチャートを参照して、本実施例の動作を説明する。

【 0 1 1 8 】

まず、第一の走査線 S L A の信号を H レベル、第二の走査線 S L B の信号を L レベルとする期間（電流書き込み期間）T 1 1 において、T F T 3、T F T 4、T F T 5 が ON、T F T 6 が OFF になる。本期間 T 1 1 において、T F T 3 の ON により、L - T F T、D - T F T のソース端子の電圧、有機 E L 素子 L E D のアノード端子の電圧 V b は、共に

10

20

30

40

50

接地線 GND の電圧と同電位となる。一方、TFT4、TFT5 の ON により、データ線 DL から、有機 EL 素子 LED に供給したい電流の 16 倍の電流が L-TFT のドレイン端子に供給される。これにより、ゲート端子の電圧 Va は、L-TFT のドレイン端子 - ソース端子間に有機 EL 素子 LED に供給したい電流の 4 倍の電流が流れるような電圧に設定される。一方、D-TFT のドレイン端子 - ソース端子間には、TFT6 が OFF であるため、電源線 VS との間の電流経路が遮断され、電流が流れない。また、有機 EL 素子 LED のアノード端子の電圧が接地線 GND の電圧と同電位であるため、有機 EL 素子 LED に流れない。

#### 【0119】

次に、第一の走査線 SLA の信号を L レベル、第二の走査線 SLB の信号を H レベルとする期間 (LED 駆動期間 = 発光期間に相当) T21 を設ける。ただし、本期間 T21 を第一の実施例の LED 駆動期間 T2 の 1/4 とする。本期間 T21 において、TFT3、TFT4、TFT5 が OFF、TFT6 が ON になる。さらに、容量 C により、D-TFT のゲート端子 - ソース端子間の電圧差は、電流書き込み期間 T11 に設定された電圧差となる。つまり、D-TFT は、飽和動作を行う限り、D-TFT から有機 EL 素子 LED に向けて電流書き込み期間 T11 に設定された電流、すなわち有機 EL 素子 LED に供給したい電流の 4 倍を供給する電流源となる。従って、D-TFT のソース端子電圧は、電流書き込み期間 T11 に設定された電流を有機 EL 素子 LED に流すようなアノード端子電圧となる。そして、D-TFT のゲート端子電圧は、有機 EL 素子 LED のアノード端子電圧に電流書き込み期間 T11 に設定されるゲート端子 - ソース端子間の電圧差を加えた電圧となる。その結果、有機 EL 素子 LED は供給された電流に従って発光する。

10

20

30

40

#### 【0120】

さらに、第一の走査線 SLA の信号を L レベル、第二の走査線 SLB の信号を L レベルとする期間 (黒表示期間) T22 を設ける。本期間 T22 において、TFT6 が OFF となり、電源線 VS と D-TFT のドレイン端子間の電流経路が遮断されるため、D-TFT から電流が流れず、有機 EL 素子 LED は発光しない。

#### 【0121】

以後、有機 EL ディスプレイでは、各ラインに上記動作を繰り返すことで、ディスプレイの表示を行う。

#### 【0122】

本実施例は、信号線 SLB と、TFT6 を追加することで、電源 VS を変動することなく、第二の実施例の効果を実現できる。

#### 【0123】

なお、第一の実施例から第三の実施例において、L-TFT と D-TFT の電流能力比を 4 倍としたが、L-TFT と D-TFT の電流能力の比は、有機 EL 素子 LED の電流 - 輝度特性と、データ線 DL の負荷容量に従って、設定することが可能である。

#### 【0124】

また、第二の実施例、並びに、第三の実施例において、LED 駆動期間を、第一の実施例の LED 駆動期間の 1/4 としたが、第一の実施例の LED 駆動期間より短くすることで、程度の差こそあるが、同様の効果が得られる。

#### 【0125】

また、第一の実施例から第三の実施例において、有機 EL 素子 LED は、カソード端子が接地しており、TFT は全て n 型 TFT (n 型薄膜トランジスタ) で構成されている。p 型 TFT (p 型薄膜トランジスタ) のみで構成する場合には、次のように構成してもよい。

#### 【0126】

有機 EL 素子 LED のアノード端子を電源配線 VS に接続し、p 型カレントミラーティア TFT (第一及び第二の p 型薄膜トランジスタ、L-TFT、D-TFT) のソース端子と有機 EL 素子 LED のカソード端子を接続する。L-TFT、D-TFT のソース端子と電源配線 VS の間に p 型 TFT (TFT3) を設ける。L-TFT のドレイン端子と階調に

50

相当する電流を供給する配線 D L 間に p 型 TFT ( TFT4 ) 、 L - TFT のドレイン端子 - ゲート端子間に p 型 TFT ( TFT5 ) を設ける。 D - TFT のドレイン端子を、 G ND が印加されている電源線に接続する。あるいは、 D - TFT のドレイン端子を、 LED 駆動期間は G ND を印加し、それ以外の期間は VS を印加することのできる電源線に接続する。あるいは、 D - TFT のドレイン端子を、 p 型 TFT ( TFT6 ) を経由して G ND が印加されている電源線に接続する。そして、走査線 S L 、 S LA 、 S LB の信号を反転する。こうすることで、第一の実施例から第三の実施例と同様な構成が実現でき、同様な効果を得ることが可能である。

## 【 0127 】

また、第一の実施例から第三の実施例において、走査線を追加することにより、第一の期間の終了時に、スイッチ機能を果たす TFT の内、 TFT5 を最も早く ON から OFF に動作させる。こうすることで、他のスイッチ機能を果たす TFT の動作に伴うノイズを抑え、精度の高い駆動が可能である。

10

## 【 産業上の利用可能性 】

## 【 0128 】

本発明は、有機 EL 素子を用いた発光表示デバイスのほか、有機 EL 素子以外の供給される電流により発光する発光素子を用いた発光表示デバイスや、供給される電流により任意の機能を示す一般的な電流負荷を用いる電流負荷デバイスにも適用できる。

## 【 符号の説明 】

## 【 0129 】

20

100 有機 EL 表示装置

101 駆動回路

LED 有機 EL 素子

L - TFT 、 D - TFT カレントミラー回路を構成する n 型 TFT

TFT3 ~ TFT6 スイッチング素子 ( スイッチ ) を構成する n 型 TFT

VS 電源線

S L 走査線

D L データ線

S L ( 1 ) ~ S L ( m ) 1 ~ m 番目の各行の走査線

D L ( 1 ) ~ D L ( n ) 1 ~ n 番目の各列のデータ線

30

C 容量

SW1 ~ SW3 スイッチング素子

【図1】

【図2】

T1; 電流書き込み期間

T2; LED駆動(発光)期間

【図3】

T11; 電流書き込み期間

T21; LED駆動(発光)期間

T22; 黒表示期間

【図4】

【図6】

【図5】

T11; 電流書き込み期間

T21; LED駆動(発光)期間

T22; 黒表示期間

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

F ターム(参考) 5C380 AA01 AB06 AB22 AC04 BA01 BA28 BA36 BA39 BB01 BB21

BD01 BE03 CC14 CC27 CC33 CC39 CC41 CC62 CC63 CD012

CD014 CD015 CD016 DA02 DA42 HA03

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发光显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2013225140A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2013-10-31 |

| 申请号            | JP2013117384                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2013-06-03 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 安部勝美                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 安部 勝美                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3241 G09G3/2011 G09G2300/0417 G09G2300/0842 G09G2300/0861 G09G2300/0866 G09G2310/0251 G09G2310/061 G09G2320/0223 G09G2320/0233 G09G2320/0238 G09G2330/025                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.670.J G09G3/20.611.H G09G3/20.611.A H05B33/14.A G09G3/3241                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC21 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/CC06 5C080/DD02 5C080/DD05 5C080/DD26 5C080/DD27 5C080/DD29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AC04 5C380/BA01 5C380/BA28 5C380/BA36 5C380/BA39 5C380/BB01 5C380/BB21 5C380/BD01 5C380/BE03 5C380/CC14 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC62 5C380/CC63 5C380/CD012 5C380/CD014 5C380/CD015 5C380/CD016 5C380/DA02 5C380/DA42 5C380/HA03 |         |            |

| 代理人(译)         | 佐藤安倍晋三<br>黒岩Soware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 优先权            | 2006240257 2006-09-05 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

要解决的问题：抑制由于施加的电压引起的薄膜晶体管的特性偏移的影响，其可以应用于大尺寸，高清晰度的发光显示装置，并且使用发光显示器提供设备。解决方案：发光显示装置在像素中具有有机EL元件LED，以及用于驱动该有机EL元件LED的驱动电路101。驱动电路101在电流写入时段中同时导通TFT 3至5，并且经由TFT 3使地线GND和LED的一端具有相同的电压。然后，来自数据线DL的电流通过TFT 4和5提供给构成电流镜电路的L-TFT和D-TFT，并保持在电容C中作为L-TFT和D-TFT的栅-源电压。到。此外，在LED驱动期间，TFT 3至5同时关闭，并且D-TFT的源极和漏极之间的电流根据电容器C的保持电压提供给LED。[选图]图1