(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-34039

(P2011-34039A)

(43) 公開日 平成23年2月17日(2011.2.17)

| (51) Int.CI.                | F 1            | テーマコード (参考) |

|-----------------------------|----------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J    | 3K107       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 660X | 5C080       |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 622Q | 5C380       |

|                             | G09G 3/20 622D |             |

|                             | G09G 3/20 621F |             |

審査請求 有 請求項の数 28 O L (全 39 頁) 最終頁に続く

|              |                              |          |                                                                                                                                                                    |

|--------------|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2009-254936 (P2009-254936) | (71) 出願人 | 308040351                                                                                                                                                          |

| (22) 出願日     | 平成21年11月6日 (2009.11.6)       |          | 三星モバイルディスプレイ株式會社                                                                                                                                                   |

| (31) 優先権主張番号 | 10-2009-0071280              |          | 大韓民国京畿道龍仁市器興区農書洞山24                                                                                                                                                |

| (32) 優先日     | 平成21年8月3日 (2009.8.3)         | (74) 代理人 | 110000671                                                                                                                                                          |

| (33) 優先権主張国  | 韓国 (KR)                      |          | 八田國際特許業務法人                                                                                                                                                         |

|              |                              | (72) 発明者 | 李白雲<br>大韓民国京畿道龍仁市器興区農書洞山24                                                                                                                                         |

|              |                              |          | F ターム (参考) 3K107 AA01 BB01 CC31 CC33 EE04<br>HH04 HH05<br>5C080 AA06 BB05 DD01 DD05 DD08<br>DD10 DD22 DD23 DD26 DD27<br>EE29 FF11 FF12 JJ02 JJ03<br>JJ04 JJ05 JJ06 |

最終頁に続く

(54) 【発明の名称】有機電界発光表示装置及びその駆動方法

## (57) 【要約】

【課題】本発明は、同時発光方式で駆動される有機電界発光表示装置及びその駆動方法に関する。

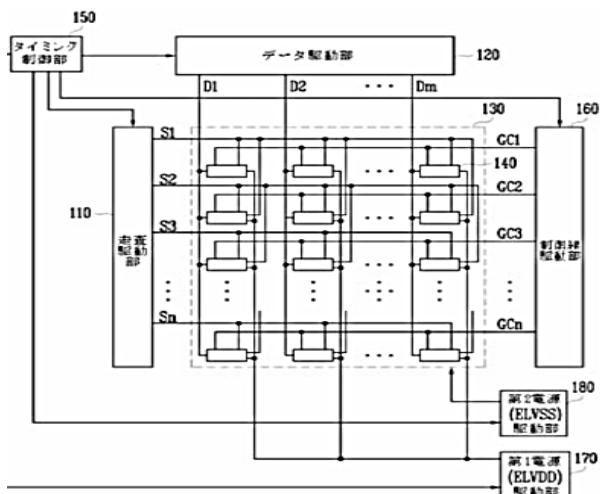

【解決手段】本発明の実施例による有機電界発光表示装置は、走査線、制御線、及びデータ線に接続された画素を備える画素部130と、前記制御線を介して各画素に制御信号を提供する制御線駆動部160と、前記画素部の各画素に第1電源電圧を印加する第1電源駆動部170と、前記画素部の各画素に第2電源電圧を印加する第2電源駆動部180とが備えられ、前記第1及び第2電源駆動部のうちの少なくとも一方は、1フレーム期間中においてレベルが変化する電圧を前記画素部の各画素に印加し、前記制御線駆動部及び前記第1、第2電源駆動部は、前記画素部に備えられる画素全体に対して同時に一括して提供されることを特徴とする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

走査線、制御線、及びデータ線に接続された画素を備える画素部と、

前記制御線を介して各画素に制御信号を供給する制御線駆動部と、

前記画素部の各画素に第1電源電圧を印加する第1電源駆動部と、

前記画素部の各画素に第2電源電圧を印加する第2電源駆動部と、を備え、

前記第1及び第2電源駆動部のうちの少なくとも一方は、1フレーム期間中においてレベルが変化する電圧を前記画素部の各画素に印加し、

前記制御線駆動部及び前記第1及び第2電源駆動部は、前記画素部に備えられる画素全体に対して、前記制御信号及び前記第1及び第2電源電圧を同時に一括して供給することを特徴とする有機電界発光表示装置。

10

**【請求項 2】**

前記走査線を介して各画素に走査信号を供給する走査駆動部と、

前記データ線を介して各画素にデータ信号を供給するデータ駆動部と、

前記制御線駆動部、第1及び第2電源駆動部、走査駆動部、及びデータ駆動部を制御するタイミング制御部と、をさらに備えることを特徴とする請求項1に記載の有機電界発光表示装置。

20

**【請求項 3】**

前記第1電源駆動部は、1フレーム期間中においてレベルが3段階に変化する第1電源電圧を印加し、第2電源駆動部は、一定レベルの第2電源電圧を1フレーム期間全体にわたり印加することを特徴とする請求項1または2に記載の有機電界発光表示装置。

20

**【請求項 4】**

前記第1及び第2電源駆動部は、1フレーム期間中においてレベルが2段階に変化する電圧をそれぞれ印加することを特徴とする請求項1または2に記載の有機電界発光表示装置。

20

**【請求項 5】**

前記第1電源駆動部は、一定レベルの第1電源電圧を1フレーム期間全体にわたり印加し、前記第2電源駆動部は、1フレーム期間においてレベルが3段階に変化する電圧を印加することを特徴とする請求項1または2に記載の有機電界発光表示装置。

30

**【請求項 6】**

前記走査信号は、1フレーム期間の一部の期間について各走査線に順次印加され、前記一部の期間以外の期間では全走査線に対して同時に印加されることを特徴とする請求項2～5のいずれか1項に記載の有機電界発光表示装置。

30

**【請求項 7】**

前記順次印加される走査信号の幅は、2水平時間(2H)として印加され、これに隣接して印加される走査信号が互いに1水平時間(1H)だけ重畠するように印加されることを特徴とする請求項6に記載の有機電界発光表示装置。

40

**【請求項 8】**

前記データ信号は、前記順次印加された走査信号に対応して各走査線に接続された画素に順次印加され、前記一部の期間以外の期間では各データ線を介して全画素に同時に印加されることを特徴とする請求項6または7に記載の有機電界発光表示装置。

40

**【請求項 9】**

前記各画素は、

ゲート電極が前記走査線に接続され、第1電極が前記データ線に接続され、第2電極が第1ノードに接続された第1トランジスタと、

50

ゲート電極が第2ノードに接続され、第1電極が前記第1電源駆動部に接続され、第2電極が有機発光素子のアノード電極に接続された第2トランジスタと、

前記第1ノードと前記第2トランジスタの第1電極との間に接続された第1キャパシタと、

前記第1ノードと前記第2ノードとの間に接続された第2キャパシタと、

50

ゲート電極が前記制御線に接続され、第1電極は前記第2トランジスタのゲート電極に接続され、第2電極は前記第2トランジスタの第2電極に接続された第3トランジスタと、

アノード電極が前記第2トランジスタの第2電極に接続され、カソード電極が前記第2電源駆動部に接続された有機発光素子と、を備えて構成されることを特徴とする請求項1～8のいずれか1項に記載の有機電界発光表示装置。

**【請求項10】**

前記第1、第2、及び第3トランジスタは、PMOSで実現されることを特徴とする請求項9に記載の有機電界発光表示装置。

**【請求項11】**

前記第1電源電圧及び制御信号が、画素部に備えられた各画素にすべてハイレベルで印加されたとき、前記各画素は、各画素に予め格納されたデータ信号に対応する輝度で同時に発光することを特徴とする請求項9または10に記載の有機電界発光表示装置。

**【請求項12】**

前記各画素は、

ゲート電極が前記走査線に接続され、第1電極が前記データ線に接続され、第2電極が第1ノードに接続された第1トランジスタと、

ゲート電極が第2ノードに接続され、第1電極が前記第2電源駆動部に接続され、第2電極が有機発光素子のカソード電極に接続された第2トランジスタと、

前記第1ノードと前記第2トランジスタの第1電極との間に接続された第1キャパシタと、

前記第1ノードと前記第2ノードとの間に接続された第2キャパシタと、

ゲート電極が前記制御線に接続され、第1電極は前記第2トランジスタのゲート電極に接続され、第2電極は前記第2トランジスタの第2電極に接続された第3トランジスタと、

カソード電極が前記第2トランジスタの第2電極に接続され、アノード電極が前記第1電源駆動部に接続された有機発光素子と、を備えて構成されることを特徴とする請求項1～8のいずれか1項に記載の有機電界発光表示装置。

**【請求項13】**

前記第1、第2、及び第3トランジスタは、NMOSで実現されることを特徴とする請求項12に記載の有機電界発光表示装置。

**【請求項14】**

画素部を構成する画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、前記各画素に備えられた画素回路の各ノードの電圧を初期化する第1ステップと、

前記画素全体に対してそれぞれ既定レベルの電圧値を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、各画素に備えられた有機発光素子のアノード電極の電圧をカソード電極の電圧以下に低下させる第2ステップと、

前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、前記各画素に備えられた駆動トランジスタの閾値電圧を格納する第3ステップと、

前記画素部の各走査線に接続された各々の画素に対して走査信号が順次印加され、前記順次印加された走査信号に対応して各走査線に接続された画素にデータ信号が印加される第4ステップと、

前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号を一括して同時に印加し、前記各画素に格納されたデータ電圧に対応する輝度で各々の画素全体が同時に発光する第5ステップと、

前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号を一括して同時に印加し、前記各画素に備えられた有機発光素子のアノード電極の電圧を低下させて発光をオフする第6ステップと、を含むことを特徴とす

10

20

30

40

50

る有機電界発光表示装置の駆動方法。

**【請求項 1 5】**

前記第1～第6ステップによって1つのフレームが実現されることを特徴とする請求項14に記載の有機電界発光表示装置の駆動方法。

**【請求項 1 6】**

順次進行するフレームについて、n番目のフレームは、左眼用の画像を表示し、n+1番目のフレームは、右眼用の画像を表示することを特徴とする請求項15に記載の有機電界発光表示装置の駆動方法。

**【請求項 1 7】**

前記n番目のフレームの発光期間とn+1番目のフレームの発光期間との間の期間の全時間をシャッタ眼鏡の応答時間に同期させるように実現することを特徴とする請求項16に記載の有機電界発光表示装置の駆動方法。 10

**【請求項 1 8】**

前記各画素は、

ゲート電極が前記走査線に接続され、第1電極が前記データ線に接続され、第2電極が第1ノードに接続された第1PMOSトランジスタと、

ゲート電極が第2ノードに接続され、第1電極が第1電源に接続され、第2電極が有機発光素子のアノード電極に接続された第2PMOSトランジスタと、

前記第1ノードと前記第2トランジスタの第1電極との間に接続された第1キャパシタと、 20

前記第1ノードと前記第2ノードとの間に接続された第2キャパシタと、

ゲート電極が制御線に接続され、第1電極は前記第2トランジスタのゲート電極に接続され、第2電極は前記第2トランジスタの第2電極に接続された第3PMOSトランジスタと、

アノード電極が前記第2トランジスタの第2電極に接続され、カソード電極が第2電源に接続された有機発光素子と、を備えて構成されることを特徴とする請求項14～17のいずれか1項に記載の有機電界発光表示装置の駆動方法。

**【請求項 1 9】**

前記第1ステップでは、走査信号がローレベルで印加され、制御信号はハイレベルで印加され、第1電源電圧がハイレベルとローレベルとの間の中間レベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。 30

**【請求項 2 0】**

前記第2ステップは、第2\_1～第2\_3ステップに分けられ、

前記第2\_1ステップでは、前記第1電源電圧がローレベルで印加され、走査信号はハイレベルまたはローレベルで印加され、制御信号はハイレベルで印加され、

前記第2\_2ステップでは、前記第1電源電圧がローレベルで印加され、走査信号はハイレベルまたはローレベルで印加され、制御信号G C(t)はハイレベルで印加され、

前記第2\_3ステップでは、前記第1電源電圧が中間レベルで印加され、走査信号はハイレベルまたはローレベルで印加され、制御信号はハイレベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。 40

**【請求項 2 1】**

前記第2\_1ステップ及び第2\_2ステップで前記走査信号がローレベルで印加されると、これに対応するデータ信号はローレベルで印加されることを特徴とする請求項20に記載の有機電界発光表示装置の駆動方法。

**【請求項 2 2】**

前記第2\_3ステップで前記走査信号がローレベルで印加されると、これに対応するデータ信号はハイレベルで印加されることを特徴とする請求項20に記載の有機電界発光表示装置の駆動方法。

**【請求項 2 3】**

前記第3ステップは、第3\_1ステップ～第3\_3ステップに分けられ、 50

前記第3\_1ステップでは、前記第1電源電圧が中間レベルで印加され、走査信号はハイレベルまたはローレベルで印加され、制御信号はハイレベルで印加され、

前記第3\_2ステップ及び第3\_3ステップでは、前記第1電源電圧が中間レベルで印加され、走査信号はローレベルで印加され、制御信号G C ( t )はローレベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。

#### 【請求項24】

前記第3\_1ステップで前記走査信号がローレベルで印加されると、これに対応するデータ信号はハイレベルで印加されることを特徴とする請求項23に記載の有機電界発光表示装置の駆動方法。

#### 【請求項25】

前記第4ステップでは、制御信号がローレベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。

#### 【請求項26】

前記第4ステップで順次印加される走査信号の幅は2水平時間(2H)として印加され、これに隣接して印加される走査信号が互いに1水平時間(1H)だけ重畠するように印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。

#### 【請求項27】

前記第5ステップでは、前記第1電源電圧がハイレベルで印加され、走査信号及び制御信号はハイレベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。

#### 【請求項28】

前記第6ステップでは、前記第1電源電圧が中間レベルで印加され、走査信号及び制御信号はハイレベルで印加されることを特徴とする請求項18に記載の有機電界発光表示装置の駆動方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、有機電界発光表示装置に関し、特に、同時発光方式で駆動される有機電界発光表示装置及びその駆動方法に関する。

#### 【背景技術】

#### 【0002】

近年、陰極線管(CRT)の欠点である重量及び体積を減らすことが可能な各種平板表示装置が開発されている。平板表示装置には、液晶表示装置(LCD)、電界放出表示装置(Field Emission Display: FED)、プラズマ表示パネル(PDP)、及び有機電界発光表示装置(Organic Light Emitting Display: OLED)などがある。

#### 【0003】

平板表示装置のうち、有機電界発光表示装置は、電子と正孔との再結合により光を発生する有機発光ダイオードを用いて画像を表示するものであり、これは、速い応答速度を有し、かつ、低消費電力で駆動されるという利点がある。

#### 【0004】

通常、有機電界発光表示装置は、有機発光素子を駆動する方式によって、パッシブマトリクス型OLED(PMOLED)と、アクティブマトリクス型OLED(AMOLED)とに分類される。

#### 【0005】

前記AMOLEDは、複数のゲートライン、複数のデータライン、及び複数の電源ラインと、これらのラインに接続され、マトリクス状に配列された複数の画素とを備える。また、前記各画素は、通常、有機発光素子と、2つのトランジスタ、すなわち、データ信号を伝達するためのスイッチングトランジスタ及び前記データ信号に応じて前記有機発光素子を駆動させるための駆動トランジスタと、前記データ電圧を維持させるための1つのキ

10

20

30

40

50

ヤパシタとからなる。

#### 【0006】

このようなAMOLEDは、消費電力が少ないというメリットがあるが、有機発光素子を駆動する駆動トランジスタのゲートとソースとの間の電圧、すなわち、駆動トランジスタの閾値電圧のばらつきによって有機発光素子を介して流れる電流の強さが変化し、表示の不均一を招くという問題がある。

#### 【0007】

つまり、前記各画素内に備えられたトランジスタは、製造工程の条件によってトランジスタの特性が変化するため、AMOLEDのすべてのトランジスタの特性が同じになるようにトランジスタを製造することが困難であり、これにより、画素間の閾値電圧のばらつきが存在するからである。

10

#### 【0008】

そこで、最近では、このような問題を克服するために、複数のトランジスタ及びキャパシタを備える補償回路が研究されており、この補償回路を各々の画素内にさらに追加することによって克服している。しかし、この場合、各画素に多数のトランジスタ及びキャパシタが実装されなければならないという問題がある。

#### 【0009】

より具体的には、このように各画素に補償回路が追加されると、各画素を構成するトランジスタ及びキャパシタと、前記トランジスタを制御する信号線が追加されることにより、下部発光方式のAMOLEDの場合、開口率が減少し、回路の構成要素が増えて複雑化するにつれ、不良が発生する確率も高くなるという欠点がある。

20

#### 【0010】

また、最近では、画面の動きボケ(motion blur)現象を除去するために、120Hz以上の高速走査駆動が要求されているが、この場合、各走査ラインあたりの充電時間が大幅に減少する。すなわち、前記補償回路が各画素に備えられ、1つの走査ラインに接続された各画素内に多数のトランジスタが形成された場合、容量性負荷が大きくなり、結果として、このような高速走査駆動の実現が困難になるという欠点がある。

#### 【先行技術文献】

#### 【特許文献】

#### 【0011】

30

【特許文献1】韓国特許第0645699号

【特許文献2】韓国特許第0707624号

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0012】

本発明は、有機電界発光表示装置の各画素を構成する有機発光素子及びこれに接続された画素回路において、前記画素回路を、3つのトランジスタ及び2つのキャパシタで構成し、前記画素を同時発光方式で駆動することにより、簡単な構成でもって各画素に備えられた駆動トランジスタの閾値電圧の補償及び高速駆動を可能にする有機電界発光表示装置及びその駆動方法を提供することを目的とする。

40

#### 【課題を解決するための手段】

#### 【0013】

上記の目的を達成するために、本発明の実施例による有機電界発光表示装置は、走査線、制御線、及びデータ線に接続された画素を備える画素部と、前記制御線を介して各画素に制御信号を供給する制御線駆動部と、前記画素部の各画素に第1電源電圧を印加する第1電源駆動部と、前記画素部の各画素に第2電源電圧を印加する第2電源駆動部とを備え、前記第1及び第2電源駆動部のうちの少なくとも一方は、1フレーム期間中においてレベルが変化する電圧を前記画素部の各画素に印加し、前記制御信号及び前記第1及び第2電源は、前記画素部に備えられる画素全体に対して同時に一括して供給することを特徴とする。

50

## 【0014】

また、前記走査線を介して各画素に走査信号を提供する走査駆動部と、前記データ線を介して各画素にデータ信号を提供するデータ駆動部と、前記制御線駆動部、電源駆動部、走査駆動部、及びデータ駆動部を制御するタイミング制御部とをさらに備える。

## 【0015】

さらに、前記第1電源駆動部は、1フレーム期間中においてレベルが3段階に変化する電圧を印加し、第2電源駆動部は、一定レベルの電圧を1フレーム期間全体にわたり印加する。

## 【0016】

なお、前記第1及び第2電源駆動部は、1フレーム期間中においてレベルが2段階に変化する電圧をそれぞれ印加する。 10

## 【0017】

さらに、前記第1電源駆動部は、一定レベルの電圧を1フレーム期間全体にわたり印加し、前記第2電源駆動部は、1フレーム期間中においてレベルのが3段階に変化する電圧を印加する。

## 【0018】

また、前記走査信号は、1フレーム期間の一部の期間について各走査線に順次印加され、前記一部の期間以外の期間では全走査線に対して同時に印加される。

## 【0019】

さらに、前記順次印加される走査信号の幅は2水平時間(2H)として印加され、これに隣接して印加される走査信号が互いに1水平時間(1H)だけ重畠するように印加されることを特徴とする。 20

## 【0020】

また、前記データ信号は、前記順次印加された走査信号に対応して各走査線に接続された画素に順次印加され、前記一部の期間以外の期間では各データ線を介して全画素に同時に印加されることを特徴とする。

## 【0021】

さらに、前記各画素は、ゲート電極が前記走査線に接続され、第1電極が前記データ線に接続され、第2電極が第1ノードに接続された第1トランジスタと、ゲート電極が第2ノードに接続され、第1電極が第1電源駆動部に接続され、第2電極が有機発光素子のアノード電極に接続された第2トランジスタと、前記第1ノードと前記第2トランジスタの第1電極との間に接続された第1キャパシタと、前記第1ノードと前記第2ノードとの間に接続された第2キャパシタと、ゲート電極が制御線に接続され、第1電極は前記第2トランジスタのゲート電極に接続され、第2電極は前記第2トランジスタの第2電極に接続された第3トランジスタと、アノード電極が前記第2トランジスタの第2電極に接続され、カソード電極が第2電源駆動部に接続された有機発光素子とが備えられて構成され、前記第1、第2、及び第3トランジスタは、PMOSで実現されることを特徴とする。 30

## 【0022】

また、前記第1電源電圧及び制御信号がハイレベルで画素部に備えられた各画素にすべて印加されたとき、前記各画素は、各画素に予め格納されたデータ信号に対応する輝度で同時に発光することを特徴とする。 40

## 【0023】

さらに、前記各画素は、ゲート電極が前記走査線に接続され、第1電極が前記データ線に接続され、第2電極が第1ノードに接続された第1トランジスタと、ゲート電極が第2ノードに接続され、第1電極が第2電源駆動部に接続され、第2電極が有機発光素子のカソード電極に接続された第2トランジスタと、前記第1ノードと前記第2トランジスタの第1電極との間に接続された第1キャパシタと、前記第1ノードと前記第2ノードとの間に接続された第2キャパシタと、ゲート電極が制御線に接続され、第1電極は前記第2トランジスタのゲート電極に接続され、第2電極は前記第2トランジスタの第2電極に接続された第3トランジスタと、カソード電極が前記第2トランジスタの第2電極に接続され

、アノード電極が第1電源駆動部に接続された有機発光素子とが備えられて構成され、前記第1、第2、及び第3トランジスタは、N M O Sで実現されることを特徴とする。

#### 【0024】

一方、本発明の実施例による有機電界発光表示装置の駆動方法は、画素部を構成する画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、前記各画素に備えられた画素回路の各ノードの電圧を初期化する第1ステップと、前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、各画素に備えられた有機発光素子のアノード電極の電圧をカソード電極の電圧以下に低下させる第2ステップと、前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号、データ信号を一括して同時に印加し、前記各画素に備えられた駆動トランジスタの閾値電圧を格納する第3ステップと、前記画素部の各走査線に接続された各々の画素に対して走査信号が順次印加され、前記順次印加された走査信号に対応して各走査線に接続された画素にデータ信号が印加される第4ステップと、前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号を一括して同時に印加し、前記各画素に格納されたデータ電圧に対応する輝度で各々の画素全体が同時に発光する第5ステップと、前記画素全体に対してそれぞれ既定レベルの電圧を有する第1電源電圧、第2電源電圧、走査信号、制御信号を一括して同時に印加し、前記各画素に備えられた有機発光素子のアノード電極の電圧を低下させて発光をオフする第6ステップとが含まれることを特徴とする。

10

20

30

40

50

#### 【0025】

また、前記第1～第6ステップによって1つのフレームが実現され、順次進行するフレームについて、n番目のフレームは左眼画像を表示し、n+1番目のフレームは右眼画像を表示することを特徴とする。

#### 【0026】

さらに、前記n番目のフレームの発光期間とn+1番目のフレームの発光期間との間の期間の全時間をシャッタ眼鏡の応答時間に同期させるように実現することを特徴とする。

#### 【発明の効果】

#### 【0027】

このような本発明によれば、有機電界発光表示装置の各画素に備えられる画素回路を、3つのトランジスタ及び2つのキャパシタで構成し、前記画素を同時発光方式で駆動する。これにより、簡単な構成でもって各画素に備えられた駆動トランジスタの閾値電圧の補償及び高速駆動が可能になるという利点がある。

#### 【0028】

また、このような同時発光方式により、3次元(3D)ディスプレイに使用された場合、より向上した性能の実現が可能になるという利点がある。

#### 【図面の簡単な説明】

#### 【0029】

【図1】本発明の実施例による有機電界発光表示装置のブロック図である。

【図2】本発明の実施例による同時発光方式の駆動動作を示す図である。

【図3】従来の順次発光方式によりシャッタ眼鏡式の3Dを実現した例を説明する図である。

【図4】本発明の実施例による同時発光方式によりシャッタ眼鏡式の3Dを実現した例を説明する図である。

【図5】同時発光方式及び順次発光方式の場合に確保可能な発光時間比率を比較するグラフである。

【図6】図1に示す画素の第1実施例による構成を示す回路図である。

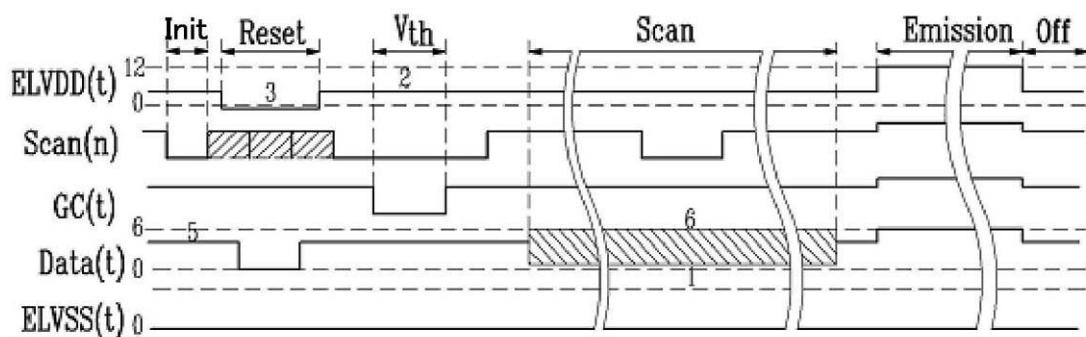

【図7a】図6に示す画素の駆動タイミング図である。

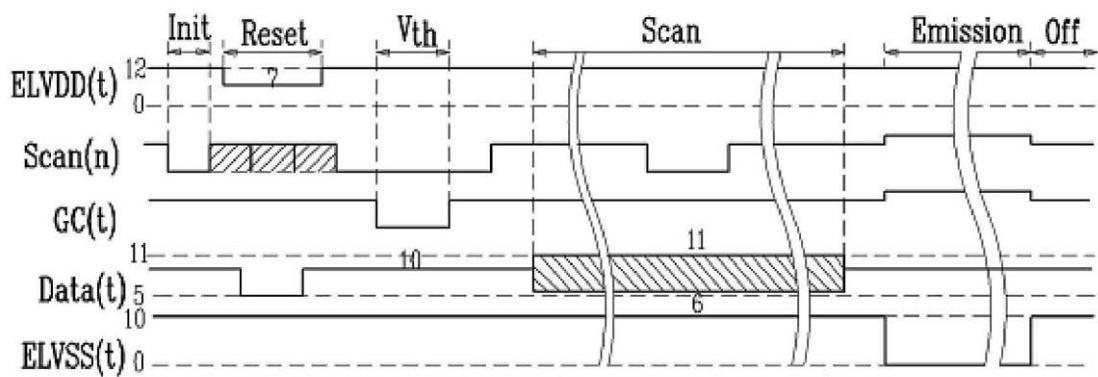

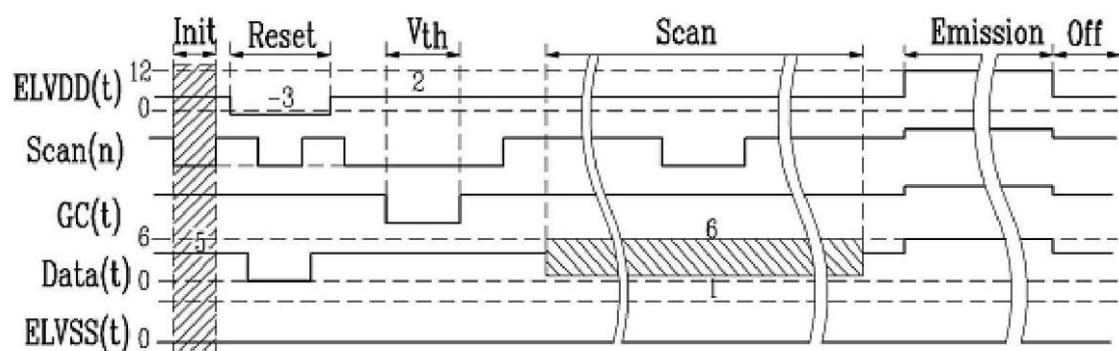

【図7b】図6に示す画素の駆動タイミング図である。

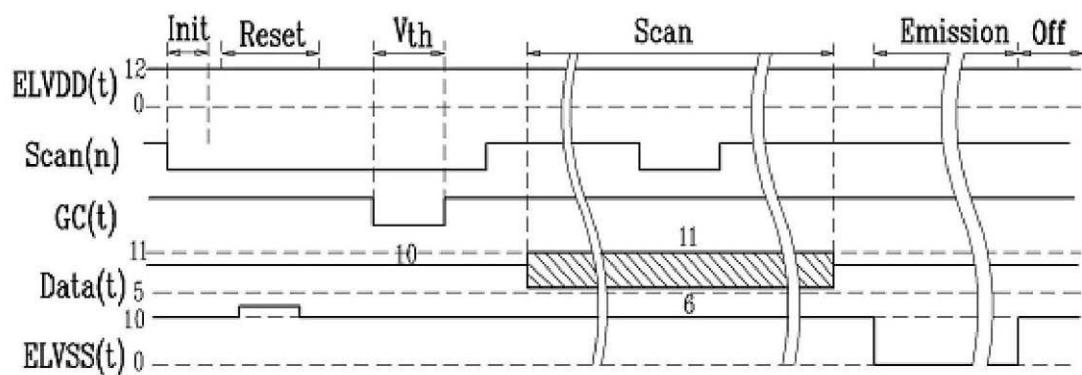

【図7c】図6に示す画素の駆動タイミング図である。

【図 8 a】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 b】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 c】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 d】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 e】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 f】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 g】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 h】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 i】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

【図 8 j】本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

10

20

20

30

40

40

【図 9】図 1 に示す画素の第 2 実施例による構成を示す回路図である。

【発明を実施するための形態】

【0030】

以下、添付図面を参照して本発明による実施例をより詳細に説明する。

【0031】

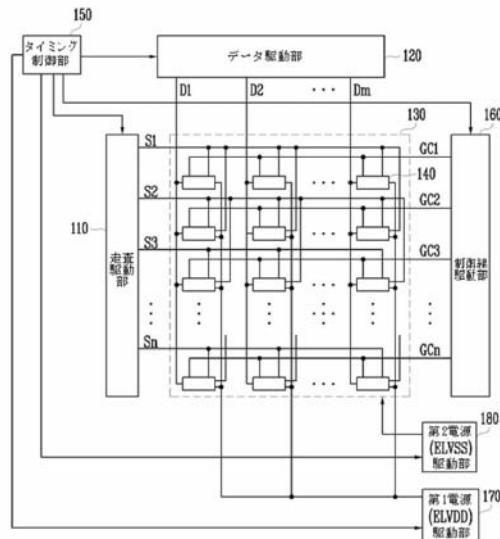

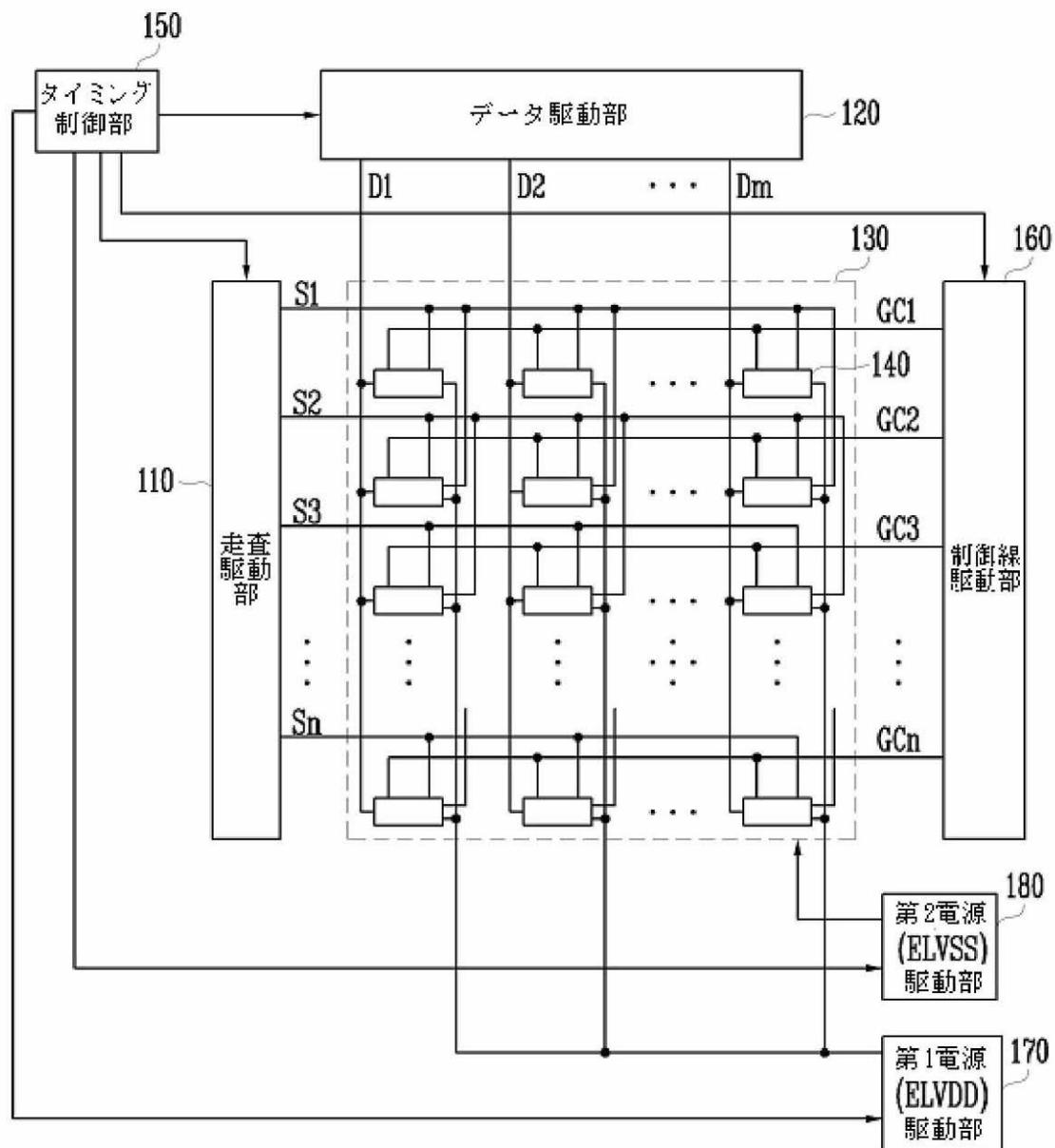

図 1 は、本発明の実施例による有機電界発光表示装置のブロック図であり、図 2 は、本発明の実施例による同時発光方式の駆動動作を示す図である。

【0032】

図 1 に示すように、本発明の実施例による有機電界発光表示装置は、走査線 S<sub>1</sub> ~ S<sub>n</sub>、制御線 G<sub>C1</sub> ~ G<sub>Cn</sub>、及びデータ線 D<sub>1</sub> ~ D<sub>m</sub>に接続された画素 140 を備える画素部 130 と、走査線 S<sub>1</sub> ~ S<sub>n</sub>を介して各画素に走査信号を提供する走査駆動部 110 と、制御線 G<sub>C1</sub> ~ G<sub>Cn</sub>を介して各画素に制御信号を提供する制御線駆動部 160 と、データ線 D<sub>1</sub> ~ D<sub>m</sub>を介して各画素にデータ信号を提供するデータ駆動部 120 と、走査駆動部 110、データ駆動部 120、及び制御線駆動部 160 を制御するためのタイミング制御部 150 とを備える。

【0033】

また、前記画素部 130 は、走査線 S<sub>1</sub> ~ S<sub>n</sub>とデータ線 D<sub>1</sub> ~ D<sub>m</sub>との交差部に位置する画素 140 を備える。画素 140 は、外部から第 1 電源電圧 E<sub>LVD</sub>D 及び第 2 電源電圧 E<sub>LVSS</sub>を受ける。この画素 140 は、データ信号に対応して、第 1 電源駆動部から有機発光素子を経て第 2 電源駆動部に供給される電流量を制御する。すると、有機発光素子において所定輝度の光が生成される。

【0034】

ただし、本発明の実施例の場合、前記第 1 電源駆動部の電圧 E<sub>LVD</sub>D 及び第 2 電源駆動部の電圧 E<sub>LVSS</sub>のうちの少なくとも一方が 1 フレーム期間中において、互いに異なるレベルの電圧を前記画素部の各画素 140 に印加することを特徴とする。すなわち、前記第 1 電源電圧 E<sub>LVD</sub>D 及び第 2 電源電圧 E<sub>LVSS</sub>のうちの少なくとも一方が 1 フレーム期間中において、段階的に変化することが可能である。

【0035】

このため、前記第 1 電源電圧 E<sub>LVD</sub>D の供給を制御する第 1 電源 (E<sub>LVD</sub>D) 駆動部 170、及び / または前記第 2 電源電圧 E<sub>LVD</sub>D の供給を制御する第 2 電源 (E<sub>LV</sub>

50

S S ) 駆動部 180 がさらに備えられ、前記第 1 電源 ( E L V D D ) 駆動部 170 及び第 2 電源 ( E L V S S ) 駆動部 180 は、前記タイミング制御部 150 によって制御される。

#### 【 0 0 3 6 】

より具体的に説明すると、従来の場合、前記第 1 電源電圧 E L V D D は固定されたハイレベルの電圧で提供され、第 2 電源 E L V S S は、固定されたローレベルの電圧で画素部の各画素に印加される。

#### 【 0 0 3 7 】

しかし、本発明の実施例では、前記第 1 電源電圧 E L V D D 及び第 2 電源電圧 E L V S S を印加するに際し、下記 3 つの方 10 式で実現することを特徴とする。

#### 【 0 0 3 8 】

第 1 の方式は、前記第 1 電源電圧 E L V D D が互いに異なる 3 つのレベルの電圧で印加され、第 2 電源電圧 E L V S S は固定されたローレベル ( 例えは、 G r o u n d ) で印加される。すなわち、前記第 1 電源電圧 E L V D D の大きさが、 1 フレーム期間中において、 3 段階で変化することが可能である。

#### 【 0 0 3 9 】

したがって、この場合、第 2 電源 ( E L V S S ) 駆動部 180 は、常に一定レベル ( G N D ) の電圧を出力するため、別途の駆動回路で実現される必要はなく、これに対する回路的費用は節減可能である。これに対し、前記第 1 電源電圧 E L V D D は、 3 つのレベルのうち、負の電圧 ( 例えは、 - 3 V ) が必要になるため、第 1 電源 ( E L V D D ) 駆動部 170 の回路構成が複雑化し得る。 20

#### 【 0 0 4 0 】

第 2 の方式は、前記第 1 電源電圧 E L V D D 及び第 2 電源電圧 E L V S S の両方をそれぞれ 2 つのレベルの電圧でそれぞれ印加するように実現するものであり、この場合、第 1 電源駆動部 170 と第 2 電源駆動部 180 とが両方とも備えられなければならない。すなわち、前記第 1 電源電圧 E L V D D および第 2 電源電圧 E L V S S の大きさが、 1 フレーム期間中において、それぞれ 2 段階で変化することが可能である。

#### 【 0 0 4 1 】

第 3 の方式は、前記第 1 の方式とは逆であり、前記第 1 電源電圧 E L V D D は固定されたハイレベルの電圧で印加され、第 2 電源電圧 E L V S S は互いに異なる 3 つのレベルの電圧で印加される。すなわち、前記第 2 電源電圧 E L V S S の大きさが、 1 フレーム期間中において、 3 段階で変化することが可能である。 30

#### 【 0 0 4 2 】

したがって、この場合、第 1 電源駆動部 170 は、常に一定レベルの電圧を出力するため、別途の駆動回路で実現される必要はなく、これに対する回路的費用は節減可能である。これに対し、前記第 2 電源電圧 E L V S S は、 3 つのレベルのうち、正の電圧が必要になるため、第 1 電源 ( E L V D D ) 駆動部 170 の回路構成が複雑化し得る。

#### 【 0 0 4 3 】

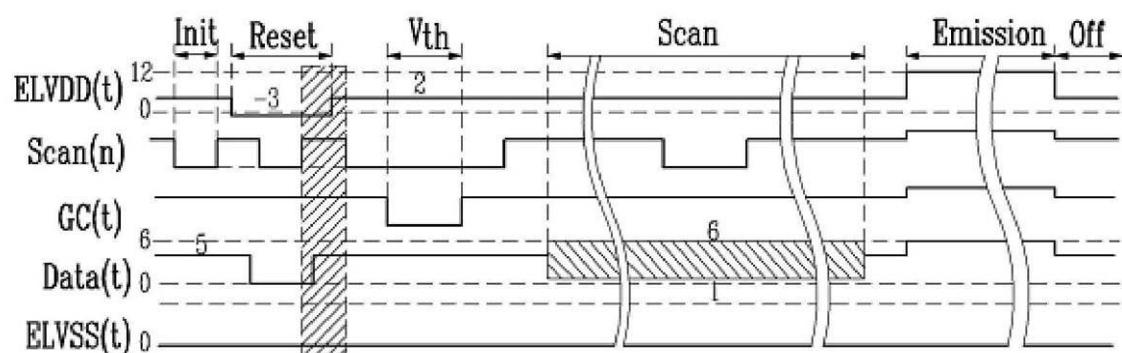

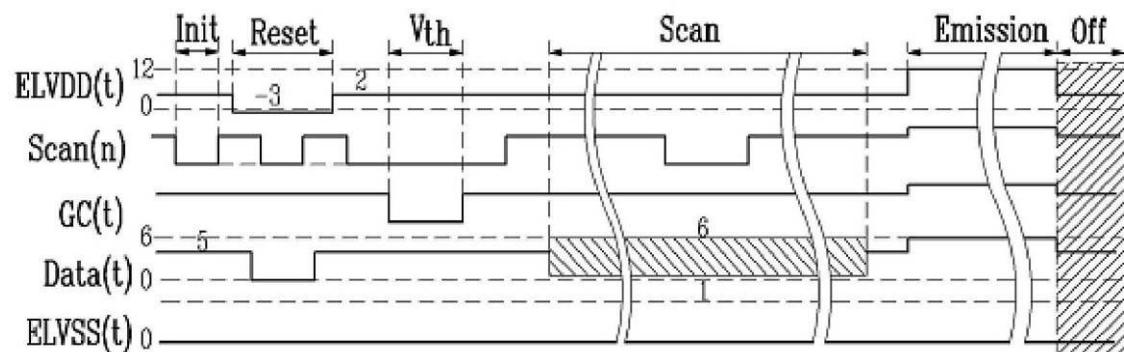

前記第 1 電源電圧 E L V D D 及び第 2 電源電圧 E L V S S を印加する 3 つの方 40 式に対する駆動タイミング図は、以下、図 7 a ~ 図 7 c に具体的に示している。

#### 【 0 0 4 4 】

また、本発明の実施例の場合、前記有機電界発光表示装置を駆動するに際し、順次発光 ( P r o g r e s s i v e E m i s s i o n : P E ) 方式ではなく、同時発光 ( S i m u l t a n e o u s E m i s s i o n : S E ) 方式で駆動することを特徴とする。これは、図 2 に示すように、 1 フレームの期間中にデータが順次入力され、前記データの入力が完了した後、 1 フレームのデータが、前記画素部 130 全体、すなわち、前記画素部内の全画素 140 を介して一括して点灯が行われることを意味する。

#### 【 0 0 4 5 】

すなわち、従来の順次発光方式の場合、各走査ラインにデータが順次入力され、これに続いて発光も順次行われていたのに対し、本発明の実施例では、前記データの入力は順次

行われるもの、発光は、データの入力が完了した後に全体的に一括して行われるものである。

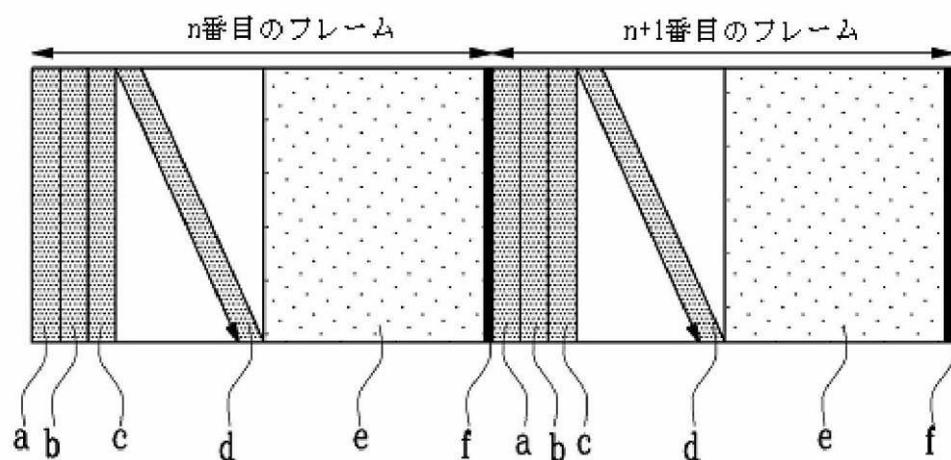

#### 【0046】

より具体的には、図2に示すように、本発明の実施例による駆動ステップは、大きくは、(a)初期化ステップと、(b)リセットステップと、(c)閾値電圧補償ステップと、(d)走査ステップ(データ入力ステップ)と、(e)発光ステップと、(f)発光オフステップとに分けられる。ここで、前記(d)走査ステップ(データ入力ステップ)は、走査ライン毎に順次行われるが、これを除く残りの(a)初期化ステップ、(b)リセットステップ、(c)閾値電圧補償ステップ、(e)発光ステップ、(f)発光オフステップは、図示のように、画素部130全体において同時に一括して行われる。10

#### 【0047】

ここで、前記(a)初期化ステップは、各画素に備えられる画素回路の各ノードの電圧を駆動トランジスタの閾値電圧の入力時と同様に初期化する期間であり、(b)リセットステップは、画素部130の各画素140に印加されたデータ電圧がリセットされるステップであって、有機発光素子が発光しないように、有機発光素子のアノード電極の電圧をカソード電極の電圧以下に低下させる期間である。

#### 【0048】

また、前記(c)閾値電圧補償ステップは、前記各画素140に備えられた駆動トランジスタの閾値電圧を補償する期間であり、(f)発光オフステップは、各画素において発光が行われた後、黒挿入(black insertion)または調光(dimming)のために発光をオフする期間である。20

#### 【0049】

これにより、前記(a)初期化ステップ、(b)リセットステップ、(c)閾値電圧補償ステップ、(e)発光ステップ、(f)発光オフステップに印加される信号、すなわち、各走査線S1～Snに印加される走査信号、各画素140に印加される第1電源ELVDD及び/または第2電源ELVSS、各制御線GC1～GCnに印加される制御信号は、前記画素部130に備えられた各画素140に対して同時に一括してそれぞれ定められた所定の電圧レベルで印加される。

#### 【0050】

このような本発明の実施例による同時発光方式によれば、各々の動作期間((a)～(f)ステップ)が時間的に明確に分離される。したがって、各画素140に備えられる補償回路のトランジスタ及びこれを制御する信号線の数を減らせるだけでなく、シャッタ(Shutter)眼鏡式の3Dディスプレイの実現が容易であるという利点がある。30

#### 【0051】

前記シャッタ眼鏡式の3Dディスプレイは、ユーザが左眼/右眼の透過率0%及び100%でスイッチされるシャッタ眼鏡を着用して画面をみると、画像表示装置、すなわち、有機電界発光表示装置の画素部において、ディスプレイされる画面が各フレーム毎に左眼画像と右眼画像とを交互に出力することにより、ユーザにとって、前記左眼画像は左眼で、前記右眼画像は右眼で視認されるようになり、これによって立体感が実現される方式をいう。40

#### 【0052】

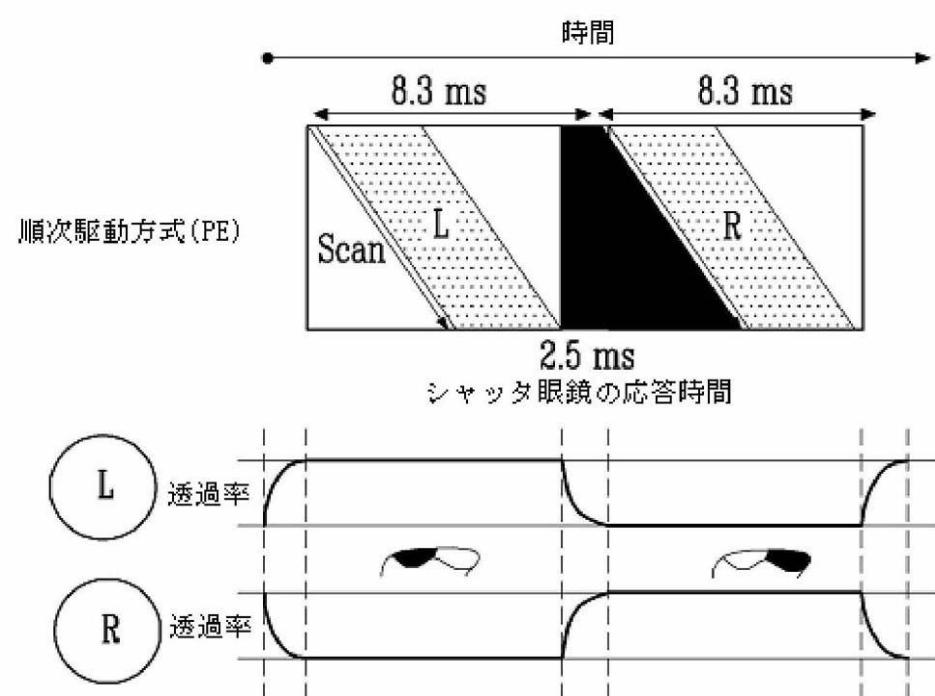

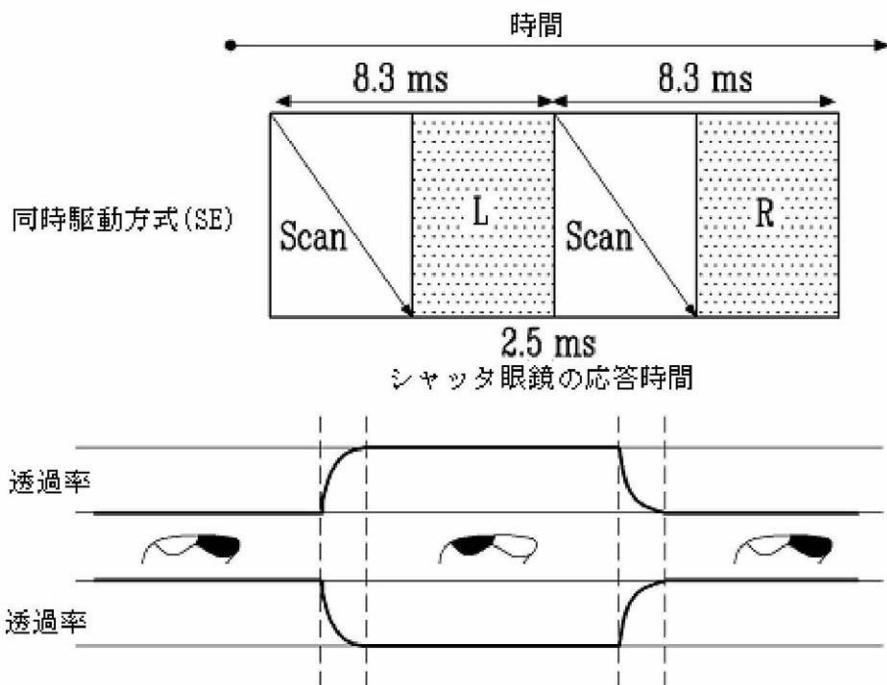

図3は、従来の順次発光方式によりシャッタ眼鏡式の3Dを実現した例を説明する図であり、図4は、本発明の実施例による同時発光方式によりシャッタ眼鏡式の3Dを実現した例を説明する図である。

#### 【0053】

また、図5は、同時発光方式及び順次発光方式の場合に確保可能な発光時間比率を比較するグラフである。

#### 【0054】

このようなシャッタ眼鏡式の3Dディスプレイを実現するにあたり、上述した従来の順次発光方式で画面を出力する場合は、図3に示すように、前記シャッタ眼鏡の応答時間(50

例えば、 $2.5\text{ ms}$ )が限られているため、前記左眼／右眼画像間のクロストーク現象を防止するために、前記応答時間だけ発光をオフしなければならない。

#### 【0055】

すなわち、左眼画像が出力されるフレーム( $n$ 番目のフレーム)と、これに続いて右眼画像が出力されるフレーム( $n+1$ 番目のフレーム)との間に前記応答時間だけ非発光期間をさらに生成しなければならないため、発光時間の確保、すなわち、発光時間比率( $duty ratio$ )が低くなるという欠点がある。

#### 【0056】

そこで、本発明の実施例による同時発光方式の場合、図4に示すように、上述したように、発光ステップが画素部全体において同時に一括して行われ、前記発光ステップ以外の期間では非発光が行われることにより、左眼画像が出力される期間と右眼画像が出力される期間との間の非発光期間が自然に確保される。10

#### 【0057】

すなわち、 $n$ 番目のフレームの発光期間と $n+1$ 番目のフレームの発光期間との間の期間であって、発光オフ期間、リセット期間、閾値電圧補償期間が非発光となる期間であるため、前記期間の全時間を前記シャッタ眼鏡の応答時間(例えば、 $2.5\text{ ms}$ )に同期させると、従来の順次発光方式とは異なり、発光時間比率を別途に低減しなくてもよい。

#### 【0058】

したがって、シャッタ眼鏡式の3Dディスプレイを実現するにあたり、前記同時発光方式は、従来の順次発光方式に比べて前記シャッタ眼鏡の応答時間だけの発光時間比率を確保できるため、より向上した性能の実現が可能になる。これは、図5のグラフから確認することができる。20

#### 【0059】

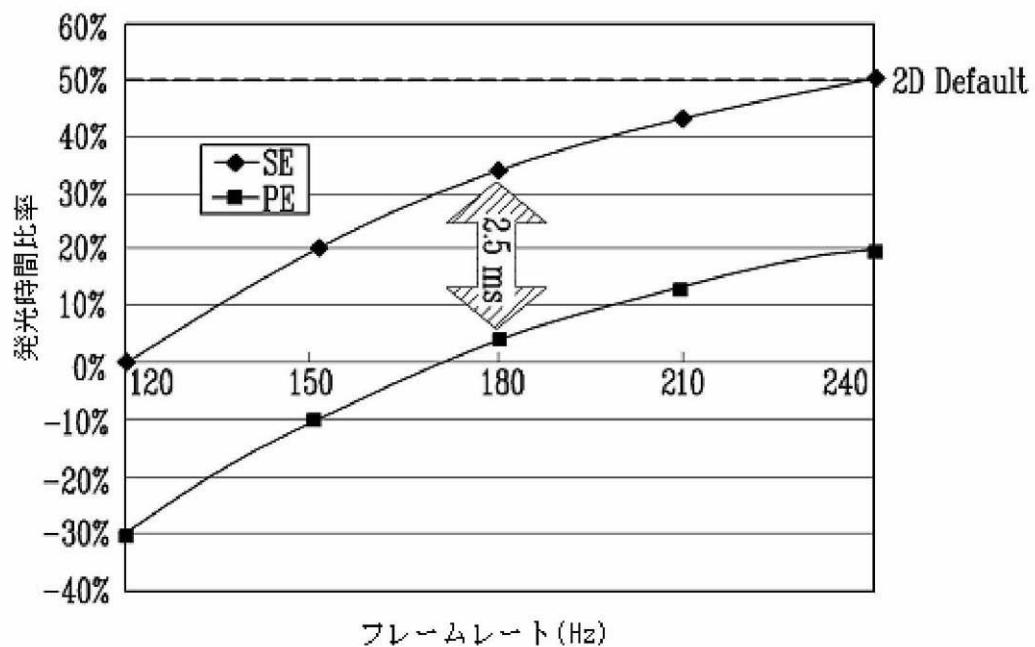

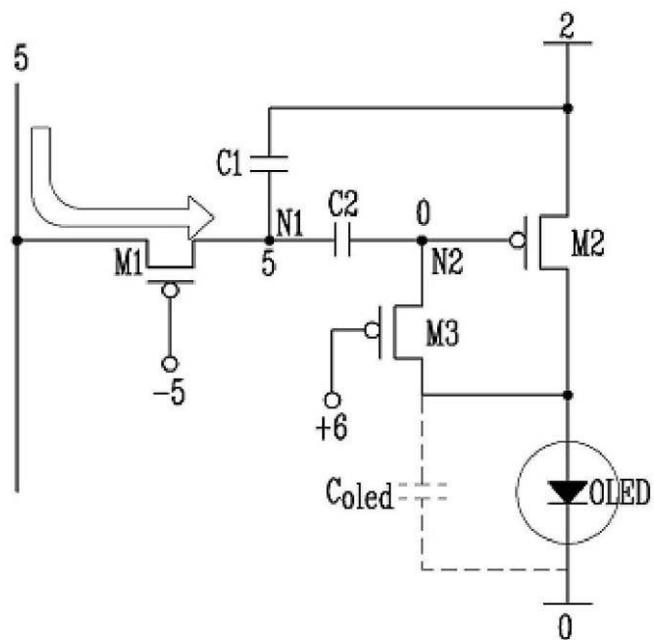

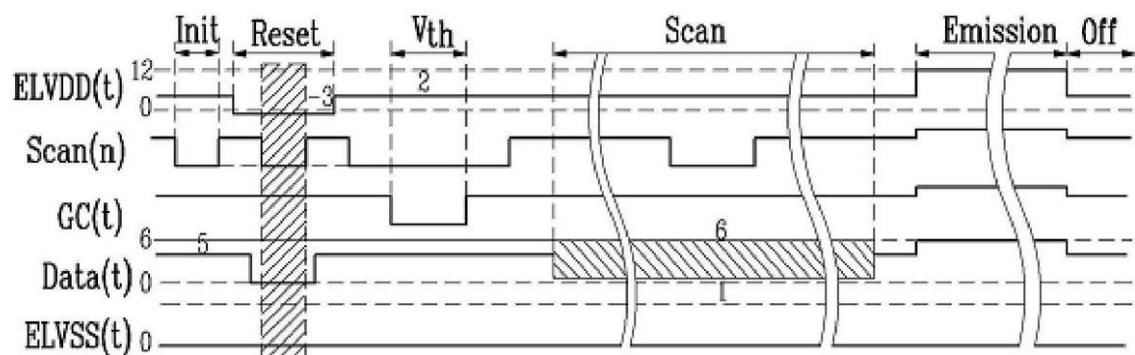

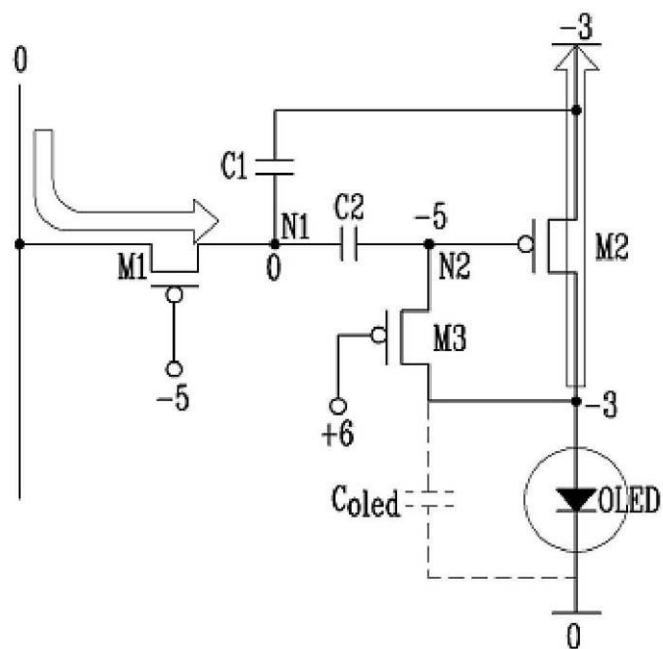

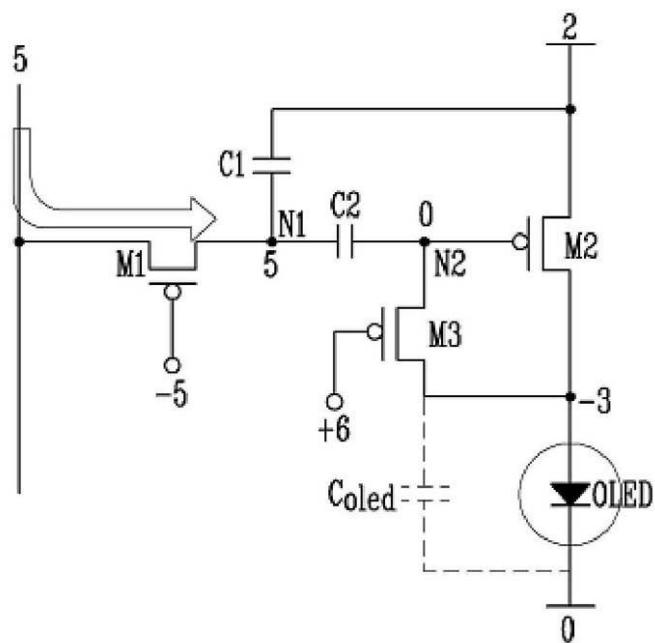

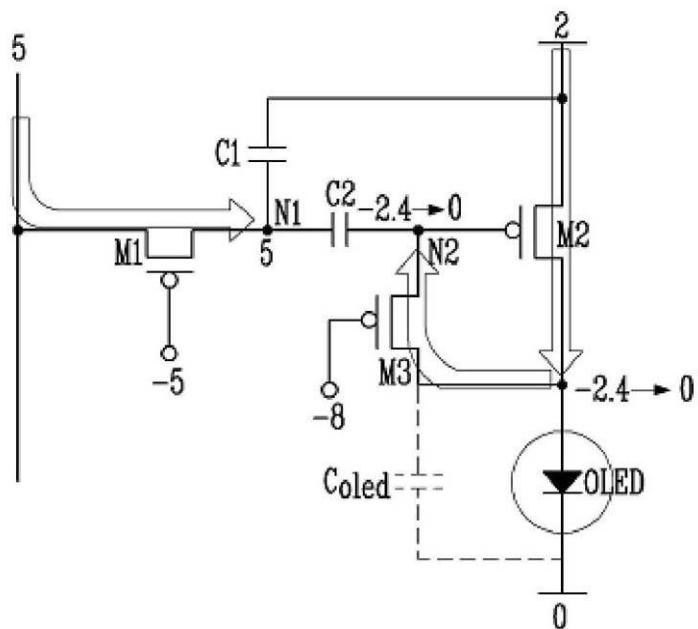

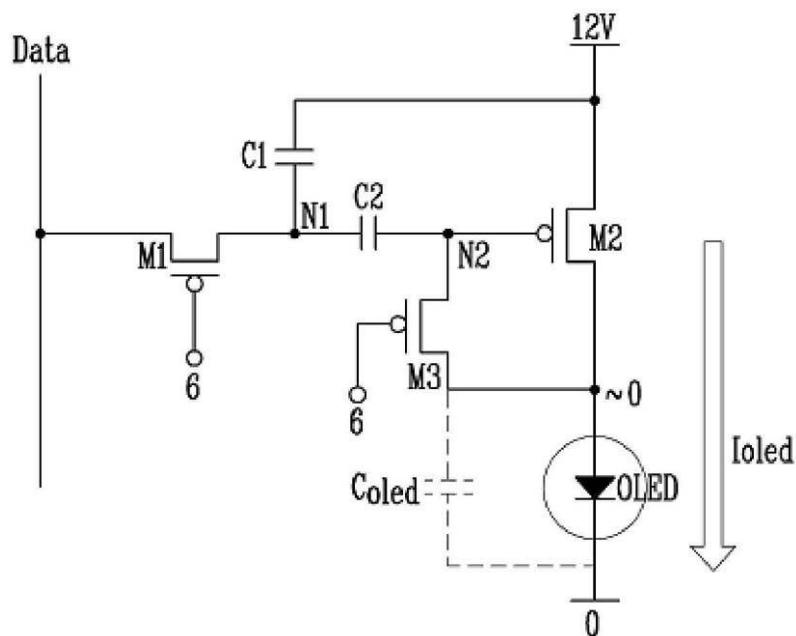

図6は、図1に示す画素の第1実施例による構成を示す回路図であり、図7a～図7cは、図6に示す画素の駆動タイミング図である。

#### 【0060】

図6に示すように、本発明の第1実施例による画素140は、有機発光素子OLED(Organic Light Emitting Diode)と、有機発光素子OLEDに電流を供給するための画素回路142とを備える。

#### 【0061】

有機発光素子OLEDのアノード電極は画素回路142に接続され、カソード電極は第2電源ELVSSに接続される。この有機発光素子OLEDは、画素回路142から供給される電流に対応して所定輝度の光を生成する。30

#### 【0062】

ただし、本発明の実施例の場合、画素部130を構成する各画素140は、1フレームの一部の期間(上述した(d)ステップ)について走査線S1～Snに走査信号が順次供給されたとき、データ線D1～Dmに供給されるデータ信号が供給されるが、1フレームの残りの期間((a)、(b)、(c)、(e)、(f)ステップ)については、各走査線S1～Snに印加される走査信号、各画素140に印加される第1電源ELVDD及び/または第2電源ELVSS、各制御線GC1～GCnに印加される制御信号が同時に一括してそれぞれ定められた所定の電圧レベルで前記各画素140に印加される。40

#### 【0063】

そこで、前記各画素140に備えられる画素回路142は、3つのトランジスタM1～M3及び2つのキャパシタC1、C2を備える。

#### 【0064】

また、本発明の実施例の場合、前記有機発光素子のアノード電極及びカソード電極によって生成される寄生キャパシタC<sub>01ed</sub>の容量を考慮して、前記第2キャパシタC<sub>2</sub>と寄生キャパシタC<sub>01ed</sub>によるカップリング効果を活用することを特徴とする。これについては、以下、図8a～図8jを用いてより詳細に説明する。

#### 【0065】

ここで、第1トランジスタM1のゲート電極は走査線Sに接続され、第1電極はデータ線Dに接続される。また、第1トランジスタM1の第2電極は第1ノードN1に接続される。

#### 【0066】

すなわち、前記第1トランジスタM1のゲート電極には走査信号Scan(n)が入力され、第1電極にはデータ信号Data(t)が入力される。

#### 【0067】

また、第2トランジスタM2のゲート電極は第2ノードN2に接続され、第1電極は第1電源ELVDD(t)に接続され、第2電極は有機発光素子のアノード電極に接続される。ここで、前記第2トランジスタM2は、駆動トランジスタとしての役割を果たす。

10

#### 【0068】

さらに、前記第1ノードN1と第2トランジスタM2の第1電極、すなわち、第1電源ELVDD(t)との間に第1キャパシタC1が接続され、前記第1ノードN1と第2ノードN2との間には第2キャパシタC2が接続される。

#### 【0069】

また、第3トランジスタM3のゲート電極は制御線GCに接続され、第1電極は前記第2トランジスタM2のゲート電極に接続され、第2電極は前記有機発光素子のアノード電極、すなわち、第2トランジスタM2の第2電極に接続される。

20

#### 【0070】

これにより、前記第3トランジスタM3のゲート電極には制御信号GC(t)が入力され、前記第3トランジスタがターンオンされた場合、前記第2トランジスタM2はダイオード接続される。

#### 【0071】

さらに、前記有機発光素子のカソード電極は第2電源ELVSS(t)に接続される。

#### 【0072】

図6に示す実施例の場合、前記第1～第3トランジスタM1～M3は、すべてPMOSで実現される。

30

#### 【0073】

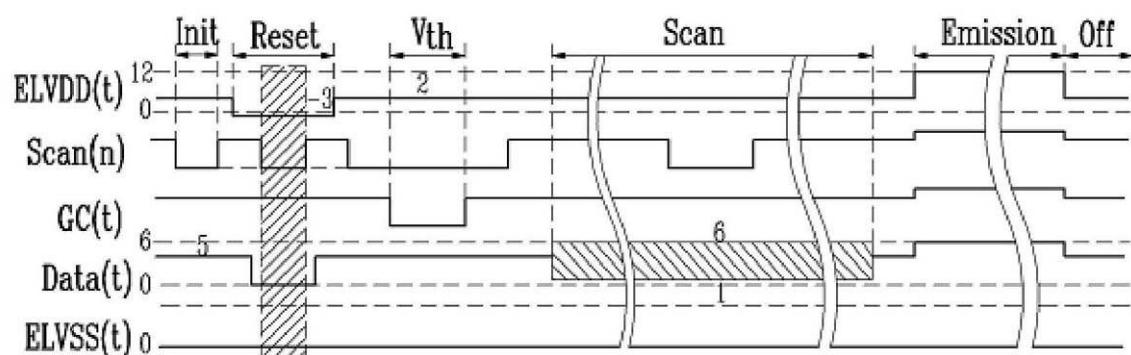

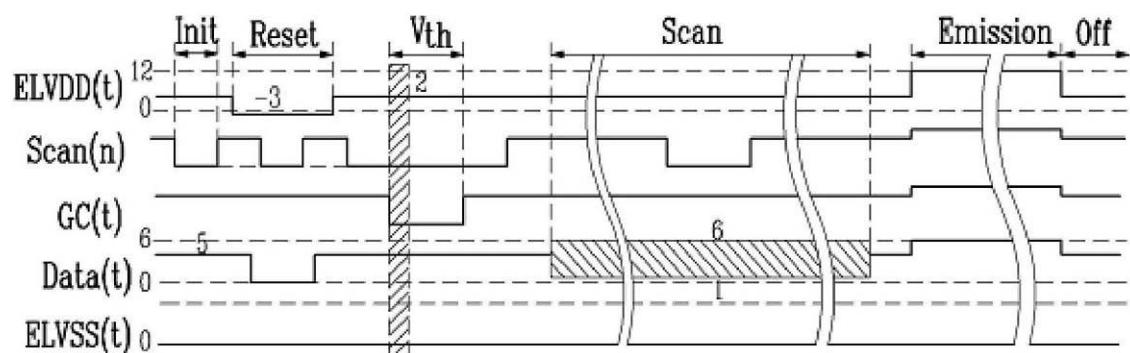

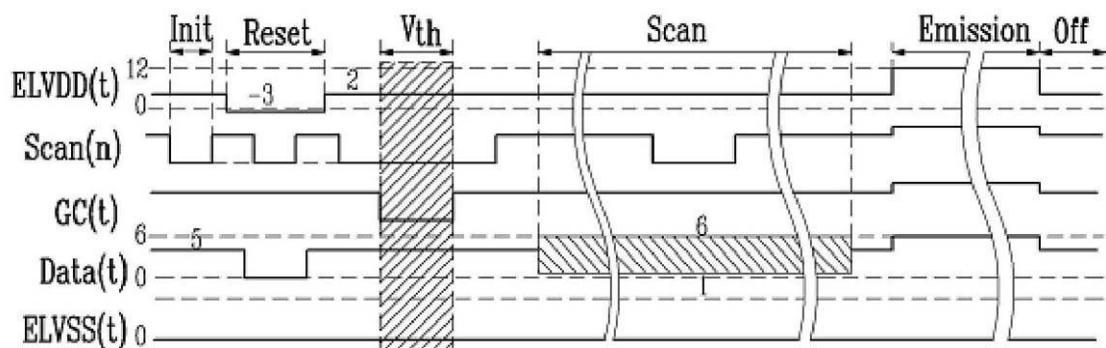

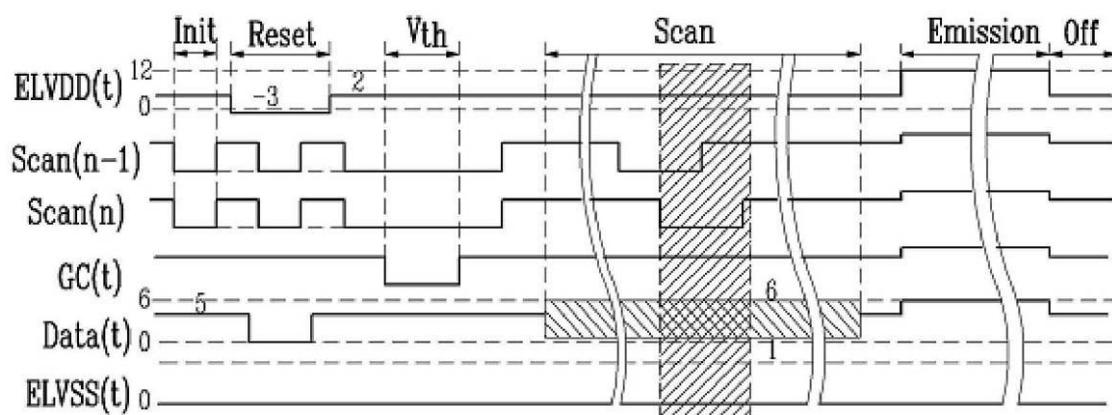

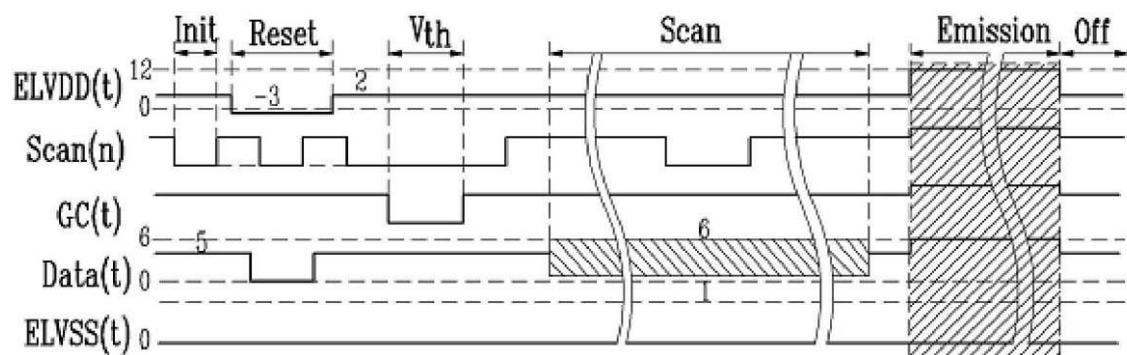

上述したように、本発明の実施例による前記各画素140は、同時発光方式で駆動されることを特徴とする。これは、具体的には、図7a～図7cに示すように、各フレーム毎に、初期化期間Initと、リセット期間Resetと、閾値電圧補償期間Vthと、走査/データ入力期間Scanと、発光期間Emissionと、発光オフ期間Offとに区分される。

#### 【0074】

このとき、前記走査/データ入力期間については、走査信号が各走査線に対して順次入力され、これに対応して各画素にデータ信号が順次入力されるが、これ以外の期間については、既定レベルの電圧を有する信号、すなわち、第1電源ELVDD(t)及び/または第2電源ELVSS(t)、走査信号Scan(n)、制御信号GC(t)、データ信号Data(t)が画素部を構成するすべての各画素140に一括して印加される。

40

#### 【0075】

すなわち、各画素140に備えられた駆動トランジスタの閾値電圧の補償及び各画素の発光動作は、フレーム毎に画素部内の全画素140において同時に実現されることを特徴とする。

#### 【0076】

ただし、本発明の実施例の場合、前記第1電源ELVDD(t)及び/または第2電源ELVSS(t)が提供されるに際し、それぞれ図7a～図7cに示すように、3つの方式で実現され得る。

#### 【0077】

まず、図7aに示すように、これは、前記第1電源ELVDD(t)が互いに異なる3つのレベル(例えば、12V、2V、-3V)の電圧で印加され、第2電源ELVSS(

50

$t$ ) は固定されたローレベル(例えば、0 V)で印加され、データ信号 Data( $t$ ) の電圧範囲は 0 ~ 6 V になる。

#### 【0078】

すなわち、この場合、第2電源(E L V S S)駆動部 180 は、常に一定レベル(GND)の電圧を出力するため、別途の駆動回路で実現される必要はなく、これに対する回路的費用は節減可能である。これに対し、前記第1電源 E L V D D は、3つのレベルのうち、負の電圧(例えば、-3 V)が必要になるため、第1電源(E L V D D)駆動部 170 の回路構成が複雑化し得る。

#### 【0079】

また、前記図 7 a に示す信号波形で駆動する場合、図示のように、リセット期間では、走査信号 Scan( $n$ ) がそれぞれ「ハイレベル(H)、ハイレベル(H)、ハイレベル(H)」、「ハイレベル(H)、ローレベル(L)、ハイレベル(H)」、「ローレベル(L)、ローレベル(L)、ローレベル(L)」で印加され得、これは、下記の図 8 b ~ 図 8 d を用いてより詳細に説明する。

#### 【0080】

次に、図 7 b に示すように、前記第1電源 E L V D D ( $t$ ) が 2 つのレベル(例えば、12 V、7 V)の電圧で印加され、前記第2電源 E L V S S ( $t$ ) も 2 つのレベル(例えば、0 V、10 V)の電圧でそれぞれ印加され、データ信号 Data( $t$ ) の電圧範囲は 0 ~ 12 V になる。

#### 【0081】

すなわち、この場合、駆動波形が単純化し得るが、互いに異なるレベルの電圧を出力するために、第1電源駆動部 170 及び第2電源駆動部 180 が両方とも備えられなければならない。

#### 【0082】

次に、図 7 c に示すように、これは、図 7 a とは逆の実施例であって、前記第1電源 E L V D D ( $t$ ) は固定されたハイレベル(例えば、12 V)の電圧で印加され、第2電源 E L V S S ( $t$ ) は互いに異なる 3 つのレベル(例えば、0 V、10 V、15 V)の電圧で印加される。

#### 【0083】

すなわち、この場合、第1電源駆動部 170 は、常に一定レベルの電圧を出力するため、別途の駆動回路で実現される必要はなく、これに対する回路的費用は節減可能である。これに対し、前記第2電源 E L V D D は、3つのレベルのうち、正の電圧が必要になるため、第1電源(E L V D D)駆動部 170 の回路構成が複雑化し得る。

#### 【0084】

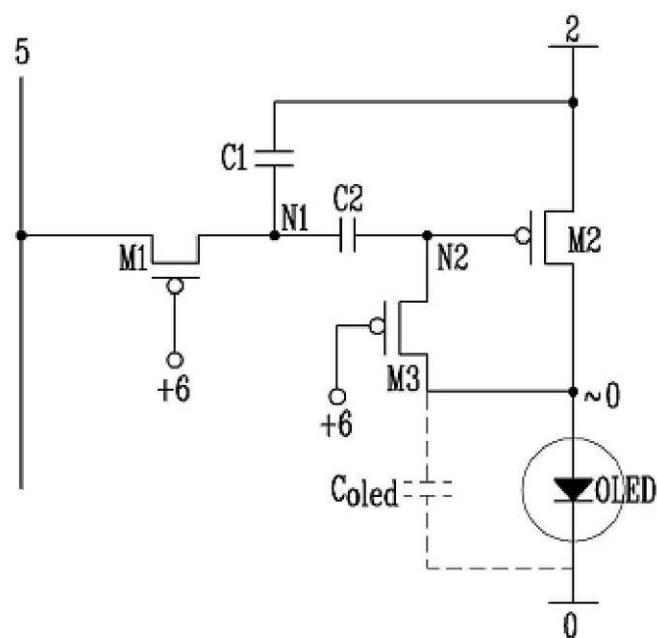

以下、図 8 a ~ 図 8 j を用いて本発明の実施例による同時発光方式の駆動をより具体的に説明する。

#### 【0085】

ただし、図 8 a ~ 図 8 j では、上述した図 7 a の駆動方式のうち、リセット期間において、走査信号 Scan( $n$ ) がそれぞれ「ハイレベル(H)、ローレベル(L)、ハイレベル(H)」で印加されることを例として説明する。

#### 【0086】

図 8 a ~ 図 8 j は、本発明の実施例による有機電界発光表示装置の駆動を説明するための図である。

#### 【0087】

ただし、説明の便宜上、入力される信号の電圧レベルを具体的な数値として説明するが、これは理解を得るために任意の値であり、実際の設計値に該当するものではない。

#### 【0088】

また、本発明の実施例の場合、第1キャパシタ C1、第2キャパシタ C2、有機発光素子の寄生キャパシタ C<sub>le<sub>d</sub></sub> の容量比は 1 : 1 : 4 であると仮定して説明する。

#### 【0089】

10

20

30

40

50

まず、図 8 a に示すように、これは、画素部 130 の各画素 140、すなわち、図 6 に示す画素に対し、各ノード N1、N2 の電圧を、その後進行する閾値電圧補償期間におけるのと同様に初期化するステップである。

#### 【0090】

すなわち、前記初期化期間では、第 1 電源 E L V D D ( t ) が中間レベル（例えば、2 V）で印加され、走査信号 S c a n ( n ) がローレベル（例えば、-5 V）で印加され、制御信号 G C ( t ) はハイレベル（例えば、6 V）で印加される。

#### 【0091】

また、前記ステップで印加されるデータ信号 D a t a ( t ) は、初期化電圧 V s u s として、本発明の実施例の場合、5 V が印加されることを例として説明し、さらに、前記第 2 キャパシタ C2 の両端間にかかる電圧差が 5 V であると仮定して説明する。

10

#### 【0092】

前記第 2 キャパシタ C2 の両端間の電圧差が 5 V と仮定することは、この後、閾値電圧補償期間に関する説明（図 8 d ~ 図 8 f）を参照するものとする。

#### 【0093】

さらに、前記初期化ステップは、画素部を構成する各画素に一括して適用されるものであるため、初期化ステップにおいて印加される信号、すなわち、第 1 電源 E L V D D ( t )、走査信号 S c a n ( n )、制御信号 G C ( t )、及びデータ信号 D a t a ( t ) は、それぞれ設定されたレベルの電圧で前記全画素に同時に印加される。

#### 【0094】

これら信号の印加により、第 1 トランジスタ M1 はターンオンされ、第 2 トランジスタ M2、第 3 トランジスタ M3 はターンオフされる。

20

#### 【0095】

したがって、第 1 ノード N1 には、データラインを介して初期化信号で印加された 5 V が印加され、前記第 2 キャパシタ C2 に 5 V が格納されているため、第 2 ノード N2 の電圧は 0 V になる。

#### 【0096】

次に、図 8 b ~ 図 8 d を参照すると、これは、画素部 130 の各画素 140、すなわち、図 6 に示す画素に印加されたデータ電圧がリセットされる期間であって、有機発光素子が発光しないように、有機発光素子のアノード電極の電圧をカソード電極の電圧以下に低下させるステップである。

30

#### 【0097】

本発明の実施例の場合、前記リセット期間は、図 8 b ~ 図 8 d の 3 つのステップで区分されて進行する。

#### 【0098】

まず、図 8 b に示すように、すなわち、前記第 1 リセット期間では、第 1 電源 E L V D D ( t ) がローレベル（例えば、-3 V）で印加され、走査信号 S c a n ( n ) がハイレベル（例えば、6 V）で印加され、制御信号 G C ( t ) はハイレベル（例えば、6 V）で印加される。

#### 【0099】

すなわち、前記走査信号 S c a n ( n ) がハイレベルで印加されることにより、PMOS である第 1 トランジスタ M1 はターンオフされ、これにより、前記データ信号 D a t a ( t ) は、前記期間について前記走査信号の電圧より低いレベルの電圧でのみ印加されればよい。

40

#### 【0100】

また、前記第 1 電源 E L V D D ( t ) で印加されるローレベルの電圧は、第 2 電源の電圧（例えば、0 V）以下の負の電圧が印加され、本発明の実施例の場合、これを -3 V と仮定して説明する。

#### 【0101】

このように前記第 1 電源 E L V D D ( t ) が -3 V で印加されると、これは、図 8 a の

10

20

30

40

50

初期化期間において提供された第1電源の電圧、すなわち、2Vより5V低い電圧が印加されるものであるため、第1キャパシタC1と第2キャパシタC2とのカップリング効果により、前記第1ノードN1の電圧も、初期化期間における5Vより5V低くなるため、0Vになり、第2ノードN2の電圧は、初期化期間における0Vより5V低い-5Vになる。

#### 【0102】

ただし、先の図8aを用いて簡単に述べたように、このとき、前記走査信号Scan(n)はローレベル(例えば、-5V)で印加され得るが、この場合は、前記第1トランジスタM1がターンオンされるため、前記第1ノードN1の電圧が0Vになるように、データ信号Data(t)は0Vが印加される。

10

#### 【0103】

すなわち、設計的制約条件における寄生カップリングにより、前記第1ノード及び第2ノードの電圧が所望するだけ十分に低下しない場合を考慮すると、このように、前記走査信号をローレベルで、これに対応するデータ信号を0Vで印加できるのである。

#### 【0104】

このように前記第2ノードN2が-5Vになると、これに接続された第2トランジスタM2のゲート電極に印加される電圧が-5Vになり、PMOSで実現された前記第2トランジスタM2はターンオンされる。

20

#### 【0105】

すなわち、第2トランジスタM2の第1及び第2電極間の電流通路が形成されることにより、前記第1電極に接続された有機発光素子のアノード電極に充電された電圧は、前記第1電源の電圧、すなわち、-3Vまで次第に低下する。

#### 【0106】

その後、図8cに示すように、前記第2リセット期間では、第1電源ELVDD(t)がローレベル(例えば、-3V)で印加され、走査信号Scan(n)がローレベル(例えば、-5V)で印加され、制御信号GC(t)はハイレベル(例えば、6V)で印加され、この場合、前記第1トランジスタM1がターンオンされるため、データ信号Data(t)は0Vが印加される。

30

#### 【0107】

すなわち、前記第2リセット期間は、第1リセット期間と比較するとき、走査信号Scan(n)がローレベル(例えば、-5V)であり、これに対応するデータ信号Data(t)が0Vで印加されるものであって、これは上述したように、設計的制約条件における寄生カップリングにより、前記第1ノード及び第2ノードの電圧が所望するだけ十分に低下しない場合を考慮して行うものである。

#### 【0108】

したがって、前記第2リセット期間は、第1リセット期間と同じ波形を維持してもよい。すなわち、第2リセット期間に印加される走査信号Scan(n)はハイレベルで印加されても構わない。

#### 【0109】

次に、図8dに示すように、前記第3リセット期間では、第1電源ELVDD(t)が中間レベル(例えば、2V)で印加され、走査信号Scan(n)がハイレベル(例えば、6V)で印加され、制御信号GC(t)はハイレベル(例えば、6V)で印加される。

40

#### 【0110】

すなわち、前記第3リセット期間の場合、前記第1電源を、図8aで説明した初期化期間におけるのと同一の電圧が印加されるように復帰させ、これにより、第1電源の電圧が前の第2リセット期間に比べて5V上昇する。これにより、第1キャパシタC1と第2キャパシタC2とのカップリング効果により、前記第1ノードN1及び第2ノードN2の電圧はそれぞれ5V、0Vに上昇する。

#### 【0111】

すなわち、前記各ノードの電圧及び第1電源の電圧は、図8aの初期化期間と同一にな

50

る。

【0112】

ただし、前記第1ないし第3リセット期間により、有機発光素子のアノード電極の電圧は、最終的にカソード電極の電圧(0V)より低い電圧である-3Vが印加された状態になる。

【0113】

また、前記第3リセット期間の場合も、前記走査信号Scan(n)はローレベル(例えば、-5V)で印加され得る。ただし、これに対応するデータ信号Data(t)は5Vで印加されなければならず、これにより、前記第1ノードN1の電圧を5Vに維持することができる。

10

【0114】

このような図8b～図8dにより、リセットステップは、画素部を構成する各画素に一括して適用される。したがって、前記第1～第3リセットステップにおいて印加される信号、すなわち、第1電源ELVDD(t)、走査信号Scan(n)、制御信号GC(t)及びデータ信号Data(t)は、各々の期間に設定されたレベルの電圧で全画素に同時に印加されなければならない。

【0115】

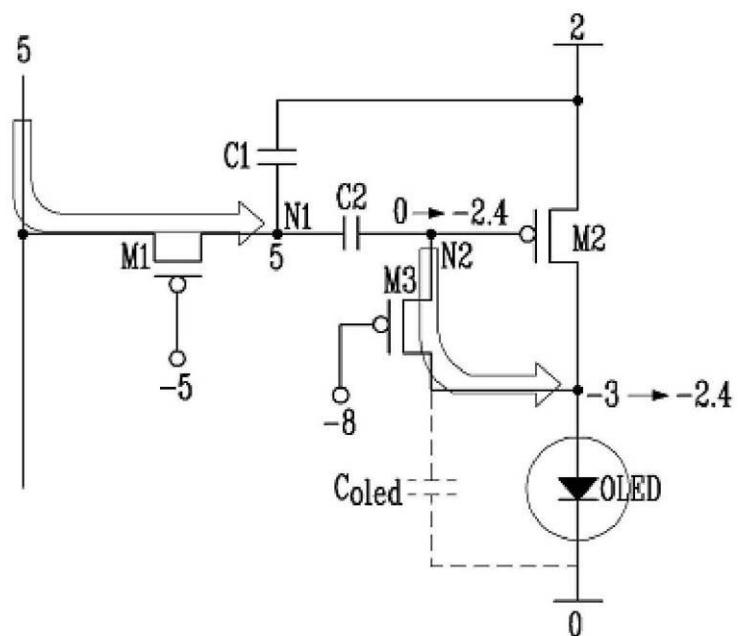

次に、図8e～図8gを参照すると、これは、画素部130の各画素140に備えられた駆動トランジスタM2の閾値電圧がキャパシタC1、C2に格納される期間であって、これは、この後、各画素にデータ電圧が充電されるとき、駆動トランジスタの閾値電圧のばらつきによる不良を除去する役割を果たす。

20

【0116】

本発明の実施例の場合、前記閾値電圧補償期間は、図8e～図8gの3つのステップに区分されて進行する。

【0117】

まず、図8eに示すように、すなわち、第1閾値電圧補償期間は、駆動トランジスタ、すなわち、第2トランジスタの閾値電圧を格納するための事前措置期間であって、先の図8dの期間と比較するとき、走査信号Scan(n)をローレベル(-5V)で印加する点で異なる。この場合、第1トランジスタM1がターンオンされるため、第1トランジスタの第1電極に印加されるデータ信号Data(t)は、先の図8dの第1ノードN1の電圧と同一の5Vで印加される。

30

【0118】

ここで、前記第1閾値電圧補償期間の場合、前記走査信号をハイレベルで印加しても構わないが、すなわち、図8dの信号印加波形をそのまま維持しても問題はないが、寄生カップリングにより、各ノードN1、N2の電圧が設定された値から外れるおそれを防止するために実現されるものである。

【0119】

次に、図8fに示すように、これは、第2閾値電圧補償期間であって、前記第2ノードN2をプルダウン(pull-down)させるステップである。

40

【0120】

このため、前記第1電源ELVDD(t)及び走査信号Scan(n)は、前のステップと同様にそれぞれ中間レベル(2V)、ローレベル(-5V)で印加され、前記制御信号GC(t)がローレベル(例えば、-8V)で印加される。

【0121】

すなわち、これら信号の印加により、第3トランジスタM3がターンオンされ、前記第3トランジスタM3がターンオンされることにより、第2トランジスタM2のゲート電極及び第2電極が電気的に接続され、結果として、前記第2トランジスタM2は、ダイオードとして動作することになる。

【0122】

これにより、前記第2ノードN2、すなわち、第2トランジスタM2のゲート電極にか

50

かる電圧は、前記第2キャパシタ $C_2$ と有機発光素子の寄生キャパシタ $C_{0.1ed}$ とのカップリング効果により、 $C_{0.1ed}/(C_2 + C_{0.1ed})$ だけ低下するのである。

【0123】

このとき、前記 $C_2$ と $C_{0.1ed}$ との容量比が1:4と仮定されたため、前記第2ノードN2の電圧は、0Vから、有機発光素子のアノード電極の電圧である-3V×4/5である-2.4Vに低下する。

【0124】

また、前記第2ノードN2及び前記有機発光素子のアノード電極は同じノードに接続された状態であるため、前記有機発光素子のアノード電極も-2.4Vになる。

【0125】

この後、図8gに示すように、これは、第3閾値電圧補償期間であって、印加される信号波形は、前の第2閾値電圧補償期間と同一である。

【0126】

ただし、先の第2閾値電圧補償期間で説明したように、第2ノードN2が-2.4Vに低下すると、駆動トランジスタとしての第2トランジスタM2はターンオンされる。前記第2トランジスタM2は、ダイオードとしての役割を果たすため、前記第1電源ELVD<sub>D(t)</sub>と前記有機発光素子のアノード電極との間の電圧差が第2トランジスタM2の閾値電圧の大きさに対応するまでターンオンされて電流が流れ、それ以降はターンオフされる。

【0127】

すなわち、例えば、前記第1電源が2Vで印加され、第2トランジスタの閾値電圧 $V_{th}$ が-2Vであるため、前記有機発光素子のアノード電極が0Vになるまで電流が流れるようになる。

【0128】

また、前記第2ノードN2と前記有機発光素子のアノード電極との電位差はないため、前記アノード電極が0Vになると、前記第2ノードN2も0Vになる。

【0129】

ただし、前記第2トランジスタM2の閾値電圧 $V_{th}$ は、実質的にその偏差( $\Delta V_{th}$ )が存在するため、実際の閾値電圧は、

【0130】

【数1】

$$\begin{aligned} V'_{th} &= V_{th} + \Delta V_{th} \\ &= -2V + \Delta V_{th} \end{aligned}$$

【0131】

になり、これにより、前記第2ノードN2の電圧は $V'_{th}$ になる。

【0132】

さらに、前記第1～第3閾値電圧補償ステップも、画素部を構成する各画素に一括して適用される。したがって、閾値電圧補償ステップにおいて印加される信号、すなわち、第1電源ELVDD<sub>D(t)</sub>、走査信号Scan(n)、制御信号GC(t)、及びデータ信号Data(t)は、それぞれ設定されたレベルの電圧で前記全画素に同時に印加される。

【0133】

次に、図8hに示すように、これは、画素部130の各走査線S1～Snに接続された各々の画素に対して走査信号が順次印加され、これにより、各データ線D1～Dmに供給されるデータ信号が印加されるステップである。

【0134】

すなわち、図8hに示す走査/データ入力期間については、走査信号が各走査線に対して順次入力され、これに対応して各走査線毎に接続された画素にデータ信号が順次入力され、前記期間において、制御信号GC(t)はハイレベル(例えば、+6V)で印加され

10

20

30

40

50

る。

【0135】

ただし、本発明の実施例の場合、図8hに示すように、前記順次印加される走査信号の幅を2水平時間(2H)として印加することが好ましい。すなわち、n-1番目の走査信号Scan(n-1)の幅に続いて、順次印加されるn番目の走査信号Scan(n)の幅は1Hだけ重畠するように印加される。

【0136】

これは、画素部の大面積化による信号線のRC遅延による充電不足現象を克服するためである。

【0137】

また、前記制御信号GC(t)がハイレベルで印加されることにより、PMOSである第3トランジスタM3はターンオフされる。

【0138】

図8hに示す画素の場合、ローレベルの走査信号が印加されて第1トランジスタM1がターンオンされると、これに対応して所定の電圧を有するデータ信号Data(t)が第1トランジスタの第1及び第2電極を経て第1ノードN1に印加される。

【0139】

このとき、前記印加されるデータ信号の電圧は、例えば、1V~6Vの範囲で印加され、この場合、前記1Vは白を示す電圧であり、前記6Vは黒を示す電圧である。

【0140】

ここで、前記印加されるデータを6Vと仮定した場合、前記第1ノードN1の電圧は、前の初期化電圧V<sub>sus</sub>である5Vから1V上昇する。これにより、前記第2ノードN2の電圧も1V上昇し、第2ノードN2の電圧は「V<sub>th</sub>+1V」になる。

【0141】

これを数式で表すと、次のとおりである。

【0142】

【数2】

$$\begin{aligned} \text{第2ノードN2の電圧} &= \Delta V_{th} + (V_{data} - V_{sus}) \\ &= \Delta V_{th} + (6V - 5V) \end{aligned}$$

10

20

30

【0143】

ただし、前記期間では、前記第1電源ELVDD(t)が2Vで印加されているため、前記第2トランジスタM2がターンオフ状態にある。これにより、有機発光素子と第1電源ELVDD(t)との間に電流経路が形成されておらず、実質的には、有機発光素子には電流が流れない。すなわち、非発光となる。

【0144】

次に、図8iを参照すると、これは、画素部130の各画素140に格納されたデータ電圧に対応する電流が各画素に備えられた有機発光素子に提供され、発光が行われる期間である。

【0145】

すなわち、前記発光期間では、第1電源ELVDD(t)がハイレベル(例えば、12V)で印加され、走査信号Scan(n)及び制御信号GC(t)はそれぞれハイレベル(例えば、6V)で印加される。

【0146】

これにより、前記走査信号Scan(n)がハイレベルで印加されることにより、PMOSである第1トランジスタM1はターンオフされるため、前記データ信号は、前記期間についてどのレベルの電圧で提供されても構わない。

【0147】

また、前記発光ステップも、画素部を構成する各画素に一括して適用されるものであるため、発光ステップにおいて印加される信号、すなわち、第1電源ELVDD(t)、走

40

50

査信号 S c a n ( n ) 、制御信号 G C ( t ) 、及びデータ信号 D a t a ( t ) は、それぞれ設定されたレベルの電圧で前記全画素に同時に印加される。

【 0 1 4 8 】

さらに、前記制御信号 G C ( t ) がハイレベルで印加されることにより、P M O S である第 3 トランジスタ M 3 はターンオフされるため、ダイオード接続されていた第 2 トランジスタ M 2 は、駆動トランジスタの役割を果たすようになる。

【 0 1 4 9 】

そこで、前記第 2 トランジスタ M 2 のゲート電極、すなわち、第 2 ノード N 2 に印加された電圧が「  $V_{t_h} + 1V$  」であり、第 2 トランジスタ M 2 の第 1 電極に印加される第 1 電源 E L V D D ( t ) がハイレベル（例えば、12V）で印加されることにより、P M O S である第 2 トランジスタ M 2 はターンオンされる。

10

【 0 1 5 0 】

このように第 2 トランジスタ M 2 のターンオンにより前記第 1 電源から有機発光素子のカソード電極までの電流経路が形成される。これにより、前記第 2 トランジスタ M 2 の  $V_{g_s}$  の電圧、すなわち、第 2 トランジスタのゲート電極と第 1 電極との電圧差に該当する電圧に対応する電流が前記有機発光素子に印加され、これに対応する明るさで発光するのである。

【 0 1 5 1 】

すなわち、

【 0 1 5 2 】

【 数 3 】

20

$$M_2 \text{ のゲート・ソース間電圧 } V_{g_s} = E L V D D ( t ) - \text{ 第2ノード } N_2 \text{ の電圧} \\ V_{t_h}' = V_{t_h} + \Delta V_{t_h}$$

【 0 1 5 3 】

を考慮すると、前記有機発光素子に流れる電流は、

【 0 1 5 4 】

【 数 4 】

$$I_{o,led} = \beta / 2 (V_{g_s} - V_{t_h}')^2 \\ = \beta / 2 [E L V D D ( t ) - (V_{data} - V_{sus} + \Delta V_{t_h}) - V_{t_h}']^2 \\ = \beta / 2 [E L V D D ( t ) - (V_{data} - V_{sus}) - V_{t_h}]^2$$

30

【 0 1 5 5 】

になるため、結果として、本発明の実施例によれば、有機発光素子に流れる電流は、第 2 トランジスタ M 2 の閾値電圧  $V_{t_h}'$  のばらつき ( $V_{t_h}$ ) が相殺されるため、 $V_{t_h}$  には関係なくなる。したがって、 $V_{t_h}$  によって発生する問題を克服することができる。

【 0 1 5 6 】

このように画素部全体の発光が行われた後は、図 8 j に示すように、発光オフステップを行う。

40

【 0 1 5 7 】

すなわち、図 8 j に示すように、前記発光オフ期間では、第 1 電源 E L V D D ( t ) が中間レベル（例えば、2V）で印加され、走査信号 S c a n ( n ) はハイレベル（例えば、6V）が印加され、制御信号 G C ( t ) はハイレベル（例えば、6V）で印加される。

【 0 1 5 8 】

すなわち、図 8 i の発光期間と比較するとき、前記第 1 電源 E L V D D ( t ) がハイレベルから中間レベル（例えば、2V）に変更されたこと以外は同一である。

【 0 1 5 9 】

これは、発光動作後、黒挿入 ( b l a c k i n s e r t i o n ) または調光 ( d i m m i n g ) のために発光をオフする期間であって、有機発光素子のアノード電極の電圧は

50

、その前に有機発光素子が発光していた場合、数十  $\mu$  s 以内に発光がオフされる電圧まで低下する。

#### 【0160】

このように、図 8 a ~ 図 8 j 期間によって 1 つのフレームが実現され、これは循環し続け、次のフレームを実現する。すなわち、図 8 j の発光オフ期間の後は、再び図 8 a の初期化期間が進行するのである。

#### 【0161】

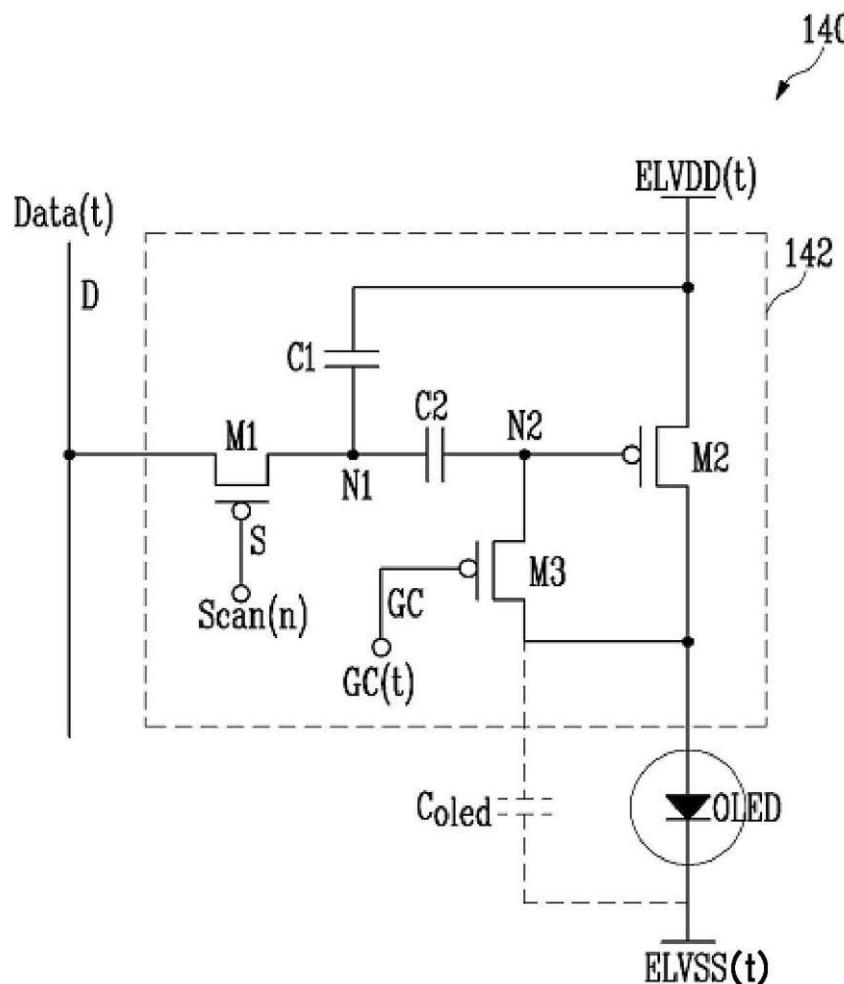

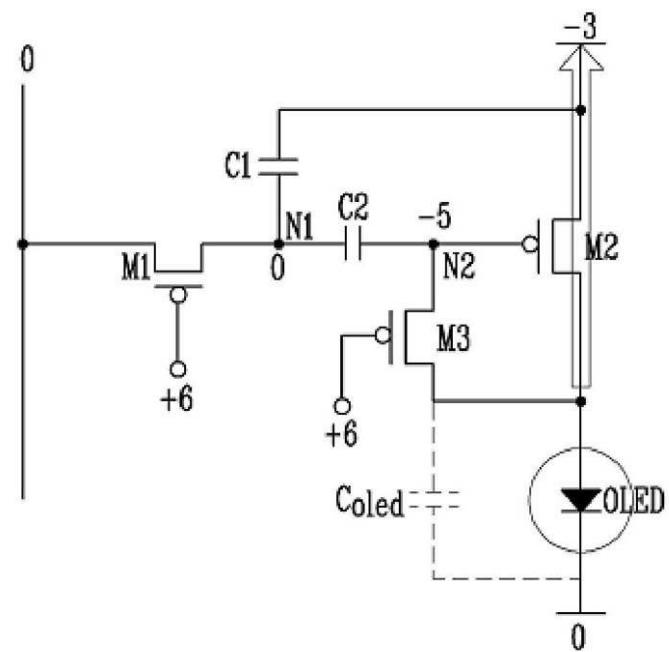

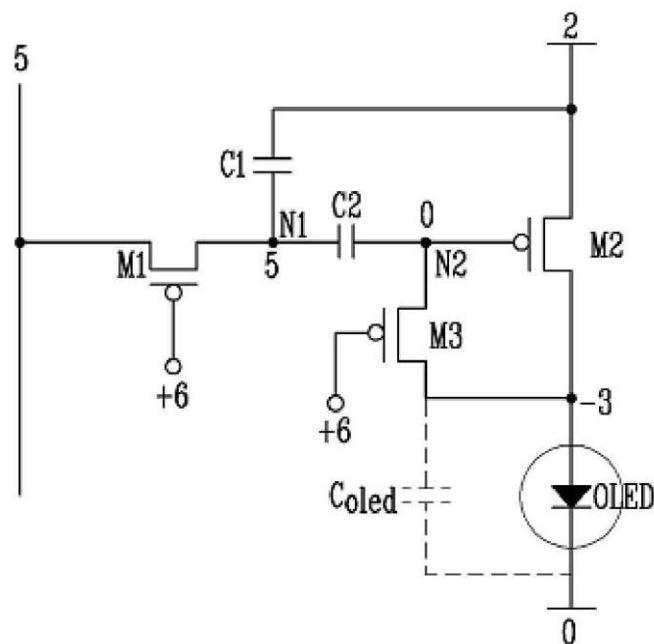

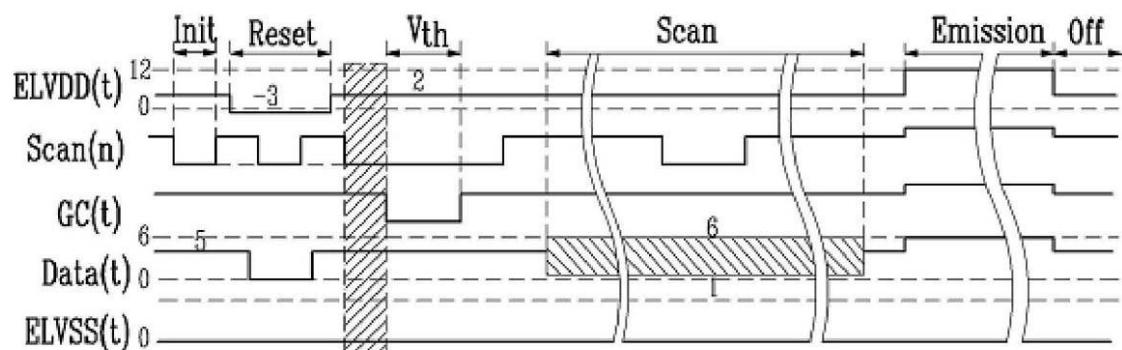

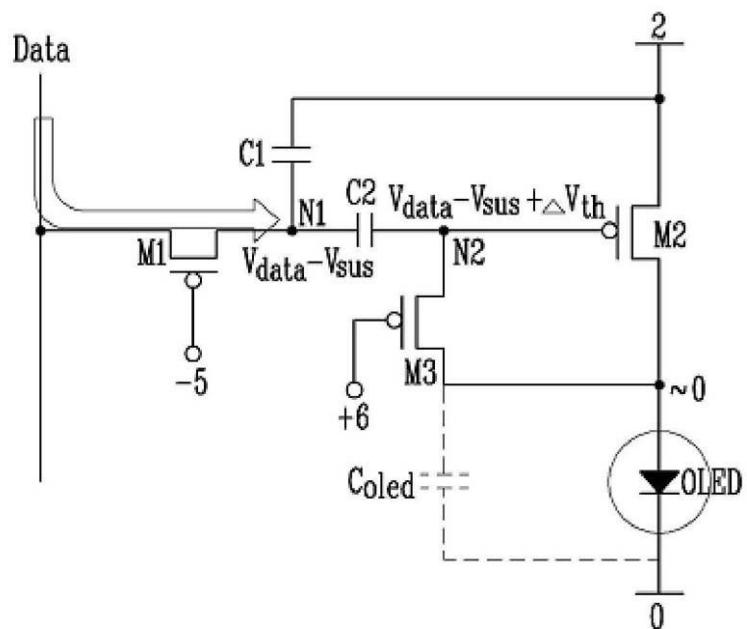

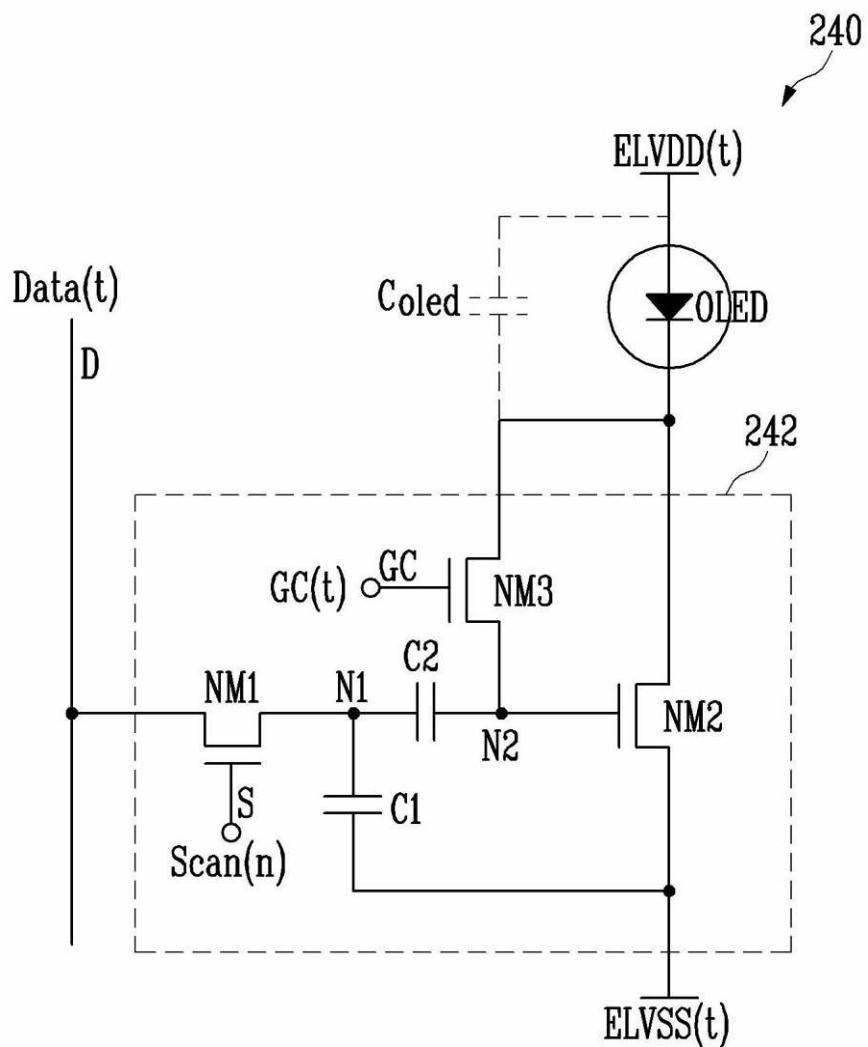

図 9 は、図 1 に示す画素の第 2 実施例による構成を示す回路図である。

#### 【0162】

図 9 を参照すると、これは、図 6 に示す実施例と比較するとき、画素回路を構成するトランジスタが N M O S で実現される点で異なる。10

#### 【0163】

この場合、駆動波形は、図 7 a ~ 図 7 c の駆動タイミング図と比較するとき、走査信号 S c a n ( n ) 、制御信号 G C ( t ) 、第 1 電源 E L V D D ( t ) 、第 2 電源 E L V S S ( t ) 、データ書き込み期間以外に供給されるデータ信号 D a t a ( t ) の駆動波形と極性が反転した形で提供される。

#### 【0164】

結果として、図 9 に示す第 2 実施例は、図 6 に示す第 1 実施例と比較するとき、トランジスタが P M O S ではなく、N M O S で実現されるものであり、その駆動動作及び原理は、第 1 実施例と同一であるため、その具体的な説明は省略する。20

#### 【0165】

図 9 に示すように、本発明の実施例による画素 240 は、有機発光素子 O L E D と、有機発光素子 O L E D に電流を供給するための画素回路 242 とを備える。

#### 【0166】

有機発光素子 O L E D のカソード電極は画素回路 242 に接続され、アノード電極は第 1 電源 E L V D D ( t ) に接続される。この有機発光素子 O L E D は、画素回路 242 から供給される電流に対応して所定輝度の光を生成する。

#### 【0167】

ただし、本発明の実施例の場合、画素部を構成する各画素 240 は、1 フレームの一部の期間（上述した（d）ステップ）について走査線 S 1 ~ S n に走査信号が順次供給されたとき、データ線 D 1 ~ D m に供給されるデータ信号が供給されるが、1 フレームの残りの期間（（a）、（b）、（c）、（e）、（f）ステップ）については、各走査線 S 1 ~ S n に印加される走査信号、各画素 240 に印加される第 1 電源 E L V D D 及び / または第 2 電源 E L V S S 、各制御線 G C 1 ~ G C n に印加される制御信号が同時に一括してそれぞれ定められた所定の電圧レベルで前記各画素 240 に印加される。30

#### 【0168】

そこで、前記各画素 240 に備えられる画素回路 242 は、3 つのトランジスタ N M 1 ~ N M 3 及び 2 つのキャパシタ C 1 、C 2 を備える。

#### 【0169】

ここで、第 1 トランジスタ N M 1 のゲート電極は走査線 S に接続され、第 1 電極はデータ線 D に接続される。また、第 1 トランジスタ N M 1 の第 2 電極は第 1 ノード N 1 に接続される。40

#### 【0170】

すなわち、前記第 1 トランジスタ N M 1 のゲート電極には走査信号 S c a n ( n ) が入力され、第 1 電極にはデータ信号 D a t a ( t ) が入力される。

#### 【0171】

また、第 2 トランジスタ N M 2 のゲート電極は第 2 ノード N 2 に接続され、第 1 電極は第 2 電源 E L V S S ( t ) に接続され、第 2 電極は有機発光素子のカソード電極に接続される。ここで、前記第 2 トランジスタ N M 2 は、駆動トランジスタとしての役割を果たす。

50

20

30

40

50

**【 0 1 7 2 】**

さらに、前記第1ノードN1と第2トランジスタNM2の第1電極、すなわち、第2電源ELVSS(t)との間に第1キャパシタC1が接続され、前記第1ノードN1と第2ノードN2との間には第2キャパシタC2が接続される。

**【 0 1 7 3 】**

また、第3トランジスタNM3のゲート電極は制御線GCに接続され、第1電極は前記第2トランジスタNM2のゲート電極に接続され、第2電極は前記有機発光素子のカソード電極、すなわち、第2トランジスタNM3の第2電極に接続される。

**【 0 1 7 4 】**

これにより、前記第3トランジスタNM3のゲート電極には制御信号GC(t)が入力され、前記第3トランジスタがターンオンされた場合、前記第2トランジスタNM2はダイオード接続される。 10

**【 0 1 7 5 】**

さらに、前記有機発光素子のアノード電極は第1電源ELVDD(t)に接続される。

**【 0 1 7 6 】**

図9に示す実施例の場合、前記第1～第3トランジスタNM1～NM3は、すべてNMOSで実現される。

**【 符号の説明 】****【 0 1 7 7 】**

- 110 走査駆動部、

120 データ駆動部、

130 画素部、

140, 240 画素、

142, 242 画素回路、

150 タイミング制御部、

160 制御線駆動部、

170 第1電源(ELVDD)駆動部、

180 第2電源(ELVSS)駆動部。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7 a】

【図 7 b】

【図 7 c】

【図 8 a】

【図 8 b】

【図 8 c】

【図 8 d】

【図 8 e】

【図 8 f】

【図 8 g】

【図 8 h】

【図 8 i】

【図 8 j】

【図9】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 1 1 H |

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 4 2 D |

| G 0 9 G | 3/20  | 6 1 2 A |

| G 0 9 G | 3/30  | H       |

| H 0 5 B | 33/14 | A       |

F ターム(参考) 5C380 AA01 AB06 BA11 BA12 BA13 BA19 BA28 BA29 BA38 BA39

BA40 BB02 BB08 BB22 BE03 CA08 CB01 CB16 CB26 CB31

CB32 CC05 CC07 CC26 CC27 CC33 CC41 CC63 CC71 CD023

CD033 CE01 CE08 CE19 DA35 DA44 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2011034039A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2011-02-17 |

| 申请号            | JP2009254936                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2009-11-06 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 三星移动显示的股票会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 李白雲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 李 白 雲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3291 G09G3/003 G09G3/3208 G09G3/3233 G09G3/3258 G09G2300/043 G09G2300/0866<br>G09G2310/063 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/30.J G09G3/20.660.X G09G3/20.622.Q G09G3/20.622.D G09G3/20.621.F G09G3/20.611.H<br>G09G3/20.642.A G09G3/20.642.D G09G3/20.612.A G09G3/30.H H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/CC33 3K107/EE04 3K107/HH04 3K107/HH05 5C080<br>/AA06 5C080/BB05 5C080/DD01 5C080/DD05 5C080/DD08 5C080/DD10 5C080/DD22 5C080/DD23<br>5C080/DD26 5C080/DD27 5C080/EE29 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ03 5C080<br>/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/BA11 5C380/BA12 5C380/BA13<br>5C380/BA19 5C380/BA28 5C380/BA29 5C380/BA38 5C380/BA39 5C380/BA40 5C380/BB02 5C380<br>/BB08 5C380/BB22 5C380/BE03 5C380/CA08 5C380/CB01 5C380/CB16 5C380/CB26 5C380/CB31<br>5C380/CB32 5C380/CC05 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC41 5C380<br>/CC63 5C380/CC71 5C380/CD023 5C380/CD033 5C380/CE01 5C380/CE08 5C380/CE19 5C380<br>/DA35 5C380/DA44 5C380/DA47 |         |            |

| 优先权            | 1020090071280 2009-08-03 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP5684469B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

要解决的问题：提供由同时发光系统驱动的有机电致发光显示装置，并提供一种驱动该装置的方法。ΣSOLUTION：有机电致发光显示装置包括：像素单元130，其像素连接到扫描线，控制线和数据线；控制线驱动器160，用于通过控制线向各个像素提供控制信号；第一电源驱动器170，用于在像素单元的各个像素上施加第一电源电压；第二电源驱动器180，用于在像素单元的各个像素上施加第二电源电压。至少，第一或第二电源驱动器用于在像素单元的各个像素上的一个帧周期期间施加其电平变化的电压。线驱动器和第一和第二电源驱动器同时提供在像素单元中提供的总像素中。 ↴