(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-42664

(P2009-42664A)

(43) 公開日 平成21年2月26日(2009.2.26)

(51) Int.Cl.

**G09G 3/30** (2006.01)

**G09G 3/20** (2006.01)

**H01L 51/50** (2006.01)

F 1

G09G 3/30 J

G09G 3/20 624B

G09G 3/20 670J

HO5B 33/14 A

テーマコード(参考)

3K107

5C080

審査請求 未請求 請求項の数 12 O L (全 18 頁)

(21) 出願番号

特願2007-209984 (P2007-209984)

(22) 出願日

平成19年8月10日 (2007.8.10)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100065385

弁理士 山下 橿平

(74) 代理人 100130029

弁理士 永井 道雄

(72) 発明者 清水 久恵

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 安部 勝美

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ回路、発光表示装置と及びそれらの駆動方法

## (57) 【要約】

【課題】TFTの使用時における電気的ストレスのTFT特性に対する影響を抑制する。

【解決手段】本発明に係る発光表示装置は、有機EL素子(OLED)と有機EL素子を駆動する駆動回路とを有し、駆動回路がゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタTFT1を備えている画素の複数と、薄膜トランジスタTFT1のゲート電位を、ソース電位より高く設定する電圧印加手段とを備える発光表示装置である。電圧印加手段は、閾値電圧が電気的ストレスに対して飽和する領域で薄膜トランジスタを駆動するように、薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加する。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタを有する薄膜トランジスタ回路の駆動方法であって、

前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、該薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加する工程を有することを特徴とする薄膜トランジスタ回路の駆動方法。

**【請求項 2】**

前記電気的ストレスは、前記薄膜トランジスタのゲート電位をソース電位よりも高くすることで印加することを特徴とする請求項 1 に記載の薄膜トランジスタ回路の駆動方法。 10

**【請求項 3】**

前記電気的ストレスを印加する際に、前記薄膜トランジスタのゲート電位をドレイン電位と同じ又はドレイン電位より高くすることを特徴とする請求項 2 に記載の薄膜トランジスタ回路の駆動方法。

**【請求項 4】**

発光素子と前記発光素子を駆動する駆動回路とを有する画素を複数備えた発光表示装置の駆動方法であって、

前記駆動回路はゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタを少なくとも 1 つ備え、

前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、前記発光表示装置の非表示期間において、前記薄膜トランジスタのゲート端子・ソース端子間に電気的ストレスを印加する工程を有することを特徴とする発光表示装置の駆動方法。 20

**【請求項 5】**

前記電気的ストレスは、前記薄膜トランジスタのゲート電位をソース電位よりも高くすることで印加することを特徴とする請求項 4 に記載の発光表示装置の駆動方法。

**【請求項 6】**

ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタと、該電気的ストレスとして該薄膜トランジスタのゲート端子・ソース端子間に電圧を印加する電圧印加手段と、を有する薄膜トランジスタ回路であって、 30

前記電圧印加手段は、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、該薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加することを特徴とする薄膜トランジスタ回路。

**【請求項 7】**

前記電圧印加手段は、前記薄膜トランジスタのゲート電位をソース電位よりも高くすることを特徴とする請求項 6 に記載の薄膜トランジスタ回路。

**【請求項 8】**

請求項 6 又は 7 に記載の薄膜トランジスタはチャネル層として非晶質酸化物半導体を用いていることを特徴とする薄膜トランジスタ回路。 40

**【請求項 9】**

発光素子と該発光素子を駆動する駆動回路とを有する画素を複数備えた発光表示装置であって、

前記駆動回路は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタと、該電気的ストレスとして該薄膜トランジスタのゲート端子・ソース端子間に電圧を印加する電圧印加手段と、を有し、

前記電圧印加手段は、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、前記発光表示装置の非表示期間において、前記薄膜トランジスタのゲート端子・ソース端子間に電気的ストレスを印加することを特徴とする発光表示装置。

**【請求項 10】**

10

20

30

40

50

前記電圧印加手段は、前記薄膜トランジスタのゲート電位をソース電位よりも高くすることを特徴とする請求項9に記載の発光表示装置。

**【請求項11】**

請求項9又は10に記載の発光表示装置において、印加される前記電圧に必要な電力は、前記発光表示装置が備える、あるいは、前記発光表示装置を含むシステムが備えるバッテリにより供給されることを特徴とする発光表示装置。

**【請求項12】**

請求項9乃至11のいずれか一項に記載の発光表示装置の薄膜トランジスタは、チャネル層として非晶質酸化物半導体を用いていることを特徴とする発光表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、薄膜トランジスタ回路、発光表示装置と及びそれらの駆動方法に係わる。本発明の発光表示装置と及びその駆動方法は、特に発光素子と発光素子に電流を供給するための駆動回路で構成される画素をマトリックス状に備えた発光表示装置とその駆動方法に好適に用いられるものである。発光素子としては例えば有機エレクトロルミネッセンス(Electro-Luminescence、以下ELという)素子を用いることができる。

**【背景技術】**

**【0002】**

近年、有機EL素子を発光素子として用いる、有機ELディスプレイの研究開発が進められている。この有機ELディスプレイでは、有機EL素子の寿命を延ばすために、また、高品質な画質を実現するために、各画素に駆動回路を備えたアクティブマトリックス(Active-Matrix、以下AMという)型有機ELディスプレイが一般的である。この駆動回路は、ガラスあるいはプラスチック等の基板上に形成される薄膜トランジスタ(Tin-Film-Transistor、以下TFTという)で構成される。有機ELディスプレイの内、主に基板と駆動回路部分をバックプレーンと呼ぶ。

**【0003】**

有機ELディスプレイ向けバックプレーンのTFTとして、非晶質シリコン(amorphous-Si、以下a-Siという)や多結晶シリコン(poly-crystalline-Si、以下p-Siという)などが検討されている。その他に、最近、新たにアモルファス酸化物半導体(amorphous-oxide-semiconductor、以下AOSという)の薄膜をTFTのチャネル層として用いるTFTが提案されている。AOS材料としては、例えば、インジウム(In)とガリウム(Ga)と亜鉛(Zn)の酸化物(amorphous-In-Ga-Zn-O、以下a-IGZOという)がある。また、亜鉛とインジウムの酸化物(amorphous-Zn-In-O、以下a-ZIOという)がある。非晶質酸化物半導体をチャネル層とするTFTは、a-Si TFTの10倍以上の移動度を備え、また、非晶質性に起因する高い均一性が得られると考えられる。従って、これらのTFTは、ディスプレイ向けバックプレーンのTFTとして有望である。非晶質酸化物半導体をチャネル層とするTFTは例えば、非特許文献1、非特許文献2に記載されている。

**【非特許文献1】Nomura et al., Nature, vol. 432, pp. 488-492, 2004**

**【非特許文献2】Yabuta et al., APL, 89, 112123, 2006**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

AM型有機ELディスプレイで高品質な表示を実現するための課題として、(1)有機EL素子の電圧・輝度特性の経時変化、(2)駆動回路の構成要素であるTFTの特性ば

10

20

30

40

50

らつき、(3)電気的ストレスによるTFTの特性変化、などがある。

【0005】

駆動回路にAOS-TFTを用いる場合、AOS-TFTの均一性が高いこと、AOS-TFTから有機EL素子に供給する電流を制御する駆動回路を採用すること、から2つの課題(1)、(2)は改善できる。

【0006】

一方、AOS-TFTには、電気的ストレスによる特性変化が見られ、上記課題(3)が残されている。

【0007】

本発明の目的は、電気的ストレスによるTFTの特性変化に伴う、表示品質の低下を抑えることにある。 10

【課題を解決するための手段】

【0008】

本発明の薄膜トランジスタ回路の駆動方法は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタを有する薄膜トランジスタ回路の駆動方法であって、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、該薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加する工程を有することを特徴とする。

【0009】

また本発明の発光表示装置の駆動方法は、発光素子と前記発光素子を駆動する駆動回路とを有する画素を複数備えた発光表示装置の駆動方法であって、前記駆動回路はゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタを少なくとも1つ備え、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、前記発光表示装置の非表示期間において、前記薄膜トランジスタのゲート端子・ソース端子間に電気的ストレスを印加する工程を有することを特徴とする。 20

【0010】

また本発明の薄膜トランジスタ回路は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタと、該電気的ストレスとして該薄膜トランジスタのゲート端子・ソース端子間に電圧を印加する電圧印加手段と、を有する薄膜トランジスタ回路であって、前記電圧印加手段は、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、該薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加することを特徴とする。 30

【0011】

また本発明の発光表示装置は、発光素子と該発光素子を駆動する駆動回路とを有する画素を複数備えた発光表示装置であって、前記駆動回路は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタと、該電気的ストレスとして該薄膜トランジスタのゲート端子・ソース端子間に電圧を印加する電圧印加手段とを有し、前記電圧印加手段は、前記閾値電圧が前記電気的ストレスに対して飽和する領域で前記薄膜トランジスタを駆動するように、前記発光表示装置の非表示期間において、前記薄膜トランジスタのゲート端子・ソース端子間に電気的ストレスを印加することを特徴とする。 40

【発明の効果】

【0012】

本発明によれば、薄膜トランジスタの閾値電圧が電気的ストレスに対して飽和する領域で使用することができるため、電気的ストレスによるTFTの特性変化の影響を抑制することができる。

【発明を実施するための最良の形態】

【0013】

10

20

30

40

50

本発明者らは、AOS-TFTの評価を進めることにより以下の知見を得た。

AOS-TFTは、電気的ストレスにより閾値電圧がシフトするという性質を有するが、この閾値電圧のシフトは経時的に飽和する傾向にある。そして閾値電圧のシフトは、ゲート電位が、ソース電位より高い場合に現れる。また、AOS-TFTの閾値電圧のシフトは電気的ストレスを取り除き、一定期間放置することで電気的ストレスを印加する前の状態に戻る性質がある。つまり、本発明に係るAOS-TFTは電気的ストレスを印加すること、電気的ストレスを取り除くことで、AOS-TFTの閾値電圧が可逆的に変化する性質に基づきなされたものである。尚、本発明は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化するTFTに適用することができ、AOS-TFTに限定されるものではない。

10

#### 【0014】

以下、本発明の実施形態として、駆動回路がa-IGZO(Indium Gallium Zinc Oxide)を含有したアモルファス酸化物)をチャネル層とするAOS-TFTを有し、有機EL素子が発光素子である有機ELディスプレイ(発光表示装置となる)について説明する。

#### 【0015】

ただし、本発明はa-IGZO以外のAOSを半導体とする発光表示装置や、有機EL素子以外の発光素子、たとえば無機EL素子を用いた発光表示装置にも適用できる。

また本発明はチャネル層として非晶質酸化物半導体を用いたTFTを有する薄膜トランジスタ回路に広く用いることができる。

20

#### 【0016】

本実施形態の薄膜トランジスタ回路は、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化する薄膜トランジスタと、薄膜トランジスタのゲート端子・ソース端子間に電気的ストレスとして電圧を印加する電圧印加手段とを有する。電圧印加手段は、閾値電圧が電気的ストレスに対して飽和する領域で薄膜トランジスタを駆動するように、薄膜トランジスタの非駆動時にゲート端子・ソース端子間に電気的ストレスを印加する。具体的には、薄膜トランジスタのゲート電位がソース電位よりも高くなるように、ゲート端子・ソース端子間に電圧を印加する。また、電気的ストレスを印加する際に、薄膜トランジスタのゲート電位をドレイン電位と同じ又はドレイン電位よりも高くしてもよい。

#### 【0017】

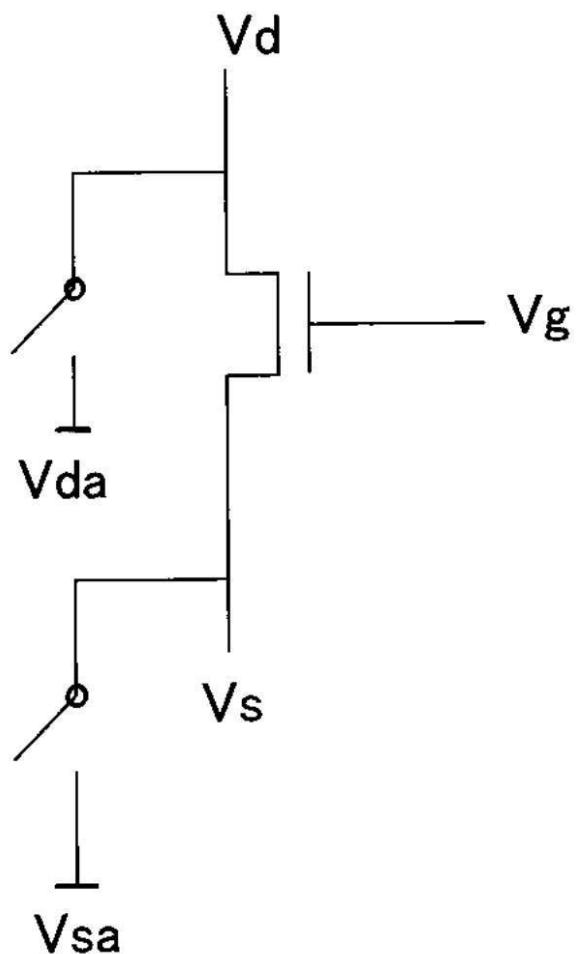

また、薄膜トランジスタのソース端子にゲート電位に対して低くするように電圧を印加してもよい。図9は薄膜トランジスタのドレイン、ソースをゲート電位に対して低くするように電圧を印加する場合を示す回路図である。電圧印加手段は2つのスイッチと2つの電源 $V_{sa}$ 、 $V_{da}$ から構成される。薄膜トランジスタの通常の使用時にはゲートに電圧 $V_g$ 、ドレインに電圧 $V_d$ 、ソースに電圧 $V_s$ を印加する。また、使用時前にはゲートに電圧 $V_g$ を印加した状態でソース側の電源 $V_{sa}$ のスイッチをONし、ソースに電圧 $V_s$ ( $V_g > V_s$ )を印加することで、ゲート電位 $V_g$ をソース電位 $V_{sa}$ よりも高くすることができる。この際、ドレイン側の電源 $V_{da}$ のスイッチをONし、ドレインに電圧 $V_d$ を印加してもよい( $V_g > V_d$ 又は $V_g = V_d$ とする)。

30

#### 【0018】

なお、発光表示装置以外のAOS-TFTを用いたAM型デバイスとしては、例えば、感圧素子を用いた圧力センサや、感光素子を用いた光センサなどにも適用することができ、同様な効果が得られる。

#### 【0019】

また、本発明での非晶質とは、X線回折において明確なピークがみられないことをいう。

#### 【0020】

本実施形態の有機ELディスプレイは、有機EL素子と、有機EL素子を駆動する駆動回路とを有する画素を複数備える。駆動回路内には、有機EL素子に供給する電流を制御する駆動a-IGZO-TFTと、駆動TFTの接続を変更する1つ又は複数のスイッチ

50

と、を少なくとも備える。さらに、表示期間において、駆動用 TFT は、電気的ストレスに対し、閾値電圧が飽和している領域で動作する。本発明において閾値電圧が飽和している領域とは、電気的ストレスに対する薄膜トランジスタの閾値電圧の変化率が小さい領域のことである。ここで、閾値電圧の変化率が小さい領域とは、電気的ストレスに対する閾値電圧の変化が薄膜トランジスタの駆動に影響を与えない領域をいう。

#### 【0021】

本実施形態の有機ELディスプレイにおいて、非発光期間、例えば、ディスプレイのスイッチがオフされている場合に、スイッチを開閉し、駆動用 TFT のゲートに H レベル、ソースとドレインに L レベルを印加する。これにより、駆動用 TFT には、電気的ストレスが印加され続けるため、閾値電圧のシフトが回復することなく、駆動用 TFT は、飽和している領域を維持することができる。なお、電気的ストレスの印加は連続的に電圧を印加しても断続的に（例えばパルスを複数回）印加してもよい。

10

#### 【0022】

この後、再度表示を行うと、駆動用 TFT は、閾値電圧が飽和している領域で動作することになる。従って、本実施形態の有機ELディスプレイでは、TFT の電気的ストレスに対する閾値電圧のシフトを小さくすることが可能であり、表示品質の低下を抑えることができる。

#### 【0023】

さらに、本実施形態の有機ELディスプレイは、ディスプレイ製造後、駆動用 TFT に電圧を印加する動作を、少なくとも使用開始の 48 時間前、より好ましくは 24 時間前まで実施することがより好ましい。本動作を実施することで、駆動用 TFT は、使用開始から、電気的ストレスに対し、閾値電圧が飽和している領域で動作することが可能となる。

20

#### 【0024】

さらに、本実施形態の有機ELディスプレイは、付属のバッテリを備えることがより好ましい。付属のバッテリを備えることで、移動中などの外部電源に接続されていない場合でも、電気的ストレスを与える動作を実施することが可能となる。駆動 TFT に電圧を印加する動作は、電流の供給をほとんど必要としないため、動作中の電力の消費は少ない。

#### 【0025】

##### （実施例 1）

まず、本実施例に使用する a - I G Z O をチャネル層とする TFT の特性を述べる。

30

#### 【0026】

a - I G Z O - TFT の作製法を以下に示す。

#### 【0027】

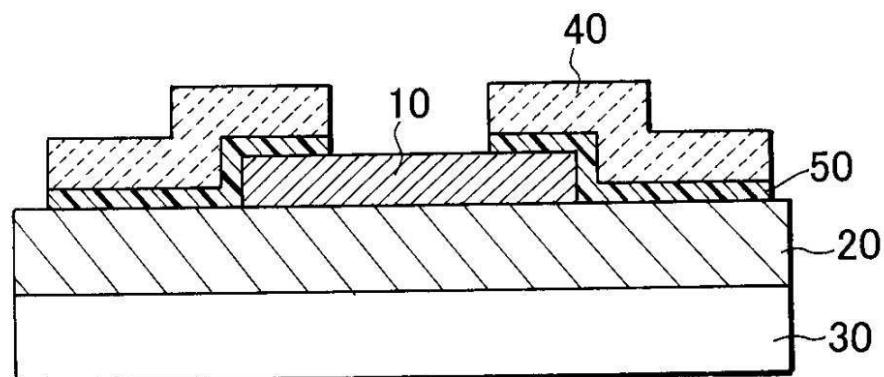

図 1 に示すように、リンあるいはヒ素などの不純物を高濃度に注入した Si 基板 30 上に 100 nm の熱酸化 SiO<sub>2</sub> 絶縁膜 20 を形成する。ここでは、Si 基板 30 の一部がゲート電極を構成する。

#### 【0028】

その後、室温において、多結晶 I G Z O をターゲットとし、スパッタ成膜法により、a - I G Z O 膜 10 を 50 nm 成膜する。次に、フォトリソグラフィ法と希塩酸によるウェットエッティングにより、a - I G Z O 膜 10 をパターニングしてチャネル層を形成する。

40

#### 【0029】

その後、レジストをフォトリソグラフィ法によりパターニングし、EB 蒸着法により、Ti 層 (5 nm) 50、Au 層 (40 nm) 40 を成膜後、リフトオフ法により、Au / Ti のソース、ドレイン電極を形成する。

#### 【0030】

さらに、300 、1 時間のアニールを行う。

#### 【0031】

以上により、図 1 に示すような a - I G Z O - TFT を形成することができる。

#### 【0032】

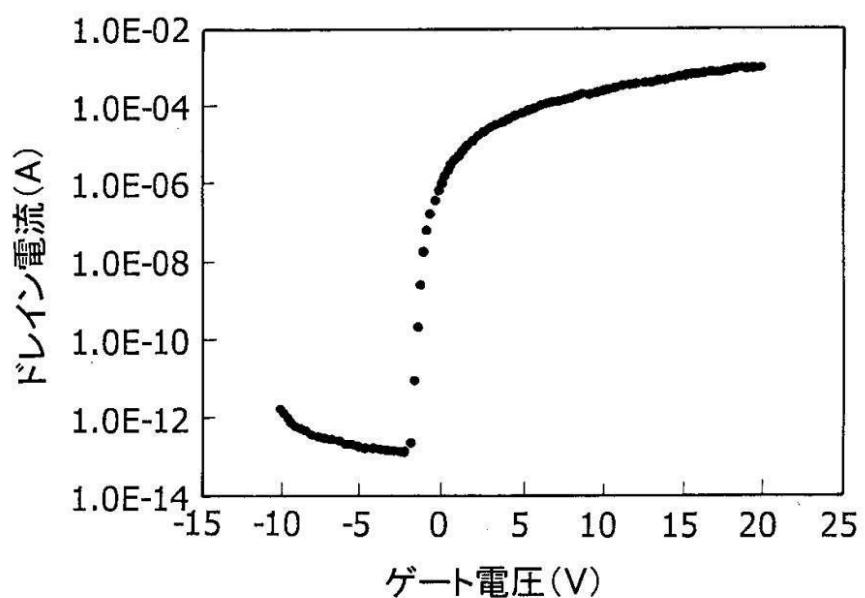

上述の作製法にて得られる a - I G Z O - TFT の電気的特性を示す。

50

## 【0033】

図2は、本TFTのId-Vg特性である。本TFTは、チャネル幅80μm、チャネル長さ10μmで、閾値電圧-0.1V、移動度 $18\text{ cm}^2/\text{Vs}$ であり、移動度が、一般的なa-Si TFTよりも10倍以上大きい。

## 【0034】

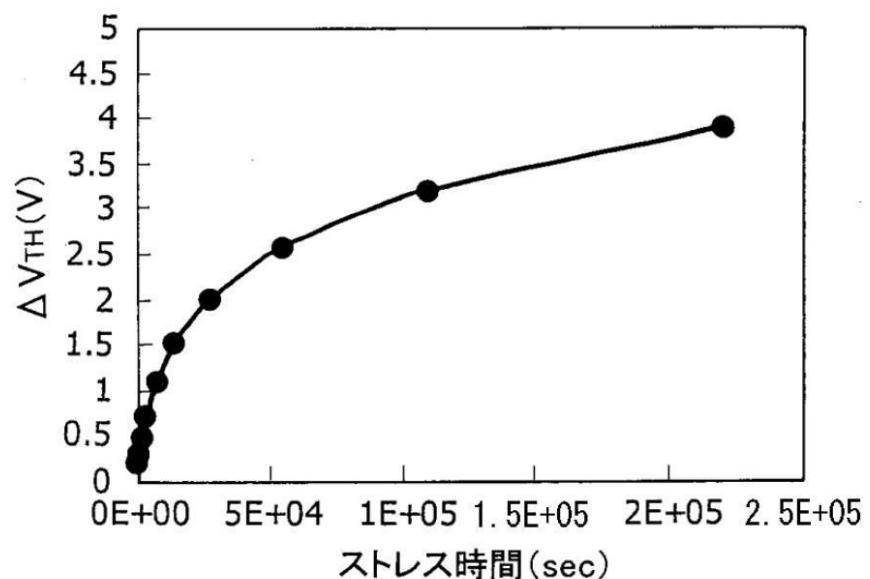

本TFTに、ゲート端子とドレイン端子間を短絡し、ドレイン端子とソース端子間に一定電流 $27\mu\text{A}$ を印加した場合の閾値電圧変化( $V_{TH}$ )を図3に示す。図3の横軸は電気的ストレスを与えている時間を示す。この時、ゲート電位をソース電位より高くする。また、ゲート電位はドレイン電位と同じ電位とする。図3の横軸の表記のたとえば $5\text{ E}+04$ は $5 \times 10^4$ を示す。

10

## 【0035】

この場合、ゲート端子とドレイン端子には一定の電圧を印加する。また、ドレイン端子とソース端子間に一定電流が流れるように、ソース端子に可変の電源を設ける。つまり、ドレイン端子とソース端子間に流れる電流は、ゲート端子とソース端子の電位差により決定されるため、ドレイン端子とソース端子間に流れる電流が一定となるようにソース端子に設けた電源の電圧を調整している。

## 【0036】

また、TFTのゲート端子の電圧はソース端子の電圧よりも大きいことから、TFTには電気的ストレスが印加されている。この場合、TFTの閾値電圧は徐々に高くなる。よって、ドレイン端子とソース端子間に流れる電流を一定にするためには、ゲート端子とソース端子の電位差を大きくする必要がある。そのために、図3のストレス時間が増加するにしたがって、ソース端子に設けた電源の電圧が小さくなるように調整している。

20

## 【0037】

本結果より、20時間(約7万秒)後から60時間の間で閾値変動が約1Vであるのに対し、測定開始から7万秒までの間で約3V変動する。従って、ストレス印加時間がある程度に達すると、電気的ストレスによる閾値電圧の変化率は一定に近づくと考えられる。図3の場合、例えば閾値変動が約1Vである領域(約7万秒以降)が閾値電圧の飽和領域であり、この領域でTFTを駆動する。

## 【0038】

尚、図3は非晶質酸化物半導体を用いた薄膜トランジスタに電気的ストレスを印加した場合の、ストレス時間と閾値電圧の関係の一例である。よって、ストレス時間と閾値電圧の関係は、使用する非晶質酸化物半導体やストレス印加条件(電圧、温度等)により変動する。

30

## 【0039】

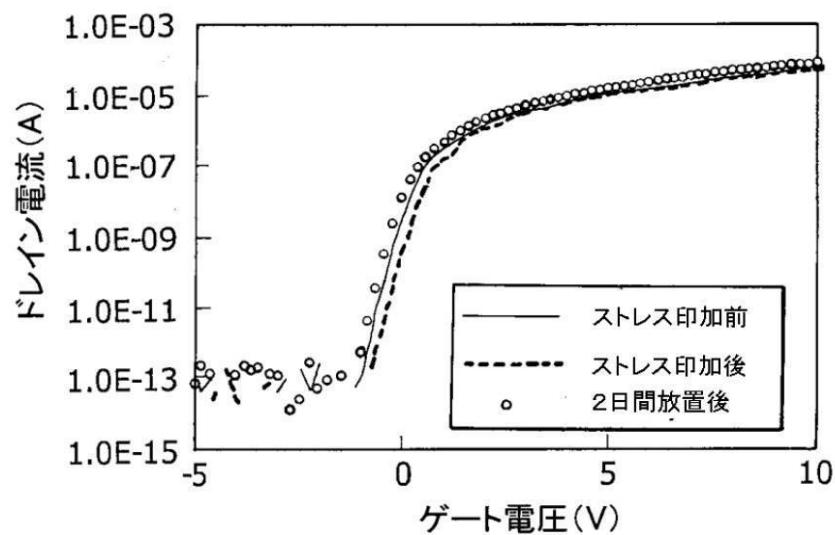

一方、上述の方法で得られる別のa-IGZO-TFT(チャネル幅180μm、チャネル長さ30μm)に、ゲート電圧12V、ドレイン電圧6V、ソース電圧0Vの電気的ストレスを800秒間印加した前後のId-Vg波形を図4に示す。その後、2日間暗所に保管した後の、同一TFTのId-Vg波形を同じく図4に示す。これによると、2日間(48時間)暗所に保管すると、電気的ストレスによる閾値電圧の変化が回復する。つまり、電気的ストレスの影響が残っているのは、48時間以下であることを示している。よって、ゲート端子・ソース端子間に印加される電気的ストレスにより閾値電圧が可逆的に変化することがわかる。

40

## 【0040】

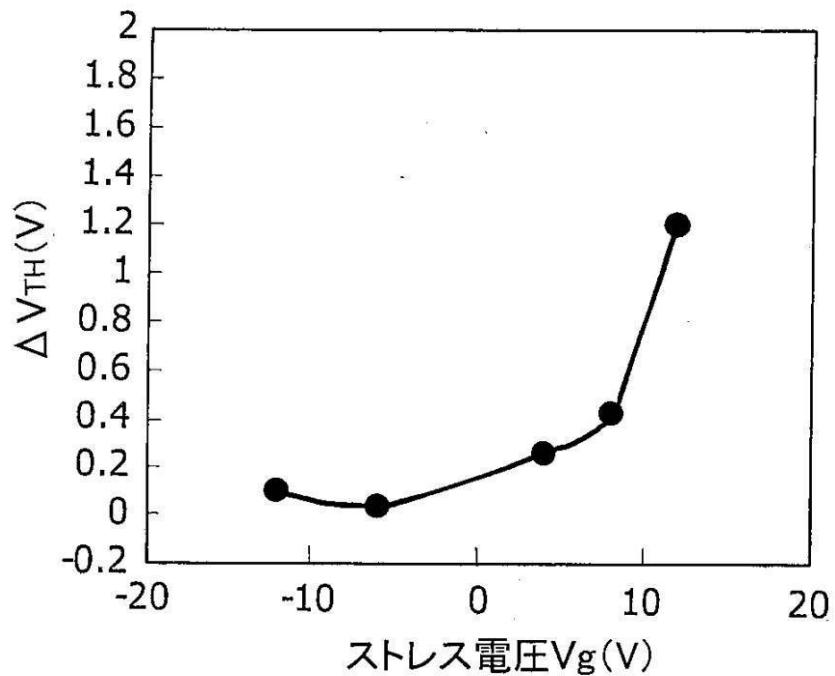

また、上述の方法で得られる別のa-IGZO-TFT(チャネル幅180μm、チャネル長さ30μm)に、ドレイン電圧6V、ソース電圧をGNDに固定して、いくつかのゲート電圧において電気的ストレスを400秒間印加する。ゲート電圧は、-12V、-6V、4V、8V、12Vの5通りである。電気的ストレスによる閾値電圧変化を図5に示す。これより、閾値変化は、ゲート電圧が、ソース電圧よりも低い場合(0V以下)では、ほとんどない。また、ゲート電圧が、ソース電圧、ドレイン電圧よりも高い場合(12V)最も変化が大きくなる。

50

## 【0041】

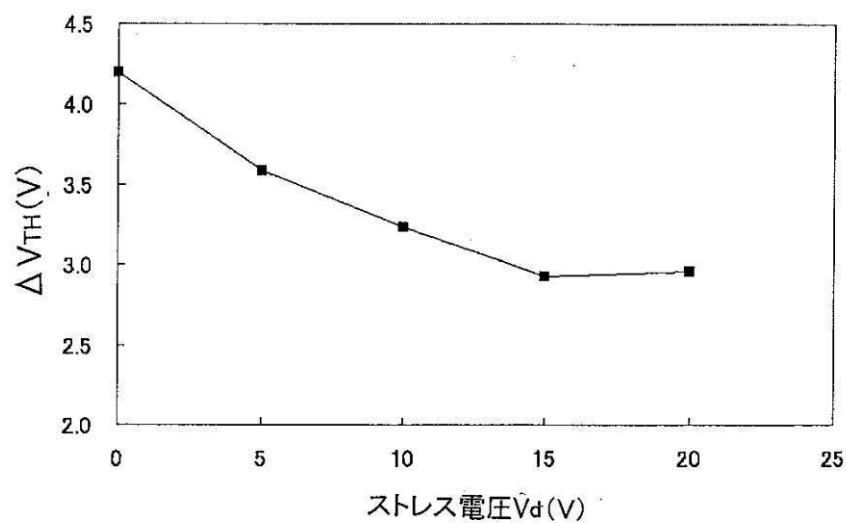

また、a - I G Z O - T F T (チャネル幅 180 μm、チャネル長さ 30 μm) に、ゲート電圧 20 V、ソース電圧を GND に固定して、いくつかのドレイン電圧において電気的ストレスを 400 秒間印加する。ドレイン電圧を変えた場合の閾値電圧変化を図 10 に示す。これより、閾値変化は、ドレイン電圧がゲート電圧 (20 V) に近づくにつれて小さくなることがわかる。

## 【0042】

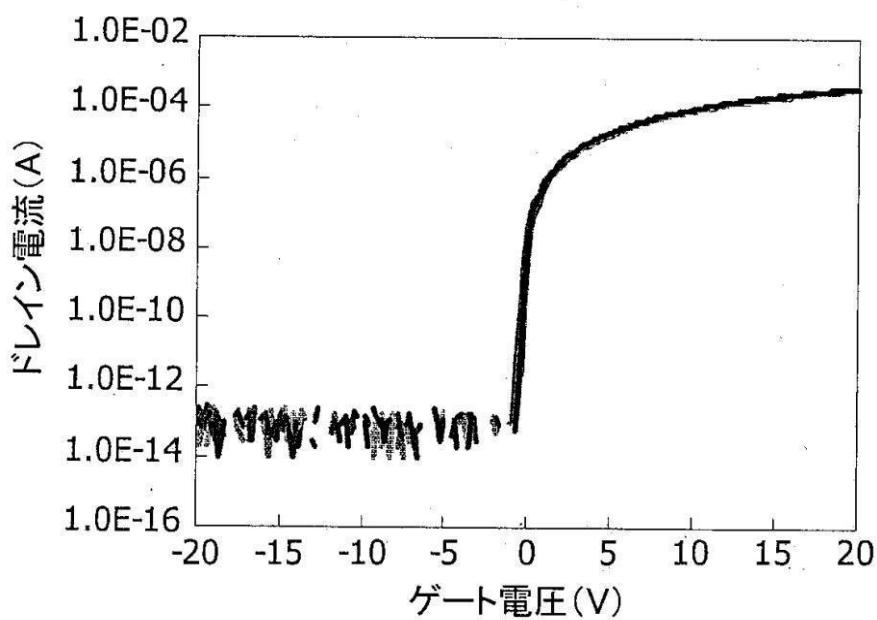

さらに、上述の方法で得られるチャネル幅 180 μm、チャネル長さ 30 μm の a - I G Z O - T F T の Id - Vg 特性を図 6 に示す。図 6 は、8 個の T F T の Id - Vg 特性を重ね書きしたもので、ほぼ 1 つに見えるほど均一性が高い。

10

## 【0043】

以上の特性を示す a - I G Z O - T F T を用いて、以下のような方法により、図 7 に示す有機 E L ディスプレイを作製する。

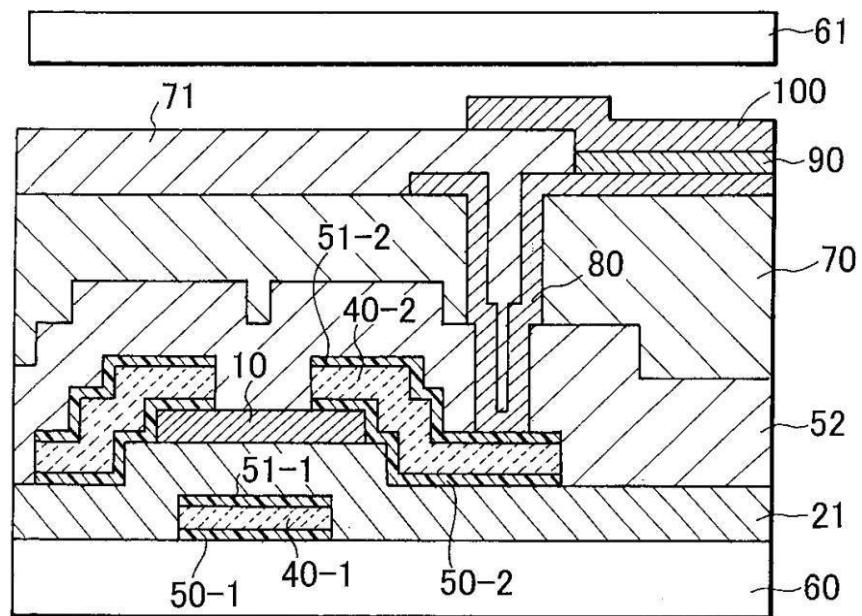

## 【0044】

ガラス基板 60 上に、まず、ゲート線並びにゲート電極として、Ti 層 50-1、Au 層 40-1、Ti 層 51-1 からなる Ti / Au / Ti 積層膜を蒸着法にて成膜する。そのパターン形成は、フォトリソグラフィ法とリフトオフ法を用いる。

## 【0045】

次に、絶縁層 21 として、スパッタ法にて SiO<sub>2</sub> 膜を成膜する。そのパターン形成は、フォトリソグラフィ法と、バッファードフッ酸によるウェットエッチング法にて行う。

20

## 【0046】

続いて、チャネル層として、スパッタ法にて a - I G Z O 膜 10 を形成する。そのパターン形成は、フォトリソグラフィ法と、希塩酸によるウェットエッチング法にて行う。

## 【0047】

続いて、データ配線並びにソース・ドレイン電極として、Ti 层 50-2、Au 层 40-2、Ti 层 51-2 からなる Ti / Au / Ti 積層膜を蒸着法にて成膜する。そのパターン形成は、フォトリソグラフィ法とリフトオフ法を用いる。

## 【0048】

続いて、層間絶縁膜として、SiO<sub>2</sub> 膜 52 を成膜する。そのパターン形成は、フォトリソグラフィ法と、バッファードフッ酸によるウェットエッチング法にて行う。

30

## 【0049】

続いて、平坦化膜として、感光性ポリイミド膜 70 をスピンドルコート法にて成膜する。パターン形成は、感光性ポリイミドを使用しているため、フォトリソグラフィ法にて露光し、剥離することで行うことができる。

## 【0050】

続いて、有機 E L 素子を形成する。

## 【0051】

まず、アノード電極として、スパッタ法にて ITO 膜 80 を成膜する。そのパターン形成は、フォトリソグラフィ法と ITO 剥離液によるウェットエッチング法、あるいは、ドライエッティング法にて行う。

40

## 【0052】

続いて、素子分離膜として、感光性ポリイミド膜 71 をスピンドルコート法にて成膜する。パターン形成は、感光性ポリイミドを使用しているため、フォトリソグラフィ法にて露光し、剥離することで行うことができる。

## 【0053】

続いて、発光層として、蒸着法にて有機膜 90 を成膜する。そのパターン形成は、メタルマスクにて行う。

## 【0054】

続いて、カソード電極 100 として、蒸着法にてアルミ膜を成膜する。そのパターン形成は、メタルマスクにて行う。

50

## 【0055】

最後に、ガラス基板61によりガラス封止を行うことで、有機ELディスプレイを作製することができる（図7）。

## 【0056】

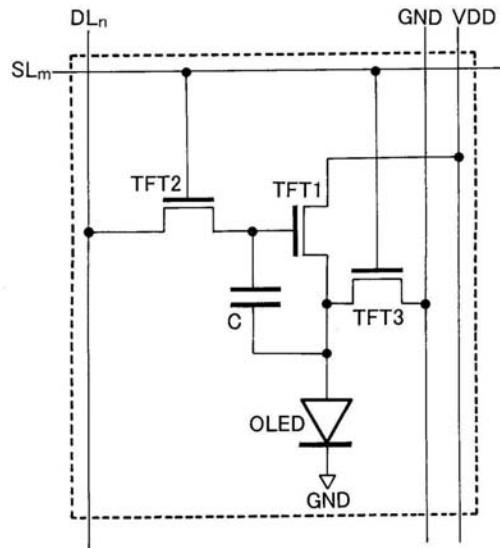

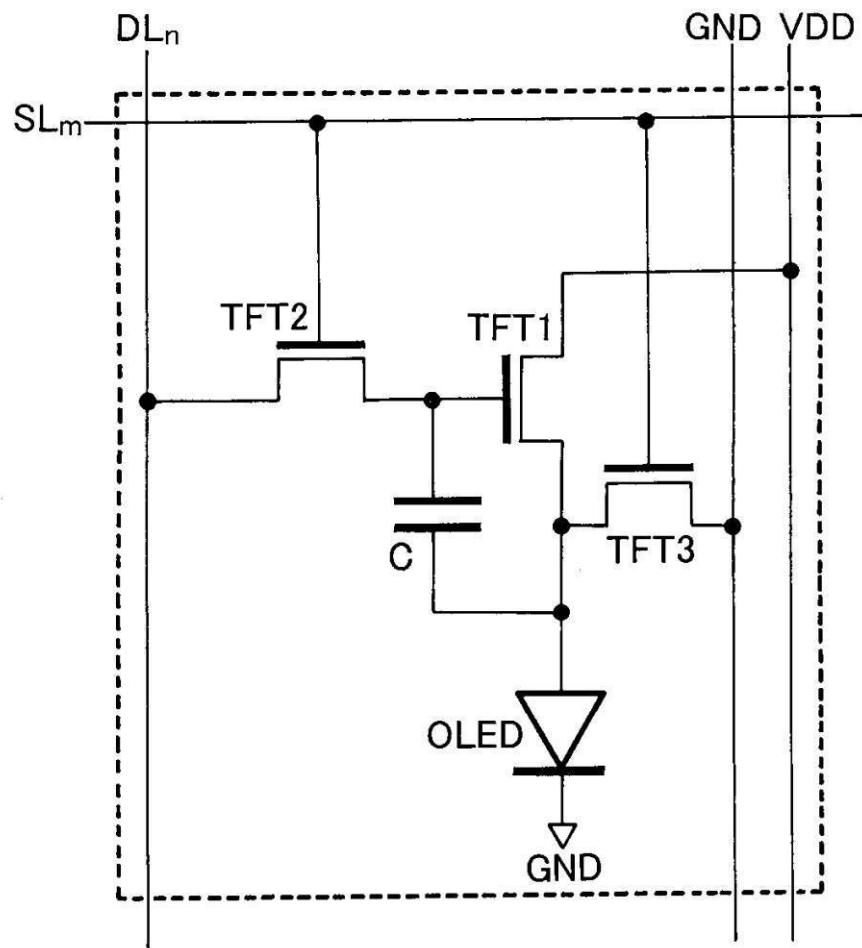

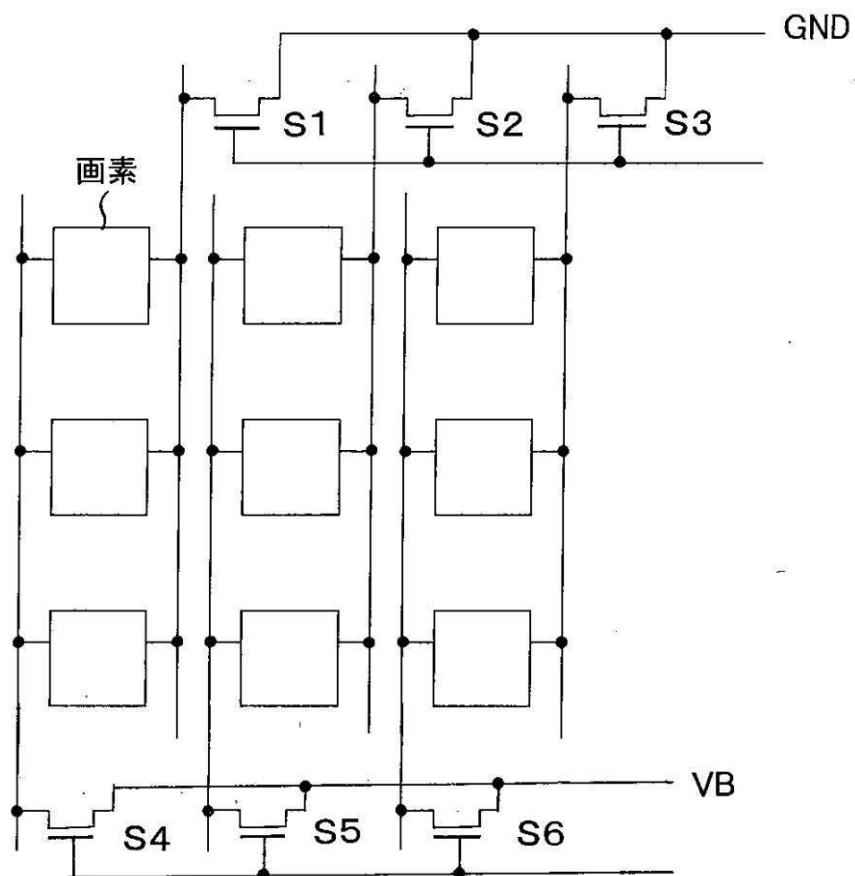

本実施例の有機ELディスプレイの画素回路を図8に示す。画素回路は有機EL素子（OLED）を除く破線で囲まれた回路構成部である。また本実施例の有機ELディスプレイの画素領域部を図11に示す。図11において、S1～S6は電圧印加手段となるスイッチを示し、画素は有機EL素子（OLED）と画素回路とからなる。本実施例において、駆動回路となる画素回路は、3つのa-IGZO-TFT（TFT1、TFT2、TFT3）と、TFT1のゲートとソース間に容量Cにて構成される。TFT1は、有機EL素子（OLED）に供給する電流を制御する駆動TFTであり、TFT2、TFT3は、スイッチとして動作する。10

## 【0057】

まず、本実施例の通常の表示期間における動作を説明する。ここでは、m行n列目の画素の動作を説明するが、他の画素の動作も同様である。通常の表示期間においてスイッチS1～S6はOFF状態となっている。

## 【0058】

走査線SL<sub>m</sub>が選択される期間において、走査線SL<sub>m</sub>にはHレベルが印加され、TFT2、TFT3がONする。その選択期間に、データ線DL<sub>n</sub>からTFT2を経由して、TFT1のゲートに階調電圧が印加され、またGND線からTFT3を経由してTFT1のソースにGND電圧が印加される。その後、次段の走査線が選択されると、走査線SL<sub>m</sub>はLレベルが印加され、TFT2、TFT3がOFFする。この時、TFT1のゲートとソース間の電圧は、容量Cにより、選択期間における階調電圧が保持される。TFT1が飽和領域で動く限り、階調電圧により、TFT1に流れる電流が決定される。よって、本階調電圧の大きさにより、OLEDに供給する電流、つまり、OLEDの輝度を制御することが可能である。20

## 【0059】

上記走査の選択は、ディスプレイ上の全走査線に対し、1秒間に60回行われる。つまり、1フレーム期間は、1/60秒である。

## 【0060】

次に、本実施例の非表示期間における動作を説明する。m行n列目の画素の動作について説明するが、他の画素の動作も同様である。30

## 【0061】

本実施例の有機ELディスプレイは、非表示期間の少なくとも一部において、全走査線SL<sub>m</sub>、DL<sub>n</sub>が選択され、TFT2、TFT3は、ONとなる。また、データ線DL<sub>n</sub>にはスイッチS4～S6をONして、GND電圧よりも高い一定電圧VBが印加される。さらに、TFT1のドレイン電圧、つまり、VDDの電圧を、スイッチS1～S3をONしてGND電圧に設定する。

## 【0062】

この時、OLEDには電流が流れず、その一方で、電気的ストレスがTFT1に印加され続ける。このため、TFT1は、電気的ストレスに対する閾値電圧の値が飽和している状態で保持される。40

## 【0063】

以上の動作を実施することで、本実施例の有機ELディスプレイは、a-IGZO-TFTを、電気的ストレスに対する閾値電圧の飽和領域で動作させることが可能となる。この結果、電気的ストレスに起因する画質の低下を抑えることができる。

## 【0064】

尚、TFT2及びTFT3はスイッチとして動作するので、閾値電圧がシフトしてもTFTの駆動電圧を予め所定の値に設定すれば駆動することができる。よって、TFT2及びTFT3については必ずしも電気的ストレスを印加する必要はないが、TFTの駆動電50

圧を一定にしたい場合、つまり閾値電圧の変動の影響を抑えたい場合は、TFT1と同様に電気的ストレスを印加してもよい。

#### (実施例2)

本実施例の有機ELディスプレイは、実施例1の有機ELディスプレイにおいて、さらにバッテリを備え、外部から電源を供給することなく、実施例1に示した非表示期間の少なくとも一部において、電気的ストレスを与える動作を実施できるようにしたものである。

#### 【0065】

製品完成後に、電気的ストレスを印加することで、TFT1を電気的ストレスに対する閾値電圧の飽和領域で動作するようになる。さらに、バッテリを用いて、上述の非表示状態の動作を行うことで、使用開始前まで、TFT1は、電気的ストレスに対する変化が飽和する領域で動作する状態に保つことが可能となる。

#### 【0066】

さらに、バッテリを備えることで、有機ELディスプレイを電源から切り離し、移動させるような場合でも、TFT1は、電気的ストレスに対する変化が飽和する領域で動作する状態を保つことが可能となる。

#### 【0067】

ただし、上述の特性の回復は、48時間以上経過すると起こるため、上記動作は、使用時から見て、48時間以上間隔を空けないようにすることが望ましい。より好ましくは、24時間以内にする。

#### 【0068】

また、上述の非表示状態の動作において、リーク電流以外に電流が流れる経路がないため、バッテリから、上述の非表示状態の動作を行うために供給される電力は少ない。従って、本実施例の有機ELディスプレイを、ノートPCや携帯電話などバッテリを備えている機器に搭載する場合、上述の非表示状態の動作を行うことによるバッテリの電力供給可能期間に対する影響はほとんどない。

#### 【0069】

また、製品完成後の電気的ストレス印加の際には、電気的ストレスとともに、温度を加えることでTFT1が電気的ストレスに対し飽和する領域に達する時間を短縮できる。

#### 【0070】

以上のように、本実施例では、a-IGZO-TFTを構成要素とする駆動回路を備える有機ELディスプレイにおいて、電気的ストレスによる表示画質の低下を抑えることが可能である。

#### 【0071】

さらに、実施例1及び2は、a-IGZOをチャネル層とするTFTのみに関してのみ記述されているが、同様の電気的ストレスに対する特性を有するAOS-TFTにおいても本発明を適用することが可能である。

#### 【0072】

また、より多階調の表示装置を実現する場合に、閾値補正機能付きの駆動回路や、カレントミラー構成の駆動回路を採用しても、上述の通り非表示期間に駆動TFTに電圧を印加することで、同様な効果を得ることができる。

#### 【0073】

また、実施例2において、印加電圧に必要な電力は、発光表示装置が備える、あるいは、表示装置を含むシステムが備えるバッテリより供給され、発光表示装置外部の電源より電力を供給されること無く、非発光期間に電圧を印加する。これにより、外部電源がなくとも電圧を印加することができる。

#### 【産業上の利用可能性】

#### 【0074】

本発明は、発光素子の駆動回路がAOSをチャネル層とするAOS-TFTを有する発光装置に適用される。また発光表示装置以外のAOS-TFTを用いたAM型デバイス、

10

20

30

40

50

例えば、感圧素子を用いた圧力センサや、感光素子を用いた光センサなどにも適用することができる。

【図面の簡単な説明】

【0075】

【図1】本発明の実施例1のa-IGZO TFTの構成1(Si基板上)を示す図である。

【図2】本発明の実施例1のa-IGZO TFTの構成1のId-Vg特性を示す図である。

【図3】本発明の実施例1のa-IGZO TFTの構成1のストレスによる閾値変化を示す図である。

【図4】本発明の実施例1のa-IGZO TFTの構成1の変化からの回復特性を示す図である。

【図5】本発明の実施例1のa-IGZO TFTの構成1のストレス変化のゲート電圧依存を示す図である。

【図6】本発明の実施例1のa-IGZO TFTの構成1の複数のId-Vg特性を示す図である。

【図7】本発明の実施例1のa-IGZO TFTの構成2(ガラス基板上)を示す図である。

【図8】本発明の実施例1の画素回路を示す図である。

【図9】薄膜トランジスタのドレイン、ソースをゲート電位に対して低くするように電圧を印加する場合を示す回路図である。

【図10】ドレイン電圧を変えた場合の閾値電圧変化を示す図である。

【図11】本実施例の有機ELディスプレイの画素領域部を示す図である。

【符号の説明】

【0076】

OLED 有機EL素子

TFT1 駆動TFT

TFT2, TFT3 スイッチングTFT

VDD 電源線

GND GND線

S<sub>L</sub><sub>m</sub> (m行目の)走査線

D<sub>L</sub><sub>n</sub> (n列目の)データ線

C 容量

10 a-IGZOチャネル層

20 热酸化シリコンゲート絶縁層

21 スパッタ成膜酸化シリコンゲート絶縁層

30 低抵抗シリコン基板(ゲート電極)

40 Au電極層

50 Ti電極層

60 ガラス基板

70 ポリイミド(PI)

80 ITO(アノード)電極層

90 OLED層

100 Al / CsCO<sub>3</sub>(カソード)電極層

10

20

30

40

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図 6】

【図 7】

【図8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(72)発明者 林 享

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

Fターム(参考) 3K107 AA01 BB01 EE03 HH04 HH05

5C080 AA06 BB05 DD29 EE29 FF11 JJ03 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管电路，发光显示装置及其驱动方法                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2009042664A</a>                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2009-02-26 |

| 申请号            | JP2007209984                                                                                                                                                                                                                                                                                                         | 申请日     | 2007-08-10 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 清水久惠<br>安部勝美<br>林享                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 清水 久惠<br>安部 勝美<br>林 享                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                          |         |            |

| CPC分类号         | G09G3/3258 G09G3/3233 G09G2300/0417 G09G2300/0842 G09G2320/0233 G09G2320/043                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.670.J H05B33/14.A G09G3/20.670.K G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD29 5C080/EE29 5C080/FF11 5C080/JJ03 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AA02 5C380/AB06 5C380/AB22 5C380/BD10 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CC27 5C380/CC33 5C380/CC52 5C380/CC62 5C380/CD013 5C380/CE02 5C380/DA06 |         |            |

| 代理人(译)         | 永井道雄                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | <a href="#">JP5414161B2</a>                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

要解决的问题：在使用TFT时抑制电应力对TFT特性的影响。解决方案：发光显示装置包括有机EL装置(OLED)和用于驱动有机EL装置的驱动电路。驱动电路包括多个像素，其具有薄膜晶体管TFT 1，其阈值电压可通过施加在栅极端子和源极端子之间的电应力可逆地改变，以及电压施加装置，用于设定薄膜晶体管的栅极电位TFT 1高于源极电位。当未驱动薄膜晶体管时，电压施加装置在栅极端子和源极端子之间施加电应力，使得薄膜晶体管在阈值电压相对于电应力饱和的区域中被驱动。