(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-40326

(P2008-40326A)

(43) 公開日 平成20年2月21日(2008.2.21)

| (51) Int.Cl.        | F 1               | テーマコード (参考) |

|---------------------|-------------------|-------------|

| G09G 3/30 (2006.01) | G09G 3/30 J 5C080 |             |

| G09G 3/20 (2006.01) | G09G 3/20 624B    |             |

|                     | G09G 3/20 622A    |             |

|                     | G09G 3/20 622G    |             |

|                     | G09G 3/20 642E    |             |

審査請求 未請求 請求項の数 14 O L (全 26 頁) 最終頁に続く

|           |                              |          |                                                                  |

|-----------|------------------------------|----------|------------------------------------------------------------------|

| (21) 出願番号 | 特願2006-216956 (P2006-216956) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号                    |

| (22) 出願日  | 平成18年8月9日 (2006.8.9)         | (74) 代理人 | 100090479<br>弁理士 井上 一                                            |

|           |                              | (74) 代理人 | 100104710<br>弁理士 竹腰 昇                                            |

|           |                              | (74) 代理人 | 100124626<br>弁理士 榎並 智和                                           |

|           |                              | (74) 代理人 | 100124682<br>弁理士 黒田 泰                                            |

|           |                              | (72) 発明者 | 北澤 幸行<br>長野県諏訪市大和3丁目3番5号 セイコ<br>ーエプソン株式会社内                       |

|           |                              |          | F ターム (参考) 5C080 AA06 BB05 DD01 EE29 JJ02<br>JJ03 JJ04 JJ05 JJ06 |

(54) 【発明の名称】アクティブマトリクス型発光装置、電子機器およびアクティブマトリクス型発光装置の画素駆動方法

## (57) 【要約】

【課題】 アクティブマトリクス型発光装置における黒表示時のコントラストの低下を、回路構成を複雑化せることなく効果的に抑制すること。

【解決手段】 走査線ドライバ(200)における、発光制御 TFT(M14)を駆動するための走査線(W2)に関する電流駆動能力を、他の制御トランジスタ(M11, M12)を駆動するための走査線(W1)に関する電流駆動能力に比べて低く設定する。これによって、黒表示時における、いわゆる黒浮き(すなわち、発光制御 TFT(M14)のゲート・ソース間の寄生容量を介して発光制御信号(GEL)の電圧変化成分が有機EL素子(OLED)側に漏れ込み、ピーク値が大きい瞬時電流(カップリング電流)が流れ、黒表示時における黒レベルが上昇する現象)が抑制される。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

発光素子と、前記発光素子を駆動する駆動トランジスタと、前記駆動トランジスタに一端が接続され、書き込みデータに応じた電荷を蓄積する保持コンデンサと、前記保持コンデンサへのデータ書き込みに関する動作を制御する、少なくとも一つの制御トランジスタと、前記発光素子と前記駆動トランジスタとの間に介在する発光制御トランジスタと、を備える画素回路と、

前記制御トランジスタのオン／オフを制御する第1の走査線ならびに前記発光制御トランジスタのオン／オフを制御する第2の走査線と、

書き込みデータを前記画素回路に伝達するデータ線と、

前記第1および第2の走査線を駆動すると共に、前記第2の走査線に関する電流駆動能力が、前記第1の走査線に関する電流駆動能力に比べて低く設定されている走査線駆動回路と、

を有することを特徴とするアクティブマトリクス型発光装置。

**【請求項 2】**

請求項1記載のアクティブマトリクス型発光装置であって、

前記走査線駆動回路は、前記第1および第2の走査線を各々駆動する第1および第2の出力バッファを備え、

前記第2の出力バッファを構成するトランジスタのサイズは、前記第1の出力バッファを構成するトランジスタのサイズよりも小さいことを特徴とするアクティブマトリクス型発光装置。

**【請求項 3】**

請求項2記載のアクティブマトリクス型発光装置であって、

前記第1および第2の出力バッファを構成するトランジスタは絶縁ゲート型電界効果トランジスタであり、前記第2の出力バッファを構成するトランジスタのチャネルコンダクタンス(W/L)は、前記第1の出力バッファを構成するトランジスタのチャネルコンダクタンス(W/L)よりも小さいことを特徴とするアクティブマトリクス型発光装置。

**【請求項 4】**

請求項1記載のアクティブマトリクス型発光装置であって、

前記走査線駆動回路は、前記第1および第2の走査線を各々駆動する第1および第2の出力バッファを備え、

前記第2の出力バッファの出力端には、前記第2の走査線に関する電流駆動能力を、前記第1の走査線に関する電流駆動能力に比べて低くするための抵抗が接続されていることを特徴とするアクティブマトリクス型発光装置。

**【請求項 5】**

請求項1記載のアクティブマトリクス型発光装置であって、

前記駆動トランジスタは絶縁ゲート型電界効果トランジスタであり、

前記第2の走査線の電位を変化させて前記発光制御トランジスタをオフからオンに移行させる際に、前記発光制御トランジスタのゲート・ソース間の寄生容量を経由して、前記第2の走査線の電位の変化成分が前記発光素子側に洩れ込むことによって生じるカップリング電流の電流量が、前記第2の走査線に関する電流駆動能力を低下させることによって低減され、これによって、黒表示時における前記発光素子の不要な発光が抑制されることを特徴とするアクティブマトリクス型発光装置。

**【請求項 6】**

請求項1記載のアクティブマトリクス型発光装置であって、

前記発光制御トランジスタと発光素子とは、基板上において近接して配置されていることを特徴とするアクティブマトリクス型発光装置。

**【請求項 7】**

請求項1記載のアクティブマトリクス型発光装置であって、

前記第2の走査線の電位の変化が生じてから、その変化が収束するまでの時間が、1水

10

20

30

40

50

平同期期間（1H）以上となるように、前記第2の走査線に関する電流駆動能力が調整されることを特徴とするアクティブマトリクス型発光装置。

【請求項8】

請求項1記載のアクティブマトリクス型発光装置であって、

前記第1の走査線を介して駆動される前記制御トランジスタは、前記保持コンデンサと前記駆動トランジスタの共通接続点と前記データ線との間に接続されたスイッチングトランジスタであり、かつ、このスイッチングトランジスタは、1水平同期期間（1H）内において、少なくとも1回オン／オフ動作を行い、

また、前記第2の走査線を介して駆動される前記発光制御トランジスタは、1垂直同期期間（1V）内の所定期間において、少なくとも1回オン／オフ動作を行うことを特徴とするアクティブマトリクス型発光装置。 10

【請求項9】

請求項1記載のアクティブマトリクス型発光装置であって、

前記画素回路は、前記データ線を経由して流れる電流によって、前記保持コンデンサに蓄積される電荷を制御して前記発光素子の発光階調を調整する電流プログラミング方式の画素回路、あるいは、前記データ線を経由して伝達される電圧信号によって、前記保持コンデンサに蓄積される電荷を制御して前記発光素子の発光階調を調整する電圧プログラミング方式の画素回路であることを特徴とするアクティブマトリクス型発光装置。

【請求項10】

請求項1記載のアクティブマトリクス型発光装置であって、

前記画素回路は、前記駆動トランジスタとしての、絶縁ゲート型電界効果トランジスタのしきい値電圧の変動を補償するための回路構成を備える電圧プログラミング方式の画素回路であり、

前記第1の走査線を介して駆動される前記制御トランジスタは、データ線に一端が接続され、他端がカッピングコンデンサの一端に接続された書込みトランジスタであり、また、前記カッピングコンデンサの他端は、前記保持コンデンサと前記駆動トランジスタの共通接続点に接続されていることを特徴とするアクティブマトリクス型発光装置。 20

【請求項11】

請求項1～請求項10のいずれか記載のアクティブマトリクス型発光装置であって、

前記発光素子は、有機エレクトロルミネッセンス素子（有機EL素子）であることを特徴とするアクティブマトリクス型発光装置。 30

【請求項12】

請求項1～請求項11のいずれか記載のアクティブマトリクス型発光装置を搭載する電子機器。

【請求項13】

請求項12記載の電子機器であって、

前記アクティブマトリクス型発光装置は、表示装置として、あるいは、光源として使用されることを特徴とする電子機器。

【請求項14】

発光素子と、前記発光素子を駆動する駆動トランジスタと、前記駆動トランジスタに一端が接続され、書込みデータに応じた電荷を蓄積する保持コンデンサと、前記保持コンデンサへのデータ書込みに関係する動作を制御する、少なくとも一つの制御トランジスタと、前記発光素子と前記駆動トランジスタとの間に介在する発光制御トランジスタと、を備える画素回路における前記制御トランジスタならびに前記発光制御トランジスタを各々、第1および第2の走査線を経由してオン／オフ駆動する、アクティブマトリクス型発光装置における画素駆動方法であって、 40

前記第2の走査線に関する電流駆動能力を、前記第1の走査線に関する電流駆動能力に比べて低く設定し、これによって、前記第2の走査線の電位を変化させて前記発光制御トランジスタをオフからオンに移行させる際に、前記発光制御トランジスタのゲート・ソース間の寄生容量を経由して、前記第2の走査線の電位の変化成分が前記発光素子側に洩れ

込むことによって生じるカップリング電流を低減し、黒表示時における前記発光素子の不要な発光を抑制することを特徴とする、アクティブマトリクス型発光装置における画素駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクティブマトリクス型発光装置およびアクティブマトリクス型発光装置の画素駆動方法に関する。特に、エレクトロルミネッセンス(EL)素子のような自己発光素子を備える画素の黒表示時における黒浮き(黒表示時においても不要な電流が流れ、これによって発光素子がわずかに発光して黒レベルが上昇し、コントラストが低下する現象)を効果的に防止する技術に関する。10

【背景技術】

【0002】

近年、高効率・薄型・軽量・低視野角依存性等の特徴を有するエレクトロルミネッセンス(EL)素子が注目され、このEL素子を用いたディスプレイの開発が活発に行われている。EL素子は蛍光性化合物に電場を加えることで発光する自己発光型の素子であり、硫化亜鉛などの無機化合物を発光物質層として用いた無機EL素子と、ジアミン類などの有機化合物を発光物質層として用いた有機EL素子とに大別される。

【0003】

有機EL素子はカラー化が容易で、無機EL素子よりはるかに低電圧の直流電流で動作するなどの利点から、近年特に携帯端末の表示装置などへの応用が期待されている。20

【0004】

有機EL素子は、ホール注入電極から発光物質層に向けてホール(正孔)を注入とともに電子注入電極から発光物質層に向けて電子を注入し、注入されたホールと電子が再結合せしめられることにより、発光中心を構成する有機分子を励起し、そしてこの励起された有機分子が基底状態に戻るときに、蛍光を発するよう構成されている。従って、有機EL素子は発光物質層を構成する蛍光物質を選択することにより発光色を変化させることができる。

【0005】

有機EL素子では、陽極側の透明電極に正の電圧が印加され、一方、陰極の金属電極に負の電圧が印加されると電荷が蓄積され、電圧値が素子固有の障壁電圧または発光閾値電圧を越えると電流が流れはじめる。そして、その直流電流値にほぼ比例した強度の発光が生じる。つまり、有機EL素子は、レーザダイオードや発光ダイオード等と同様に、電流駆動型の自己発光素子といえる。30

【0006】

有機EL表示装置の駆動方式は、パッシブマトリクス方式とアクティブマトリクス方式に大別される。ただし、パッシブマトリクス駆動方式では、表示画素数が制限され、寿命や消費電力の点でも制限がある。したがって、有機EL表示装置の駆動方式として、大面積・高精細度のディスプレイパネルを実現するうえで有利なアクティブマトリクス型の駆動方式が用いられることが多くなり、アクティブマトリクス駆動方式のディスプレイの開発が盛んに行われている。40

【0007】

アクティブマトリクス駆動方式の表示装置では、一方の電極がドットマトリクス状にパターニングされ、各電極上に形成された有機EL素子を独立して駆動するために、個々の電極毎に、発光制御トランジスタとしてのポリシリコン薄膜トランジスタ(ポリシリコンTFT)が形成される。また、有機EL素子を駆動するための駆動トランジスタや、データ書き込みに関連した動作を制御する制御トランジスタとしても、ポリシリコンTFTが使用される。

【0008】

以下の説明では、ポリシリコンTFTを、単に「TFT」という場合がある。但し、单50

に「TFT」という場合には、その材料はポリシリコンに限定されるものではなく、例えば、アモルファスシリコンTFTであってもよい。

#### 【0009】

有機EL素子の発光階調は、TFTの特性に大きな影響を受ける。下記の特許文献1では、走査線を介して駆動されるTFTに光が照射されたときに生じるリーク電流（光リーク電流）によって、保持コンデンサに蓄積されている電荷が変動してしまう点に着目し、ダイオードを挿入することによって、その電荷の変動を抑制している。

#### 【特許文献1】特開2006-17966号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

特許文献1では、TFTの光リーク電流を問題としているが、TFTにおいて生じるリーク電流としては、オフ時のリーク電流（暗電流）ならびに回路動作に起因して生じるリーク電流もあり、これらを総合的に検討することが重要である。

#### 【0011】

本発明の発明者は、アクティブマトリクス型発光装置の黒表示時（つまり、発光制御トランジスタはオンしているが、駆動トランジスタからは電流が供給されず、結果的に発光素子は非発光状態を維持する状態）において、わずかながら不要な電流が流れ、これによって発光素子が発光して黒レベルが上昇し、コントラストが低下する現象（黒浮き）が生じる場合があることに注目し、その原因について総合的に検討した。

#### 【0012】

その結果、特に、回路動作に起因して生じる、瞬時の大きなリーク電流が黒浮きの発生に大きく関与していることがわかった。

#### 【0013】

すなわち、走査線の電位を変化させて発光制御トランジスタをオフからオンに移行させる際に、その発光制御トランジスタのゲート・ソース間の寄生容量を経由して、走査線の電位の変化成分が発光素子側に洩れ込み、瞬時に大きな電流が流れる。以下の説明では、この電流を「カップリング電流」という。「カップリング電流」は、発光制御トランジスタの寄生容量を介して発光素子にカップリング（結合）する、過渡的なパルスに起因する電流である。

#### 【0014】

このカップリング電流が流れると、黒表示時であるにもかかわらず、発光素子が瞬時に発光して黒レベルが上昇し、コントラストが低下する。この現象は、人の視覚に印象づけられるため、表示画像の画質が低下する。

#### 【0015】

すなわち、従来問題となっていたTFTの物理的な特性に基づくリーク電流ではなく、回路的な要因によって生じるリーク電流が、黒表示時のコントラストの低下に直結する重要な要因であることが、本発明の発明者の検討によって明らかとなった。

#### 【0016】

本発明はこのような考察に基づいてなされたものであり、その目的は、アクティブマトリクス型発光装置における黒表示時のコントラストの低下を、回路構成を複雑化させることなく効果的に抑制することにある。

#### 【課題を解決するための手段】

#### 【0017】

(1) 本発明のアクティブマトリクス型発光装置は、発光素子と、前記発光素子を駆動する駆動トランジスタと、前記駆動トランジスタに一端が接続され、書き込みデータに応じた電荷を蓄積する保持コンデンサと、前記保持コンデンサへのデータ書き込みに係する動作を制御する、少なくとも一つの制御トランジスタと、前記発光素子と前記駆動トランジスタとの間に介在する発光制御トランジスタと、を備える画素回路と、前記制御トランジスタのオン／オフを制御する第1の走査線ならびに前記発光制御トランジスタのオン／オフ

10

20

30

40

50

を制御する第2の走査線と、書き込みデータを前記画素回路に伝達するデータ線と、前記第1および第2の走査線を駆動すると共に、前記第2の走査線に関する電流駆動能力が、前記第1の走査線に関する電流駆動能力に比べて低く設定されている走査線駆動回路と、を有する

第2の走査線に関する電流駆動能力を意図的に低下させることによって、発光制御トランジスタの駆動パルスの立ち上がり波形を鈍らせ（すなわち、時間に対する電圧の変化を緩やかとし）、これによって、発光制御トランジスタの寄生容量を介して、大きなピーク電流値をもつ瞬時電流（カップリング電流）が流れるのを抑制することができる。したがって、黒表示時における黒レベルの上昇（黒浮き）が低減され、コントラスト低下による表示画像の画質の低下の心配がなくなる。また、走査線駆動回路における第2の走査線に関する駆動能力を調整することは容易であり、特別の回路を設ける必要がないため、回路構成が複雑化することなく、実現が容易である。

10

## 【0018】

(2) 本発明のアクティブマトリクス型発光装置の一態様では、前記走査線駆動回路は、前記第1および第2の走査線を各々駆動する第1および第2の出力バッファを備え、

前記第2の出力バッファを構成するトランジスタのサイズは、前記第1の出力バッファを構成するトランジスタのサイズよりも小さい。

## 【0019】

出力段のバッファを構成するトランジスタサイズを調整することによって、第2の走査線に関する駆動能力を、第1の走査線に関する駆動能力よりも意図的に低く設定するものである。ここで、「トランジスタのサイズの大小」は、「1個のトランジスタのサイズを比較した場合の大小」だけにとどまらない。例えば、第1の走査線を駆動する出力バッファにおいては、単位サイズの複数のトランジスタが並列に接続され、これに対して、第2の走査線を駆動する出力バッファでは、単位サイズのトランジスタを1個だけ使用しているような場合も含まれる（並列接続のトランジスタを一つのトランジスタと考えれば、トランジスタのサイズが異なる、と見ることができるからである）。

20

## 【0020】

(3) 本発明のアクティブマトリクス型発光装置の他の態様では、前記第1および第2の出力バッファを構成するトランジスタは絶縁ゲート型電界効果トランジスタであり、前記第2の出力バッファを構成するトランジスタのチャネルコンダクタンス(W/L)は、前記第1の出力バッファを構成するトランジスタのチャネルコンダクタンス(W/L)よりも小さい。

30

## 【0021】

出力バッファを構成するMOSトランジスタのチャネルコンダクタンス(ゲート幅W/ゲート長L)を調整することによって、第2の走査線に関する電流駆動能力を、第1の走査線に関する駆動能力に比べて意図的に低下させるものである。

## 【0022】

(4) 本発明のアクティブマトリクス型発光装置の他の態様では、前記走査線駆動回路は、前記第1および第2の走査線を各々駆動する第1および第2の出力バッファを備え、前記第2の出力バッファの出力端には、前記第2の走査線に関する電流駆動能力を、前記第1の走査線に関する電流駆動能力に比べて低くするための抵抗が接続されている。

40

## 【0023】

抵抗の挿入によって電流量を制限し、第2の走査線に関する電流駆動能力を、第1の走査線に関する電流駆動能力に比べて低下させるものである。この抵抗は、第2の走査線の電圧変化を鈍らせるための時定数回路の構成要素とみることもできる。出力段のバッファを構成するトランジスタのサイズは同じであっても、第2の走査線を駆動する出力バッファにのみ抵抗を介在させれば、第2の走査線に関する電流駆動能力のみを低下させることができる。出力段バッファを構成するトランジスタのサイズを小さくし、さらに抵抗を挿入して電流駆動能力を絞る（微調整する）、というような使用態様であってもよい。

## 【0024】

50

(5) 本発明のアクティブマトリクス型発光装置の他の態様では、前記駆動トランジスタは絶縁ゲート型電界効果トランジスタであり、前記第2の走査線の電位を変化させて前記駆動トランジスタをオフからオンに移行させる際に、前記発光制御トランジスタのゲート・ソース間の寄生容量を経由して、前記第2の走査線の電位の変化成分が前記発光素子側に洩れ込むことによって生じるカップリング電流の電流量が、前記第2の走査線に関する電流駆動能力を低下させることによって低減され、これによって、黒表示時における前記発光素子の不要な発光が抑制される。

#### 【0025】

回路的な要因によって生じるカップリング電流が、黒表示時のコントラストの低下に直結する重要な要因であり、したがって、本発明は、そのカップリング電流の低減を優先的な解決課題とする点を明らかとしたものである。10

#### 【0026】

(6) 本発明のアクティブマトリクス型発光装置の他の態様では、前記発光制御トランジスタと発光素子とは、基板上において近接して配置されている。

#### 【0027】

高集積化のためには、基板上において、発光制御トランジスタと発光素子とを近接して配置する必要があり、この場合には、発光制御トランジスタの寄生容量を経由して流れるカップリング電流が減衰することなく、そのまま発光素子に供給されることになり、いわゆる黒浮きの現象が顕在化するおそれがある。本発明によれば、特別の回路を設けることなく、黒レベルの上昇を抑制でき、高集積のアクティブマトリクス型発光装置においてもコントラストが低下する心配がない。20

#### 【0028】

(7) 本発明のアクティブマトリクス型発光装置の他の態様では、前記第2の走査線の電位の変化が生じてから、その変化が収束するまでの時間が、1水平同期期間(1H)以上となるように、前記第2の走査線に関する電流駆動能力が調整される。

#### 【0029】

第2の走査線の電位変化が収束するまでの時間が、1水平同期期間(1H)以上となるようにし(つまり、第2の走査線をCR時定数回路とみた場合に、CR時定数を1H以上となるようにし)、急峻な電位変化を避けることによって、ピーク値が大きな、瞬時的なカップリング電流の発生を確実に防止することができる。30

#### 【0030】

(8) 本発明のアクティブマトリクス型発光装置の他の態様では、前記第1の走査線を介して駆動される前記制御トランジスタは、前記保持コンデンサと前記駆動トランジスタの共通接続点と前記データ線との間に接続されたスイッチングトランジスタであり、かつ、このスイッチングトランジスタは、1水平同期期間(1H)内において、少なくとも1回オン/オフ動作を行い、また、前記第2の走査線を介して駆動される前記発光制御トランジスタは、1垂直同期期間(1V)内の所定期間ににおいて、少なくとも1回オン/オフ動作を行う。

#### 【0031】

第1の走査線を介して駆動される制御トランジスタ(スイッチングトランジスタ)は、1水平期間(1H)内に1水平時間に対し十分短時間(数100ns~数μs)でスイッチングする必要があるのに対して、電流駆動能力が弱められた第2の走査線を介して駆動される発光制御トランジスタは、1垂直同期期間(1V)中の所定期間のみオン/オフ動作をすればよく(つまり、オン/オフが頻繁に発生せず)、しかも、その発光制御トランジスタのオンタイミングと、他のトランジスタの動作タイミングとの間には、所定のマージンが設けられるのが通常である。したがって、第2の走査線の駆動能力を意図的に若干低下させても、そのマージンを有効利用して駆動タイミングを調整すれば、回路動作上の遅延は特に問題とならない。また、発光制御トランジスタの場合、他の制御トランジスタのように、頻繁かつ高速なオン/オフを求められないため、この点でも、特に問題は生じない。よって、第2の走査線の駆動能力を意図的に低下させたとしても実際の回路動作上、特に40

問題は生じない。

【0032】

(9) 本発明のアクティブマトリクス型発光装置の他の態様では、前記画素回路は、前記データ線を経由して流れる電流によって、前記保持コンデンサに蓄積される電荷を制御して前記発光素子の発光階調を調整する電流プログラミング方式の画素回路、あるいは、前記データ線を経由して伝達される電圧信号によって、前記保持コンデンサに蓄積される電荷を制御して前記発光素子の発光階調を調整する電圧プログラミング方式の画素回路である。

【0033】

本発明は、電圧プログラミング方式の発光装置ならびに電流プログラミング方式の発光装置の双方に適用可能である。 10

【0034】

(10) 本発明のアクティブマトリクス型発光装置の他の態様では、前記画素回路は、前記駆動トランジスタとしての、絶縁ゲート型電界効果トランジスタのしきい値電圧の変動を補償するための回路構成を備える電圧プログラミング方式の画素回路であり、前記第1の走査線を介して駆動される前記制御トランジスタは、データ線に一端が接続され、他端がカップリングコンデンサの一端に接続された書き込みトランジスタであり、また、前記カップリングコンデンサの他端は、前記保持コンデンサと前記駆動トランジスタの共通接続点に接続されている。 20

【0035】

駆動トランジスタのしきい値電圧のばらつきによる駆動電流の変動を抑制するために、駆動トランジスタのオフ時(黒表示時)のリーク電流も低減され、さらに、カップリング電流による黒レベルの上昇が抑制されるため、所望のレベルの黒表示が確実に実現される。

【0036】

(11) 本発明のアクティブマトリクス型発光装置の他の態様では、前記発光素子は、有機エレクトロルミネッセンス素子(有機EL素子)である。 30

【0037】

有機EL素子はカラー化が容易で、無機EL素子よりはるかに低電圧の直流電流で動作するなどの利点から、近年、大型の表示パネル等としての利用が期待されている。本発明によれば、カップリング電流による黒レベルの上昇を抑制可能な、高品質の有機ELパネルを実現することができる。

【0038】

(12) 本発明の電子機器は、本発明のアクティブマトリクス型発光装置を搭載する。

【0039】

アクティブマトリクス型の発光装置は、大面積・高精細度のディスプレイパネルを実現するうえで有利であり、かつ、本発明のアクティブマトリクス型発光装置は、コントラストの低下が生じないように工夫されている。したがって、例えば、電子機器における表示機器として利用可能である。 40

【0040】

(13) 本発明の電子機器の一態様では、前記アクティブマトリクス型発光装置は、表示装置として、あるいは、光源として使用される。

【0041】

本発明のアクティブマトリクス型発光装置は、例えば、携帯端末に搭載される表示パネルとして、あるいは、カーナビゲーション装置のような車載用機器のインジケータとして使用可能であり、高精彩で大画面の表示パネルとしても使用できる。また、例えば、プリンタにおける光源としても使用することができる。

【0042】

(14) 本発明のアクティブマトリクス型発光装置における画素駆動方法は、発光素子と、前記発光素子を駆動する駆動トランジスタと、前記駆動トランジスタに一端が接続さ 50

れ、書込みデータに応じた電荷を蓄積する保持コンデンサと、前記保持コンデンサへのデータ書込みに関する動作を制御する、少なくとも一つの制御トランジスタと、前記発光素子と前記駆動トランジスタとの間に介在する発光制御トランジスタと、を備える画素回路における前記制御トランジスタならびに前記発光制御トランジスタを各々、第1および第2の走査線を経由してオン／オフ駆動する、アクティブマトリクス型発光装置における画素駆動方法であって、前記第2の走査線に関する電流駆動能力を、前記第1の走査線に関する電流駆動能力に比べて低く設定し、これによって、前記第2の走査線の電位を変化させて前記駆動トランジスタをオフからオンに移行させる際に、前記発光制御トランジスタのゲート・ソース間の寄生容量を経由して、前記第2の走査線の電位の変化成分が前記発光素子側に洩れ込むことによって生じるカップリング電流を低減し、黒表示時における前記発光素子の不要な発光を抑制する。

10

## 【0043】

本発明の画素駆動方法によれば、第2の走査線の駆動能力を低下させてカップリング電流を低減し、黒レベルの上昇を効果的に抑制することができる。

## 【発明を実施するための最良の形態】

## 【0044】

本発明の具体的な実施形態について説明する前に、本発明の発明者によってなされた、アクティブマトリクス型画素回路における、TFTのリーク電流についての検討結果について説明する。

20

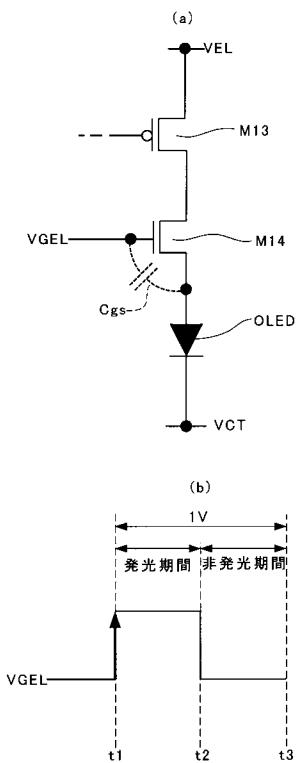

## 【0045】

図14(a), (b)は、アクティブマトリクス型画素回路における、TFTのリーク電流について説明するための図であり、(a)は画素回路の主要部の回路であり、(b)は、発光素子の動作に伴って生じるリーク電流の種類を説明するためのタイミング図である。

20

## 【0046】

図14(a)に示される回路において、M13は、駆動トランジスタ(PチャネルMOS TFT)であり、M14は、スイッチング素子としての発光制御トランジスタ(NMOS TFT)であり、OLEDは、発光素子としての有機EL素子である。発光制御トランジスタ(M14)は、発光制御信号(GEL)によってオン／オフ駆動される。発光制御トランジスタ(M14)には、ゲート・ソース間に寄生容量(Cgs)が存在する。なお、VELならびにVCTは、画素電源電圧である。

30

## 【0047】

有機EL素子(OLED)の動作状態は、図14(b)に示されるように、発光期間(時刻t1～時刻t2)と、非発光期間(時刻t2～時刻t3)に大別される。また、時刻t1において、発光制御信号(発光制御パルス：GEL)がローレベルからハイレベルに立ち上がり、時刻t2において、ハイレベルからローレベルに立ち下がる。時刻t1～時刻t3が、1垂直同期期間(1V)に相当する。

30

## 【0048】

以下の説明では、「黒」を表示することを前提とする。すなわち、図14(a)の回路において、発光素子(OLED)の発光期間(時刻t1～時刻t2)であっても、駆動トランジスタ(M13)はオフを維持して駆動電流は流れないので理想である。しかし、現実には、リーク電流が存在する。図14(a)の回路におけるリーク電流成分は、3種類の成分に分けることができる。

40

## 【0049】

その一つは、発光制御信号がハイレベルの期間(時刻t1～t2)において流れる画素電流(第1のリーク電流)であり、この第1のリーク電流は、駆動トランジスタ(PMOS TFT)M13のオフ時のリーク電流である。

## 【0050】

他の一つは、発光制御信号がローレベルの期間(時刻t2～t3)において流れる画素電流(第2のリーク電流)であり、この第2のリーク電流は、発光制御トランジスタ(N

50

MOSFET) M14 のオフ時のリーク電流である。一般に、第1のリーク電流の方が、第2のリーク電流に比べて電流量が大きい。

#### 【0051】

また、残りの一つが、発光制御信号（発光制御パルス：GEL）の立ち上がり時（時刻t1）において、その発光制御信号（GEL）の電圧変化成分が、発光制御トランジスタ（M14）のゲート・ソース間容量（Cgs）を介して発光素子（OLED）側に洩れ込み、これによって流れる第3のリーク電流である。本明細書では、この第3のリーク電流を、「カップリング電流」と称する。発光制御信号（GEL）が、寄生容量（Cgs）を介して発光素子（OLED）に結合（カップリング）することによって生じる電流であることを考慮したものである。従来、特に、この第3のリーク電流（カップリング電流）については、何ら、考慮されていない。

10

#### 【0052】

以上の3種類のリーク電流を考慮すると、図14(a)の回路における総合的なリーク電流（Ileak）は、以下の式(1)によって表わすことができる。

$$I_{leak} = n \times I_{gel} + d \times I_{offfp} + (1 - d) \times I_{offfn} \dots \dots \quad (1)$$

ここで、nは、1フレーム内の発光回数であり、dは、発光デューティ（1V期間に対する発光期間の割合であり、0 < d < 1）であり、Igelは、GEL信号のカップリングに起因するカップリング電流であり、Iofffpは、PMOSFET（駆動トランジスタM13）のオフ時のリーク電流（オフ電流）であり、Iofffnは、NMOSFET（発光制御トランジスタM14）のオフ時のリーク電流（オフ電流）である。

20

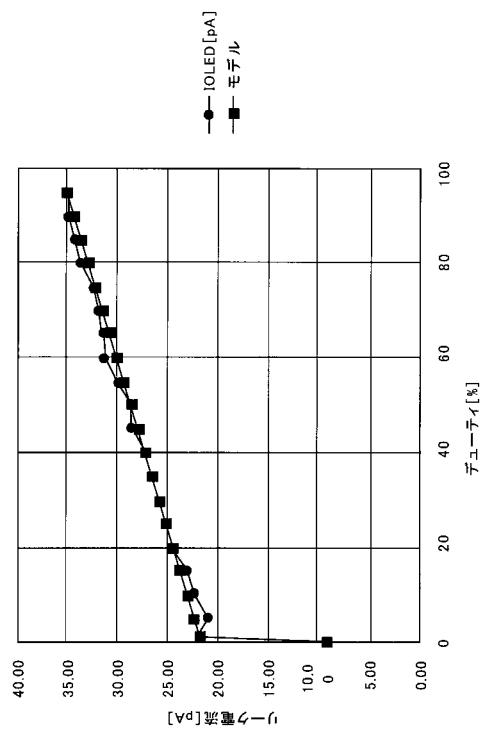

#### 【0053】

上述の(1)式によるリーク電流モデルによって、現実のリーク電流を高精度にシミュレーションできることは、本発明の発明者によってなされた実験結果（図15）から、明らかである。

#### 【0054】

図15は、リーク電流のデューティ依存性について、リーク電流の評価式に基づくコンピュータシミュレーションを実施した結果と、発光素子に流れるリーク電流の実測値とを重ね合わせて示す図である。なお、デューティとは、上述のとおり、1V期間に対する、発光素子の発光期間の割合である。

30

#### 【0055】

図15において、黒い四角をプロットした特性線は、シュミレーションモデルによる特性線であり、黒い丸をプロットした特性線は、発光素子に流れるリーク電流の実測値である。図示されるように、双方の特性線は、ほぼ一致している。つまり、上述の(1)式によるリーク電流モデルが、実際のリーク電流値を精度よく反映していることがわかる。

#### 【0056】

ここで、注目すべきは、従来、何ら対策されていない第3のリーク電流（カップリング電流）の存在である。このカップリング電流は、瞬時的ではあるものの、ピーク電流値が大きいため、このカップリング電流によって発光素子が瞬時に発光することによる黒レベルの上昇（コントラストの低下）が、人の目には印象的に残り、このことが、表示画像の画質の低下に直結する。

40

#### 【0057】

そこで、本発明では、このカップリング電流を回路的な工夫（すなわち、第2の走査線に関する電流駆動能力を意図的に低下させ、発光制御信号GELの立上り/立下りの電圧変化を緩やかにすること）によって低減し、黒レベルの上昇によるコントラストの低下を抑制する。

#### 【0058】

次に、本発明の実施形態について、図面を参照して説明する。

#### 【0059】

（第1の実施形態）

図1は、本発明のアクティブマトリクス型発光装置の一例（電流プログラミング方式の有

50

機 E L パネル ) の全体構成を示す回路図である。

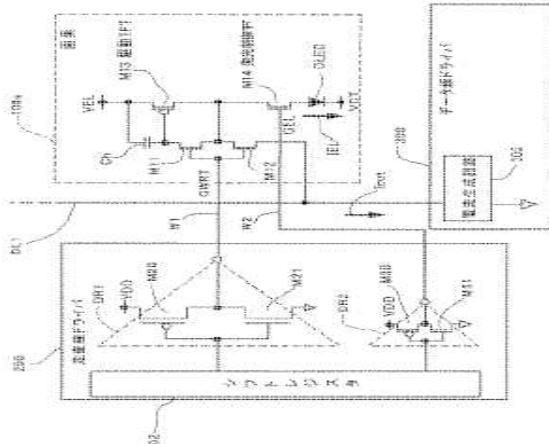

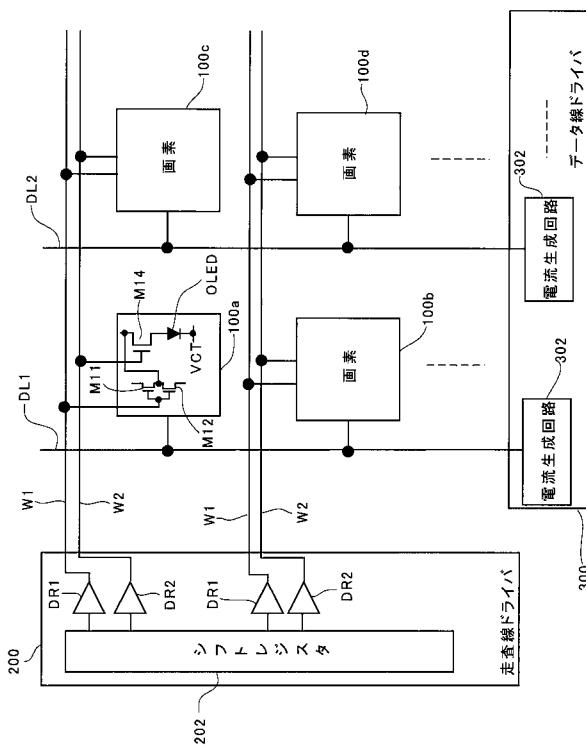

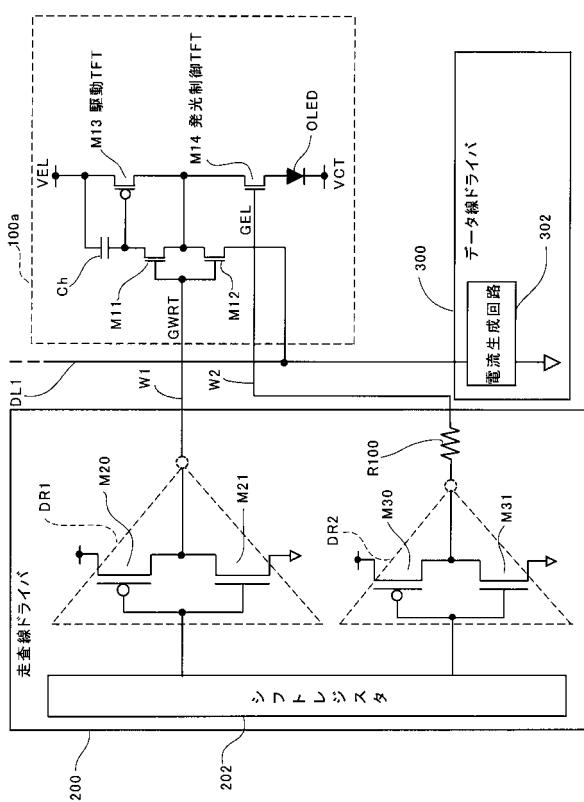

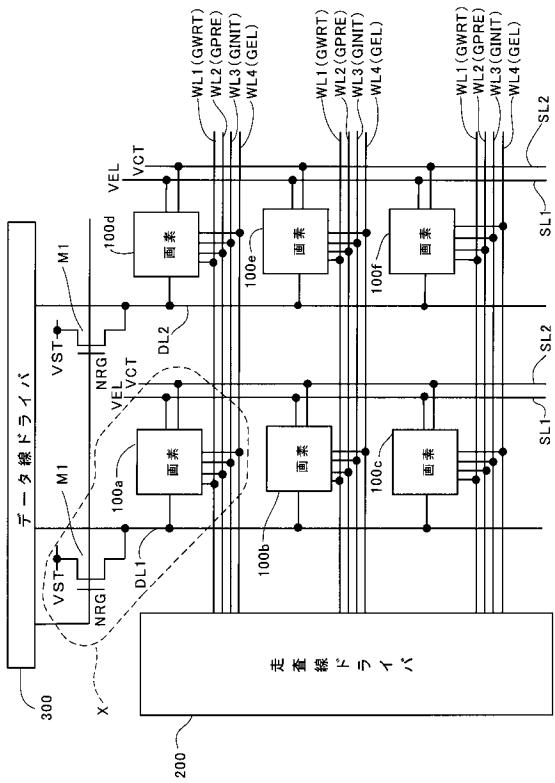

【 0 0 6 0 】

図示されるように、図 1 のアクティブマトリクス型発光装置は、アクティブマトリクス型の画素 ( 画素回路 ) 1 0 0 a ~ 1 0 0 d と、走査線ドライバ ( 走査線駆動回路 ) 2 0 0 と、データ線ドライバ ( データ線駆動回路 ) 3 0 0 と、第 1 および第 2 の走査線 ( W 1 , W 2 ) と、データ線 ( D L 1 , D L 2 ) と、を有する。

【 0 0 6 1 】

画素 ( 画素回路 ) 1 0 0 a ~ 1 0 0 d は、第 1 の走査線 ( W 1 ) を介して駆動される、制御トランジスタとしての N M O S T F T ( M 1 1 , M 1 2 ) と、第 2 の走査線を介して駆動される発光制御トランジスタ ( M 1 4 ) と、有機 E L 素子 ( O L E D ) と、を備える。

10

【 0 0 6 2 】

また、走査線ドライバ 2 0 0 は、シフトレジスタ 2 0 2 と、第 1 の走査線 ( W 1 ) を駆動するための出力バッファ ( D R 1 ) と、第 2 の走査線を駆動するための出力バッファ ( D R 2 ) と、を備える。

【 0 0 6 3 】

また、データ線ドライバ 3 0 0 は、データ線 ( D L 1 , D L 2 ) を電流駆動するための電流生成回路 3 0 2 を備える。

【 0 0 6 4 】

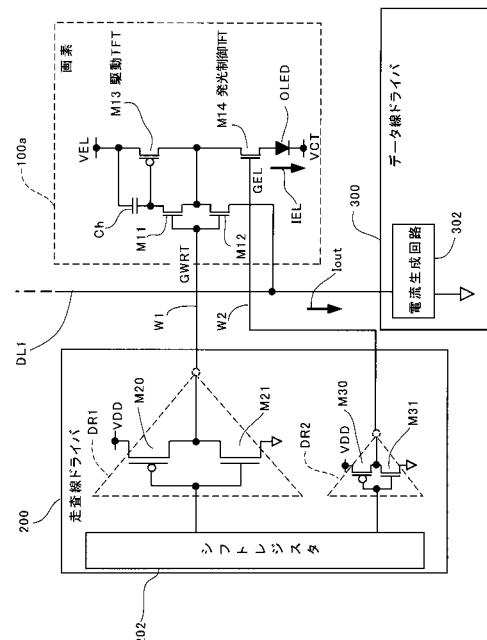

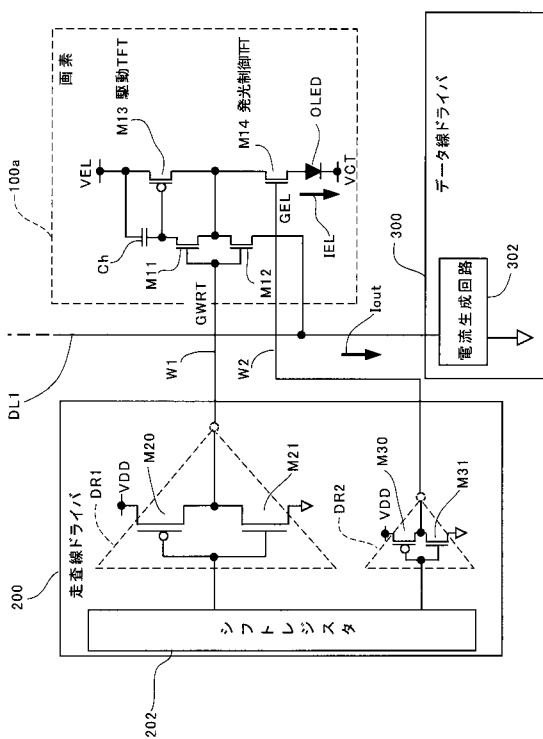

図 2 は、図 1 のアクティブマトリクス型発光装置における、画素 ( 画素回路 ) の具体的な回路構成ならびに走査線ドライバにおける出力バッファの回路構成とトランジスタサイズを示す回路図である。なお、図 2 では、図 1 に示される複数の画素のうち、画素 1 0 0 a のみを描いている。

20

【 0 0 6 5 】

画素 ( 画素回路 ) 1 0 0 a は、保持コンデンサ ( C h ) と、この保持コンデンサ ( C h ) とデータ線 ( D L 1 ) との間に設けられた、保持コンデンサ ( C h ) へのデータの書き込み動作および書き込まれたデータの保持動作を制御する制御トランジスタ ( スイッチングトランジスタ : M 1 1 , M 1 2 ) と、有機 E L 素子 ( O L E D ) を発光させるための駆動電流 ( I E L ) を生成する駆動トランジスタ ( P M O S T F T ) M 1 3 と、発光制御トランジスタ ( N M O S T F T ) M 1 4 と、を備える。駆動トランジスタ ( M 1 3 ) 、発光制御トランジスタ ( M 1 4 ) ならびに有機 E L 素子 ( O L E D ) は、画素電源電圧 ( V E L , V C T ) 間に直列に接続されている。

30

【 0 0 6 6 】

また、走査線ドライバ 2 0 0 に設けられる出力バッファ ( D R 1 , D R 2 ) は各々、 C M O S インバータで構成される。図 2 では、1 段のインバータしか記載されていないが、これに限定されるものではなく、複数のインバータを偶数段、あるいは、奇数段接続してもよい。

【 0 0 6 7 】

ここで、注目すべき点は、発光制御トランジスタ ( M 1 4 ) を駆動するための走査線 ( W 2 ) に関する電流駆動能力が、他の制御トランジスタを駆動するための走査線 ( W 1 ) に関する電流駆動能力に比べて意図的に低く設定されている点である。

40

【 0 0 6 8 】

すなわち、出力バッファ ( D R 2 ) を構成するトランジスタ ( P M O S T F T ( M 3 0 ) , N M O S T F T ( M 3 1 ) ) のサイズは、出力バッファ D R 1 を構成するトランジスタ ( P M O S T F T ( M 2 0 ) , N M O S T F T ( M 2 1 ) ) のサイズよりも小さく設定されている。図中、出力バッファ ( D R 1 ) に比べて出力バッファ ( D R 2 ) を小さく描いているのは、トランジスタのサイズの違いを明らかとするためである。

【 0 0 6 9 】

具体的には、例えば、出力バッファ ( D R 2 ) を構成するトランジスタ ( P M O S T F T ( M 3 0 ) , N M O S T F T ( M 3 1 ) ) のゲート長 ( L ) は 1 0 μ m 、ゲート幅 ( W

50

)は $100\mu m$ である。これに対して、出力バッファDR1を構成するトランジスタ(PMOS TFT(M20), NMOS TFT(M21))のゲート長(L)は $10\mu m$ 、ゲート幅(W)は $400\mu m$ である。つまり、出力バッファ(DR2)を構成するトランジスタのチャネルコンダクタンス(W/L)は、出力バッファ(DR1)を構成するトランジスタの略1/4である。

#### 【0070】

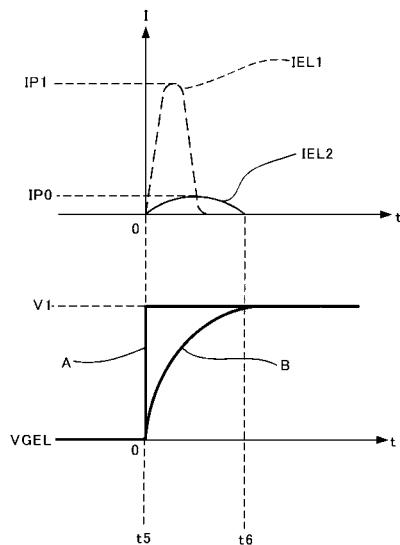

図3は、図2の回路におけるカップリング電流の低減効果を説明するための図である。図3の下側には、発光制御トランジスタ(M14)のオン/オフを制御する発光制御信号(GEL)の、2種類の立上り波形が示されている。急峻な立上り波形(A)は従来どおりの駆動による波形である。これに対して、所定の時定数で立上る(電圧の変化が緩やかな)波形Bは、図2に示される電流駆動能力が低く設定されている出力バッファ(DR2)によって走査線W2を駆動した場合の波形である。

10

#### 【0071】

図3の上側には、黒表示時において、発光制御トランジスタ(M14)のゲート・ソース間の寄生容量Cgs(図14(a)参照)を介して流れるカップリング電流の様子を示している。カップリング電流(IEL1:図中、点線で示される)は、発光制御信号(GEL)の立上り波形Aに対応したカップリング電流であり、そのピーク値(IP1)があり、かなり大きい。

20

#### 【0072】

一方、カップリング電流(IEL2:図中、実線で示される)は、発光制御信号(GEL)の立上り波形Bに対応したカップリング電流であり、そのピーク値(IP0)は、(IP1)に比べてかなり小さい。

20

#### 【0073】

カップリング電流(IEL1)は、瞬時的ではあるものの、そのピーク電流値(IP1)が大きいため、このカップリング電流によって発光素子(OLED)が瞬時に発光することによる黒レベルの上昇(コントラストの低下)が、人の目には印象的に残り、このことが、表示画像の画質の低下に直結する。

30

#### 【0074】

一方、カップリング電流(IEL2)は、時間軸方向に分散されてピーク値(IP0)が低いために、黒レベルの上昇はごくわずかであり、人の目には、ほとんど感知されない程度である。

30

#### 【0075】

このように、第2の走査線に関する電流駆動能力を意図的に低下させ、発光制御信号GELの立上り/立下りの電圧変化を緩やかにすることによって、ピーク値の大きな瞬的なカップリング電流を低減することができ、したがって、黒レベルの上昇によるコントラストの低下を抑制することができる。

40

#### 【0076】

なお、第2の走査線に関する電流駆動能力の低下は、若干の駆動遅延をもたらすが、駆動タイミングを適正化すれば、特に問題は生じない。すなわち、発光制御トランジスタ(M14)は、1V期間中の所定期間のみにオン/オフ動作をする、駆動頻度の低いトランジスタであり、一方、他の制御トランジスタ(M11, M12)は、1H期間中に少なくとも1回はオン/オフ駆動をする、駆動頻度の高いトランジスタであり、かつ、発光制御トランジスタのサイズは、他のTFTに比べて大きい。つまり、発光制御トランジスタ(M14)は、他の制御トランジスタ(M11, M12)ほどの高速スイッチング性能は最初から求められておらず、また、その駆動に際しては、ある程度のタイミングマージンが設けられている。したがって、第2の走査線(W2)の駆動能力を低下させることによって、若干の駆動遅延が生じたとしても、そのタイミングマージンを利用して、駆動タイミングを調整すれば、駆動に際しては、さしたる問題は生じない。

#### 【0077】

第2の走査線を駆動するドライバ回路DR2の駆動能力であるが、バッファ回路を構成

50

する TFT の飽和電流を  $I_{sat}$  、 1 水平期間を  $T_{1H}$  、第 2 の走査線の配線容量を  $C_{W2}$  、走査線の電圧振幅を  $V$  とすると、  $C_{W2} \times V / I_{sat} = T_{1H}$  を満たすようにバックファ回路の駆動能力を設定する事が望ましい。また、カップリング電流は第 2 の走査線信号の立ち上がり時に発生するものが黒浮きの原因となるため、 Pch-TFT のみ駆動能力を制限するように回路を構成しても良い。

#### 【 0078 】

また、発光装置の高集積化が進展すると、発光素子と発光制御トランジスタが、基板上でますます近接して配置されるようになり、この場合、発光制御パルスが発光素子側に洩れ込むと、そのパルス状の電流が減衰されずに、そのまま発光素子に流れて黒浮きが顕在化する。よって、本発明は、高集積化にも適した駆動回路を提供できる、という効果も奏する。

10

#### 【 0079 】

また、同じサイズのトランジスタを 2 個並列に接続しているような場合も、その 2 個のトランジスタを 1 個のトランジスタとみれば、実質的にはトランジスタサイズを変更していることになる。

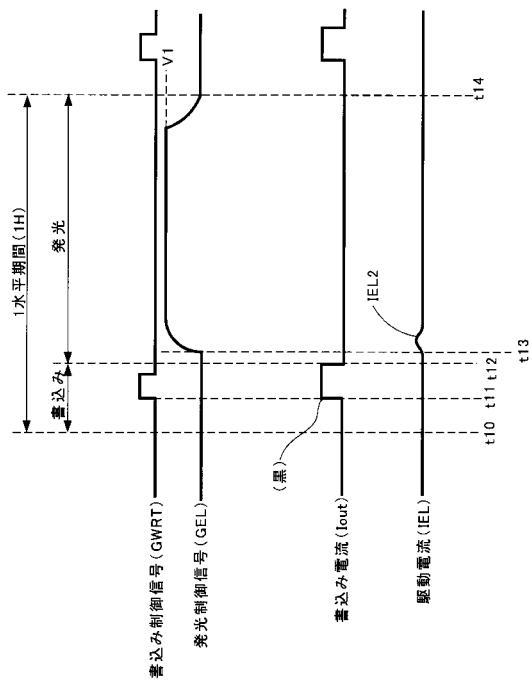

#### 【 0080 】

次に、図 2 の画素回路の具体的な動作について説明する。図 4 は、図 2 の画素回路における動作を説明するためのタイミング図である。図 4において、時刻  $t_{10}$  ~ 時刻  $t_{12}$  は書き込み期間（電流  $I_{out}$  による保持容量  $Ch$  の電荷調整期間）であり、時刻  $t_{12}$  ~ 時刻  $t_{14}$  は、発光期間である。発光期間では、保持コンデンサ（ $Ch$ ）の両端電圧が保持されると共に、駆動トランジスタ（M13）によって駆動電流  $I_{EL}$  が生成され（ただし、黒表示時には駆動トランジスタはオフ状態を維持する）、その駆動電流  $I_{EL}$  が、オン状態の発光制御トランジスタ（M14）を介して有機 EL 素子（OLED）に供給される。

20

#### 【 0081 】

図 4において、時刻  $t_{11}$ において、第 1 の走査線（W1）を介して伝達される走査書き込み制御信号（GWR T）がハイレベルとなり、これに伴って NMOS TFT (M11, M12) が共にオンし、これによって、保持コンデンサ（ $Ch$ ）の一端が、データ線（DL1）に電気的に接続される。同時に、電流生成回路 302 によって生成された電流（書き込み電流） $I_{out}$  によって、保持コンデンサ（ $Ch$ ）の保持電荷が調整され、これにより、発光階調のプログラミングがなされる。ここでは、黒の表示を前提とするため、黒の階調がプログラムされる。

30

#### 【 0082 】

次に、時刻  $t_{13}$  に、ワード線 W2 を介して発光制御信号（GEL）が所定の時定数で緩やかに立ち上る。このとき流れる駆動電流（ $I_{EL2}$ ）は、カップリング電流成分のみであり、そして、そのカップリング電流は時間軸方向に分散されて、そのピーク値はきわめて小さい。したがって、黒レベルの上昇（黒浮きの程度）は、ほとんど問題とならない。

40

#### 【 0083 】

時刻  $t_{14}$ において、発光期間が終了する。発光制御信号（GEL）は、時刻  $t_{14}$  より少し前のタイミングでハイレベルからローレベルに転じるよう、タイミングが調整されている。

#### 【 0084 】

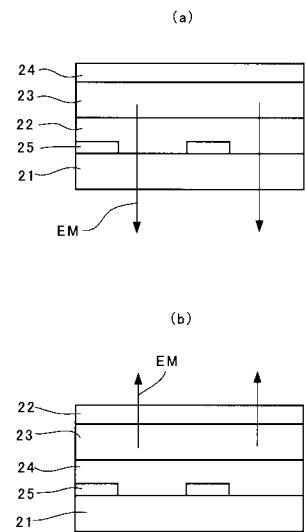

次に、アクティブマトリクス型の有機 EL パネルにおける画素の断面構造と採光方式について説明する。

#### 【 0085 】

図 5 は、アクティブマトリクス型の有機 EL パネルにおける画素の断面構造と採光方式について説明するためのデバイスの断面図であり、(a) はボトムエミッション型の構造を示す図であり、(b) はトップエミッション型の構造を示す図である。

#### 【 0086 】

50

図5(a), 図5(b)において、参照符号21は、透明なガラス基板であり、参照符号22は透明電極(ITO)であり、参照符号23は有機発光層(有機電子輸送層や有機ホール輸送層が積層形成される場合を含む)であり、参照符号24は、アルミニウム等の金属電極であり、参照符号25は、TFT(ポリシリコン薄膜トランジスタ)回路である。

#### 【0087】

TFT回路25を構成するポリシリコン薄膜トランジスタとしては、製造時の最高温度が摂氏600度以下に抑えられた、いわゆる「低温ポリシリコン薄膜トランジスタ」を使用するのが好ましい。

#### 【0088】

有機発光層23は、例えば、インクジェット式印字方法により形成することができる。また、透明電極22や金属電極24は、例えば、スパッタリング法により形成することができる。

#### 【0089】

図5(a)のボトムエミッション型構造では、基板21を介して光(EM)が出射される。これに対して、図5(b)のトップエミッション型構造では、基板21の反対側の方向に、光(EM)が出射される。

#### 【0090】

図5(a)のボトムエミッション構造の場合、画素回路を構成する素子数が増加してTFT回路25の占有面積が増大すれば、その分だけ発光部の開口率が低下し、その発光輝度が低下する場合があり得る。この点、図5(b)のトップエミッション型構造では、TFT回路25の占有面積が増大しても開口率の低下が生じる心配はない。画素回路の素子数の増大が問題となる場合には、図5(b)のトップエミッション型構造を採用するのが好ましいといえる。ただし、これに限定されるものではなく、開口率の若干の低下が問題とならない場合には、ボトムエミッション型構造を採用することもできる。

#### 【0091】

##### (第2の実施形態)

図6は、本発明のアクティブマトリクス型発光装置の他の例(第2の走査線を駆動する出力バッファの出力端に電流制限抵抗を接続することによって電流駆動能力を低下させる例)の回路構成を示す回路図である。図6において、図2と共通する部分には同じ参照符号を付してある。

#### 【0092】

図6のアクティブマトリクス型発光装置の回路構成は、図2に示される回路の回路構成とほぼ同じである。但し、図6では、2つの出力バッファ(DR1, DR2)を構成するトランジスタ(M20, M21, M30, M31)のサイズ(チャネルコンダクタンスW/L)は同じであり、かつ、出力バッファ(DR2)の出力端には抵抗R100が接続されている。

#### 【0093】

抵抗R100は電流制限抵抗として機能し、また、CRの時定数回路の構成要素としても機能する。抵抗R100の抵抗値を適宜、調整することによって、第2の走査線(W2)に関する電流駆動能力を最適化することができる。

#### 【0094】

この抵抗R100が介在することによって、出力バッファ(DR2)による電流駆動能力が実質的に弱められる。したがって、第2の走査線(W2)を介して発光制御トランジスタ(M14)を駆動する際の発光制御信号(GEL)の立上り波形が鈍化し、カップリング電流が低減され、黒レベルの上昇が抑制される。

#### 【0095】

図6では、2つの出力バッファ(DR1, DR2)を構成するトランジスタのサイズを同じにしているが、これに限定されるものではない。例えば、出力バッファ(DR2)を構成するトランジスタのサイズを相対的に小さくし、さらに、抵抗R100を接続して、

10

20

30

40

50

走査線 (W2) についての電流駆動能力を微調整することも可能である。

【0096】

接続する抵抗値 R は 1 水平期間を  $T_{1H}$ 、第 2 の走査線の配線容量を  $C_{W2}$  とすると、 $C_{W2} \times R = T_{1H}$  を満たすように抵抗値 R を設定する事が好ましい。

【0097】

(第 3 の実施形態)

図 7 は、本発明のアクティブマトリクス型発光装置の他の例の全体構成を示すブロック図である。以下の説明では、アクティブマトリクス型発光装置は、有機 EL パネルとする。

【0098】

図 7 の有機 EL 表示パネルでは、発光素子として有機 EL 素子が用いられ、能動素子としてポリシリコン薄膜トランジスタ (TFT) が用いられる。以下の説明では、「ポリシリコン薄膜トランジスタ」を、「薄膜トランジスタ」、「TFT」あるいは、単に「トランジスタ」と記載する場合がある。

【0099】

なお、有機 EL 素子は、薄膜トランジスタ (TFT) が形成された基板上に形成される。また、有機 EL 素子は、発光層を含む有機層を 2 つの電極で挟み込んだ構造をもち、本発明においては、好ましくは、トップエミッション型の構造が採用される。

【0100】

図 7 のアクティブマトリクス型発光装置は、マトリクス状に配置された、有機 EL 素子を含む画素 (画素回路) 100a ~ 100f と、データ線 (DL1, DL2) と、複数本を一組とする走査線 (WL1 ~ WL4) と、走査線ドライバ 200 と、データ線プリチャージ回路 (M1) を備えるデータ線ドライバ 300 と、画素電源配線 (SL1, SL2) と、を有する。

【0101】

画素プリチャージ回路 (M1) は、十分な電流駆動能力をもつ N 型の絶縁ゲート型 TFT (MOSTFT) で構成される。この TFT (M1) は、データ線プリチャージ制御信号 (NRG) によってオン / オフが制御され、ドレインが、データ線プリチャージ電圧 (単に、プリチャージ電圧ということがある) VST に接続され、ソースが、データ線 (DL1, DL2) に接続されている。また、データ線プリチャージ電圧 (VST) は、例えば、10V 以上に設定される。

【0102】

走査線 (WL1) は、書き込み制御信号 GWRD によって、各画素 (100a ~ 100f) 内の書き込みトランジスタ (図 7 では不図示) のオン / オフを制御する。

【0103】

また、走査線 (WL2) は、画素プリチャージ制御信号 (GPRE) によって、各画素 (100a ~ 100f) 内の画素プリチャージトランジスタ (図 1 では不図示) を制御する。

【0104】

また、走査線 (WL3) は、補償制御信号 (GINIT) によって、各画素 (100a ~ 100f) 内の補償トランジスタ (図 7 では不図示) を制御する。

【0105】

また、走査線 (WL4) は、発光制御信号 (GEL) によって、各画素 (100a ~ 100f) 内の発光制御トランジスタ (図 1 では不図示) を制御する。

【0106】

走査線ドライバ 200 は、これらの 4 本の走査線 (WL1 ~ WL4) を、所定のタイミングで周期的に駆動する。

【0107】

また、画素電源配線 (SL1) は、有機 EL 素子を発光させるための高レベル電源電圧 (Vee1 : 例えば 13V) を、各画素に供給する。また、画素電源配線 (SL2) は、低レベル電源電圧 (VST : 例えば 接地電位) を各画素に供給する。

10

20

30

40

50

## 【0108】

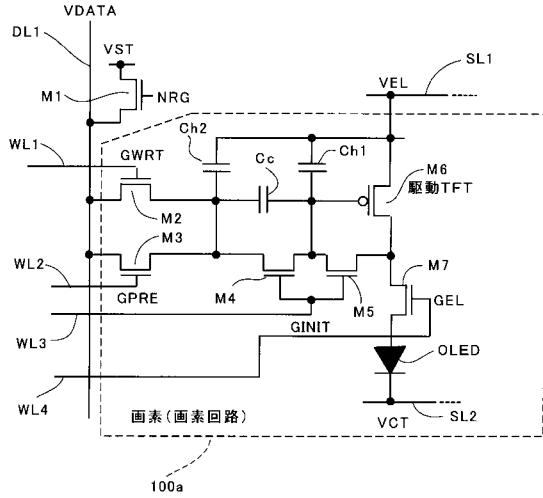

図8は、図7の有機EL表示パネルの要部(図7中、点線で囲まれるX部分)の具体的な回路構成例を示す回路図である。

## 【0109】

図示されるように、画素(画素回路)100aは、書き込みトランジスタ(M2)と、カップリングコンデンサ(Cc)と、第1および第2の保持容量(ch1, ch2)と、駆動トランジスタ(M6)と、画素プリチャージトランジスタ(M3, M4)と、補償トランジスタ(M4, M5)と、発光制御トランジスタ(M7)と、発光素子としての有機EL素子(OLED)と、により構成される。

## 【0110】

書き込みトランジスタ(M2)は、N型TFTからなり、一端がデータ線(DL1)に接続され、他端がカップリングコンデンサ(Cc)の一端に接続され、ゲートが走査線WL1に接続されている。この書き込みトランジスタ(M2)は、書き込み制御信号(GWRT)によって、データの書き込み時にオン状態となる。

10

## 【0111】

駆動トランジスタ(M6)はP型TFTからなり、一端が画素電源電圧(VEL)に接続され、ゲートがカップリングコンデンサ(Cc)の他端に接続されている。この駆動トランジスタ(M6)は、有機EL素子(OLED)の発光期間においてオンし、駆動電流を有機EL素子(OLED)に供給する。

20

## 【0112】

カップリングコンデンサ(Cc)は、書き込みトランジスタ(M2)の他端と、駆動トランジスタ(M6)のゲートとの間に介在する。データの書き込み期間において、書き込み電圧の変化成分(交流成分)が、このカップリングコンデンサ(Cc)を介して駆動トランジスタ(M6)のゲートに伝達される。

## 【0113】

第1の保持コンデンサ(ch1)は、その一端が、駆動トランジスタ(M6)とカップリングコンデンサ(Cc)の共通接続点に接続され、他端が画素電源電圧(VEL)に接続されている。ここで、第1の保持コンデンサ(ch1)の他端は、VELの代わりに、グランド(GND)に接続することも可能である。つまり、第1の保持コンデンサ(ch1)の他端は、安定した直流電位に接続されることになる。

30

## 【0114】

この第1の保持コンデンサ(ch1)は、書き込みデータ(書き込み電圧)を保持して、非選択期間においても、有機EL素子(OLED)の発光を維持することを可能とする。また、この第1の保持コンデンサ(ch1)は、駆動トランジスタ(M6)のゲート電圧を安定化する機能も併せ持つ。

## 【0115】

第2の保持コンデンサ(ch2)は、その一端が、書き込みトランジスタ(M2)とカップリングコンデンサ(Cc)の共通接続点に接続され、他端が画素電源電圧(VEL)に接続されている。ここで、第2の保持コンデンサ(ch2)の他端は、VELの代わりに、グランド(GND)に接続することも可能である。つまり、第2の保持コンデンサ(ch2)の他端は、安定した直流電位に接続されることになる。

40

## 【0116】

この第2の保持コンデンサ(ch2)は、書き込みトランジスタ(M2)のソース・ドレイン容量(寄生容量)に起因するデータ線(DL1)とのクロストークや、他のデータ線との電磁的なカップリングによるクロストークによって、カップリングコンデンサの一端の電位が変動することを抑制するために設けられている。これによって、駆動トランジスタ(M6)のゲートの電位が安定化されることになる。

## 【0117】

画素プリチャージトランジスタ(M3)は、一端がデータ線DL1に接続され、ゲートが走査線(WL2)に接続される。この画素プリチャージトランジスタ(M3)は、画素

50

プリチャージ制御信号 ( G P R E ) によって、データ線プリチャージ期間 ( データ線プリチャージ回路 M 1 がオンする期間 ) においてオンされ、カップリングコンデンサ ( C c ) をプリチャージ ( 初期化 ) する。その結果として、カップリングコンデンサ ( C c ) の両端の電位が、収束目標の電圧に近いレベルまで引き上げられる ( この点は、図 3 を用いて説明する )。また、この画素プリチャージトランジスタ ( M 3 ) は、データ線プリチャージ期間が終了するとオフし、これによって、画素 ( 具体的にはカップリングコンデンサ C c ) が、データ線 ( D L 1 ) から切り離される。

#### 【 0 1 1 8 】

なお、補償トランジスタ ( M 4 ) も、カップリングコンデンサ ( C c ) をプリチャージ ( 初期化 ) するのに貢献するため、補償トランジスタ ( M 4 ) は、画素プリチャージトランジスタの機能を兼ねていることができる。

10

#### 【 0 1 1 9 】

また、補償トランジスタ ( M 4 , M 5 ) のゲートは走査線 ( W L 3 ) に接続され、補償制御信号 ( G I N I T ) によって、しきい値電圧の補償期間においてオンされる。補償トランジスタ ( M 4 , M 5 ) は、カップリングコンデンサ ( C c ) の書き込みトランジスタ ( M 2 ) 側の端の直流電位を、目標値 ( 駆動トランジスタ M 6 のしきい値電圧を反映した電圧値 ( すなわち、書き込みデータに加えられる補償値 ( 補正值 ) である ) ) に収束させるための電流経路を形成する働きをする。つまり、駆動トランジスタ ( M 6 ) のしきい値電圧のばらつきを吸収するための、ゲート電圧の補償値 ( 補正值 ) を発生させる働きをするのであり、この点に着目し、トランジスタ ( M 4 , M 5 ) を「補償トランジスタ」と称している。

20

#### 【 0 1 2 0 】

また、上述のように、補償トランジスタ ( M 4 ) は、カップリングコンデンサ ( C c ) のプリチャージ ( 初期化 ) のための電流経路を形成する機能も併せ持つ。

#### 【 0 1 2 1 】

また、発光制御トランジスタ ( M 7 ) は、駆動トランジスタ ( M 6 ) と有機 E L 素子 ( O L E D ) との間に介在し、そのゲートは、走査線 ( W L 4 ) に接続されている。この発光制御トランジスタ ( M 7 ) は、発光制御信号 ( G E L ) によって、有機 E L 素子 ( O L E D ) の発光期間においてオンされ、駆動電流を有機 E L 素子発光制御トランジスタ ( M 7 ) ( O L E D ) に供給して、有機 E L 素子 ( O L E D ) を発光させる。この発光制御トランジスタ ( M 7 ) が存在することから、画素 ( 画素回路 ) 1 0 0 a は、アクティブマトリクス型の画素 ( 画素回路 ) となる。

30

#### 【 0 1 2 2 】

この発光制御トランジスタ ( M 7 ) を駆動するための走査線 ( W L 4 ) についての電流駆動能力は、前掲の実施形態と同様に、他のトランジスタを駆動するための走査線 ( W L 1 ~ W L 3 ) についての電流駆動能力に比べて低く設定されており、これによって、カップリング電流に起因する黒レベルの上昇が抑制される。

#### 【 0 1 2 3 】

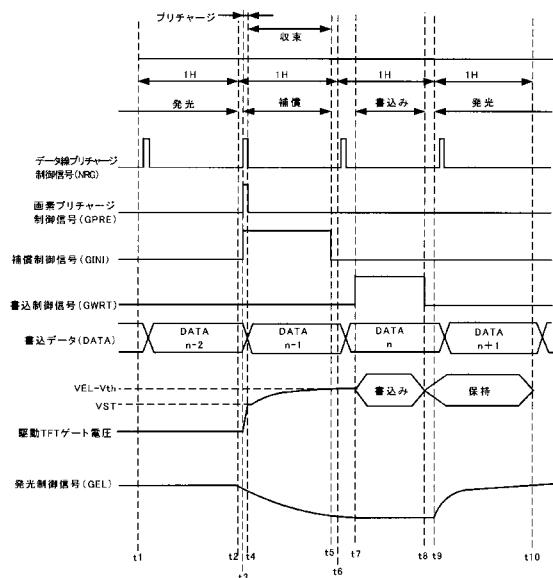

次に、図 8 の画素 ( 画素回路 ) の動作について説明する。図 9 は、図 8 の画素 ( 画素回路 ) の動作タイミングならびに駆動トランジスタのゲート電圧波形の変化を説明するための図である。

40

#### 【 0 1 2 4 】

図 8 において、時刻 t 1 ~ 時刻 t 2 , 時刻 t 2 ~ 時刻 t 6 , 時刻 t 6 ~ 時刻 t 9 , 時刻 t 9 ~ 時刻 t 1 0 の各々は、1 水平同期期間 ( 図中、1 H と記載 ) に相当する。

#### 【 0 1 2 5 】

図 8 の場合、時刻 t 2 以前と、時刻 t 9 以後は、有機 E L 素子 ( O L E D ) が発光する「発光期間」である。また、時刻 t 3 ~ 時刻 t 5 の期間は、駆動トランジスタ ( M 6 ) のしきい値電圧ばらつきを補償するための「補償期間」である。また、時刻 t 7 ~ 時刻 t 8 の期間は、データ線 ( D L 1 ) から、書き込みトランジスタならびにカップリングコンデンサを介してデータを書込む「書き込み期間」である。

50

## 【0126】

各水平同期期間（1H）の開始直後の、極短い期間に、データ線プリチャージ信号（N R G）がハイレベルとなり、これによって、データ線プリチャージ回路（M1）がオンして、データ線のプリチャージが行われる。

## 【0127】

図8の画素100aに関しては、画素プリチャージ制御信号（G P R E）は、時刻t3～t4にハイレベルとなる（つまり、データ線プリチャージ期間に同期してハイレベルとなる）。画素プリチャージ制御信号（G P R E）がハイレベルである期間において、画素プリチャージトランジスタ（M3）がオンし、画素100aは、この画素プリチャージトランジスタ（M3）を介してデータ線（D L 1）と接続される。これにより、カップリングコンデンサ（C c）のプリチャージ（初期化）が行われる。ただし、画素プリチャージトランジスタ（M3）がオンするのは、データ線（D L 1）のプリチャージ期間のみであり、その期間が終了するとすぐにオフする。

10

## 【0128】

また、補償制御信号（G I N I T）は、時刻t3～時刻t5の期間（補償期間）においてハイレベルとなる。これによって、補償トランジスタ（M4, M5）がオンし、駆動トランジスタ（M6）がダイオード接続状態となると共に、そのダイオードのアノードと、カップリングコンデンサ（C c）の両端の各々とを結ぶ電流経路が形成される。そして、カップリングコンデンサ（C c）の両端の電位は、駆動トランジスタ（M6）のしきい値電圧（V t h）を反映した電圧値（V E L - V t h）に収束する。

20

## 【0129】

書き込み制御信号（G W R T）は、時刻t7～時刻t8の間にハイレベルとなり、これによって、書き込みトランジスタ（M2）がオンする。画素100aには、データ線（D L 1）から、n番目のデータ（D A T A n）が書き込まれる。これによって、駆動トランジスタ（M6）がオンする。また、書き込まれたデータ（書き込み電圧）は、第1の保持容量（c h 1）が存在するために、画素100aの非選択期間においても保持される。

20

## 【0130】

発光制御信号（G E L）は、データの書き込みが終了した後の、時刻t9においてハイレベルとなり、これによって、発光制御トランジスタ（M7）がオンする。駆動トランジスタ（M6）からの駆動電流が有機EL素子（O L E D）に供給され、有機EL素子（O L E D）が発光する。

30

## 【0131】

図9の下側には、駆動トランジスタ（M6）のゲート電圧の変化の様子が示されている。時刻t3に画素プリチャージ信号（G P R E）がハイレベルとなって画素プリチャージトランジスタ（M3）がオンし、また、その時刻t3には、補償制御信号（G I N I T）もハイレベルに転じるために、補償トランジスタ（M4）も同時にオンする。これによって、データ線（D L 1）と、カップリングコンデンサ（C c）の両端の各々とが電気的に接続される。したがって、時刻t3～時刻t4の期間において、データ線（D L 1）のプリチャージ電流によって、カップリングコンデンサ（C c）は急速にプリチャージされる。よって、駆動トランジスタ（M6）のゲート電位は、データ線のプリチャージ電圧（V S T：データ線プリチャージ回路（M1）の一端に接続される電圧）まで急速に上昇する。データ線プリチャージ回路（M1）の電流駆動能力は高いため、カップリングコンデンサ（C c）の高速なプリチャージが可能である。

40

## 【0132】

時刻t4になると、画素プリチャージトランジスタ（M3）はオフするため、画素100aは、データ線（D L 1）から切り離される。また、このとき、補償トランジスタM5がオンすることによって、駆動トランジスタのゲート・ドレイン間がショートされ、ダイオード接続状態となっている。

## 【0133】

したがって、時刻t4～時刻t7においては、ダイオード接続状態の駆動トランジスタ

50

(M6)からの順方向電流が直接的に、カップリングコンデンサ(Cc)の駆動トランジスタ(M6)側の端に供給され、また、その順方向電流が、オンしている補償トランジスタ(M4)を経由して、カップリングコンデンサ(Cc)の書き込みトランジスタ(M2)側の端にも供給され、これによって、カップリングコンデンサ(Cc)の両端は充電され、時間の経過と共に上昇し、結果的に、駆動トランジスタ(M6)のしきい値電圧(Vth)を反映した電位(VEL-Vth)に収束する。プリチャージによって、駆動トランジスタ(M6)のゲート電位が、収束目標値に近い電位(VST)となっているため、(VEL-Vth)への収束が早められる。この収束した電圧値(VEL-Vth)が、正規の書き込み電圧を補償(補正)するための補償(補正)電圧値となる。

## 【0134】

10

また、駆動トランジスタ(M6)のゲート電圧を(VEL-Vth)に収束させるには、ある程度の時間がかかるが、本発明では、画素プリチャージ期間後は、画素はデータ線(DL1)から電気的に切り離されるため、データ線(DL1)を介した他の画素へのデータ書き込みと、画素100a内部における補償動作とを並行的に行うことができ、複数の水平同期期間にわたってその補償動作を行わせることも可能であり、したがって、十分な補償期間を確保することができる。

## 【0135】

そして、時刻t7にデータが書き込まれ、その書き込まれたデータは、時刻t8以降も保持される。

## 【0136】

20

図9の最下に示されるように、発光制御信号(GEL)は、時刻t2から時刻t7にわたって、すなわち、1水平同期期間(1H)以上にわたって、その電位が緩やかに変化する。図9から明らかなように、発光制御信号(GEL)のオフ期間は、t2からt9までの2H分の期間であり、十分に長い時間があることになる。この点に着目し、走査線(WL4)の電流駆動能力を弱めて、走査線の電位の変化開始から収束までの時間が、1H以上となるよう設定する。

## 【0137】

ここで、特に、書き込み期間(時刻t7～時刻t8)において、発光制御トランジスタ(M7)が完全にオフしているという条件が満たされれば、補償期間(時刻t3～t5)において、補償動作に伴う若干の電流が発光素子に洩れ込んで、それほど大きな問題は生じない。本発明では、ピーク値の大きなカップリング電流を低減することによる黒浮きの抑制を優先させ、画質の低下を最小限に抑える。

30

## 【0138】

本実施形態では、駆動トランジスタのしきい値電圧のばらつきによる駆動電流の変動を抑制するために、駆動トランジスタのオフ時(黒表示時)のリーク電流も低減され、さらに、カップリング電流による黒レベルの上昇が抑制されるため、所望のレベルの黒表示が確実に実現される。

## 【0139】

40

(第4の実施形態)

本実施形態では、本発明のアクティブマトリクス型発光装置を用いた電子機器について説明する。

## 【0140】

なお、本発明の発光装置は、携帯電話、コンピュータ、CDプレーヤー、DVDプレーヤーなどの小型の、携帯電子機器に用いて、特に有効である。もちろんこれらに限られるものではない。

## 【0141】

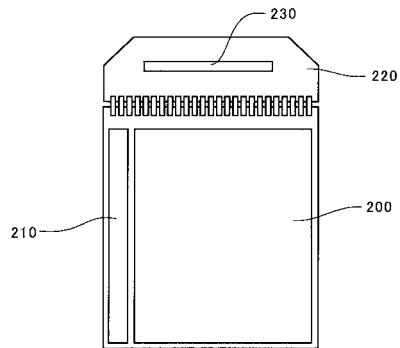

(1) 表示パネル

図10は、本発明のアクティブマトリクス型発光装置を用いた表示パネルの全体のレイアウト構成を示す図である。

この表示パネルは、電圧プログラム式画素を有するアクティブマトリクス型有機EL素子

50

200と、レベルシフタを内蔵した走査線ドライバ210と、フレキシブルT A Bテープ220と、RAM / コントローラ付き外部アナログドライバL S I 230と、を有する。

【0142】

(2) モバイルコンピュータ

図11は、図11の表示パネルを搭載したモバイルパソコンコンピュータの外観を示す斜視図である。

図11において、パソコンコンピュータ1100は、キーボード1102を含む本体1104と、表示ユニット1106と、を備える。

【0143】

(3) 携帯電話端末

図12は、本発明の表示パネルを搭載した携帯電話端末の概観を示す斜視図である。

携帯電話1200は、複数の操作キー1202と、スピーカ1204と、マイク1206と、本発明の表示パネル100と、を備える。

【0144】

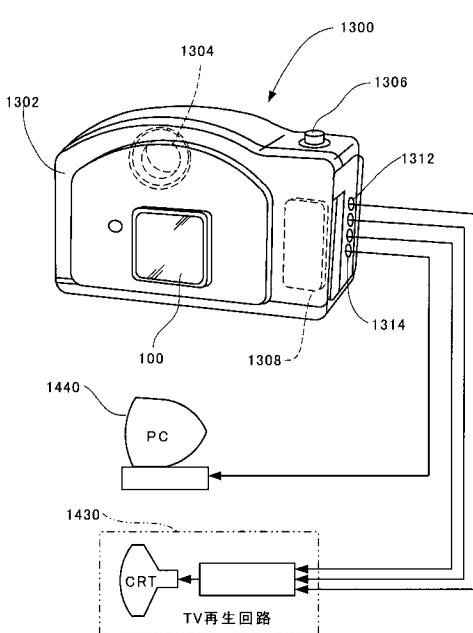

(4) デジタルスチルカメラ

図13は、本発明の有機ELパネルをファインダーとして用いたデジタルスチルカメラの外観と使用態様を示す図である。

このデジタルスチルカメラ1300は、ケース1302の後面に、CCDからの画像信号に基づき表示を行う有機ELパネル100を備える。そのため、この有機ELパネル100は、被写体を表示するファインダーとして機能する。光学レンズならびにCCDを有する受光ユニット1304が、ケース1302の前面(図の後方)に備わっている。

【0145】

撮影者が有機エレクトロルミネッセンス素子パネル100に表示された被写体画像を決定し、シャッターを開放するとCCDからの画像信号が伝送され、回路基板1308内のメモリに保存される。このデジタルスチルカメラ1300では、ケース1302の側面にビデオ信号出力端子1312及びデータ通信用入出力端子1314が設けられている。図示されるように、必要に応じて、TVモニタ1430及びパソコンコンピュータ1440を、それぞれ、ビデオ信号端子1312及び入出力端子1314に接続する。所定の操作により、回路基板1308のメモリに保存された画像信号が、TVモニタ1430及びパソコンコンピュータ1440への出力となる。

【0146】

本発明は、上述の電子機器の他、TVセット、ビューファインダー式及びモニタリング式のビデオテープ録画器、PDA端末、カーナビゲーションシステム、電子ノート、電卓、ワードプロセッサ、ワークステーション、TV電話、POSシステム端末、及びタッチパネル付きデバイス等における表示パネルとして使用可能である。

【0147】

また、本発明の発光装置は、プリンタ等の光源としても使用可能である。また、本発明にかかる画素駆動回路は、例えば、磁気抵抗RAM、コンデンサセンサ(capacitance sensor)、電荷センサ(charge sensor)、DNAセンサ、暗視カメラ、及びその他多くの装置などに応用可能である。

【0148】

また、本発明にかかる画素駆動回路は、有機/無機EL素子の駆動のみならず、レーザダイオード(LD)や発光ダイオードの駆動にも利用可能である。

【0149】

以上、説明したように、本発明によれば、回路構成を複雑化させることなく、エレクトロルミネッセンス(EL)素子のような自己発光素子を備えるアクティブマトリクス型発光装置の黒表示時における黒浮き(黒表示時においても不要な電流が流れ、これによって発光素子がわずかに発光して黒レベルが上昇し、コントラストが低下する現象)を効果的に防止することができる。

【0150】

10

20

30

40

50

本発明によれば、アクティブマトリクス型発光装置が高集積化されて、発光制御トランジスタと発光素子とが基板上でより近接して配置されたとしても、カップリング電流による黒浮きによる表示画像の画質低下が問題となることがない。

#### 【0151】

また、本発明は、電流プログラミング方式／電圧プログラミング方式のアクティブマトリクス型発光装置の双方に適用可能である。

#### 【0152】

駆動 TFT のしきい値電圧のばらつきを補償可能な電圧プログラミング方式のアクティブマトリクス型発光装置に本発明を適用した場合には、駆動トランジスタのしきい値電圧のばらつきによる駆動電流の変動を抑制するために、駆動トランジスタのオフ時（黒表示時）のリーク電流も低減され、さらに、カップリング電流による黒レベルの上昇が抑制されるため、所望のレベルの黒表示が確実に実現される。10

#### 【0153】

また、本発明のアクティブマトリクス型発光装置は、特別な回路を搭載する必要がないため、アクティブ回路基板が特に大型化する心配がなく、携帯端末のような小型の電子機器への搭載にも適する。

#### 【0154】

本発明のアクティブマトリクス型発光装置は、黒表示時におけるコントラストの低下を抑制するという効果を奏し、したがって、アクティブマトリクス型発光装置およびアクティブマトリクス型発光装置の画素駆動方法として有用であり、特に、エレクトロルミネッセンス（EL）素子のような自己発光素子を備えるアクティブマトリクス型発光装置の黒表示時における黒浮きを防止する技術として有用である。20

#### 【図面の簡単な説明】

#### 【0155】

【図1】本発明のアクティブマトリクス型発光装置の一例（電流プログラミング方式の有機ELパネル）の全体構成を示す回路図である。

【図2】図1のアクティブマトリクス型発光装置における、画素（画素回路）の具体的な回路構成ならびに走査線ドライバにおける出力バッファの回路構成とトランジスタサイズを示す回路図である。

#### 【図3】図2の回路におけるカップリング電流の低減効果を説明するための図である。

【図4】図2の画素回路における動作を説明するためのタイミング図である。

【図5】図5は、アクティブマトリクス型の有機ELパネルにおける画素の断面構造と採光方式について説明するためのデバイスの断面図であり、（a）はボトムエミッション型の構造を示す図であり、（b）はトップエミッション型の構造を示す図である。

【図6】本発明のアクティブマトリクス型発光装置の他の例（第2の走査線を駆動する出力バッファの出力端に電流制限抵抗を接続することによって電流駆動能力を低下させる例）の回路構成を示す回路図である。

【図7】本発明のアクティブマトリクス型発光装置の他の例の全体構成を示すブロック図である。

【図8】図7の有機EL表示パネルの要部（図7中、点線で囲まれるX部分）の具体的な回路構成例を示す回路図である。40

【図9】図8の画素（画素回路）の動作タイミングならびに駆動トランジスタのゲート電圧波形の変化を説明するための図である。

【図10】本発明のアクティブマトリクス型発光装置を用いた表示パネルの全体のレイアウト構成を示す図である。

【図11】図10の表示パネルを搭載したモバイルパーソナルコンピュータの外観を示す斜視図である。

#### 【図12】本発明の表示パネルを搭載した携帯電話端末の概観を示す斜視図である。

【図13】本発明の有機ELパネルをファインダーとして用いたデジタルスチルカメラの外観と使用態様を示す図である。50

【図14】アクティブマトリクス型画素回路における、TFTのリーク電流について説明するための図であり、(a)は画素回路の主要部の回路であり、(b)は、発光素子の動作に伴って生じるリーク電流の種類を説明するためのタイミング図である。

【図15】リーク電流のデューティ依存性に関して、リーク電流の評価式に基づくコンピュータシミュレーションを実施した結果と、発光素子に流れるリーク電流の実測値とを重ね合わせて示す図である。

### 【符号の説明】

#### 【0156】

21 ガラス基板、22 透明電極 (ITO)、23 有機発光層、

10 24 金属電極層、25 TFT回路、

100 (100a ~ 100d) 画素 (画素回路)、200 走査線ドライバ、

202 シフトレジスタ、300 データ線ドライバ、302 電流生成回路、

W1 (WL1 ~ WL3) 発光制御トランジスタ以外の制御トランジスタを駆動するための第1の走査線、

W2 (WL4) 発光制御トランジスタを駆動するための第2の走査線、

DL1, DL2 データ線、

DR1 第1の走査線を駆動するための第1の出力バッファ、

DR2 第2の走査線を駆動するための第2の出力バッファ、

M13 発光制御トランジスタ、M14 発光制御トランジスタ、

OLED 有機EL素子等の発光素子、Ch 保持コンデンサ、

VEL 画素電源電圧 (高レベル)、VCT 画素電源電圧 (低レベル)、

GWRD 書込み制御信号、GEL 発光制御信号 (発光制御パルス)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 2 2 E

テーマコード(参考)

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵发光装置，电子装置和有源矩阵发光装置的像素驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2008040326A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2008-02-21 |

| 申请号            | JP2006216956                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2006-08-09 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 北澤幸行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 北澤幸行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3233 G09G3/3266 G09G3/3283 G09G2300/0439 G09G2300/0819 G09G2300/0838 G09G2300/0842 G09G2300/0852 G09G2300/0866 G09G2300/0876 G09G2310/0262 G09G2310/0289 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.622.A G09G3/20.622.G G09G3/20.642.E G09G3/20.622.E G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD01 5C080/EE29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB11 5C380/AB12 5C380/AB22 5C380/AB23 5C380/AB24 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC10 5C380/AC11 5C380/AC12 5C380/AC13 5C380/BA38 5C380/BA39 5C380/BA40 5C380/BB02 5C380/BB23 5C380/BC02 5C380/BC03 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CA29 5C380/CB01 5C380/CB14 5C380/CB16 5C380/CB17 5C380/CB31 5C380/CC04 5C380/CC07 5C380/CC13 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC63 5C380/CC65 5C380/CD014 5C380/CD036 5C380/CF22 5C380/CF23 5C380/CF41 5C380/DA06 5C380/DA20 5C380/DA47 5C380/HA13 |         |            |

| 代理人(译)         | 井上一<br>托莫卡祖·纳米<br>黑田靖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | <a href="#">JP4281765B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

解决的问题：在有源矩阵发光器件中，在黑色显示期间有效地抑制对比度的降低，而不会使电路结构复杂化。扫描线驱动器（200）具有用于驱动发光控制TFT（M14）的扫描线（W2）和用于驱动其他控制晶体管（M11，M12）的扫描线的电流驱动能力。将其设置为低于（W1）的当前驱动器容量。结果，所谓的黑色显示期间的黑色浮动（即，发光控制信号（GEL）的电压变化分量通过发光控制TFT（M14）的栅极和源极之间的寄生电容传输到有机EL元件（OLED）一侧）。泄漏被抑制，具有大峰值的瞬时电流（耦合电流）流动，并且在黑色显示期间黑色电平增加的现象被抑制。[选择图]图2