(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-52432

(P2007-52432A)

(43) 公開日 平成19年3月1日(2007.3.1)

| (51) Int.C1.                | F 1                          | テーマコード (参考)                               |

|-----------------------------|------------------------------|-------------------------------------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30                    | J 3K107                                   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20                    | 611A 5C080                                |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20                    | 621E                                      |

|                             | G09G 3/20                    | 624B                                      |

|                             | G09G 3/20                    | 621A                                      |

|                             |                              | 審査請求 有 請求項の数 41 O L (全 30 頁) 最終頁に続く       |

| (21) 出願番号                   | 特願2006-221420 (P2006-221420) | (71) 出願人 590002817                        |

| (22) 出願日                    | 平成18年8月15日 (2006.8.15)       | 三星エスディアイ株式会社                              |

| (31) 優先権主張番号                | 10-2005-0075428              | 大韓民国京畿道水原市靈通区▲しん▼洞5                       |

| (32) 優先日                    | 平成17年8月17日 (2005.8.17)       | 75番地                                      |

| (33) 優先権主張国                 | 韓国 (KR)                      | (74) 代理人 100095957                        |

| (31) 優先権主張番号                | 10-2005-0075429              | 弁理士 龟谷 美明                                 |

| (32) 優先日                    | 平成17年8月17日 (2005.8.17)       | (74) 代理人 100096389                        |

| (33) 優先権主張国                 | 韓国 (KR)                      | 弁理士 金本 哲男                                 |

|                             |                              | (72) 発明者 鄭 貢容                             |

|                             |                              | 大韓民国京畿道水原市靈通区▲シン▼洞5                       |

|                             |                              | 75番地 三星エスディアイ株式会社内                        |

|                             |                              | F ターム (参考) 3K107 AA01 BB01 CC42 CC45 EE03 |

|                             |                              | HH00 HH04                                 |

|                             |                              | 5C080 AA06 BB05 DD22 DD26 EE28            |

|                             |                              | FF11 JJ02 JJ03 JJ04                       |

(54) 【発明の名称】有機電界発光表示装置、発光制御駆動装置および論理和回路

## (57) 【要約】

【課題】E-L表示パネルの内部にSOP型で設計される新しい形態の発光制御駆動装置とこれを備えた有機電界発光表示装置、および論理和回路を提供する。

【解決手段】複数の画素を有する画素部12と、走査信号を印加する走査駆動部14と、データ信号を印加するデータ駆動部20と、発光制御信号を印加する発光制御駆動部16とを備え、発光制御駆動部16は、複数のフリップフロップを有するシフトレジスタと、シフトレジスタ内のそれぞれ隣接する2つのフリップフロップから、第1出力信号OUTnおよび反転された第1出力信号OUTBnと、第2出力信号OUTn+1および反転された第2出力信号OUTBn+1との合わせて4つの信号を入力されて能動負荷を制御し、論理和の演算により発光制御信号を出力する論理ゲートを複数有する論理演算部とから構成される有機電界発光表示装置が提供される。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

所定の映像を表示する複数の画素を有する画素部と；

前記複数の画素を順次に選択する走査信号を印加する走査駆動部と；

前記走査信号により選択された画素にデータ信号を印加するデータ駆動部と；

前記複数の画素の発光を制御する発光制御信号を印加する発光制御駆動部と；

を備え、

前記発光制御駆動部は、

開始パルスを入力され、クロック信号および反転されたクロック信号に同期して出力信号を生成するフリップフロップと、一段前のフリップフロップの前記出力信号を新たな入力とし、前記クロック信号および前記反転されたクロック信号に同期して新たな出力信号を生成する、複数のフリップフロップとを有するシフトレジスタと；

前記シフトレジスタ内のそれぞれ隣接する2つのフリップフロップから、第1出力信号および反転された第1出力信号と、第2出力信号および反転された第2出力信号との合わせて4つの信号が入力され、前記4つの信号を用いて能動負荷を制御し、前記第1出力信号および前記第2出力信号に対する論理和の演算により発光制御信号を出力する論理ゲートを複数有する論理演算部と；

から構成されることを特徴とする、有機電界発光表示装置。

## 【請求項 2】

前記複数のフリップフロップそれぞれは、

前記反転されたクロック信号の立ち下がりエッジで入力信号をサンプリングする第1トランジスタと；

前記第1トランジスタの出力信号を反転するための第1インバータと；

前記クロック信号の立ち下がりエッジで前記第1インバータの出力信号をサンプリングする第2トランジスタと；

前記第2トランジスタの出力信号を反転する第2インバータと；

を含むことを特徴とする、請求項1に記載の有機電界発光表示装置。

## 【請求項 3】

前記それぞれの隣接するフリップフロップは、前記第2トランジスタの出力信号と前記第2インバータの出力信号とを前記論理ゲートに印加することを特徴とする、請求項2に記載の有機電界発光表示装置。

## 【請求項 4】

前記第1インバータおよび第2インバータは、

正の電源電圧が印加される端子と出力端子との間に連結され、前記フリップフロップの第1トランジスタ、または第2トランジスタを介して伝達される信号に基づいてオン／オフ動作を行う第3トランジスタと；

負の電源電圧が印加される端子と前記出力端子との間に連結され、前記第3トランジスタのオン／オフに基づいて出力電流量を制御する第4トランジスタと；

を含むことを特徴とする、請求項3に記載の有機電界発光表示装置。

## 【請求項 5】

前記第1インバータおよび第2インバータは、前記第4トランジスタのゲート端子とドレイン端子との間に連結され、前記第4トランジスタのゲート電圧を制御するダイオード連結した第5トランジスタをさらに含むことを特徴とする、請求項4に記載の有機電界発光表示装置。

## 【請求項 6】

前記第3トランジスタのオン抵抗は、前記第4トランジスタのオン抵抗より小さいことを特徴とする、請求項5に記載の有機電界発光表示装置。

## 【請求項 7】

前記第1インバータおよび第2インバータは、前記第4トランジスタのソース端子とゲート端子との間に連結され、前記第5トランジスタがオフとなった時、前記第4トランジ

スタのソース - ゲート間の電圧を維持するキャパシタをさらに含むことを特徴とする、請求項 6 に記載の有機電界発光表示装置。

【請求項 8】

前記第 1 ~ 第 5 トランジスタは、PMOS トランジスタであることを特徴とする、請求項 7 に記載の有機電界発光表示装置。

【請求項 9】

前記複数の論理ゲートそれぞれは、

第 1 電源電圧が印加される端子に連結され、前記隣接する 2 つのフリップフロップから出力される前記第 1 出力信号と前記第 2 出力信号とのレベル状態に基づいてオン / オフ動作を行う入力部と；

前記入力部と第 2 電源電圧が印加される端子との間に連結され、前記隣接する 2 つのフリップフロップから出力される 2 つの反転された出力信号のレベル状態に基づいて選択的にダイオード連結される第 6 トランジスタを有する第 1 能動負荷と；

前記第 1 電源電圧が印加される端子と発光制御線との間に連結され、前記入力部または前記第 1 能動負荷の出力信号レベル状態に基づいてオン / オフ動作を行う出力トランジスタと；

前記第 2 電源電圧が印加される端子と前記発光制御線との間に連結され、前記隣接する 2 つのフリップフロップから出力される 2 つの出力信号のレベル状態に基づいて選択的にダイオード連結される第 7 トランジスタを有する第 2 能動負荷と；

を含むことを特徴とする、請求項 1 に記載の有機電界発光表示装置。

10

20

30

30

40

50

【請求項 10】

前記入力部は、

前記第 1 電源電圧が印加される端子に連結され、前記第 1 出力信号のレベル状態に基づいてオン / オフ動作を行う第 8 トランジスタと；

前記第 8 トランジスタと直列に連結され、前記第 2 出力信号のレベル状態に基づいてオン / オフ動作を行う第 9 トランジスタと；

から構成されることを特徴とする、請求項 9 に記載の有機電界発光表示装置。

【請求項 11】

前記第 1 能動負荷は、

前記第 6 トランジスタのゲートとドレインとの間に連結され、前記反転された第 1 出力信号のレベル状態に基づいてオン / オフ動作を行う第 10 トランジスタと；

前記第 10 トランジスタと並列に連結され、前記反転された第 2 出力信号のレベル状態に基づいてオン / オフ動作を行う第 11 トランジスタと；

をさらに含み、

前記反転された第 1 出力信号および前記反転された第 2 出力信号が共にハイレベルの信号である場合、前記第 1 能動負荷に流れる電流は遮断されることを特徴とする、請求項 10 に記載の有機電界発光表示装置。

【請求項 12】

前記第 2 能動負荷は、

前記第 7 トランジスタのゲートに連結され、前記第 1 出力信号のレベル状態に基づいてオン / オフ動作を行う第 12 トランジスタと；

前記第 12 トランジスタに直列連結され、前記第 2 出力信号のレベル状態に基づいてオン / オフ動作を行う第 13 トランジスタと；

をさらに含み、

前記第 1 出力信号と前記第 2 出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、前記第 2 能動負荷に流れる電流は遮断されることを特徴とする、請求項 11 に記載の有機電界発光表示装置。

【請求項 13】

前記複数の論理ゲートそれぞれは、

前記第 6 トランジスタのソース端子に連結され、前記第 1 出力信号のレベル状態に基づ

いてオン／オフ動作を行う第14トランジスタと；

前記第14トランジスタと直列に連結され、前記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタと；

を有するスイッチング部をさらに含み、

前記第1出力信号および前記第2出力信号がローレベルである場合、前記第6トランジスタをオフさせて、前記第1能動負荷に流れる電流を遮断することを特徴とする、請求項12に記載の有機電界発光表示装置。

【請求項14】

前記複数の論理ゲートそれぞれは、

前記第6トランジスタのソース端子とゲート端子との間に連結され、前記第6トランジスタのソース-ゲート間の電圧を維持する第1キャパシタと；

前記第7トランジスタのソース端子とゲート端子との間に連結され、前記第7トランジスタのソース-ゲート間の電圧を維持する第2キャパシタと；

をさらに含むことを特徴とする、請求項13に記載の有機電界発光表示装置。

【請求項15】

前記複数の論理ゲートそれぞれは、前記第2キャパシタの両端に連結され、前記入力部または前記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むことを特徴とする、請求項14に記載の有機電界発光表示装置。

【請求項16】

前記第6～第16トランジスタは、PMOSトランジスタであることを特徴とする、請求項15に記載の有機電界発光表示装置。

【請求項17】

前記画素部、前記走査駆動部、前記データ駆動部および前記発光制御駆動部は、1つの基板上に形成されることを特徴とする、請求項1に記載の有機電界発光表示装置。

【請求項18】

前記有機電界発光表示装置は、複数の有機電界発光表示装置がタイル形態で結合して1つの映像を表示することを特徴とする、請求項1に記載の有機電界発光表示装置。

【請求項19】

開始パルスを入力され、クロック信号および反転されたクロック信号に同期する第1出力信号を生成する第1フリップフロップと；

前記第1フリップフロップの出力信号が入力され、前記クロック信号および前記反転されたクロック信号に同期する第2出力信号を生成する第2フリップフロップと；

前記第1出力信号および反転された第1出力信号、並びに前記第2出力信号および反転された第2出力信号が入力され、前記第1フリップフロップと前記第2フリップフロップから出力された4つの信号を用いて能動負荷を制御し、前記第1出力信号と前記第2出力信号との論理和の演算により発光制御信号を出力する論理ゲートと；

を含むことを特徴とする発光制御駆動装置。

【請求項20】

前記複数のフリップフロップそれぞれは、

前記反転されたクロック信号の立ち下がりエッジで入力信号をサンプリングする第1トランジスタと；

前記第1トランジスタの出力信号を反転するための第1インバータと；

前記クロック信号の立ち下がりエッジで前記第1インバータの出力信号をサンプリングする第2トランジスタと；

前記第2トランジスタの出力信号を反転する第2インバータと；

を含むことを特徴とする、請求項19に記載の発光制御駆動装置。

【請求項21】

前記第1インバータおよび第2インバータは、

正の電源電圧が印加される端子と出力端子との間に連結され、前記フリップフロップの

10

20

30

40

50

第1トランジスタ、または第2トランジスタを介して伝達される信号に基づいてオン／オフ動作を行う第3トランジスタと；

負の電源電圧が印加される端子と前記出力端子との間に連結され、前記第3トランジスタのオン／オフに基づいて出力電流量を制御する第4トランジスタと；

を含むことを特徴とする、請求項20に記載の発光制御駆動装置。

【請求項22】

前記第1インバータおよび第2インバータは、前記第4トランジスタのゲート端子とドレイン端子との間に連結され、前記第4トランジスタのゲート電圧を制御するダイオード連結した第5トランジスタをさらに含むことを特徴とする、請求項21に記載の発光制御駆動装置。

10

【請求項23】

前記第3トランジスタのオン抵抗は、前記第4トランジスタのオン抵抗より小さいことを特徴とする、請求項22に記載の発光制御駆動装置。

【請求項24】

前記第1インバータおよび第2インバータは、前記第4トランジスタのソース端子とゲート端子との間に連結され、前記第5トランジスタがオフとなった時、前記第4トランジスタのソース-ゲート間の電圧を維持するキャパシタをさらに含むことを特徴とする、請求項23に記載の発光制御駆動装置。

【請求項25】

前記第1～第5トランジスタは、PMOSトランジスタであることを特徴とする、請求項24に記載の発光制御駆動装置。

20

【請求項26】

前記複数の論理ゲートそれぞれは、

第1電源電圧が印加される端子に連結され、前記第1出力信号および前記第2出力信号のレベル状態に基づいてオン／オフ動作を行う入力部と；

前記入力部と第2電源電圧が印加される端子との間に連結され、前記反転された第1出力信号または前記反転された第2出力信号のレベル状態に基づいて選択的にダイオード連結される第6トランジスタを有する第1能動負荷と；

前記第1電源電圧が印加される端子と発光制御線との間に連結され、前記入力部または前記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う出力トランジスタと；

前記第2電源電圧が印加される端子と前記発光制御線との間に連結され、前記第1出力信号および前記第2出力信号のレベル状態に基づいて選択的にダイオード連結される第7トランジスタを有する第2能動負荷と；

を含むことを特徴とする、請求項19に記載の発光制御駆動装置。

30

【請求項27】

前記入力部は、

前記第1電源電圧が印加される端子に連結され、前記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第8トランジスタと；

前記第8トランジスタと直列に連結され、前記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第9トランジスタと；

から構成されることを特徴とする、請求項26に記載の発光制御駆動装置。

40

【請求項28】

前記第1能動負荷は、

前記第6トランジスタのゲートとドレインとの間に連結され、前記反転された第1出力信号のレベル状態に基づいてオン／オフ動作を行う第10トランジスタと；

前記第10トランジスタと並列に連結され、前記反転された第2出力信号のレベル状態に基づいてオン／オフ動作を行う第11トランジスタと；

をさらに含み、

前記反転された第1出力信号および前記反転された第2出力信号が共にハイレベルの信

50

号である場合、前記第1能動負荷に流れる電流は遮断されることを特徴とする、請求項27に記載の発光制御駆動装置。

【請求項29】

前記第2能動負荷は、

前記第7トランジスタのゲートに連結され、前記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第12トランジスタと；

前記第12トランジスタに直列連結され、前記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第13トランジスタと；

をさらに含み、

前記第1出力信号と前記第2出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、前記第2能動負荷に流れる電流は遮断されることを特徴とする、請求項28に記載の発光制御駆動装置。 10

【請求項30】

前記複数の論理ゲートそれぞれは、

前記第6トランジスタのソース端子に連結され、前記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第14トランジスタと；

前記第14トランジスタに直列連結され、前記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタと；

を有するスイッチング部をさらに含み、

前記第1出力信号および前記第2出力信号がローレベルである場合、前記第6トランジスタをオフさせて、前記第1能動負荷に流れる電流を遮断することを特徴とする請求項29に記載の発光制御駆動装置。 20

【請求項31】

前記複数の論理ゲートそれぞれは、

前記第6トランジスタのソース端子とゲート端子との間に連結され、前記第6トランジスタのソース－ゲート間の電圧を維持する第1キャパシタと；

前記第2トランジスタのソース端子とゲート端子との間に連結され、前記第7トランジスタのソース－ゲート間の電圧を維持する第2キャパシタと；

をさらに含むことを特徴とする、請求項30に記載の発光制御駆動装置。 30

【請求項32】

前記複数の論理ゲートそれぞれは、前記第2キャパシタの両端に連結され、前記入力部または前記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むことを特徴とする請求項31に記載の発光制御駆動装置。 40

【請求項33】

前記第6～第16トランジスタは、PMOSトランジスタであることを特徴とする、請求項32に記載の発光制御駆動装置。

【請求項34】

第1電源電圧が印加される端子に連結され、第1入力信号および第2入力信号のレベル状態に基づいてオン／オフ動作を行う入力部と；

前記入力部と第2電源電圧が印加される端子との間に連結され、反転された第1入力信号または反転された第2入力信号のレベル状態に基づいて選択的にダイオード連結される第6トランジスタを有する第1能動負荷と；

前記第1電源電圧が印加される端子と発光制御線との間に連結され、前記入力部または前記第1能動負荷の出力信号レベル状態に基づいてオン／オフ動作を行う出力トランジスタと；

前記第2電源電圧が印加される端子と前記発光制御線との間に連結され、前記第1入力信号および前記第2入力信号のレベル状態に基づいて選択的にダイオード連結される第7トランジスタとを有する第2能動負荷と；

を含むことを特徴とする、論理和回路。

【請求項35】

10

20

30

40

50

前記入力部は、

前記第1電源電圧が印加される端子に連結され、前記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第8トランジスタと；

前記第3トランジスタと直列に連結され、前記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第9トランジスタと；

から構成されることを特徴とする、請求項34に記載の論理和回路。

【請求項36】

前記第1能動負荷は、

前記第6トランジスタのゲートとドレインとの間に連結され、前記反転された第1入力信号のレベル状態に基づいてオン／オフ動作を行う第10トランジスタと；

前記第10トランジスタと並列に連結され、前記反転された第2入力信号のレベル状態に基づいてオン／オフ動作を行う第11トランジスタと；

をさらに含み、

前記反転された第1入力信号および前記反転された第2入力信号が共にハイレベルの信号である場合、前記第1能動負荷に流れる電流は遮断されることを特徴とする、請求項35に記載の論理和回路。

【請求項37】

前記第2能動負荷は、

前記第7トランジスタのゲートに連結され、前記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第12トランジスタと；

前記第12トランジスタに直列連結され、前記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第13トランジスタと；

をさらに含み、

前記第1出力信号と前記第2出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、前記第2能動負荷に流れる電流は遮断されることを特徴とする、請求項36に記載の論理和回路。

【請求項38】

前記複数の論理ゲートそれぞれは、

前記第6トランジスタのソース端子に連結され、前記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第14トランジスタと；

前記第14トランジスタと直列に連結され、前記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタとを有するスイッチング部と；

をさらに含み、

前記第1入力信号および前記第2入力信号がローレベルである時、前記第6トランジスタをオフさせて、前記第1能動負荷に流れる電流を遮断することを特徴とする、請求項37に記載の論理和回路。

【請求項39】

前記複数の論理ゲートそれぞれは、

前記第6トランジスタのソース端子とゲート端子との間に連結され、前記第6トランジスタのソース-ゲート間の電圧を維持する第1キャパシタと；

前記第7トランジスタのソース端子とゲート端子との間に連結され、前記第7トランジスタのソース-ゲート間の電圧を維持する第2キャパシタと；

をさらに含むことを特徴とする、請求項38に記載の論理和回路。

【請求項40】

前記複数の論理ゲートそれぞれは、

前記第2キャパシタの両端に連結され、前記入力部または前記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むことを特徴とする、請求項39に記載の論理和回路。

【請求項41】

前記第1～第11トランジスタは、PMOSトランジスタであることを特徴とする、請

10

20

30

40

50

求項 4 0 に記載の論理和回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機電界発光表示装置、発光制御駆動装置および論理和回路に関し、より詳細には、画素の発光を制御する信号を発生する SOP ( System On Panel ) 形態の発光制御駆動装置、これを備えた有機電界発光表示装置、および論理和回路に関する。

【背景技術】

【0002】

平板表示装置は、陰極線管を用いた表示装置より重さや容積を低減することができるという長所があるため、研究開発が進んでいる。これにより、液晶表示装置 ( LCD ; Liquid Crystal Display ) 、電界放出表示装置 ( FED ; Field Emission Display ) 、プラズマディスプレイパネル ( PDP ; Plasma Display Panel ) および有機電界発光表示装置 ( Organic Electroluminescent Display Device ; 以下、「有機 EL 表示装置」という) 等が開発され実用化されている。これらのうち PDP は、大型画面化が可能であるが、発光効率と輝度が低いため、消費電力が大きいという問題がある。また、LCD は、応答速度が遅く、バックライトにより発光するため、消費電力が大きいという問題がある。

【0003】

これらに対して、有機 EL 表示装置は、有機物質を用いて発光させるものであって、LCD に比べて視野角が広く、応答速度が速く、そして自発光素子によりコントラストが良好であり、視認性に優れている。また、バックライトが不要なので、消費電力が少なく、薄形化および軽量化が可能である。

【0004】

しかしながら、有機 EL 表示装置は、大型画面を構成する場合、製造プロセスの制約から、ガラス基板 1 枚から製造できる EL 表示パネルの大きさが制限される。また、大画面の場合、画面の一部に欠陥が発生した場合、収率の低下が回避できず、画面内の均一性の確保も困難となる。

【0005】

上記のような大型画面を構成しがたい有機 EL 表示装置についての解決方法の 1 つとして開発された技術が、タイルリング ( Tiling ) 技術であり、これは、複数の小型の EL 表示パネルを接合させて、1 つの大型のパネルを形成する方法である。

【0006】

各小型の EL 表示パネルは、従来の EL 表示パネルと同様に所定の映像を表示する複数の画素よりなる。上記複数の画素を活性化するために、走査駆動部は、走査信号を印加し、データ駆動部は、走査信号が印加された画素にデータ信号を印加する。また、上記データ信号の正確なプログラミングと発光タイムを制御するために、発光制御駆動部から各画素に発光制御信号を印加する。

【0007】

また、小型の EL 表示パネルを駆動するための多様な信号を印加する走査駆動部、データ駆動部および発光制御駆動部は、多様な方式で各小型の EL 表示パネルと電気的に連結される。

【0008】

例えば、各小型の EL 表示パネルに接着され電気的に連結されているテープキャリアパッケージ ( Tape Carrier Package ; TCP ) にチップ等の形態で装着することができる。また、各小型の EL 表示パネルに接着され電気的に連結されている可撓性印刷回路 ( Flexible Printed Circuit ; FPC ) 、またはフィルム ( film ) 等にチップ等の形態で装着することができる。これを COF ( C

10

20

30

40

50

hip On Flexible board、またはChip On Film)方式という。これとは異なって、EL表示パネルのガラス基板上に直接チップ等の形態で装着したものは、COG (Chip On Glass) 方式とよばれる。これらの方法は、各駆動部を別々に設計し、電気的に連結するので、費用が多くかかり、また、モジュールの簡素化に向かないという問題がある。

#### 【0009】

したがって、近年、EL表示パネルの内部に画素部、走査／発光制御駆動部、および／またはデータ駆動部を設計し、1つのEL表示パネルにあらゆるシステムを構築する試みがなされている。これをSOP (System On Panel) という。

#### 【0010】

タイルリング (Tiling) 技術を用いた大型の有機EL表示装置である場合、複数の小型のパネルを接合するので、各小型のEL表示パネルをCOF型やCOG型等で製作するよりも、SOP型で製作する方が、各小型のEL表示パネルを接合しやすい。また、各駆動部が占める面積を低減することができ、各駆動部の集積回路を設計するに要する費用や時間を軽減することができる。

#### 【0011】

しかし、SOP型の有機EL表示装置を開発するためには、データ駆動部または走査／発光制御駆動部における駆動周波数や電子移動度等のような、EL表示パネル内部の様々な事情や条件を考慮する必要がある。現行の技術水準では、データ駆動部は高周波数での駆動を必要とするため、データ駆動部をパネルの内部に設計することは、非常に困難である。

#### 【0012】

したがって、データ駆動部は、CMOS技術を用いた集積回路の形態で外部から連結され、走査駆動部または／および発光制御駆動部は、EL表示パネルの内部に形成される。それゆえ、SOP型の有機EL表示装置を実現するために、走査駆動部および発光制御駆動部が、EL表示パネルの内部で最適な駆動を行うことが可能な、簡易な回路構成が必要とされている。

#### 【0013】

【特許文献1】特開2004-第054058号公報

【特許文献2】特開2004-第070300号公報

【特許文献3】大韓民国特許第0381063号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

本発明の目的は、EL表示パネルの内部にSOP型で設計され、画素の発光を制御するための発光制御信号を生成する新しい形態の発光制御駆動装置とこれを備えた有機電界発光表示装置、および論理和回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0015】

上記目的を達成するために、本発明のある観点によれば、所定の映像を表示する複数の画素を有する画素部と、上記複数の画素を順次に選択する走査信号を印加する走査駆動部と、上記走査信号により選択された画素にデータ信号を印加するデータ駆動部と、上記複数の画素の発光を制御する発光制御信号を印加する発光制御駆動部とを備え、上記発光制御駆動部は、開始パルスを入力され、クロック信号および反転されたクロック信号に同期して出力信号を生成するフリップフロップと、一段前のフリップフロップの上記出力信号を新たな入力とし、上記クロック信号および上記反転されたクロック信号に同期して新たな出力信号を生成する、複数のフリップフロップとを有するシフトレジスタと、上記シフトレジスタ内のそれぞれ隣接する2つのフリップフロップから、第1出力信号および反転された第1出力信号と、第2出力信号および反転された第2出力信号との合わせて4つの信号が入力され、上記4つの信号を用いて能動負荷を制御し、上記第1出力信号および上記第2出力信号を用いて能動負荷を制御する。

10

20

30

40

50

記第2出力信号に対する論理和の演算により発光制御信号を出力する論理ゲートを複数有する論理演算部とから構成される有機電界発光表示装置が提供される。

【0016】

また、上記複数のフリップフロップそれぞれは、上記反転されたクロック信号の立ち下がりエッジで入力信号をサンプリングする第1トランジスタと、上記第1トランジスタの出力信号を反転するための第1インバータと、上記クロック信号の立ち下がりエッジで上記第1インバータの出力信号をサンプリングする第2トランジスタと、上記第2トランジスタの出力信号を反転する第2インバータとを含むとしてもよい。

【0017】

また、上記それぞれの隣接するフリップフロップは、上記第2トランジスタの出力信号と上記第2インバータの出力信号とを上記論理ゲートに印加するとしてもよい。

【0018】

また、上記第1インバータおよび第2インバータは、正の電源電圧が印加される端子と出力端子との間に連結され、上記フリップフロップの第1トランジスタ、または第2トランジスタを介して伝達される信号に基づいてオン／オフ動作を行う第3トランジスタと、負の電源電圧が印加される端子と上記出力端子との間に連結され、上記第3トランジスタのオン／オフに基づいて出力電流量を制御する第4トランジスタとを含むとしてもよい。

【0019】

また、上記第1インバータおよび第2インバータは、上記第4トランジスタのゲート端子とドレイン端子との間に連結され、上記第4トランジスタのゲート電圧を制御するダイオード連結した第5トランジスタをさらに含むとしてもよい。

【0020】

また、上記第3トランジスタのオン抵抗は、上記第4トランジスタのオン抵抗より小さいとしてもよい。

【0021】

また、上記第1インバータおよび第2インバータは、上記第4トランジスタのソース端子とゲート端子との間に連結され、上記第5トランジスタがオフとなった時、上記第4トランジスタのソース-ゲート間の電圧を維持するキャパシタをさらに含むとしてもよい。

【0022】

また、上記第1～第5トランジスタは、PMOSトランジスタであるとしてもよい。

【0023】

また、上記複数の論理ゲートそれぞれは、第1電源電圧が印加される端子に連結され、上記隣接する2つのフリップフロップから出力される上記第1出力信号と上記第2出力信号とのレベル状態に基づいてオン／オフ動作を行う入力部と、上記入力部と第2電源電圧が印加される端子との間に連結され、上記隣接する2つのフリップフロップから出力される2つの反転された出力信号のレベル状態に基づいて選択的にダイオード連結される第6トランジスタを有する第1能動負荷と、上記第1電源電圧が印加される端子と発光制御線との間に連結され、上記入力部または上記第1能動負荷の出力信号レベル状態に基づいてオン／オフ動作を行う出力トランジスタと、上記第2電源電圧が印加される端子と上記発光制御線との間に連結され、上記隣接する2つのフリップフロップから出力される2つの出力信号のレベル状態に基づいて選択的にダイオード連結される第7トランジスタを有する第2能動負荷とを含むとしてもよい。

【0024】

また、上記入力部は、上記第1電源電圧が印加される端子に連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第8トランジスタと、上記第8トランジスタと直列に連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第9トランジスタとから構成されるとしてもよい。

【0025】

また、上記第1能動負荷は、上記第6トランジスタのゲートとドレインとの間に連結され、上記反転された第1出力信号のレベル状態に基づいてオン／オフ動作を行う第10ト

10

20

30

40

50

ランジスタと、上記第10トランジスタと並列に連結され、上記反転された第2出力信号のレベル状態に基づいてオン／オフ動作を行う第11トランジスタとをさらに含み、上記反転された第1出力信号および上記反転された第2出力信号が共にハイレベルの信号である場合、上記第1能動負荷に流れる電流は遮断されるとしてもよい。

【0026】

また、上記第2能動負荷は、上記第7トランジスタのゲートに連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第12トランジスタと、上記第12トランジスタに直列連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第13トランジスタとをさらに含み、上記第1出力信号と上記第2出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、上記第2能動負荷に流れる電流は遮断されるとしてもよい。

10

【0027】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子に連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第14トランジスタと、上記第14トランジスタと直列に連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタとを有するスイッチング部をさらに含み、上記第1出力信号および上記第2出力信号がローレベルである場合、上記第6トランジスタをオフさせて、上記第1能動負荷に流れる電流を遮断するとしてもよい。

【0028】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子とゲート端子との間に連結され、上記第6トランジスタのソース－ゲート間の電圧を維持する第1キャパシタと、上記第7トランジスタのソース端子とゲート端子との間に連結され、上記第7トランジスタのソース－ゲート間の電圧を維持する第2キャパシタとをさらに含むとしてもよい。

20

【0029】

また、上記複数の論理ゲートそれぞれは、上記第2キャパシタの両端に連結され、上記入力部または上記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むとしてもよい。

【0030】

また、上記第6～第16トランジスタは、PMOSトランジスタであるとしてもよい。

30

【0031】

また、上記画素部、上記走査駆動部、上記データ駆動部および上記発光制御駆動部は、1つの基板上に形成されるとしてもよい。

【0032】

また、上記有機電界発光表示装置は、複数の有機電界発光表示装置がタイル形態で結合して1つの映像を表示するとしてもよい。

【0033】

また、上記目的を達成するために、本発明の別の観点によれば、開始パルスを入力され、クロック信号および反転されたクロック信号に同期する第1出力信号を生成する第1フリップフロップと、上記第1フリップフロップの出力信号が入力され、上記クロック信号および上記反転されたクロック信号に同期する第2出力信号を生成する第2フリップフロップと、上記第1出力信号および反転された第1出力信号、並びに上記第2出力信号および反転された第2出力信号が入力され、上記第1フリップフロップと上記第2フリップフロップから出力された4つの信号を用いて能動負荷を制御し、上記第1出力信号と上記第2出力信号との論理和の演算により発光制御信号を出力する論理ゲートとを含む発光制御駆動装置が提供される。

40

【0034】

また、上記複数のフリップフロップそれぞれは、上記反転されたクロック信号の立ち下がりエッジで入力信号をサンプリングする第1トランジスタと、上記第1トランジスタの出力信号を反転するための第1インバータと、上記クロック信号の立ち下がりエッジで上

50

記第1インバータの出力信号をサンプリングする第2トランジスタと、上記第2トランジスタの出力信号を反転する第2インバータとを含むとしてもよい。

【0035】

また、上記第1インバータおよび第2インバータは、正の電源電圧が印加される端子と出力端子との間に連結され、上記フリップフロップの第1トランジスタ、または第2トランジスタを介して伝達される信号に基づいてオン／オフ動作を行う第3トランジスタと、負の電源電圧が印加される端子と上記出力端子との間に連結され、上記第3トランジスタのオン／オフに基づいて出力電流量を制御する第4トランジスタとを含むとしてもよい。

【0036】

また、上記第1インバータおよび第2インバータは、上記第4トランジスタのゲート端子とドレイン端子との間に連結され、上記第4トランジスタのゲート電圧を制御するダイオード連結した第5トランジスタをさらに含むとしてもよい。

【0037】

また、上記第3トランジスタのオン抵抗は、上記第4トランジスタのオン抵抗より小さいとしてもよい。

【0038】

また、上記第1インバータおよび第2インバータは、上記第4トランジスタのソース端子とゲート端子との間に連結され、上記第5トランジスタがオフとなった時、上記第4トランジスタのソース - ゲート間の電圧を維持するキャパシタをさらに含むとしてもよい。

【0039】

また、上記第1～第5トランジスタは、PMOSトランジスタであるとしてもよい。

【0040】

また、上記複数の論理ゲートそれぞれは、第1電源電圧が印加される端子に連結され、上記第1出力信号および上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う入力部と、上記入力部と第2電源電圧が印加される端子との間に連結され、上記反転された第1出力信号または上記反転された第2出力信号のレベル状態に基づいて選択的にダイオード連結される第6トランジスタを有する第1能動負荷と、上記第1電源電圧が印加される端子と発光制御線との間に連結され、上記入力部または上記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う出力トランジスタと、上記第2電源電圧が印加される端子と上記発光制御線との間に連結され、上記第1出力信号および上記第2出力信号のレベル状態に基づいて選択的にダイオード連結される第7トランジスタを有する第2能動負荷とを含むとしてもよい。

【0041】

また、上記入力部は、上記第1電源電圧が印加される端子に連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第8トランジスタと、上記第8トランジスタと直列に連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第9トランジスタとから構成されるとしてもよい。

【0042】

また、上記第1能動負荷は、上記第6トランジスタのゲートとドレインとの間に連結され、上記反転された第1出力信号のレベル状態に基づいてオン／オフ動作を行う第10トランジスタと、上記第10トランジスタと並列に連結され、上記反転された第2出力信号のレベル状態に基づいてオン／オフ動作を行う第11トランジスタとをさらに含み、上記反転された第1出力信号および上記反転された第2出力信号が共にハイレベルの信号である場合、上記第1能動負荷に流れる電流は遮断されるとしてもよい。

【0043】

また、上記第2能動負荷は、上記第7トランジスタのゲートに連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第12トランジスタと、上記第12トランジスタに直列連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第13トランジスタとをさらに含み、上記第1出力信号と上記第2出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、上記第2能動負荷に流れる電

10

20

30

40

50

流は遮断されるとしてもよい。

【0044】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子に連結され、上記第1出力信号のレベル状態に基づいてオン／オフ動作を行う第14トランジスタと、上記第14トランジスタに直列連結され、上記第2出力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタとを有するスイッチング部をさらに含み、上記第1出力信号および上記第2出力信号がローレベルである場合、上記第6トランジスタをオフさせて、上記第1能動負荷に流れる電流を遮断するとしてもよい。

【0045】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子とゲート端子との間に連結され、上記第6トランジスタのソース－ゲート間の電圧を維持する第1キャパシタと、上記第2トランジスタのソース端子とゲート端子との間に連結され、上記第7トランジスタのソース－ゲート間の電圧を維持する第2キャパシタとをさらに含むとしてもよい。

【0046】

また、上記複数の論理ゲートそれぞれは、上記第2キャパシタの両端に連結され、上記入力部または上記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むとしてもよい。

【0047】

また、上記第6～第16トランジスタは、PMOSトランジスタであるとしてもよい。

【0048】

また、上記目的を達成するために、本発明のさらに別の観点によれば、第1電源電圧が印加される端子に連結され、第1入力信号および第2入力信号のレベル状態に基づいてオン／オフ動作を行う入力部と、上記入力部と第2電源電圧が印加される端子との間に連結され、反転された第1入力信号または反転された第2入力信号のレベル状態に基づいて選択的にダイオード連結される第6トランジスタを有する第1能動負荷と、上記第1電源電圧が印加される端子と発光制御線との間に連結され、上記入力部または上記第1能動負荷の出力信号レベル状態に基づいてオン／オフ動作を行う出力トランジスタと、上記第2電源電圧が印加される端子と上記発光制御線との間に連結され、上記第1入力信号および上記第2入力信号のレベル状態に基づいて選択的にダイオード連結される第7トランジスタとを有する第2能動負荷とを含む論理回路が提供される。

【0049】

また、上記入力部は、上記第1電源電圧が印加される端子に連結され、上記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第8トランジスタと、上記第3トランジスタと直列に連結され、上記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第9トランジスタとから構成されるとしてもよい。

【0050】

また、上記第1能動負荷は、上記第6トランジスタのゲートとドレインとの間に連結され、上記反転された第1入力信号のレベル状態に基づいてオン／オフ動作を行う第10トランジスタと、上記第10トランジスタと並列に連結され、上記反転された第2入力信号のレベル状態に基づいてオン／オフ動作を行う第11トランジスタとをさらに含み、上記反転された第1入力信号および上記反転された第2入力信号が共にハイレベルの信号である場合、上記第1能動負荷に流れる電流は遮断されるとしてもよい。

【0051】

また、上記第2能動負荷は、上記第7トランジスタのゲートに連結され、上記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第12トランジスタと、上記第12トランジスタに直列連結され、上記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第13トランジスタとをさらに含み、上記第1出力信号と上記第2出力信号とのうち、少なくとも一方の信号のレベルがハイレベルである場合、上記第2能動負荷に流れる電流は遮断されるとしてもよい。

10

20

30

40

50

## 【0052】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子に連結され、上記第1入力信号のレベル状態に基づいてオン／オフ動作を行う第14トランジスタと、上記第14トランジスタと直列に連結され、上記第2入力信号のレベル状態に基づいてオン／オフ動作を行う第15トランジスタとを有するスイッチング部とをさらに含み、上記第1入力信号および上記第2入力信号がローレベルである時、上記第6トランジスタをオフさせて、上記第1能動負荷に流れる電流を遮断するとしてもよい。

## 【0053】

また、上記複数の論理ゲートそれぞれは、上記第6トランジスタのソース端子とゲート端子との間に連結され、上記第6トランジスタのソース-ゲート間の電圧を維持する第1キャパシタと、上記第7トランジスタのソース端子とゲート端子との間に連結され、上記第7トランジスタのソース-ゲート間の電圧を維持する第2キャパシタとをさらに含むとしてもよい。

## 【0054】

また、上記複数の論理ゲートそれぞれは、上記第2キャパシタの両端に連結され、上記入力部または上記第1能動負荷の出力信号のレベル状態に基づいてオン／オフ動作を行う第16トランジスタをさらに含むとしてもよい。

## 【0055】

また、上記第1～第11トランジスタは、PMOSトランジスタであるとしてもよい。

## 【発明の効果】

## 【0056】

本発明によれば、パネルの内部に直接PMOSトランジスタで構成される複数のフリップフロップと複数の論理ゲートを形成することによって、SOPを具現することが容易であるという利点がある。

## 【0057】

また、本発明では、隣接するフリップフロップの4つの出力を論理ゲートの入力として使用することによって、追加的な信号を必要としない。すなわち、フリップフロップの出力を利用することによって、消費電力を低減することができる。

## 【0058】

さらに、本発明では、4入力論理ゲートを使用することによって、入力信号がローである時に発生する静電流を遮断することができ、漏洩電流による電力消費を減少させることができる。

## 【0059】

したがって、本発明は、SOP用に最適の発光制御駆動部を提供し、本発明に係る発光制御駆動部を用いることにより、消費電力を最小化することが可能な有機EL表示装置を提供することができる。

## 【発明を実施するための最良の形態】

## 【0060】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書および図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

## 【0061】

また、以下に示す実施の形態についての説明において、添付図面に示されたトランジスタは、課題を解決するための手段に記載された、第1トランジスタとしてのスイッチングトランジスタM6、以下同様に、第2トランジスタとしてのスイッチングトランジスタM7、第3トランジスタとしてのトランジスタM8、第4トランジスタとしてのトランジスタM9、第5トランジスタとしてのトランジスタM10、第6トランジスタとしてのトランジスタM13、第7トランジスタとしてのトランジスタM17、第8トランジスタとしてのトランジスタM11、第9トランジスタとしてのトランジスタM12、第10トランジスタとしてのトランジスタM15\_1、第11トランジスタとしてのトランジスタM1

10

20

30

40

50

5\_2、第12トランジスタとしてのトランジスタM16\_1、第13トランジスタとしてのトランジスタM16\_2、第14トランジスタとしてのトランジスタM14\_1、第15トランジスタとしてのトランジスタM14\_2、第16トランジスタとしてのトランジスタM19、出力トランジスタとしての出力トランジスタM18、とする。

【0062】

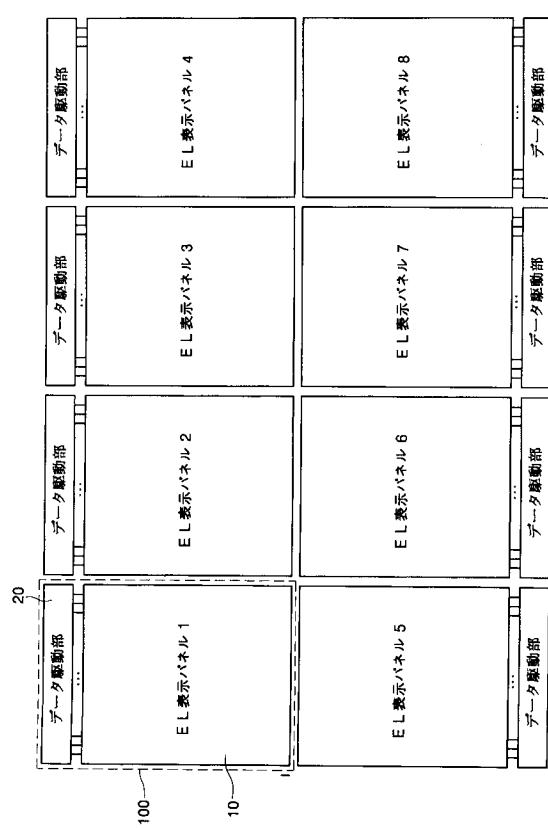

図1は、本発明の実施形態に係るタイルリング技術を用いた大型の有機EL表示装置を示すブロック図である。

【0063】

図1を参照すると、本発明の実施形態に係るタイルリング技術を用いた大型の有機EL表示装置は、複数の小型の有機EL表示装置100が接合されて構成される。図1の場合、行(row)に4つの小型の有機EL表示装置100が接合され、これが2列(column)で構成されるが、設計者は、必要に応じて多様な大きさで接合することができる。

10

【0064】

各小型の有機EL表示装置100は、映像を表示することのできるEL表示パネル10と、EL表示パネル10に映像データ信号を供給するデータ駆動部20とから構成される。

【0065】

それぞれのEL表示パネル10は、基本的に同じ構造を有し、各エッジ面を接着剤で接着し、1つに組合わせたEL表示パネルを形成する。接着剤には、紫外線硬化樹脂や熱硬化樹脂、例えば、エポキシ樹脂等が使用される。

20

【0066】

各EL表示パネル10は、従来の有機EL表示装置に使われるEL表示パネルと同一の製造工程により生産されることができる。したがって、同一の製造工程により生産された同じ複数のEL表示パネルを取り付けて、1つの大型のEL表示パネルが形成される。

【0067】

このようなEL表示パネルに形成される走査駆動部、発光制御駆動部および複数の画素の薄膜トランジスタは、高速の応答速度および均一性を具現するために、薄膜トランジスタのチャンネルとしてポリシリコンを有する。この際、ポリシリコンは、非晶質シリコン層をガラス基板上に形成された後、低温ポリシリコン(Low Temperature

30

Poly Silicon; LTPS)工程を経て、結晶化される。

【0068】

このようなLTPS工程を経て形成されたポリシリコンにより、複数のトランジスタが形成され、複数のトランジスタを用いてEL表示パネルの内部にレッド、グリーン、ブルーのサブ画素から構成される画素部と、上記各画素を選択し、発光を制御するための信号を生成する走査駆動部および発光制御駆動部が形成される。ここで、EL表示パネル10については後述する。

【0069】

各小型の有機EL表示装置100それぞれのデータ駆動部20は、CMOS形成技術を用いた外装型集積回路ICとして設計され、それぞれがEL表示パネル10に電気的に連結される。1つのEL表示パネル10とデータ駆動部20間との電気的な連結は、可撓性フィルム上に印刷された金属パターンによりなされる。すなわち、データ駆動部20の出力端子は、金属パターンの一端に電気的に連結され、EL表示パネル10上に設けられたデータ線は、金属パターンの他端に電気的に連結される。これをテープキャリアパッケージ(Tape Carrier Package; TCP)方式という。それぞれのデータ駆動部20は、可撓性フィルム上に設けられた複数の導電性線を介してデータ信号をEL表示パネル10の画素部に供給する。

40

【0070】

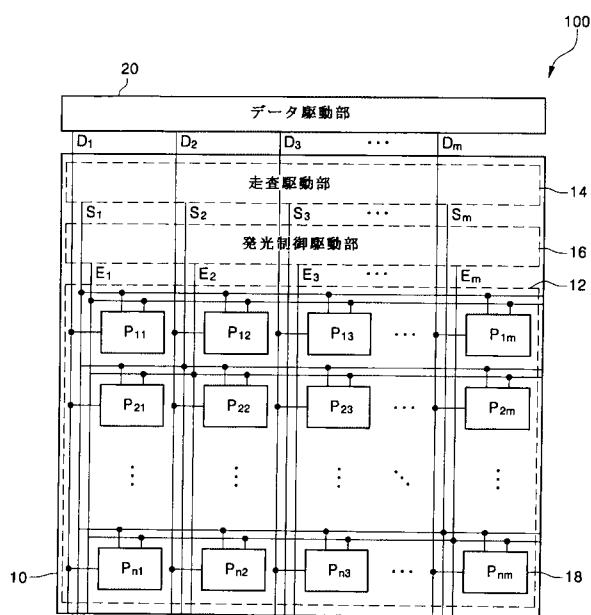

図2は、図1に示す本発明の実施形態に係る小型の有機EL表示装置100を詳細に示すブロック図である。

50

## 【0071】

図2を参照すると、小型の有機EL表示装置100は、EL表示パネル10と、データ駆動部20とから構成される。

## 【0072】

また、EL表示パネル10は、画素部12、走査駆動部14および発光制御駆動部16から構成される。

## 【0073】

画素部12は、複数のデータ線D1～Dm(mは自然数)、複数の走査線S1～Sn(nは自然数)、複数の発光制御線E1～En、およびこれらの線が交差する領域に形成された複数の画素P11～Pnmを備える。

10

## 【0074】

複数のデータ線D1～Dmは、データ駆動部20と電気的に連結され、また図2における垂直方向に延長されて各画素にそれぞれデータ信号を伝達する。

## 【0075】

また、複数の走査線S1～Snと複数の発光制御線E1～Enは、従来の有機EL表示装置とは異なって、データ線D1～Dmと同様の方向に延長されるが、図2における水平方向に配置された各画素に同一の走査および発光制御信号を伝達するために、各走査線S1～Snおよび発光制御線E1～Enごとにコンタクトホールを形成する。したがって、コンタクトホールを介して接続される金属配線を図2における水平方向に延長し、図2における水平方向の画素には、走査信号および発光制御信号が伝達される。

20

## 【0076】

各画素P11～Pnmは、レッド、グリーン、ブルーの3つのサブ画素が反復的に行と列とに配列される。各レッド、グリーン、ブルーのサブ画素は、実際光を発光する有機発光層の有機物質が異なるだけで、配線のレイアウトや駆動回路部の回路連結関係はいずれも同一である。したがって、各画素は、印加されるデータ信号に該当する輝度をもってレッド、グリーンおよびブルーの光を発光し、これら3色の組合せで1つのカラーを表現する。各画素の回路構成については、図3および図4を用いて説明する。

20

## 【0077】

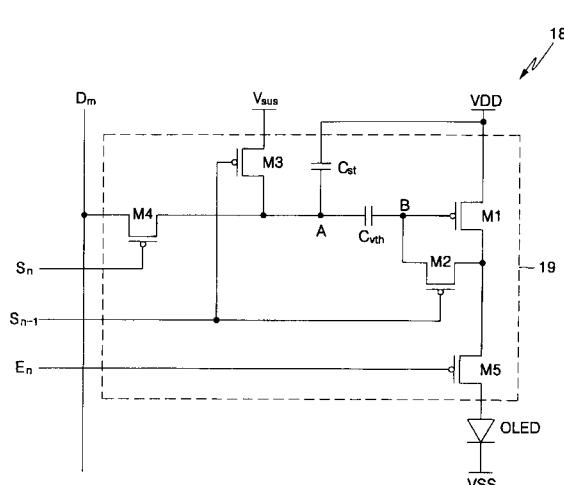

図3は、図2に示す画素部の複数の画素のうち代表的な画素を示す回路図である。

30

## 【0078】

図3を参照すると、画素回路18は、画素駆動部19と、有機EL素子OLEDとから構成される。

## 【0079】

画素駆動部19は、データ線Dm、走査線Sn-1、走査線Sn、発光制御線En、電圧VDDが印加される第1電源電圧線、および電圧Vssが印加される第2電源電圧線に連結されている。したがって、データ線Dmからのデータ信号Vdata信号に相当する駆動電流を有機EL素子OLEDに供給する。

## 【0080】

有機EL素子OLEDは、アノード電極、カソード電極および有機発光層から構成される。アノード電極は、画素駆動部19に連結され、カソード電極は、電圧VSSが印加される基準電源電圧線に連結される。したがって、有機EL素子OLEDは、画素駆動部19から供給される駆動電流を印加され、その電流量に該当する発光輝度で発光する。

40

## 【0081】

画素駆動部19は、5つのトランジスタM1～M5と、2つのキャパシタCst、Cvtとから構成される。以下、画素駆動部19について詳細に説明する。

## 【0082】

スイッチングトランジスタM4は、ソース端子にデータ線Dmが連結され、ゲート端子に走査線Snが連結され、走査線Snを介して伝達される走査信号によりオンとなり、データ線Dmから印加されるデータ信号Vdataを伝達する。

## 【0083】

50

駆動トランジスタM1は、ソース端子に電圧VDDが印加される第1電源電圧線が連結され、ゲート端子に印加される電圧に該当する駆動電流I<sub>OLED</sub>を生成する。

【0084】

スレショルド電圧(閾値電圧)補償トランジスタM2は、駆動トランジスタM1のゲート端子とドレイン端子との間に連結され、走査線S<sub>n-1</sub>に連結したゲート端子に印加される走査信号によりオンとなり、駆動トランジスタM1のスレショルド電圧を補償する。

【0085】

キャパシタC<sub>vt</sub>は、スイッチングトランジスタM4のドレイン端子と駆動トランジスタM1のゲート端子との間に連結され、駆動トランジスタM1のスレショルド電圧V<sub>t</sub>hに該当する電圧を保持する。

10

【0086】

キャパシタC<sub>st</sub>は、電圧VDDが印加される第1電源電圧線とキャパシタの一方の端子との間に連結され、データ線D<sub>m</sub>に伝達されるデータ電圧V<sub>data</sub>を保持する。

【0087】

負の電源電圧印加トランジスタM3は、ソース端子が電圧V<sub>sus</sub>が印加される第2電源電圧線に連結され、ドレイン端子がキャパシタC<sub>vt</sub>hおよびキャパシタC<sub>st</sub>との連結地点に連結される。そして、走査線S<sub>n-1</sub>から伝達される走査信号(以下、走査線S<sub>n-1</sub>から印加される走査信号を「以前走査信号」という。)がゲート端子に印加されることによりオンとなり、第2電源電圧線に印加される電圧V<sub>sus</sub>をキャパシタC<sub>vt</sub>hとキャパシタC<sub>st</sub>との連結地点に印加する。

20

【0088】

発光制御トランジスタM5は、駆動トランジスタM1のドレイン端子と有機EL素子OLEDのアノード電極との間に連結され、ゲート端子に印加される発光制御信号E<sub>n</sub>の制御によってオン/オフ動作を行い、駆動トランジスタM1から供給される駆動電流を有機EL素子OLEDに供給するか、または遮断する役割を果たす。

【0089】

次に、画素回路18の動作をタイミング図を用いて説明する。

【0090】

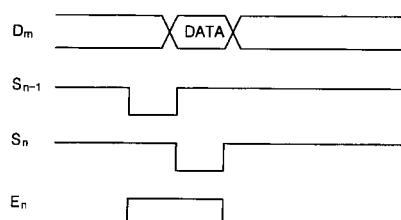

図4は、図3に示す画素回路の動作を説明するためのタイミング図である。

30

【0091】

図3および図4を参照すると、まず、画素回路18にローレベルの以前走査信号が印加され、走査線S<sub>n</sub>からハイレベルの走査信号(以下、走査線S<sub>n</sub>から印加される走査信号を「現在走査信号」という)と発光制御線E<sub>n</sub>から制御信号(以下、発光制御線E<sub>n</sub>から印加される制御信号を「発光制御信号」という)が印加されると、スレショルド電圧補償トランジスタM2と負の電源電圧印加トランジスタM3がオンとなり、残りのトランジスタM4、M5はオフとなる。したがって、駆動トランジスタM1は、ダイオードのような役割を果たし(以下、トランジスタが、ダイオードのような役割を果たす様に連結されることを「ダイオード連結」という)、第1キャパシタC<sub>vt</sub>hの一方の電極Bに電圧V<sub>D</sub>D-V<sub>th</sub>[V]が印加される。また、負の電源電圧印加トランジスタM3がオンとなり、第1キャパシタC<sub>vt</sub>hの他方の電極Aに電圧V<sub>sus</sub>[V]が印加される。したがって、第1キャパシタC<sub>vt</sub>hには、V<sub>sus</sub>-V<sub>DD</sub>+V<sub>th</sub>[V]の電圧が保持される。ここで、上記電圧V<sub>DD</sub>は、第1電源電圧線から印加される電圧である。

40

【0092】

次に、画素回路18にローレベルの現在走査信号が印加され、ハイレベルの以前走査信号と発光制御信号が印加されると、スイッチングトランジスタM4だけがオンとなる。この時、データ線D<sub>m</sub>からのデータ電圧V<sub>data</sub>が、スイッチングトランジスタM4を介して第1キャパシタC<sub>vt</sub>hの他方の電極Aに印加される。したがって、第1キャパシタC<sub>vt</sub>hの他方の電極Aは、一定の電圧差V(V=V<sub>sus</sub>-V<sub>data</sub>)分の電圧変動が生じ、これにより、第1キャパシタC<sub>vt</sub>hの一方の電極Bもその分の電圧変動が生じる。したがって、第1キャパシタの一方の電極Bおよび駆動トランジスタM1のゲー

50

ト端子に印加される電圧は、 $V_{DD} - V_{th} - V = V_{DD} - V_{th} - V_{sus} + V_{data}$  [v] である。

【0093】

最後に、画素回路 18 にハイレベルの以前走査信号および現在走査信号が印加され、ローレベルの発光制御信号が印加されると、発光制御トランジスタ M5 だけがオンとなる。この時、駆動トランジスタ M1 から出力される駆動電流  $I_{OLED}$  は、次の式 1 で表される。

【0094】

【数 1】

$$\begin{aligned} I_{OLED} &= k(Vgs_{M1} - Vth)^2 \\ &= k\{VDD - (VDD - Vth - V_{sus} + V_{data}) - Vth\}^2 \\ &= k(V_{data} - V_{sus})^2 \\ &\dots \quad (\text{式 1}) \end{aligned}$$

10

【0095】

ここで、 $Vgs_{M1}$  は、駆動トランジスタ M1 のソース - ゲート間の電圧であり、 $Vth$  は、駆動トランジスタ M1 のスレショルド電圧、k は定数である。

【0096】

式 1 に示すように、図 3 に示す画素回路 18 は、スレショルド電圧  $Vth$  の補償と第 1 電源電圧  $VDD$  による  $IR - drop$  (電圧降下) を補償することができる。

20

【0097】

さらに図 2 を参照すると、走査駆動部 14 は、データ駆動部 20 と画素部 12 との間に形成される。これは、複数の EL 表示パネル 10 が接合されて、1 つの大型パネルが形成されるので、各走査駆動部 14 は、データ駆動部 20 と同じ側 (これを片軸駆動という) に形成されなければならない。このような走査駆動部 14 は、複数の走査線  $S1 \sim Sn$  に連結され、画素部 12 に順次に走査信号を印加して、各画素  $P11 \sim Pnm$  を順次に選択する。

【0098】

発光制御駆動部 16 は、走査駆動部 14 と画素部 12 との間に形成され、複数の発光制御線  $E1 \sim En$  に連結され、画素部 12 に順次に発光制御信号を印加して、各画素  $P11 \sim Pnm$  の発光時間を制御する。

30

【0099】

データ駆動部 20 は、前述したように、可撓性フィルム上に設けられた複数の導電性線を介してデータ信号を EL 表示パネル 10 の画素部 12 に供給する。

【0100】

上記のような本発明の実施形態に係る小型の有機 EL 表示装置 100 は、EL 表示パネル 10 と、データ駆動部 20 とから構成される。また、EL 表示パネル 10 は、画素部 12 と、走査駆動部 14 と、発光制御駆動部 16 とから構成される。以下、発光制御駆動部について好ましい実施形態を参照して詳細に説明する。

40

【0101】

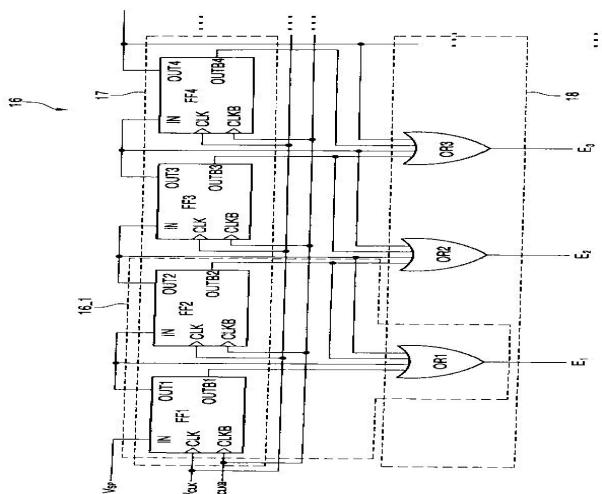

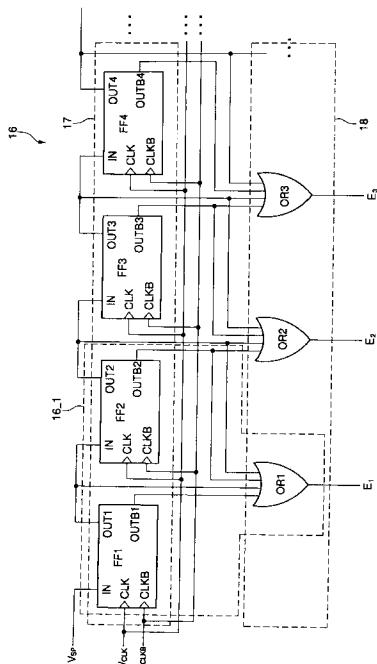

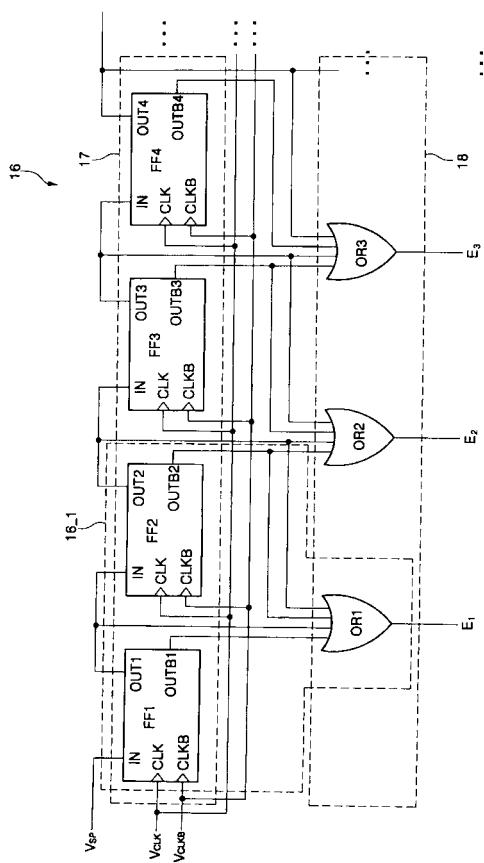

図 5 は、本発明の実施形態に係る有機 EL 表示装置の発光制御駆動部を示すブロック図である。

【0102】

図 5 を参照すると、発光制御駆動部 16 は、複数のフリップフロップ FF1、FF2、FF3、FF4、…が連結され、入力信号を 1 クロック周期だけシフトさせて信号を出力するシフトレジスタ 17 と、シフトレジスタ 17 の隣接するフリップフロップにおける 4 つの出力信号が印加され、論理和の演算により発光制御信号を生成する複数の論理ゲート OR1、OR2、OR3、…よりなる論理演算部 18 とから構成される。

50

## 【0103】

シフトレジスタ17は、複数のフリップフロップFF1、FF2、FF3、FF4、…から構成されている。第1フリップフロップFF1は、開始パルス $V_{s_p}$ 、クロック信号 $V_{CLK}$ および反転されたクロック信号 $V_{CLK_B}$ を入力され、クロック信号 $V_{CLK}$ の立ち下がりエッジで開始パルス $V_{s_p}$ をサンプリングしてクロック1周期の間維持し、出力信号OUT1および反転された出力信号OUTB1を出力する。

## 【0104】

第2フリップフロップFF2は、第1フリップフロップFF1の出力信号OUT1とクロック信号 $V_{CLK}$ 、および反転されたクロック信号 $V_{CLK_B}$ を入力され、クロック信号 $V_{CLK}$ の1周期の間にシフトされ、次の立ち下がりエッジで入力信号をサンプリングしてクロック(CLK)1周期の間維持し、出力信号OUT2および反転された出力信号OUTB2を出力する。

## 【0105】

以下、第3フリップフロップFF3、第4フリップフロップFF4、…は、第1フリップフロップFF1、第2フリップフロップFF2と同様の動作を繰り返して、シフトされた信号を出力する。各フリップフロップは、基本的に同じ構成からなっており、これについては、図面を参照して後述する。

## 【0106】

論理演算部18は、複数の論理ゲートOR1、OR2、OR3、…から構成され、各論理ゲートごとに発光制御線に連結され、発光制御信号を各画素に印加する。

## 【0107】

第1論理ゲートOR1は、第1フリップフロップFF1の2つの出力信号OUT1、OUTB1と、第2フリップフロップFF2の2つの出力信号OUT2、OUTB2とを入力信号として印加される。第1論理ゲートOR1は、入力された4つの入力信号OUT1、OUTB1、OUT2、OUTB2に対して論理和の演算を行う。本発明の実施形態に係る第1論理ゲートOR1は、一般的な論理ゲートとは異なり、第1フリップフロップFF1および第2フリップフロップFF2の出力信号OUT1、OUT2がローレベルの信号であり、かつ第1フリップフロップFF1および第2フリップフロップFF2の反転された出力信号OUTB1、OUTB2がハイレベルの信号である時にだけ、ローレベルの発光制御信号E1を出力し、それ以外のレベルの組み合わせでは、ハイレベルの発光制御信号E1を出力する。

## 【0108】

次に、第2論理ゲートOR2は、第2フリップフロップFF2の2つの出力信号OUT2、OUTB2と第3フリップフロップFF3の2つの出力信号OUT3、OUTB3を入力信号として印加され、第1論理ゲートOR1と同じ論理和の演算を行い、第2発光制御信号E2を出力する。

## 【0109】

第3論理ゲートOR3～第n論理ゲートORnも、第1論理ゲートOR1および第2論理ゲートOR2と同様に、4つの入力信号に対して論理和の演算を行い、各々の発光制御信号E3～Enを出力する。各論理ゲートは、基本的に同じ構成からなっており、これについては、図面を参照して後述する。

## 【0110】

前述したように、本発明の実施形態に係る発光制御駆動部16は、シフトレジスタ17と論理演算部18とから構成され、シフトレジスタ17の隣接する2つのフリップフロップFF1、FF2と論理演算部18の1つの論理ゲートOR1との連結関係を基本発光制御駆動回路16\_1として設定して、発光制御信号E1～Enを生成する。前述した図5の発光制御駆動部の動作原理は、図9に示すタイミング図を参照して後述する。

## 【0111】

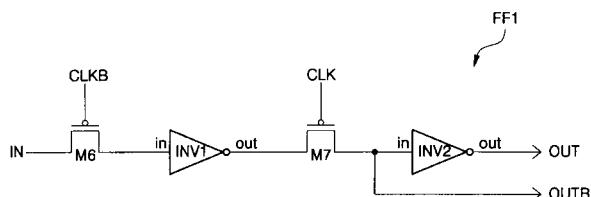

図6は、図5に示す発光制御駆動部のシフトレジスタを構成する代表的なフリップフロップFF1を示す回路図である。

10

20

30

40

50

## 【0112】

図6を参照すると、フリップフロップFF1は、2つのスイッチングトランジスタM6、M7と、2つのインバータINV1、INV2とから構成される。具体的には、フリップフロップFF1は、反転されたクロック信号CLKBによって制御され、反転されたクロック信号CLKBの立ち下がりエッジで入力信号INをサンプリングするトランジスタM6と、トランジスタM6の出力信号を反転する第1インバータINV1と、クロック信号CLKの立ち下がりエッジで第1インバータINV1の出力信号をサンプリングするトランジスタM7と、トランジスタM7の出力信号を反転する第2インバータINV2とから構成される。ここで、トランジスタM6、M7は、PMOSトランジスタである。

## 【0113】

したがって、入力信号INがトランジスタM6に印加され、反転されたクロック信号CLKBが立ち下がりエッジに変換される時、トランジスタM6は、入力信号INをサンプリングし、第1インバータINV1に伝達する。クロック信号CLKが立ち下がりエッジに変換される時、トランジスタM7は、オンとなり、第1インバータINV1は、サンプリングされた信号を反転させて出力する。トランジスタM7から伝達された第1インバータINV1の出力信号OUTBは、第2インバータINV2でさらに反転されて出力OUTされる。

## 【0114】

前述のように、本発明の実施形態に係るフリップフロップFF1は、入力信号IN、クロック信号CLKおよび反転されたクロック信号CLKBを用いて所望する大きさの出力信号を生成することができる。第2インバータINV2の入力信号OUTBと出力信号OUTは、前述した論理ゲートOR1の2入力信号となる。また、第2インバータINV2の出力信号OUTは、次のフリップフロップFF2の入力信号となり、入力信号を1クロック周期だけシフトして出力させて、論理ゲートOR1の2入力信号として印加する。したがって、4入力論理ゲートの入力信号OUT1、OUTB1、OUT2、OUTB2において、入力信号OUTB1またはOUTB2は、追加の信号無しに各フリップフロップFF1、FF2の第2インバータINV2の入力端に印加される信号を取り出して使用される。したがって、追加の信号を必要とせず、論理ゲートの入力信号をフリップフロップから全て印加することによって、消費電力を低減することができる。

## 【0115】

次に、フリップフロップFF1に使われる第1インバータINV1および第2インバータINV2について説明する。

## 【0116】

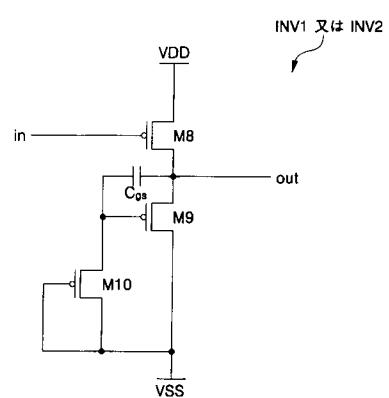

図7は、図6に示すフリップフロップのインバータの構造を詳細に示す回路図である。

## 【0117】

第1インバータINV1および第2インバータINV2は、同じ構造を有するインバータであるから、説明の便宜上、第1インバータINV1のみについて説明する。

## 【0118】

図7を参照すると、インバータINV1は、3つのPMOSトランジスタM8、M9、M10よりなる。

## 【0119】

トランジスタM8は、ソース端子が第1電源電圧VDDが印加される端子に連結され、ゲート端子がフリップフロップFF1のトランジスタM6の出力端子に連結され、ドレイン端子が、出力端outに連結される。出力端outは、フリップフロップFF1のトランジスタM7の入力端子に連結される。したがって、トランジスタM8は、トランジスタM6から伝達された入力信号inの制御によってオン／オフ動作を行い、第1電源電圧VDDを出力端outに出力したり、遮断する。ここで、第1電源電圧VDDは、正の電源電圧であり、例えば5[V]の電圧が供給される。

## 【0120】

トランジスタM9は、トランジスタM8のドレイン端子と出力端outにソース端子が

10

20

30

40

50

連結され、第2電源電圧VSSにドレイン端子が連結され、ゲート端子に印加される電圧によって能動負荷としての役割を果たす。

【0121】

また、トランジスタM10は、トランジスタM9のゲート端子とドレイン端子との間に連結され、ゲート端子とドレイン端子が連結される。そしてトランジスタM10は、ダイオードのような役割を果たし、トランジスタM9のゲート電圧を制御する。ここで、第2電源電圧VSSは、負の電源電圧であり、例えば-7[V]の電圧が供給される。したがって、トランジスタM9は、能動負荷であり、ソース端子に印加される電圧とゲート端子に印加される電圧との差によって常にオン状態にあるようになる。ここで、トランジスタM9のチャンネル長さ(Lenth)L9は、トランジスタM8のチャンネル長さL8より大きくし、トランジスタM9のチャンネル幅(Width)W9は、トランジスタM8のチャンネル幅W8より小さいことが好ましい。すなわち、これは、トランジスタM8がオンとなった時、トランジスタM9のオン抵抗がトランジスタM8のオン抵抗より非常に大きくなるようにするためである。

10

【0122】

また、インバータINV1は、トランジスタM9のソース端子とゲート端子との間に連結され、トランジスタM10がオフとなった時、トランジスタM9のソース-ゲート間の電圧Vgsm9を維持するキャパシタCstをさらに含むことができる。

20

【0123】

次に、上記のような構成を有するインバータINV1の動作原理について説明する。

20

【0124】

まず、ローレベル7[V]の入力信号inがトランジスタM8のゲート端子に印加されると、トランジスタM8は、オンとなり、トランジスタM9、M10もオンとなる。しかしながら、トランジスタM9は、トランジスタM8よりオン抵抗が大きくなり、実質的に出力端outの電圧は、第1電源電圧VDD、すなわちハイレベルの電圧、例えば5[V]が出力される。

30

【0125】

次に、ハイレベル5[V]の入力信号inがトランジスタM8のゲート端子に印加されると、トランジスタM8は、オフとなり、既にトランジスタM9、M10は、オンとなっている状態である。したがって、出力端outの電圧は、以前に出力されたハイレベルの電圧5[V]からだんだんローレベルに遷移され、この際、トランジスタM10は、オフとなり、トランジスタM9のゲート端子は、フローティングされる。したがって、トランジスタM9のソース-ゲート電圧Vgsm9は、一定電圧を維持するようになり、ソース端子に連結した出力端子outは、第2電源電圧VSSの電圧、すなわちローレベルの電圧(例えば、-7[V])だけ低下するようになる。この際、トランジスタM9のゲート電圧も、出力端outの電圧が変換されることによって、-7[V]から-15[V]程度までに下降する。

30

【0126】

前述したように、本発明の実施形態に係るフリップフロップは、クロック信号CLKおよび反転されたクロック信号CLKBの状態変化によってサンプリングされる入力信号の制御により所望する大きさの出力信号を出力することができ、これにより、シフトレジスタ17の隣接するフリップフロップFF1、FF2の4つの出力信号OUT1、OUTB1、OUT2、OUTB2を後述する論理ゲートOR1の入力端に印加する。

40

【0127】

次に、シフトレジスタ17の隣接するフリップフロップFF1、FF2の4つの出力信号OUT1、OUTB1、OUT2、OUTB2が印加される論理ゲートOR1について詳細に説明する。

【0128】

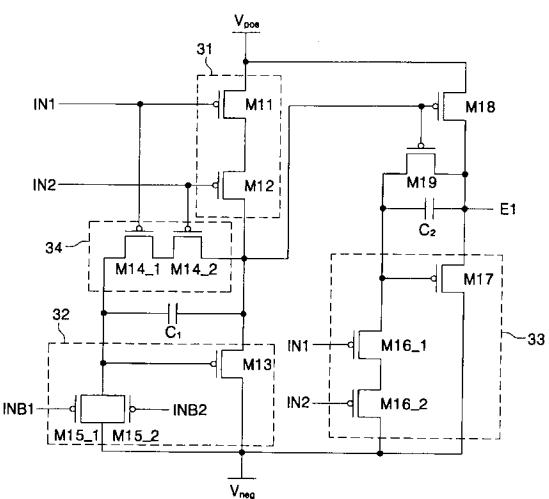

図8は、図5に示す発光制御駆動部の論理演算部を構成する複数の論理ゲートのうち代表的な論理ゲートを詳細に示す回路図である。

50

## 【 0 1 2 9 】

図8を参照すると、本発明の実施形態に係る論理ゲートは、2つの入力信号IN1、IN2によってオン／オフ動作を行う入力部31と、入力部31に連結され、2つの反転された入力信号INB1、INB2によって選択的にダイオード連結されるトランジスタM13を有する第1能動負荷32と、入力部31の出力を受信し、受信されるレベルによってオン／オフ動作を行う出力トランジスタM18と、出力トランジスタM18に連結され、2つの入力信号IN1、IN2によって選択的にダイオード連結されるトランジスタM17とを有する第2能動負荷33とを含む。

## 【 0 1 3 0 】

また、論理ゲートは、2つの入力信号IN1、IN2によってオン／オフ動作を行い、2つの入力信号IN1、IN2がローである時、第1能動負荷32に流れる電流を遮断するスイッチング部34と、トランジスタM13のソースとゲート間の電圧を維持する第1キャパシタC1と、トランジスタM17のソースとゲート間の電圧を維持する第2キャパシタC2とをさらに含む。

## 【 0 1 3 1 】

さらに、本発明の実施形態に係る論理ゲートは、第2キャパシタC2の両端に連結され、入力部31の出力信号によってオン／オフ動作を行い、出力信号がローである時、第2能動負荷33に流れる電流を遮断するトランジスタM19をさらに含む。

## 【 0 1 3 2 】

ここで、入力信号IN1は、フリップフロップFF1の出力信号OUT1であり、反転された入力信号INB1は、フリップフロップFF1の反転された出力信号OUTB1である。また、入力信号IN2は、フリップフロップFF2の出力信号OUT2であり、反転された入力信号INB2は、フリップフロップFF2の反転された出力信号OUTB2である。

## 【 0 1 3 3 】

詳細に説明すると、入力部31は、第1電源電圧としての正の電源電圧Vposが印加される端子に連結され、入力信号IN1のレベルによってオン／オフ動作を行うトランジスタM11と、トランジスタM11に連結され、入力信号IN2のレベルによってオン／オフ動作を行うトランジスタM12とから構成される。したがって、入力部31は、2つの入力信号IN1、IN2が共にローレベルである時にだけ、オンとなり、正の電源電圧Vposを出力し、それ以外のレベルでは、オフとなる。

## 【 0 1 3 4 】

第1能動負荷32は、トランジスタM12と第2電源電圧としての負の電源電圧Vnegが印加される端子との間に連結され、反転された2つの入力信号INB1、INB2のレベル状態によってダイオード連結されるトランジスタM13と、トランジスタM13のゲートとドレインとの間に連結され、反転された2つの入力信号INB1、INB2のレベル状態によってそれぞれオン／オフ動作を行う2つのトランジスタM15\_1、M15\_2とから構成される。したがって、反転された2つの入力信号INB1、INB2のレベル状態が共にハイレベルである時を除いて、トランジスタM13は、ダイオード連結され、負の電源電圧Vnegとスレショルド電圧VthM13との和に該当する電圧を入力部31の出力端に印加する。

## 【 0 1 3 5 】

出力トランジスタM18は、正の電源電圧Vposが印加される端子と発光制御線E1との間に連結され、入力部31と第1能動負荷32の出力端にゲート端子が連結されてゲート端子に印加される電圧によってオン／オフ動作を行う。したがって、ゲート端子に印加される電圧がローレベルである時、トランジスタM18は、オンとなり、正の電源電圧Vposを発光制御線E1に伝達する。

## 【 0 1 3 6 】

第2能動負荷33は、トランジスタM18と負の電源電圧Vnegが印加される端子との間に連結され、2つの入力信号IN1、IN2のレベル状態によってダイオード連結さ

10

20

30

40

50

れるトランジスタM17と、トランジスタM17のゲートとドレインとの間に連結され、2つの入力信号IN1、IN2のレベル状態によってそれぞれオン／オフ動作を行う2つのトランジスタM16\_1、M16\_2とから構成される。したがって、2つの入力信号IN1、IN2のレベル状態が共にローレベルである時だけ、トランジスタM17は、ダイオード連結され、負の電源電圧V<sub>neg</sub>とスレショルド電圧V<sub>thM17</sub>との和に該当する電圧を発光制御線E1に印加する。

【0137】

また、スイッチング部34は、第1能動負荷32のトランジスタM13のソースとゲートとの間に連結され、2つの入力信号IN1、IN2によってそれぞれオン／オフ動作を行う2つのトランジスタM14\_1、M14\_2が直列に連結されている。スイッチング部34は、2つの入力信号IN1、IN2が共にローレベルである時、トランジスタM13のソースとゲート間の電圧差V<sub>gsM13</sub>を0[V]とし、トランジスタM13に流れる電流を遮断する。したがって、入力部31がオンとなる時、第1能動負荷32を介して流れる静電流(Static Current)を遮断することができる。

【0138】

さらに、トランジスタM19は、第2能動負荷33のトランジスタM17のソースとゲートとの間に連結され、第1入力部31の出力信号によってオン／オフ動作を行う。したがって、トランジスタM19は、第1入力部31の出力信号がローレベルである時、トランジスタM17のソースとゲート間の電圧差V<sub>gsM17</sub>を0[V]とし、トランジスタM17に流れる電流を遮断する。したがって、トランジスタM18がオンとなる時、第2能動負荷33を介して流れる静電流を遮断することができる。

【0139】

ここで、本発明の実施形態に係る論理ゲートを構成する全てのトランジスタは、いずれもPMOSトランジスタで構成される。ただし、本発明の実施形態に係る論理ゲートをNMOSトランジスタで構成することは、当業者が容易に変更し得る程度のことであり、本発明の等価範囲に属するものと理解すべきである。すなわち、本発明の実施形態に係る論理ゲートを構成するPMOSトランジスタを、NMOSトランジスタに変え、正の電源電圧と負の電源電圧を取り換えれば、NMOSトランジスタよりなる論理ゲートが設計できる。

【0140】

次に、本発明の実施形態に係る論理ゲートが、2つの入力信号IN1、IN2および2つの反転された入力信号INB1、INB2のレベル状態によってどのような発光制御信号E1を出力するかを説明する。

【0141】

まず、2つの入力信号IN1、IN2が共にローレベルの信号であり、かつ反転された2つの入力信号INB1、INB2が共にハイレベルの信号である時、入力部31の2つのトランジスタM11、M12は、共にオンとなり、スイッチング部34の2つのトランジスタM14\_1、M14\_2も共にオンとなる。また、第2能動負荷33の2つのトランジスタM16\_1、M16\_2も共にオンとなる。ただし、第1能動負荷32の2つのトランジスタM15\_1、M15\_2は、共にオフとなる。

【0142】

したがって、正の電源電圧V<sub>pos</sub>は、入力部31を通じて出力トランジスタM18およびトランジスタM19のゲート端子に印加される。この際、スイッチング部34は、オンとなり、第1能動負荷32のトランジスタM13のソース-ゲート電圧V<sub>gsM13</sub>を0[V]とする。したがって、トランジスタM13は、オフとなり、能動負荷32では、静電流が流れない。一方、正の電源電圧V<sub>pos</sub>をゲート端子に印加された出力トランジスタM18およびトランジスタM19は、オフとなり、第2能動負荷33のダイオード連結されるトランジスタM17によって、発光制御線E1からは、負の電源電圧V<sub>neg</sub>とスレショルド電圧V<sub>thM17</sub>との和に相当するローレベルの発光制御信号が出力される。

10

20

30

40

50

## 【0143】

次に、入力信号IN1がハイレベルであり、かつ入力信号IN2がローレベルであるか、または、入力信号IN1がローレベルであり、かつ入力信号IN2がハイレベルである場合、すなわち、入力信号IN1とIN2との信号レベルが互いに異なる場合、本発明の実施形態に係る論理ゲートの状態は、次の通りである。

## 【0144】

入力部31の2つのトランジスタM11、M12のうちいずれか1つのトランジスタM11またはトランジスタM12は、オフとなり、スイッチング部34の2つのトランジスタM14\_1、M14\_2のうちいずれか1つのトランジスタM14\_1またはトランジスタM14\_2も、オフとなる。また、第2能動負荷33の2つのトランジスタM16\_1、M16\_2のうちいずれか1つのトランジスタM16\_1またはトランジスタM16\_2もオフとなる。ただし、第1能動負荷32の並列に連結された2つのトランジスタM15\_1、M15\_2のうちいずれか1つのトランジスタM15\_1またはトランジスタM15\_2は、オンとなる。

## 【0145】

したがって、入力部31とスイッチング部34は、オフとなり、第1能動負荷32のトランジスタM13は、ダイオード連結され、出力トランジスタM18のゲート端子の電圧は、負の電源電圧V<sub>neg</sub>とスレショルド電圧V<sub>th<sub>M13</sub></sub>との和だけローレベルに下降するようになる。ローレベルの電圧を印加された出力トランジスタM18は、オンとなり、正の電源電圧V<sub>pos</sub>を発光制御線E1に出力する。この際、トランジスタM19は、オンとなり、第2能動負荷33のトランジスタM17のソース-ゲート電圧V<sub>gs<sub>M17</sub></sub>を0[V]とする。したがって、トランジスタM17は、オフとなり、能動負荷33では、静電流が流れない。つまり、発光制御線E1には、正の電源電圧V<sub>pos</sub>のみが出力、すなわちハイレベルの信号が出力される。

## 【0146】

また、2つの入力信号IN1、IN2が共にハイレベルである場合は、入力信号IN1とIN2との信号レベルが互いに異なる場合と同様に、発光制御信号E1として、ハイレベルの信号が出力されることが分かる。

## 【0147】

上記のように、本発明の実施形態に係る論理演算部18を構成する論理ゲートは、追加の信号を必要とせず、シフトレジスタ17の隣接するフリップフロップFF1、FF2から出力される4つの信号OUT1、OUTB1、OUT2、OUTB2が印加され、これら4つの信号を用いて論理ゲートの能動負荷を制御し、論理和の演算を行い、所望する形態の発光制御信号E1を生成することができる。この時、2つの入力信号IN1、IN2がローレベルである場合、論理ゲートの能動負荷32、33を介して流れる静電流を遮断することができ、入力部31の出力信号がローレベルである場合、第2能動負荷33を介して流れる静電流を遮断することができる。

## 【0148】

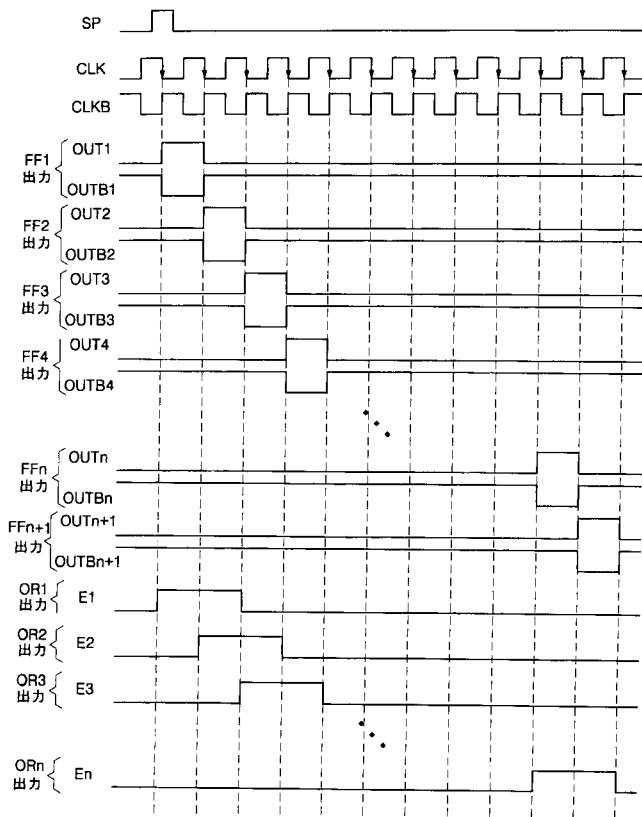

図9は、本発明の実施形態に係る発光制御駆動部の動作を示す各信号のタイミング図である。

## 【0149】

図9を参照すると、複数のフリップフロップFF1～FF<sub>n+1</sub>で構成されるシフトレジスタは、クロック信号CLKおよび反転されたクロック信号CLKBを共通に印加され、一段前のフリップフロップの出力信号を、フリップフロップの入力信号として印加される。ただし、第1フリップフロップFF1は、開始パルスV<sub>sp</sub>が入力信号として印加される。

## 【0150】

まず、開始パルスV<sub>sp</sub>が第1フリップフロップFF1の入力として印加されると、クロック信号CLKの立ち下がりエッジで、第1フリップフロップFF1は、ハイレベルの出力信号OUT1およびローレベルの反転された出力信号OUTB1をクロック1周期の

10

20

30

40

50

間にに出力する。

【0151】

次に、第1フリップフロップFF1の出力信号OUT1が第2フリップフロップFF2の入力として印加されると、クロック信号CLKの2番目の立ち下がりエッジで、第2フリップフロップFF2は、ハイレベルの出力信号OUT2およびローレベルの反転された出力信号OUTB2をクロック1周期の間にに出力する。

【0152】

上記のような動作を繰り返して、最後に第1フリップフロップFFnの出力信号OUTnが、第n+1フリップフロップFFn+1の入力として印加されると、クロック信号CLKのn+1番目の立ち下がりエッジで、第n+1フリップフロップFFn+1は、ハイレベルの出力信号OUTn+1およびローレベルの反転された出力信号OUTBn+1をクロック1周期の間にに出力する。

【0153】

上記のような動作により、本発明の実施形態に係るシフトレジスタは、クロック1周期毎にシフトされる2つの信号OUT、OUTBを出力する。

【0154】

また、複数の論理ゲートOR1～ORnで構成される論理演算部18は、フリップフロップFF1～FFn+1の出力信号を印加され、論理和の演算を行い、発光制御信号を出力する。

【0155】

まず、第1論理ゲートOR1は、第1フリップフロップFF1の2つの出力信号OUT1、OUTB1と、第2フリップフロップFF2の2つの出力信号OUT2、OUTB2を入力として印加される。したがって、第1出力信号OUT1と第2出力信号OUT2がローレベルであり、かつ反転された第1出力信号OUTB1および反転された第2出力信号OUTB2がハイレベルである場合にだけ、第1論理ゲートOR1は、ローレベルの発光制御信号E1を出力し、それ以外のレベル状態では、ハイレベルの発光制御信号E1を出力する。

【0156】

次に、第2論理ゲートOR2は、第2フリップフロップFF2の2つの出力信号OUT2、OUTB2と、第3フリップフロップFF3の2つの出力信号OUT3、OUTB3を入力として印加される。したがって、第2出力信号OUT2と第3出力信号OUT3がローレベルであり、かつ反転された第2出力信号OUTB2および反転された第3出力信号OUTB3がハイレベルである場合にだけ、第2論理ゲートOR2は、ローレベルの発光制御信号E2を出力し、それ以外のレベル状態では、ハイレベルの発光制御信号E2を出力する。第2発光制御信号E2は、第1発光制御信号E1よりクロック1周期だけシフトされ出力される。

【0157】

上記のような動作を繰り返して、最後に第n論理ゲートORnは、第nフリップフロップFFnの2つの出力信号OUTn、OUTBnと、第n+1フリップフロップFFn+1の2つの出力信号OUTn+1、OUTBn+1を入力として印加される。したがって、第n出力信号OUTnと第n+1出力信号OUTn+1がローレベルであり、かつ反転された第n出力信号OUTBnおよび反転された第n+1出力信号OUTBn+1がハイレベルである場合にだけ、第n論理ゲートORnは、ローレベルの発光制御信号Enを出力し、それ以外のレベル状態では、ハイレベルの発光制御信号Enを出力する。

【0158】

以上のような本発明の実施形態に係る有機EL表示装置の発光制御駆動部16は、パネルの内部に直接PMOSトランジスタで構成される複数のフリップフロップと、複数の論理ゲートを形成することによって、SOP(System On Panel)を具現することが容易であるという利点がある。

【0159】

10

20

30

40

50

また、本発明の実施形態に係る有機EL表示装置の発光制御駆動部16は、シフトレジスタ17の隣接するフリップフロップの4つの出力を論理ゲートの入力として使用することによって、追加的な信号を必要としない。すなわち、フリップフロップの出力を利用することによって、消費電力を低減することができる。

【0160】

さらに、本発明の実施形態に係る有機EL表示装置の発光制御駆動部16は、4入力論理ゲートを使用することによって、入力信号がローである場合(すなわち反転された入力信号がハイレベルの場合)に発生する静電流を遮断することができ、漏洩電流による電力消費を減少することができる。

【0161】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されることは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それについても当然に本発明の技術的範囲に属するものと了解される。

【0162】

例えば、本発明の実施形態における論理ゲートをはじめとする各構成要素に係るトランジスタを、PMOSトランジスタではなく、NMOSトランジスタで構成することは、当業者が容易に変更し得る程度のことであり、本発明の等価範囲に属するものと理解すべきである。

【図面の簡単な説明】

【0163】

【図1】本発明の実施形態に係るタイルリング技術を用いた有機電界発光表示装置を示すブロック図である。

【図2】図1における代表的な小型の有機電界発光表示装置を詳細に示すブロック図である。

【図3】図2における画素部が含む複数の画素のうち、代表的な画素を示す回路図である。

【図4】図3における画素回路の動作を表すタイミング図である。

【図5】本発明の実施形態に係る有機EL表示装置の発光制御駆動部を示すブロック図である。

【図6】図5における発光制御駆動部のシフトレジスタを構成する代表的なフリップフロップを示す回路図である。

【図7】図6におけるフリップフロップのインバータ構造を詳細に示す回路図である。

【図8】図5における発光制御駆動部の論理演算部を構成する複数の論理ゲートのうち、代表的な論理ゲートを詳細に示す回路図である。

【図9】本発明の実施形態に係る発光制御駆動部の動作を示すタイミング図である。

【符号の説明】

【0164】

|         |          |

|---------|----------|

| 1 0     | EL表示パネル  |

| 1 2     | 画素部      |

| 1 4     | 走査駆動部    |

| 1 6     | 発光制御駆動部  |

| 1 7     | シフトレジスタ  |

| 1 8     | 論理演算部    |

| 2 0     | データ駆動部   |

| C 1     | 第1キャパシタ  |

| C 2     | 第2キャパシタ  |

| I N V 1 | 第1インバータ  |

| I N V 2 | 第2インバータ  |

| M 6     | 第1トランジスタ |

10

20

30

40

50

|                     |               |    |

|---------------------|---------------|----|

| M 7                 | 第 2 トランジスタ    |    |

| M 8                 | 第 3 トランジスタ    |    |

| M 9                 | 第 4 トランジスタ    |    |

| M 1 0               | 第 5 トランジスタ    |    |

| M 1 3               | 第 6 トランジスタ    |    |

| M 1 7               | 第 7 トランジスタ    | 10 |

| M 1 1               | 第 8 トランジスタ    |    |

| M 1 2               | 第 9 トランジスタ    |    |

| M 1 5 _ 1           | 第 1 0 トランジスタ  |    |

| M 1 5 _ 2           | 第 1 1 トランジスタ  |    |

| M 1 6 _ 1           | 第 1 2 トランジスタ  |    |

| M 1 6 _ 2           | 第 1 3 トランジスタ  |    |

| M 1 4 _ 1           | 第 1 4 トランジスタ  |    |

| M 1 4 _ 2           | 第 1 5 トランジスタ  |    |

| M 1 9               | 第 1 6 トランジスタ  |    |

| M 1 8               | 出力トランジスタ      |    |

| O R n               | 論理ゲート         |    |

| O U T n             | 第 1 出力信号      |    |

| O U T B n           | 反転された第 1 出力信号 |    |

| O U T n + 1         | 第 2 出力信号      | 20 |

| O U T B n + 1       | 反転された第 2 出力信号 |    |

| V s p               | 開始パルス         |    |

| V c l k 、 C L K     | クロック信号        |    |

| V c l k b 、 C L K B | 反転されたクロック信号   |    |

| V D D               | 第 1 電源電圧      |    |

| V S S               | 第 2 電源電圧      |    |

| V p o s             | 正の電源電圧        |    |

| V n e g             | 負の電源電圧        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 3 H |

| H 0 5 B | 33/14 | A       |

| G 0 9 G | 3/20  | 6 8 0 G |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置，发光控制驱动装置和OR电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2007052432A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2007-03-01 |

| 申请号            | JP2006221420                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2006-08-15 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 鄭寶容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 鄭寶容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3233 G09G3/3266 G09G2300/0408 G09G2300/0417 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0221 G09G2310/0262 G09G2330/021 G11C19/00 G11C19/184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.A G09G3/20.621.E G09G3/20.624.B G09G3/20.621.A G09G3/20.623.H H05B33/14.A G09G3/20.680.G G09G3/20.624.Z G09G3/3266 G09G3/3275 G09G3/3291 G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC42 3K107/CC45 3K107/EE03 3K107/HH00 3K107/HH04 5C080 /AA06 5C080/BB05 5C080/DD22 5C080/DD26 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5B074/AA10 5B074/CA01 5C380/AA01 5C380/AB18 5C380/AB24 5C380/AB34 5C380 /AB40 5C380/AC05 5C380/BA01 5C380/BA11 5C380/BA28 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA08 5C380/CA12 5C380/CA48 5C380/CB01 5C380/CB12 5C380/CB16 5C380/CB17 5C380 /CB32 5C380/CB37 5C380/CC05 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC55 5C380/CC64 5C380/CD025 5C380/CF07 5C380/CF10 5C380/CF23 5C380/CF33 5C380/CF43 5C380/CF46 5C380 /DA02 5C380/DA06 5C380/HA03 5C380/HA07 |         |            |

| 优先权            | 1020050075428 2005-08-17 KR<br>1020050075429 2005-08-17 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 其他公开文献         | <a href="#">JP4789746B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

要解决的问题：提供一种在电致发光(EL)显示面板中被设计为面板上系统(SOP)类型的新型发射控制驱动器，并且提供一种有机电致发光显示装置和逻辑或电路。解决方案：有机发光显示(OLED)装置包括：具有多个像素的像素部分12;施加扫描信号的扫描驱动部14;施加数据信号的数据驱动部20;以及施加发射控制信号的发射控制驱动部分16。发射控制驱动部分16包括：具有多个触发器的移位寄存器;以及包括多个逻辑门的逻辑运算部分，其中每个逻辑门接收来自两个相邻的触发器的总共第一和第二输出信号OUT<sub>n</sub>，OUT<sub>n</sub>+1和第一和第二反相输出信号OUT<sub>Bn</sub>，OUT<sub>Bn</sub>+1的四个信号-移位寄存器中的触发器，控制有源负载，并通过逻辑或运算输出发射控制信号。Z