(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-134874

(P2005-134874A)

(43) 公開日 平成17年5月26日(2005.5.26)

(51) Int.Cl.<sup>7</sup>

G09G 3/30

G09G 3/20

H05B 33/14

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611H

5C080

G09G 3/20

621F

G09G 3/20

622C

G09G 3/20

622E

審査請求 未請求 請求項の数 20 O L (全 23 頁) 最終頁に続く

(21) 出願番号

特願2004-219579 (P2004-219579)

(22) 出願日

平成16年7月28日 (2004.7.28)

(31) 優先権主張番号

2003-076002

(32) 優先日

平成15年10月29日 (2003.10.29)

(33) 優先権主張国

韓国 (KR)

(71) 出願人

590002817

三星エスディアイ株式会社

大韓民国京畿道水原市靈通区▲しん▼洞5

75番地

(74) 代理人

100095957

弁理士 龟谷 美明

(74) 代理人

100096389

弁理士 金本 哲男

(72) 発明者

申 東蓉

大韓民国ソウル市冠岳区奉天1洞969-

37

(72) 発明者

キム グムナム

大韓民国ソウル市東大門区踏十里2洞21

-1番地 ダソムビラ302

最終頁に続く

(54) 【発明の名称】発光表示装置およびその表示パネルと駆動方法

## (57) 【要約】

【課題】発光表示装置の画素回路において、トランジスタのしきい電圧や移動度の偏差を補償し、データ線を速く充電できるようにする。

【解決手段】有機EL素子の駆動電流を調節する駆動トランジスタを備え、駆動トランジスタのゲート・ソース間に第1キャパシタ、ゲートとブースト走査線の間に第2キャパシタが連結されている。各画素回路が選択され、輝度設定用のデータ電流が送られて、データ線が所定時間内に充電され、その後、電流・電圧変換された電圧が第1キャパシタに保存される。次にブースト走査線の電圧レベルを変化させると、第1および第2キャパシタの電圧分割によって第1キャパシタの保存電圧が減少し、減少後の電圧に対応した微少電流が、駆動トランジスタから有機EL素子に供給され、有機EL素子が所望の明るさで発光する。これにより、データ線の寄生容量による信号遅延を軽減できる。

【選択図】 図8

## 【特許請求の範囲】

## 【請求項 1】

データ信号を伝達する複数のデータ線と；選択信号を伝達する複数の第1走査線と；第1制御信号を伝達する複数の第2走査線と；前記データ線と前記第1走査線によって定められる複数の画素回路を含む発光表示装置において，

前記画素回路は，

印加される電流に対応して発光する発光素子と；

前記第1走査線からの選択信号に応答して前記データ線からの前記データ信号を伝達する第1スイッチング素子と；

前記発光素子を発光させるための駆動電流を供給し，前記第1スイッチング素子から前記データ信号が伝達される間はダイオード連結されるトランジスタと；

前記第1スイッチング素子からの前記データ信号の電流であるデータ電流に対応する第1電圧を保存する第1保存素子と；

前記第1保存素子と前記第2走査線の間に電気的に連結されており，前記第1制御信号が第1レベルから第2レベルに変わった場合に前記第1保存素子とのカップリングによって前記第1保存素子の第1電圧を第2電圧に変更する第2保存素子と；

第2制御信号に応答して，前記第2電圧によって前記トランジスタから出力される前記駆動電流を前記発光素子に伝達する第2スイッチング素子と；

を含むことを特徴とする発光表示装置。

## 【請求項 2】

前記第1保存素子は，前記トランジスタの第1主電極と制御電極の間に電気的に連結され，前記第2保存素子は前記トランジスタの制御電極と前記第2走査線の間に電気的に連結されることを特徴とする，請求項1に記載の発光表示装置。

## 【請求項 3】

前記画素回路は，前記選択信号に応答して前記トランジスタをダイオード連結する第3スイッチング素子をさらに含むことを特徴とする，請求項1または2のいずれかに記載の発光表示装置。

## 【請求項 4】

前記第2制御信号は前記選択信号であり，前記第1スイッチング素子は第1導電タイプのトランジスタであり，前記第2スイッチング素子は前記第1導電タイプと反対である第2導電タイプのトランジスタであることを特徴とする，請求項1，2または3のいずれかに記載の発光表示装置。

## 【請求項 5】

前記第2制御信号を伝達する複数の第3走査線をさらに含むことを特徴とする，請求項1，2または3のいずれかに記載の発光表示装置。

## 【請求項 6】

前記第2制御信号が動作不能レベルである期間は，前記選択信号が動作可能レベルである期間を含むことを特徴とする，請求項1，2，3，4または5のいずれかに記載の発光表示装置。

## 【請求項 7】

前記第1制御信号が前記第1レベルである期間は，前記選択信号が動作可能レベルである期間を含むことを特徴とする，請求項1，2，3，4，5または6のいずれかに記載の発光表示装置。

## 【請求項 8】

前記第2制御信号が動作不能レベルである期間は，前記第1制御信号が前記第1レベルである期間を含むことを特徴とする，請求項1，2，3，4，5，6または7のいずれかに記載の発光表示装置。

## 【請求項 9】

前記複数の第1走査線に前記選択信号を供給する第1走査駆動部と；

前記複数の第2走査線に前記第1制御信号を供給する第2走査駆動部と；

10

20

30

40

50

をさらに含み，

前記第2走査駆動部は，前記第1制御信号の前記第1レベルおよび前記第2レベルの高低を決定して出力するバッファと；を含むことを特徴とする，請求項1，2，3，4，5，6，7または8のいずれかに記載の発光表示装置。

【請求項10】

前記バッファは，前記第1制御信号に対応する入力信号を受信し，前記入力信号とその反転信号に各々対応して前記第1レベルおよび前記第2レベルの電圧を前記第2走査線に出力することを特徴とする，請求項9に記載の発光表示装置。

【請求項11】

前記第1走査駆動部は，開始信号をシフトさせながら順次に出力する第1シフトレジスターと； 10

一定の周期を有する第2切断信号と；

前記第1シフトレジスターの出力を演算して前記第1シフトレジスターの出力の幅を調節して前記選択信号に対応する信号を出力する第1論理ゲートと；

を含み，

前記第2走査駆動部は前記開始信号をシフトさせながら順次に出力する第2シフトレジスターと；

一定の周期を有する第1切断信号と；

前記第2シフトレジスターの出力を演算して前記第2シフトレジスターの出力の幅を調節して前記第1制御信号に対応する信号を出力する第2論理ゲートと； 20

を含むことを特徴とする，請求項9または10のいずれかに記載の発光表示装置。

【請求項12】

前記第2切断信号の幅が前記第1切断信号の幅より広いことを特徴とする，請求項9，10または11のいずれかに記載の発光表示装置。

【請求項13】

前記第1走査駆動部は，前記第1シフトレジスターの出力を前記第2制御信号に対応させて出力することを特徴とする，請求項9，10，11または12のいずれかに記載の発光表示装置。

【請求項14】

データ信号を伝達する複数のデータ線と； 30

選択信号を伝達する複数の第1走査線と；

第1制御信号を伝達する複数の第2走査線と；

前記データ線と前記第1走査線に各々電気的に連結されている複数の画素回路を含む発光表示装置を駆動する方法において，

前記画素回路は，

前記選択信号の動作可能レベルに応答して前記データ線からのデータ信号を伝達する第1スイッチング素子と；

第1主電極と制御電極の間に第1保存素子が形成され，前記制御電極と前記第2走査線の間に第2保存素子が形成されているトランジスタと；

前記トランジスタからの駆動電流に対応して発光する発光素子と；を含み，

前記駆動方法は，

前記第1制御信号を第1レベルに維持した状態で前記選択信号を動作不能レベルから前記動作可能レベルに変更して前記データ信号の電流であるデータ電流に対応する電圧を前記第1保存素子に充電する第1段階と；

前記選択信号を前記動作可能レベルから前記動作不能レベルに変更して前記データ電流を遮断し，前記第1制御信号を前記第1レベルから第2レベルに変更して前記第1保存素子の電圧を変更する第2段階と；

を含むことを特徴とする発光表示装置の駆動方法。

【請求項15】

前記第1制御信号が前記第1レベルである期間は，前記選択信号が前記動作可能レベル 50

である期間を含むことを特徴とする，請求項14に記載の発光表示装置の駆動方法。

【請求項16】

前記発光表示装置は，第2制御信号を伝達する複数の第3走査線をさらに含み，前記第1段階で前記第2制御信号を動作不能レベルにして前記トランジスタから前記発光素子を電気的に遮断し，前記第2段階で前記第2制御信号を動作可能レベルにして前記トランジスタに前記発光素子を電気的に連結することを特徴とする，請求項14または15のいずれかに記載の発光表示装置の駆動方法。

【請求項17】

前記第2制御信号が前記動作不能レベルである期間は前記第1制御信号が前記第1レベルである期間を含むことを特徴とする，請求項14，15または16のいずれかに記載の発光表示装置の駆動方法。

【請求項18】

データ信号を伝達する複数のデータ線と；

選択信号を伝達する複数の走査線と；

前記データ線と前記走査線によって定められる画素回路と；

を含む発光表示装置の表示パネルにおいて，

前記画素回路は，

印加される電流に対応して発光する発光素子と；

前記発光素子を発光させるための駆動電流を供給するトランジスタと；

前記走査線からの選択信号に応答して前記データ線からの前記データ信号を前記トランジスタに伝達する第1スイッチング素子と；

前記選択信号に応答して前記トランジスタをダイオード連結する第2スイッチング素子と；

前記トランジスタの第1主電極と制御電極の間に電気的に連結される第1保存素子と；

前記トランジスタの制御電極と第1制御信号を供給する信号線の間に電気的に連結される第2保存素子と；

第2制御信号に応答して前記トランジスタからの駆動電流を前記発光素子に伝達する第3スイッチング素子と；

を含むことを特徴とする発光表示装置の表示パネル。

【請求項19】

前記選択信号によって前記データ信号が前記トランジスタに伝達される第1期間，

前記データ信号が遮断されて前記第1制御信号が第1レベルから第2レベルに変更され，

前記第2制御信号に応答して前記駆動電流が前記発光素子に伝達される第2期間の順序で動作することを特徴とする，請求項18に記載の発光表示装置の表示パネル。

【請求項20】

前記第2制御信号が動作不能レベルである期間は，前記第1制御信号が前記第1レベルである期間を含み，前記第1制御信号が前記第1レベルである期間は前記選択信号が動作可能レベルである期間を含むことを特徴とする，請求項18または19のいずれかに記載の発光表示装置の表示パネル。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は，発光表示装置とその表示パネルおよびその駆動方法に関し，特に有機物質の電界発光(有機EL；Organic Electroluminescence以下，“有機EL”と言う)を利用した能動駆動方式表示装置による電流記入方式に関する。

【背景技術】

【0002】

一般に有機EL表示装置は，蛍光性有機化合物を電気的に励起して発光させる表示装置であって，行列形態に配列されたN×M個の有機発光セルを電圧駆動あるいは電流駆動して映像を表現できるようになっている。このような現用の有機発光セルは，ダイオード特

10

20

30

40

50

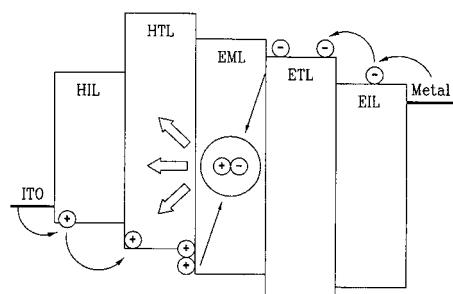

性を示すので有機発光ダイオード (OLED; Organic Light Emitting Diode) と呼ばれ、図1に示したようにアノード (ITO電極; Indium Tin Oxide Electrode; インジウムスズ酸化物電極)、有機薄膜、カソード電極層 (金属電極) の構造を有している。有機薄膜は電子と正孔の均衡を良くして発光効率を向上させるために発光層 (EML; Emissive Layer)、電子輸送層 (ETL; Electron Transport Layer) および正孔輸送層 (HTL; Hole Transport Layer) を含む多層構造からなり、また、別途の電子注入層 (EIL; Electron Injection Layer) と正孔注入層 (HIL; Hole Injection Layer) を含んでいる。

## 【0003】

10 このように構成される有機発光セルを駆動する方式には、単純マトリックス方式と薄膜トランジスタ (TFT; Thin Film Transistor) またはMOSFET (Metal Oxide Semiconductor Field Effect Transistor; MOS型電界効果トランジスタ) を利用した能動駆動方式がある。単純マトリックス方式では、正極線と負極線を直交するように配置して両電極線を1本づつ選択して駆動する。これに対し能動駆動方式では、薄膜トランジスタを各ITO画素電極に連結し、薄膜トランジスタのゲートに連結されたキャパシタ容量に蓄積される電圧によって駆動する方式である。本発明は能動駆動方式に属し、この方式はキャパシタに電圧を蓄積させるための印加信号形態によって電圧記入方式と電流記入方式に分かれる。

## 【0004】

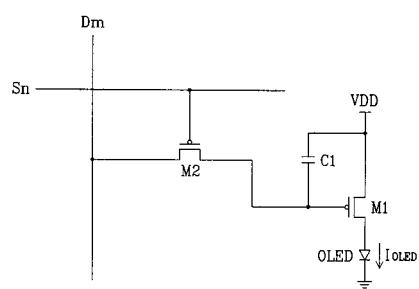

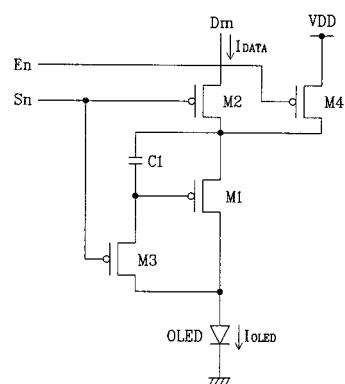

以下、図2および図3を参照して従来技術による電圧および電流記入方式の有機EL表示装置について説明する。なお、全文を通じて、使用する導電型がpチャンネルまたはnチャンネルである電界効果トランジスタ (Mi) を、pMOS (Mi) またはnMOS (Mi) ように、また、導電型不定の場合はMOS (Mi) と略記することもある。

## 【0005】

図2は有機EL素子を駆動するための従来の電圧記入方式の画素回路であって、N×M個の画素のうちの一つを代表的に示した図面である。図2によれば、有機EL素子 (OLED) にpMOS (M1) のドレインが連結されて発光のための電流を電源線 (VDD) から供給する。MOS (M1) の電流量はスイッチングMOS (M2) を通じて印加されるデータ電圧によって制御されるようになっている。この時、印加された電圧を一定期間維持するためのキャパシタ (C1) がMOS (M1) のソースとゲートの間に連結されている。MOS (M2) のゲートにはオン/オフ形態の選択信号を伝達する選択走査線 (S<sub>n</sub>) が連結されており、ソース側にはデータ線 (D<sub>m</sub>) が連結されている。

## 【0006】

30 このような構造の画素の動作を見てみると、スイッチングMOS (M2) のゲートに印加される選択信号によってMOS (M2) が導通すると、データ線 (D<sub>m</sub>) からのデータ電圧がMOS (M1) のゲートに印加される。その結果、キャパシタ (C1) によってゲートとソース (VDD線) の間に充電された電圧 (VGS) に対応してMOS (M1) に電流 (I<sub>OLED</sub>) が流れ、この電流 (I<sub>OLED</sub>) に対応して有機EL素子 (OLED) が発光する。

## 【0007】

この時、有機EL素子 (OLED) に流れる電流は次の数式1のようである。

## 【数1】

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = \frac{\beta}{2} (V_{DD} - V_{DATA} - |V_{TH}|)^2 \dots \dots \quad (\text{数式1})$$

ここで、I<sub>OLED</sub> は有機EL素子 (OLED) に流れる電流、V<sub>GS</sub> はMOS (M1) のゲート・ソース間の電圧、V<sub>TH</sub> はMOS (M1) のしきい電圧、V<sub>DATA</sub> はデータ

10

20

30

40

50

タ電圧，は定数値である。

【0008】

図2の画素回路によると，印加されるデータ電圧に対応する電流が，数式1で示すだけ，有機EL素子(OLED)に供給され，供給された電流に対応する輝度で有機EL素子(OLED)が発光する。この時，印加されるデータ電圧は所定の明暗階調を表現するために一定の範囲で多段階の値(階調)を有する。

【0009】

しかし，このような従来の電圧記入方式画素回路では製造工程の不均一性によって，薄膜MOSのしきい電圧( $V_{TH}$ )および電子移動度の偏差が画素ごとに生じるため，高い輝度分解能に要する多段階の階調が得がたいという問題点がある。例えば，3V幅の画像信号で画素の薄膜MOSを駆動する場合，8ビット(256)階調を表現するためには約12mV(=3V/256)間隔で薄膜MOSのゲート印加電圧を設定しなければならないが，もし製造工程の不均一で薄膜MOSのしきい電圧の偏差が100mVもある場合には，画素毎に明暗変動することも予想され，精密な明暗階調を表現することが難しくなる。また，移動度の偏差によって数式1での $I$ 値が変わるので，さらに精密階調を表現することが難しくなる。

【0010】

これに反し，電流記入方式の画素回路では，画素回路に電流を供給する電流源の特性が表示パネル全体，つまり，全てのデータ線に対して一様であるとすれば，各画素内の駆動MOSが不均一な電圧-電流特性を有するとしても均一なディスプレイ特性を得ることができる。このことは，各画素内の駆動MOSが小型化を要求されて特性不均一を生じ易くても，配置スペースに余裕のある電流源トランジスタを均一に製造できるであろうという考えに基づいている。

【0011】

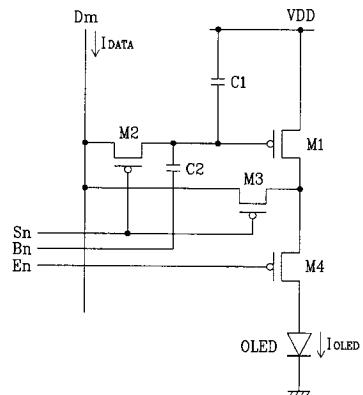

図3は，有機EL素子を駆動するための，従来の電流記入方式画素回路であって， $N \times M$ 個の画素のうちの一つを代表的に示した図面である。図3によれば，有機EL素子(OLED)にMOS(M1)が連結されて発光電流を供給し，MOS(M1)の電流値はMOS(M2)を通じて印加されるデータ電流によって制御されるようになっている。

【0012】

まず，回路の動作を見ると，選択走査線( $S_n$ )からの選択信号によってMOS(M2,M3)が導通すれば，pMOS(M1)はダイオード連結状態になって，MOS(M1)のゲート電位が低下し，キャパシタ(C1)に電流が流れ電圧が充電され，ソースからドレインに電流が流れる。時間経過によってキャパシタ(C1)の充電電圧が高くなつてMOS(M1)のドレイン電流がMOS(M2)のドレイン電流と同一になれば，キャパシタ(C1)の充電電流が停止して充電電圧が安定になる。したがって，データ線( $D_m$ )からの輝度設定用データ電流( $I_{DATA}$ )に対応する電圧がキャパシタ(C1)に保存される。次に，選択走査線( $S_n$ )からの選択信号が高電圧になってMOS(M2,M3)が遮断されるが，発光走査線( $E_n$ )からの発光信号が低電圧になってMOS(M4)が導通する。その結果，電源線( $VDD$ )から電流が供給されてキャパシタ(C1)に保存された電圧に対応する電流が有機EL素子(OLED)に流れ設定された輝度で発光が行なわれる。この時，有機EL素子(OLED)に流れる電流は数式2のようになる。

【0013】

【数2】

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = I_{DATA} \dots \dots \quad (\text{数式2})$$

ここで， $V_{GS}$ はMOS(M1)のゲートとソースの間の電圧， $V_{TH}$ はMOS(M1)

10

20

30

40

50

) のしきい電圧 , は定数値を示す。

【0014】

数式2で示したように, 従来の電流記入方式画素回路によると, 有機EL素子に流れる電流( $I_{OLED}$ )はデータ電流( $I_{DATA}$ )と同一であるので, 記入電流源が全データ線に対して均一であれば, 全ての画素が均一な特性を有する。しかし, 有機EL素子に流れる電流( $I_{OLED}$ )は微細電流でありながら, データ線の電圧範囲が広いので, 微細電流( $I_{DATA}$ )で画素回路を駆動する場合にはデータ線の寄生容量などを充電するのに時間が多くかかるという問題点がある。例えば, データ線負荷キャパシタンスが30pFであると仮定する場合, 数十nAから数百nA程度のデータ電流でデータ線の負荷を充電するためには数msの時間が必要である。これは数十μs水準であるライン時間(例えば, 水平走査時間)を考慮してみると, 充電時間が十分でないという問題点がある。

10

【発明の開示】

【発明が解決しようとする課題】

【0015】

本発明は, 上記問題点を解決するものであって, パソコンのしきい電圧や移動度を補償することができ, データ線を十分速く充電できる発光表示装置を提供することにある。

【課題を解決するための手段】

【0016】

上記課題を解決するために, 本発明のある観点によれば, データ信号を伝達する複数のデータ線と, 選択信号を伝達する複数の第1走査線と, 第1制御信号を伝達する複数の第2走査線と, データ線と第1走査線によって定められる複数の画素回路が形成されている発光表示装置が提供される。この画素回路は, 印加される電流に対応して発光する発光素子と, 第1走査線からの選択信号に応答してデータ線からのデータ信号を伝達する第1スイッチング素子と, 発光素子を発光させるための駆動電流を供給し, 第1スイッチング素子からデータ信号が伝達される期間はダイオード連結されるトランジスタと, 第1スイッチング素子からのデータ信号の電流であるデータ電流に対応する第1電圧を保存する第1保存素子と, 第1保存素子と第2走査線の間に電気的に連結されていて, 第1制御信号が第1レベルから第2レベルに変わる場合に第1保存素子とのカップリングを通じて第1保存素子の第1電圧を第2電圧に変更する第2保存素子と, 第2制御信号に応答して第2電圧によって前記トランジスタから出力される駆動電流を発光素子に伝達する第2スイッチング素子とを含む。

20

【0017】

この時, 上記第2制御信号が動作不能レベルである期間は選択信号が動作可能レベルである期間を含むことができる。そして, 上記第1制御信号が上記第1レベルである期間は選択信号が動作可能レベルである期間を含むことができ, 上記第2制御信号が動作不能レベルである期間は上記第1制御信号が上記第1レベルである期間を含むことができる。

30

【0018】

上記第1保存素子は, 上記トランジスタの第1主電極と制御電極の間に電気的に連結され, 上記第2保存素子は上記トランジスタの制御電極と上記第2走査線の間に電気的に連結されてもよい。

40

【0019】

上記画素回路は, 上記選択信号に応答して上記トランジスタをダイオード連結する第3スイッチング素子をさらに含むことができる。

【0020】

上記第2制御信号は上記選択信号であり, 上記第1スイッチング素子は第1導電タイプのトランジスタであり, 上記第2スイッチング素子は上記第1導電タイプと反対である第2導電タイプのトランジスタであってもよい。

【0021】

上記第2制御信号を伝達する複数の第3走査線をさらに含むことができる。

50

【 0 0 2 2 】

本発明の一つの特徴による発光表示装置は、複数の第1走査線に選択信号を供給する第1走査駆動部と、複数の第2走査線に第1制御信号を供給する第2走査駆動部とをさらに含み、第2走査駆動部は第1制御信号の第1レベルおよび第2レベルの電圧の値を決定して出力するバッファとを含むことができる。バッファは第1制御信号に対応する入力信号を受信し、入力信号と上記入力信号を反転した信号に各々対応して第1レベルおよび第2レベルの電圧を第2走査線に出力することができる。

【 0 0 2 3 】

上記第1走査駆動部は、開始信号をシフトさせながら順次に出力する第1シフトレジスターと、一定の周期を有する第2切断信号と、第1シフトレジスターの出力を演算して第1シフトレジスターの出力の幅を調節して上記選択信号に対応する信号を出力する第1論理ゲートとを含み、上記第2走査駆動部は開始信号をシフトさせながら順次に出力する第2シフトレジスターと、一定の周期を有する第1切断信号と、第2シフトレジスターの出力を演算して第2シフトレジスターの出力の幅を調節して上記第1制御信号に対応する信号を出力する第2論理ゲートとを含むことができる。

【 0 0 2 4 】

上記第2切断信号の幅が上記第1切断信号の幅よりも広くてもよい。

【 0 0 2 5 】

上記第1走査駆動部は、上記第1シフトレジスターの出力を上記第2制御信号に対応させて出力することができる。

【 0 0 2 6 】

上記課題を解決するために、本発明の別の観点によれば、データ信号を伝達する複数のデータ線と、選択信号を伝達する複数の第1走査線と、第1制御信号を伝達する複数の第2走査線と、データ線と第1走査線に各々電気的に連結されている複数の画素回路を含む発光表示装置を駆動する方法が提供される。画素回路は、選択信号の動作可能レベルに応答してデータ線からのデータ信号を伝達する第1スイッチング素子と、第1主電極と制御電極の間に第1保存素子が形成されて、制御電極と第2走査線の間に第2保存素子が形成されているトランジスタと、トランジスタからの駆動電流に対応して発光する発光素子とを含む。駆動方法は、第1制御信号を第1レベルに維持した状態で選択信号を動作不能レベルから動作可能レベルに変更してデータ信号の電流であるデータ電流に対応する電圧を第1保存素子に充電する第1段階と、選択信号を動作可能レベルから動作不能レベルに変更してデータ電流を遮断し、第1制御信号を第1レベルから第2レベルに変更して第1保存素子の電圧を変更する第2段階とを含む。

【 0 0 2 7 】

この時、上記第1制御信号が上記第1レベルである期間は選択信号が上記動作可能レベルである期間を含むことができる。

〔 0 0 2 8 〕

上記発光表示装置は、上記第2制御信号を伝達する複数の第3走査線をさらに含み、上記第1段階で上記第2制御信号を動作不能レベルにして上記トランジスタから上記発光素子を電気的に遮断し、上記第2段階で上記第2制御信号を動作可能レベルにして上記トランジスタに上記発光素子を電気的に連結することが可能である。

〔 0 0 2 9 〕

上記第2制御信号が上記動作不能レベルである期間は上記第1制御信号が上記第1レベルである期間を含むことが可能である。

[ 0 0 3 0 ]

上記課題を解決するために、本発明の他の観点によれば、データ信号を伝達する複数のデータ線と、選択信号を伝達する複数の走査線と、データ線と走査線によって定められる複数の画素回路とを含む発光表示装置の表示パネルが提供される。この画素回路は、印加される電流に対応して発光する発光素子と、発光素子を発光させるための駆動電流を供給するトランジスタと、走査線からの選択信号に応答してデータ線からのデータ信号をトラ

ンジスタに伝達する第1スイッチング素子と，選択信号に応答してトランジスタをダイオード連結する第2スイッチング素子と，トランジスタの第1主電極と制御電極の間に電気的に連結される第1保存素子と，トランジスタの制御電極と第1制御信号を供給する信号線の間に電気的に連結される第2保存素子と，第2制御信号に応答してトランジスタからの駆動電流を発光素子に伝達する第3スイッチング素子とを含む。

【0031】

上記選択信号によって上記データ信号が上記トランジスタに伝達される第1期間，上記データ信号が遮断されて上記第1制御信号が第1レベルから第2レベルに変更され，上記第2制御信号に応答して上記駆動電流が上記発光素子に伝達される第2期間の順序で動作することが可能である。

10

【0032】

この時，上記第2制御信号が動作不能レベルである期間は上記第1制御信号が第1レベルである期間を含み，上記第1制御信号が上記第1レベルである期間は選択信号が動作可能レベルである期間を含むことができる。

【発明の効果】

【0033】

本発明によれば，大きいデータ電流で有機EL素子に流れる電流を制御することができるので，1水平走査期間内はデータ線を十分に充電することができる。また，有機EL素子に流れる電流はトランジスタのしきい電圧偏差や移動度の偏差が補償され，高解像度と大面積の発光表示装置が実現できる。そして，データ線の寄生成分に適切に対応することができ，選択走査線を駆動する走査駆動部の負荷を減らすことができる。

20

【発明を実施するための最良の形態】

【0034】

以下に添付図面を参照しながら，本発明の好適な実施の形態について詳細に説明する。なお，本明細書及び図面において，実質的に同一の機能構成を有する構成要素については，同一の符号を付することにより重複説明を省略する。

【0035】

図面で本発明を明確に説明するために説明と関係ない部分は省略した。明細書全体を通じて類似部分については同一図面符号を付けた。ある部分が他の部分と連結されているとする時，これは直接的に連結されている場合だけでなく，その中間に他の素子を隔てて連結されている場合も含む。また，電源線(VDD)には電位VDDが与えられ，接地線には基準電位の零ボルトが与えられているものと仮定する。

30

【0036】

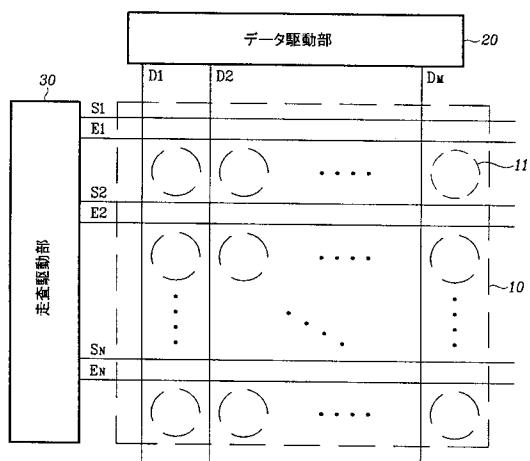

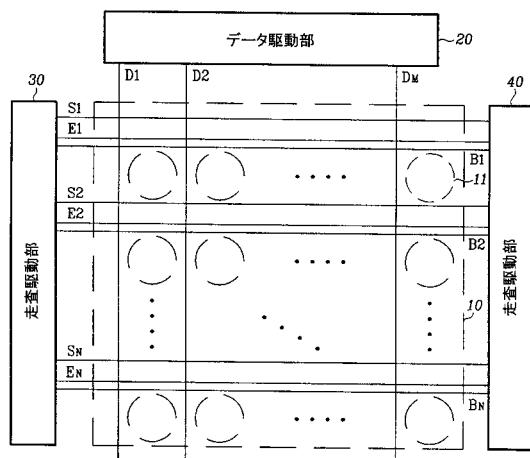

まず，図4を参照して本発明の実施形態に係る発光表示装置の一例として有機EL表示装置について説明する。図4は本発明の実施形態に係る発光表示装置の一例として有機EL表示装置の概略的な平面図である。

【0037】

図4によれば，本発明の実施形態に係る発光表示装置の一例としての有機EL表示装置は，有機EL表示パネル10，データ駆動部20および第1走査駆動部30を含む。

【0038】

有機EL表示パネル10は，縦に延びている複数のデータ線(D<sub>1</sub> - D<sub>M</sub>)，横に延びている複数の走査線(S<sub>1</sub> - S<sub>N</sub>，E<sub>1</sub> - E<sub>N</sub>)および複数の画素回路11を含む。データ線(D<sub>1</sub> - D<sub>M</sub>)は画像信号を示すデータ電流を画素回路11に伝達する。選択走査線(S<sub>1</sub> - S<sub>N</sub>)は選択信号を画素回路11に伝達し，発光走査線(E<sub>1</sub> - E<sub>N</sub>)は発光信号を画素回路11に伝達する。画素回路11は隣接した二つのデータ線と隣接した二つの選択走査線によって定義される画素領域に形成されている。選択走査線は，第1走査線に，発光走査線は，第3走査線に相当する。

40

【0039】

データ駆動部20は，データ線(D<sub>1</sub> - D<sub>M</sub>)にデータ電流を印加し，第1走査駆動部30は選択走査線(S<sub>1</sub> - S<sub>N</sub>)および発光走査線(E<sub>1</sub> - E<sub>N</sub>)に各々選択信号および発

50

光信号を順次に印加する。

【0040】

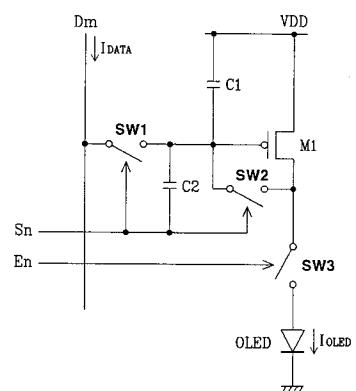

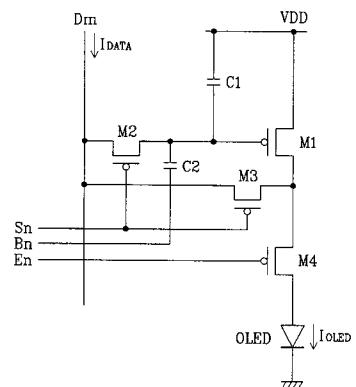

次に、図5を参照して本発明の第1実施形態に係る発光表示装置の一例としての有機EL表示装置の画素回路11について詳細に説明する。図5は本発明の第1実施形態に係る画素回路の等価回路図である。そして、図5では説明の便宜上、m番目データ線(D<sub>m</sub>)とn番目選択走査線(S<sub>n</sub>)に連結された画素回路のみを示した。

【0041】

図5によれば、本発明の第1実施形態に係る画素回路11は有機EL素子(OLED、発光素子)、MOS(M1)、スイッチング素子(SW1, SW2, SW3)およびキャパシタ(C1, C2)を含み、MOS(M1)にはpMOSを使用している。

10

【0042】

スイッチング素子(SW1、第1スイッチング素子)はデータ線(D<sub>m</sub>)とMOS(M1、トランジスタ)のゲートの間に連結され、選択走査線(S<sub>n</sub>)からの選択信号に応答してデータ線(D<sub>m</sub>)からのデータ電流(I<sub>DATA</sub>)をMOS(M1)に伝達する。スイッチング素子(SW2、第3スイッチング素子)はMOS(M1)のドレインとゲートの間に連結され、選択走査線(S<sub>n</sub>)からの選択信号に応答してMOS(M1)をダイオード連結させる。この時、図5のデータ電流(I<sub>DATA</sub>)に付けられた矢印は信号が送られる方向を示し、電流の流れる方向とは反対になっていて、全体的な電流の流れは、電源線(VDD)からpMOS(M1)のソースとドレインを通ってデータ線(D<sub>m</sub>)に流れ、発光時には発光素子(OLED)に流れる。

20

【0043】

MOS(M1)は電源線(VDD)にソースが連結され、スイッチング素子(SW3、第2スイッチング素子)にドレインが連結されている。MOS(M1)のゲート-ソース電圧はデータ電流(I<sub>DATA</sub>)に対応して決定され、キャパシタ(C1、第1保存素子)はMOS(M1)のゲート(制御電極)とMOS(M1)のソース(第1主電極)の間に連結されて、MOS(M1)のゲート-ソース電圧を一定期間維持する。キャパシタ(C2、第2保存素子)は、ゲート-ソース電圧を低下させる目的で、選択走査線(S<sub>n</sub>)とMOS(M1)のゲートの間に連結されて、MOS(M1)のゲート電圧を調節する。

【0044】

スイッチング素子(SW3)は発光走査線(E<sub>n</sub>)からの発光信号(第2制御信号)に応答してMOS(M1)に流れる電流を有機EL素子(OLED)に供給する。有機EL素子(OLED)はスイッチング素子(SW3)と接地線の間に連結され、MOS(M1)に流れる電流の量に対応した光を発する。

30

【0045】

本発明の第1実施形態ではスイッチング素子(SW1, SW2, SW3)を一般的なスイッチとして示したが、スイッチング素子(SW1, SW2, SW3)もMOSで形成することが好ましい。以下ではスイッチング素子(SW1, SW2, SW3)をpMOSで実現した実施形態について図6および図7を参照して詳細に説明する。

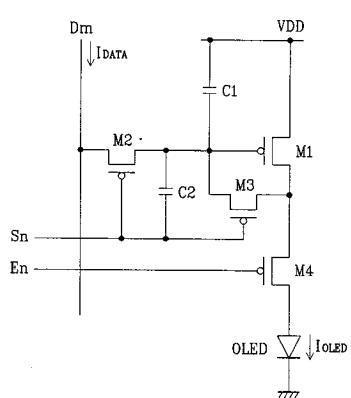

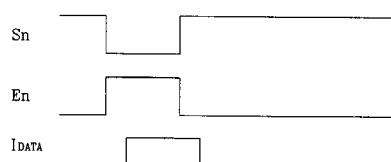

【0046】

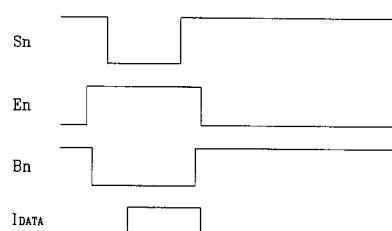

図6は本発明の第2実施形態に係る画素回路の回路図であり、図7は図6の画素回路を駆動するための駆動波形図である。

40

【0047】

図6に示したように、本発明の第2実施形態に係る画素回路は図5の画素回路でスイッチング素子(SW1, SW2, SW3)の代りにMOS(M2, M3, M4)が形成されている点を除けば、第1実施形態と同一な構造を有する。MOS(M2, M3, M4)はpMOSで形成されており、MOS(M2, M3)のゲートには選択走査線(S<sub>n</sub>)が連結され、MOS(M4)のゲートには発光走査線(E<sub>n</sub>)が連結されている。本発明に係る実施形態において、MOS(M2)は、第1スイッチング素子に、MOS(M3)は、第3スイッチング素子に、また、MOS(M4)は第2スイッチング素子に相当する。

【0048】

50

次に、図7を参照して図6の画素回路の動作について詳しく説明する。まず、選択走査線( $S_n$ )を通じて印加される低電圧(動作可能レベル)の選択信号によってMOS(M2, M3)が導通し、MOS(M1)はダイオード連結されてデータ線( $D_m$ )からのデータ電流( $I_{DATA}$ )がMOS(M1)に流れる。そして、発光走査線( $E_n$ )を通じて印加される高電圧(動作不能レベル)の発光信号によってMOS(M4)は遮断されていて、MOS(M1)と有機EL素子(OLED)は電気的に遮断されている。ここで、低電圧(動作可能レベル)または高電圧(動作不能レベル)とは、pMOSが通電可能か不能かを基準にした表現で、説明する対象に応じて表現が変化する。

例えば、nMOSについて論じる場合には、高電圧(動作可能レベル)または低電圧(動作不能レベル)となる。

10

【0049】

この時、MOS(M1)のゲートとソースの間の電圧の絶対値(以下、“ゲート-ソース電圧”と言う)( $V_{GS}$ )とMOS(M1)に流れる電流( $I_{DATA}$ )の間には数式3の関係が成立するので、MOS(M1)のゲート-ソース電圧( $V_{GS}$ )は数式4のようになる。

【0050】

【数3】

$$I_{DATA} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 \quad \dots \dots \quad (\text{数式3})$$

20

ここで、 $\beta$ は定数値であり、 $V_{TH}$ はMOS(M1)のしきい電圧の絶対値である。

【0051】

【数4】

$$V_{GS} = V_{DD} - V_G = \sqrt{\frac{2I_{DATA}}{\beta}} + V_{TH} \quad \dots \dots \quad (\text{数式4})$$

30

ここで、 $V_G$ はMOS(M1)のゲート電圧であり、 $V_{DD}$ は電源線( $V_{DD}$ )によってMOS(M1)に供給される電圧である。

【0052】

次に、選択走査線( $S_n$ )の選択信号が高電圧(動作不能レベル)になって、発光走査線( $E_n$ )の発光信号が低電圧(動作可能レベル)になれば、pMOS(M2, M3)が遮断され、pMOS(M4)が導通する。選択走査線( $S_n$ )の選択信号が低電圧から高電圧になればキャパシタ( $C_2$ )と選択走査線( $S_n$ )の接続点の電圧が選択信号のレベル上昇幅( $V_S$ )ほど上昇する。したがって、キャパシタ( $C_1, C_2$ )のカップリングによってMOS(M1)のゲート電圧( $V_G$ )は上昇し、その上昇幅( $V_S$ )は数式5のようになる。

40

【0053】

【数5】

$$\Delta V_G = \frac{\Delta V_S C_2}{C_1 + C_2} \quad \dots \dots \quad (\text{数式5})$$

ここで、 $C_1$ および $C_2$ は各々キャパシタ( $C_1, C_2$ )のキャパシタンスである。

【0054】

MOS(M1)のゲート電圧( $V_G$ )が $V_S$ だけ増加したので、MOS(M1)に流

50

れる電流 ( $I_{OLED}$ ) は数式 6 のようになる。つまり, MOS (M1) のゲート電圧 ( $V_G$ ) が増加しただけ, MOS (M1) のゲート-ソース電圧 ( $V_{GS}$ ) の電圧値が小さくなるので, MOS (M1) のドレイン電流 ( $I_{OLED}$ ) の電流値をデータ電流 ( $I_{DATA}$ ) に比べて小さくすることができる。そして, 発光走査線 ( $E_n$ ) の発光信号によって MOS (M4) が導通しているので, MOS (M1) の電流 ( $I_{OLED}$ ) が有機EL素子 (OLED) に供給されて発光する。つまり, まず大電流でデータ線とキャパシタ (C1) を高速充電し, 次に, キャパシタ (C2) 接続により, MOS (M1) のゲート-ソース電圧 ( $V_{GS}$ ) を小さくして, 有機EL素子 (OLED) に適切な大きさの電流を供給できる。

【0055】

10

【数6】

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - \Delta V_G - V_{TH})^2 = \frac{\beta}{2} \left( \sqrt{\frac{2I_{DATA}}{\beta}} - \Delta V_G \right)^2$$

· · · · (数式6)

【0056】

そして, 数式 6 からデータ電流 ( $I_{DATA}$ ) は数式 7 のように与えられるので, データ電流 ( $I_{DATA}$ ) を有機EL素子 (OLED) に流れる電流 ( $I_{OLED}$ ) より大きい値に設定することができる。つまり, 大きいデータ電流 ( $I_{DATA}$ ) で有機EL素子 (OLED) に流れる微細電流を制御することができるので, データ線の充電時間を確保することができる。

【0057】

20

【数7】

$$I_{DATA} = I_{OLED} + \Delta V_G \sqrt{2\beta I_{OLED}} + \frac{\beta}{2} (\Delta V_G)^2$$

· · · · (数式7)

【0058】

本発明の第2実施形態では, 走査線 ( $S_n$ ) からの選択信号でキャパシタ (C2) の接続点電圧を設定した。この時, MOS (M1, M2, M3) に存在する寄生キャパシタンス成分によって数式 5 でキャパシタ (C1, C2) の比率 ( $C_2 / (C_1 + C_2)$ ) が変わることがある。ところが, 選択信号の電圧変動幅 ( $V_S$ ) は固定されているので, キャパシタ (C1, C2) の比率 ( $C_2 / (C_1 + C_2)$ ) 変動に適切に対応できない。したがって, 数式 5 でゲート電圧 ( $V_G$ ) の増加量 ( $\Delta V_G$ ) が調節され, これにより数式 6 で  $I_{OLED}$  値が変化する。つまり, 有機EL素子 (OLED) に供給される電流 ( $I_{OLED}$ ) が設定値と異なる値を有するようになり輝度が変わることがある。

30

【0059】

以下, 選択走査線 ( $S_n$ ) の代りに別途の信号線でキャパシタ (C2, 第2保存素子) の入力端を駆動する実施形態について図8および図9を参照して詳細に説明する。

40

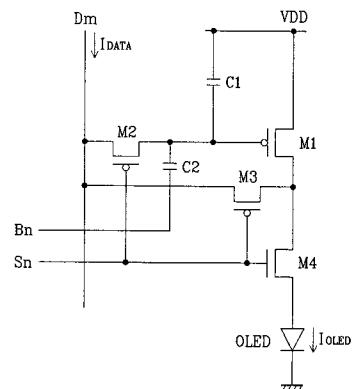

【0060】

図8は本発明の第3実施形態に係る画素回路の回路図であり, 図9は図8の画素回路を駆動するための駆動波形図である。

【0061】

図8に示したように, 第3実施形態に係る画素回路はキャパシタ (C2) の入力端に連結されるブースト走査線 ( $B_n$ , 第2走査線) とMOS (M3) の連結状態を除くと, 図6の画素回路と同一である。つまり, キャパシタ (C2) の入力端には選択走査線 ( $S_n$ ) の代りにブースト走査線 ( $B_n$ ) が連結されている。そして, 図9に示したように, ブースト走査線 ( $B_n$ ) からのブースト信号 (第1制御信号) は選択走査線 ( $S_n$ ) からの選択信号と同一な形態を有する。

50

## 【0062】

また、図6のようにMOS(M3)がMOS(M1)のゲートとドレインの間に連結されている場合にはMOS(M3)が遮断される時、MOS(M1)のゲート電圧が影響を受けてキャパシタ(C1, C2)の電圧が変わることがある。ところが、図8のようにMOS(M3)がMOS(M1)のドレインとデータ線(D<sub>m</sub>)の間に連結されると、MOS(M3)が遮断される時、MOS(M1)のゲート電圧が受ける影響を軽減できる。

## 【0063】

そして、キャパシタ(C2)の入力端の電圧はブースト走査線(B<sub>n</sub>)からのブースト信号の電圧上昇幅(ΔV<sub>B</sub>)だけ上昇し、MOS(M1)のゲート電圧(V<sub>G</sub>)の増加量(ΔV<sub>G</sub>)は式8のようになる。したがって、MOS(M1, M2, M3)の寄生キャパシタンス成分に対応してブースト信号の電圧上昇幅(ΔV<sub>B</sub>)を調節してMOS(M1)のゲート電圧(V<sub>G</sub>)の上昇幅(ΔV<sub>G</sub>)を所望の値に設定することができる。つまり、有機EL素子(OLED)に供給される電流(I<sub>OLED</sub>)を所望の値に設定することができる。ここで、回路の動作を見ると、選択走査線(S<sub>n</sub>)からの低電圧(動作可能レベル)の選択信号によりMOS(M2, M3)が導通し、キャパシタ(C1)にデータ電流に対応する電圧(第1電圧)が保存される。その後、選択走査線(S<sub>n</sub>)からの高電圧(動作不能レベル)の選択信号によりMOS(M2, M3)が遮断され、ブースト信号からの信号が低電圧(第1レベル)から高電圧(第2レベル)に変更された時、キャパシタ(C1)とキャパシタ(C2)の電圧分割によって、キャパシタ(C1)の電圧が減少する(第2電圧)。そして、発光走査線(E<sub>n</sub>)からの信号によってMOS(M4)が導通し、キャパシタ(C1)の減少した電圧に対応した電流がMOS(M1)から有機EL素子(OLED)に供給され、有機EL素子(OLED)が所望の明るさで発光する。

## 【0064】

## 【数8】

$$\Delta V_G = \frac{\Delta V_B C_2}{C_1 + C_2} \dots \dots \text{ (式8)}$$

## 【0065】

また、第2実施形態のように選択走査線(S<sub>n</sub>)がキャパシタ(C2)に連結されれば、キャパシタ(C2)によって選択走査線(S<sub>n</sub>)を駆動する第1走査駆動部30の負荷が大きくなる。ところが、第3実施形態のようにキャパシタ(C2)を別途のブースト走査線(B<sub>n</sub>)で駆動すれば、選択走査線(S<sub>n</sub>)を駆動する第1走査駆動部30のドライバーの負荷を減らすことができる。

## 【0066】

そして、図9では選択信号、発光信号およびブースト信号のタイミングを同一に表示したが、これとは異なって、これらタイミングを異ならせることもできる。

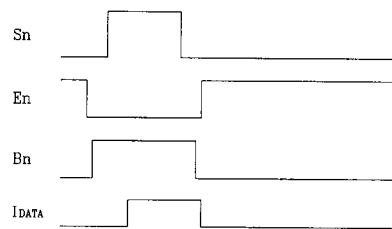

## 【0067】

まず、図10を参照して本発明の第4実施形態に係る駆動波形について説明する。図10は図8の画素回路を駆動する本発明の第4実施形態に係る駆動波形図である。

## 【0068】

選択走査線(S<sub>n</sub>)の選択信号によってMOS(M2, M3)が導通してMOS(M1)にデータ電流(I<sub>DATA</sub>)が伝達される間にMOS(M4)が遮断されている必要がある。もし、MOS(M1)にデータ電流(I<sub>DATA</sub>)が伝達される間にMOS(M4)が導通して有機EL素子(OLED)に電流が流れると、MOS(M1)のドレインにはデータ電流(I<sub>DATA</sub>)と有機EL素子(OLED)に流れる電流のベクトル和に相当する電流が流れ、この電流に対応する電圧がキャパシタ(C1)に記入される。しかし、図9のような場合には、選択走査線(S<sub>n</sub>)と発光走査線(E<sub>n</sub>)に連結される負荷の差によって選択信号の上昇時間と発光信号の下降時間が異なることがある。したがって、図10のように発光信号のパルスの終わりを選択信号のパルスの終わりより後にくるよう

10

20

30

40

50

にすれば、MOS(M2)が導通している途中にMOS(M4)が導通しない。

【0069】

そして、ブースト走査線( $B_n$ )からのブースト信号のパルスの終わりが選択信号のパルスの終わりより先にくれば、キャパシタ(C2)の入力端電圧が上昇した後にデータ電流( $I_{DATA}$ )の記入が完了するので、キャパシタ(C2)の入力端電圧を上昇させた効果がなくなる。したがって、図10のように選択走査線( $S_n$ )に伝達される選択信号のパルスの終わりをブースト走査線( $B_n$ )に伝達されるブースト信号のパルスの終わりより先に持ってくると、データ電流( $I_{DATA}$ )の記入後にキャパシタ(C2)の入力端電圧が上昇する。

【0070】

また、ブースト信号のパルス開始が選択信号のパルス開始より後に来ると、キャパシタ(C1)に電圧が記入される途中でキャパシタ(C2)の入力端電圧下降によってキャパシタ(C1)の電圧が変わる。このようにキャパシタ(C1)の電圧が変化するとキャパシタ(C1)の電圧記入動作が再び行われなければならないので、キャパシタ(C1)に電圧を記入する時間が足りない。したがって、図10のように選択走査線( $S_n$ )に伝達される選択信号の開始をブースト走査線( $B_n$ )に伝達されるブースト信号の開始より後にくるようにすれば、キャパシタ(C2)の入力端電圧が下降した後にデータ電流( $I_{DATA}$ )の記入動作が行なわれる。

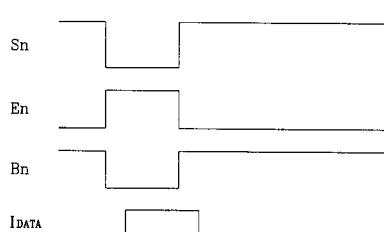

【0071】

次に、図11を参照して本発明の第5実施形態に係る駆動波形について説明する。図1 20

1は図8の画素回路を駆動する本発明の第5実施形態に係る駆動波形図である。

【0072】

図9のタイミングでブースト信号線( $B_n$ )と発光走査線( $E_n$ )に連結される負荷の差によって発光信号のパルスの終わりがブースト信号のパルスの終わりより先に来ると、発光信号のパルスの終わりとブースト信号のパルスの終わりの間の期間内にキャパシタ(C2)の入力端電圧上昇前の電流が有機EL素子(OLED)に流れ、有機EL素子(OLED)にストレスを与える。このような動作が継続して繰り返されれば有機EL素子(OLED)の寿命が短くなることがある。したがって、図11のようにブースト信号線( $B_n$ )に伝達されるブースト信号のパルスの終わりを発光走査線( $E_n$ )に伝達される発光信号のパルスの終わりより先にくるようにして、キャパシタ(C2)の入力端電圧上昇後に有機EL素子(OLED)に電流が流れるようにする。

【0073】

そして、発光信号のパルス開始がブースト信号のパルス開始より後に来ると、ブースト信号のパルス開始と発光信号のパルス開始の間の期間内にキャパシタ(C2)の電圧下降による電流が有機EL素子(OLED)に流れ、有機EL素子(OLED)にストレスを与える。このようなストレスが繰り返されると有機EL素子(OLED)の寿命が短くなることがある。したがって、図11のように発光信号のパルス開始をブースト信号のパルス開始より先にくるようにして、MOS(M4)が遮断された後にキャパシタ(C2)の入力端電圧が下降するようにする。

【0074】

このように本発明の第2実施形態～第5実施形態ではMOS(M2, M3, M4)をpMOSで説明したが、本発明はこれに限定されず、MOS(M2, M3, M4)をpチャンネル、nチャンネルまたはこれらの組み合わせで使用することもできる。MOS(M2, M3, M4)がnチャンネルである場合には選択信号と発光信号は図7、図9、図10および図11の選択信号と発光信号に対して反転した形態を有すればよい。本発明に係る実施形態において、pチャンネルおよびnチャンネルは、第1導電タイプのトランジスタ、第2導電タイプのトランジスタに相当する。

【0075】

特に、MOS(M2, M3)をpチャンネル、MOS(M4)をnチャンネルにする場合、またはMOS(M2, M3)をnチャンネル、MOS(M4)をpチャンネルとする

10

20

30

40

50

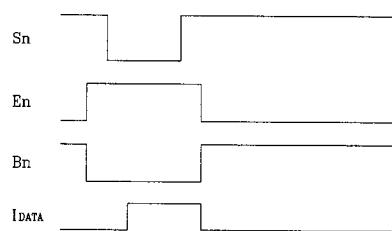

場合には発光走査線 ( $E_n$ ) を除去することもできる。以下、このような実施形態について図12を参照して説明する。図12は本発明の第6実施形態に係る画素回路の回路図である。

#### 【0076】

図12に示したように、本発明の第6実施形態に係る画素回路は、MOS(M4)がnチャンネルであり、MOS(M4)のゲートに選択走査線 ( $S_n$ ) が連結された点を除くと、図8の画素回路と同じ構造を有する。つまり、MOS(M4)のゲートには発光走査線 ( $E_n$ ) の代りに選択走査線 ( $S_n$ ) が連結されている。その結果、選択走査線 ( $S_n$ ) からの選択信号が低電圧になる時、MOS(M4)は遮断され、選択信号が高電圧になる時、MOS(M4)は導通するので、第6実施形態に係る画素回路は第3実施形態の画素回路と同じ動作を行なう。

#### 【0077】

そして、MOS(M4)がpチャンネルであり、MOS(M2, M3)がnチャンネルである場合には、選択走査線 ( $S_n$ ) に伝達される選択信号が反転した形態であればよい。このような場合の詳細な動作は当業者であれば容易に分かるので詳細な説明を省略する。

#### 【0078】

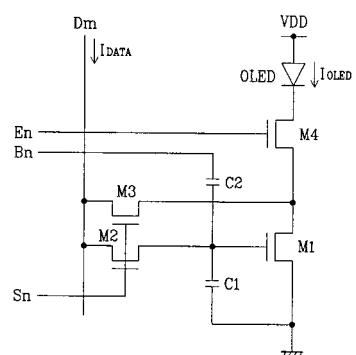

また、本発明の第1実施形態～第5実施形態では、MOS(M1)をpMOSとして説明したが、これとは異なってnMOSをMOS(M1)として用いることもできる。以下、図13および図14を参照してこのような実施形態について詳細に説明する。

#### 【0079】

図13は本発明の第7実施形態による画素回路の回路図であり、図14は図13の画素回路を駆動するための駆動波形図である。

#### 【0080】

図13に示すように、本発明の第7実施形態による画素回路は、MOS(M1～M4)が全てnMOSで実現されており、その連結構造は、図8の画素回路と対称をなす。詳しく説明すると、MOS(M2)はデータ線 ( $D_m$ ) とMOS(M1)のゲートの間に連結され、そのゲートに選択走査線 ( $S_n$ ) が連結される。MOS(M3)はMOS(M1)のドレインとデータ線 ( $D_m$ ) の間に連結され、そのゲートに選択走査線 ( $S_n$ ) が連結される。MOS(M1)は接地線にソースが連結され、有機EL素子 (OLED) にドレインが連結されている。キャパシタ (C1) はMOS(M1)のゲートとソースの間に連結され、有機EL素子 (OLED) はMOS(M4)と電源線 (VDD) の間に連結される。MOS(M4)のゲートには発光走査線 ( $E_n$ ) が連結されており、キャパシタ (C2) の入力端にはブースト走査線 ( $B_n$ ) が連結されている。

#### 【0081】

そして、MOS(M2, M3, M4)がnMOSであるので、図14に示したように、図13の画素回路を駆動するために選択走査線 ( $S_n$ ) と発光走査線 ( $E_n$ ) に各々伝達される選択信号と発光信号は図9に示した信号に対して反転した形態を有する。また、MOS(M1)がnMOSであるのでMOS(M1)のゲート-ソース電圧 ( $V_{GS}$ ) の値を小さくするためには、MOS(M1)のゲート電圧 ( $V_G$ ) を下降させなければならない。したがって、ブースト走査線 ( $B_n$ ) に伝達されるブースト信号も図9のブースト信号に対して反転した形態を有する。

#### 【0082】

図13の画素回路の詳細な動作は第3実施形態の説明から容易に分かるので、その説明を省略する。そして、図13の画素回路に対しても前述した全ての変形された形態を適用することができ、これに対する詳細な説明は省略する。

#### 【0083】

次に、第3実施形態～第7実施形態のようにブースト走査線 ( $B_n$ ) を選択走査線 ( $S_n$ ) と異ならせて駆動する場合には、図15に示したように発光表示装置の一例としての有機EL表示装置はブースト走査線 ( $B_n$ ) を駆動するための第2走査駆動部40をさら

に含むことができる。以下では第1走査駆動部30, 第2走査駆動部40について図16および図17を参照して詳細に説明する。

【0084】

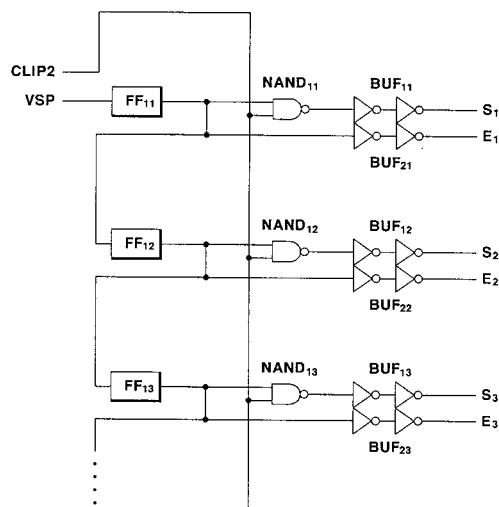

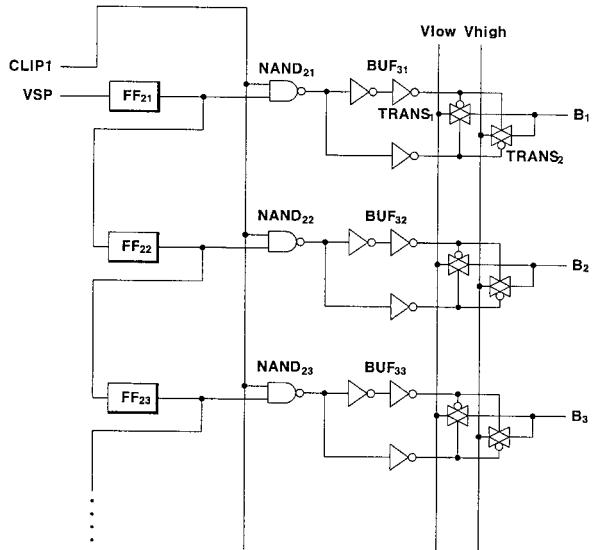

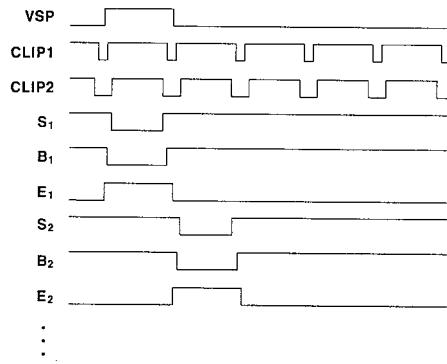

図16は図8の画素回路の選択走査線と発光走査線を駆動するための走査駆動部の概略的な図面であり, 図17は図8の画素回路のブースト信号線を駆動するための走査駆動部の概略的な図面である。図18は図16および図17の走査駆動部の駆動タイミング図である。

【0085】

図16に示したように, 選択走査線と発光走査線を駆動するための第1走査駆動部30はN個のフリップフロップ( $FF_{1,1} \sim FF_{1,N}$ , 第1シフトレジスター), N個の2入力NANDゲート( $NAND_{1,1} \sim NAND_{1,N}$ , 第1論理ゲート)および2N個のバッファ( $BUF_{1,1} \sim BUF_{1,N}$ ,  $BUF_{2,1} \sim BUF_{2,N}$ )からなる。任意のフリップフロップ( $FF_{1,j}$ ,  $j = 1 \sim N - 1$ )の出力端は次段フリップフロップ( $FF_{1,j+1}$ )の入力端に連結されてシフトレジスターとして動作する。つまり, 第1フリップフロップ( $FF_{1,1}$ )の出力端は第2フリップフロップ( $FF_{1,2}$ )の入力端に連結され, 第2フリップフロップ( $FF_{1,2}$ )の出力端は第3フリップフロップ( $FF_{1,3}$ )の入力端に連結される形態で連結されている。そして, 第1フリップフロップ( $FF_{1,1}$ )の入力端には開始信号のパルス( $VSP$ )が入力される。

【0086】

任意のフリップフロップ( $FF_{1,j}$ ,  $j = 1 \sim N$ )の出力は, 第2切断信号( $CLIP_2$ )と共に対応する2入力NANDゲート( $NAND_{1,j}$ )の入力になり, このNANDゲート( $NAND_{1,j}$ )の出力はバッファ( $BUF_{1,j}$ )に入力される。バッファ群( $BUF_{1,1} \sim BUF_{1,N}$ ,  $BUF_{2,1} \sim BUF_{2,N}$ )の各々は, 一般にいくつかのインバータからなり, 図16では2個のインバータで形成されて同相出力になっている。そして, バッファ( $BUF_{1,j}$ )の出力端が選択走査線( $S_j$ )に連結されている。また, 各フリップフロップ( $FF_{1,j}$ )の出力はバッファ( $BUF_{2,j}$ )に直接連結され, このバッファ( $BUF_{2,j}$ )の出力端が発光走査線( $E_j$ )に連結されている。

【0087】

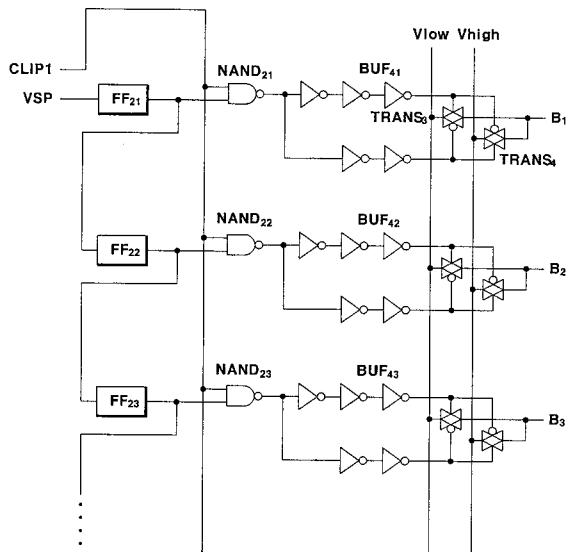

次に, 図17に示すように, ブースト走査線を駆動するための第2走査駆動部40はN個のフリップフロップ( $FF_{2,1} \sim FF_{2,N}$ , 第2シフトレジスター), N個の2入力NANDゲート( $NAND_{2,1} \sim NAND_{2,N}$ , 第2論理ゲート)およびN個のバッファ( $BUF_{3,1} \sim BUF_{3,N}$ )で構成される。図16と同様に任意のフリップフロップ( $FF_{2,j}$ ,  $j = 1 \sim N - 1$ )の出力端は次段フリップフロップ( $FF_{2,j+1}$ )の入力端に連結されてシフトレジスターとして動作し, 第1フリップフロップ( $FF_{2,1}$ )の入力端には開始信号のパルス( $VSP$ )が入力される。

【0088】

任意のフリップフロップ( $FF_{2,j}$ ,  $j = 1 \sim N$ )の出力は, 第1切断信号( $CLIP_1$ )と共に対応する2入力NANDゲート( $NAND_{2,j}$ )の入力になり, このNANDゲート( $NAND_{2,j}$ )の出力はバッファ( $BUF_{3,j}$ )に入力される。各バッファ( $BUF_{3,j}$ )はバッファ機能を行なうために, NANDゲート( $NAND_{2,j}$ )の出力を同相増幅する2段のインバータと, NANDゲート( $NAND_{2,j}$ )の出力を反転増幅する1段のインバータと, ブースト信号のレベル( $V_{high}$ 又は $V_{low}$ )を選択するための2個のCMOS伝達ゲート( $TRANS_1$ ,  $TRANS_2$ )を含む。

【0089】

第1伝達ゲート( $TRANS_1$ )は低い電圧を供給する信号線( $V_{low}$ )とブースト走査線( $B_j$ )の間に連結されており, 2段のインバータを通過したNANDゲート( $NAND_{2,j}$ )の出力が低電圧である場合または1段のインバータを通過したNANDゲート( $NAND_{2,j}$ )の出力が高電圧である場合に, 低い電圧をブースト走査線( $B_n$ )に出力する。そして, 第2伝達ゲート( $TRANS_2$ )は高い電圧を供給する信号線( $V_{high}$ )とブースト信号線( $B_j$ )の間に連結されており, 2段のインバータを通過した

10

20

30

40

50

NANDゲート( $NAND_{2j}$ )の出力が高電圧である場合または1段のインバータを通過したNANDゲート( $NAND_{2j}$ )の出力が低電圧である場合に高い電圧をブースト走査線( $B_j$ )に出力する。

#### 【0090】

次に、図16および図17の走査駆動部の動作を図18を参照して説明する。

#### 【0091】

まず、第1走査駆動部30の動作を見ると、図18に示したように開始信号のパルス( $VSP$ )がフリップフロップ群( $FF_{11} \sim FF_{1N}$ )内部で順次にシフトされて各々出力される。フリップフロップ( $FF_{11} \sim FF_{1N}$ )の出力はNANDゲート( $NAND_{11} \sim NAND_{1N}$ )によって第2切断信号( $CLIP_2$ )とNAND演算されて幅が減り、反転した形態で出力される。このNANDゲート( $NAND_{11} \sim NAND_{1N}$ )の出力がバッファ( $BUF_{11} \sim BUF_{1N}$ )を経て選択走査線( $S_1 \sim S_N$ )に選択信号として伝達される。そして、フリップフロップ( $FF_{11} \sim FF_{1N}$ )の出力はバッファ( $BUF_{21} \sim BUF_{2N}$ )を経て発光走査線( $E_1 \sim E_N$ )に発光信号として伝達される。この時、開始信号のパルスが高電圧の信号であれば、発光走査線( $E_1 \sim E_N$ )の発光信号は高電圧であり、選択走査線( $S_1 \sim S_N$ )の選択信号は、NANDゲート( $NAND_{11} \sim NAND_{1N}$ )の反転動作によって低電圧になる。

10

#### 【0092】

次の第2走査駆動部40の動作を見ると、第1走査駆動部30と同様に開始信号のパルス( $VSP$ )がフリップフロップ( $FF_{21} \sim FF_{2N}$ )を経て順次にシフトされて出力される。フリップフロップ( $FF_{21} \sim FF_{2N}$ )の出力はNANDゲート( $NAND_{21} \sim NAND_{2N}$ )によって第1切断信号( $CLIP_1$ )とNAND演算され、幅が減つて反転した形態で出力される。このNANDゲート( $NAND_{21} \sim NAND_{2N}$ )の出力が高電圧であれば、第2伝達ゲート( $TRANS_2$ )によってバッファ( $BUF_{31} \sim BUF_{3N}$ )から高い電圧が出力される。そして、NANDゲート( $NAND_{21} \sim NAND_{2N}$ )の出力が低電圧であれば、第1伝達ゲート( $TRANS_1$ )によってバッファ( $BUF_{31} \sim BUF_{3N}$ )から低い電圧が出力される。

20

#### 【0093】

この時、図18に示したように、第2切断信号( $CLIP_2$ )の低電圧パルス幅を第1切断信号( $CLIP_1$ )の幅より広くすれば、ブースト走査線( $B_1 \sim B_N$ )に伝達されるブースト信号の低電圧期間が、選択走査線( $S_1 \sim S_N$ )に伝達される選択信号の低電圧期間を含むようにできる。また、発光走査線( $E_1 \sim E_N$ )に伝達される発光信号は第2切断信号( $CLIP_2$ )によって幅が狭くならないので、発光信号が高電圧である期間はブースト信号が低電圧である期間を含むようになる。

30

#### 【0094】

そして、第2走査駆動部40でバッファ( $BUF_{31} \sim BUF_{3N}$ )のインバータの個数を異なるようにすることもできる。以下、このような実施形態について図19を参照して詳細に説明する。図19は図8の画素回路のブースト信号線を駆動するための他の走査駆動部の概略的な図面である。

40

#### 【0095】

図19の第2走査駆動部40はバッファ( $BUF_{41} \sim BUF_{4N}$ )を除けば図17の第2走査駆動部40と同じ構造を有する。詳しく説明すれば、各バッファ( $BUF_{4j}$ )はNANDゲート( $NAND_{2j}$ )の出力を受信する3段のインバータ、NANDゲート( $NAND_{2j}$ )の出力を受信する2段のインバータ、そしてブースト信号のレベルを調整するための2個の伝達ゲート( $TRANS_3, TRANS_4$ )を含む。

40

#### 【0096】

第1伝達ゲート( $TRANS_3$ )は低い電圧を供給する信号線( $V_{low}$ )とブースト走査線( $B_j$ )の間に連結されており、3段のインバータを通過したNANDゲート( $NAND_{2j}$ )の出力が高電圧である場合に低い電圧をブースト走査線( $B_j$ )に出力する。そして、第2伝達ゲート( $TRANS_4$ )は高い電圧を供給する信号線( $V_{high}$ )

50

とブースト信号線（ $B_j$ ）の間に連結されており、2段のインバータを通過したNANDゲート（ $NAND_{2,j}$ ）の出力が低電圧である場合に高い電圧をブースト走査線（ $B_j$ ）に出力する。

#### 【0097】

つまり、図19では奇数段のインバータによって入力信号が反転したので伝達ゲート（ $TRANS_3$ ,  $TRANS_4$ ）の動作を図17の伝達ゲート（ $TRANS_1$ ,  $TRANS_2$ ）の動作と反対にした。バッファを除いた残りの構成は図17の第2走査駆動部40と同一であるので動作についての説明は省略する。

#### 【0098】

そして、図16～図19では図8の画素回路を基準にして選択信号、発光信号およびブースト信号が各々低電圧、高電圧および低電圧である場合について説明したが、画素回路のトランジスタ導電型が変更されて、これら信号のレベル（大小）関係が変更される場合にも第1走査駆動部30、第2走査駆動部40を適用することができる。ただし、この場合にはバッファのインバータ段数を調節したりまたはこれと類似して第1走査駆動部30、第2走査駆動部40を変更すればよい。このような第1走査駆動部30、第2走査駆動部40の詳細な構造および動作は当業者であれば容易に分かるので説明を省略する。

#### 【0099】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されることは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それについても当然に本発明の技術的範囲に属するものと了解される。

#### 【図面の簡単な説明】

##### 【0100】

【図1】有機電界発光素子の概念図である。

【図2】従来の電圧駆動方式の画素回路の回路図である。

【図3】従来の電流駆動方式の画素回路の回路図である。

【図4】本発明の実施形態に係る発光表示装置の一例として有機EL表示装置の概略的な平面図である。

【図5】本発明の第1実施形態に係る画素回路の等価回路図である。

【図6】本発明の第2実施形態に係る画素回路の回路図である。

【図7】図6の画素回路を説明するための駆動波形図である。

【図8】本発明の第3実施形態に係る画素回路の回路図である。

【図9】図8の画素回路を説明するための駆動波形図である。

【図10】図8の画素回路を駆動する本発明の第4実施形態に係る駆動波形図である。

【図11】図8の画素回路を駆動する本発明の第5実施形態に係る駆動波形図である。

【図12】本発明の第6実施形態に係る画素回路の回路図である。

【図13】本発明の第7実施形態に係る画素回路の回路図である。

【図14】図13の画素回路を駆動するための駆動波形図である。

【図15】本発明の実施形態3～実施形態7に係る発光表示装置の一例として有機EL表示装置の概略的な平面図である。

【図16】図8の画素回路の選択走査線と発光走査線を駆動するための走査駆動部の概略的な図面である。

【図17】図8の画素回路のブースト信号線を駆動するための走査駆動部の概略的な図面である。

【図18】図16および図17の走査駆動部の駆動タイミング図である。

【図19】図8の画素回路のブースト信号線を駆動するための他の走査駆動部の概略的な図面である。

#### 【符号の説明】

##### 【0101】

1 1 画素回路

2 0 データ駆動部

3 0 第1走査駆動部

4 0 第2走査駆動部

B<sub>n</sub> ブースト走査線B<sub>U</sub> F<sub>1,1</sub> ~ B<sub>U</sub> F<sub>1,N</sub> バッファ C<sub>1</sub>, C<sub>2</sub> キャパシタD<sub>1</sub> ~ D<sub>M</sub> データ線F<sub>F</sub> F<sub>1,1</sub> ~ F<sub>F</sub> F<sub>1,N</sub> フリップフロップI<sub>DAT</sub>A データ電流I<sub>OLED</sub> 発光素子の電流M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>, M<sub>4</sub> トランジスタN<sub>AND</sub> F<sub>1,1</sub> ~ N<sub>AND</sub> F<sub>1,N</sub> NANDゲート

OLED 有機EL素子

S<sub>1</sub> ~ S<sub>N</sub> 選択走査線E<sub>1</sub> ~ E<sub>N</sub> 発光走査線S<sub>W</sub> 1, S<sub>W</sub> 2, S<sub>W</sub> 3 スイッチング素子T<sub>RANS</sub> 1, T<sub>RANS</sub> 2, T<sub>RANS</sub> 3, T<sub>RANS</sub> 4 伝達ゲートV<sub>G</sub> ゲート電圧V<sub>GS</sub> ゲート-ソース電圧

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 2 G |

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 4 1 D |

| H 0 5 B | 33/14 | A       |

(72)発明者 柳 道亨

大韓民国釜山市南区ムンヒョン3洞97-1番地 15/5

F ターム(参考) 3K007 AB17 BA06 DB03 GA00

5C080 AA06 BB05 DD05 DD28 EE28 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发光显示装置及其显示面板和驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2005134874A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2005-05-26 |

| 申请号            | JP2004219579                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2004-07-28 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星工スディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 申東蓉<br>キム グムナム<br>柳道亨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 申 東蓉<br>キム グムナム<br>柳 道亨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | H01L51/50 G09G1/04 G09G3/10 G09G3/20 G09G3/30 G09G3/32 H05B33/08 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G09G3/325 G09G3/3266 G09G2300/0852 G09G2300/0861 G09G2310/0251 G09G2320/0252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.621.F G09G3/20.622.C G09G3/20.622.E G09G3/20.622.G<br>G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/3241 G09G3/3266 G09G3/3275 G09G3/3283<br>G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD05 5C080<br>/DD28 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01<br>3K107/CC35 3K107/CC42 3K107/EE04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/BA05 5C380<br>/BA19 5C380/BA20 5C380/BA39 5C380/CA12 5C380/CA13 5C380/CA49 5C380/CB01 5C380/CB17<br>5C380/CB26 5C380/CB27 5C380/CC02 5C380/CC03 5C380/CC12 5C380/CC26 5C380/CC27 5C380<br>/CC33 5C380/CC34 5C380/CC37 5C380/CC38 5C380/CC39 5C380/CC62 5C380/CC63 5C380/CC64<br>5C380/CD012 5C380/CD014 5C380/CD024 5C380/CF31 5C380/DA02 5C380/DA06 |         |            |

| 优先权            | 1020030076002 2003-10-29 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP5140232B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

**摘要(译)**

要解决的问题：为了补偿阈值电压的偏差和发光显示装置的像素电路中的晶体管的迁移率，以便可以对数据线快速充电。提供了用于调节有机EL装置的驱动电流的驱动晶体管，并且第一电容器连接在驱动晶体管的栅极和源极之间，并且第二电容器连接在栅极和升压扫描线之间。选择每个像素电路，发送用于亮度设置的数据电流，在预定时间内对数据线充电，然后将电流-电压转换后的电压存储在第一电容器中。接下来，当升压扫描线的电压电平改变时，由于第一电容器和第二电容器的分压，第一电容器的存储电压降低，并且从驱动晶体管到有机EL元件产生与降低的电压相对应的微小电流。有机EL元件发射具有期望亮度的光。由此，可以减少由于数据线的寄生电容引起的信号延迟。[选择图]图8