(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-213027

(P2004-213027A)

(43) 公開日 平成16年7月29日(2004.7.29)

(51) Int.Cl.<sup>7</sup>

**G09F 9/30**

**H01L 21/20**

**H01L 21/336**

**H01L 27/08**

**H01L 29/786**

F 1

G09F 9/30 338

G09F 9/30 365Z

H01L 21/20

H01L 27/08 331E

H05B 33/14 A

テーマコード(参考)

3K007

5C094

5FO48

5FO52

5F110

審査請求 未請求 請求項の数 22 O L (全 21 頁) 最終頁に続く

(21) 出願番号 特願2004-3453 (P2004-3453)

(22) 出願日 平成16年1月8日 (2004.1.8)

(31) 優先権主張番号 2003-000971

(32) 優先日 平成15年1月8日 (2003.1.8)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 2003-008153

(32) 優先日 平成15年2月10日 (2003.2.10)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 503447036

サムスン エレクトロニクス カンパニー

リミテッド

大韓民国キヨンギード、スウォンーシ、ヨ

ントン-ク、マエタンードン 416

(74) 代理人 100089705

弁理士 松本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

(74) 代理人 100096013

弁理士 富田 博行

最終頁に続く

(54) 【発明の名称】多結晶シリコン薄膜トランジスタ表示板及びその製造方法

## (57) 【要約】

【課題】 本発明が目的とする技術的課題は、均一な表示特性を有する有機発光表示装置用薄膜トランジスタアレイ基板を提供することにある。

【解決手段】 非晶質シリコン層を蒸着する工程と、マスクを通じた複数のレーザーショットで非晶質シリコン層を多結晶シリコン層に変換する工程と、多結晶シリコン層上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート線を形成する工程と、ゲート線上に第1層間絶縁膜を形成する工程と、第1層間絶縁膜上にデータ線を形成する工程と、前記データ線上に第2層間絶縁膜を形成する工程と、第2層間絶縁膜上に画素電極を形成する工程とを含む過程により薄膜トランジスタ表示板を製造する。レーザーショットで用いられるマスクは複数のレーザー透過領域と遮断領域を有し、透過領域と遮断領域は所定の規則により混在している。このようにすれば、シリコン層の多結晶化のためのレーザー照射の時互いに異なるレーザーショットで露光される部分が互いに混在するようにし、レーザーショット間の境界が線として認識されることを防止できる。

**【特許請求の範囲】****【請求項 1】**

複数の画素領域に区画される絶縁基板と、

前記絶縁基板上に形成されているゲート配線と、

前記ゲート配線と絶縁されて交差して画素領域を区画する第1データ配線と、

前記ゲート配線と絶縁されて交差している第2データ配線と、

前記画素領域内に形成されている画素電極と、

前記ゲート配線及び前記第1データ配線にゲート電極及びソース電極が各々連結されると共に多結晶シリコン層を含むスイッチング薄膜トランジスタと、

前記スイッチング薄膜トランジスタのドレーン電極、前記画素電極及び前記第2データ配線に、ゲート電極、ドレーン電極及びソース電極が各々連結されると共に多結晶シリコン層を含む駆動薄膜トランジスタとを含み、

前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能は区分領域別に差があり、前記区分領域は前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能別に区分すると2種類以上で分類され、異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板。

**【請求項 2】**

異なる種類の前記区分領域を混在させる前記所定の規則は、特定区分領域を中心にしてその上下左右には異種の区分領域が配置され、対角方向には同種の区分領域が配置される請求項1に記載の薄膜トランジスタ表示板。

**【請求項 3】**

前記各区分領域は一つの画素領域である請求項1に記載の薄膜トランジスタ表示板。

**【請求項 4】**

前記スイッチング薄膜トランジスタ及び駆動薄膜トランジスタの駆動性能差は、これらが含む多結晶シリコン層の結晶質の差である請求項1に記載の薄膜トランジスタ表示板。

**【請求項 5】**

複数の画素領域に区画される絶縁基板と、

前記絶縁基板上の前記複数の画素領域ごとに形成されている多結晶シリコン層と、

前記多結晶シリコン層上に形成されているゲート絶縁膜と、

前記ゲート絶縁膜上に形成されているゲート配線と、

前記ゲート配線上に形成されている第1層間絶縁膜と、

前記層間絶縁膜上に形成され、前記ゲート配線と交差して前記画素領域を区画するデータ配線と、

前記データ配線上に形成されている第2層間絶縁膜と、

前記第2層間絶縁膜上の前記複数の画素領域ごとに形成されている画素電極とを含み、

前記多結晶シリコン層の結晶質は区分領域別に差があり、前記区分領域は前記多結晶シリコン層の結晶質別に区分すると2種類以上で分類され、異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板。

**【請求項 6】**

前記画素電極上の所定領域に形成されている有機発光層と、

前記画素電極上に形成され、前記有機発光層の領域を限定している隔壁と、

前記有機発光層と前記隔壁上に形成されている共通電極と、をさらに含む請求項5に記載の薄膜トランジスタ表示板。

**【請求項 7】**

前記多結晶シリコン層は、スイッチングトランジスタ部及び駆動トランジスタ部と、前記駆動トランジスタ部と連結されている維持電極部とを含み、

前記ゲート配線は、前記スイッチングトランジスタ部、駆動トランジスタ部及び前記維持電極部と各々重複する、第1ゲート電極、第2ゲート電極及び維持電極を含み、

前記データ配線は、第1及び第2データ線、前記第1データ線及び前記スイッチングトランジスタ部のソース領域と連結されている第1ソース電極、前記スイッチングトランジ

10

20

30

40

50

スイッチ部のドレーン領域及び前記第2ゲート電極と連結されている第1ドレーン電極、前記第2データ線及び前記駆動トランジスタ部のソース領域と連結されている第2ソース電極を含み、

前記画素電極は前記駆動トランジスタ部のドレーン領域と連結されている請求項5に記載の薄膜トランジスタ表示板。

#### 【請求項8】

絶縁基板上に非晶質シリコン層を蒸着する工程と、

マスクを通じた複数のレーザーショットで前記非晶質シリコン層を多結晶シリコン層に変換する工程と、

前記多結晶シリコン層上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート線を形成する工程と、

前記ゲート線上に第1層間絶縁膜を形成する工程と、

前記第1層間絶縁膜上にデータ線を形成する工程と、

前記データ線上に第2層間絶縁膜を形成する工程と、

前記第2層間絶縁膜上に画素電極を形成する工程とを含み、

前記マスクは複数のレーザー透過領域と遮断領域とを有し、前記透過領域と遮断領域は所定の規則により混在している薄膜トランジスタ表示板の製造方法。

#### 【請求項9】

前記画素電極上に隔壁を形成する工程と、

前記隔壁により区画された前記画素電極上の所定領域に有機発光層を形成する工程と、

前記有機発光層上に共通電極を形成する工程と、をさらに含む請求項8に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項10】

前記マスクの前記透過領域と遮断領域とは、画素領域一つを基礎単位として面積と模様が区画される請求項8に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項11】

前記マスクの前記透過領域と遮断領域を混在させる前記所定の規則は、特定の透過領域を中心にしてその上下左右には遮断領域が配置され、対角方向には透過領域が配置される請求項8に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項12】

前記マスクは前記透過領域の配置模様によって2つ以上のブロックに区分され、

前記マスクを通じた複数のレーザーショットで前記非晶質シリコン層を多結晶シリコン層に変換する工程は、前記マスクを一つのブロックに該当する距離分ずつ平行移動させながらレーザーを照射する請求項8に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項13】

前記マスクの各ブロックごとに形成されている透過領域の全てを一つのブロック内に配置した場合に、一つのブロック全体が透過領域になる請求項12に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項14】

非晶質シリコン層を蒸着する工程と、

透過領域と遮断領域を有するマスクを通じてレーザービームを照射することで前記非晶質シリコン層を溶融する工程と、

前記溶融されたシリコン層が凝固して結晶化する工程とを含み、

前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部は階段状に形成されているシリコン結晶化方法。

#### 【請求項15】

前記階段状境界線が形成されたマスクの透過領域を階段状スリットパターンとすれば、前記階段状境界線は前記階段状スリットパターンの上側境界線と下側境界線のいずれか一侧にのみ形成されているマスクを用いる請求項14に記載のシリコン結晶化方法。

#### 【請求項16】

10

20

30

40

50

前記階段状スリットパターンが、当該スリットパターンの短軸方向に複数形成されている請求項15に記載のシリコン結晶化方法。

【請求項17】

前記スリットパターンは、前記階段状スリットパターンと、長方形スリットパターンに区分され2列に形成されており、前記階段状スリットパターンと前記長方形スリットパターンは各々スリットパターンの短軸方向に複数形成されている請求項15に記載のシリコン結晶化方法。

【請求項18】

前記階段状スリットパターンをその長軸方向に平行移動した場合に、当該階段状スリットパターンが前記長方形スリットパターンの間に位置するように、互いにずれた位置に前記階段状スリットパターンと前記長方形スリットパターンが形成されている請求項17に記載のシリコン結晶化方法。

【請求項19】

レーザービームを利用したシリコン結晶化方法に用いられ、透過領域と遮断領域を有するマスクで、前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部は階段状に形成されているマスク。

【請求項20】

複数のスイッチング薄膜トランジスタ、複数の駆動薄膜トランジスタ、有機EL膜からなる有機発光表示装置の製造方法において、

前記駆動薄膜トランジスタの非晶質シリコン層を蒸着する工程と、

透過領域と遮断領域を有するマスクを通じてレーザービームを照射することで前記非晶質シリコン層を溶融する工程と、

前記溶融されたシリコン層が凝固して結晶化する工程とを含み、

前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部は階段状に形成されているマスクを用いるシリコン結晶化方法を利用する有機発光表示装置の製造方法。

【請求項21】

複数の画素領域に区画される絶縁基板と、

前記基板上に形成されているゲート配線と、

前記ゲート配線と絶縁されて交差して画素領域を区画する第1データ配線と、

前記ゲート配線と絶縁されて交差している第2データ配線と、

前記画素領域内に形成されている画素電極と、

前記画素領域内に形成されている表示端子と、

前記画素電極と前記表示端子を接続する補助回路と、

前記ゲート配線及び前記第1データ配線にゲート電極及びソース電極が各々連結されると共に多結晶シリコン層を含むスイッチング薄膜トランジスタと、

前記スイッチング薄膜トランジスタのドレーン電極、前記表示端子及び前記第2データ配線に、ゲート電極、ドレーン電極及びソース電極が各々連結されると共に多結晶シリコン層を含む駆動薄膜トランジスタとを含み、

前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能は区分領域別に差があり、前記区分領域は前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能別に区分すると2種類以上で分類され、異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板。

【請求項22】

前記多結晶シリコン層は、スイッチングトランジスタ部及び駆動トランジスタ部と、前記駆動トランジスタ部と連結されている維持電極部とを含み、

前記ゲート配線は前記スイッチング、駆動トランジスタ部及び前記維持電極部と各々重複する、第1ゲート電極、第2ゲート電極及び維持電極とを含み、

前記データ配線は、第1及び第2データ線、前記第1データ線及び前記スイッチングトランジスタ部のソース領域と連結されている第1ソース電極と、前記スイッチングトランジスタ部のドレーン領域及び前記第2ゲート電極と連結されている第1ドレーン電極と、

10

20

30

40

50

前記第2データ線及び前記駆動トランジスタ部のソース領域と連結されている第2ソース電極とを含み、

前記画素電極は補助回路を介して前記駆動トランジスタ部のドレーン領域と連結されている請求項5に記載の薄膜トランジスタ表示板。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、多結晶シリコンパターンの形成方法及びこれを用いて製造された薄膜トランジスタ表示板に関し、さらに詳しくは有機発光表示装置の一基板として使用する薄膜トランジスタ表示板に関する。 10

#### 【背景技術】

#### 【0002】

一般に、有機発光表示装置は、蛍光性有機物質を電気的に励起発光させて画像を表示する装置であって、正孔注入電極（アノード）と電子注入電極（カソード）とこれらの間に形成されている有機発光層とを含む。

#### 【0003】

このような有機発光表示装置は、有機発光層に電荷を注入した場合に、注入された電子と正孔が対となった後消滅しながら発光する自己発光型表示装置である。この時、有機発光表示装置は有機発光層の発光効率を向上させるために電子輸送層（ETL：Electron Transport Layer）及び正孔輸送層（HTL：Hole Transport Layer）などを含み、電子注入層（EIL：Electron Injection Layer）と正孔注入層（HIL：Hole Injection Layer）などをさらに含んでもよい。 20

#### 【0004】

マトリックス状に配列されている有機発光セルを駆動する方法として、受動的な単純マトリックス方式と薄膜トランジスタを利用した能動マトリックス方式がある。単純マトリックス方式がアノードラインとカソードラインを互いに交差するように配置し、特定画素に対応するラインを時分割的に選択駆動する反面、能動マトリックス方式は各有機発光セルのアノード電極に駆動薄膜トランジスタとコンデンサーを接続したものであり、信号伝達は時分割であっても、各画素の信号をコンデンサーに蓄積して、どの画素も約1画面走査期間だけ、容量（キャパシタ）により電圧を維持し、発光させるような駆動方式である。 30

#### 【0005】

この時、有機発光セルに発光のための電流を供給する駆動薄膜トランジスタからの電流量は、スイッチングトランジスタを通じて印加されるデータ電圧により制御され、スイッチングトランジスタのゲートとソースは各々ゲート信号線（またはスキャンライン）とデータ信号線に連結され、両信号線は互いに交差して配置されている。従って、ゲート信号線を通じて伝えられた信号によりスイッチングトランジスタがオンになればデータラインを通じて駆動電圧が駆動薄膜トランジスタのゲートに印加され、駆動薄膜トランジスタを通じて有機発光セルに電流が流れ発光が行われる。このような有機発光セルはR、G、B画素別に備えられてカラー画面を実現する。 40

#### 【0006】

このような有機発光表示装置において、画素領域内の駆動薄膜トランジスタの素子特性の均一性が第1に求められる条件である。これは、薄膜トランジスタの素子特性が位置（それぞれのトランジスタ）によって異なる場合、同じ画像信号に対して位置により互いに異なる輝度を示すようになり、全体画面の輝度、色相の不均一を生じるためである。

#### 【0007】

このような駆動薄膜トランジスタの素子特性の均一性は結晶化工程によって強く影響されるが、既存のELA(Excimer Laser Anneal)方式の場合、ラインビームを使用するため 50

に何回ものレーザービーム照射工程のうちエネルギー不均一による不良照射が発生しやすく、そのライン全体の駆動薄膜トランジスタが他の領域と異なる特性を示すことになり、その結果、縦筋の不均一領域が発生してしまう場合がある。これを解決するために、均一な駆動薄膜トランジスタ特性を確保する結晶化技術の開発に力を注いだが、その代表的なものがSLS(Sequential Lateral Solidification)方式(連続的側面固状化又は逐次的横方向結晶化)である。しかし、最も均一性が高いレーザービームでもその偏差が±10%に達する現状を考慮すれば、全ての駆動薄膜トランジスタを均一に作るということは極めて難しいことである。

【発明の開示】

【発明が解決しようとする課題】

10

【0008】

本発明が目的とする技術的課題は、均一な表示特性を有する有機発光表示装置用薄膜トランジスタアレイ基板を提供することにある。

【課題を解決するための手段】

【0009】

このような課題を解決するために本発明では、多結晶化のためのレーザー熱処理工程でレーザビームの透過領域と遮断領域が混在しているマスクを介してレーザー照射する。

【0010】

さらに詳しくは、複数の画素領域に区画される絶縁基板と、前記基板上に形成されているゲート配線と、前記ゲート配線と絶縁され交差して画素領域を区画する第1データ配線と、前記ゲート配線と絶縁されて交差している第2データ配線と、前記画素領域内に形成されている画素電極と、前記ゲート配線及び前記第1データ配線にゲート電極及びソース電極が各々連結されると共に多結晶シリコン層を含むスイッチング薄膜トランジスタと、前記スイッチング薄膜トランジスタのドレーン電極、前記画素電極及び前記第2データ配線にゲート電極、ドレーン電極及びソース電極が各々連結されると共に多結晶シリコン層を含む駆動薄膜トランジスタとを含み、前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能は前記画素領域一つを基礎単位として分けられる区分領域別で差があり、前記区分領域は前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能別に分けると2種類以上に分類される。異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板を用いる。

20

【0011】

この時、異なる種類の前記区分領域が混在する前記所定の規則は、特定区分領域を中心にしてその上下左右には異種の区分領域が配置され、対角方向には同種の区分領域が配置されたり、前記区分領域は一つの画素領域であり得る。また、前記スイッチング及び駆動薄膜トランジスタの駆動性能の差はこれらが含む多結晶シリコン層の結晶質の差からくるものである。

【0012】

さらに、複数の画素領域に区画される絶縁基板、前記基板上の前記複数の画素領域ごとに形成されている多結晶シリコン層、前記多結晶シリコン層上に形成されているゲート絶縁膜、前記ゲート絶縁膜上に形成されているゲート配線、前記ゲート配線上に形成されている第1層間絶縁膜、前記層間絶縁膜上に形成され、前記ゲート配線と交差して前記画素領域を区画するデータ配線、前記データ配線上に形成されている第2層間絶縁膜、前記第2層間絶縁膜上の前記複数の画素領域ごとに形成されている画素電極を含み、前記多結晶シリコン層の結晶質は前記画素領域一つを基礎単位として分けられる区分領域別で差があり、前記区分領域は前記多結晶シリコン層の結晶質別に分けると2種類以上に分類され、異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板を用いる。

40

【0013】

この時、前記画素電極上の所定領域に形成されている有機発光層、前記画素電極上に形成され、前記有機発光層の領域を限定している隔壁、前記有機発光層と前記隔壁上に形成

50

されている共通電極をさらに含むことができ、前記多結晶シリコン層はスイッチング及び駆動トランジスタ部と前記駆動トランジスタ部と連結されている維持電極部を含み、前記ゲート配線は前記スイッチング及び駆動トランジスタ部及び前記維持電極部と各々重複する第1ゲート電極、第2ゲート電極及び維持電極を含み、前記データ配線は第1及び第2データ線、前記第1データ線及び前記スイッチングトランジスタ部のソース領域と連結されている第1ソース電極、前記スイッチングトランジスタ部のドレーン領域及び前記第2ゲート電極と連結されている第1ドレーン電極、前記第2データ線及び前記駆動トランジスタ部のソース領域と連結されている第2ソース電極を含み、前記画素電極は前記駆動トランジスタ部のドレーン領域と連結されていることが好ましい。

【0014】

10

このような薄膜トランジスタ表示板は、絶縁基板上に非晶質シリコン層を蒸着する工程と、マスクを通じた複数のレーザーショットで前記非晶質シリコン層を多結晶シリコン層に変換する工程と、前記多結晶シリコン層上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート線を形成する工程と、前記ゲート線上に第1層間絶縁膜を形成する工程と、前記第1層間絶縁膜上にデータ線を形成する工程と、前記データ線上に第2層間絶縁膜を形成する工程と、前記第2層間絶縁膜上に画素電極を形成する工程とを含む。前記マスクは複数のレーザー透過領域と遮断領域を有し、前記透過領域と遮断領域が所定の規則により混在する方法で製造される。

【0015】

20

ここで、前記画素電極上に隔壁を形成する工程と、前記隔壁により区画された前記画素電極上の所定領域に有機発光層を形成する工程と、前記有機発光層上に共通電極を形成する工程とをさらに含むことができる。前記マスクの前記透過領域と遮断領域は、画素領域一つを基礎単位として面積と模様が区画されるのが好ましい。

【0016】

また、前記マスクの前記透過領域と遮断領域が混在する前記所定の規則は、特定透過領域を中心にしてその上下左右には遮断領域が配置され、対角方向には透過領域が配置されることであっても良い。

【0017】

30

また、前記マスクは前記透過領域の配置模様によって2つ以上のブロックに区分され、前記マスクによる複数のレーザーショットで前記非晶質シリコン層を多結晶シリコン層に変換する工程とは、前記マスクを一つのブロックに該当する距離分ずつ平行移動させながらレーザーを照射する過程によることもできる。前記マスクの各ブロックごとに形成されている透過領域の全てを一つのブロック内に配置すれば一つのブロック全体が透過領域となるのが好ましい。

【0018】

本発明のシリコン結晶化方法は、非晶質シリコン層を蒸着する工程と、透過領域と遮断領域を有するマスクを通じてレーザービームを照射して前記非晶質シリコン層を溶融する工程と、前記溶融されたシリコン層が凝固して結晶化する工程とを含み、前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部は階段状に形成されることが好ましい。

【0019】

40

そして、前記マスクの透過領域をスリットパターン、前記階段状境界線が形成されたマスクの透過領域を階段状スリットパターンとすれば、前記階段状境界線は前記階段状スリットパターンの上側境界線と下側境界線のいずれか一側にのみ形成されているマスクを用いることが好ましい。

【0020】

前記階段状スリットパターンはスリットパターンの短軸方向で複数形成されているマスクを用いるのが好ましい。前記スリットパターンは、前記階段状スリットパターンと長方形スリットパターンとに区分され二列に形成されており、前記階段状スリットパターンと前記長方形スリットパターンは、各々スリットパターンの短軸方向に複数形成されているマスクを用いるのが好ましい。

50

**【 0 0 2 1 】**

前記階段状スリットパターンをその長軸方向に平行移動すれば前記長方形スリットパターンの間に位置するように、互いにずれる位置に前記階段状スリットパターンと前記長方形スリットパターンが形成されているマスクを用いるのが好ましい。

**【 0 0 2 2 】**

前記目的を達成するために本発明のマスクは、レーザービームによるシリコン結晶化方法を利用して透過領域と遮断領域を有するマスクであって、前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部が階段状であることが好ましい。

**【 0 0 2 3 】**

前記目的を達成するために本発明の有機発光表示装置の製造方法は、複数のスイッチング薄膜トランジスタ、複数の駆動薄膜トランジスタ、有機ELからなる有機発光表示装置の製造方法において、前記駆動薄膜トランジスタの非晶質シリコン層を蒸着する工程と、透過領域と遮断領域を有するマスクを通じてレーザービームを照射して前記非晶質シリコン層を溶融する工程と、前記溶融されたシリコン層が凝固して結晶化する工程とを含み、前記マスクの遮断領域と前記透過領域の境界線の少なくとも一部が階段状に形成されているマスクを用いるシリコン結晶化方法を採用することが好ましい。この他に、本発明の実施例には、複数の画素領域に区画される絶縁基板と、前記基板上に形成されているゲート配線と、前記ゲート配線と絶縁され交差して画素領域を区画する第1データ配線と、前記ゲート配線と絶縁されて交差している第2データ配線と、前記画素領域内に形成されている画素電極と、前記画素領域内に形成されている表示端子と、前記画素電極と前記表示端子を接続する補助回路と、前記ゲート配線及び前記第1データ配線にゲート電極及びソース電極が各々連結されると共に多結晶シリコン層を含むスイッチング薄膜トランジスタと、前記スイッチング薄膜トランジスタのドレーン電極、前記表示端子及び前記第2データ配線にゲート電極、ドレーン電極及びソース電極が各々連結されると共に多結晶シリコン層を含む駆動薄膜トランジスタとを含み、前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能は前記画素領域一つを基礎単位として分けられる区分領域別で差があり、前記区分領域は前記スイッチングトランジスタ及び駆動薄膜トランジスタの駆動性能別に分けると2種類以上に分類される。異なる種類の前記区分領域が所定の規則により混在している薄膜トランジスタ表示板が含まれる。

**【 発明の効果 】****【 0 0 2 4 】**

シリコン層の多結晶化のためにレーザービームを照射する時に、互いに異なるレーザーショットで露光される部分が互いに混在するようにしてレーザーショット間の境界が線として認識されることを防止することができる。

**【 発明を実施するための最良の形態 】****【 0 0 2 5 】**

添付した図面を参照して本発明の実施例に対して本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様な形態で実現することができ、ここで説明する実施例に限定されない。

**【 0 0 2 6 】**

図面は、各種の層及び領域を明確に表現するために厚さを拡大して示している。明細書全体を通じて類似した部分については同一図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時は、中間に他の部分がないことを意味する。

**【 0 0 2 7 】**

以下、図面を参照して本発明の実施例による薄膜トランジスタアレイ基板について説明する。

**【 0 0 2 8 】**

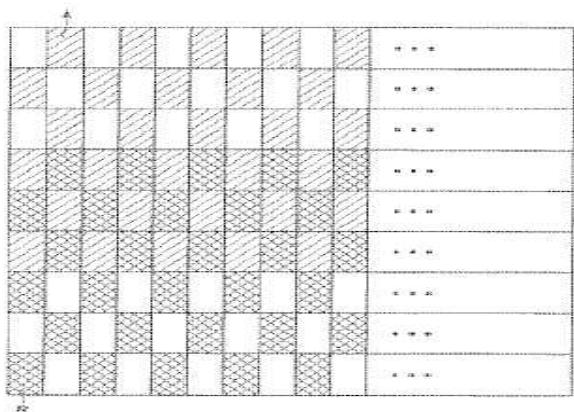

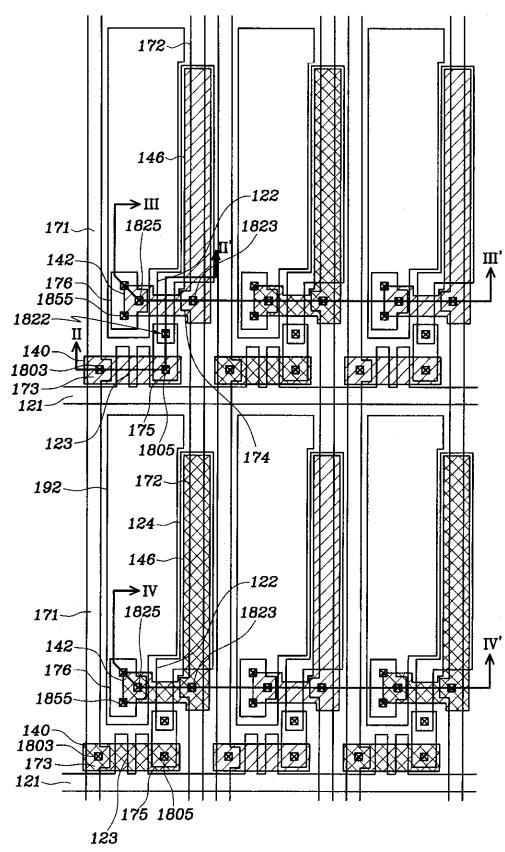

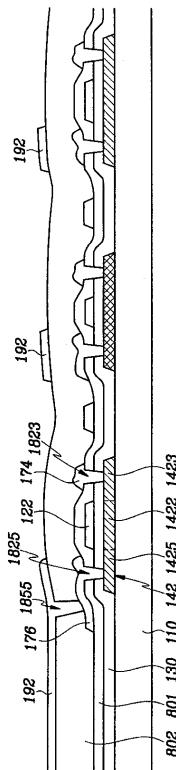

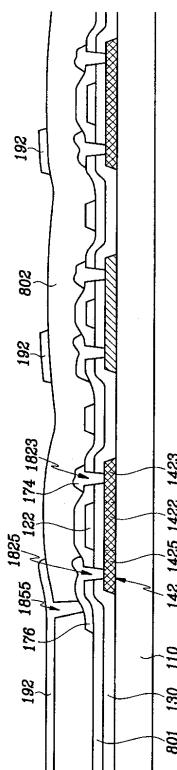

図1は本発明の第1の実施例による有機発光表示装置用薄膜トランジスタアレイ基板の

10

20

30

40

50

配置図であり、図2は図1のI I - I I'線に沿って断面図であり、図3は図1のI I I - I I I'線に沿って断面図であり、図4は図1のI V - I V'線に沿って断面図である。

### 【0029】

絶縁基板110上に多結晶シリコンからなる半導体層が形成されている。半導体層はスイッチング薄膜トランジスタの半導体部140、駆動薄膜トランジスタの半導体部142及び維持電極部146を含む。半導体部140、142は両側に位置しており、n型またはp型不純物としてドーピングされているソース領域1403、1423及びドレーン領域1405、1425と、これらの間に各々配置されているスイッチングチャンネル部1402、1404及び駆動チャンネル部1422を有する。

10

### 【0030】

本発明の第1実施例で、駆動薄膜トランジスタのソース及びドレーン領域1423、1425はp型不純物としてドーピングされ、スイッチング薄膜トランジスタのソース及びドレーン領域1403、1405はn型不純物としてドーピングされている。しかし、駆動方式によっては駆動薄膜トランジスタのソース及びドレーン領域1423、1425がn型不純物としてドーピングされ、スイッチング薄膜トランジスタのソース及びドレーン領域1403、1405がp型不純物としてドーピングされてもよい。

20

### 【0031】

ここで、半導体層（半導体部及び維持電極部）140、142、146は画素領域別に結晶質が多少異なることがある。これは後述するように、多結晶化のためのレーザー熱処理過程において、半導体層全体（多数の半導体層）が1度のレーザーショットで照射することはできず、何回ものショットに分けて照射されるためである。即ち、レーザーショット間のエネルギー不均一が半導体層の結晶質の不均一をもたらすことになる。

20

### 【0032】

同一レーザーショットで照射された領域は実質的に同一で均質な結晶質を有し、異なるレーザーショットで照射された領域間では互いに異なる結晶質を有することが多い。しかし、本発明の第1実施例による薄膜トランジスタ表示板では、対角方向に位置した画素領域間には半導体層140、142、146が実質的に同一な結晶質を有し、上下左右に位置する画素領域間には半導体層140、142、146が互いに異なる結晶質を有する。ここで、上記した「対角方向」とは、ある特定の画素（区分領域）を中心とした場合の、斜め方向を言う。

30

### 【0033】

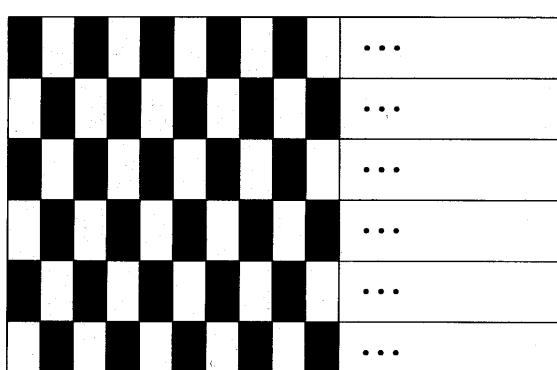

図1で、同一結晶質を有する半導体層に対しては同一斜線部で表示する。

### 【0034】

半導体層140、142、146の下部には酸化シリコンまたは窒化シリコンからなる遮断層が形成されている。半導体層140、142、146上には酸化シリコンまたは窒化シリコンからなるゲート絶縁膜130が形成されている。

40

### 【0035】

ゲート絶縁膜130上に、銀や銀合金またはアルミニウムやアルミニウム合金などのような低抵抗な材料で構成された単一膜またはこれを含む多層膜からなるゲート配線が形成されている。ゲート配線は横方向に延びているゲート線121及びゲート線121に連結され、スイッチングチャンネル部1402、1404と重複するスイッチング電極部1231、1232を有する第1ゲート電極123を含む。また、ゲート配線はゲート線121から分離され駆動チャンネル部1422と重複する第2ゲート電極122と縦方向に延びて維持電極部146と重複する維持電極124を含む。ゲート配線121、122、123、124はゲート線121の端に連結され、外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッドをさらに含むことができる。ここで、維持電極124は維持電極部146または以後形成される第2データ線172と重複して維持蓄電器を構成する。ゲート配線121、122、123、124が多層膜である場合は、他の物質と接触特性の良いパッド用物質を含むことができる。

50

## 【0036】

ゲート配線 121、122、123、124 上には、窒化シリコンまたは酸化シリコンまたは有機絶縁物質からなる第1層間絶縁膜 801 が形成されている。第1層間絶縁膜 801 上には、銀または銀合金またはアルミニウムやアルミニウム合金などのような低抵抗から構成された単一膜またはこれを含む多層膜からなるデータ配線及び電源供給配線が形成されている。

## 【0037】

データ配線は、縦方向に形成されゲート線 121 と交差して画素領域を区画・定義するデータ線 171、データ線 171 に連結されスイッチング薄膜トランジスタの半導体部 140 上に位置する第1ソース電極 173 及び第1ソース電極 173 と分離され第1ゲート電極 123 に対して第1ソース電極 173 の反対側であって、スイッチング薄膜トランジスタの半導体部 140 上に位置する第1ドレーン電極 175 を含む。10

## 【0038】

電源供給配線は、縦方向に延びて維持電極 124 と重なっている電源供給線 172、電源供給線 172 に連結され駆動薄膜トランジスタの半導体部 142 の上部まで延びている第2ソース電極 174 及び第2ソース電極 174 と分離され第2ゲート電極 122 に対して第2ソース電極 174 の反対側であって、駆動薄膜トランジスタの半導体部 142 上に位置する第2ドレーン電極 176 を含む。図示していないが、データ線 171 と電源供給線 172 は外部回路と連結するために幅が拡張された部分を各々含むことができる。

## 【0039】

第1ソース及び第1ドレーン電極 173、175 は、第1層間絶縁膜 801 及びゲート絶縁膜 130 の第1及び第2接触孔 1803、1805 を通じてスイッチング薄膜トランジスタの半導体部 140 のソース及びドレーン領域 1403、1405 と各々連結されている。また、第1ドレーン電極 175 は、第1層間絶縁膜 801 の第5接触孔 1822 を通じて第2ゲート電極 122 と連結されている。20

## 【0040】

第2ソース及び第2ドレーン電極 174、176 は、第1層間絶縁膜 801 及びゲート絶縁膜 130 の第3及び第4接触孔 1823、1825 を通じて駆動薄膜トランジスタの半導体部 142 のソース及びドレーン領域 1423、1425 と各々連結されている。

## 【0041】

データ配線 171、173、175 及び電源供給配線 172、174、176 上には第2層間絶縁膜 802 が形成され、第2層間絶縁膜 802 上にはITO (Indium Tin Oxide) またはIZO (Indium Zinc Oxide) などの透明導電物質からなる画素電極 192 が形成されている。画素電極 192 は第2層間絶縁膜 802 の第5接触孔 1855 を通じて第2ドレーン電極 176 と連結されている。この場合に、第2ドレインの半導体層 1425 を第4接触孔 1825 から細長く延長すると共に、第2ドレーン電極 176 も第1層間絶縁膜 801 の上で半導体層 1425 の延長部と平行に延長させる。第2ドレーン電極 176 と半導体層 1425 の延長端部では絶縁層 801、802 に追加の接触孔（第6接触孔、第7接触孔とする）を用意し、画素電極 192 は第7接触孔を通して第2ドレーン電極 176 と半導体層 1425 の延長端部に接触させる。説明の便宜上、第5接触孔 1855 を表示端子と呼び替えて、この表示端子と画素電極の接触を切断する。このようにすると、表示端子と画素電極の間に、新しく補助回路として、高抵抗の半導体と低抵抗の金属導体が並列に接続される。この補助回路は、各画素の輝度偏差を補正するために用いることが可能である。例えば、通常は製作された状態で使用されるが、特定の画素の輝度が過大である時、その画素の第5接触孔を通して強いレーザー光を照射し、低抵抗の金属導体を切断するならば、その画素の輝度を低下させることができある。また、延長した半導体パターンがレーザー光で切断可能であれば、画素を非発光にすることも可能であり、このような各種の導体切断構造は、当業者ならば、誰でも容易に考案できる。3040

## 【0042】

本発明の第1実施例による有機発光表示装置用薄膜トランジスタ表示板は、図示してい50

ないが、画素電極 192 上に形成され有機物質からなる画素領域隔壁と隔壁により区画されている各画素領域の画素電極 192 上に形成されている赤色、緑色、青色の有機発光層及び有機発光層と隔壁上に形成されている共通電極を有する。

#### 【0043】

本発明の第1実施例による薄膜トランジスタ表示板では、前述のようにそれぞれの画素領域に配置されている半導体層 140、142、146 の結晶質が対角方向で同一であり、上下左右では異なるようにして、駆動性能が異なる薄膜トランジスタが点々と混在して分布するようとする。このようにすれば、性能が異なる薄膜トランジスタが直線を境界として分れて分布する時に現れる縞模様不良を防止することができる。これは、分割されたレーザー照射領域の間に照射されるレーザーエネルギーの偏差により半導体層の結晶質に差異が発生しても、分割照射領域を混合して配置することで、薄膜トランジスタの性能が異なる二つの領域間の境界を認識できなくなるものである。10

#### 【0044】

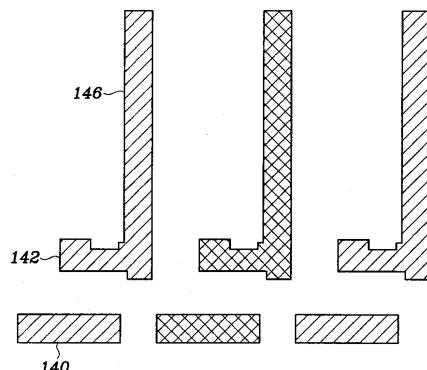

以下、このような有機発光表示装置用薄膜トランジスタ表示板を製造する方法について図5乃至図7、図1乃至図4を参照して説明する。

#### 【0045】

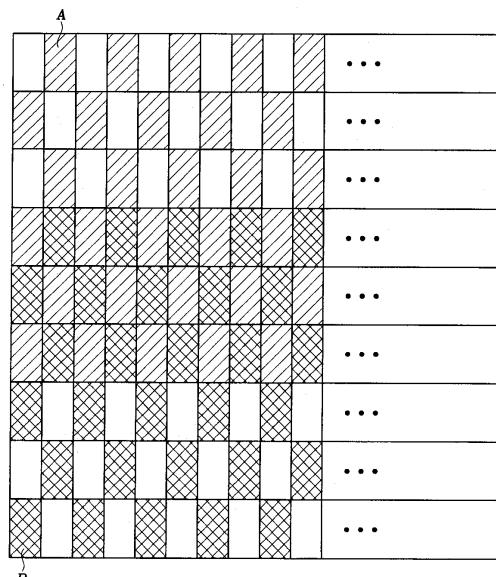

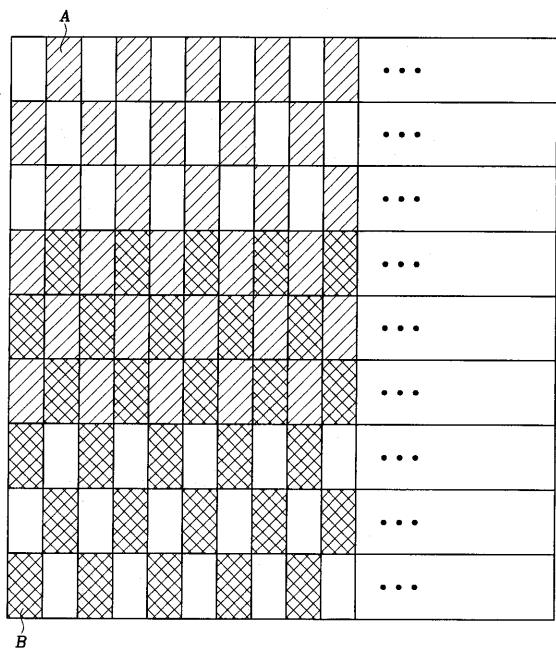

図5は本発明の第1実施例による薄膜トランジスタ表示板を製造する過程の多結晶シリコンパターンを形成する工程とを示す配置図であり、図6は図5の多結晶シリコンパターンを形成する時使用するレーザー照射マスクの遮光パターンの配置図であり、図7は図6のレーザー照射マスクを用いて非晶質シリコン層にレーザーを照射する方法を示す。20

#### 【0046】

まず、絶縁基板 110 上に酸化シリコンなどを蒸着して遮断層（図示しない）を形成し、遮断層上に非晶質シリコン層を蒸着する。非晶質シリコン層の蒸着は LPCVD、PECVD またはスパッタリングで実施することができる。

#### 【0047】

次に、非晶質シリコン層をレーザー熱処理して多結晶シリコンに変換する。この時、非晶質シリコン層へのレーザー照射は図6に示すようなマスクで実施する。

#### 【0048】

図6で、白色部分はレーザーが透過する部分であり、黒色部分はレーザーが遮断される部分である。レーザーが透過する部分の一つを単位透過領域、レーザーが遮断される部分の一つを単位遮断領域とする時、単位透過領域と単位遮断領域は画素一つの領域と同一な模様と大きさを有する。しかし、単位透過領域と単位遮断領域を幾つかの画素を合せた領域と模様及び大きさを同じにしたり、または幾つかの単位透過領域を合わせて一つの画素領域となるように形成することもできる。30

#### 【0049】

このようなマスクでレーザーを照射すれば、レーザーの光が通過する部分に位置した非晶質シリコン層は溶融され、光が遮断される部分に位置した非晶質シリコン層はそのまま残るようになる。この時、レーザーの照射は1回の照射で非晶質シリコン層を完全に溶かす程の強いエネルギーを有するレーザーで一気に実施することもでき、或いはそれより弱いエネルギーのレーザーを数回繰り返し照射して非晶質シリコン層を溶かすこともできる。40

#### 【0050】

第1次レーザー照射が終ればマスクを移動して配置し、第2次レーザー照射を実施する。この時、マスクは上下、左右または対角方向等いかなる方向にも移動できるが、第2次レーザー照射時にマスクが覆う領域が第1次レーザー照射時にマスクが覆う領域と一部重畠するように配置する。ここで、マスクの配置は図7に示すように、第1次レーザー照射でレーザーが遮断されて非晶質シリコン層がそのまま残っている部分の一部が第2次レーザー照射で露光できるようにマスクの移動距離を調節する。

#### 【0051】

図7では、第1次レーザー照射時に露光される領域をA、第2次レーザー照射時に露光50

される領域をBと表示する。

【0052】

このような方式で引き続きマスクを移動させながらレーザー照射を実施すれば、非晶質シリコン層全体がレーザー照射を受けて溶融された後凝固しながら結晶を形成し、多結晶シリコン層に変化する。

【0053】

前記では、レーザー照射を第1次、第2次に分けて説明したが、ここでの第1次、第2次は順番の意味ではなく、単に互いに別のレーザーショットであることを意味する。つまり、第2次レーザー照射は第1次レーザー照射に直ちにつながるものではなく、後に第1次とは別個で実施されるレーザーショットによるレーザー照射を意味する。

10

【0054】

次に、多結晶シリコン層を写真エッチングし、スイッチング及び駆動薄膜トランジスタ部半導体層140、142と維持電極部半導体層146を形成する。このようにすれば、図5に示すように、上下左右に位置した画素領域間には半導体層140、142、146の結晶質が互いに異なり、対角方向に位置した画素領域間には半導体層140、142、146の結晶質が実質的に同一な半導体層140、142、146の配置を得ることができる。

【0055】

次に、半導体層140、142、146上にゲート絶縁膜130を蒸着する。次いで、ゲート用金属層を蒸着して感光膜を塗布し、露光及び現像して第1感光膜パターンを形成する。第1感光膜パターンをマスクとしてゲート金属層をエッチングして第2ゲート電極122と維持電極124を形成し、露出されている駆動トランジスタ部多結晶シリコン層142にp型不純物イオンを注入して駆動トランジスタのソース及びドレーン領域1423、1425を形成する。この時、スイッチングトランジスタ部半導体層140は第1感光膜パターン及びゲート金属層に覆われて保護される。

20

【0056】

次に、第1感光膜パターンを除去し、感光膜を新たに塗布し露光及び現像して第2感光膜パターンを形成する。第2感光膜パターンをマスクとしてゲート金属層をエッチングして第1ゲート電極123及びゲート線121を形成し、露出されているスイッチングトランジスタ部半導体層140にn型不純物イオンを注入してスイッチングトランジスタのソース及びドレーン領域1403、1405を形成する。この時、駆動トランジスタ部半導体層142は第2感光膜パターンに覆われて保護される。

30

【0057】

次に、ゲート配線121、122、123及び維持電極133上に第1層間絶縁膜801を積層し、写真エッチングしてスイッチング及び駆動トランジスタのソース及びドレーン領域1403、1405、1423、1425を各々露出させる接触孔1803、1805、1823、1825と第2ゲート電極122の一端部を露出させる接触孔1822を形成する。次に、データ金属層を積層し写真エッチングしてデータ配線171、173、175と電源供給配線172、174、176を形成する。次に、第2層間絶縁膜802を積層し写真エッチングして第2ドレーン電極176を露出する接触孔1855を形成する。次に、第2層間絶縁膜802上にITOまたはIZOなどの透明な導電物質やアルミニウム、銀等の反射特性が良い導電物質を蒸着し写真エッチングして画素電極192を形成する。

40

【0058】

次に、図示していないが、画素電極192上に黒色顔料を含む有機膜を塗布し、露光後現像して隔壁を形成し、各画素領域に有機発光層を形成する。この時、有機発光層は多層構造であることが一般的である。有機発光層はマスキング後、蒸着、インクジェットプリントティングなどの方法で形成する。次に、有機発光層上に伝導性有機物質を塗布してバッファー層を形成し、バッファー層上にITOまたはIZOなどの透明導電物質やアルミニウム、銀等の金属を蒸着して共通電極を形成する。

50

## 【0059】

ここで、画素電極192を透明導電物質で形成する場合には、共通電極は反射性に優れた金属で形成し、画素電極192を反射性に優れた金属で形成する場合には、共通電極は透明な導電物質で形成する。また、共通電極を透明な導電物質で形成する場合には、共通電極形成の前後にアルミニウムなどの低抵抗物質で補助電極を形成することができる。

## 【0060】

以上の第1実施例では第1次、第2次レーザー照射のみでシリコン層を全てアニーリングしているが、さらに多いレーザー照射でシリコン層をアニーリングし、多結晶シリコン層の結晶質が異なる領域をさらに複雑に配置する事も出来る。

## 【0061】

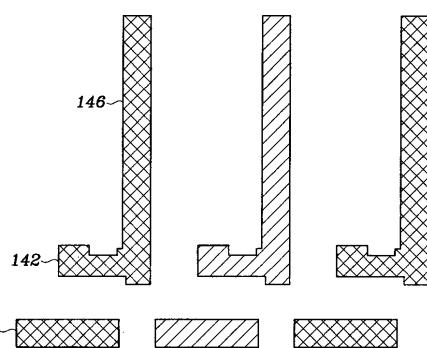

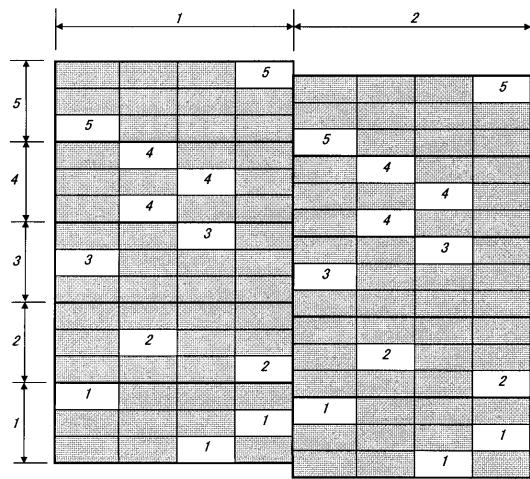

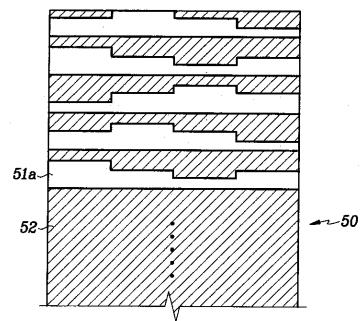

図8は本発明の第2実施例によるレーザー照射マスクの遮光パターンの配置図である。図8のレーザー照射マスクは、第5次までのレーザー照射を経てからシリコン層の全領域がアニーリングできるようにデザインされている。

## 【0062】

図8に示すように、第2の実施例によるレーザー照射マスクは横方向に2個のブロックに区分され、縦方向に5個のブロックに区分される。図8で、各ブロックは番号で表示されている。横方向に区分される2個のブロックはブロック間上下に少しづれているだけで透過領域の配置は同一である。縦方向に区分される5個のブロックは透過領域の位置がブロック別にそれぞれ異なり、これら5個のブロックの透過領域を一つのブロック内に配置するとすればブロック全体が透過領域になる。

## 【0063】

この時、5個のブロックの透過領域を一つのブロック内に配置すればブロック全体が透過領域になるという原則を満足する以上、各ブロック内の透過領域配置は多様に変形できる。

## 【0064】

図9は図8のレーザー照射マスクを用いて非晶質シリコン層にレーザーを照射する方法を示す図面である。

## 【0065】

まず、図8に示すマスクの縦方向の第1ブロックをシリコン層上の所定領域に配置し、第1次レーザーショットを通じて透過領域のシリコン層を熱処理する。次に、縦方向のブロック一つに該当する距離分マスクを下方に平行移動して配置し、第2次レーザーショットを通じて透過領域のシリコン層を熱処理する。次いで、縦方向のブロック一つに該当する距離分マスクを下方に平行移動して配置し、レーザーを照射する過程をさらに3回繰り返せば、最初に第1ブロックが置かれていた領域は全てレーザーの照射を受けて熱処理される。

## 【0066】

以上のように、本発明の第2実施例によるレーザー熱処理方法では、各ブロックが5次のレーザーショットを通じて熱処理されることにより結晶質が異なる多結晶シリコン領域が第1の実施例に比してさらに複雑に混在することになる。

## 【0067】

各ブロックを全て熱処理するために何回のレーザーショットを実施するかは、必要によって無制限に増やすことができる。つまり、2回（第1の実施例）以上であれば3回、4回、5回などいずれも可能である。例えば、10回のレーザーショットを実施する場合は、10個のブロックで分割され10個のブロックの透過領域を一つのブロックに配置し、ブロック全体が透過領域となるように透過領域を配置したマスクを用いて、ブロック一つに該当する距離分ずつマスクを移動配置しながらレーザーを照射すれば良い。

## 【0068】

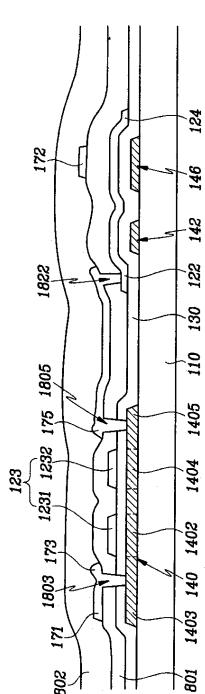

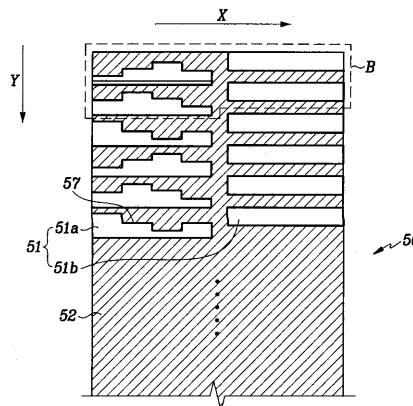

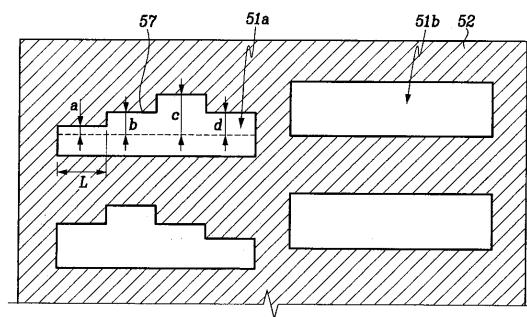

以下、本発明による好ましい第3の実施例を詳細に説明する。図10aに結晶化のためのマスクを示し、図10bには図10aのB領域を拡大して示した。

## 【0069】

10

20

30

40

50

このようなマスク 5 0 にはレーザービームが通過する透過領域であるスリットパターン 5 1 が一つ以上形成されている。この時、マスクの遮断領域 5 2 と透過領域 5 1 の境界線 5 7 が階段状となっている。

#### 【0070】

このようなマスク 5 0 を通じてレーザービームを照射してシリコン層を結晶化すれば、階段状境界線 5 7 を含むスリットパターン 5 1 によって結晶質が異なる多結晶シリコン結晶粒が混合して形成される。このような多結晶シリコン層を使用して薄膜トランジスタ配列を形成すれば、互いに異なる特性を有する薄膜トランジスタが基板全体に均等に混在して配置される。このようにすれば、薄膜トランジスタの特性差により個々の画素が表示する画像に差が出ることがある。画面全体的にはその差が均等に混ざっているので肉眼で識別できなくなる。10

#### 【0071】

以下に詳細に説明する。

#### 【0072】

マスク 5 0 はレーザービームを通過させる透過領域である複数のスリットパターン 5 1 と、レーザービームを吸収する前記スリットパターン間の領域である遮断領域 5 2 に区分される。スリットパターン 5 1 はスリットパターンの短軸方向 (Y) に複数形成されている。スリットパターン 5 1 は後述する階段状スリットパターン 5 1 a と長方形スリットパターン 5 1 b に区分され、2列に形成されている。20

#### 【0073】

図 10 a 及び図 10 b に示されるように、マスクの遮断領域 5 2 と透過領域 5 1 の境界線の一部 5 7 は階段状に形成されている。そして、このような階段状境界線 5 7 の各断層（段差）は互いに異なる高さを有する。つまり、階段の各断層の高さが次第に高くなったり、次第に低くなるように形成される。また、断層の高さが低くなるうちに高くなったり、高くなるうちに低くなったりする。30

#### 【0074】

このような階段状境界線 5 7 が形成されたスリットパターンを階段状スリットパターン 5 1 a という。このような階段状境界線 5 7 を有する階段状スリットパターン 5 1 a と長方形スリットパターン 5 1 b は、各々スリットパターンの短軸方向 (Y) に複数形成されている。そして、Y 方向に沿って見た場合に、階段状スリットパターン 5 1 a の間に長方形スリットパターンの一部分が重なるように長方形スリットパターン 5 1 b が形成されている。このような階段状境界線 5 7 は、スリットパターン 5 1 の上側部と下側部のいずれか一方にのみ形成されているのが好ましい。図 10 a 及び図 10 b には階段状境界線 5 7 はスリットパターン 5 1 の上側部に形成されている。40

#### 【0075】

前述したような本発明のシリコン結晶化方法によるシリコン結晶化過程を説明する。

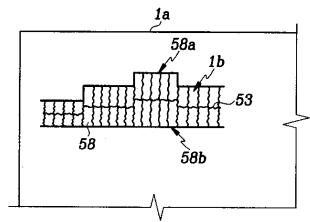

図 11 は、レーザービームを階段状境界線 5 7 が形成されたスリットパターン 5 1 を通じて照射した場合、非晶質シリコンが多結晶シリコンに結晶化されたことを示した図面である。

#### 【0076】

非晶質シリコンの上に位置したマスク 5 0 を通じてレーザービームを照射すれば、照射されたレーザービームはマスク 5 0 に形成されたスリットパターン 5 1 により分けられ、部分的に非晶質シリコンを溶かして液体化する。この場合、レーザーエネルギーの強さの程度は、非晶質シリコンが完全に溶ける程度の高エネルギー領域帯を使用する。そして、非晶質シリコンは基板上に固体状態のシード (seed)、つまり成長点が全く残らない状態となる。50

#### 【0077】

図 11 に示すように、完全に溶けて液体化した非晶質シリコンは、レーザービーム照射が終われば非晶質シリコン領域 1 a と液体化したシリコン領域 1 b に分けられる。そして、非晶質シリコン領域と液体化したシリコン領域の界面 5 3 で非晶質シリコン領域の界面

部が結晶化シードとして作用し、シリコングレーン 5 8 の側面成長（横方向結晶化）が進行される。グレーン 5 8 の側面成長は、非晶質シリコン領域 1 a と液体化したシリコン領域 1 b の界面 5 3 に対して垂直に起こる。

#### 【 0 0 7 8 】

図 10 a 及び図 10 b に示すように、マスク 5 0 に形成されたスリットパターンは階段状スリットパターン 5 1 a の第 1 列と、長方形スリットパターン 5 1 b の第 2 列に区分される。結晶化過程で、第 1 列の階段状スリットパターン 5 1 a でシリコンを結晶化した後マスク 5 0 を移動して第 2 列の長方形スリットパターン 5 1 b でシリコンを結晶化する。第 1 列の階段状スリットパターン 5 1 a と第 2 列の長方形スリットパターン 5 1 b は各々縦軸方向に一列に配置されている。

10

#### 【 0 0 7 9 】

そして、横軸方向には階段状スリットパターン 5 1 a 間に長方形スリットパターン 5 1 b の一部が重なるように長方形スリットパターン 5 1 b が形成されている。これは結晶化しない領域が発生しないようにするためである。

#### 【 0 0 8 0 】

マスク 5 0 の移動により第 1 列と第 2 列が重なった部分ではグレーンの成長が目立つ。図 11 に示すように、マスク 5 0 に形成された階段状スリットパターンの上側部に対応するシリコンの上側界面 5 8 a と階段状スリットパターンの下側部に対応するシリコンの下側界面 5 8 b でグレーン 5 8 が各々側面成長し、側面成長したそれぞれのグレーン 5 8 は液体化されたシリコン領域 1 b の横中心線 5 3 で衝突して成長を止める。

20

#### 【 0 0 8 1 】

一方、薄膜トランジスタの電流駆動能力は多結晶シリコングレーン 5 8 の長さと幅によって変化する。SLS 方式ではグレーンの長さと幅はマスクのスリットパターン 5 1 によって決まる。特に、階段状スリットパターンと長方形スリットパターンの 2 列からなるスリットパターン 5 1 では、マスクの移動時に階段状スリットパターンと長方形スリットパターンが重なるオーバーラップ長さを調節すれば多結晶シリコンのグレーンの長さと幅を調節することができる。図 10 b に示された a、b、c、d がオーバーラップ長さを示す。即ち、階段状境界線 5 7 をスリットパターン 5 1 の下部にのみ形成すれば上部のグレーンの成長点の位置が変わる。それで、グレーンの大きさの調節が可能となり、上部で成長したグレーンと下部で成長したグレーンがあうグレーン境界線の位置まで調節することが可能である。

30

#### 【 0 0 8 2 】

図 11 には、本発明によるマスクを用いて形成されたグレーンを示した。図 11 のように、画素ごとにグレーンの大きさが異なり、さらにグレーンの成長点が同一な線上に位置しないためグレーン境界線 5 3 の位置も画素ごとに一致しない。

また、これを通じて電流駆動能力が異なる複数の駆動薄膜トランジスタを 1 回の SLS 工程で作り出すことができる。

#### 【 0 0 8 3 】

この場合、互いに異なるオーバーラップ長さ（a、b、c、d）を適用させる各断層の幅（L）を一つの画素の幅と一致させれば多結晶シリコン層の結晶質偏差を画素単位で基板全体に均等に混在させることができるため、薄膜トランジスタの電流駆動能力の偏差も基板全体に均等に分布するようになる。従って、レーザービームの結晶化工エネルギーの偏差による薄膜トランジスタの特性偏差が目立つことを防止し、画質を向上させることができる。即ち、個々の薄膜トランジスタの特性は不均一であるが、不均一な特性の薄膜トランジスタがランダムに分布するため全体的には薄膜トランジスタ特性の不均一性が均等に分散される効果がある。それで、肉眼では薄膜トランジスタ特性の不均一による差を認識できず、均一な画質として認識される。

40

#### 【 0 0 8 4 】

本発明第 4 の実施例によるシリコン結晶化方法が図 12 に示されている。ここで、既に示した図面の符号と同一な符号は同じ機能をする同一部材を示す。

50

## 【0085】

図12に示されるように、階段状シリットパターン51aのみで形成されているマスク50でシリコンを結晶化することもできる。この場合、階段状シリットパターン51aのみで形成されているマスク50でシリコンを結晶化した後、階段状シリットパターン51aを所定間隔上下に移動させてレーザービームを照射すれば本発明第3の実施例のような効果が発生する。つまり、個々の薄膜トランジスタの特性は不均一であるが、不均一な特性的薄膜トランジスタがランダムに分布するため、全体的に見れば薄膜トランジスタ特性の不均一性が均等に分散される効果がある。それで、肉眼では薄膜トランジスタ特性の不均一による差を認識できず、均一な画質として認識される。

## 【0086】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求の範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態も本発明の権利範囲に属するものである。

## 【図面の簡単な説明】

## 【0087】

【図1】本発明の第1実施例による薄膜トランジスタ表示板の配置図である。

【図2】図1のI—I'-線に沿った断面図である。

【図3】図1のII—II'線に沿って断面図である。

【図4】図1のIV—IV'線に沿った断面図である。

【図5】本発明の第1実施例による薄膜トランジスタ表示板を製造する過程で多結晶シリコンパターンを形成する工程とを示す配置図である。 20

【図6】図5の多結晶シリコンパターンを形成する時に用いられるレーザー照射マスクの遮光パターンの配置図である。

【図7】図6のレーザー照射マスクを用いて非晶質シリコン層にレーザーを照射する方法を示す図面である。

【図8】本発明の第2実施例によるレーザー照射マスクの遮光パターンの配置図である。

【図9】図8のレーザー照射マスクを用いて非晶質シリコン層にレーザーを照射する方法を示す図面である。

【図10a】本発明の第3実施例によるシリコン結晶化方法に用いられるマスクを簡略に示した図面である。 30

【図10b】図10aのB領域を拡大して示した図面である。

【図11】レーザービームを階段状パターンが形成されたマスクの透過領域を通じて照射した場合、非晶質シリコンが多結晶シリコンに結晶化されることを示した図面である。

【図12】本発明の第4実施例によるシリコン結晶化方法に用いられるマスクを簡略に示した図面である。

## 【符号の説明】

## 【0088】

50 マスク

51 透過領域

52 遮断領域

110 絶縁基板

121 ゲート線

124 維持電極

130 ゲート絶縁膜

140、142、146 半導体層

171 データ線

173、174 ソース電極

192 画素電極

801 第1層間絶縁膜

802 第2層間絶縁膜

10

20

30

40

50

1 4 0 3 、 1 4 2 3 ソース領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

|   |   |   |   |

|---|---|---|---|

| 1 | 4 | 3 | 5 |

| 3 | 2 | 4 | 1 |

| 5 | 4 | 1 | 2 |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

| 1 | 4 | 3 | 5 |

| 3 | 2 | 4 | 1 |

| 5 | 4 | 1 | 2 |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

【図10a】

【図10b】

【図11】

【図12】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

H 05 B 33/14

F I

H 01 L 29/78 627G

H 01 L 29/78 612Z

テーマコード(参考)

(74)代理人 100114487

弁理士 山崎 幸作

(72)発明者 金 縣 裁

大韓民国京畿道城南市盆唐区二梅洞123番地 青丘アパート601棟903号

(72)発明者 姜 淑 映

大韓民国ソウル市瑞草区瑞草2洞 宇星アパート501棟413号

(72)発明者 金 東 範

大韓民国ソウル市江南区 清 潭洞43-1番地 現代ビラ403号

(72)発明者 李 秀 卿

大韓民国ソウル市冠岳区新林9洞1546-10番地 202号

(72)発明者 姜 明 求

大韓民国ソウル市松坡区新川洞 美星アパート3棟205号

F ターム(参考) 3K007 AB17 BA06 DB03 FA00 GA00

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5C094 | AA03 | AA43 | AA48 | AA55 | BA03 | BA12 | CA19 | CA24 | DA13 | DB04 |

| EA04  | FA01 | FB01 | FB19 | FB20 | GB10 |      |      |      |      |      |

| 5F048 | AB10 | AC04 | BA16 | BC16 | BF03 |      |      |      |      |      |

| 5F052 | AA02 | BA02 | BA12 | CA07 | DA02 | DB02 | DB03 | DB07 | JA01 |      |

| 5F110 | AA30 | BB01 | CC02 | DD13 | DD14 | EE02 | EE03 | EE06 | EE14 | EE43 |

| FF02  | FF03 | FF27 | GG02 | GG13 | GG43 | GG45 | GG47 | HJ13 | HL02 |      |

| HL03  | HL06 | HM18 | NN03 | NN23 | NN24 | NN27 | NN71 | NN73 | NN77 |      |

| NN78  | PP03 | PP06 | QQ11 |      |      |      |      |      |      |      |

## 【要約の続き】

【選択図】 図7

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 多晶硅薄膜晶体管阵列面板及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2004213027A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2004-07-29 |

| 申请号            | JP2004003453                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2004-01-08 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 金縣裁<br>姜淑映<br>金東範<br>李秀卿<br>姜明求                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 金 縣 裁<br>姜 淑 映<br>金 東 範<br>李 秀 卿<br>姜 明 求                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | H01L51/50 G09F9/30 H01L21/00 H01L21/20 H01L21/336 H01L21/77 H01L21/84 H01L27/01 H01L27/08 H01L27/12 H01L27/32 H01L29/04 H01L29/786 H01L29/788 H01L31/036 H01L31/0392 H01L31/20 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | H01L21/02678 C30B13/24 C30B29/06 H01L21/02532 H01L21/02595 H01L21/2026 H01L27/1229 H01L27/1285 H01L27/1296 Y10T428/24273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H01L21/20 H01L27/08.331.E H05B33/14.A H01L29/78.627.G H01L29/78.612.Z G09F9/30.365 H01L27/088.331.E H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/FA00 3K007/GA00 5C094/AA03 5C094/AA43 5C094/AA48 5C094/AA55 5C094/BA03 5C094/BA12 5C094/CA19 5C094/CA24 5C094/DA13 5C094/DB04 5C094/EA04 5C094/FA01 5C094/FB01 5C094/FB19 5C094/FB20 5C094/GB10 5F048/AB10 5F048/AC04 5F048/BA16 5F048/BC16 5F048/BF03 5F052/AA02 5F052/BA02 5F052/BA12 5F052/CA07 5F052/DA02 5F052/DB02 5F052/DB03 5F052/DB07 5F052/JA01 5F110/AA30 5F110/BB01 5F110 /CC02 5F110/DD13 5F110/DD14 5F110/EE02 5F110/EE03 5F110/EE06 5F110/EE14 5F110/EE43 5F110/FF02 5F110/FF03 5F110/FF27 5F110/GG02 5F110/GG13 5F110/GG43 5F110/GG45 5F110 /GG47 5F110/HJ13 5F110/HL02 5F110/HL03 5F110/HL06 5F110/HM18 5F110/NN03 5F110/NN23 5F110/NN24 5F110/NN27 5F110/NN71 5F110/NN73 5F110/NN77 5F110/NN78 5F110/PP03 5F110 /PP06 5F110/QQ11 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE04 3K107/GG00 3K107/HH00 5F152/AA03 5F152/AA06 5F152/AA08 5F152/BB02 5F152/CC09 5F152/CD13 5F152/CD14 5F152 /CE05 5F152/CE13 5F152/CE14 5F152/CE16 5F152/EE05 5F152/FF01 5F152/FF03 5F152/FF28 5F152/FG08 5F152/FH04 5F152/FH05 |         |            |

| 代理人(译)         | 小林 泰<br>千叶昭夫<br>山崎幸作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 优先权            | 1020030000971 2003-01-08 KR<br>1020030008153 2003-02-10 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | <a href="#">JP4636487B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

本发明的目的是提供一种用于有机发光显示装置的具有均匀显示特性的薄膜晶体管阵列基板。解决方案：沉积非晶硅层的步骤，通过多次通过掩模的激光束将非晶硅层转换为多晶硅层的步骤以及在多晶硅层上形成的栅极绝缘膜在栅极绝缘膜上形成栅极线的步骤，在栅极线上形成第一层间绝缘膜的步骤，在第一层间绝缘膜上形成数据线的步骤以及在数据线上的步骤。通过包括形成第二层间绝缘膜的步骤和在第二层间绝缘膜上形成像素电极的步骤的过程来制造薄膜晶体管阵列面板。用于激光射击的掩模具有多个激光透射区域和阻挡区域，并且透射区域和阻挡区域根据预定规则混合。这使得可以防止在用于硅层的多晶化的激光照射期间由不同的激光束曝光的部分彼此混合，并且可以防止激光束之间的边界被识别为线。。[选择图]图7