(12)发明专利申请

(10)申请公布号 CN 111435585 A

(43)申请公布日 2020.07.21

(21)申请号 202010027233.6

(22)申请日 2020.01.10

(30)优先权数据

10-2019-0004166 2019.01.11 KR

(71)申请人 三星显示有限公司

地址 韩国京畿道龙仁市

(72)发明人 李启旭

(74)专利代理机构 北京钲霖知识产权代理有限公司 11722

代理人 冯志云 李英艳

(51)Int.Cl.

G09G 3/3208(2016.01)

G09G 3/3266(2016.01)

G09G 3/3275(2016.01)

权利要求书2页 说明书17页 附图8页

(54)发明名称

有机发光二极管显示器

(57)摘要

一种有机发光二极管显示器包括：多个像素组，在第一方向上平行设置，并且每个像素组包括n1个像素区域；驱动电压线，设置在所述n1个像素区域中的两个相邻的像素区域之间，并在与所述第一方向相交的第二方向上延伸，以将驱动电压施加到所述两个相邻的像素区域；初始化电压线，在所述第二方向上延伸，以将初始化电压施加到所述像素组；数据线，在所述第二方向上延伸，以将数据电压施加到所述像素组；第一驱动低电压线，在所述第二方向上延伸，与将驱动低电压施加到所述像素组；以及扫描线，在所述第一方向上延伸，并与所述驱动电压线、所述初始化电压线、所述数据线和所述第一驱动低电压线相交，其中，3×n2个像素组设置在两条相邻的第一驱动低电压线之间。

1. 一种有机发光二极管显示器，其中，所述有机发光二极管显示器包括：

多个像素组，在第一方向上平行设置，其中，所述多个像素组均包括n1个像素区域，并且n1为自然数；

多条驱动电压线，设置在所述n1个像素区域中的两个相邻的像素区域之间，并在与所述第一方向相交的第二方向上延伸，以将驱动电压施加到所述两个相邻的像素区域；

多条初始化电压线，在所述第二方向上延伸，以将初始化电压施加到所述多个像素组；

多条数据线，在所述第二方向上延伸，以将数据电压施加到所述多个像素组；

多条第一驱动低电压线，在所述第二方向上延伸，以将驱动低电压施加到所述多个像素组；以及

扫描线，在所述第一方向上延伸，并与所述多条驱动电压线、所述多条初始化电压线、所述多条数据线和所述多条第一驱动低电压线相交，

其中，所述多个像素组中的 $3 \times n_2$ 个像素组设置在所述多条第一驱动低电压线中的两条相邻的第一驱动低电压线之间，并且n2为自然数。

2. 根据权利要求1所述的有机发光二极管显示器，所述有机发光二极管显示器还包括：

多条第二驱动低电压线，在所述第二方向上延伸，以将所述驱动低电压施加到所述多个像素组，

其中，所述多个像素组中的单个像素组设置在所述多条第二驱动低电压线中的两条相邻的第二驱动低电压线之间。

3. 根据权利要求2所述的有机发光二极管显示器，其中，

所述多个像素组中的所述单个像素组设置在所述多条数据线中的两条相邻的数据线之间，并且

所述 $3 \times n_2$ 个像素组设置在所述多条初始化电压线中的两条相邻的初始化电压线之间。

4. 根据权利要求3所述的有机发光二极管显示器，其中，

所述多个像素组中的三个像素组设置在所述两个相邻的第一驱动低电压线之间。

5. 根据权利要求4所述的有机发光二极管显示器，其中，所述有机发光二极管显示器还包括：

驱动低电压传输线，在所述第一方向上延伸，

其中，所述多条第一驱动低电压线和所述多条第二驱动低电压线电连接到所述驱动低电压传输线。

6. 根据权利要求1所述的有机发光二极管显示器，其中，所述有机发光二极管显示器还包括：

多个开口，限定为与所述多条第一驱动低电压线交叠。

7. 根据权利要求6所述的有机发光二极管显示器，其中，所述有机发光二极管显示器还包括：

阴极电极，通过所述多个开口电连接到所述多条第一驱动低电压线。

8. 根据权利要求1所述的有机发光二极管显示器，其中，

所述扫描线包括在所述第一方向上延伸的两条布线和将所述两条布线彼此连接的桥。

9. 根据权利要求8所述的有机发光二极管显示器，其中，

所述扫描线在除了所述桥之外的所述两条布线与所述多条数据线中的一条数据线相交的部分中包括切口区域。

10. 根据权利要求1所述的有机发光二极管显示器，其中，

所述多个像素组的所述像素区域均包括薄膜晶体管、连接到所述薄膜晶体管的阳极电极和设置在所述阳极电极上的有机发光层。

## 有机发光二极管显示器

[0001] 本申请要求于2019年1月11日提交的第10-2019-0004166号韩国专利申请的优先权，上述韩国专利申请的内容通过引用被全部包含于此。

### 技术领域

[0002] 本公开涉及有机发光二极管显示器，更具体地，涉及高分辨率的有机发光二极管显示器。

### 背景技术

[0003] 近来，有机发光二极管显示器作为用于显示图像的装置已备受关注。

[0004] 与液晶显示器不同，由于有机发光二极管显示器具有自发射特性而无需额外的光源，因此可以减小其厚度和重量。此外，有机发光二极管显示器具有诸如低功耗、高亮度和高响应速度的高品质特性。

[0005] 与液晶显示器相比，有机发光二极管显示器具有复杂的像素结构，因此随着其分辨率提高，可能无法有效地确保用于形成像素的空间。

### 发明内容

[0006] 本发明的示例性实施例涉及一种有机发光二极管显示器，其中，可以实现高分辨率而无需增加用于连接驱动低电压线和阴极电极的开口，并且可以增加栅极布线或数据布线的宽度。

[0007] 本发明的示例性实施例提供了一种有机发光二极管显示器，包括：多个像素组，在第一方向上平行设置，其中，所述多个像素组均包括n1个像素区域，并且n1为自然数；多条驱动电压线，设置在所述n1个像素区域中的两个相邻的像素区域之间，并在与所述第一方向相交的第二方向上延伸，以将驱动电压施加到所述两个相邻的像素区域；多条初始化电压线，在所述第二方向上延伸，以将初始化电压施加到所述多个像素组；多条数据线，在所述第二方向上延伸，以将数据电压施加到所述多个像素组；多条第一驱动低电压线，在所述第二方向上延伸，以将驱动低电压施加到所述多个像素组；以及扫描线，在所述第一方向上延伸，并与所述多条驱动电压线、所述多条初始化电压线、所述多条数据线和所述多条第一驱动低电压线相交，其中，所述多个像素组中的 $3 \times n_2$ 个像素组设置在所述多条第一驱动低电压线中的两条相邻的第一驱动低电压线之间，并且n2为自然数。

[0008] 在示例性实施例中，所述有机发光二极管显示器还可以包括：多条第二驱动低电压线，在所述第二方向上延伸，以将所述驱动低电压施加到所述多个像素组，其中，所述多个像素组中的单个像素组可以设置在所述多条第二驱动低电压线中的两条相邻的第二驱动低电压线之间。

[0009] 在示例性实施例中，所述多个像素组中的所述单个像素组可以设置在所述多条数据线中的两条相邻的数据线之间，并且所述 $3 \times n_2$ 个像素组可以设置在所述多条初始化电压线中的两条相邻的初始化电压线之间。

[0010] 在示例性实施例中,所述多个像素组中的三个像素组可以设置在所述两个相邻的第一驱动低电压线之间。

[0011] 在示例性实施例中,所述有机发光二极管显示器还可以包括:驱动低电压传输线,在所述第一方向上延伸,其中,所述多条第一驱动低电压线和所述多条第二驱动低电压线可以电连接到所述驱动低电压传输线。

[0012] 在示例性实施例中,多个开口可以限定为与所述多条第一驱动低电压线交叠。

[0013] 在示例性实施例中,所述有机发光二极管显示器还可以包括:阴极电极,通过所述多个开口电连接到所述多条第一驱动低电压线。

[0014] 在示例性实施例中,所述扫描线可以包括在所述第一方向上延伸的两条布线和将所述两条布线彼此连接的桥。

[0015] 在示例性实施例中,所述扫描线可以在除了所述桥之外的所述两条布线与所述多条数据线中的一条数据线相交的部分中包括切口区域。

[0016] 在示例性实施例中,所述多个像素组的所述像素区域均包括薄膜晶体管、连接到所述薄膜晶体管的阳极电极和设置在所述阳极电极上的有机发光层。

[0017] 本发明的另一示例性实施例提供了一种有机发光二极管显示器,包括:多个像素组,在第一方向上平行设置,其中,所述多个像素组均包括n1个像素区域,并且n1为自然数;多条驱动电压线,设置在所述n1个像素区域中的两个相邻的像素区域之间,并在与所述第一方向相交的第二方向上延伸,以将驱动电压施加到所述两个相邻的像素区域;多条初始化电压线,在所述第二方向上延伸,以将初始化电压施加到所述多个像素组;多条数据线,在所述第二方向上延伸,以将数据电压施加到所述多个像素组;以及扫描线,包括在所述第一方向上延伸的两条布线和将所述两条布线彼此连接的桥,其中,所述扫描线的所述两条布线与所述多条驱动电压线和所述多条初始化电压线相交。

[0018] 在示例性实施例中,所述有机发光二极管显示器还可以包括:多条第一驱动低电压线,在所述第二方向上延伸,其中,所述多个像素组中的 $3 \times n_2$ 个像素组可以设置在所述多条第一驱动低电压线中的两条相邻的第一驱动低电压线之间,并且n2为自然数。

[0019] 在示例性实施例中,多个开口可以限定为与所述多条第一驱动低电压线交叠,并且所述有机发光二极管显示器还可以包括:阴极电极,通过所述多个开口电连接到所述多条第一驱动低电压线。

[0020] 在示例性实施例中,所述有机发光二极管显示器还可以包括:多条第二驱动低电压线,在所述第二方向上延伸,其中,所述多个像素组中的单个像素组可以设置在所述多条第二驱动低电压线中的两条相邻的第二驱动低电压线之间。

[0021] 在示例性实施例中,所述多个像素组中的三个像素组可以设置在所述两个相邻的第一驱动低电压线之间。

[0022] 在示例性实施例中,所述有机发光二极管显示器还可以包括:驱动低电压传输线,在所述第一方向上延伸,其中,所述多条第一驱动低电压线和所述多条第二驱动低电压线可以电连接到所述驱动低电压传输线。

[0023] 本发明的另一示例性实施例提供了一种有机发光二极管显示器,其包括:基板;金属层,设置在所述基板上;半导体层,设置在所述金属层上;栅极绝缘层,覆盖所述半导体层;栅极层,包括低电压栅极连接件,并设置在所述栅极绝缘层上;层间绝缘层,覆盖所述栅

极层；存储电极和数据层，设置在所述层间绝缘层上；以及平坦化层，覆盖所述存储电极和所述数据层，其中，所述数据层可以包括驱动电压线、第一驱动低电压线和第二驱动低电压线，并且所述第一驱动低电压线可以与所述低电压栅极连接件交叠。

[0024] 在示例性实施例中，所述有机发光二极管显示器还可以包括：阳极电极，设置在所述平坦化层；有机发光层，设置在所述阳极电极上；以及阴极电极，设置在所述有机发光层上。

[0025] 在示例性实施例中，开口可以限定为穿过所述平坦化层以与所述第一驱动低电压线交叠。

[0026] 在示例性实施例中，所述第一驱动低电压线可以通过所述开口电连接到所述阴极电极。

[0027] 根据本发明的示例性实施例，如本文阐述的，与用于与阴极电极连接的开口交叠的第一驱动低电压线设置在三个或更多个像素组的相对侧处，并且两个像素区域设置为由一条驱动电压线驱动，因此，即使在小的像素空间中仍可以实现高分辨率。在这样的实施例中，通过在小的像素空间中宽广地形成栅极布线和数据布线的宽度，对于高分辨率驱动余量，可以减小RC延迟。

[0028] 在这样的实施例中，通过在一个像素组的相对侧处设置不具有用于与阴极电极连接的开口的第二驱动低电压线，可以减小在远离第一驱动低电压线的距离处设置的像素区域中的压降现象。

## 附图说明

[0029] 通过参考附图更详细地描述本发明的示例性实施例，本发明的以上和其他特征将变得更加明显，其中：

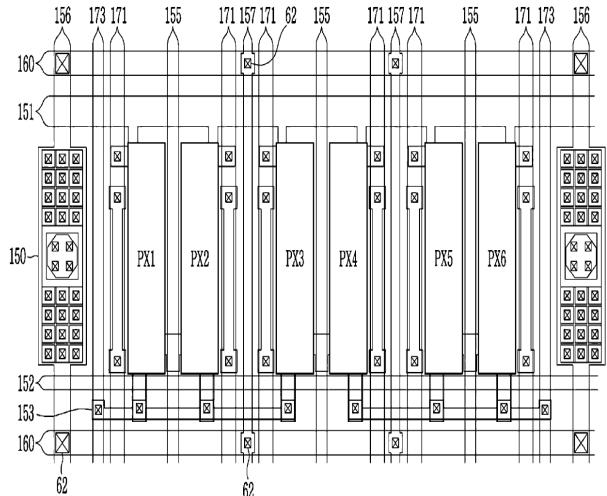

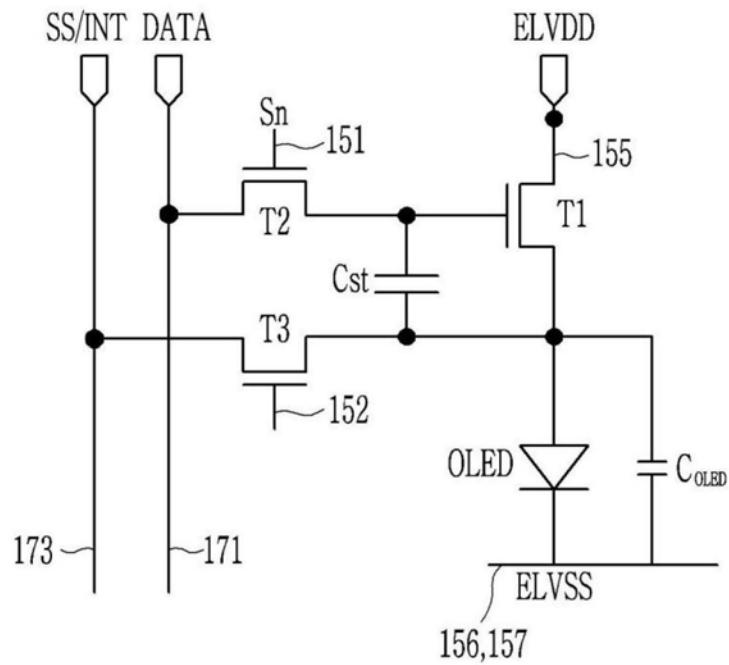

[0030] 图1示出了根据示例性实施例的有机发光二极管显示器的一个像素的等效电路图；

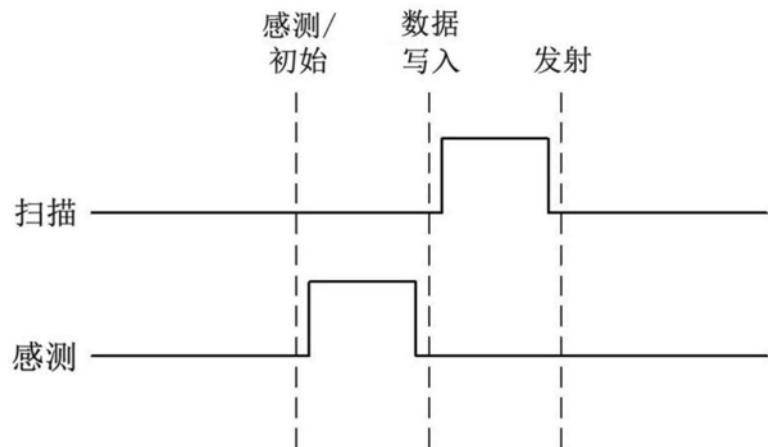

[0031] 图2示出了根据示例性实施例的施加到有机发光二极管显示器的一个像素的信号的信号时序图；

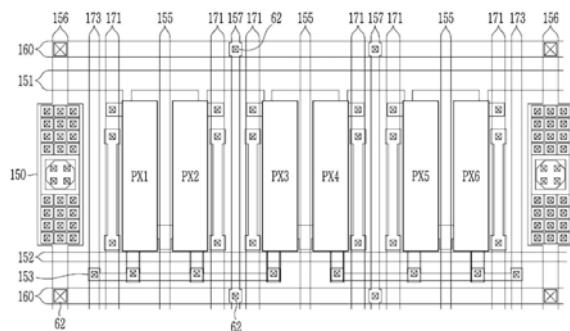

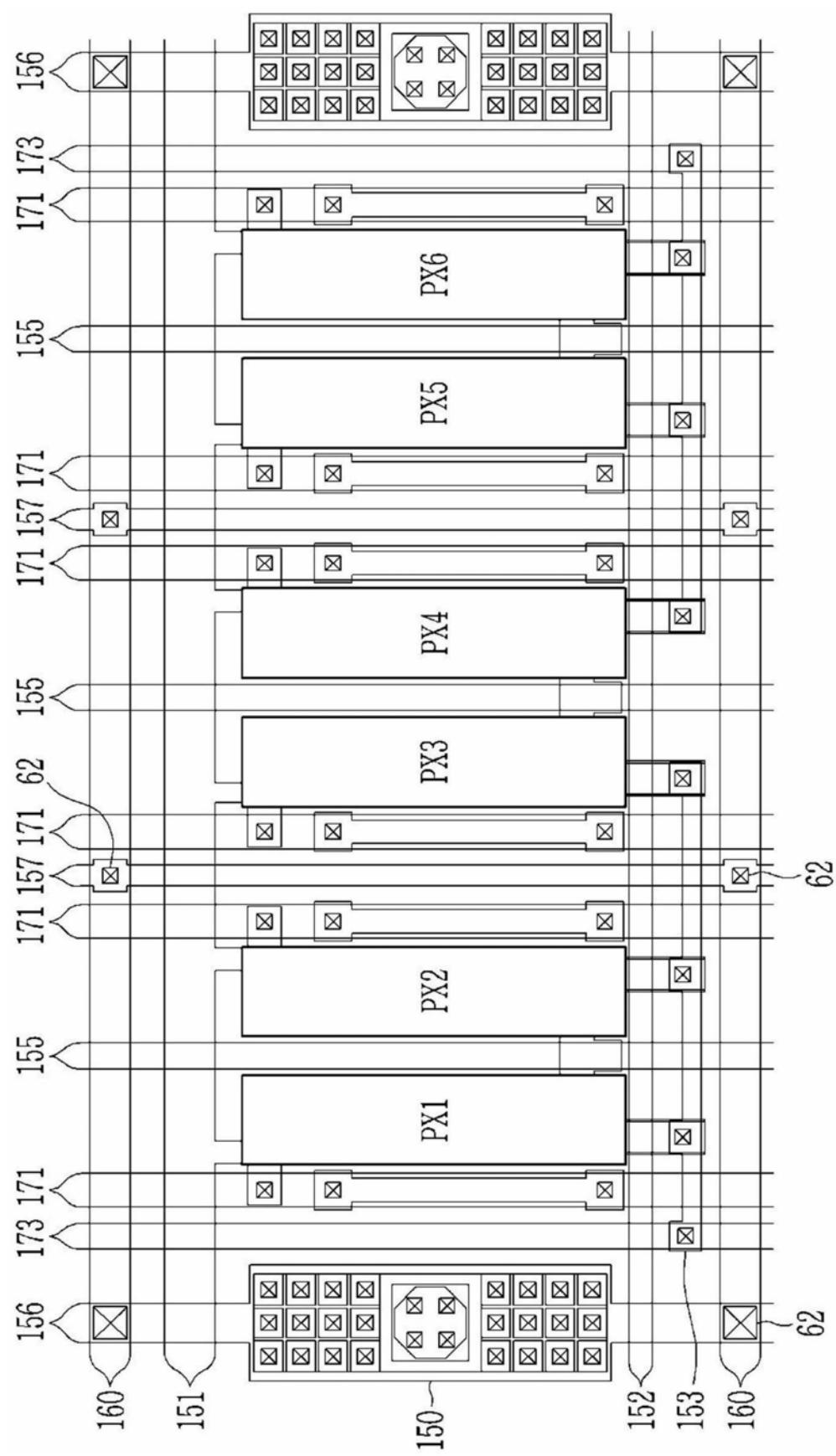

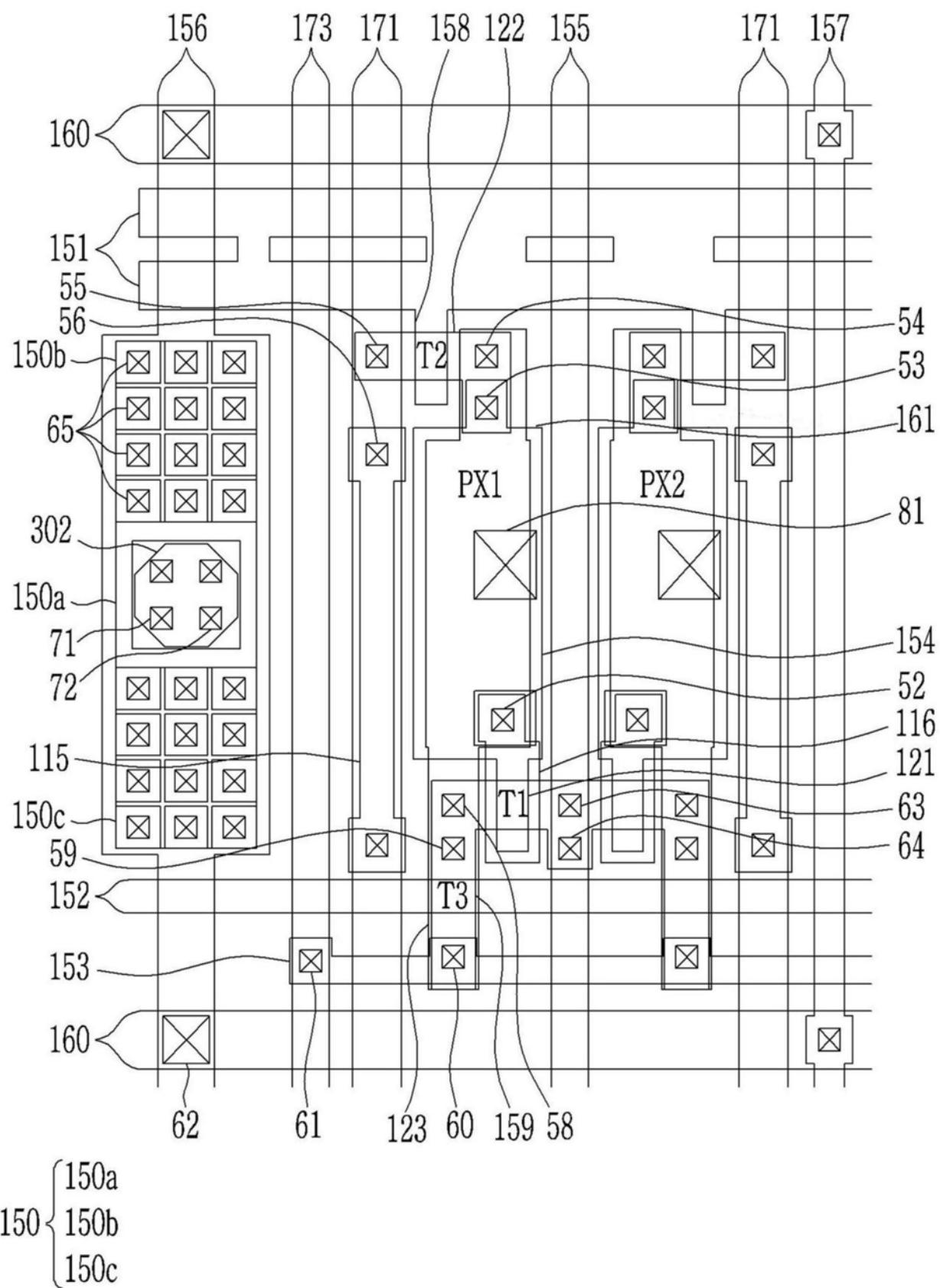

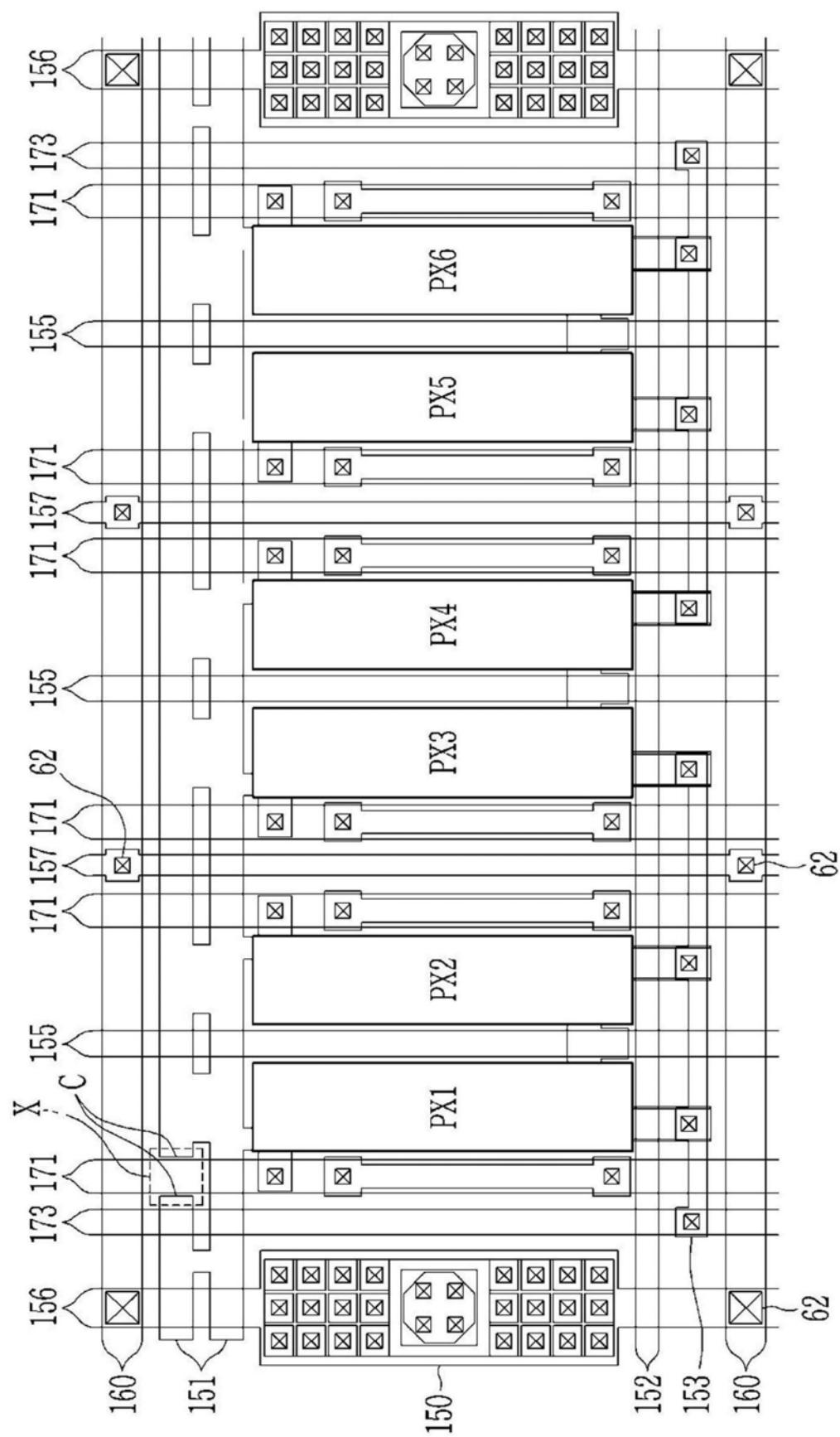

[0032] 图3示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图；

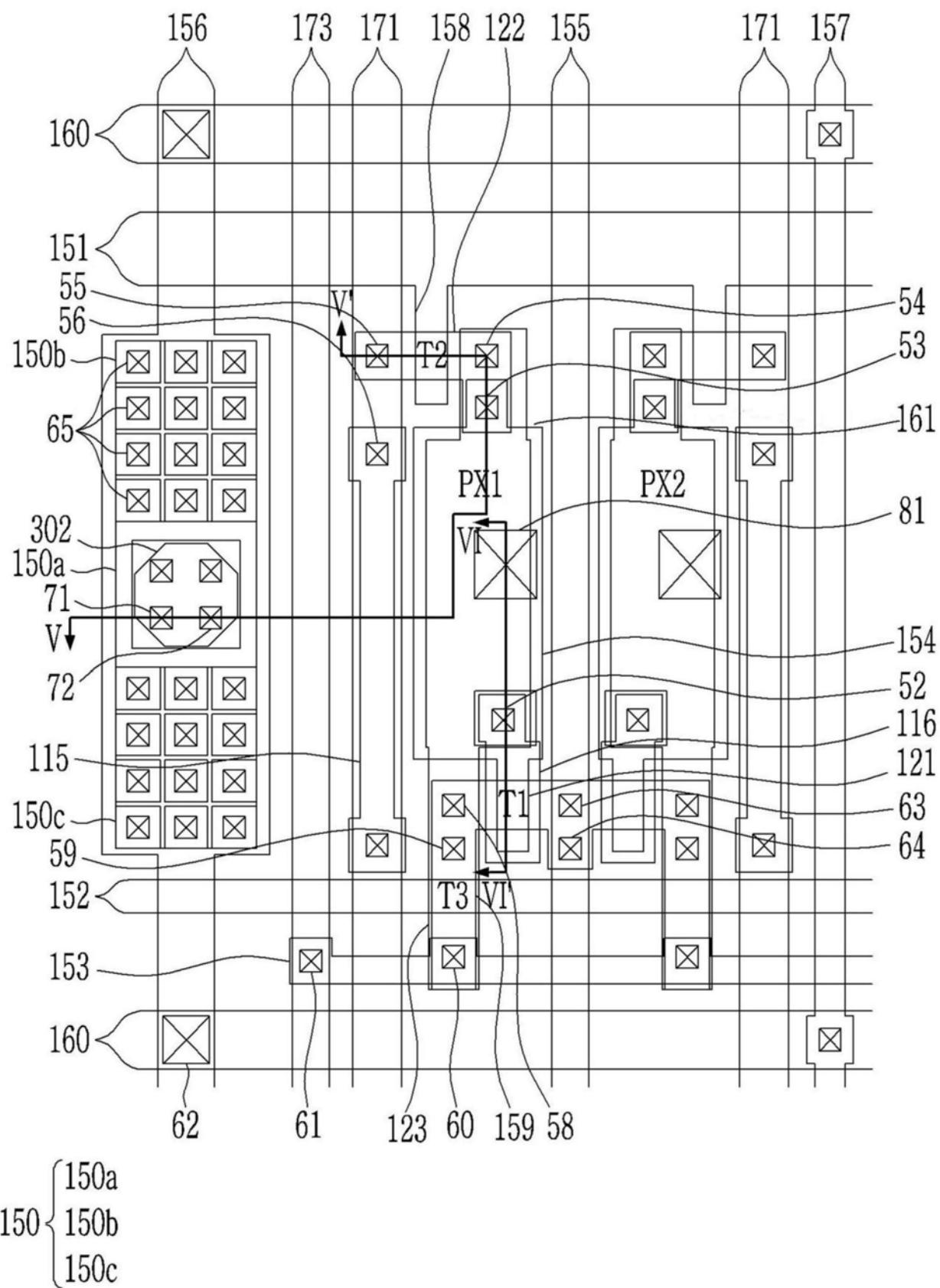

[0033] 图4示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图；

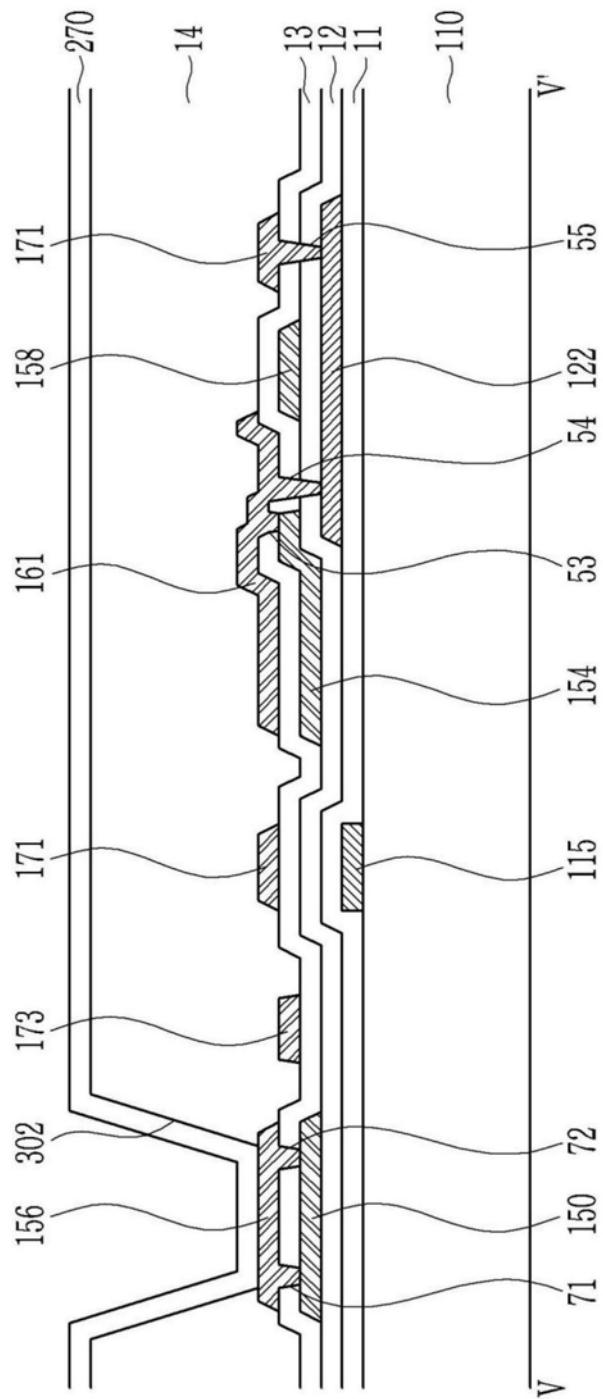

[0034] 图5示出了沿着图4的线V-V'截取的截面图；

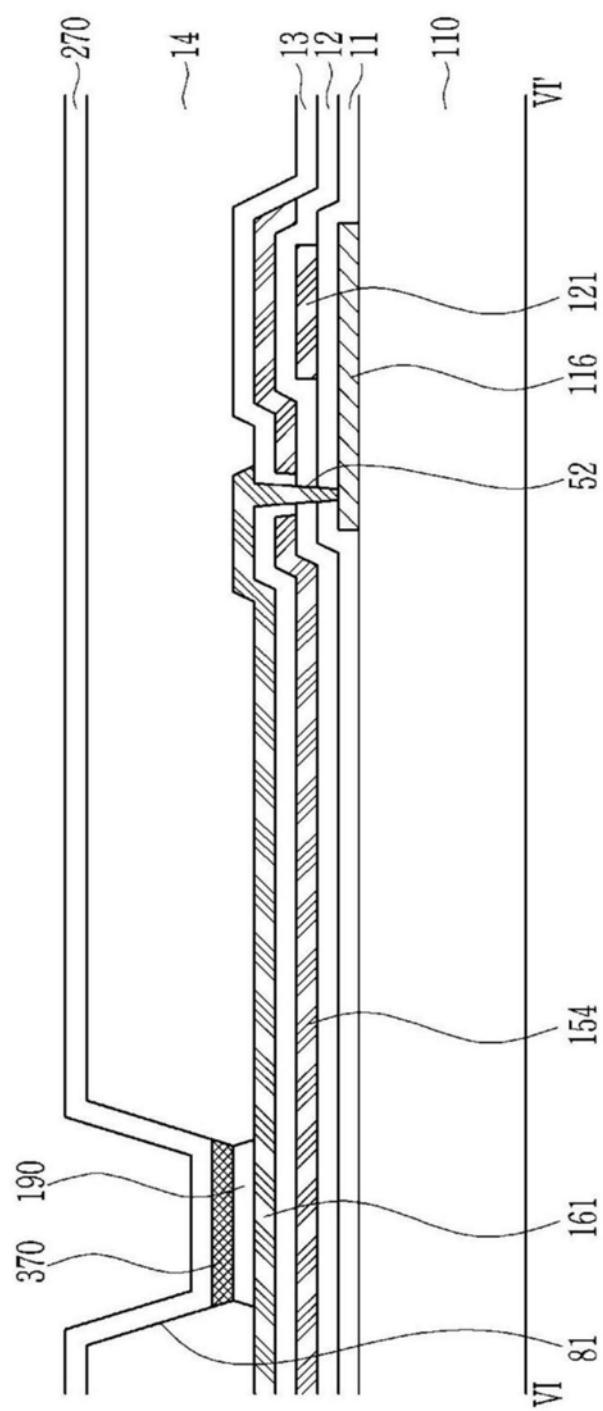

[0035] 图6示出了沿着图4的线VI-VI'截取的截面图；

[0036] 图7示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图；

[0037] 图8示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图；以及

[0038] 图9示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图，其中扫描线被修复。

## 具体实施方式

[0039] 现在将在下文中参照附图更充分地描述本发明，在附图中示出了各种实施例。然而，本发明可以以许多不同的形式来实施，而不应该被解释为局限于在此阐述的实施例。而

是提供这些实施例使本公开将是彻底的且完整的，并将把本发明的范围充分地传达给本领域的技术人员。同样的附图标记始终指同样的元件。

[0040] 将理解的是，当元件被称作“在”另一元件“上”时，该元件可以直接在另一元件上，或者可以在它们之间存在中间元件。相反，当元件被称作“直接在”另一元件“上”时，不存在中间元件。

[0041] 将理解的是，尽管在这里可使用术语“第一”、“第二”、“第三”等来描述不同的元件、组件、区域、层和/或部分，但是这些元件、组件、区域、层和/或部分不应受这些术语的限制。这些术语仅是用来将一个元件、组件、区域、层或部分与另一个元件、组件、区域、层或部分区分开来。因此，在不脱离本文教导的情况下，下面讨论的“第一元件”、“第一组件”、“第一区域”、“第一层”或“第一部分”可被命名为第二元件、第二组件、第二区域、第二层或第二部分。

[0042] 这里使用的术语仅是为了描述特定实施例的目的，而不意图是限制性的。如这里所使用的，单数形式的“一个”、“一种”和“所述(该)”也意图包括复数形式，除非上下文另外明确指出。“或”是指“和/或”。“A和B中的至少一个(一种)”是指“A和/或B”。如这里使用的，术语“和/或”包括相关所列项中的任一项以及其中一个或更多个项的所有组合。还将理解的是，当在本说明书中使用术语“包含”和/或“包括”时，说明存在陈述的特征、区域、整体、步骤、操作、元件和/或组件，但不排除存在或附加一个或更多个其他特征、区域、整体、步骤、操作、元件、组件和/或它们的组。

[0043] 此外，在这里可以使用诸如“下”或“底”和“上”或“顶”之类的相对术语来描述如附图中所示的一个元件与其他元件的关系。将理解的是，空间相对术语意在涵盖除了在附图中描绘的方位之外的装置的不同方位。例如，如果在一幅附图中装置被翻转，则描述为在其他元件“下”侧的元件随后将被定位为“在”其他元件“上”侧。因此，根据附图的具体方位，示例性术语“下”可以涵盖“下”和“上”两种方位。类似地，如果在一幅附图中装置被翻转，则描述为在其他元件“下方”或“下面”的元件随后将被定位为“在”其他元件“上方”。因此，示例性术语“在…下方”或“在…下面”可以涵盖“在…上方”和“在…下方”两种方位。

[0044] 考虑到讨论中的测量和与特定量的测量相关的误差(即，测量系统的限制)，如这里所使用的“大约”或“近似”包括所述值，并且意指在本领域普通技术人员确定的特定值的可接受的偏差范围内。

[0045] 除非另有定义，否则这里使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域的普通技术人员所通常理解的意思相同的意思。将进一步理解，术语(例如在通用的字典中定义的术语)应该被解释为具有与它们在相关领域的背景和本公开中的意思一致的意思，并且不应解释为理想的或过于形式化的意思，除非这里明确如此定义。

[0046] 这里参照作为理想实施例的示意图的截面图来描述示例性实施例。这样，预计这些示图的形状出现由例如制造技术和/或公差而引起的变化。因此，这里描述的实施例不应该被理解为局限于在此示出的区域的具体形状，而应该包括例如由制造导致的形状偏差。例如，示出或描述为平坦的区域通常可以具有粗糙的和/或非线性的特征。此外，示出的锐角可以被倒圆。因此，在附图中示出的区域实际上是示意性的，它们的形状并不意图示出区域的精确形状，也不意图限制权利要求的范围。

[0047] 此外，在整个说明书中，措词“在平面上”是指从俯视图或沿厚度方向的平面图观

察目标部分,而措词“在截面图上”是指观察通过从侧面竖直地切割目标部分所形成的截面图。

[0048] 在下文中,将参照附图详细地描述本发明的示例性实施例。

[0049] 有机发光二极管显示器的示例性实施例可以以多个像素组、驱动低电压线和驱动电压线的布置为特征。具体地,第一驱动低电压线设置在三个或更多个像素组之间,驱动电压线设置在两个像素区域的中央处。

[0050] 首先,将参照图1和图2描述根据示例性实施例的有机发光二极管显示器的像素的驱动操作,并且将参照图3至图9描述第一驱动低电压线、驱动电压线和多个像素组的布置特征。

[0051] 图1示出了根据示例性实施例的有机发光二极管显示器的像素的等效电路图。

[0052] 参照图1,有机发光二极管显示器的像素的示例性实施例包括连接到多条信号线(扫描线151、前一扫描线152、数据线171、初始化电压线173、驱动电压线155、第一驱动低电压线156和第二驱动低电压线157)的多个晶体管T1、T2和T3、存储电容器Cst、附加电容器C<sub>OLED</sub>和有机发光二极管OLED。

[0053] 在图1中显示的有机发光二极管显示器的像素可以是具有高分辨率的有机发光二极管显示器的像素,并且每个像素可以由单条数据线171和单条扫描线151来控制。

[0054] 首先,将详细描述一个像素的结构。

[0055] 包括在一个像素中的多个晶体管T1、T2和T3包括第一晶体管(或驱动晶体管)T1、连接到扫描线151的第二晶体管(或开关晶体管)T2和连接到前一扫描线152的第三晶体管(或初始化晶体管)T3(在下文中还被称作为感测晶体管)。第三晶体管T3可以连接到初始化电压线173,初始化电压线173以与前一扫描线152的时序不同的时序施加栅极导通电压(感测电压SS或初始化电压INT)。

[0056] 扫描线151连接到栅极驱动器(未示出),以将扫描信号Sn传输到第二晶体管T2。

[0057] 前一扫描线152连接到栅极驱动器,并将施加到位于前一级的像素的前一扫描信号传输到第三晶体管T3。

[0058] 数据线171是用于传输在数据驱动器(未示出)中产生的数据电压DATA的布线,并且为每个像素列提供单条数据线171。单条数据线171和单条扫描线151可以选择单个像素,以向其输入数据电压DATA。从有机发光二极管OLED(还被称作为有机发光元件)发射的光的亮度根据施加到像素的数据电压DATA而改变。

[0059] 驱动电压线155施加驱动电压ELVDD,驱动低电压线156和157施加驱动低电压ELVSS。驱动电压线155以及驱动低电压线156和157可以由在竖直方向上延伸的布线来限定,驱动低电压线156和157包括第一驱动低电压线156和第二驱动低电压线157。施加到驱动电压线155以及驱动低电压线156和157的电压可以均为恒定的电压。驱动电压ELVDD用作用于在驱动晶体管T1中产生输出电流的输入电压,并且当输出电流施加到有机发光二极管OLED时,驱动低电压ELVSS施加到另一电极(在下文中还被称作为阴极电极)。

[0060] 在示例性实施例中,阴极电极270和第一驱动低电压线156通过限定在平坦化层14(在图4和图5中示出)中的开口302(在图4和图5中示出)彼此电连接,以将驱动低电压ELVSS施加到阴极电极270(在图4和图5中示出)。在这样的实施例中,第二驱动低电压线157未设置有用于与阴极电极270连接的开口302,驱动低电压ELVSS可以通过驱动低电压传输线160

(在图3和图4中示出)施加到每个像素。

[0061] 在下文中,将更详细地描述多个晶体管T1、T2和T3。

[0062] 在示例性实施例中,驱动晶体管T1是调整对应于施加到栅电极的数据电压DATA而输出的驱动电流的量的晶体管,并且输出的驱动电流施加到有机发光二极管OLED,从而基于数据电压DATA调整有机发光二极管OLED的亮度。在这样的实施例中,驱动晶体管T1的第一电极(输入侧电极)连接到驱动电压ELVDD,第二电极(输出侧电极)连接到有机发光二极管OLED的第一电极(在下文中还被称作为阳极电极或像素电极)。驱动晶体管T1的栅电极连接到第二晶体管T2的第二电极(输出侧电极),以接收数据电压DATA。

[0063] 驱动晶体管T1的栅电极连接到存储电容器Cst的一个电极。存储电容器Cst使得传输到驱动晶体管T1的栅电极的数据电压DATA在一帧内保持。因此,驱动晶体管T1的栅电极的电压根据存储在存储电容器Cst中的电压而改变,因此,从驱动晶体管T1输出的驱动电流可以在一帧内恒定地输出。

[0064] 第二晶体管T2(还被称作为开关晶体管)是用于使数据电压DATA接收到像素中的晶体管。栅电极连接到扫描线151,第一电极(输入侧电极)连接到数据线171,第二电极(输出侧电极)连接到驱动晶体管T1的栅电极。当第二晶体管T2响应于通过扫描线151传输的扫描信号Sn而导通时,通过数据线171传输的数据电压DATA传输到驱动晶体管T1的栅电极,然后存储在存储电容器Cst中。

[0065] 第三晶体管T3(还被称作为初始化晶体管或感测晶体管)用于使驱动晶体管T1的第二电极(输出侧电极)、存储电容器Cst的一个电极和有机发光二极管OLED的阳极电极初始化。第三晶体管T3的栅电极连接到前一扫描线152,第三晶体管T3的第一电极(输入侧电极)连接到初始化电压线173。第三晶体管T3的第二电极(输出侧电极)电连接到驱动晶体管T1的第二电极(输出侧电极),由此连接到有机发光二极管OLED的阳极电极和发光二极管电容器COLED。发光二极管电容器COLED保持阳极电极电压。

[0066] 初始化电压线173不仅提供初始化电压INT,而且还用作用于在任何时段期间感测连接到第三晶体管T3的第二电极的阳极电极的电压的布线,并且还被称作为感测线。因此,第三晶体管T3还被称作为感测晶体管。

[0067] 现在将详细描述第三晶体管T3的操作。当有机发光二极管OLED发光(发射时段)时,阳极电极的电压存储在存储电容器Cst的一个电极中。在这种情况下,数据电压DATA存储在存储电容器Cst的另一电极中。因此,当栅极导通电压施加到第三晶体管T3的栅电极时,初始化电压线173作为感测线而操作,并且阳极电极的电压通过感测线传输到感测部分(未示出)。在下文中,帧周期的其中初始化电压线173作为感测线而操作的部分将被称作为感测时段。然后,在帧周期的其中栅极导通电压施加到第三晶体管T3的栅电极的其余部分中,通过初始化电压线173施加初始化电压INT,从而阳极电极电压被初始化。在下文中,帧周期的其余部分将被称作为初始化时段。

[0068] 当在感测时段中感测的电压不同于基于施加的数据电压DATA所预计的阳极电极电压时,数据电压DATA可以被校正并提供到像素。即,可以改变驱动晶体管T1的特性,并且可以感测驱动晶体管T1的改变后的特性且可以提供与改变后的特性对应的数据电压DATA,由此使有机发光二极管OLED正常地发光。

[0069] 在这样的实施例中,期望存储电容器Cst的两个电极中的每一个在一帧内保持数

据电压DATA和有机发光二极管OLED的阳极电极电压(驱动晶体管T1的输出侧电极电压)。

[0070] 现在将参照图1和图2详细地描述根据示例性实施例的有机发光二极管显示器的一个像素的操作。

[0071] 图2示出了根据示例性实施例的施加到有机发光二极管显示器的一个像素的信号的信号时序图。

[0072] 在图2中,由“扫描”指示的信号是施加到扫描线151的信号,由“感测”指示的信号是施加到前一扫描线152的信号。

[0073] 首先,高电平的前一扫描信号在“感测/初始”时段期间通过前一扫描线152被供应到像素。然后,被施加高电平的前一扫描信号的第三晶体管T3导通。在这种情况下,通过初始化电压线173来确定存储在有机发光二极管OLED的阳极电极中的电压(感测时段),然后,有机发光二极管OLED的阳极电极的电压改变为初始化电压INT(初始时段)。

[0074] 当每个像素中的驱动晶体管T1由于感测时段或过程分散(process dispersion)而具有不同的阈值电压时或当驱动晶体管T1的特性由于长时间段的操作而改变时,可以感测阈值电压的这种差异,使得有机发光二极管OLED正常地发光。

[0075] 之后,在“数据写入”时段期间,通过扫描线151向像素供应高电平的扫描信号Sn。第二晶体管T2由高电平的扫描信号Sn导通。当第二晶体管T2导通时,数据电压DATA经由第二晶体管T2输入到驱动晶体管T1的栅电极并存储在存储电容器Cst的一个电极中。

[0076] 驱动晶体管T1被确定为基于施加到栅电极的数据电压DATA而导通,并且驱动晶体管T1将驱动电压ELVDD输出到有机发光二极管OLED的阳极电极。

[0077] 有机发光二极管OLED的阳极电极电压存储在存储电容器Cst中,并在一帧内保持。

[0078] 在上面,已经参照图1和图2主要描述了电路结构和电路操作。

[0079] 在下文中,将参照图3至图9描述像素的示例性实施例的结构。在示例性实施例中,当划分电路部分和发光元件部分时,像素对应于由电路部分占据的区域。两个或更多个像素区域PX1、PX2、...共同限定一个像素组。在示例性实施例中,每个像素区域PX1、PX2、...包括多个薄膜晶体管T1、T2和T3,并可以对应于由扫描线151、前一扫描线152、驱动电压线155、数据线171和初始化电压线173围绕的一个区域。在这样的实施例中,每个像素区域PX1、PX2、...可以是由第一驱动低电压线156和第二驱动低电压线157的一部分围绕的区域。在示例性实施例中,有机发光二极管显示器可以包括三个像素组(PX1和PX2)、(PX3和PX4)以及(PX5和PX6)。在这样的实施例中,第一像素组(PX1和PX2)包括两个像素区域PX1和PX2,第二像素组(PX3和PX4)包括两个像素区域PX3和PX4,第三像素组(PX5和PX6)包括两个像素区域PX5和PX6。

[0080] 在示例性实施例中,如在图3至图9中示出的,包括驱动电压线155,其中驱动电压线155设置为延伸穿过包括第一像素区域PX1和第二像素区域PX2的第一像素组(PX1和PX2)的第一像素区域PX1和第二像素区域PX2之间的区域,并且包括第一驱动低电压线156,其中第一驱动低电压线156设置在第一像素组(PX1和PX2)、第二像素组(PX3和PX4)和第三像素组(PX5和PX6)的右侧和左侧。在这样的实施例中,第二驱动低电压线157设置为穿过第一像素组(PX1和PX2)和第二像素组(PX3和PX4)之间的区域以及第二像素组(PX3和PX4)和第三像素组(PX5和PX6)之间的区域。在下文中,将参照图3至图7更详细地描述驱动电压线155、第一驱动低电压线156和第二驱动低电压线157的布置以及根据该布置的效果。

[0081] 图3和图4示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图,图5和图6分别示出了沿着图4的线V-V'和线VI-VI'截取的截面图。

[0082] 参照图3至图6,有机发光二极管显示器的示例性实施例包括位于基板110上的金属层(115和116)、半导体层(121、122和123)、栅极层(150、151、152、153、154、158、159和160)、数据层(171、173、155、156和157)、像素电极层、阳极电极190、有机发光层370和阴极电极270,并且这些层可以在绝缘层布置在它们之间的情况下彼此绝缘,除非它们通过接触孔彼此连接。

[0083] 基板110可以为玻璃基板或包括塑料或聚酰亚胺(“PI”)的柔性基板。在示例性实施例中,在基板110为柔性基板的情况下,可以进一步提供额外的无机绝缘层。

[0084] 现在将描述设置在基板110上的金属层(115和116)。根据其形成位置,金属层(115和116)包括第一金属层115和第二金属层116。第一金属层115与数据线171的一部分交叠并连接到数据线171。第一金属层115可以与数据线171在同一方向上延伸,并且可以与数据线171具有相同的宽度。第二金属层116与驱动晶体管T1的栅电极154和存储电极161部分地交叠,并连接到栅电极154和存储电极161。因为存储电极161接收阳极电极190的电压,所以第二金属层116接收阳极电极190的电压。第二金属层116可以与驱动晶体管T1的栅电极154交叠,与形成电容器。

[0085] 缓冲层11设置在基板110以及第一金属层115和第二金属层116上。缓冲层11可以包括无机绝缘材料或由无机绝缘材料制成。

[0086] 半导体层(121、122和123)设置在缓冲层11上。半导体层(121、122和123)包括相应晶体管的半导体121、122和123,相应晶体管的半导体121、122和123包括驱动晶体管T1、第二晶体管T2和第三晶体管T3的沟道。半导体层(121、122和123)可以包括氧化物半导体或由氧化物半导体形成。第一半导体121是驱动晶体管T1的半导体,并包括沟道区以及分别设置在沟道区的相对侧处的源极区和漏极区。第二半导体122是第二晶体管T2的半导体,并包括沟道区以及设置在沟道区的相对侧处的源极区和漏极区,第三半导体123是第三晶体管T3的半导体,并包括沟道区以及设置在沟道区的相对侧处的源极区和漏极区。

[0087] 半导体121、122和123中的每一者的源极区和漏极区分别电连接到第一电极和第二电极。源极区和漏极区延伸并通过接触孔电连接到另一层。

[0088] 第一半导体121的漏极区可以连接到第三半导体123的漏极区,并可以一体地形成一个且统一的单元。第二半导体122的漏极区可以与存储电极161交叠。

[0089] 第一栅极绝缘层12设置在半导体层(121、122和123)和缓冲层11上。第一栅极绝缘层12可以包括无机绝缘材料或由无机绝缘材料形成。栅极层(150、151、152、153、154、158、159和160)设置在第一栅极绝缘层12上。栅极层(150、151、152、153、154、158、159和160)包括低电压栅极连接件150、扫描线151、前一扫描线152、初始化电压传输导体153、驱动晶体管T1的栅电极154、第二晶体管T2的栅电极158、第三晶体管T3的栅电极159和驱动低电压传输线160。

[0090] 在示例性实施例中,如图4所示,低电压栅极连接件150具有在第二方向(竖直方向)上形成的矩形岛状结构。低电压栅极连接件150与第一驱动低电压线156交叠,并通过多个接触孔65电连接到第一驱动低电压线156。在这样的实施例中,第一驱动低电压线156的一部分可以用激光照射,以电连接到阴极电极270。

[0091] 在示例性实施例中,如图4所示,扫描线151在第一方向(水平方向)上延伸,前一扫描线152也在第一方向上延伸。

[0092] 初始化电压传输导体153具有在第一方向上延伸的岛状结构。对于每预定数量的像素列,初始化电压传输导体153将多个像素连接到初始化电压线173。即,初始化电压传输导体153在第一方向上穿过与其相邻的多个像素区域,并延伸到设置有初始化电压线173的位置。在这样的实施例中,初始化电压线173连接到三个像素区域PX1、PX2和PX3,并且单条初始化电压线173形成在三个像素区域PX1、PX2和PX3的相应侧中的每一侧处。

[0093] 驱动低电压传输线160在第一方向(或水平方向)上延伸,并与在第二方向(或竖直方向)上延伸的第一驱动低电压线156和第二驱动低电压线157相交。驱动低电压传输线160在第二方向上设置在与其相邻的像素区域之间,并在第一方向上通过相邻的像素区域PX1、PX2、PX3、PX4、PX5和PX6之间的接触孔62电连接到第一驱动低电压线156和第二驱动低电压线157。

[0094] 在示例性实施例中,两条第一驱动低电压线156在第二方向上延伸,其中第一像素组(PX1和PX2)、第二像素组(PX3和PX4)和第三像素组(PX5和PX6)位于它们之间,并且两条第一驱动低电压线156通过接触孔62电连接到驱动低电压传输线160。在这样的实施例中,两条第二驱动低电压线157通过接触孔62电连接到驱动低电压传输线160,第一像素组(PX1和PX2)、第二像素组(PX3和PX4)和第三像素组(PX5和PX6)中的任何一个位于它们之间。

[0095] 根据示例性实施例,因为用于连接第一驱动低电压线156和阴极电极270的开口302的区域减小,所以在远离电压供应(未示出)的像素(即,设置在中央部分处的像素区域PX2、PX3、PX4和PX5)中可能发生压降。在这样的实施例中,通过设置第二驱动低电压线157且一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)位于它们之间,在设置在中央部分处的像素区域PX2、PX3、PX4和PX5中,电压可以保持恒定。

[0096] 然而,本发明不限于上面描述的示例性实施例,在可选的示例性实施例中,第一驱动低电压线156可以设置在 $3 \times n$ 个像素组的相对侧处,以通过接触孔62连接到驱动低电压传输线160。这里,n为1、2、3等的自然数。即,第一驱动低电压线156可以设置在三个像素组或六个像素组或九个像素组的相对侧处,以通过接触孔62连接到驱动低电压传输线160。在这样的实施例中,第二驱动低电压线157可以设置在两个像素组或一个像素组的相对侧处,以通过接触孔62连接到驱动低电压传输线160。

[0097] 驱动晶体管T1的栅电极154包括与其中设置有驱动晶体管T1的沟道的第一半导体121交叠的交叠部分和从交叠部分扩展并延伸的扩展部分。在这样的实施例中,驱动晶体管T1的栅电极154的交叠部分可以限定或用作栅电极154,扩展部分可以限定存储电容器Cst的一个电极。栅电极154的交叠部分可以与第二金属层116交叠,以形成电容器。栅电极154的扩展部分与第二晶体管T2的漏极区交叠,扩展部分通过接触孔53和54连接到第二晶体管T2的第二半导体122,从而从第二晶体管T2的第二电极接收数据电压DATA。

[0098] 第二晶体管T2的栅电极158可以由从扫描线151突出的部分限定,第二晶体管T2的沟道限定在第二晶体管T2的第二半导体122和栅电极158交叠的位置处。

[0099] 第三晶体管T3的栅电极159可以由前一扫描线152和第三晶体管T3的第三半导体123彼此交叉的部分限定。第三晶体管T3的沟道限定在第三半导体123和栅电极159交叠的位置处。

[0100] 层间绝缘层13设置在栅极层(150、151、152、153、154、158、159和160)和第一栅极绝缘层12上。层间绝缘层13可以包括无机绝缘材料或由无机绝缘材料形成。

[0101] 存储电极161和数据层(171、173、155、156和157)设置在层间绝缘层13上。存储电极161具有与驱动晶体管T1的栅电极154的扩展部分交叠的扩展部分，并包括从扩展部分向下延伸的第一延伸部分和从扩展部分向上延伸的第二延伸部分。在这样的实施例中，存储电极161的扩展部分与栅电极154交叠，以形成存储电容器Cst。从存储电极161的扩展部分向下延伸的第一延伸部分通过接触孔58和59连接到驱动晶体管T1的第二电极，并通过接触孔52连接到第二金属层116。从存储电极161的扩展部分向上延伸的第二延伸部分通过接触孔54连接到第二晶体管T2的第二电极。存储电极161可以通过在存储电极161的扩展部分的中央附近限定或形成的接触孔81连接到阳极电极190(如图6所示)。

[0102] 数据层(171、173、155、156和157)包括数据线171、初始化电压线173、驱动电压线155、第一驱动低电压线156和第二驱动低电压线157。

[0103] 数据线171设置在一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)的相对侧处，并在与第一方向垂直的第二方向(竖直方向)上延伸。数据线171通过接触孔55连接到第二晶体管T2的源极区(第一电极)，以将数据电压DATA施加到第二晶体管T2。数据线171包括与第一金属层115交叠的区域。数据线171通过接触孔56连接到第一金属层115。在示例性实施例中，两条数据线171连接到每个像素组，例如，连接到一个像素区域PX1和一个像素区域PX2。

[0104] 初始化电压线173在第二方向上延伸，并施加初始化电压INT。初始化电压线173可以设置在多个像素组的相对侧处，在示例性实施例中，两条初始化电压线173设置在三个像素组的相对侧处。初始化电压线173通过接触孔61连接到初始化电压传输导体153。初始化电压传输导体153通过接触孔60连接到第三晶体管T3的源极区(第一电极)。因此，在这样的实施例中，初始化电压INT施加到每个像素的第三晶体管T3的第一电极。

[0105] 驱动电压线155以及第一驱动低电压线156和第二驱动低电压线157也在第二方向(竖直方向)上延伸。

[0106] 驱动电压线155设置在一个像素组的两个相邻的像素区域的中央。在示例性实施例中，在包括两个像素区域PX1和PX2的一个像素组中，驱动电压线155设置在这两个像素区域PX1和PX2之间，以连接到像素区域PX1和PX2中的每一个。驱动电压线155传输驱动电压ELVDD，并通过接触孔63和64连接到驱动晶体管T1的源极区(第一电极)，以将驱动电压ELVDD传输到驱动晶体管T1的第一电极。一个像素组的两个像素区域PX1和PX2设置为相对于驱动电压线155彼此面对。第一像素区域PX1和第二像素区域PX2中的每一者的驱动晶体管T1可以设置为靠近驱动电压线155，第二晶体管T2可以设置为相比于驱动晶体管T1距驱动电压线155更远。第一像素区域PX1的驱动晶体管T1的半导体可以通过将第二像素区域PX2与驱动晶体管T1的半导体连接来限定或形成。因此，连接到第一像素区域PX1中的驱动晶体管T1的源极区的半导体区域可以是第二像素区域PX2中的驱动晶体管T1的源极区。

[0107] 第一驱动低电压线156设置在多个像素组的侧部，并传输驱动低电压ELVSS。第一驱动低电压线156包括扩展部分(150a、150b和150c)以及从扩展部分(150a、150b和150c)延伸的延伸部分。在示例性实施例中，如图4所示，扩展部分(150a、150b和150c)与低电压栅极连接件150交叠，并包括作为中央部分的第一部分150a、位于中央部分上方的第二部分150b

和位于中央部分下方的第三部分150c。

[0108] 在这样的实施例中,用于将驱动低电压ELVSS传输到阴极电极270的开口302被限定为与第一部分150a交叠。用于连接第一驱动低电压线156和低电压栅极连接件150的接触孔71和72限定在开口302中。多个接触孔65被限定为与用于连接低电压栅极连接件150和第一驱动低电压线156的第二部分150b和第三部分150c交叠。在示例性实施例中,12(=3×4)个接触孔65限定或形成在第二部分150b和第三部分150c中,但是接触孔65的数量可以进行各种修改。在可选的示例性实施例中,开口302可以在第二部分150b和第三部分150c中。

[0109] 当用于连接第一驱动低电压线156和阴极电极270的开口302的区域减小时,在远离电压供应(未示出)的像素(即,设置在中央部分处的像素区域PX2、PX3、PX4和PX5)中可能发生压降。在示例性实施例中,第二驱动低电压线157设置在一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)的相对侧处,并将驱动低电压ELVSS传输到相应的像素区域。因此,在这样的实施例中,通过在一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)的相对侧处设置第二驱动低电压线157,在设置在中央部分处的像素区域PX2、PX3、PX4和PX5中,电压也可以有效地保持恒定。

[0110] 然而,本发明不限于上面描述的示例性实施例,在可选的示例性实施例中,两条第一驱动低电压线156可以平行地设置,其中3×n个像素组位于它们之间。这里,n为1、2、3等的自然数。在这样的实施例中,这两条第一驱动低电压线156之间可以设置有三个像素组或六个像素组或九个像素组。

[0111] 平坦化层14设置在存储电极161、数据层(171、173、155、156和157)和层间绝缘层13上。平坦化层14可以包括有机绝缘材料或由有机绝缘材料形成,并且为其下方的层提供平坦的表面。像素电极层设置在平坦化层14上,阳极电极190设置在像素电极层上。

[0112] 阳极电极190将从驱动晶体管T1输出到其的电流传输到有机发光层370。阳极电极190通过接触孔81连接到存储电极161,以接收从驱动晶体管T1输出的电流。阴极电极270设置在有机发光层370上,并且阴极电极270通过限定或形成在平坦化层14中的开口302连接到第一驱动低电压线156。第一驱动低电压线156通过限定或形成在层间绝缘层13中的接触孔71和72连接到低电压栅极连接件150。

[0113] 已经描述了根据示例性实施例的有机发光二极管显示器的多个像素的结构。

[0114] 根据有机发光二极管显示器的示例性实施例,第一驱动低电压线156设置在三个或更多个像素组的相对侧处,并且两个像素区域设置为由单条驱动电压线155来驱动,因此,可以在减小的像素空间中实现高分辨率,并且即使在小的像素空间中仍可以宽广地形成栅极布线和数据布线。

[0115] 在下文中,将与对比实施例进行比较来详细描述由于根据示例性实施例的有机发光二极管显示器的驱动电压线155、第一驱动低电压线156和第二驱动低电压线157的布置而带来的效果。

[0116] (表1)

| 类别          | 对比实施例   | 示例性实施例  |

|-------------|---------|---------|

| 1个周期        | 1.9μs   | 1.9μs   |

| 驱动低电压线的布置   | 3个像素1条线 | 6个像素3条线 |

| 驱动电压线的布置    | 1个像素1条线 | 2个像素1条线 |

| 栅极层/数据层的厚度  | 0.7μm   | 0.7μm   |

| 栅极层电阻 (R)   | 5750Ω   | 2510Ω   |

| 栅极层的布线宽度    | 8μm     | 16μm    |

| 栅极层电容 (C)   | 656F    | 767F    |

| 数据层电阻 (R)   | 4523Ω   | 2720Ω   |

| 数据层的布线宽度    | 4.5μm   | 8μm     |

| 数据层电容 (C)   | 204F    | 227F    |

| (栅极 R*C) /4 | 0.943μs | 0.481μs |

| 数据 R*C      | 0.923μs | 0.617μs |

| 2*数据 R*C    | 1.846μs | 1.234μs |

| 总 RC        | 2.789μs | 1.715μs |

[0117]

[0118] 参照表1,有机发光二极管显示器的对比实施例具有设置在包括三个像素区域的一个像素组的相对侧处的两条驱动低电压线,并且单条驱动电压线连接到一个像素区域的左侧或右侧,以驱动有机发光二极管显示器。

[0119] 在根据本发明的有机发光二极管显示器的示例性实施例中,三条驱动低电压线之间设置有包括两个像素区域的一个像素组。即,第一驱动低电压线156之间设置有三个像素组,并且第二驱动低电压线157之间设置有一个像素组。这里,对于一条第一驱动低电压线156,限定或形成了开口302,而对于第二驱动低电压线157,未形成开口。

[0120] 期望的是,宽度为至少40微米(μm)的第一驱动低电压线156形成用于电连接阴极电极270和第一驱动低电压线156的开口302,根据示例性实施例,通过设置其间具有第一像素组(PX1和PX2)、第二像素组(PX3和PX4)和第三像素组(PX5和PX6)的第一驱动低电压线156,在整个像素中确保了空间,因此,栅极层的布线可以从8μm加宽到16μm,并且数据层的布线可以从4.5μm加宽到8μm。因为栅极层和数据层的布线被加宽,所以栅极层的电阻和数据层的电阻减少了大约50%。

[0121] 因此,根据示例性实施例的像素的总电阻-电容("RC")延迟减小至1.715μm。因为根据示例性实施例的一个像素以比作为像素驱动的一个周期的1.9微秒(μs)快的时间被驱动,所以一条数据布线可以由一条栅极布线驱动。

[0122] 在示例性实施例中,因为可以通过保持栅极层和数据层的电容并增加栅极层的布线和数据层的布线的宽度来减小栅极层和数据层电阻,所以栅极层的布线和数据层的布线的厚度可以恒定地保持在大约0.7μm。因为布线被形成为具有等于或小于大约0.7μm的厚度,所以可以确保根据示例性实施例的有机发光二极管显示器的驱动余量。

[0123] 即,根据示例性实施例,因为连接到单条驱动电压线和单条驱动低电压线的每个

像素区域增加,所以充分宽广地确保了用于容纳栅极层的布线和数据层的布线的空间。在这样的实施例中,当栅极层的布线和数据层的布线的宽度形成为宽广时,可以为高分辨率驱动余量有效地确保RC延迟减小效果。

[0124] 根据示例性实施例,可以宽广地形成栅极层的布线和数据层的布线。在下文中,将参照图7和图8描述宽广地形成栅极层的布线的结构。

[0125] 图7示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图,图8示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图。

[0126] 参照图7和图8,有机发光二极管显示器的示例性实施例包括金属层(115和116)、半导体层(121、122和123)、栅极层(150、151、152、153、154、158、159和160)和数据层(171、173、155、156和157),并且这些层利用它们之间的绝缘层彼此绝缘,除非通过接触孔连接。根据其形成位置,金属层(115和116)设置在基板110上,金属层(115和116)包括第一金属层115和第二金属层116。

[0127] 缓冲层11可以设置在基板110以及第一金属层115和第二金属层116上,缓冲层11可以包括无机绝缘材料或由有机绝缘材料形成。

[0128] 每个晶体管的半导体121、122和123设置在缓冲层11上,并且每个晶体管的半导体121、122和123包括驱动晶体管T1、第二晶体管T2和第三晶体管T3的沟道。第一半导体121是驱动晶体管T1的半导体,并包括沟道区以及设置在沟道区的相对侧处的源极区和漏极区。第二半导体122是第二晶体管T2的半导体,并包括沟道区以及设置在沟道区的相对侧处的源极区和漏极区,第三半导体123是第三晶体管T3的半导体,并包括沟道区以及设置在沟道区的相对侧处的源极区和漏极区。

[0129] 第一栅极绝缘层12可以设置在半导体层(121、122和123)和缓冲层11上,第一栅极绝缘层12可以包括无机绝缘材料或由无机绝缘材料形成。

[0130] 栅极层(150、151、152、153、154、158、159和160)可以设置在第一栅极绝缘层12上。栅极层(150、151、152、153、154、158、159和160)包括低电压栅极连接件150、扫描线151、前一扫描线152、初始化电压传输导体153、驱动晶体管T1的栅电极154、第二晶体管T2的栅电极158、第三晶体管T3的栅电极159和驱动低电压传输线160。

[0131] 低电压栅极连接件150具有在第二方向(竖直方向)上延伸的矩形岛状结构。低电压栅极连接件150与第一驱动低电压线156交叠,并通过多个接触孔65电连接到第一驱动低电压线156。在示例性实施例中,第一驱动低电压线156的一部分可以用激光照射,以电连接阴极电极270。

[0132] 在示例性实施例中,如图7所示,扫描线151在第一方向(水平方向)上延伸,前一扫描线152在第一方向(水平方向)上延伸。扫描线151在与数据层布线相交的区域中划分成或分支成两条线,这两条线在不与数据层布线相交的区域中被桥接以占据宽广的区域。扫描线151包括桥,当在与数据层布线相交的区域中发生短路时,可以有效地对扫描线151进行修复。将参照图9对此进行更详细地描述。

[0133] 初始化电压传输导体153具有在第一方向上延伸的岛状结构。初始化电压传输导体153是用于将为每预定数量的像素列提供的初始化电压线173连接到多个像素的元件。即,初始化电压传输导体153在第一方向上延伸穿过与其相邻的多个像素区域,并延伸到设置有初始化电压线173的位置。在示例性实施例中,如图7所示,初始化电压线173连接到三

个像素区域PX1、PX2和PX3，并且它们形成在三个像素区域PX1、PX2和PX3中的相应侧的每一侧处。

[0134] 驱动低电压传输线160在第一方向上延伸，并与在第二方向上延伸的第一驱动低电压线156和第二驱动低电压线157相交。驱动低电压传输线160在第二方向上设置在与其相邻的像素区域之间，并在第一方向上通过位于相邻的像素区域PX1、PX2、PX3、PX4、PX5和PX6之间的接触孔62电连接到第一驱动低电压线156和第二驱动低电压线157。

[0135] 在示例性实施例中，两条第一驱动低电压线156在第一像素组（PX1和PX2）、第二像素组（PX3和PX4）和第三像素组（PX5和PX6）的侧部在第二方向上延伸，这两条第一驱动低电压线156通过接触孔62电连接到驱动低电压传输线160。在这样的实施例中，两条第二驱动低电压线157在位于它们之间的第一像素组（PX1和PX2）、第二像素组（PX3和PX4）和第三像素组（PX5和PX6）中的任意一组的相对侧通过接触孔62电连接到驱动低电压传输线160。

[0136] 根据示例性实施例，如图8所示，因为用于连接第一驱动低电压线156和阴极电极270的开口302的区域减小，所以在远离电压供应（未示出）的像素（即，设置在中央部分处的像素区域PX2、PX3、PX4和PX5）中可能发生压降。在这样的实施例中，通过在一个像素组（PX1和PX2）、（PX3和PX4）或（PX5和PX6）的相对侧处设置第二驱动低电压线157，在设置在中央部分处的像素区域PX2、PX3、PX4和PX5中，电压可以保持恒定。然而，本发明不限于上面描述的示例性实施例，可选地，第一驱动低电压线156可以设置在 $3 \times n$ 个像素组的相对侧处，以通过接触孔62连接到驱动低电压传输线160。这里，n为1、2、3等的自然数。即，第一驱动低电压线156可以设置在三个像素组或六个像素组或九个像素组的相对侧处，以通过接触孔62连接到驱动低电压传输线160。在示例性实施例中，第二驱动低电压线157可以设置在两个像素组或一个像素组的相对侧处，以通过接触孔62连接到驱动低电压传输线160。

[0137] 驱动晶体管T1的栅电极154包括与其中设置有驱动晶体管T1的沟道的第一半导体121交叠的交叠部分和从交叠部分延伸并扩展的扩展部分。在示例性实施例中，驱动晶体管T1的栅电极154的交叠部分用作栅电极154，扩展部分限定存储电容器Cst的一个电极。栅电极154的交叠部分可以与第二金属层116交叠，以形成电容器。栅电极154的扩展部分与第二晶体管T2的漏极区交叠，并且扩展部分通过接触孔53和54连接到第二晶体管T2的第二半导体122，以从第二晶体管T2的第二电极接收数据电压DATA。

[0138] 第二晶体管T2的栅电极158是从扫描线151突出的部分，并且第二晶体管T2的沟道形成在第二晶体管T2的第二半导体122和栅电极158交叠的位置处。

[0139] 第三晶体管T3的栅电极159是前一扫描线152和第三晶体管T3的第三半导体123彼此交叉的部分。第三晶体管T3的沟道形成在第三半导体123和栅电极159交叠的位置处。

[0140] 层间绝缘层13设置在栅极层（150、151、152、153、154、158、159和160）和第一栅极绝缘层12上。层间绝缘层13可以包括无机绝缘材料或由无机绝缘材料形成。

[0141] 存储电极161和数据层（171、173、155、156和157）设置在层间绝缘层13上。

[0142] 存储电极161具有与驱动晶体管T1的栅电极154的扩展部分交叠的扩展部分，并包括分别从扩展部分向上和向下延伸的第一延伸部分和第二延伸部分。这里，存储电极161的扩展部分与栅电极154交叠，以形成存储电容器Cst。从存储电极161的扩展部分向下延伸的第一延伸部分通过接触孔58和59连接到驱动晶体管T1的第二电极，并通过接触孔52连接到第二金属层116。从存储电极161的扩展部分向上延伸的第二延伸部分通过接触孔54连接到

第二晶体管T2的第二电极。存储电极161可以通过在存储电极161的扩展部分的中央附近限定或形成的接触孔81连接到阳极电极190(参考图6)。

[0143] 数据层(171、173、155、156和157)包括数据线171、初始化电压线173、驱动电压线155、第一驱动低电压线156和第二驱动低电压线157。

[0144] 数据线171设置在一个像素组(PX1和PX2)的相对侧，并在与第一方向垂直的第二方向(竖直方向)上延伸。数据线171通过接触孔55连接到第二晶体管T2的源极区(第一电极)，以将数据电压DATA施加到第二晶体管T2。数据线171包括与第一金属层115交叠的区域。数据线171通过接触孔56连接到第一金属层115。在示例性实施例中，两条数据线171连接到一个像素组，即，分别连接到第一像素区域PX1和第二像素区域PX2。

[0145] 初始化电压线173在第二方向上延伸，并施加初始化电压INT。初始化电压线173可以设置在多个像素组的相对侧处，两条初始化电压线173设置在三个像素组的相对侧处。初始化电压线173通过接触孔61连接到初始化电压传输导体153。初始化电压传输导体153通过接触孔60连接到第三晶体管T3的源极区(第一电极)。因此，在这样的实施例中，初始化电压INT施加到每个像素的第三晶体管T3的第一电极。

[0146] 驱动电压线155以及第一驱动低电压线156和第二驱动低电压线157也在第二方向(竖直方向)上延伸。

[0147] 驱动电压线155设置在一个像素组的两个相邻的像素区域的中央。在示例性实施例中，在包括两个像素区域PX1和PX2的一个像素组(PX1和PX2)中，驱动电压线155设置在这两个像素区域PX1和PX2之间，以连接到像素区域PX1和PX2中的每一者。驱动电压线155传输驱动电压ELVDD，并通过接触孔63和64连接到驱动晶体管T1的源极区(第一电极)，以将驱动电压ELVDD传输到驱动晶体管T1的第一电极。一个像素组(PX1和PX2)的两个像素区域PX1和PX2设置为相对于驱动电压线155彼此面对。第一像素区域PX1和第二像素区域PX2中的每一者的驱动晶体管T1可以设置为靠近驱动电压线155，第二晶体管T2可以设置为相比于驱动晶体管T1距驱动电压线155更远。第一像素区域PX1的驱动晶体管T1的半导体可以通过将第二像素区域PX2与驱动晶体管T1的半导体连接来形成。因此，连接到形成在第一像素区域PX1中的驱动晶体管T1的源极区的半导体区域可以是形成在第二像素区域PX2中的驱动晶体管T1的源极区。

[0148] 第一驱动低电压线156设置在多个像素组的侧部，并传输驱动低电压ELVSS。第一驱动低电压线156包括扩展部分(150a、150b和150c)和从扩展部分(150a、150b和150c)延伸的延伸部分。扩展部分(150a、150b和150c)与低电压栅极连接件150交叠，并包括作为中央部分的第一部分150a、位于中央部分上方的第二部分150b和位于中央部分下方的第三部分150c。

[0149] 在示例性实施例中，开口302被限定为与第一部分150a交叠，用于将驱动低电压ELVSS传输到阴极电极270。用于连接第一驱动低电压线156和低电压栅极连接件150的接触孔71和72限定或形成在开口302中。在这样的实施例中，多个接触孔65被限定为与第二部分150b和第三部分150c交叠，用于连接低电压栅极连接件150和第一驱动低电压线156。在示例性实施例中，12(=3×4)个接触孔65限定或形成在第二部分150b和第三部分150c中，但是接触孔65的数量可以进行各种修改。在可选的示例性实施例中，开口302可以限定或形成与第二部分150b和第三部分150c交叠。

[0150] 根据示例性实施例,因为用于连接第一驱动低电压线156和阴极电极270的开口302的区域减小,所以在远离电压供应(未示出)的像素(即,设置在中央部分处的像素区域PX2、PX3、PX4和PX5)中可能发生压降。然而,根据示例性实施例,第二驱动低电压线157设置在一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)的相对侧处,并将驱动低电压ELVSS传输到相应的像素区域。因此,通过在一个像素组(PX1和PX2)、(PX3和PX4)或(PX5和PX6)的相对侧处设置第二驱动低电压线157,在设置在中央部分处的像素区域PX2、PX3、PX4和PX5中,也可以有效地保持电压恒定。

[0151] 然而,本发明不限于上面描述的示例性实施例,可选地,两条第一驱动低电压线156可以平行地设置且 $3 \times n$ 个像素组位于它们之间。这里,n为1、2、3等的自然数。即,这两条第一驱动低电压线156之间可以设置有三个像素组或六个像素组或九个像素组。

[0152] 平坦化层14设置在存储电极161、数据层(171、173、155、156和157)和层间绝缘层13上。平坦化层14可以包括有机绝缘材料或由有机绝缘材料形成,并具有平坦的上表面,以使由其下方的层限定的任何台阶结构平坦化。

[0153] 像素电极层(未示出)设置在平坦化层14上,并且阳极电极190设置在像素电极层上。

[0154] 阳极电极190将从驱动晶体管T1输出到有机发光二极管OLED的一个电极的电流传输到有机发光层370。阳极电极190通过接触孔81连接到存储电极161,从而接收从驱动晶体管T1输出的电流。阴极电极270设置在有机发光层370上,并且阴极电极270通过限定或形成在平坦化层14中的开口302连接到第一驱动低电压线156。第一驱动低电压线156通过限定或形成在层间绝缘层13中的接触孔71和72连接到低电压栅极连接件150。

[0155] 根据有机发光二极管显示器的示例性实施例,第一驱动低电压线156设置在三个或更多个像素组的相对侧处,并且两个像素区域设置为由一条驱动电压线155来驱动,因此,即使在小的像素空间中仍可以实现高分辨率,并且即使在小的像素空间中仍可以广泛地提供栅极布线和数据布线。

[0156] 在有机发光二极管显示器的这样的实施例中,可以确保足够的空间来在栅极层中为扫描线151提供两条线,从而即使当扫描线151和数据线171短路时,也可以简单地通过切割来有效地执行修复工艺。

[0157] 图9示出了根据示例性实施例的有机发光二极管显示器的多个像素的平面图,其中对扫描线进行修复。

[0158] 参照图9,扫描线151包括在第一方向上延伸的两条布线和连接这两条布线的桥。桥设置在不与数据线171、初始化电压线173、驱动电压线155、第一驱动低电压线156和第二驱动低电压线157相交的区域中。

[0159] 然而,在与数据层(171、173、155、156和157)相交的区域X中,扫描线151中未设置桥,并且可能发生短路。在这种情况下,为了防止扫描信号Sn和数据电压DATA干扰,执行用于切割发生短路的区域X的修复工艺。

[0160] 当如图9所示切割发生短路的区域X时,扫描线151在沿第一方向延伸的一些布线中包括切口区域C。当从扫描线151的一侧提供扫描信号Sn(参考图1)时,扫描信号Sn通过除了切口区域C之外的在第一方向上延伸的另一布线施加到第一像素区域PX1的第二晶体管T2的栅电极158,由此在不受干扰的情况下传输扫描信号Sn。

[0161] 在根据本发明的有机发光二极管显示器的示例性实施例中，第一驱动低电压线156设置在三个或更多个像素组的相对侧处，并且两个像素区域由一条驱动电压线155驱动，使得即使在小的像素空间中扫描线151仍可以以两条布线宽广地形成。因此，由于提供了包括两条布线和桥的扫描线151，所以当在扫描线151和数据线171相交的区域中发生短路时，可以通过切割工艺简单地执行修复工艺。

[0162] 虽然结合目前被视为实际的示例性实施例的内容描述了本发明，但应当理解，本发明不限于所公开的实施例，而是相反，本发明意在覆盖包括在所附权利要求的精神和范围内的各种修改和等同布置。

图1

图2

图3

图4

图5

图6

图7

图8

图9

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光二极管显示器                                     |         |            |

| 公开(公告)号        | <a href="#">CN111435585A</a>                   | 公开(公告)日 | 2020-07-21 |

| 申请号            | CN202010027233.6                               | 申请日     | 2020-01-10 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                       |         |            |

| 申请(专利权)人(译)    | 三星显示有限公司                                       |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                       |         |            |

| [标]发明人         | 李启旭                                            |         |            |

| 发明人            | 李启旭                                            |         |            |

| IPC分类号         | G09G3/3208 G09G3/3266 G09G3/3275               |         |            |

| CPC分类号         | G09G3/3225 G09G3/3291 H01L27/3262 H01L27/3276  |         |            |

| 代理人(译)         | 冯志云                                            |         |            |

| 优先权            | 1020190004166 2019-01-11 KR                    |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

一种有机发光二极管显示器包括：多个像素组，在第一方向上平行设置，并且每个像素组包括n1个像素区域；驱动电压线，设置在所述n1个像素区域中的两个相邻的像素区域之间，并在与所述第一方向相交的第二方向上延伸，以将驱动电压施加到所述两个相邻的像素区域；初始化电压线，在所述第二方向上延伸，以将初始化电压施加到所述像素组；数据线，在所述第二方向上延伸，以将数据电压施加到所述像素组；第一驱动低电压线，在所述第二方向上延伸，与将驱动低电压施加到所述像素组；以及扫描线，在所述第一方向上延伸，并与所述驱动电压线、所述初始化电压线、所述数据线和所述第一驱动低电压线相交，其中，3×n2个像素组设置在两条相邻的第一驱动低电压线之间。