(12)发明专利申请

(10)申请公布号 CN 110993677 A

(43)申请公布日 2020.04.10

(21)申请号 201911326488.6

(22)申请日 2019.12.20

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 张洁 刘利宾

(74)专利代理机构 北京中博世达专利商标代理有限公司 11274

代理人 成亚婷

(51)Int.Cl.

H01L 27/32(2006.01)

权利要求书1页 说明书5页 附图1页

(54)发明名称

显示基板及显示装置

(57)摘要

本公开实施例公开了一种显示基板及显示装置,涉及显示技术领域,用于减小其扇出走线中每相邻两条信号线走线之间的信号串扰,有利于提升显示基板及显示装置的显示效果。所述显示基板包括:衬底、光遮挡层和扇出走线结构。光遮挡层设置于衬底的表面。扇出走线结构包括绝缘设置的第一走线层和第二走线层。第一走线层和第二走线层中的一者与光遮挡层同层设置。本公开实施例提供的显示基板及显示装置用于OLED显示。

1. 一种显示基板,其特征在于,包括:

衬底;

光遮挡层,设置于所述衬底的表面;

扇出走线结构,包括绝缘设置的第一走线层和第二走线层;

其中,所述第一走线层和第二走线层中的一者与所述光遮挡层同层设置。

2. 根据权利要求1所述的显示基板,其特征在于,所述显示基板还包括:依次层叠设置于所述光遮挡层的远离所述衬底的一侧的第一绝缘层、第一导电图案、第二绝缘层以及第二导电图案;

所述第一走线层和第二走线层中的另一者与所述第二导电图案同层设置。

3. 根据权利要求2所述的显示基板,其特征在于,所述显示基板包括显示区以及位于所述显示区的至少一侧的周边区;所述光遮挡层、所述第一导电图案和所述第二导电图案位于所述显示区内;所述扇出走线结构位于所述周边区内。

4. 根据权利要求1~3任一项所述的显示基板,其特征在于,

所述第一走线层包括多条第一走线;所述第二走线层包括多条第二走线;

所述第一走线在所述衬底上的正投影与所述第二走线在所述衬底上的正投影交替间隔排布。

5. 根据权利要求4所述的显示基板,其特征在于,所述第一走线的宽度和所述第二走线的宽度相等。

6. 根据权利要求4所述的显示基板,其特征在于,所述第一走线在所述衬底上的正投影与对应的所述第二走线在所述衬底上的正投影之间的间隔极小值的取值范围为:0.5um~1um。

7. 根据权利要求2所述的显示基板,其特征在于,所述显示基板还包括:依次层叠设置于所述光遮挡层的靠近所述第一绝缘层的一侧的缓冲层和半导体图案。

8. 根据权利要求2所述的显示基板,其特征在于,所述第二导电图案为金属导电图案。

9. 根据权利要求1所述的显示基板,其特征在于,

所述光遮挡层为金属层;

所述第一走线层和所述第二走线层均为金属走线层。

10. 一种显示装置,其特征在于,包括:如权利要求1~9任一项所述的显示基板。

## 显示基板及显示装置

### 技术领域

[0001] 本公开涉及显示技术领域,尤其涉及一种显示基板及显示装置。

### 背景技术

[0002] 在有机电致发光二极管(Organic Light-Emitting Diode,OLED)显示装置中,OLED基板包括显示区以及位于显示区旁侧的周边区。显示区内通常设有多种类型的信号线,例如栅线、数据线等。周边区内通常设有用于连接各信号线与对应驱动芯片的扇出走线。显示装置中的驱动芯片通过扇出走线向显示区内的各信号线传输驱动信号,可以实现对应画面的显示。

### 发明内容

[0003] 本公开一些实施例的目的在于提供一种显示基板及显示装置,用于减小其扇出走线中每相邻两条信号线走线之间的信号串扰,有利于提升显示基板及显示装置的显示效果。

[0004] 为达到上述目的,本公开一些实施例提供了如下技术方案:

[0005] 一方面,提供了一种显示基板。所述显示基板包括:衬底、光遮挡层和扇出走线结构。光遮挡层设置于衬底的表面。扇出走线结构包括绝缘设置的第一走线层和第二走线层。第一走线层和第二走线层中的一者与光遮挡层同层设置。

[0006] 在一些实施例中,显示基板还包括:依次层叠设置于光遮挡层的远离衬底的一侧的第一绝缘层、第一导电图案、第二绝缘层以及第二导电图案。第一走线层和第二走线层中的另一者与第二导电图案同层设置。

[0007] 在一些实施例中,显示基板包括显示区以及位于所述显示区的至少一侧的周边区。光遮挡层、第一导电图案和第二导电图案位于显示区内。扇出走线结构位于周边区内。

[0008] 在一些实施例中,第一走线层包括多条第一走线。第二走线层包括多条第二走线。多条第一走线在衬底上的正投影与多条第二走线在衬底上的正投影间隔设置。

[0009] 在一些实施例中,第一走线的宽度和第二走线的宽度相等。各第一走线在衬底上的正投影与对应的第二走线在衬底上的正投影之间的间隔相等或大略相等。

[0010] 在一些实施例中,第一走线在衬底上的正投影与对应的第二走线在衬底上的正投影之间的间隔极小值的取值范围为:0.5um~1um。

[0011] 在一些实施例中,显示基板还包括依次层叠设置于所述光遮挡层的靠近所述第一绝缘层的一侧的缓冲层和半导体图案。

[0012] 在一些实施例中,第二导电图案为金属导电图案。

[0013] 在一些实施例中,光遮挡层为金属层。第一走线层和第二走线层均为金属走线层。

[0014] 在本公开一些实施例提供的显示基板中,扇出走线结构包括绝缘设置的第一走线层和第二走线层。由于光遮挡层通常形成在衬底的表面,因此,将第一走线层和第二走线层中的一者与光遮挡层同层设置时,能够允许第一走线层与第二走线层之间沿垂直于衬底的

方向具有较远的距离,也即可以使得第一走线层与第二走线层之间存在较厚的绝缘薄膜,从而确保第一走线层与第二走线层之间良好绝缘,进而减小第一走线层和第二走线层之间的信号串扰,以提升显示基板及显示装置的显示效果。

[0015] 此外,在第一走线层和第二走线层之间能够良好绝缘的前提下,将扇出走线结构的第一走线层中的每条第一走线与第二走线层中对应第二走线之间的间隔合理减小,可以对应压缩扇出走线结构的占用空间,从而提升显示基板的屏占比。当然,若在扇出走线结构占用空间不变的情况下,第一走线与对应第二走线之间的间隔合理减小,可以对应加宽第一走线和第二走线的宽度,以减小第一走线和第二走线的阻抗,从而提升扇出走线结构的阻抗均匀性,进而提升显示基板及显示装置的显示效果。

[0016] 另一方面,提供了一种显示装置。所述显示装置包括:如上述一些实施例中所述的显示基板。本公开一些实施例提供的显示装置所能实现的有益效果,与上述一些实施例提供的显示基板所能达到的有益效果相同,在此不做赘述。

## 附图说明

[0017] 此处所说明的附图用来提供对本公开实施例的进一步理解,构成本公开实施例的一部分,本公开的示意性实施例及其说明用于解释本公开,并不构成对本公开的不当限定。在附图中:

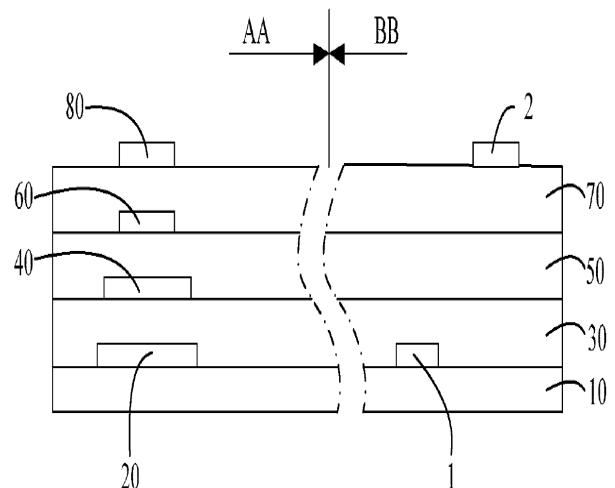

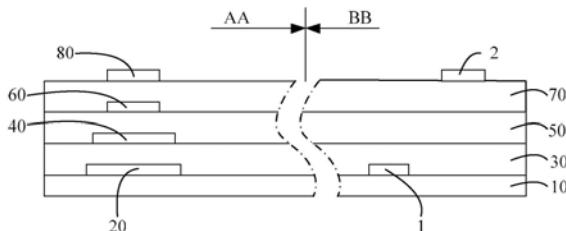

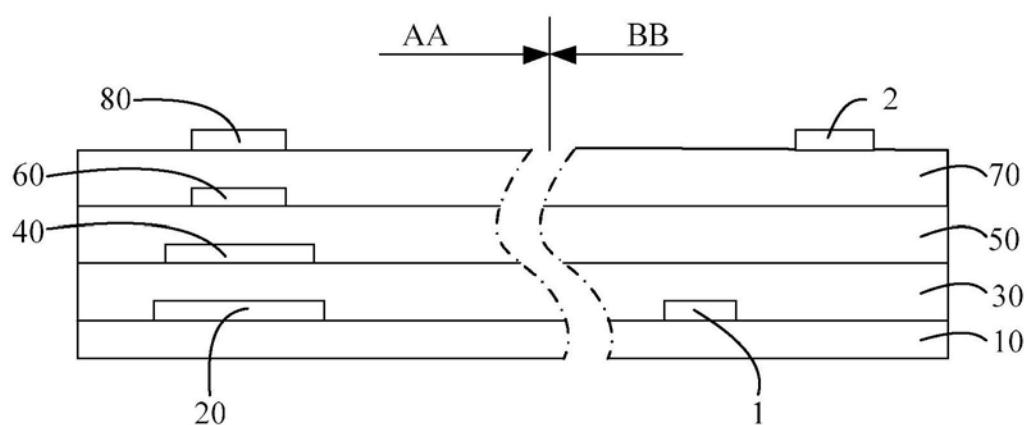

[0018] 图1为本公开一些实施例提供的一种扇出走线结构的结构示意图;

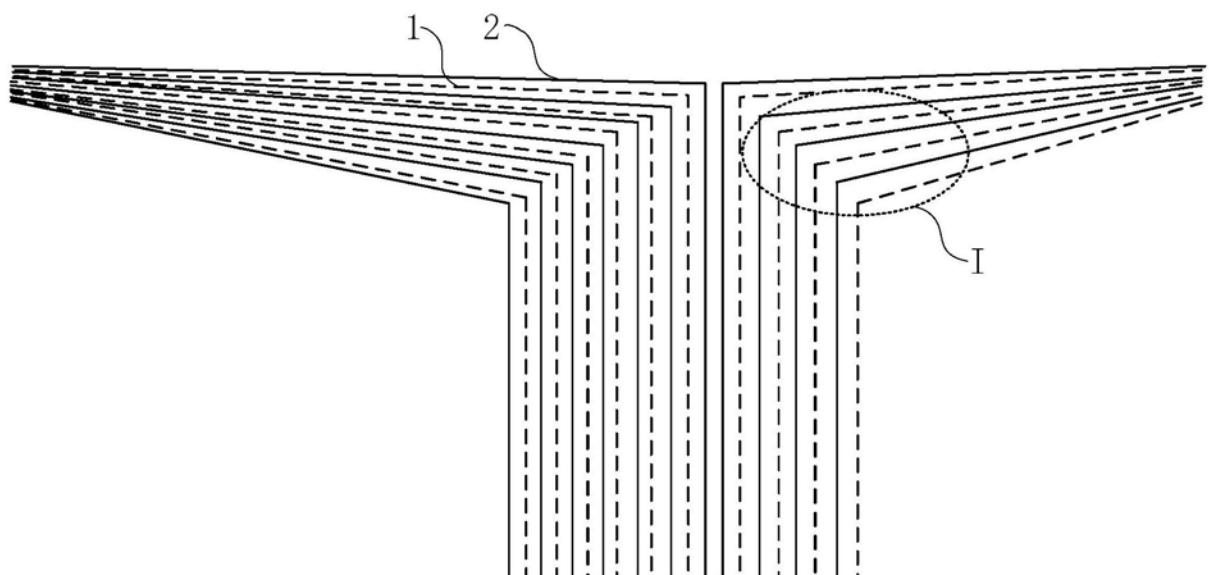

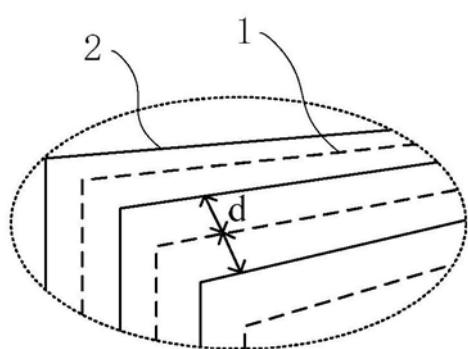

[0019] 图2为本公开一些实施例提供的一种第一走线和第二走线的分布示意图;

[0020] 图3为本公开一些实施例提供的一种显示基板的结构示意图。

## 具体实施方式

[0021] 为便于理解,下面结合说明书附图,对本公开一些实施例提供的技术方案进行详细的描述。显然,所描述的实施例仅仅是所提出的技术方案的一部分实施例,而不是全部的实施例。基于本公开的一些实施例,本领域技术人员所能获得的所有其他实施例,均属于本公开保护的范围。

[0022] 请参阅图1~图3,在本公开一些实施例中,显示基板包括:衬底10、光遮挡(Light Shielding,简称LS)层20和扇出走线结构。光遮挡层20设置于衬底10的表面。扇出走线结构包括绝缘设置的第一走线层和第二走线层。第一走线层和第二走线层中的一者与光遮挡层20同层设置。

[0023] 上述光遮挡层20用于遮挡从衬底10一侧入射至显示基板内的环境光信号,光遮挡层20通常为金属层,即,光遮挡层20采用具有遮光性能的金属材料制作形成,例如钼,但不限于此。此外,可选的,0≤光遮挡层20的光透过率≤10%。

[0024] 上述扇出走线结构中的第一走线层和第二走线层均为金属走线层,即,其采用导电性能良好的金属材料制作形成,例如铝、铜、钼、钛、银、金、钽、钨、铬单质或铝合金等,但不限于此。

[0025] 请继续参阅图3,显示基板还包括:依次层叠设置于光遮挡层20的远离衬底10的一侧的第一绝缘层50、第一导电图案60、第二绝缘层70以及第二导电图案80。第一走线层和第二走线层中的另一者与第二导电图案80同层设置。

[0026] 可选的,第二导电图案80为金属导电图案,即,其采用导电性能良好的金属材料制作形成,例如铝、铜、钼、钛、银、金、钽、钨、铬单质或铝合金等,但不限于此。相应的,第一导电图案60为金属导电图案或非金属导电图案,均可。示例的,第一导电图案60采用导电性能良好的金属材料制作形成,例如铝、铜、钼、钛、银、金、钽、钨、铬单质或铝合金等。

[0027] 上述的“同层设置”可以指采用相同的材料并一次构图工艺制作成型,或是采用不同的材料但二者位于相同的两个膜层之间,或者采用不同的材料并与同一个膜层直接接触。该构图工艺包括光刻工艺,或包括光刻工艺以及刻蚀步骤在内的工艺。所述光刻工艺是指包括成膜(例如化学气相沉积成膜,Chemical Vapor Deposition,简称CVD)、曝光、显影等工艺过程且利用光刻胶、掩模板、曝光机等形成图形的工艺。

[0028] 需要说明的是,在一些示例中,上述显示基板为阵列基板,可应用于OLED显示装置或LCD(Liquid Crystal Display,液晶显示器)显示装置中。阵列基板的衬底10上通常设有多个薄膜晶体管(Thin-Film Transistor,简称TFT)。以下以阵列基板中的TFT为顶栅结构的TFT为例进行详细说明。

[0029] 请继续参阅图3,显示基板还包括:依次层叠设置于光遮挡层20的靠近第一绝缘层50的一侧的缓冲层30和半导体图案40。

[0030] 如此,半导体图案40可以用来形成各TFT的有源层,但不限于此。可选的,有源层在衬底10上的正投影位于光遮挡层20在衬底10上的正投影内,或二者部分重叠。这样利用光遮挡层20遮挡入射至对应有源层的导电沟道的环境光信号,能够确保该有源层所在TFT的电学性能。可选的,半导体图案40采用非晶硅( $\alpha$ -Si)或多晶硅(Poly-Si)材料制作形成。

[0031] 第一导电图案60可以用来形成各TFT的栅极以及对应的栅线等,但不限于此。相应的,第一绝缘层50为栅绝缘层。

[0032] 第二导电图案80可以用来形成各TFT的源极、漏极以及对应的数据线等,但不限于此。相应的,第二绝缘层70为层间绝缘层。

[0033] 上述栅绝缘层、层间绝缘层和缓冲层30可以分别采用氮化硅( $\text{SiN}_x$ )、氧化硅( $\text{SiO}_x$ )或氮氧化硅( $\text{SiN}_x\text{O}_y$ )等材料制作形成,但不限于此。

[0034] 当然,若阵列基板中的TFT为底栅结构的TFT,那么上述半导体图案40与第一导电图案60之间的相对位置可以对应调整。本公开一些实施例对此不再详述。

[0035] 此外,需要补充的是,上述的半导体图案40、第一导电图案60和第二导电图案80是指将其对应的薄膜通过构图工艺图案化之后所形成的图案,以利用所述图案的各部分形成显示基板中的对应结构。

[0036] 可以理解的是,显示基板通常具有显示区AA以及位于显示区AA的至少一侧的周边区BB。如图3所示,光遮挡层20、半导体图案40、第一导电图案60和第二导电图案80位于显示区AA内。扇出走线结构位于周边区BB内。缓冲层30、第一绝缘层50和第二绝缘层70分别位于显示区AA以及周边区BB内。

[0037] 由于扇出走线结构通常位于周边区BB内,用于将显示区AA内的信号线通过走线引出。因此,第一走线1和第二走线2可以分别与对应的信号线电连接。若第一走线1或第二走线2与对应的信号线之间存在绝缘层,则第一走线1或第二走线2穿过形成该绝缘层的过孔与对应的信号线电连接。本公开实施例对信号线的类型及其设置位置不做限定,根据实际需求选择设置即可。

[0038] 在本公开一些实施例中,由于扇出走线结构设置的区域,也即扇出(Fanout)区,相对于显示区AA较小,且扇出走线结构中需要设置的走线数量众多。因此,将第一走线层和第二走线层中的一者与光遮挡层20同层设置,另一者与第二导电图案80同层设置,使得第一走线层和第二走线层之间至少包括缓冲层30、第一绝缘层50和第二绝缘层70,可以确保第一走线层和第二走线层之间沿垂直于衬底10的方向具有较远的距离,也即使得第一走线层和第二走线层之间具有厚度足够的绝缘介质,从而确保第一走线层与第二走线层之间良好绝缘。进而,能够减小第一走线层和第二走线层之间的信号串扰,有效提升显示基板及显示装置的显示效果。

[0039] 示例性的,如图1和图2所示,第一走线层包括多条第一走线1。第二走线层包括多条第二走线2。第一走线1在衬底上的正投影与第二走线2在衬底上的正投影交替间隔排布,可以使得每相邻的两条第一走线1之间、每相邻的两条第二走线2之间均具有合理的间距。

[0040] 此外,可选的,第一走线1的宽度和第二走线2的宽度相等。这样不仅方便于扇出走线结构的制作,还有利于确保扇出走线结构中各走线的阻抗均匀性。

[0041] 值得一提的是,在一些实施例中,第一走线1在衬底10上的正投影与对应的第二走线2在衬底10上的正投影之间的间隔极小值 $d_{min}$ 的取值范围为:0.5μm~1μm。此处,间隔极小值 $d_{min}$ 是指对应间隔所能允许的最小取值。

[0042] 在本公开一些实施例中,扇出走线结构采用如上所述的设置方式,能够在第一走线层和第二走线层之间良好绝缘的前提下,将扇出走线结构的第一走线层中的每条第一走线1与第二走线层中对应第二走线2之间的间隔合理减小,可以对应压缩扇出走线结构的占用空间,从而提升显示基板的屏占比。当然,若在扇出走线结构占用空间不变的情况下,第一走线1与对应第二走线2之间的间隔合理减小,还可以对应加宽第一走线1和第二走线2的宽度,以减小第一走线1和第二走线2的阻抗,从而提升扇出走线结构的阻抗均匀性,进而提升显示基板及显示装置的显示效果。

[0043] 以下以第一走线层与光遮挡层20同层设置,第二走线层与第二导电图案80同层设置为例进行详细说明。

[0044] 在相关技术中,扇出走线结构的第一走线层与第二走线层之间通常仅设有一层绝缘薄膜,即具有较小的绝缘层厚度。由此,为了避免第一走线和对应的第二走线之间产生信号串扰,第一走线1在衬底10上的正投影与对应的第二走线2在衬底10上的正投影之间需要预留一定的间隔,例如为5μm。

[0045] 然而,在本公开一些实施例中,扇出走线结构的第一走线层与第一走线层与光遮挡层20同层设置,第二走线层与第二导电图案80同层设置,使得第一走线层与第二走线层之间可以存在多层绝缘薄膜,即具有较大的绝缘层厚度。由此,第一走线1在衬底10上的正投影与对应的第二走线2在衬底10上的正投影之间的间隔可以从上述的5μm对应减小至1μm,甚至更小。从而可以对应压缩扇出走线结构的占用空间,以提升显示基板的屏占比。

[0046] 当然,若扇出走线结构的占用空间不变,那么第一走线1和第二走线2的宽度,可以对应加宽。例如,第一走线1在衬底10上的正投影与对应的第二走线2在衬底10上的正投影之间的间隔可以从上述的5μm对应减小至1μm时,第一走线1和第二走线2可以同时在其左右两侧分别加宽1μm。从而能够减小第一走线1和第二走线2的阻抗,以提升扇出走线结构的阻抗均匀性,减小信号损耗,进而提升显示基板及显示装置的显示效果。

[0047] 本公开一些实施例提供了一种显示装置。显示装置包括：如上述一些实施例中所述的显示基板。

[0048] 例如，所述显示装置为手机、平板电脑、笔记本电脑、显示器、电视机、数码相框或导航仪等具有显示功能的产品或部件。

[0049] 本公开一些实施例提供的显示装置所能实现的有益效果，与上述一些实施例提供的显示基板所能达到的有益效果相同，在此不做赘述。

[0050] 在上述实施方式的描述中，具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0051] 以上所述，仅为本发明的具体实施方式，但本发明的保护范围并不局限于此，任何熟悉本技术领域的技术人员在本发明揭露的技术范围内，可轻易想到变化或替换，都应涵盖在本发明的保护范围内。因此，本发明的保护范围应以所述权利要求的保护范围为准。

图1

图2

图3

|                |                              |                      |            |

|----------------|------------------------------|----------------------|------------|

| 专利名称(译)        | 显示基板及显示装置                    |                      |            |

| 公开(公告)号        | <a href="#">CN110993677A</a> | 公开(公告)日              | 2020-04-10 |

| 申请号            | CN201911326488.6             | 申请日                  | 2019-12-20 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司                |                      |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司                |                      |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司                |                      |            |

| [标]发明人         | 张洁<br>刘利宾                    |                      |            |

| 发明人            | 张洁<br>刘利宾                    |                      |            |

| IPC分类号         | H01L27/32                    |                      |            |

| CPC分类号         | H01L27/3279                  |                      |            |

| 外部链接           | <a href="#">Espacenet</a>    | <a href="#">Sipo</a> |            |

### 摘要(译)

本公开实施例公开了一种显示基板及显示装置，涉及显示技术领域，用于减小其扇出走线中每相邻两条信号线走线之间的信号串扰，有利于提升显示基板及显示装置的显示效果。所述显示基板包括：衬底、光遮挡层和扇出走线结构。光遮挡层设置于衬底的表面。扇出走线结构包括绝缘设置的第一走线层和第二走线层。第一走线层和第二走线层中的一者与光遮挡层同层设置。本公开实施例提供的显示基板及显示装置用于OLED显示。