(12) 发明专利申请

(10) 申请公布号 CN 105405398 A

(43) 申请公布日 2016. 03. 16

(21) 申请号 201510965326. 2

(22) 申请日 2015. 12. 21

(66) 本国优先权数据

201510543528. 8 2015. 08. 28 CN

(71) 申请人 北京航空航天大学

地址 100191 北京市海淀区学院路 37 号

(72) 发明人 李洪革 张子裕

(51) Int. Cl.

G09G 3/3225(2016. 01)

权利要求书2页 说明书6页 附图4页

(54) 发明名称

一种白平衡可调的AMOLED显示驱动

(57) 摘要

本发明涉及有机发光二极管显示技术领域，公开了一种白平衡可调的AMOLED显示驱动。针对现有AMOLED显示驱动仅能支持单一白平衡点显示的不足，提出了一种白平衡可调的AMOLED显示驱动，该驱动具有两种显示模式：D65模式和D93模式。当图像的白平衡点为D65时，显示驱动工作在D65模式；当图像的白平衡点为D93时，显示驱动工作在D93模式。因此，该驱动可以根据图像的白平衡点调整显示驱动的显示模式，从而实现更好的显示效果。

1. 一种白平衡可调的 AMOLED 显示驱动, 该显示驱动可以根据显示图像的白平衡点调整显示模式, 具有更好的图像再现效果。

2. 根据权利要求 1 所述的白平衡可调的 AMOLED 显示驱动, 具有两种显示模式:D65 模式和 D93 模式。当图像的白平衡点为 D65 时, 显示驱动工作在 D65 模式; 当图像的白平衡点为 D93 时, 显示驱动工作在 D93 模式。所述 AMOLED 显示驱动可以根据图像的白平衡点调整显示模式。

3. 根据权利要求 1 所述的白平衡可调的 AMOLED 显示驱动, 包括:

接口模块, 获取主机发送过来的图像数据或控制命令, 将数据或命令传送给所述控制寄存器组。

图像存储器 (GRAM), 存储一帧 QVGA 尺寸的图像信息, 在无外部图像数据输入时, 可以继续提供图像数据。

控制寄存器组, 获取所述的接口模块发送的图像数据或控制命令, 控制所述显示驱动的工作状态。

时序控制器, 获取所述控制寄存器组发送的命令, 产生控制所述源极驱动器和 AMOLED 屏所需的时序信号。

白平衡调整模块, 根据所述控制寄存器组的控制信号, 调整图像数据, 使得显示驱动工作在 D65 模式或 D93 模式。

源极驱动器, 获取所述白平衡调整模块或图像存储器模块发送的图像数据, 根据所述时序控制器的时序信号, 将图像数据变成相应模拟电压信号并行输出给 AMOLED 屏。

4. 根据权利要求 3 所述的控制寄存器组, 其中的控制寄存器组包括一个索引寄存器, 判断下次写操作的寄存器; 一个接口控制寄存器, 控制接口工作模式的转换和 D65 模式与 D93 模式的转换; 一个查找表写地址寄存器 R, 存储 R 通道查找表的写地址; 一个查找表写地址寄存器 G, 存储 G 通道查找表的写地址; 一个查找表写地址寄存器 B, 存储 B 通道查找表的写地址; 一个 GRAM 写地址寄存器, 存储图像存储器 (GRAM) 的写地址; 一个译码逻辑电路, 获取所述索引寄存器的数据, 结合索引寄存器的值判断下次写操作的寄存器。

5. 根据权利要求 4 所述的接口控制寄存器, 其中的 CLS[1:0] 是 MCU 接口控制位, 当 CLS[1:0] = 2'b00 时, MCU 接口工作在 18bit 模式, 此时数据 / 命令总线的宽度为 18bit; 当 CLS[1:0] = 2'b01 时, MCU 接口工作在 16bit 模式, 此时数据 / 命令总线的宽度为 16bit; 当 CLS[1:0] = 2'b10 时, MCU 接口工作在 9bit 模式, 此时数据 / 命令总线的宽度为 9bit; 当 CLS[1:0] = 2'b11 时, MCU 接口工作在 8bit 模式, 此时数据 / 命令总线的宽度为 8bit。接口控制寄存器的 ena\_RGB 位是 RGB 接口使能信号。当 ena\_RGB 为低电平时, 接口模块选择 MCU 接口或 SPI 接口, 屏幕显示所需的场行同步信号由时序控制器提供; 当 ena\_RGB 为高电平时, 接口模块选择 RGB 接口, 此时场行同步信号由 RGB 接口提供。接口控制寄存器的 POS 位是 RGB 接口模式选择信号。当 POS 为高电平时, RGB 接口工作在 18bit 模式, 此时 RGB 接口在时钟上升沿每次传输 18bit 数据, 传送一组 RGB 数据需要一个周期; 当 POS 为低电平时, RGB 接口工作在 6bit 模式, 此时 RGB 接口在时钟上升沿一次传输 6bit 数据, 传送一组 RGB 数据需要三个周期。接口控制寄存器的 Ctrl 位是 D65 模式和 D93 模式选择位。以原始图像为 D65 白平衡点为例, 当选择信号 Ctrl 为高电平时, 显示驱动工作在 D65 模式; 当选择信号 Ctrl 为低电平时, 显示驱动工作在 D93 模式。

6. 根据权利要求 3 所述的白平衡调整模块,其中包括一个 R 通道查找表,一个 G 通道查找表,一个 B 通道查找表和一个数据选择器。所述 R 通道查找表、G 通道查找表、B 通道查找表获取接口模块传来的图像数据,按照各自通道查找表的内容将原始数据改为另一白平衡点下的数据。所述数据选择器用来选择输出给图像存储器和源极驱动器的数据。以原始图像为 D65 白平衡点为例,当选择信号 Ctrl1 为高电平时,选择原始数据 R[5:0]、G[5:0]、B[5:0] 进行输出,此时显示驱动工作在 D65 模式;当选择信号 Ctrl1 为低电平时,选择查找表数据 R' [5:0]、G' [5:0]、B' [5:0] 进行输出,此时显示驱动工作在 D93 模式。

7. 根据权利要求 3 所述的控制寄存器组,基于控制寄存器组可以写 R/G/B 通道查找表的值,使得该显示驱动适用于多种 AMOLED 屏。具体操作如下:当索引寄存器中 ID[3:0] = 4'b0101 时,下一个写操作将把数据写入权利要求 6 所述的 R 通道查找表,其对应的写地址由权利要求 4 所述的查找表写地址寄存器 R 给出;当索引寄存器中 ID[3:0] = 4'b0110 时,下一个写操作将把数据写入权利要求 6 所述的 G 通道查找表,其对应的写地址由权利要求 4 所述的查找表写地址寄存器 G 给出;当索引寄存器中 ID[3:0] = 4'b0111 时,下一个写操作将把数据写入权利要求 6 所述的 B 通道查找表,其对应的写地址由权利要求 4 所述的查找表写地址寄存器 B 给出。

8. 根据权利要求 6 所述的 R/G/B 通道查找表,其中各通道的查找表的值按照以下算法确定:

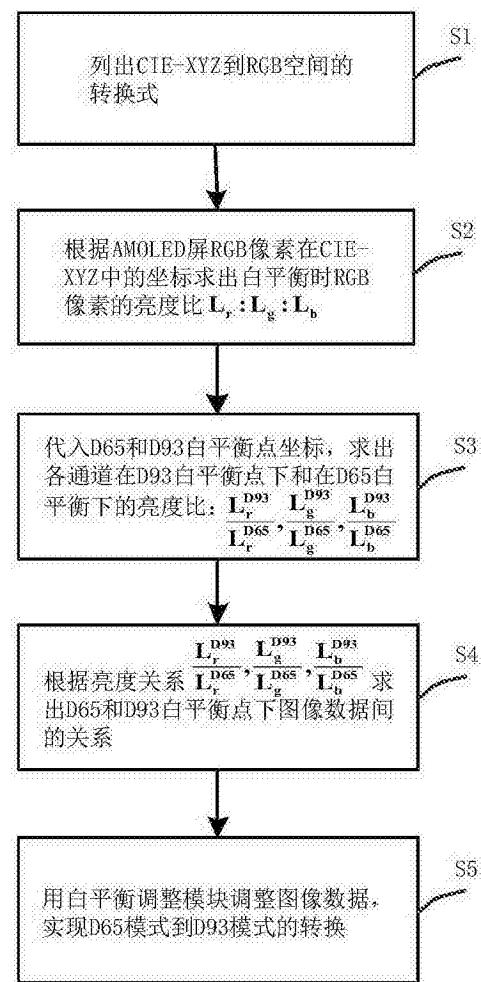

S1. 列出 CIE-XYZ 空间到 RGB 空间的转换公式;

S2. 根据 AMOLED 屏的 RGB 像素在 CIE-XYZ 空间中的坐标,求出自平衡时 RGB 像素的亮度比: $L_r:L_g:L_b$ 。

S3. 代入 D65 和 D93 白平衡点在 CIE-XYZ 空间中的坐标,求出各通道在 D93 白平衡点下

和在 D65 白平衡点下的亮度比: $\frac{L_r^{D93}}{L_r^{D65}}, \frac{L_g^{D93}}{L_g^{D65}}, \frac{L_b^{D93}}{L_b^{D65}}$ 。

S4. 根据亮度关系 $\frac{L_r^{D93}}{L_r^{D65}}, \frac{L_g^{D93}}{L_g^{D65}}, \frac{L_b^{D93}}{L_b^{D65}}$ 求出在 D65 和 D93 白平衡点下图像数据之间的关系。

S5. 用权利要求 3 所述的白平衡调整模块调整图像数据,从而实现 D65 模式到 D93 模式的转换。

## 一种白平衡可调的 AMOLED 显示驱动

### 技术领域

[0001] 本发明涉及有机发光二极管显示技术领域,具体涉及一种白平衡可调的 AMOLED 显示屏驱动。

### 背景技术

[0002] AMOLED(Active-matrix organic light-emitting diode, 有源矩阵有机发光二极管),是一种广泛应用于电视和移动设备中的显示技术。其中 AM 是指有该有机发光显示器件 (OLED) 是主动发光器件。相比现在的主流平板显示技术如薄膜晶体管液晶显示器等, OLED 具有高对比度,低功耗,视角宽,体积薄等优点,是目前平板显示技术中受到关注最多的技术之一。

[0003] AMOLED 显示的白色是由红绿蓝三基色合成的,调整红绿蓝的亮度比可以获得相应的白平衡。由于不同地区人们对白色的感觉并不相同,因此不同的国家采用了不同的白平衡参考点。在电视应用领域,欧美等国家采用色温为 6500K 的白点 (D65) 作为显示的白平衡点。而亚洲国家如日本等常采用色温为 9300K 的白点 (D93) 作为显示的白平衡点。在计算机应用领域,经常采用两种色温的白平衡点 :6500K, 9300K。为了更好的再现原始图像,屏幕的白平衡点需要和图像的白平衡点一致。而对于传统的显示驱动来说,其只能使得屏幕显示一个标准的白平衡点。为了使得屏幕能显示不同的白平衡点,需要驱动芯片具有白平衡调整的功能。

### 发明内容

[0004] 本发明针对现有 AMOLED 显示驱动仅能支持单一白平衡点显示的不足,提出了一种白平衡可调的 AMOLED 显示驱动,该驱动具有两种显示模式 :D65 模式和 D93 模式。当图像的白平衡点为 D65 时,显示驱动工作在 D65 模式;当图像的白平衡点为 D93 时,显示驱动工作在 D93 模式。因此,该驱动可以根据图像的白平衡点调整显示驱动的显示模式,从而实现更好的显示效果。

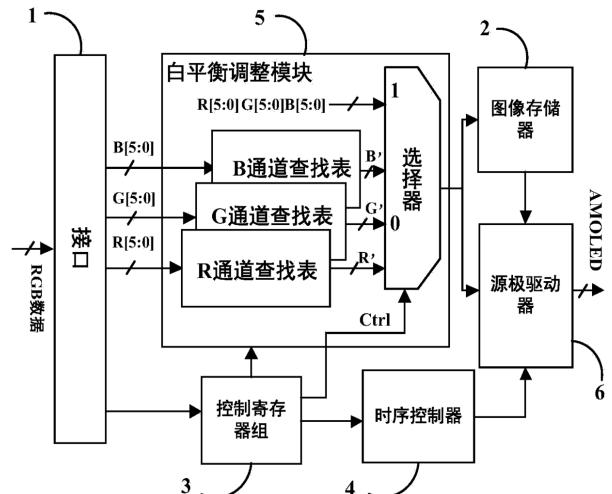

[0005] 本发明提供的一种白平衡可调的 AMOLED 显示驱动,包括以下几个结构:

[0006] 接口模块 1,获取主机发送过来的图像数据或控制命令,将数据或命令传送给所述控制寄存器组。

[0007] 图像存储器 2(GRAM),存储一帧 QVGA 尺寸的图像信息。在无外部图像数据输入时,GRAM 可以继续提供图像数据。

[0008] 控制寄存器组 3,获取所述的接口模块发送的图像数据或控制命令,控制所述显示驱动的工作状态。

[0009] 时序控制器 4,获取所述控制寄存器组发送的控制信号,产生控制所述源极驱动器和 AMOLED 屏所需的时序信号。

[0010] 白平衡调整模块 5,根据所述控制寄存器组的控制信号 Ctrl1,调整图像数据,使得显示 驱动工作在 D65 模式或 D93 模式。

[0011] 源极驱动器 6, 获取所述白平衡调整模块或图像存储器模块发送的图像数据, 根据所述时序控制器的时序信号, 将图像数据变成相应模拟电压信号并行输出给 AMOLED 屏。

[0012] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述接口模块包括 MCU 并行接口、串行 SPI 接口和 RGB 接口。其中 MCU 并行接口有 18-/16-/9-/8-bit 四种模式, RGB 接口有 18bit 和 6bit 两种模式。

[0013] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述图像存储器可以使得显示静态图像时, 不需要外部提供图像数据, 从而降低显示驱动的功耗。

[0014] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述控制寄存器组包括一个索引寄存器, 判断下次写操作的寄存器;一个接口控制寄存器, 控制接口工作模式的转换和 D65 模式与 D93 模式的转换;一个查找表写地址寄存器 R, 存储 R 通道查找表的写地址;一个查找表写地址寄存器 G, 存储 G 通道查找表的写地址;一个查找表写地址寄存器 B, 存储 B 通道查找表的写地址;一个图像存储器 (GRAM) 写地址寄存器, 存储图像存储器 (GRAM) 的写地址;一个译码逻辑电路, 获取所述索引寄存器的值, 判断下次写操作的寄存器。

[0015] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述时序控制器包括场行同步信号发生器和源极驱动控制器。所述场行同步信号发生器工作在驱动使用 MCU 接口和 SPI 接口时, 用于产生帧同步信号和行同步信号。当驱动使用 RGB 接口时, 场行同步信号发生器不工作, 此时帧同步信号和行同步信号由 RGB 接口输入;所述的源极驱动控制器, 获取所述场行同步信号发生器或 RGB 接口传来的帧同步信号和行同步信号, 根据帧行同步信号产生所述源极驱动器需要的时序信号。

[0016] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述白平衡调整模块包括一个 R 通道查找表, 一个 G 通道查找表, 一个 B 通道查找表和一个数据选择器。所述 R 通道查找表、G 通道查找表、B 通道查找表获取接口模块传来的图像数据, 按照各自通道查找表的内容将原始数据改为另一白平衡点下的图像数据。所述数据选择器用来选择输出给图像存储器和源极驱动器的数据。以原始图像的白平衡点为 D65 举例, 当选择信号 Ctrl 为高电平时, 选择原始数据 R[5:0]、G[5:0]、B[5:0] 进行输出, 此时显示驱动工作在 D65 模式;当选择信号 Ctrl 为低电平时, 选择查找表数据 R' [5:0]、G' [5:0]、B' [5:0] 进行输出, 此时显示驱动工作在 D93 模式。

[0017] 所述的一种白平衡可调的 AMOLED 显示驱动, 所述源极驱动器获取串行的图像数据, 并行输出模拟电压信号给 AMOLED 屏的源极端口。当显示动态图像时, 所述源极驱动器从所述白平衡调整模块获取图像数据;当显示静态图像时, 所述源极驱动器从所述图像存储器获取图像数据。

[0018] 本发明的上述技术方案相比现有技术具有以下优点:

[0019] (1) 可以根据图像的白平衡点调整显示驱动的显示模式, 具有更好的图像再现效果;

[0020] (2) 由于本方案中的多接口设计, 可以使得外部主机通过接口模块随时修改查找表的值, 因此本显示驱动可适用于多种 AMOLED 屏。

## 附图说明

[0021] 图 1 是本发明的白平衡可调的 AMOLED 显示驱动总体框架图;

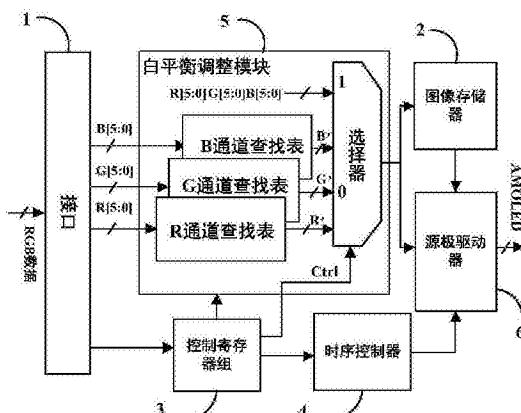

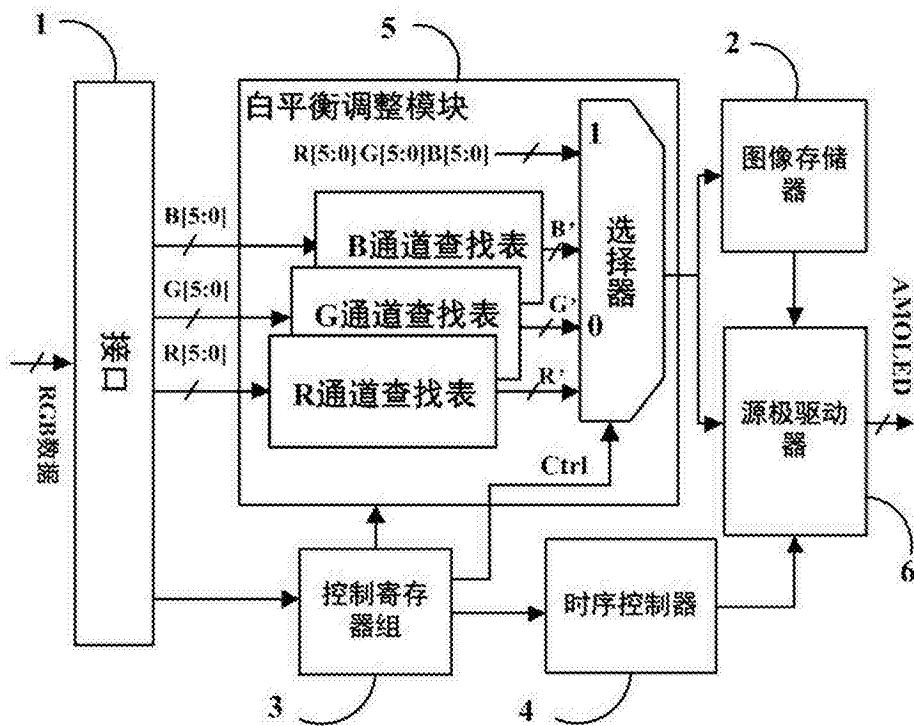

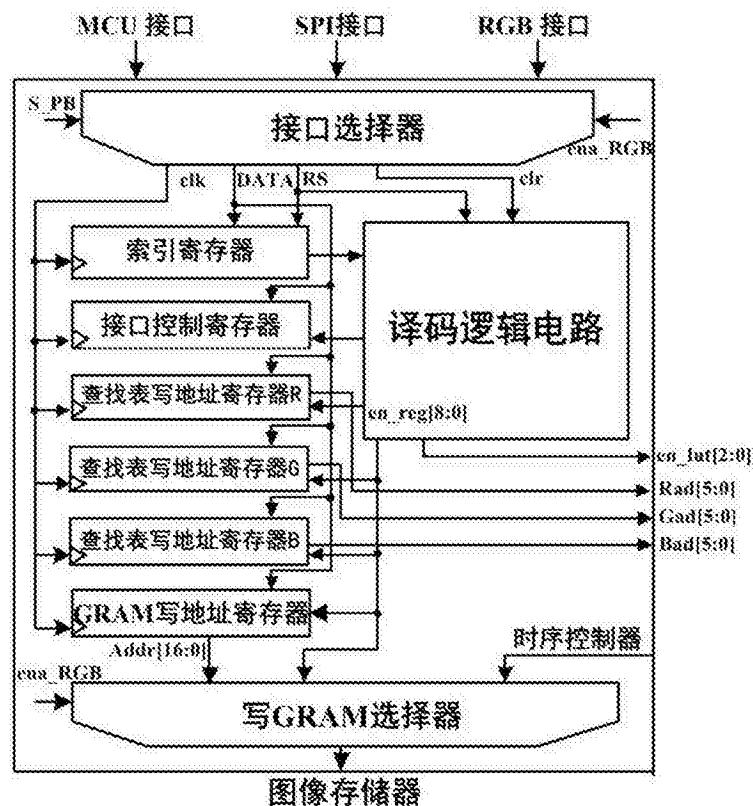

- [0022] 图 2 是本发明中的控制寄存器组结构示意图；

[0023] 图 3A 至图 3F 是本发明的控制寄存器组中的各个寄存器的结构示意图；

[0024] 图 4 是本发明中的白平衡调整方案示意图；

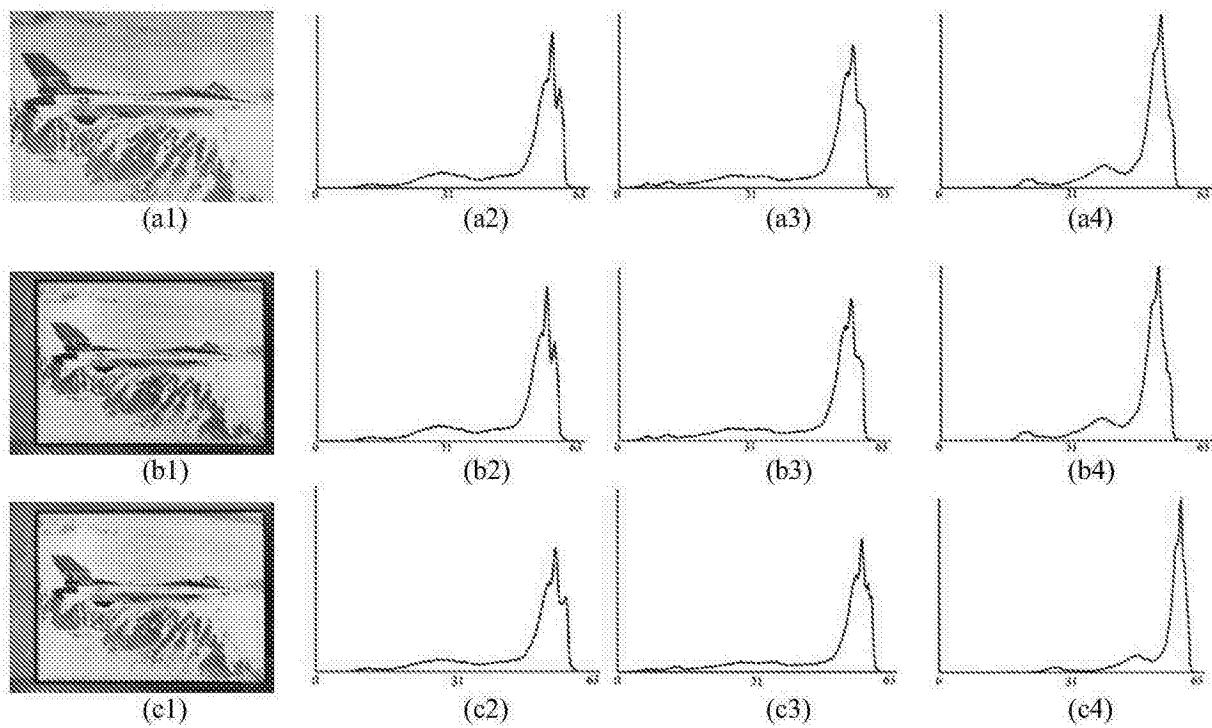

[0025] 图 5a(1) 是具有 D65 白平衡点的原始图像；图 5a(2)、图 5a(3)、图 5a(4) 分别是图 5a(1) 的 R、G、B 三个通道的灰度等级直方图。

[0026]

[0027] 图 5b(1) 是 D65 白平衡点图像在本发明的 D65 模式下的显示效果图；图 5b(2)、图 5b(3)、图 5b(4) 分别是图 5b(1) 的 R、G、B 三个通道的灰度等级直方图。

[0028] 图 5c(1) 是 D65 白平衡点图像在本发明的 D93 模式下的显示效果图；图 5c(2)、图 5c(3)、图 5c(4) 分别是图 5c(1) 的 R、G、B 三个通道的灰度等级直方图。

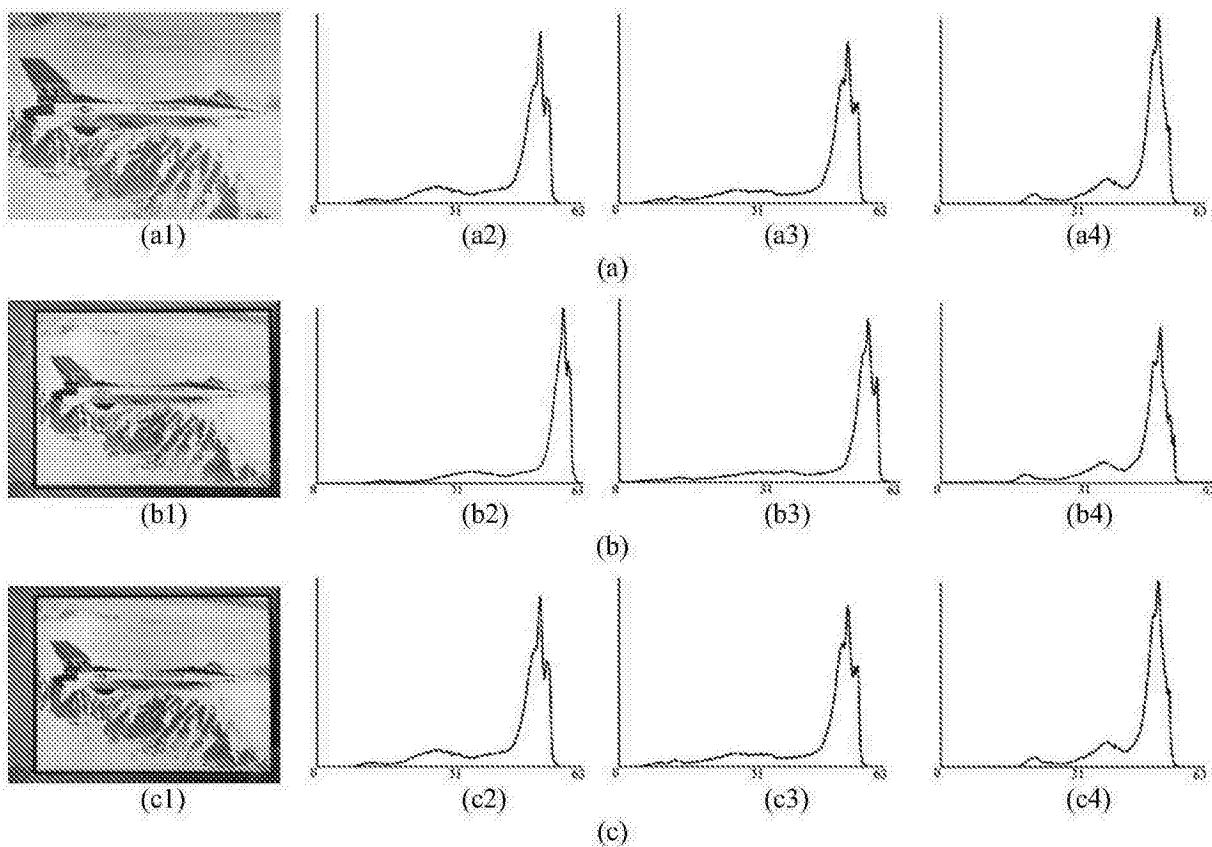

[0029] 图 6a(1) 是具有 D93 白平衡点的原始图像；图 6a(2)、图 6a(3)、图 6a(4) 分别是图 6a(1) 的 R、G、B 三个通道的灰度等级直方图。

[0030] 图 6b(1) 是 D93 白平衡点图像在本发明的 D65 模式下的显示效果图；图 6b(2)、图 6b(3)、图 6b(4) 分别是图 6b(1) 的 R、G、B 三个通道的灰度等级直方图。

[0031] 图 6c(1) 是 D93 白平衡点图像在本发明的 D93 模式下的显示效果图；图 6c(2)、图 6c(3)、图 6c(4) 分别是图 6c(1) 的 R、G、B 三个通道的灰度等级直方图。

## 具体实施方式

- [0032] 下面将结合附图和实施例对本发明做进一步的详细说明。

[0033] 请参考图 2，图 2 为本发明一实施例的控制寄存器组示意图。所述接口选择器用于选择当前有效的接口：当 S\_PB 为高电平时，选择 MCU 接口为当前有效的接口；当 S\_PB 为低电平时，选择 SPI 接口为当前有效的接口；当 ena\_RGB 为高电平时，选择 RGB 接口为有效接口；当 ena\_RGB 为低电平时，RGB 接口无效，此时由所述时序控制器提供场行同步信号。以 S\_PB 高电平为例，此时外部主机通过 MCU 接口发送图像数据或命令。接口选择器选择 MCU 接口的 4 路信号作为输出：clk 时钟信号，DATA[17:0] 数据或命令信号，RS 寄存器选择信号，clr 清零信号。当主机通过 MCU 接口发送图像数据或命令时，首先发送写索引寄存器命令。此时 RS 为低电平，译码逻辑电路的输出 en\_reg[8:0] 全为低电平，即索引寄存器写使能，而接口控制寄存器、查找表写地址寄存器 R、查找表写地址寄存器 G、查找表写地址寄存器 B 和 GRAM 写地址寄存器写无效，图像存储器 GRAM 写无效，R 通道查找表写无效，G 通道查找表写无效，B 通道查找表写无效。数据 DATA[17:0] 在 clk 时钟信号上升沿时将下次写寄存器的地址写入索引寄存器中。索引寄存器命令发送完成后，将 RS 置为高电平，此时索引寄存器写无效，译码逻辑电路根据索引寄存器当前的值输出寄存器写使能信号 en\_reg[8:0]。当 en\_reg[8:0] = 9' b000000001 时，接口控制寄存器写有效；当 en\_reg[8:0] = 9' b000000010 时，查找表写地址寄存器 R 写有效；当 en\_reg[8:0] = 9' b000000100 时，查找表写地址寄存器 G 写有效；当 en\_reg[8:0] = 9' b000001000 时，查找表写地址寄存器 B 写有效；当 en\_reg[8:0] = 9' b000010000 时，图像存储器 (GRAM) 写地址寄存器写有效。当 en\_reg[8:0] = 9' b000100000 时，图像存储器 GRAM 写有效；当 en\_reg[8:0] = 9' b001000000 时，R 通道查找表写有效，此时 en\_lut[2:0] = 3' b001；当 en\_reg[8:0] = 9' b010000000 时，G 通道查找表写有效，此时 en\_lut[2:0] = 3' b010；当 en\_reg[8:0] = 9' b100000000 时，B 通

道查找表写有效,此时 en\_lut[2:0] = 3'b100 ;译码逻辑电路输出稳定后,数据 DATA[17:0] 在下一个 clk 时钟信号上升沿时存入写有效的寄存器中。

[0034] 以下请参考图 3A, 图 3A 描述了索引寄存器的内容。当 RS 为低电平时,索引寄存器写有效,此时数据存入 IB15 至 IB0 中。其中 ID[3:0] 是有效信号位,其值决定了下个写操作的访问对象。IB15 至 IB4 是无效信号位。当主机写数据或者命令时,首先需要写索引寄存器的值,以确定下次写入的数据或命令要存入哪个寄存器中。

[0035] 以下请参考图 3B, 图 3B 描述了接口控制寄存器的内容。当索引寄存器中 ID[3:0] = 4'b0001 时,下一个写入的寄存器为接口控制寄存器。接口控制寄存器的 CLS[1:0] 是 MCU 接口控制位,当 CLS[1:0] = 2'b00 时,MCU 接口工作在 18bit 模式,此时数据 / 命令总线的宽度为 18bit ;当 CLS[1:0] = 2'b01 时,MCU 接口工作在 16bit 模式,此时数据 / 命令总线的宽度为 16bit ;当 CLS[1:0] = 2'b10 时,MCU 接口工作在 9bit 模式,此时数据 / 命令总线的宽度为 9bit ;当 CLS[1:0] = 2'b11 时,MCU 接口工作在 8bit 模式,此时数据 / 命令总线的宽度为 8bit。接口控制寄存器的 ena\_RGB 位是 RGB 接口使能信号。当 ena\_RGB 为低电平时,接口模块选择 MCU 接口或 SPI 接口,显示所需的场行同步信号由时序控制器提供;当 ena\_RGB 为高电平时,接口模块选择 RGB 接口,此时场行同步信号由 RGB 接口提供。接口控制寄存器的 POS 位是 RGB 接口模式选择信号。当 POS 为高电平时,RGB 接口工作在 18bit 模式,此时 RGB 接口在时钟上升沿每次传输 18bit 数据,传送一组 RGB 数据需要一个周期;当 POS 为低电平时,RGB 接口工作在 6bit 模式,此时 RGB 接口在时钟上升沿一次传输 6bit 数据,传送一组 RGB 数据需要三个周期。接口控制寄存器的 Ctrl1 位是 D65 模式和 D93 模式选择位。以原始图像为 D65 白平衡点为例,当选择信号 Ctrl1 为高电平时,选择原始数据 R[5:0]、G[5:0]、B[5:0] 进行输出,此时显示驱动工作在 D65 模式;当选择信号 Ctrl1 为低电平时,选择查找表数据 R'[5:0]、G'[5:0]、B'[5:0] 进行输出,此时显示驱动工作在 D93 模式。

[0036] 以下请同时参考图 3C, 图 3D 及图 3E。图 3C 描述了查找表地址寄存器 R 的内容。当索引寄存器中 ID[3:0] = 4'b0010 时,下一个写入的寄存器为查找表地址寄存器 R。其中 IB[15:6] 是无效数据位, Rad[5:0] 存储了将要写入数据的 R 查找表的地址。对于 R 通道来说,输入的图像数据位宽为 6bit,因此需要 64 组寄存器作为 R 通道的查找表。图 3D 和图 3E 分别描述了查找表地址寄存器 G 和查找表地址寄存器 B 的内容,各位代表的意义和查找表地址寄存器 R 类似,在此不再赘述。

[0037] 以下请参考图 3F, 图 3F 描述了 GRAM 写地址寄存器的内容。当索引寄存器中 ID[3:0] = 4'b1000 时,下一个写入的寄存器为 GRAM 写地址寄存器。Addr[16:0] 存储了图像存储器 GRAM 的写地址。对于一幅 QVGA 尺寸的图像来说,一帧数据需要占用 240\*320 = 76800 个 18bit 寄存器,而 Addr[16:0] 可寻址 131072 个寄存器,因此可以满足存储一帧 QVGA 尺寸图像的需求。

[0038] 除了图 3B 至图 3F 所述的五个寄存器之外,图 2 所述的控制寄存器组还可以写查找表数据。请参考图 2 以及图 1,当索引寄存器中 ID[3:0] = 4'b0101 时,下一个写操作将把数据写入图 1 中的 R 通道查找表,其对应的写地址由图 2 中的查找表写地址寄存器 R 给出;当索引寄存器中 ID[3:0] = 4'b0110 时,下一个写操作将把数据写入图 1 中的 G 通道查找表,其对应的写地址由图 2 中的查找表写地址寄存器 G 给出;当索引寄存器中 ID[3:0]

= 4'b0111 时,下一个写操作将把数据写入图 1 中的 B 通道查找表,其对应的写地址由图 2 中的查找表写地址寄存器 B 给出。

[0039] 除了图 3B 至图 3F 所述的五个寄存器之外,图 2 所述的控制寄存器组还可以写图像存储器 GRAM 中的数据。请参考图 1、图 2 和图 3,当所以寄存器中 ID[3:0] = 4'b1001 时,下一个写操作将把数据写入图 1 中的图像存储器,其对应的写地址由图 2 中的 GRAM 写地址寄存器给出。

[0040] 图 1、图 2 和图 3 描述了本发明所述白平衡可调的 AMOLED 显示驱动,该驱动不仅可以驱动屏幕的显示,而且可以根据图像的白平衡点调整该驱动的显示模式,从而获得更好的图像显示效果。在实际应用中,需要通过计算确定 RGB 通道查找表的值。

[0041] 图 4 描述了计算 RGB 通道查找表值的步骤。为了计算 D65 模式和 D93 模式下数据间的关系,首先需要确定在 D65 显示模式和 D93 显示模式下的亮度关系。然后根据伽马校正原理,可以得出 D65 显示模式和 D93 显示模式下图像数据的关系。最后,通过白平衡调整电路实现图像数据的调整。下面对白平衡调整方法做具体介绍。

[0042] S1 :CIE-XYZ 空间到 RGB 空间的转换公式如下 :

[0043]

$$\begin{bmatrix} X \\ Y \\ Z \end{bmatrix} = \begin{bmatrix} X_r & X_g & X_b \\ Y_r & Y_g & Y_b \\ Z_r & Z_g & Z_b \end{bmatrix} \begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} C_r x_r & C_g x_g & C_b x_b \\ C_r y_r & C_g y_g & C_b y_b \\ C_r z_r & C_g z_g & C_b z_b \end{bmatrix} \begin{bmatrix} R \\ G \\ B \end{bmatrix} \quad (1)$$

[0044] 式 (1) 中  $X_k, Y_k, Z_k, k \in \{r, g, b\}$  是 RGB 像素在 CIE-XYZ 空间下的三刺激值。其中  $C_r = X_r + Y_r + Z_r$ ,  $C_g = X_g + Y_g + Z_g$ ,  $C_b = X_b + Y_b + Z_b$ 。而  $(x_k, y_k, z_k), k \in \{r, g, b\}$  是 RGB 像素在 CIE-XYZ 空间下的坐标值。

[0045] S2 :由于 RGB 像素在 CIE-XYZ 空间的坐标值是已知的,可由式 (1) 求出  $C_r, C_g$  和  $C_b$  的值 :

[0046]

$$\begin{bmatrix} C_r \\ C_g \\ C_b \end{bmatrix} = A^{-1} \begin{bmatrix} x_0 \\ y_0 \\ z_0 \end{bmatrix} = \frac{1}{|A|} \begin{bmatrix} (y_g z_b - y_b z_g)x_0 + (x_b z_g - x_g z_b)y_0 \\ (x_g y_b - x_b y_g)z_0 \\ (y_b z_r - y_r z_b)x_0 + (x_r z_b - x_b z_r)y_0 \\ (x_b y_r - x_r y_b)z_0 \\ (y_r z_g - y_g z_r)x_0 + (x_g z_r - x_r z_g)y_0 \\ (x_r y_g - x_g y_r)z_0 \end{bmatrix} = \begin{bmatrix} A_1 x_0 + B_1 y_0 + C_1 z_0 \\ A_2 x_0 + B_2 y_0 + C_2 z_0 \\ A_3 x_0 + B_3 y_0 + C_3 z_0 \end{bmatrix}$$

[0047] 因为 CIE-XYZ 空间中仅有 Y 分量表示亮度,因此白平衡时 RGB 像素的亮度比为 :

[0048]  $L_r : L_g : L_b = C_r y_r : C_g y_g : C_b y_b \quad (3)$

[0049]  $= (A_1 x_0 + B_1 y_0 + C_1 z_0) : (A_2 x_0 + B_2 y_0 + C_2 z_0) : (A_3 x_0 + B_3 y_0 + C_3 z_0)$

[0050] 在式 (3) 中,  $A_k, B_k, C_k (k = 1, 2, 3)$  对于给定屏幕都是已知量。

[0051] S3 :若以 D65 白平衡点到 D93 白平衡点转换为例,由式 (3) 代入 D65 的坐标

[0052]  $(0.313, 0.329, 0.358)$  和 D93 的坐标  $(0.283, 0.297, 0.420)$  可以得出相应色素的亮度比为 :

[0053]

$$\begin{cases} \frac{L_r^{D93}}{L_r^{D65}} = \frac{(0.283A_1 + 0.297B_1 + 0.42C_1)(0.313A_3 + 0.329B_3 + 0.358C_3)}{(0.283A_3 + 0.297B_3 + 0.42C_3)(0.313A_1 + 0.329B_1 + 0.358C_1)} \\ \frac{L_g^{D93}}{L_g^{D65}} = \frac{(0.283A_2 + 0.297B_2 + 0.42C_2)(0.313A_3 + 0.329B_3 + 0.358C_3)}{(0.283A_3 + 0.297B_3 + 0.42C_3)(0.313A_2 + 0.329B_2 + 0.358C_2)} \\ \frac{L_b^{D93}}{L_b^{D65}} = 1 \end{cases}$$

[0054] S4 :由于亮度与数据近似成线性关系 :

[0055]  $L = k(63 - D)$

[0056] 结合 S3 得出的 D65 和 D93 白平衡点下 RGB 像素的亮度关系,可以得到 D65 和 D93 白平衡点下图像数据的关系 :

[0057]

$$\begin{cases} D'_r = \frac{L_r^{D93}}{L_r^{D65}} D_r + 63 \left(1 - \frac{L_r^{D93}}{L_r^{D65}}\right) \\ D'_g = \frac{L_g^{D93}}{L_g^{D65}} D_g + 63 \left(1 - \frac{L_g^{D93}}{L_g^{D65}}\right) \\ D'_b = D_b \end{cases} \quad (4)$$

[0058] 式 (4) 中,  $D'_r, D'_g, D'_b \in [0, 63]$  是 D93 白平衡点下的图像数据,  $D_r, D_g, D_b \in [0, 63]$  是 D65 白平衡点下的图像数据。

[0059] S5 :得到不同白平衡点的图像数据关系后,需要利用硬件电路进行数据的调整。本发明采用了白平衡调整模块调整图像数据,以有效显示不同白平衡点下的图像。

[0060] 图 5 是白平衡点为 D65 的图像在本发明所述方案下显示的效果图。图 5(a1)、图 5(a2)、图 5(a3) 和图 5(a4) 分别是白平衡点为 D65 的原始图片及其 R、G、B 通道的灰度直方图。图 5b(1) 是 D65 白平衡点图像在本发明的 D65 模式下的显示效果图;图 5b(2)、图 5b(3)、图 5b(4) 分别是图 5b(1) 的 R、G、B 三个通道的灰度等级直方图。图 5c(1) 是 D65 白平衡点图像在本发明的 D93 模式下的显示效果图;图 5c(2)、图 5c(3)、图 5c(4) 分别是图 5c(1) 的 R、G、B 三个通道的灰度等级直方图。通过对比图片及其直方图可知, D65 模式可以很好的再现原始图像,而 D93 模式则会使得图像显示偏蓝。

[0061] 图 6 是白平衡点为 D93 的图像在本发明所述方案下显示的效果图。图 6(a1)、图 6(a2)、图 6(a3) 和图 6(a4) 分别是白平衡点为 D93 的原始图片及其 R、G、B 通道的灰度直方图。图 6b(1) 是 D93 白平衡点图像在本发明的 D65 模式下的显示效果图;图 6b(2)、图 6b(3)、图 6b(4) 分别是图 6b(1) 的 R、G、B 三个通道的灰度等级直方图。图 6c(1) 是 D93 白平衡点图像在本发明的 D93 模式下的显示效果图;图 6c(2)、图 6c(3)、图 6c(4) 分别是图 6c(1) 的 R、G、B 三个通道的灰度等级直方图。通过对比图片及其直方图可知, D93 模式可以很好的再现原始图像,而 D65 模式则会使得图像显示偏红。

[0062] 综上所述,本发明提供了一种白平衡可调的 AMOLED 显示驱动方案。通过将输入的图像数据按照本发明所述的步骤进行修改,使得 AMOLED 显示屏可以有效的显示不同白平衡点下的图像。由于本方案中提供了多种接口,可使得外部主机通过接口随时修改查找表的值,因此本方案适用于多种 AMOLED 屏。

图 1

图 2

| 寄存器名称 | 地址   | TB15 | TB14 | TB13 | TB12 | TB11 | TB10 | TB9 | TB8 | TB7 | TB6 | TB5 | TB4 | TB3 | TB2 | TB1 | TB0 |     |

|-------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 索引寄存器 | RS=0 | X    | X    | X    | X    | X    | X    | X   | X   | X   | X   | X   | X   | X   | ID3 | ID2 | ID1 | ID0 |

图 3A

| 寄存器名称   | 地址   | TB15 | TB14 | TB13    | TB12 | TB11 | TB10 | TB9 | TB8 | TB7 | TB6 | TB5 | TB4 | TB3 | TB2 | TB1 | TB0 |

|---------|------|------|------|---------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 接口控制寄存器 | 0x01 | CLS1 | CLS0 | ena_RGB | POS  | Ctrl | X    | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   |

图 3B

| 寄存器名称       | 地址   | TB15 | TB14 | TB13 | TB12 | TB11 | TB10 | TB9 | TB8 | TB7 | TB6 | TB5   | TB4   | TB3   | TB2   | TB1   | TB0   |

|-------------|------|------|------|------|------|------|------|-----|-----|-----|-----|-------|-------|-------|-------|-------|-------|

| 查找表写地址寄存器 R | 0x02 | X    | X    | X    | X    | X    | X    | X   | X   | X   | X   | Rad 5 | Rad 4 | Rad 3 | Rad 2 | Rad 1 | Rad 0 |

图 3C

| 寄存器名称       | 地址   | TB15 | TB14 | TB13 | TB12 | TB11 | TB10 | TB9 | TB8 | TB7 | TB6 | TB5   | TB4   | TB3   | TB2   | TB1   | TB0   |

|-------------|------|------|------|------|------|------|------|-----|-----|-----|-----|-------|-------|-------|-------|-------|-------|

| 查找表写地址寄存器 G | 0x03 | X    | X    | X    | X    | X    | X    | X   | X   | X   | X   | Gad 5 | Gad 4 | Gad 3 | Gad 2 | Gad 1 | Gad 0 |

图 3D

| 寄存器名称       | 地址   | TB15 | TB14 | TB13 | TB12 | TB11 | TB10 | TB9 | TB8 | TB7 | TB6 | TB5   | TB4   | TB3   | TB2   | TB1   | TB0   |

|-------------|------|------|------|------|------|------|------|-----|-----|-----|-----|-------|-------|-------|-------|-------|-------|

| 查找表写地址寄存器 B | 0x04 | X    | X    | X    | X    | X    | X    | X   | X   | X   | X   | Bad 5 | Bad 4 | Bad 3 | Bad 2 | Bad 1 | Bad 0 |

图 3E

| 寄存器名称       | 地<br>址 | TB16    | TB15    | TB14    | TB13    | TB12    | TB11    | TB10    | TB9    | TB8    | TB7    | TB6    | TB5    | TB4    | TB3    | TB2    | TB1    | TB0    |

|-------------|--------|---------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| GRAM 写地址寄存器 | 0x08   | Addr 16 | Addr 15 | Addr 14 | Addr 13 | Addr 12 | Addr 11 | Addr 10 | Addr 9 | Addr 8 | Addr 7 | Addr 6 | Addr 5 | Addr 4 | Addr 3 | Addr 2 | Addr 1 | Addr 0 |

图 3F

图 4

图 5

图 6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种白平衡可调的AMOLED显示驱动                             |         |            |

| 公开(公告)号        | <a href="#">CN105405398A</a>                   | 公开(公告)日 | 2016-03-16 |

| 申请号            | CN201510965326.2                               | 申请日     | 2015-12-21 |

| [标]申请(专利权)人(译) | 北京航空航天大学                                       |         |            |

| 申请(专利权)人(译)    | 北京航空航天大学                                       |         |            |

| 当前申请(专利权)人(译)  | 北京航空航天大学                                       |         |            |

| [标]发明人         | 李洪革<br>张子裕                                     |         |            |

| 发明人            | 李洪革<br>张子裕                                     |         |            |

| IPC分类号         | G09G3/3225                                     |         |            |

| CPC分类号         | G09G3/3225                                     |         |            |

| 优先权            | 201510543528.8 2015-08-28 CN                   |         |            |

| 其他公开文献         | CN105405398B                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明涉及有机发光二极管显示技术领域，公开了一种白平衡可调的AMOLED显示驱动。针对现有AMOLED显示驱动仅能支持单一白平衡点显示的不足，提出了一种白平衡可调的AMOLED显示驱动，该驱动具有两种显示模式：D65模式和D93模式。当图像的白平衡点为D65时，显示驱动工作在D65模式；当图像的白平衡点为D93时，显示驱动工作在D93模式。因此，该驱动可以根据图像的白平衡点调整显示驱动的显示模式，从而实现更好的显示效果。