(12) 发明专利

(10) 授权公告号 CN 102738200 B

(45) 授权公告日 2016. 08. 03

(21) 申请号 201210080760. 9

审查员 王一帆

(22) 申请日 2012. 03. 23

(30) 优先权数据

2011-079619 2011. 03. 31 JP

(73) 专利权人 索尼公司

地址 日本东京

(72) 发明人 山田二郎 横山诚一 长谷川英史

槇田笃哉 上杉昌尚 权藤胜一

市川朋芳 山下淳一

(74) 专利代理机构 北京康信知识产权代理有限

责任公司 11240

代理人 余刚 吴孟秋

(51) Int. Cl.

H01L 27/32(2006. 01)

H01L 51/52(2006. 01)

(56) 对比文件

TW 549009 B, 2003. 08. 21,

US 2001/0028060 A1, 2001. 10. 11,

US 2004/0066136 A1, 2004. 04. 08,

权利要求书2页 说明书19页 附图30页

(54) 发明名称

显示单元及其制造方法

(57) 摘要

一种显示单元及其制造方法, 该显示单元在基板上包括: 多个有机 EL 器件; 以及配置在多个有机 EL 器件之间的器件间区域中的绝缘膜。该绝缘膜包括位于彼此相邻的有机 EL 器件之间的位置中的沟槽。

1. 一种显示单元,包括位于基板上的:

多个有机EL器件;以及

绝缘膜,配置在所述多个有机EL器件之间的器件间区域中,所述绝缘膜包括位于彼此相邻的所述有机EL器件之间的位置中的沟槽,其中,所述有机EL器件包括:

第一电极,为所述多个有机EL器件中的每一个配置;

有机层,针对所述多个有机EL器件公共地配置在所述第一电极和所述绝缘膜上,且包括空穴注入层或空穴输送层、以及发光层;以及

第二电极,针对所述多个有机EL器件公共地配置在所述有机层上,并且

所述空穴注入层或所述空穴输送层在所述沟槽内的厚度小于其在所述沟槽外的厚度。

2. 根据权利要求1所述的显示单元,其中,所述空穴注入层或所述空穴输送层在所述沟槽内的厚度向所述沟槽的深度方向变小。

3. 根据权利要求1所述的显示单元,其中,所述多个有机EL器件具有在一个方向上延伸的矩形形状,并且以与其短边平行的行方向和与其长边平行的列方向排列,并且

遍及所述多个有机EL器件的多个行在所述列方向上连续地配置所述沟槽。

4. 根据权利要求1所述的显示单元,其中,所述多个有机EL器件具有矩形形状,并且以与其短边平行的行方向和与其长边平行的列方向排列,并且

为所述多个有机EL器件的每一行在所述列方向上配置所述沟槽。

5. 根据权利要求3所述的显示单元,其中,所述多个有机EL器件在所述行方向上的节距等于或小于30μm。

6. 根据权利要求1所述的显示单元,其中,所述绝缘膜包括第一绝缘膜和第二绝缘膜,所述第一绝缘膜被配置在所述基板与所述多个有机EL器件之间,并且所述第二绝缘膜被配置在所述第一绝缘膜上的器件间区域中,并且

所述沟槽包括第一沟槽和第二沟槽,所述第一沟槽被配置在所述第一绝缘膜中,并且所述第二沟槽被配置在所述第二绝缘膜中,与所述第一沟槽相通,且具有比所述第一沟槽的宽度更窄的宽度。

7. 根据权利要求1所述的显示单元,包括位于所述沟槽的底面上的导电膜,

其中,所述导电膜被连接至预定电位。

8. 根据权利要求7所述的显示单元,其中,所述预定电位是地电位或所述第二电极的电位。

9. 根据权利要求7所述的显示单元,包括:

驱动电路,包括所述基板与所述多个有机EL器件之间、所述基板与所述绝缘膜之间的晶体管,

其中,所述导电膜是遮挡光的遮光层。

10. 根据权利要求1所述的显示单元,其中,所述发光层是发射白光的层,并且

所述有机EL器件包括将所述白光提取为红光、绿光或蓝光的彩色滤光器。

11. 根据权利要求1所述的显示单元,其中,所述有机EL器件包括有机层,并且

所述沟槽的宽度等于或小于所述有机层的厚度。

12. 一种制造显示单元的方法,所述方法包括:

在基板上形成多个有机EL器件;以及

在所述多个有机EL器件之间的器件间区域中形成绝缘膜，

其中，在所述绝缘膜的形成中，在所述绝缘膜的彼此相邻的所述有机EL器件之间的位置中配置沟槽，

其中，形成所述多个有机EL器件包括：

为所述多个有机EL器件中的每一个形成第一电极；

在所述第一电极和所述绝缘膜上，针对所述多个有机EL器件公共地形成有机层，所述有机层包括空穴注入层或空穴输送层、以及发光层；以及

在所述有机层上，针对所述多个有机EL器件公共地形成第二电极，并且

其中，在所述绝缘膜中配置了所述沟槽之后执行所述有机层的形成，

其中，所述空穴注入层或所述空穴输送层在所述沟槽内的厚度小于其在所述沟槽外的厚度。

13. 根据权利要求12所述的制造显示单元的方法，其中，通过蒸发法执行所述有机层的形成，并且满足数学表达式1，

数学表达式1: $X/Y > w/d$

其中，X表示从所述沟槽的入口边缘到蒸发源的偏移距离，Y表示所述基板与所述蒸发源之间的距离，w表示所述沟槽的宽度，并且d表示所述沟槽的深度。

14. 根据权利要求13所述的制造显示单元的方法，其中，在所述有机层的形成中，所述蒸发法是在旋转所述基板的同时执行膜的形成的旋转蒸发法，并且在旋转所述基板一周的期间的部分或全部时间内满足所述数学表达式1。

15. 根据权利要求13所述的制造显示单元的方法，其中，在所述有机层的形成中，所述蒸发法是在所述蒸发源和所述基板在一个方向上相对移动的同时执行膜的形成的线性蒸发法，并且在所述基板通过所述蒸发源的期间的部分或全部时间内满足所述数学表达式1。

16. 根据权利要求13所述的制造显示单元的方法，其中，在所述有机层中的所述空穴注入层或所述空穴输送层的形成中，满足所述数学表达式1。

## 显示单元及其制造方法

### 技术领域

[0001] 本公开涉及一种具有有机EL(电致发光)器件的显示单元及其制造方法。

### 背景技术

[0002] 有机EL器件具有这样一种结构:其中,第一电极、包括发光层的有机层以及第二电极被顺次层积在衬底上。形成有机层的方法的实例包括一种通过使用蒸发掩膜来分别蒸镀红发光层、绿发光层和蓝发光层的方法,和一种不使用蒸发掩膜而层积红发光层、绿发光层和蓝发光层的方法。在要求具有高分辨率和改善的孔径比的显示单元中,后一种方法将来可能会成为主流。

[0003] 在层积多个发光层的方法中,针对所有有机EL器件公共地配置有机层。因此,相邻有机EL器件之间通过空穴注入层会发生驱动电流泄漏。从而,非发光像素受发光像素影响会略微发光,这会导致混色和效率下降。为解决这一缺陷,例如在日本待审查专利申请公开第2009-4347号中,在有机EL器件之间的区域中形成一种倒锥形分隔壁,且之后再形成空穴注入层,从而空穴注入层被截断成多个部分。

### 发明内容

[0004] 在日本待审查专利申请公开第2009-4347号所述的现有方法中,形成了空穴注入层之后,为了在分隔壁上形成第二电极的过程中不把第二电极截断成多个部分,要进行热处理以便使分隔壁变成正锥形。然而,有如下缺陷存在:在蒸发步骤的过程中进行热处理的情况下,特性劣化的概率更高。

[0005] 期望提供一种能够抑制相邻有机EL器件之间的驱动电流泄漏而不降低特性的显示单元及其制造方法。

[0006] 根据本公开的一实施方式,提供了一种显示单元,包括:位于基板上的多个有机EL器件以及配置在多个有机EL器件之间的器件间区域中的绝缘膜,该绝缘膜包括位于彼此相邻的有机EL器件之间的位置中的沟槽。

[0007] 在本公开的实施方式的显示单元中,绝缘膜被配置在多个有机EL器件之间的器件间区域中。该绝缘膜在彼此相邻的有机EL器件之间的位置中具有沟槽。因此,有机层中的诸如空穴注入层和空穴输送层的具有较高导电性的层在沟槽内的厚度小于其在沟槽外的厚度,并且增大了其沟槽内的电阻。从而,抑制了彼此相邻的有机EL器件之间的驱动电流泄漏。

[0008] 根据本公开的一实施方式,提供了一种显示单元制造方法,该方法包括:在基板上形成多个有机EL器件,以及在多个有机EL器件之间的器件间区域中形成绝缘膜。在绝缘膜的形成中,在绝缘膜的彼此相邻的有机EL器件之间的位置中配置沟槽。

[0009] 根据本公开的实施方式的显示单元或本公开的实施方式的显示单元制造方法,绝缘膜被配置在多个有机EL器件之间的器件间区域中。沟槽被配置在绝缘膜的彼此相邻的有机EL器件之间的位置中。从而,抑制了彼此相邻的有机EL器件之间的驱动电流泄漏。并且,

不需要执行现有的热处理,从而,允许特性不会劣化。

[0010] 需要理解的是,无论上述一般性描述还是以下详细描述均是示例性的,并且意在提供对如权利要求所述的本技术的进一步说明。

## 附图说明

[0011] 所包括的附图提供了对本公开的进一步理解,将这些附图合并到本说明书中并构成其一部分。附图示出了实施方式,并与说明书一同用来阐明本技术的原理。

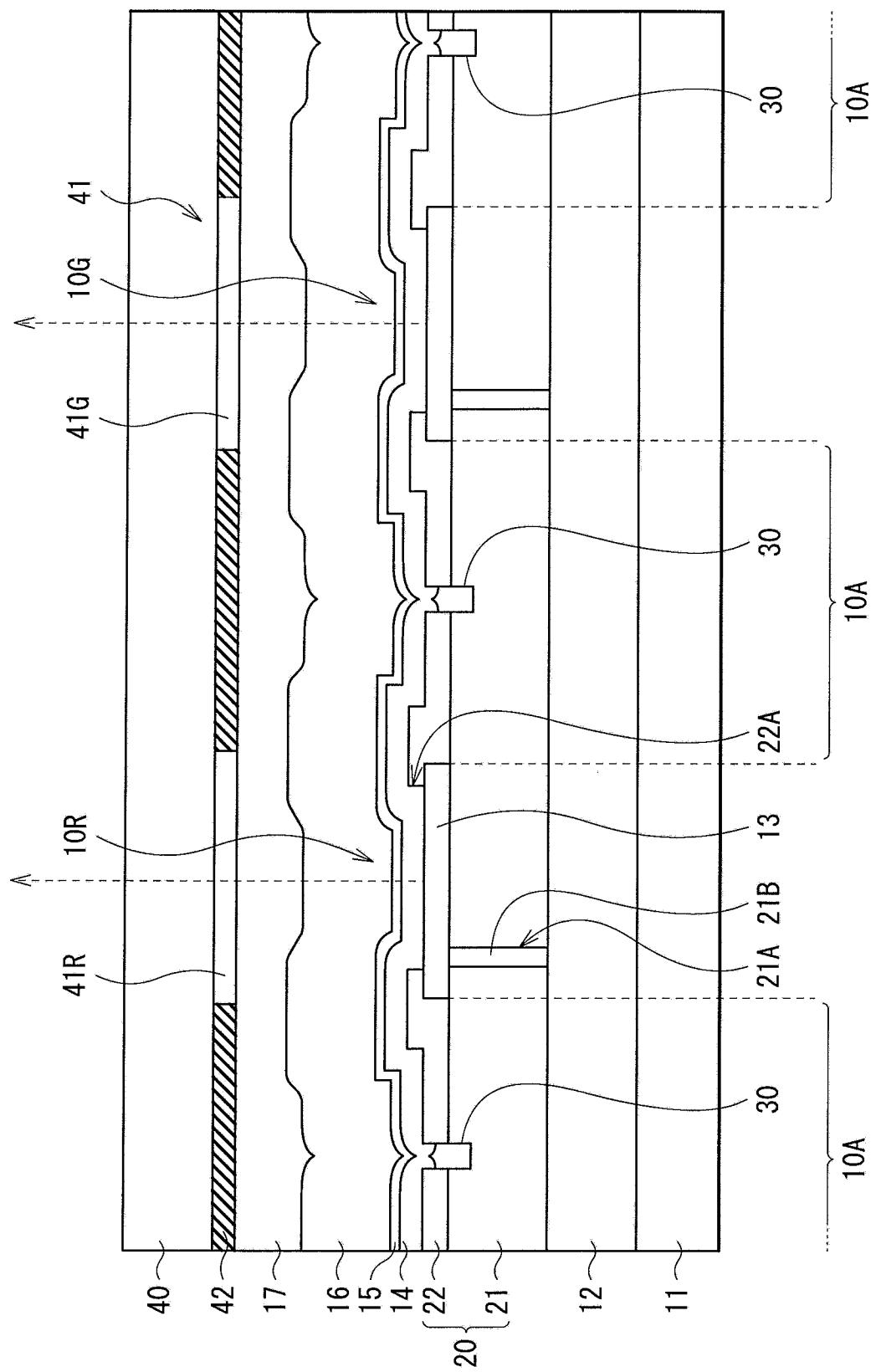

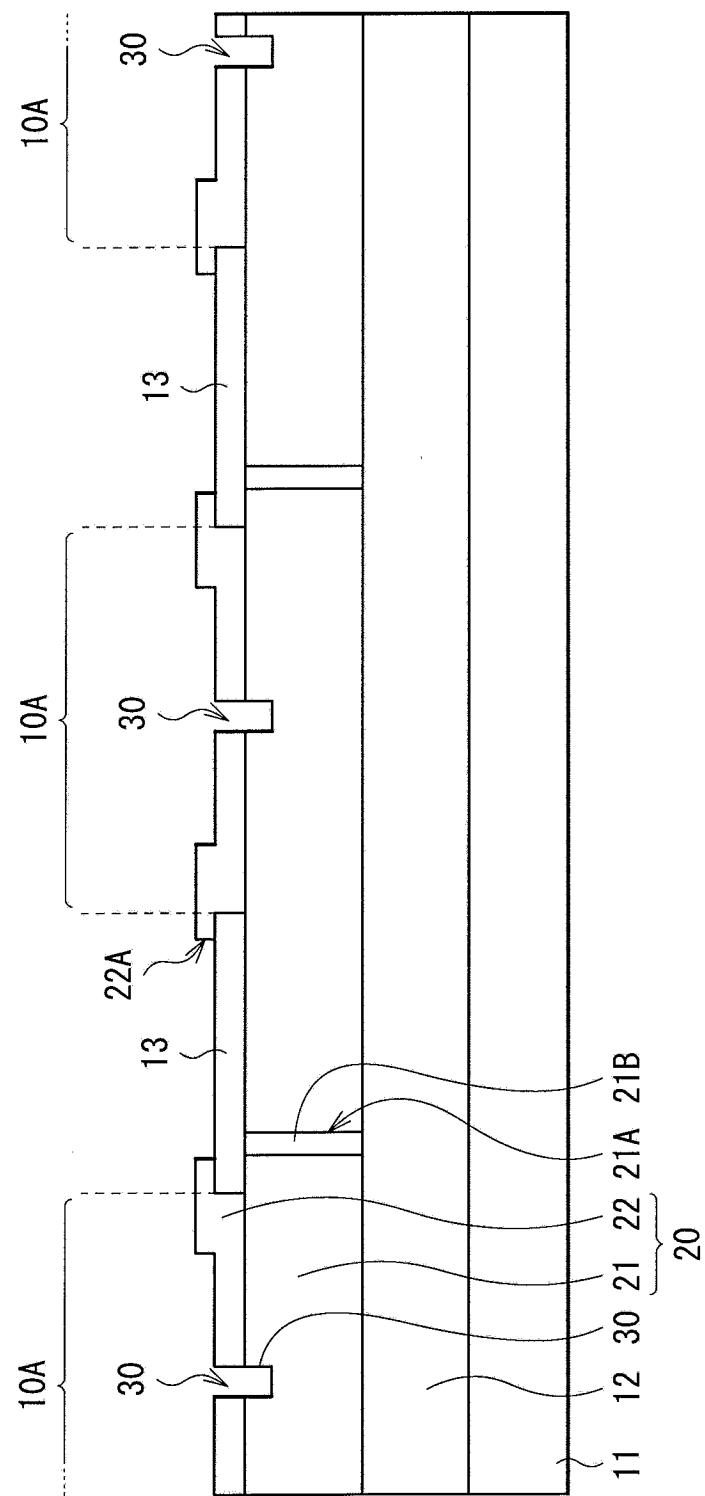

[0012] 图1是示出根据本公开第一实施方式的显示单元的结构的图。

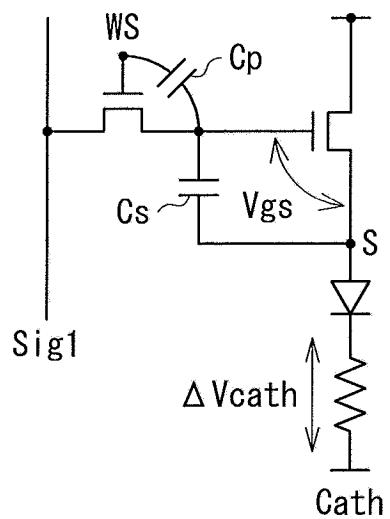

[0013] 图2是示出图1所示的像素驱动电路的一个实例的图。

[0014] 图3是示出图1所示的显示区的结构的平面图。

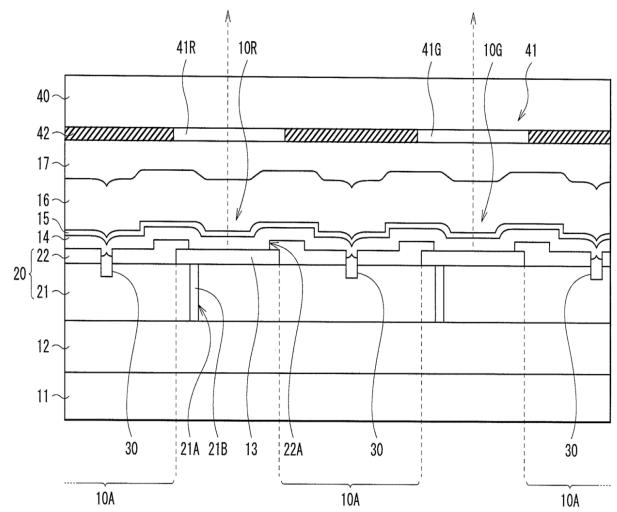

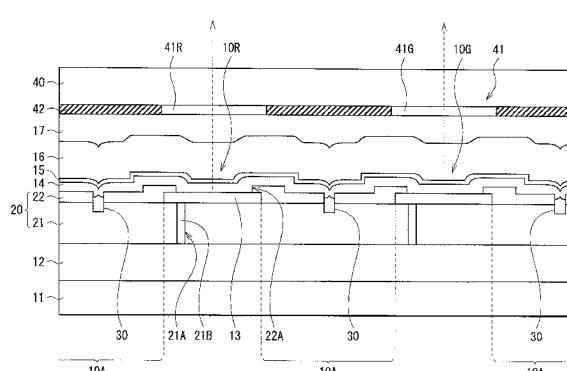

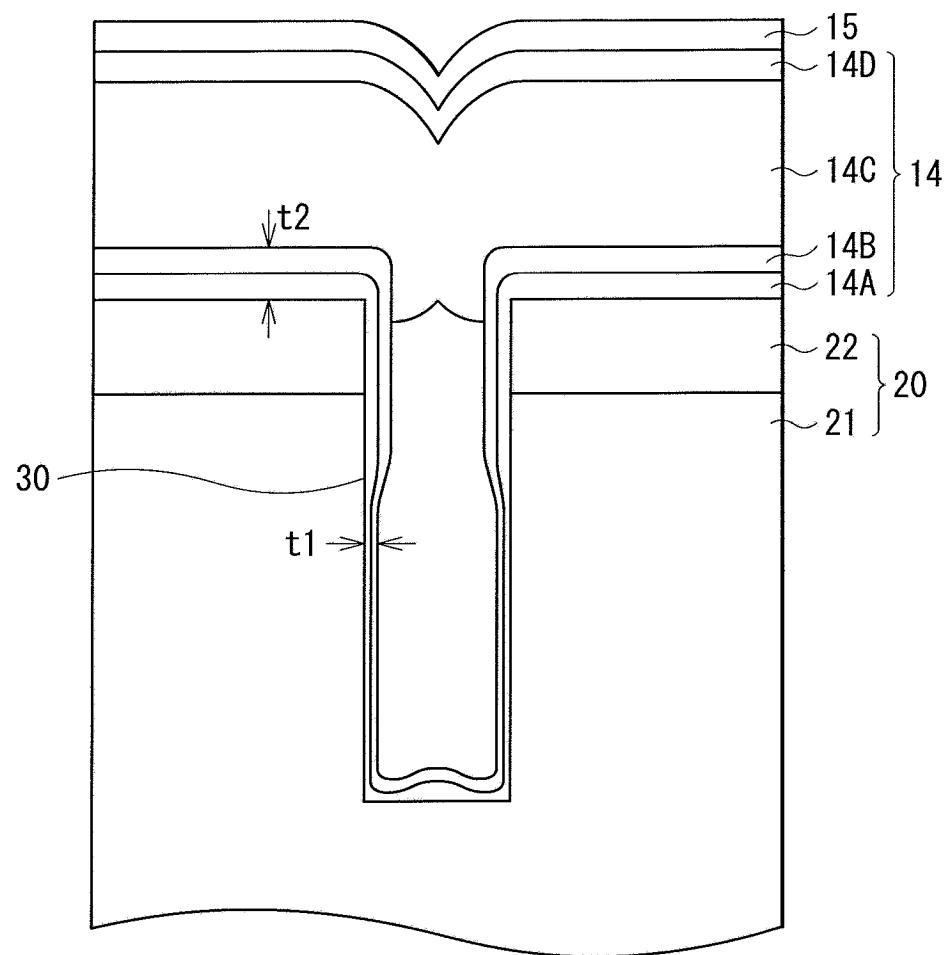

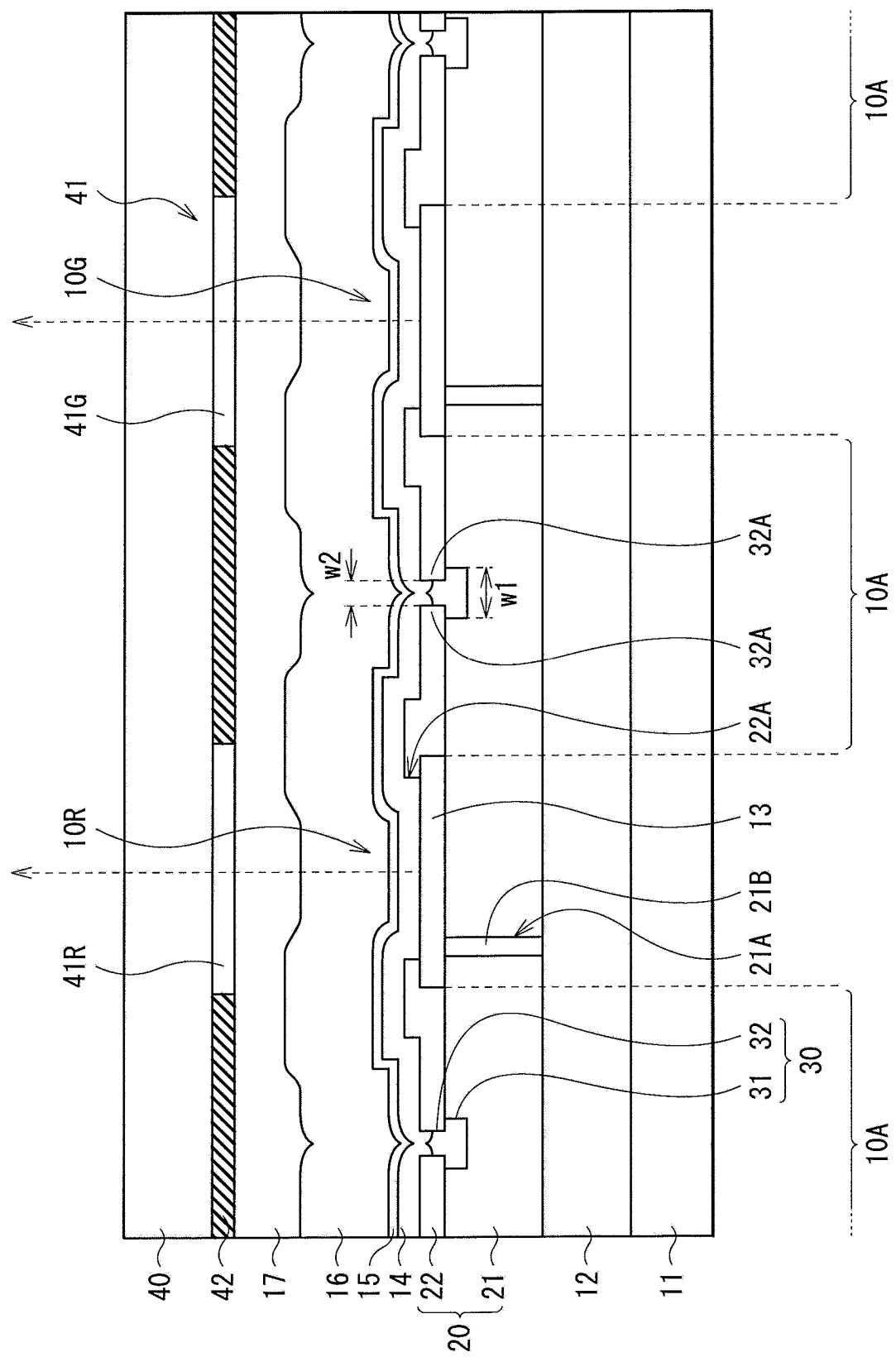

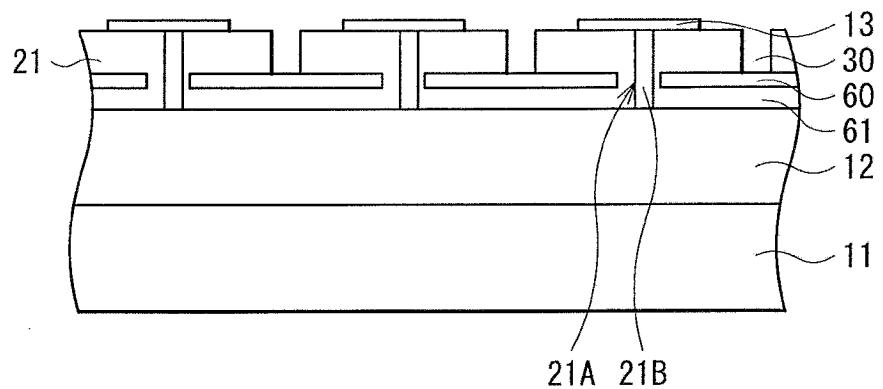

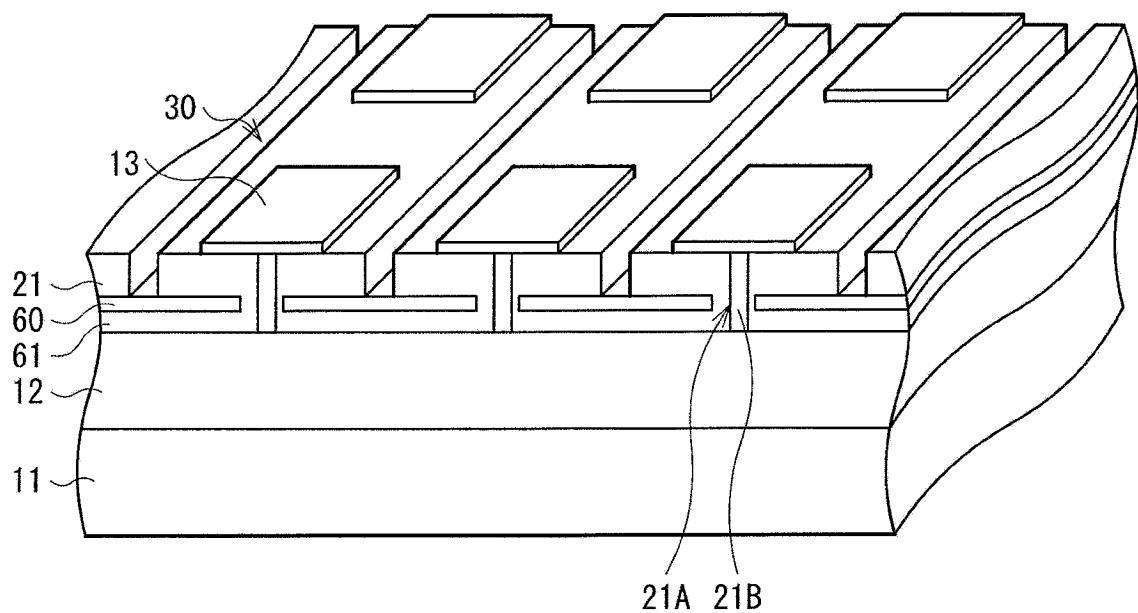

[0015] 图4是沿着图3的线IV-IV截得的截面图。

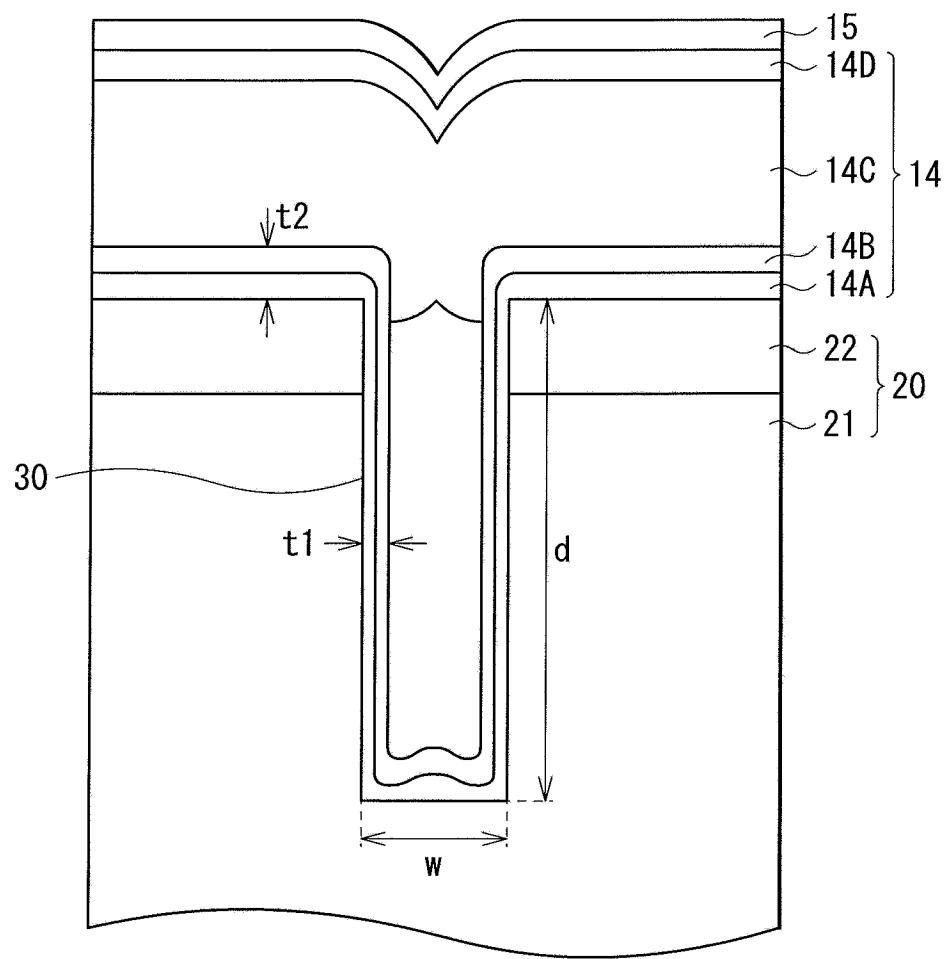

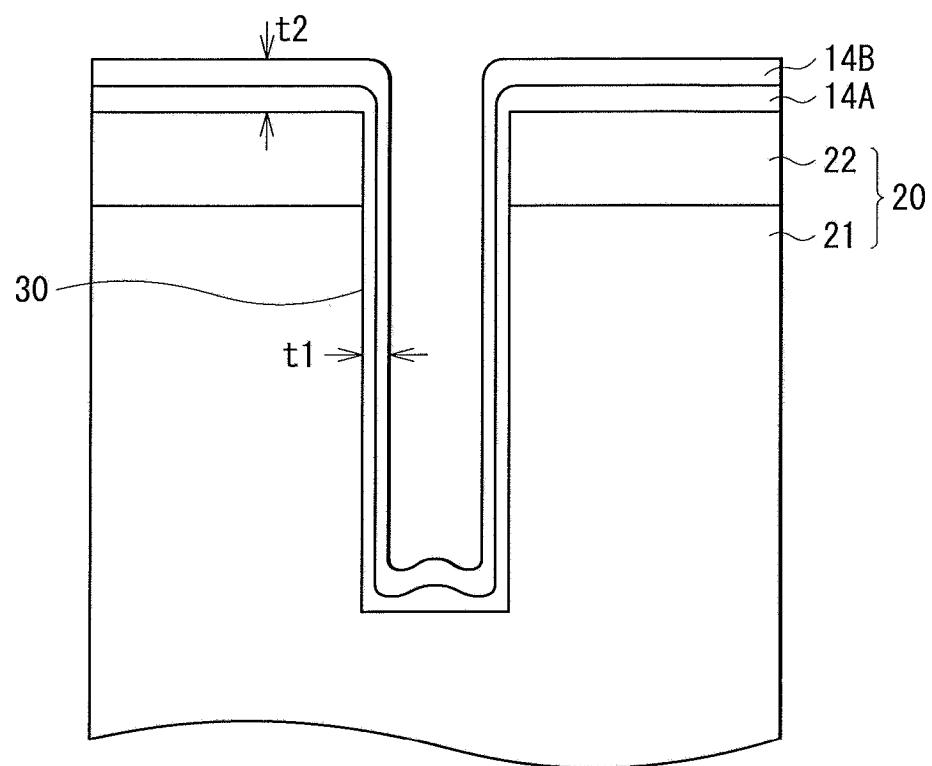

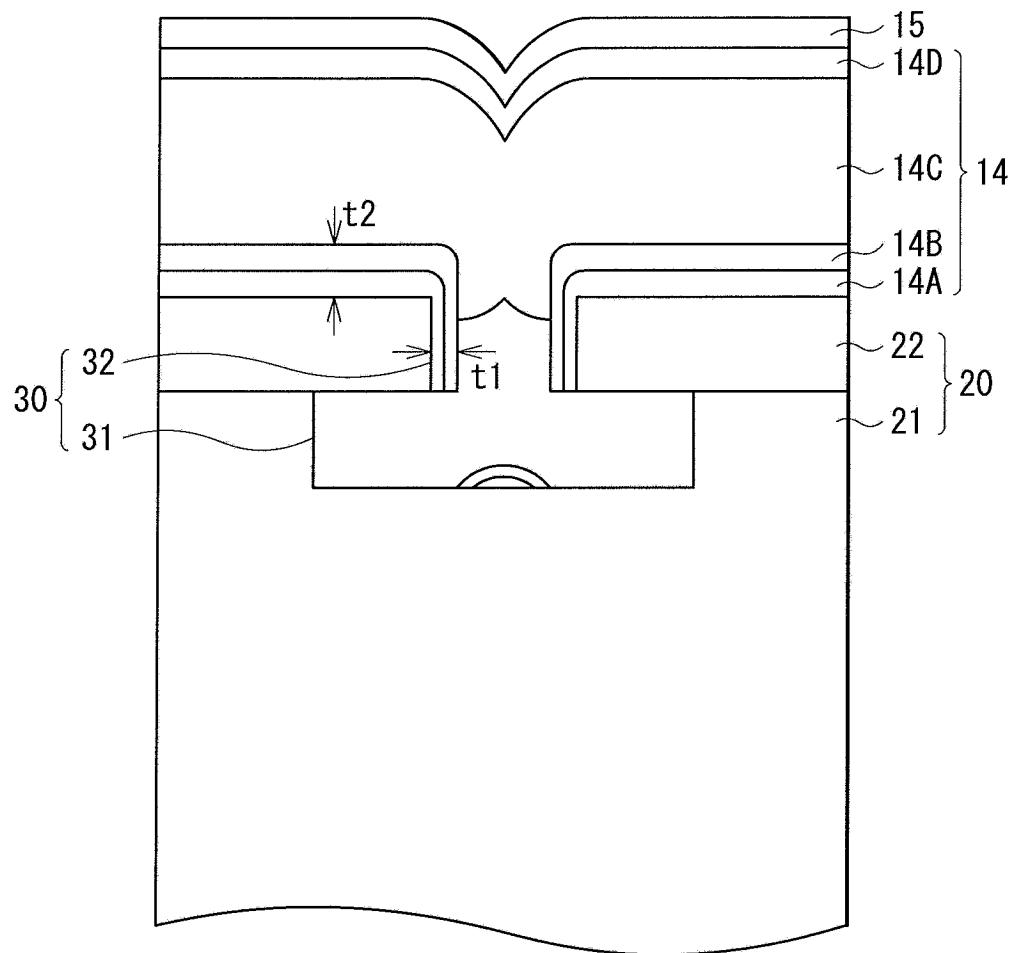

[0016] 图5是在图4所示的沟槽附近的区域的经放大后的截面图。

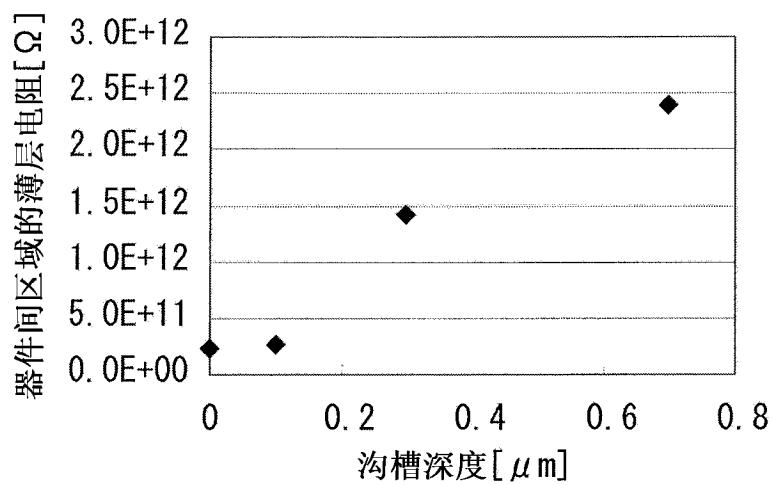

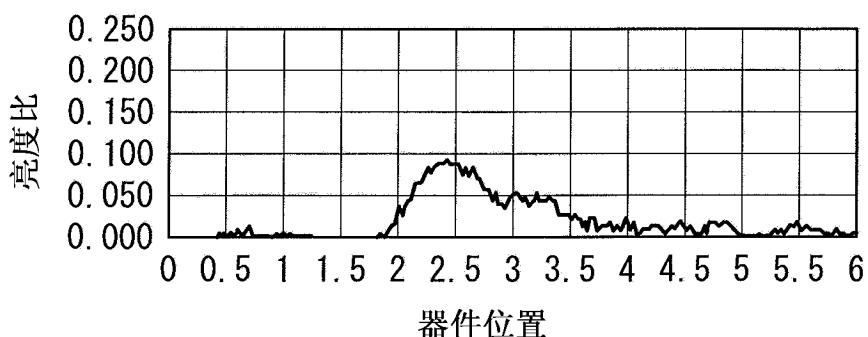

[0017] 图6是示出沟槽深度与器件间区域的薄层电阻之间的关系的图。

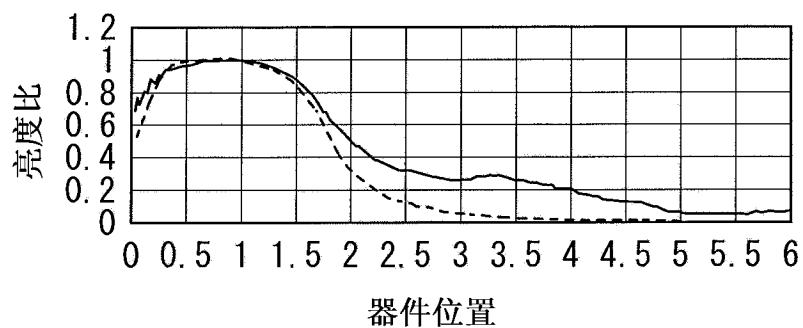

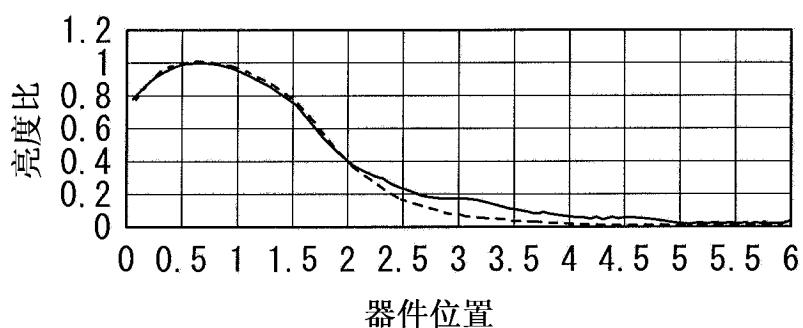

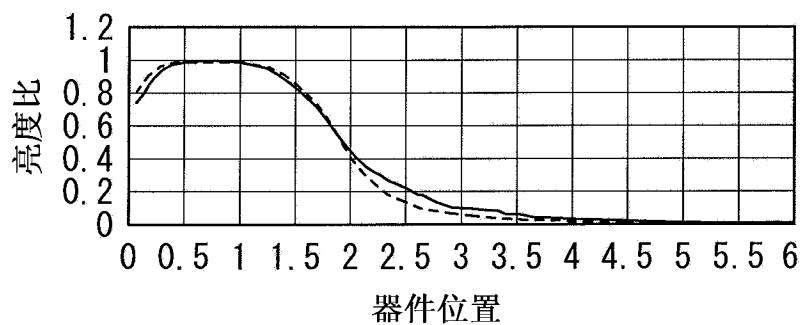

[0018] 图7A至图7C是示出将在配置了沟槽的情况下相邻像素的亮度的测量结果与在未配置沟槽的情况下进行对比的图。

[0019] 图8A至图8C是示出图7A至图7C所示的浮置(floating)器件的情况与相邻器件被接地的情况之间的亮度差的经放大后的图。

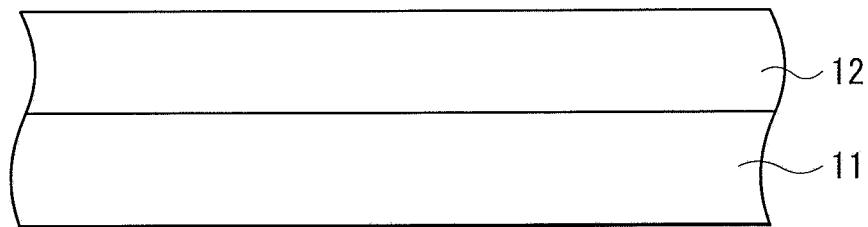

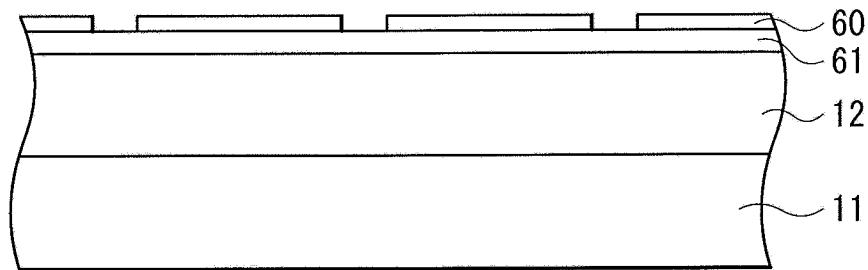

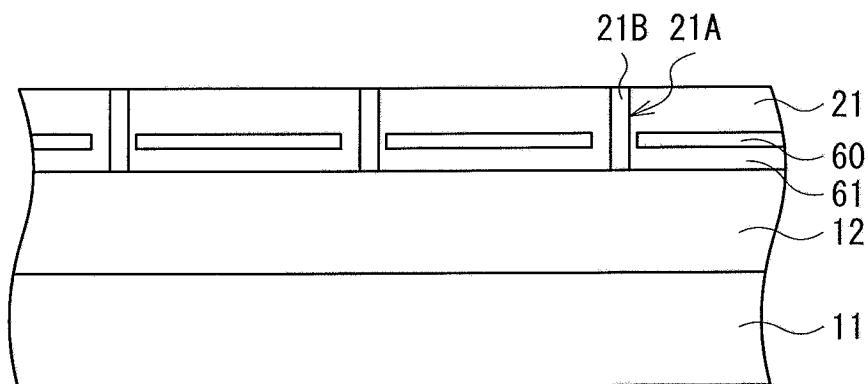

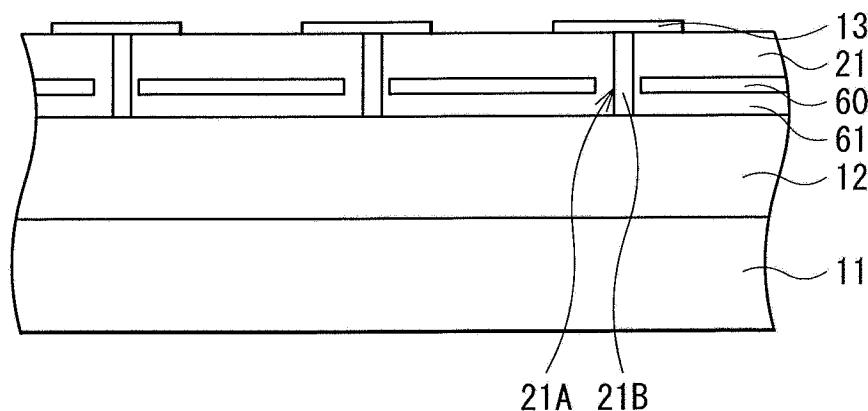

[0020] 图9是示出以所示步骤顺序制造图1所示显示单元的方法的截面图。

[0021] 图10是示出图9步骤之后的步骤的截面图。

[0022] 图11是示出图10步骤之后的步骤的截面图。

[0023] 图12是示出图11步骤之后的步骤的截面图。

[0024] 图13是示出图12步骤之后的步骤的截面图。

[0025] 图14是示出图13步骤之后的步骤的截面图。

[0026] 图15是示出图14步骤之后的步骤的截面图。

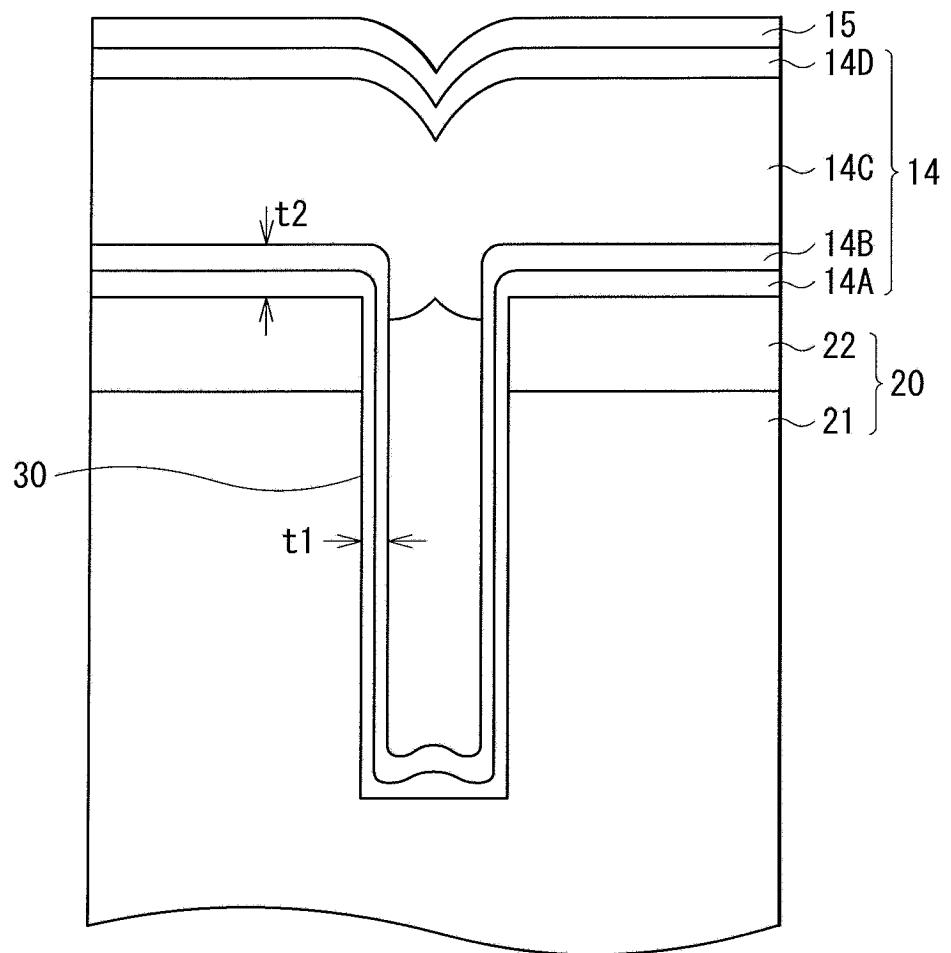

[0027] 图16是示出根据本公开第二实施方式的显示单元中的显示区的沟槽附近的区域的经放大后的截面图。

[0028] 图17是用于说明制造图16所示显示单元的方法的图。

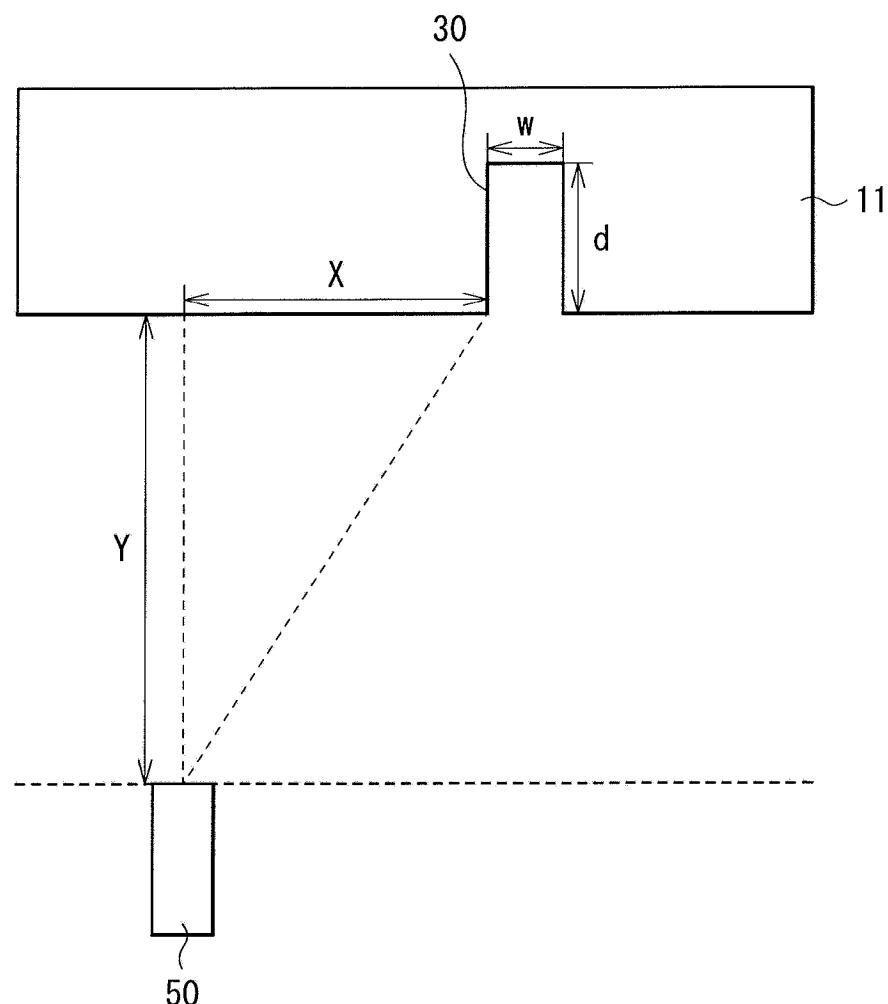

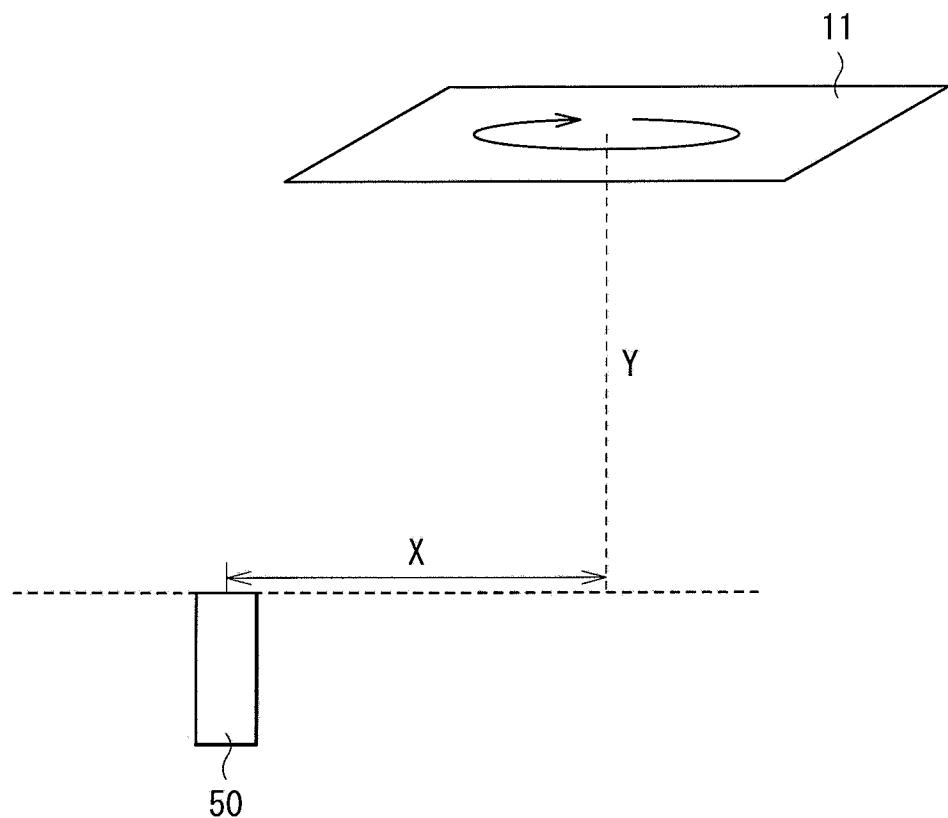

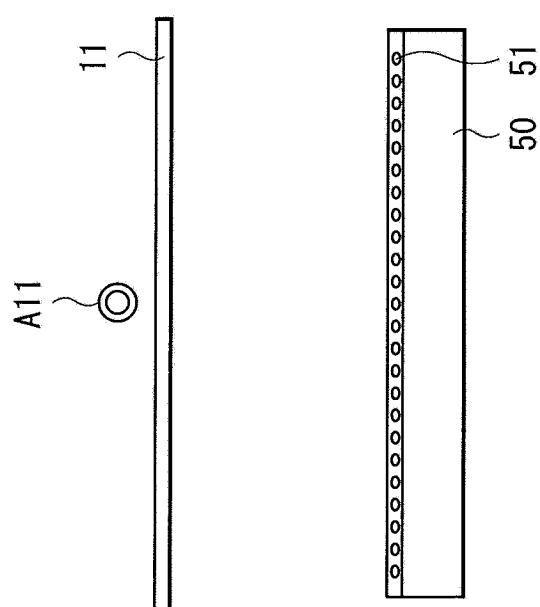

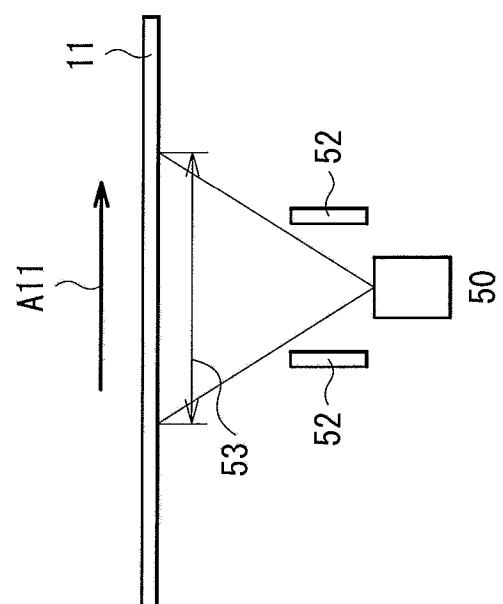

[0029] 图18是用于说明旋转式蒸发法的图。

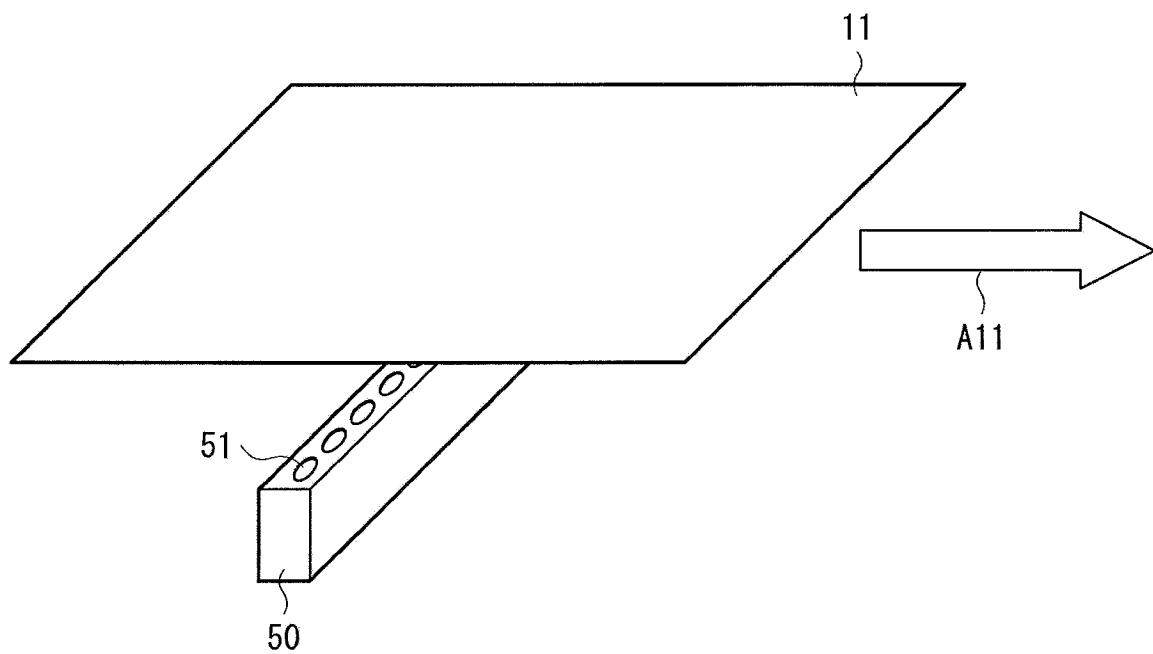

[0030] 图19是用于说明线性蒸发法的图。

[0031] 图20是示出图19所示线性蒸发法的沿着基板移动方向和与其垂直的方向看去的结构的示图。

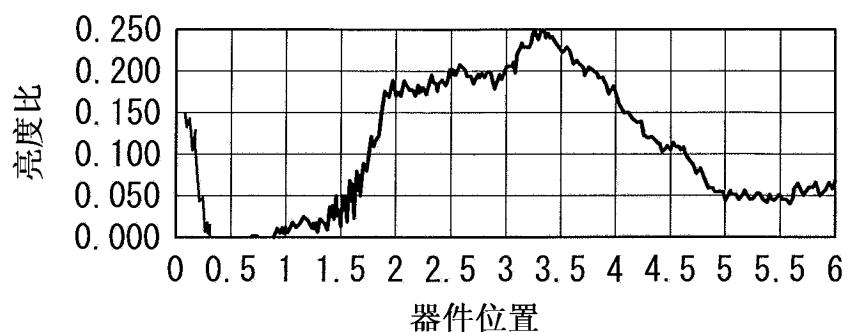

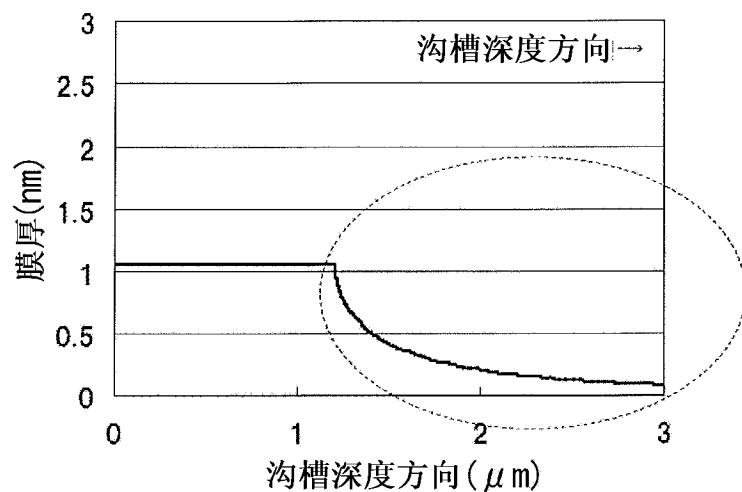

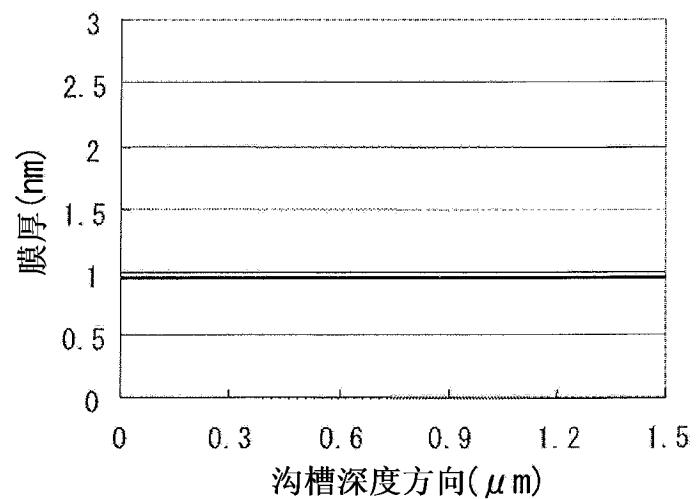

[0032] 图21是示出空穴注入层和空穴输送层的沟槽内的厚度的第一仿真结果的图。

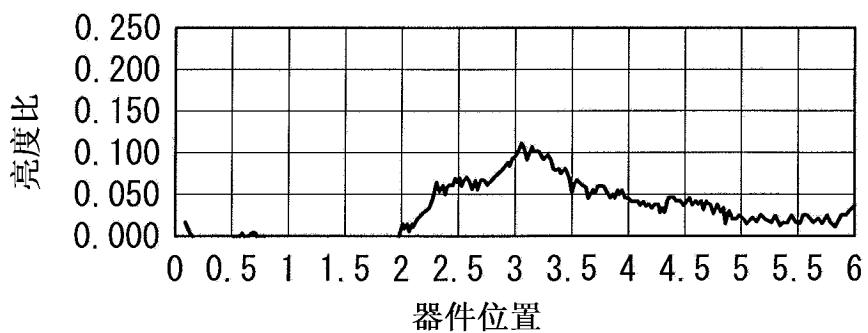

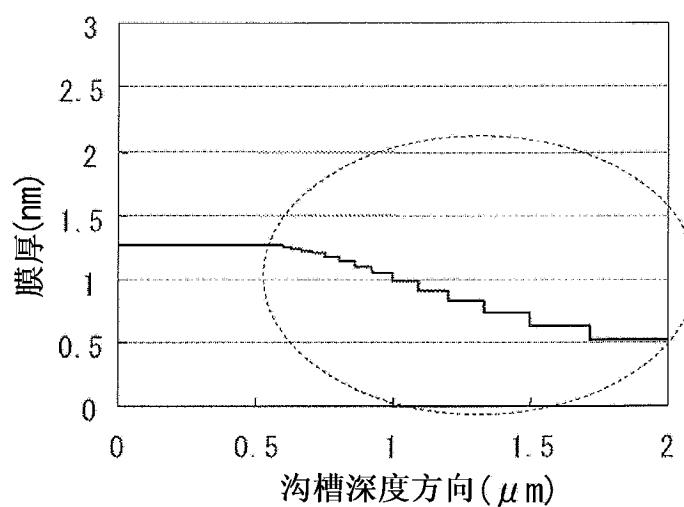

[0033] 图22是示出空穴注入层和空穴输送层的沟槽内的厚度的第二仿真结果的图。

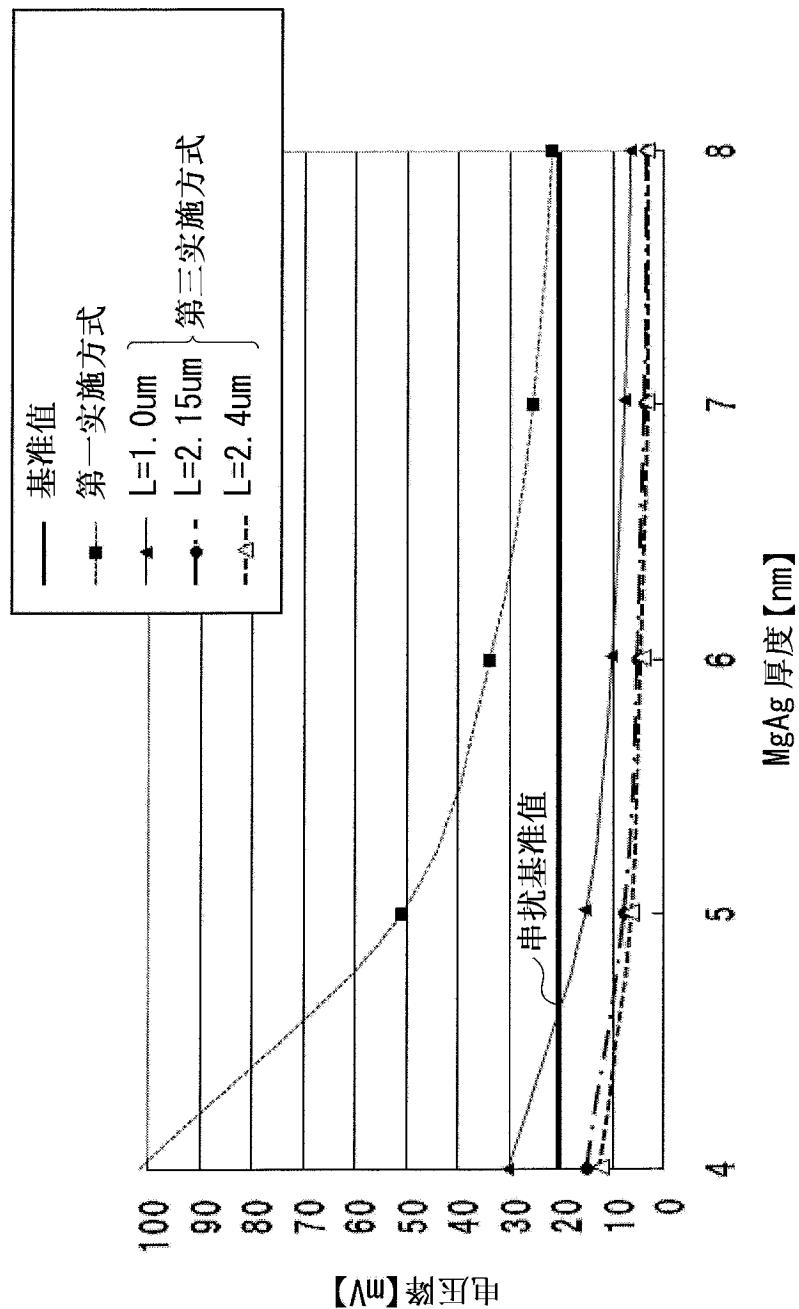

[0034] 图23是示出空穴注入层和空穴输送层的沟槽内的厚度的第三仿真结果的图。

[0035] 图24是示出根据本公开第三实施方式的显示单元中的显示区的结构的平面图。

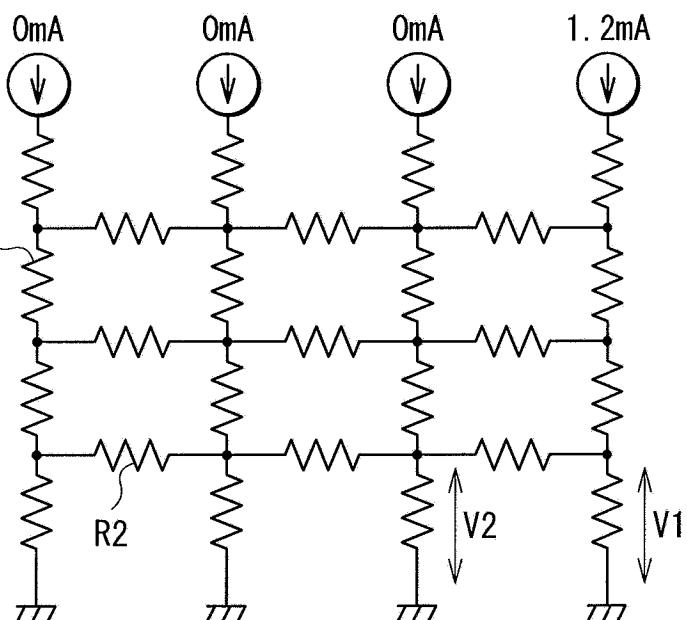

[0036] 图25是用于说明在配置了图24所示沟槽的情况下第二电极的电阻和显示状态的图。

[0037] 图26是用于说明在配置了图3所示沟槽的情况下第二电极的电阻和显示状态的图。

- [0038] 图27是示出在图2所示像素驱动电路中的有机EL器件内流通的电流Ids的电路图。

- [0039] 图28是用于说明通过改变图24所示各个沟槽之间的列方向上的间隔和第二电极的厚度来检测第二电极的电阻和电压降而获得的仿真的图。

- [0040] 图29是示出第二电极的列方向上的电阻和行方向上的电阻的仿真结果的图。

- [0041] 图30是示出第二电压的电压降的仿真结果的图。

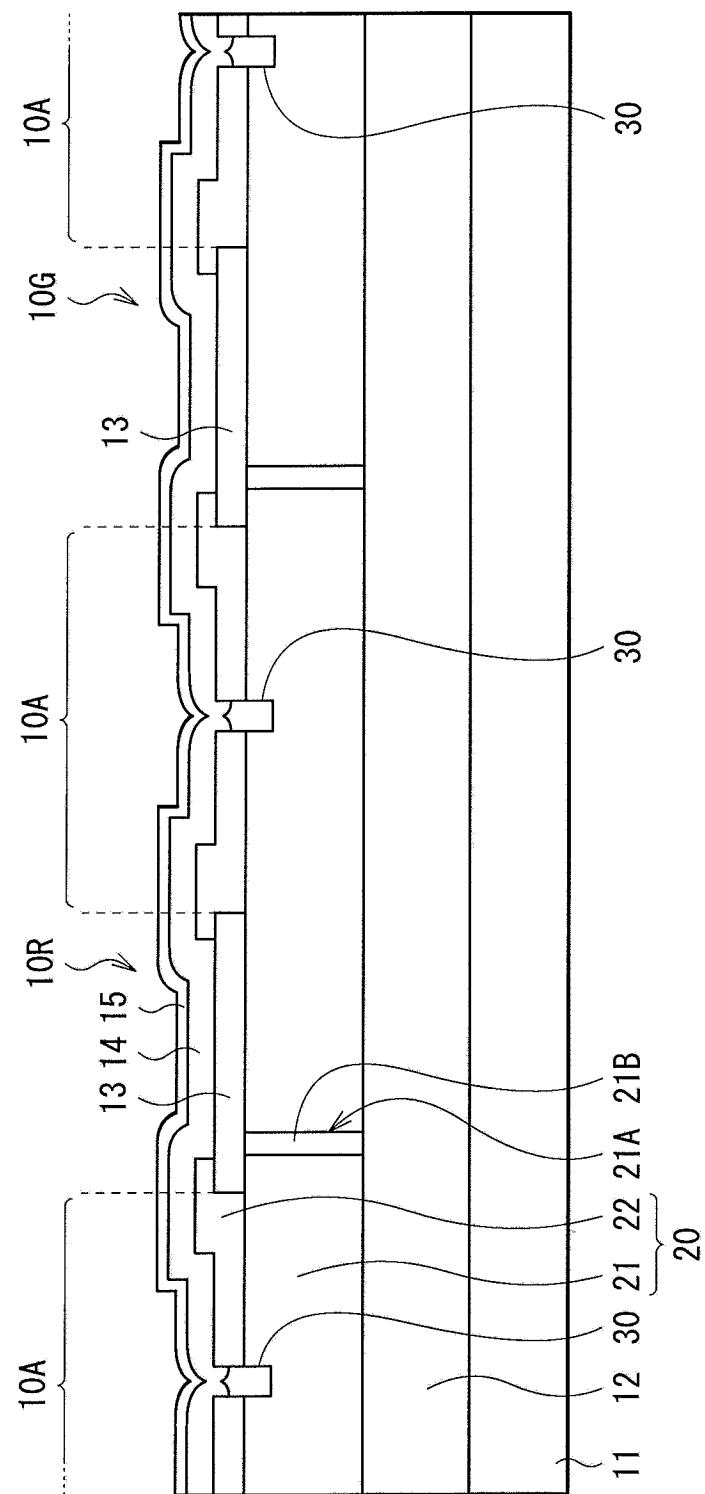

- [0042] 图31是示出根据本公开第四实施方式的显示单元中的显示区的结构的截面图。

- [0043] 图32是示出图31所示的沟槽附近的区域的经放大后的截面图。

- [0044] 图33是示出图31所示沟槽的另一形状的截面图。

- [0045] 图34是示出根据本公开第五实施方式的显示单元中的显示区的结构的截面图。

- [0046] 图35是示出图34所示的沟槽附近的区域的经放大后的截面图。

- [0047] 图36A至图36D是示出以所示步骤顺序制造图34所示显示单元的方法的截面图。

- [0048] 图37A和图37B是示出图36D步骤之后的步骤的斜视图和截面图。

- [0049] 图38是示出图37A和图37B步骤之后的步骤的截面图。

- [0050] 图39是示出包括上述实施方式的显示单元的模块的示意性结构的平面图。

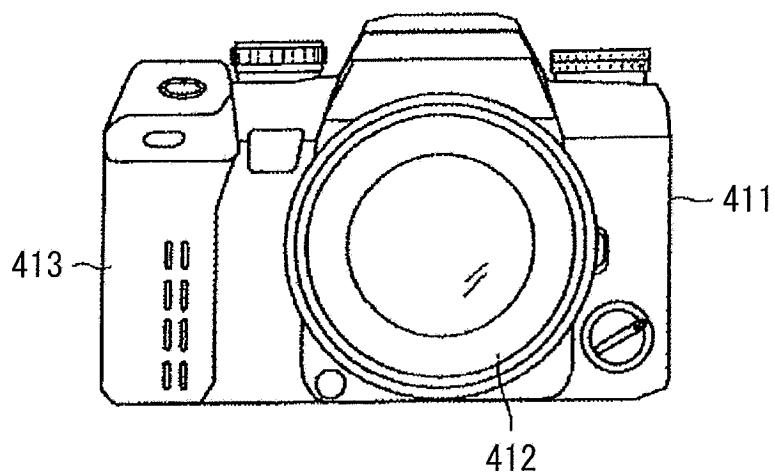

- [0051] 图40A和图40B是示出上述实施方式的显示单元的第一应用实例的外观的正面图和背面图。

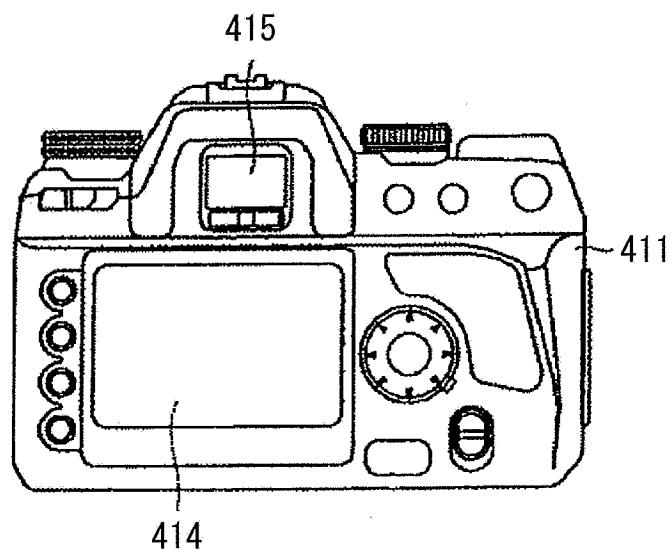

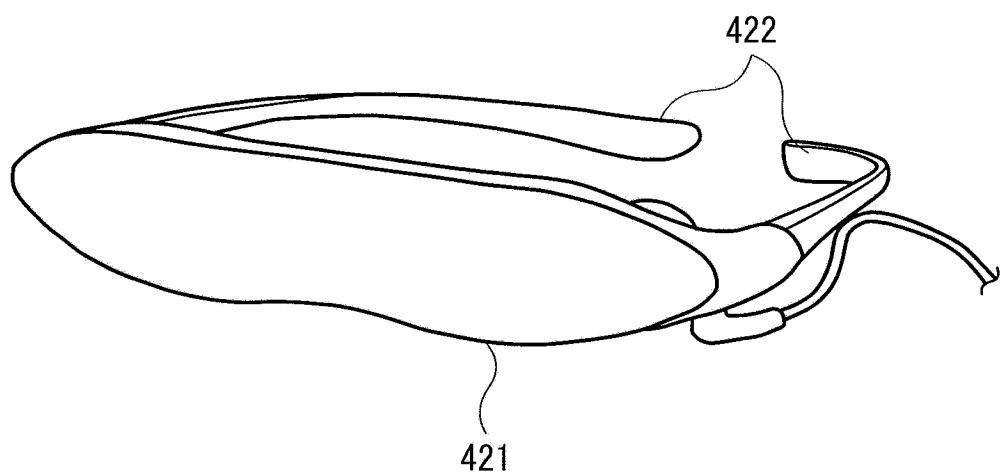

- [0052] 图41是示出第二应用实例的外观的斜视图。

### 具体实施方式

- [0053] 下文将参照附图对本公开的实施方式进行详细描述。该描述将按照以下顺序进行。

- [0054] 1. 第一实施方式(在绝缘膜中,相邻有机EL器件之间的位置处配置沟槽的实例)。

- [0055] 2. 第二实施方式(在形成有机层的步骤中,限定了基板上的沟槽与蒸发源之间的位置关系的实例)。

- [0056] 3. 第三实施方式(为多个有机EL器件的各行在列方向上配置沟槽的实例)。

- [0057] 4. 第四实施方式(以两步骤方式改变沟槽宽度的实例)。

- [0058] 5. 第五实施方式(在沟槽底面上配置导电膜的实例)。

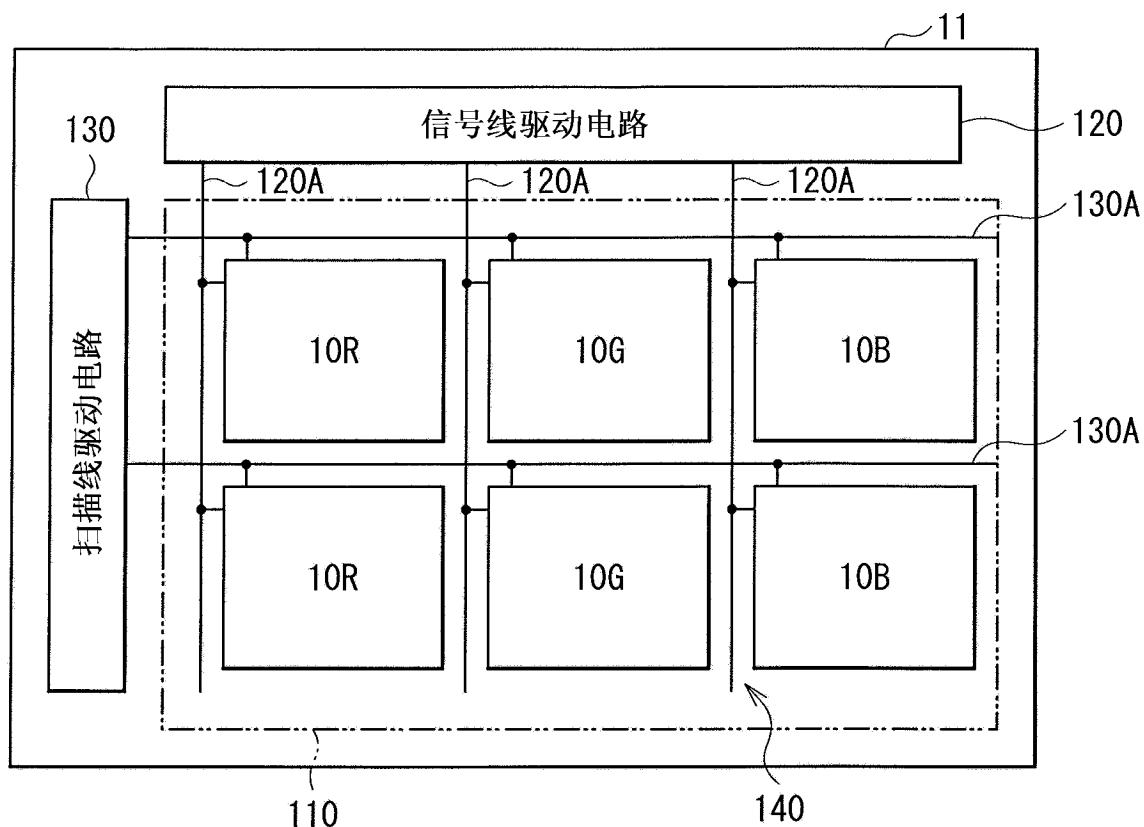

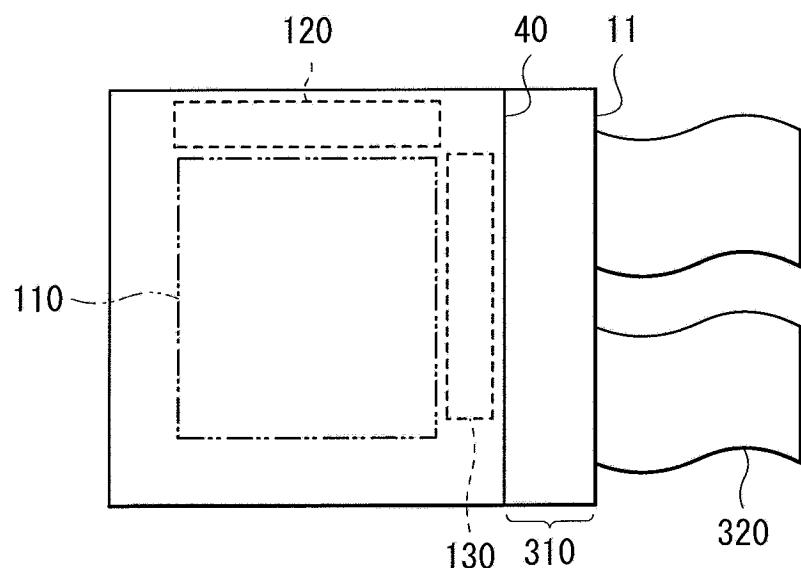

- [0059] 图1示出了根据本公开第一实施方式的显示单元的结构。该显示单元是用于数字单镜头反光摄像机的取景器、头戴式显示器等的小型高清晰度有机EL显示单元。例如,该显示单元配置有显示区110,在该显示区中,后述的多个有机EL器件10R、10G和10B在由玻璃等制成的基板11上被排列成矩阵形状。信号线驱动电路120和扫描线驱动电路130是用于显示视频的驱动器,它们被配置在显示区110的周边。

- [0060] 在显示区110中,配置了像素驱动电路140。图2示出了像素驱动电路140的一个实例。像素驱动电路140是形成在位于后述的第一电极13的下层中的有源驱动电路。例如,像素驱动电路140具有驱动晶体管Tr1、写入晶体管Tr2、电容器(保持电容量)Cs以及在第一电源线(Vcc)和第二电源线(GND)之间与驱动晶体管Tr1串联的有机EL器件10R(或10G/10B)。电容器Cs的一个电极被连接至驱动晶体管Tr1与写入晶体管Tr2之间,且电容器Cs的另一电极被连接至驱动晶体管Tr1与有机EL器件10R(10G/10B)之间。

- [0061] 在像素驱动电路140中,多条信号线120A被布置在列方向上,且多条扫描线130A被

布置在行方向上。各信号线120A和各扫描线130A的各个交差点均对应有机EL器件10R、10G和10B中的一个(子像素)。各信号线120A被连接至信号线驱动电路120。从信号线驱动电路120通过信号线120A向写入晶体管Tr2的源极提供图像信号。各扫描线130A被连接至扫描线驱动电路130。从扫描线驱动电路130通过扫描线130A顺次向写入晶体管Tr2的栅极提供扫描信号。

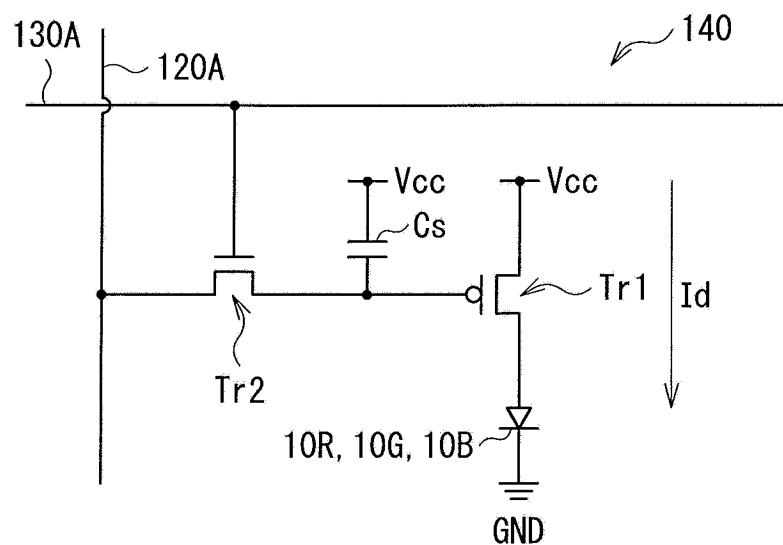

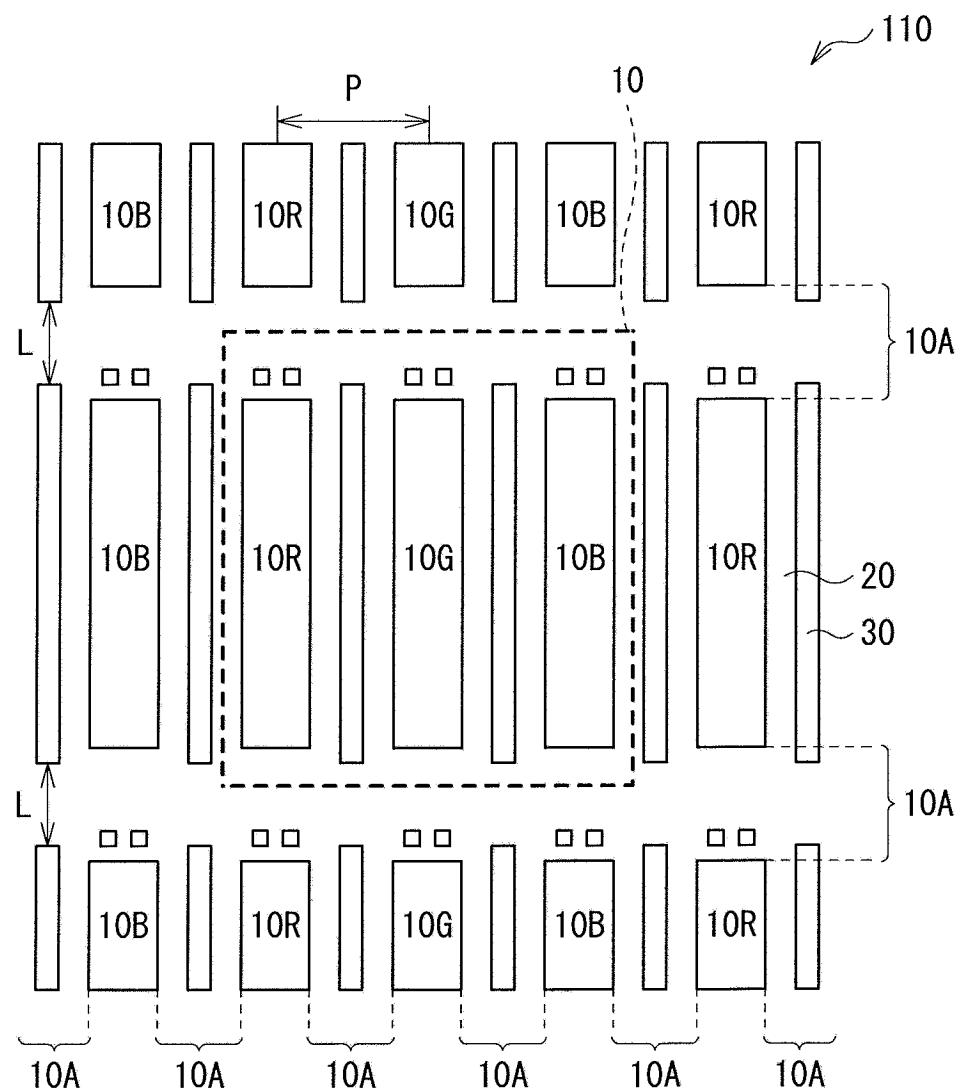

[0062] 图3示出了图1所示的显示区110的一部分的平面结构。多个有机EL器件10R、10G和10B在基板11上被排列成矩阵形状。各有机EL器件10R、10G和10B具有长边在某一方向上的矩形形状。在平行于其短边的行方向上,具有不同色彩的有机EL器件10R、10G和10B被顺序排列。在平行于其长边的列方向上,排列具有同一色彩的有机EL器件10R(或10G/10B)。

[0063] 彼此相邻的三个有机EL器件10R、10G和10B组成一个像素10。每个有机EL器件10R、10G和10B组成一个子像素。例如,多个有机EL器件10R、10G和10B在行方向上的节距(中心距离)p等于或小于30μm。具体地,例如,一个像素10是各边约为10μm的正方形,并且,多个有机EL器件10R、10G和10B的节距p例如约为3.3μm。

[0064] 在多个有机EL器件10R、10G和10B之间的器件间区域10A中配置绝缘膜20。绝缘膜20具有位于相邻有机EL器件10R和10G(或相邻有机EL器件10G和10B、或相邻有机EL器件10B和10R)之间的位置处的沟槽30。因此,在该显示单元中,能够抑制相邻有机EL器件10R和10G(或相邻有机EL器件10G和10B、或相邻有机EL器件10B和10R)之间的驱动电流泄漏。

[0065] 例如,遍及多个有机EL器件10R、10G和10B的多个行从显示区110的上端到下端在列方向上连续配置沟槽30。从而,若有机EL器件10R、10G和10B的后述的第二电极15在行方向上被沟槽30截断,则允许该第二电极15作为列方向上的连续共用电极而存在。对于沟槽30的细节,将在下文中给予描述。

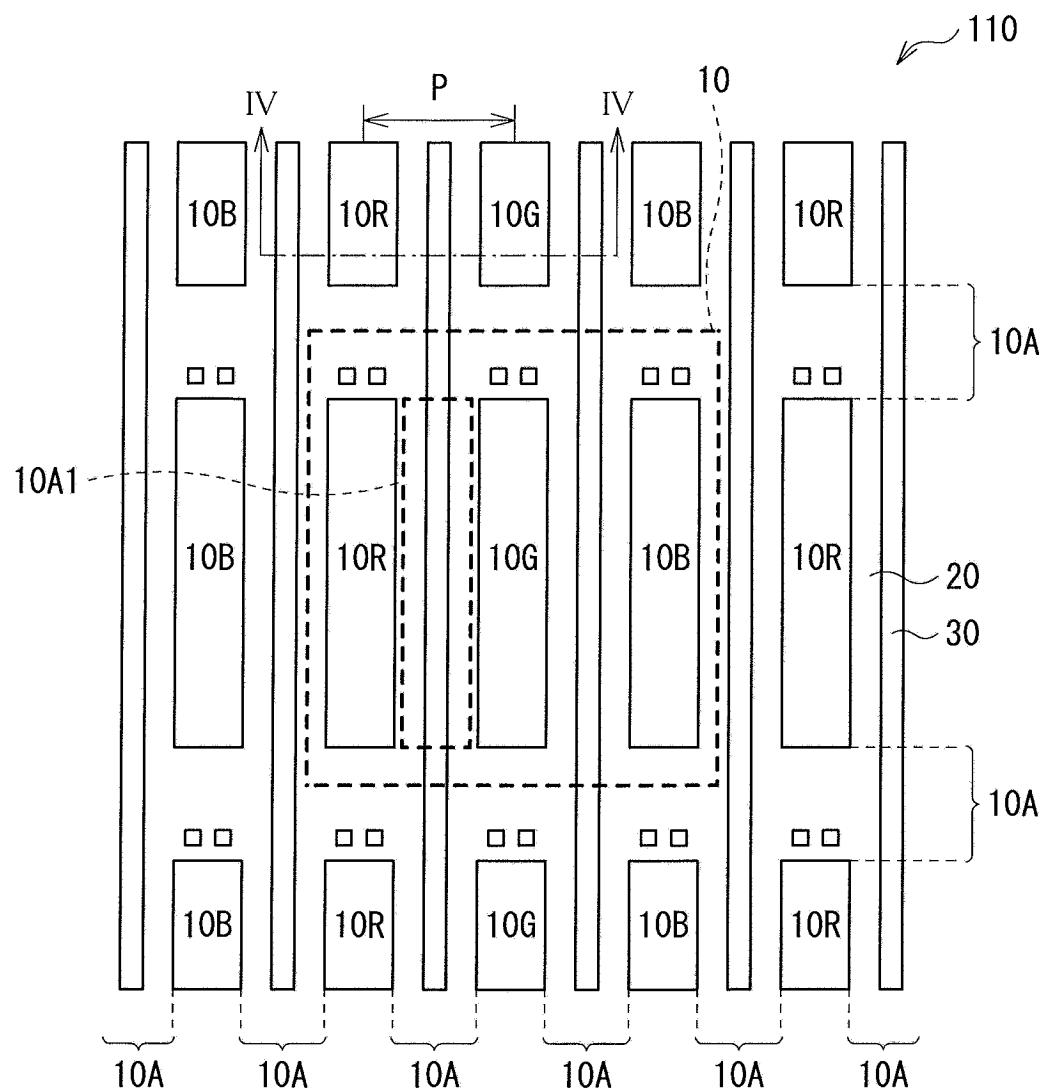

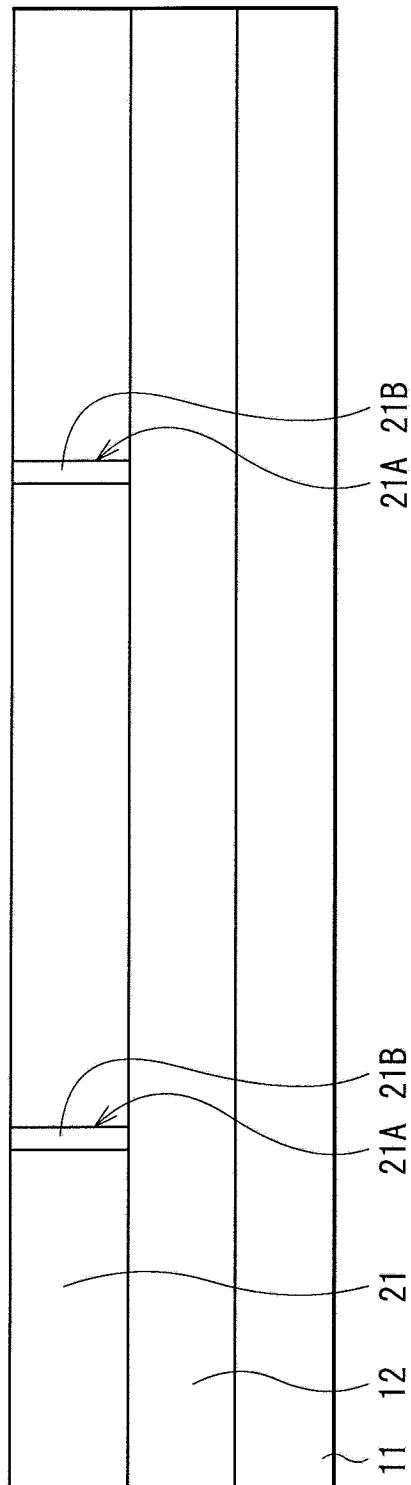

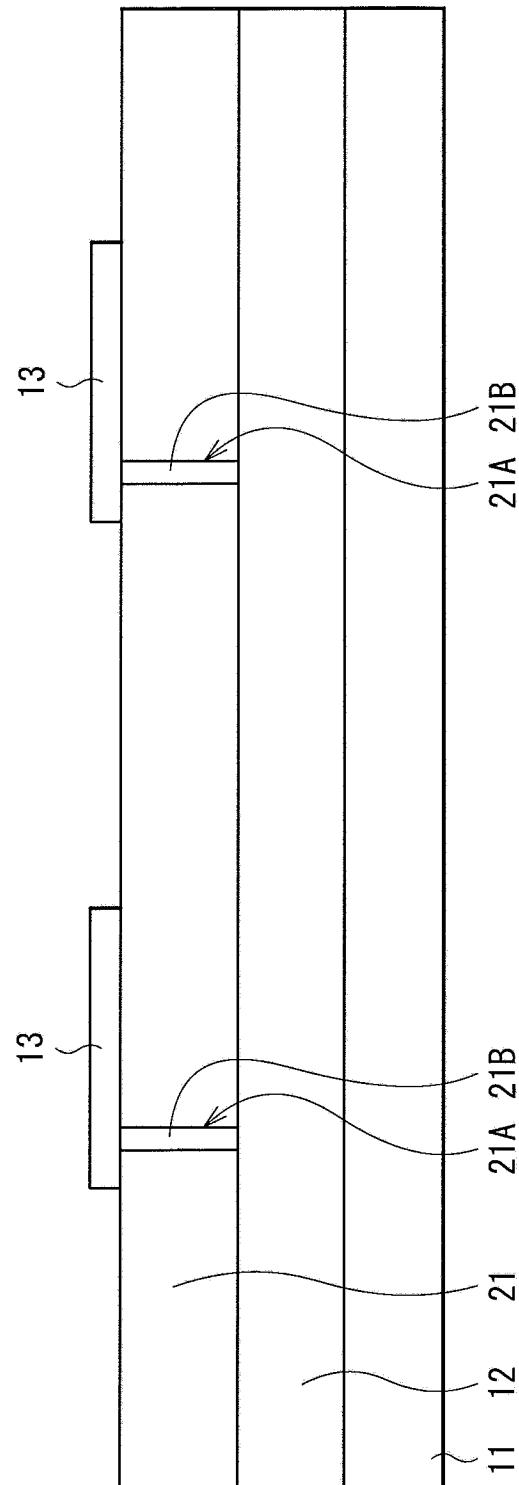

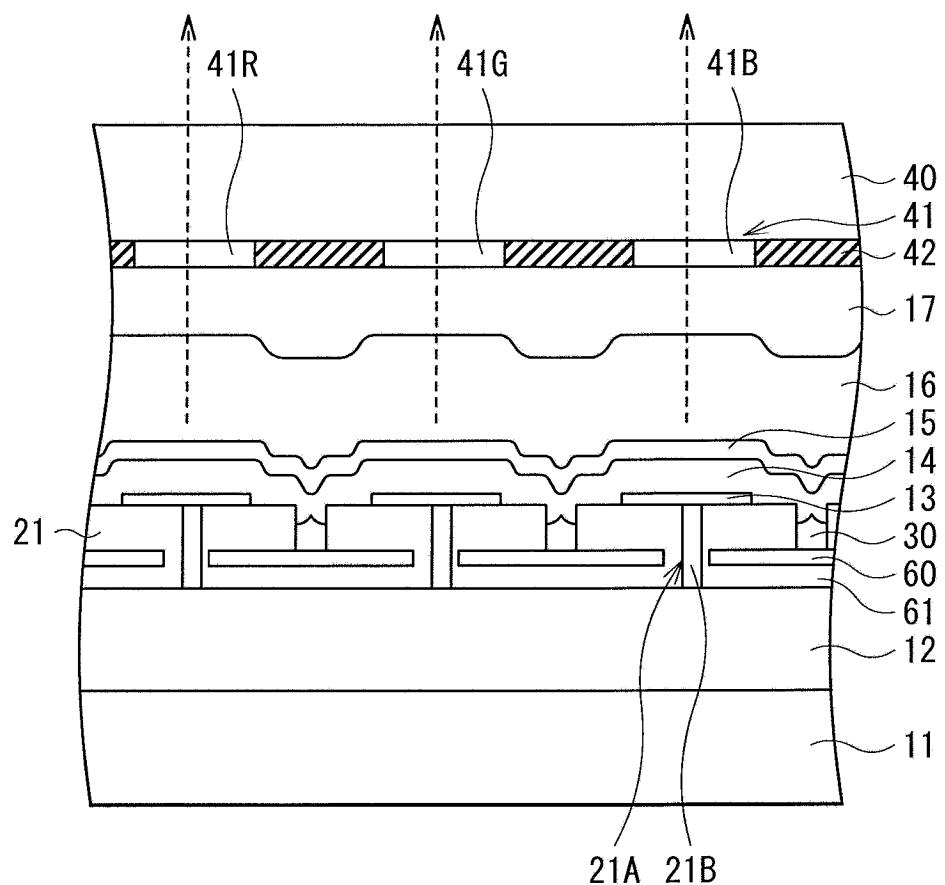

[0066] 图4示出了沿着图3的线IV-IV截得的截面结构。在基板11上,配置了包括上述像素驱动电路140的驱动电路层12等。基板11的配置了驱动电路层12的整个表面被第一绝缘膜21覆盖。在第一绝缘膜21上,配置了上述多个有机EL器件10R、10G和10B。在图4中,仅示出了有机EL器件10R和10G。在多个有机EL器件10R、10G和10B之间的器件间区域10A中,第二绝缘膜22被配置在第一绝缘膜21上。第一绝缘膜21和第二绝缘膜22组成图3中的绝缘膜20。沟槽30贯通第二绝缘膜22,并被配置在第一绝缘膜21在厚度方向上的一部分中。

[0067] 第一绝缘膜21用于平坦化其上形成像素电路层12的基板11的表面。第一绝缘膜21例如具有从100nm至1000nm(包括端点)的厚度,并且由氮氧化硅(SiON)或氧化硅(SiO<sub>2</sub>或SiO)制成。在第一绝缘膜21的构成材料是诸如SiON、SiO<sub>2</sub>和SiO的硅基材料的情况下,可通过刻蚀容易地形成深度在第一绝缘膜21的厚度方向上的沟槽30。第一绝缘膜21配置有用于连接至驱动电路层12的像素驱动电路140的驱动晶体管Tr1的接触孔21A。接触孔21A配置有由导电金属制成的插塞21B。

[0068] 第二绝缘膜22用于确保第一电极13与第二电极15之间的绝缘性,并且用于精确获得发光区的所需形状。第二绝缘膜22不仅覆盖器件间区域10A并且还覆盖第一电极13的顶面端部,并具有对应于第一电极13的发光区的开口22A。第二绝缘膜22例如具有从100nm至200nm(包括端点)的厚度,并且由SiON制成。在第二绝缘膜22的构成材料是诸如SiON的硅基材料的情况下,可通过刻蚀容易地形成深度在第二绝缘膜22的厚度方向上的沟槽30。

[0069] 有机EL器件10R、10G和10B被配置在第一绝缘膜21上。在有机EL器件10R、10G和10B

中,从靠近基板11一侧顺次层积第一电极13、包括发光层的有机层14和第二电极15。在图4中,尽管仅示出了有机EL器件10R和10G,但有机EL器件10B也具有同样结构。

[0070] 有机EL器件10R、10G和10B被保护膜16覆盖。并且,由玻璃等制成的密封基板40与保护膜16的整个表面贴合,其间介有粘附层17,从而密封有机EL器件10R、10G和10B。

[0071] 为多个有机EL器件10R、10G和10B的每一个配置第一电极13。第一电极13例如具有约100nm的厚度,由作为高反射材料的铝(AI)或包括铝(AI)的合金制成,并且从第二电极15一侧提取发光层产生的光(顶发光)。第一电极13的厚度优选为发光层产生的光不能从其透过并可以维持光提取效率的一个值,例如,在30nm至200nm(包括端点)范围内。第一电极13的构成材料的实例包括由铝(AI)、其合金、以及诸如金(Au)、铂(Pt)、镍(Ni)、铬(Cr)、铜(Cu)、钨(W)、钼(Mo)、钛(Ti)、钽(Ta)和银(Ag)等金属元素的单质或合金制成的反射电极。

[0072] 并且,第一电极13可具有约20nm厚的接触层(未示出),它作为上述反射电极的基底,由钛(Ti)、钨(W)、铜(Cu)、钽(Ta)、钼(Mo)等制成的。接触层还具有作为即使减小第一电极13的厚度仍能维持高反射率的反射辅助层的功能。在配置了接触层的情况下,第一电极13的厚度等于或大于15nm便足够了。

[0073] 并且,第一电极13可具有由作为接触层或反射辅助层的钛层、由铝或其合金等制成的上述反射电极、以及钛层或钽层构成的三层层积结构。另外,第一电极13可利用由上述反射电极和由ITO(铟锡氧化物)、IZO(注册商标)(铟锌复合氧化物)、SnO<sub>2</sub>等制成的透明电极构成的复合膜来形成。

[0074] 有机层14针对多个有机EL器件10R、10G和10B被公共地配置在第一电极13和第二绝缘膜22上。有机层14例如具有如图5所示从靠近第一电极13一侧顺次层积空穴注入层14A、空穴输送层14B、发光层14C和电子输送层14D的结构。

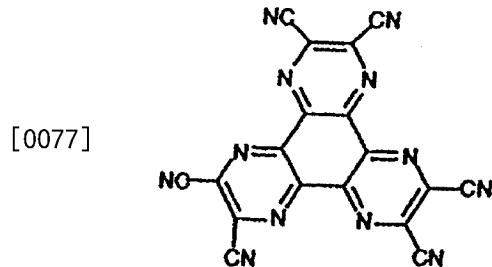

[0075] 空穴注入层14A用于提高空穴注入效率,并作为缓冲层防止泄漏。空穴注入层14A例如具有从2nm到10nm(包括端点)的厚度,并由化学式1所示的六氢基氮杂苯并菲(hexatriazatriphenylene)构成。

[0076] [化学式1]

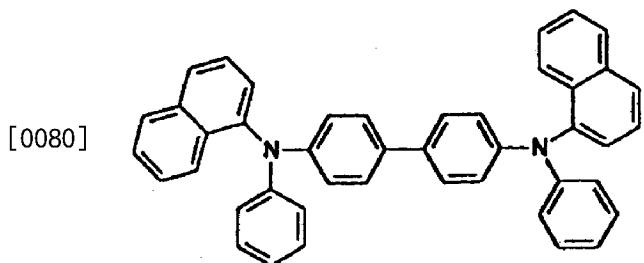

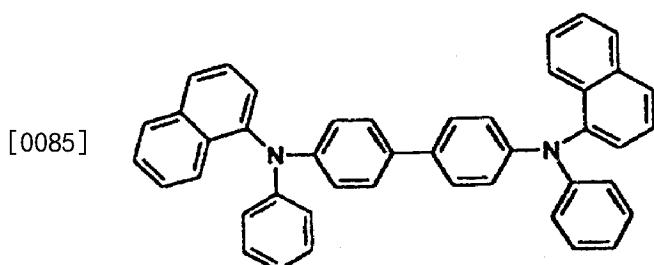

[0078] 空穴输送层14B用于提高向发光层14C的空穴注入效率。空穴输送层14B例如具有30nm的厚度,并由化学式2所示材料构成。

[0079] [化学式2]

[0081] 发光层14C是从靠近第一电极13一侧顺次层积10nm厚的红色发光层(未示出)、10nm厚的发光隔离层(未示出)、10nm厚的蓝色发光层(未示出)和10nm厚的绿色发光层而形成的白色发光层。通过施加电场,使得从第一电极13通过空穴注入层14A和空穴输送层14B注入的空穴的一部分与从第二电极15通过电子输送层14D注入的电子的一部分复合,从而红色发光层发出红光。发光隔离层用于减小向红色发光层的电子供给量。通过施加电场,使得从第一电极13通过空穴注入层14A、空穴输送层14B和发光隔离层注入的空穴的一部分与从第二电极15通过电子输送层14D注入的电子的一部分复合,从而蓝色发光层发出蓝光。通过施加电场,使得从第一电极13通过空穴注入层14A、空穴输送层14B和发光隔离层注入的空穴的一部分与从第二电极15通过电子输送层14D注入的电子的一部分复合,从而绿色发光层发出绿光。红色发光层、绿色发光层和蓝色发光层在对应于第二绝缘膜22的开口22A的区域中发光。

[0082] 红色发光层包括一种以上的红色发光材料、空穴输送材料、电子输送材料和双电荷(both-electric-charge)输送材料。红色发光材料可以是荧光材料或磷光材料。具体地,红色发光层例如具有约5nm的厚度,并由通过在4,4'-双(2,2-二苯乙烯基)联苯(DPVBi)中混合30wt%的2,6-双[(4'-(甲氧基二苯胺)苯乙烯基]-1,5二腈基萘(BSN)而获得的混合物构成。

[0083] 例如,发光隔离层由化学式3所示材料构成。

[0084] [化学式3]

[0086] 绿色发光层例如包括一种以上的绿色发光材料、空穴输送材料、电子输送材料和双电荷输送材料。绿色发光材料可以是荧光材料或磷光材料。具体地,绿色发光层例如具有约10nm的厚度,并由通过在DPVBi中混合5wt%的香豆素6而获得的混合物构成。

[0087] 蓝色发光层例如包括一种以上的蓝色发光材料、空穴输送材料、电子输送材料和双电荷输送材料。蓝色发光材料可以是荧光材料或磷光材料。具体地,蓝色发光层例如具有约30nm的厚度,并由通过在DPVBi中混合2.5wt%的4,4'-双[2-{4-(N,N-二苯胺)苯基}乙烯基]联苯(DPAVBi)而获得的混合物构成。

[0088] 电子输送层14D用于提高将电子注入到发光层14C的效率。电子输送层14D例如具有约20nm的厚度,并由8羟基喹啉铝(Alq3)构成。

[0089] 图4所示的第二电极15针对多个有机EL器件10R、10G和10B共同被配置在有机层14上。第二电极例如具有从靠近第一电极13一侧顺次层积约0.3nm厚的由氟化锂(LiF)构成的第一层、约3nm厚的由钙(Ca)构成的第二层以及约5nm厚的由Mg-Ag合金构成的第三层而形成的结构。由于以下原因,第二电极15在显示区110以外的区域中被连接至辅助配线(未示出)。即,由于有机层14针对多个有机EL器件10R、10G和10B共同被配置,所以不能为各个有机EL器件10R、10G和10B制作第二电极15与辅助配线之间的连接。

[0090] 图4所示的保护膜16例如具有从0.5μm到10μm(包括端点)的厚度,并由氮化硅(SiN)构成。图4所示的粘附层17例如是由紫外线固化树脂或热固性树脂构成。

[0091] 图4所示的密封基板40被置于有机EL器件10R、10G和10B的第二电极15一侧,并将有机EL器件10R、10G和10B连同粘附层17一起封住。密封基板40例如是由诸如对有机EL器件10R、10G和10B发出的光透明的玻璃等材料制成的。

[0092] 密封基板40例如配置有彩色滤光片41和作为黑矩阵的遮光膜42。彩色滤光片41用于从有机EL器件10R、10G和10B发出的白光中提取出红光、绿光或蓝光,并且具有红色滤光片41R、绿色滤光片41G和蓝色滤光片(未示出)。红色滤光片41R、绿色滤光片41G和蓝色滤光片(未示出)对应于有机EL器件10R、10G和10B而被顺次布置。红色滤光片41R、绿色滤光片41G和蓝色滤光片(未示出)分别是由混合有颜料的树脂制成的。通过选择颜料进行调整,使得在预定的红色、绿色或蓝色波长范围内的光透过率很高,并且在其他波长范围中的光透过率很低。

[0093] 遮光膜42用于吸收由有机EL器件10R、10G和10B以及其间的配线反射的外部光,从而改善对比度。遮光膜42例如是由混入黑色着色剂的具有等于或大于1的光学密度的黑色树脂膜、或通过利用薄膜干涉的薄膜滤光器构成。如上所述,遮光膜42优选由黑色树脂膜构成,因为这样可以廉价且容易地形成该膜。薄膜滤光器通过层积一层以上由金属、金属氮化物或金属氧化物构成的薄膜来获得,并且用于通过利用薄膜干涉来衰减光。薄膜滤光器的具体实例包括其中交替层积铬和氧化铬(III)(Cr<sub>2</sub>O<sub>3</sub>)的滤光器。

[0094] 图3和图4所示的沟槽30用于抑制如上所述的器件间区域10A中的驱动电流泄漏。即,有机层14被配置为多个有机EL器件10R、10G和10B共用的层。并且,图5所示的空穴注入层14A和空穴传送层14B在有机层14中具有相对较高的导电性。因此,空穴注入层14A和空穴传送层14B容易形成相邻有机EL器件10R、10G和10B的第一电极13之间的漏电路径。所以,例如,若有机EL器件10R发光,则相邻的有机EL器件10G也发光,从而单一红色色度被移位了。

[0095] 器件间区域10A中的这种漏电流的影响随着有机EL器件10R、10G和10B的尺寸缩小会越发显著。例如,将讨论图3中夹在有机EL器件10R的长边与相邻的有机EL器件10G的长边之间的矩形区域10A1中流通的漏电流IL。矩形区域10A1中的电阻R由有机EL器件10R与10G之间的距离和有机EL器件10R与10G的长边长度的比来确定(薄层电阻),并且是与有机EL器件10R、10G和10B的尺寸无关的常量。另外,有机EL器件10R、10G和10B的JV特性(J:电流密度)也是与有机EL器件10R、10G和10B的尺寸无关的常量。即,整个表面上用于100nit发光所需的电压V是与有机EL器件10R、10G和10B的尺寸无关的常量。因此,漏电流IL(=V/R)是与有机EL器件10R、10G和10B的尺寸无关的常量。同时,用于发光的驱动电流I<sub>0</sub>根据有机EL器件10R、10G和10B的尺寸而变化一个数量级以上。因此,漏电流IL相对于用于发光的驱动电流I<sub>0</sub>的比随有机EL器件10R、10G和10B的尺寸变小而变大,导致对图像质量产生更大影响。

[0096] 在该情况下,通过在器件间区域10A中配置沟槽30,如图5所示,空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1可被减薄至约为其沟槽30外厚度t2的十分之一。因此,可以增大空穴注入层14A和空穴输送层14B在沟槽30内的电阻,并抑制器件间区域10A中的驱动电流泄漏。从而,漏电流 $I_L$ 相对于用于发光的驱动电流 $I_0$ 的比变为等于或小于百分之几,并且漏电流对图像质量的影响可被降至几乎不可见的水平。

[0097] 沟槽30的宽度w优选等于或小于有机层14的总膜厚,且具体地,优选从10nm到150nm(包括端点)。因此,如图5所示,发光层14C可以跨过沟槽30连续。从而,电子输送层14D和第二电极15可以在沟槽30上方保持连续而不被截断成部分。因此,可以避免第二电极15被沟槽30切断的现象发生,并且可以在列方向以及行方向上将沟槽配置成格子状。

[0098] 图6示出了通过检测沟槽30的深度d与包括沟槽30的器件间区域10A的薄层电阻之间的关系而获得的结果。图6示出了多个有机EL器件10R、10G和10B的节距p约为3.3μm的情况的测量结果。从表6可看出,随着沟槽30的深度d加深,可以更多地减小漏电流。例如,为了近乎完全地抑制节距p约为3.3μm的情况下相邻器件的发光,可能需要约2\*12Ω/□的薄层电阻等效值,且可能需要等于或大于500nm的深度d。

[0099] 下文中,将对有机EL器件10R、10G和10B的节距与所需电阻值之间的关系给予描述。

[0100] 将对具有不同节距的两种类似形状的像素给予讨论,其中,各自节距为p和p';各自的发光面积为S和S';各自的驱动电流为 $I_0$ 和 $I_0'$ ;各自的漏电流为 $I_L$ 和 $I_L'$ ;并且各自所需的电阻值为R和R'。

[0101] 对于一定的亮度,各自的电流密度是一致的。因此,建立表达式如下:

$$[0102] I_0' = (S'/S)I_0$$

$$[0103] = (p'/p)^2 I_0$$

[0104] 其中,漏电流 $I_L$ 与所需驱动电流 $I_0$ 的比为r和r',则建立表达式如下:

$$[0105] I_L = r I_0$$

$$[0106] I_L' = r I_0'$$

[0107] 其中,  $r' = r$

[0108] 并且,各自的驱动电压是一致的,为V。因此,建立表达式如下:

$$[0109] R' = V/I_L'$$

$$[0110] = (r I_0 R) / (r I_0')$$

$$[0111] = (I_0 R) / ((p'/p)^2 I_0)$$

[0112] 所以,建立表达式如下:

$$[0113] R'/R = (p/p')^2$$

[0114] 图7A至图7C示出了通过使一个器件发光并测量与所述器件相邻的一个器件的亮度相对所述器件的亮度的比而获得的结果。实际发光的器件被置于横轴的从0.5到1(包括端点)的附近,并且与其相邻的器件被置于横轴的从3.5到4(包括端点)的附近。图7A示出了未配置沟槽的比较例1的测量结果,图7B示出了沟槽30的深度d为300nm的实例1-1的测量结果,并且图7C示出了沟槽30的深度d为700nm的实例1-2的测量结果。此外,在图7A至7C中,实线表示相邻器件是浮置器件的情况下亮度,并且虚线表示相邻器件被接地(0V)的情况下亮度。两个亮度值之间的差代表漏电流。图8A至图8C表示通过放大上述差而得到的测量

结果。

[0115] 从图7A至图7C以及图8A至图8C可看出,在配置了沟槽30的实例1-1和1-2中,相邻器件的亮度比低于未配置沟槽的比较例1的亮度比。即,可以发现,在器件间区域10A中配置沟槽30的情况下,可以抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。

[0116] 并且,比较实例1-1与实例1-2,随着沟槽30的深度d加深,相邻器件的亮度比由于以下可能原因会更低。即,空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1极薄,并且增大了具有这一很薄厚度t1的部分的电阻。因此,随着沟槽30的深度d加深,整个器件间区域10A的电阻被增大了。即,可以发现,随着沟槽30的深度d加深,可以抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。

[0117] 例如,可以如下制造该显示单元。

[0118] 图9至图15示出了一种以所示步骤顺序制造显示单元的方法。首先,如图9所示,在由上述材料制成的基板11上形成包括像素驱动电路140的驱动电路层12。接下来,例如通过等离子体CVD(等离子体增强化学气相沉积)法形成例如具有从100nm到1000nm(包括端点)厚度的例如SiON膜、SiO<sub>2</sub>膜或SiO膜。随后,例如通过光刻法和干法刻蚀法,以确定形状形成SiON膜、SiO<sub>2</sub>膜或SiO膜。再如图9所示,形成具有接触孔21A的第一绝缘膜21。在此之后,再次如图9所示,将由导电金属制成的插塞21B埋入第一绝缘膜21的接触孔21A中。

[0119] 之后,例如通过溅射法在第一绝缘膜21上形成例如钛膜和铝合金膜(未示出)。在此之后,例如通过光刻法和干法刻蚀法,以确定形状形成钛膜和铝合金膜,从而如图10所示,为多个有机EL器件10R、10G和10B中的每一个形成第一电极13。

[0120] 形成第一电极13之后,在第一电极13和第一绝缘膜21上,通过PECVD法形成例如具有从10nm到200nm(包括端点)厚度的SiON膜。例如通过光刻法和干法刻蚀法,以确定形状形成该SiON膜,从而如图11所示,形成具有开口22A的第二绝缘膜22。

[0121] 形成第二绝缘膜22之后,如图12所示,例如通过光刻法和干法刻蚀法,在第二绝缘膜22和第一绝缘膜21中配置沟槽30。在第一绝缘膜21中,可以配置用于刻蚀沟槽30的停止层(未示出)。

[0122] 配置了沟槽30之后,如图13所示,在第一电极13和第二绝缘膜22上,例如通过蒸发法形成有机层14的空穴注入层14A和空穴输送层14B。此时,空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1被减薄至约为其沟槽30外厚度t2的十分之一。因此,增大了空穴注入层14A和空穴输送层14B在沟槽30内的电阻,并且抑制了器件间区域10A中的驱动电流泄漏。

[0123] 随后,如图14和图15所示,例如通过蒸发法形成有机层14的发光层14C和电子输送层14D。而后,例如通过真空蒸发法形成第二电极15。此时,由于沟槽30的宽度w例如等于或小于有机层14的总膜厚,具体为从10nm到150nm(包括端点),所以发光层14C可以跨过沟槽30连续。从而,电子输送层14D和第二电极15可以在沟槽30上方保持连续而不被截断成部分,并且这可以避免第二电极15被沟槽30截断成部分的状态出现。从而,形成了图3和图4所示的有机EL器件10R、10G和10B。

[0124] 随后,如图4所示,例如通过CVD法或溅射法,在有机EL器件10R、10G和10B上形成由上述材料制成的保护膜16。

[0125] 此外,再如图4所示,例如在由上述材料制成的密封基板40上形成由上述材料制成

的遮光膜42。随后,通过旋转涂布等将红色滤光片41R的材料涂覆在密封基板40上。通过光刻技术来图案化该产物,再经烧制,从而形成红色滤光片41R。而后,以与红色滤光片41R相同的方式相继形成蓝色滤光片(未示出)和绿色滤光片41G。

[0126] 在此之后,再如图4所示,在保护膜16上形成粘附层17,并且将密封基板40与保护层16贴合,且其间介有粘附层17。从而,制成了图1至图4所示的显示单元。

[0127] 在该显示单元中,从扫描线驱动电路130通过写入晶体管Tr2的栅电极向各像素提供扫描信号,并且来自信号线驱动电路120的图像信号通过写入晶体管Tr2而被保持在保持电容Cs中。即,根据保持在保持电容Cs中的信号来控制驱动晶体管Tr1导通/截止,从而将驱动电流Ids注入各有机EL器件10R、10G和10B中,产生电子-空穴复合,并因此发光。光从第二电极15、保护膜16、粘附层17、彩色滤光片41和密封基板40透过(顶发光),并被提取出。

[0128] 在该情况下,在多个有机EL器件10R、10G和10B之间的器件间区域10A中配置绝缘膜20(第一绝缘膜21和第二绝缘膜22)。绝缘膜20在相邻有机EL器件10R和10G(相邻有机EL器件10G和10B、或相邻有机EL器件10B和10R)之间的位置处具有沟槽30。因此,有机层14中具有较高导电性的层(诸如空穴注入层14A和空穴输送层14B)在沟槽30内的厚度t1小于其沟槽30外厚度t2,并增大了沟槽30内的电阻。从而,抑制了相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。

[0129] 如上所述,在本实施方式的显示单元中,在多个有机EL器件10R、10G和10B之间的器件间区域10A中配置绝缘膜20(第一绝缘膜21和第二绝缘膜22)。绝缘膜20中,在相邻有机EL器件10R和10G(或相邻有机EL器件10G和10B、或相邻有机EL器件10B和10R)之间的位置处配置沟槽30。从而,可以抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。此外,不同于现有显示单元,它在蒸发步骤过程中,不需要对倒锥形分隔壁进行热处理以将其形状改变为正锥形,因此避免了特性的下降。

[0130] 在上述实施方式中,已对层积第一绝缘膜21和第二绝缘膜22作为绝缘膜20的情况给予了描述。然而,可以省去第二绝缘膜22,并且仅配置第一绝缘膜21作为绝缘膜20。

[0131] [第二实施方式]

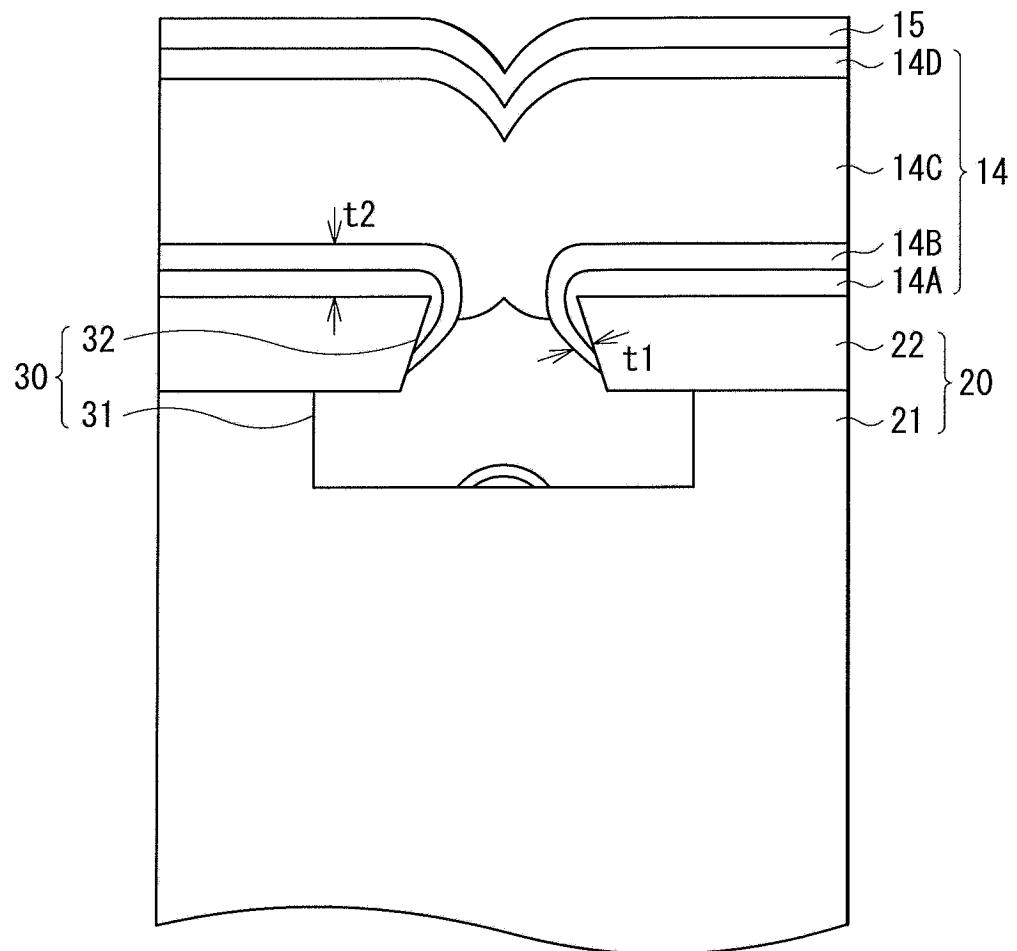

[0132] 图16示出了在根据本公开第二实施方式的显示单元中的显示区110的沟槽30附近的区域的经放大后的截面结构。在本实施方式中,空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1随着其在沟槽30中的位置变深而变薄。因此,在本实施方式中,可以更多地增加空穴注入层14A和空穴输送层14B的电阻,并且可以更好地抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。除了这一点,本实施方式的显示单元具有与上述第一实施方式同样的结构、同样的功能以及同样的效果。

[0133] 例如,可以如下制造该显示单元。由于制造步骤类似于第一实施方式,故将参照图9至图15给予描述。

[0134] 首先,如图9所示,与第一实施方式一样,在基板11上形成包括像素驱动电路140的驱动电路层12和第一绝缘膜21。

[0135] 接下来,如图10所示,与第一实施方式一样,在第一绝缘膜21上为多个有机EL器件10R、10G和10B中的每一个形成第一电极13。

[0136] 随后,如图11所示,与第一实施方式一样,形成第二绝缘膜22。

[0137] 在此之后,如图12所示,与第一实施方式一样,在第二绝缘膜22和第一绝缘膜21中

配置沟槽30。

[0138] 在配置了沟槽30之后,如图13至图15所示,在第一电极13和第二绝缘膜22上方,例如通过蒸发法形成有机层14的空穴注入层14A、空穴输送层14B、发光层14C和电子输送层14D。

[0139] 在形成有机层14的步骤中,如图17所示,基板11上的沟槽30与蒸发源50之间的位置关系优选满足数学表达式1。因此,如图16所示,可以使空穴注入层14A和空穴输送层14B的沟槽30内的厚度t1随其在沟槽30中的位置变深而变薄。需要注意的是,在该情况下,基板11并不指基板11本身,而是指蒸发时基板11的表面,具体地,第二绝缘膜22的表面。

[0140] [数学表达式1]

[0141]  $X/Y > w/d$

[0142] 在该表达式中,X表示从沟槽30的入口边缘到蒸发源50的偏移距离,Y表示基板11与蒸发源50之间的距离,w表示沟槽宽度,并且d表示沟槽30的深度。

[0143] 数学表达式1在图17中表示 $\tan\theta > \tan\alpha$ ,即, $\theta > \alpha$ ,其中 $\theta$ 是由从蒸发源50向基板11所引的垂线与从蒸发源50到沟槽30的入口的直线形成的角度,并且 $\alpha$ 是由沟槽30的壁表面与从沟槽30的入口到其底面的直线形成的角度。

[0144] 作为蒸发方法,例如可使用旋转蒸发法或线性蒸发法。旋转蒸发法是一种使用单元型蒸发源50并且当基板11在蒸发源50上方旋转时实现成膜的方法。此时,将蒸发源50布置成使得基板11上的沟槽30与蒸发源50之间的位置关系满足数学表达式1。并且,只要在基板11旋转一周期间的部分或全部时间内满足数学表达式1,即可达到上述减薄空穴注入层14A和空穴输送层14B的膜厚的效果。

[0145] 在旋转蒸发法中,材料被放进蒸发源的坩埚(未示出)中,并通过用加热器加热坩埚来蒸发该材料。作为坩埚的材料,期望诸如PBN和氧化铝的陶瓷、钽等。被蒸发的分子按照蒸发源50的指向性(n值)直线飞行,并沉积在基板11上。在该情况下,n值表示在给定位置处的蒸发密度A相对中心处的蒸发密度A0的比( $A/A_0$ ),并且是近似由 $\cos n\theta$ 获得的值。

[0146] 例如,如图19和图20所示,线性蒸发法是一种使用长蒸发源50并且当蒸发源50和作为蒸发对象的基板11以箭头A11的方向相对移动时进行成膜的方法。在线状蒸发源50中,沿纵向配置了多个开口51,并从各开口51喷出蒸发材料。通过在基板移动方向A11上配置限制板52来确定运送方向上的成膜宽度53。此时,将蒸发源50布置成使得基板11上的沟槽30与蒸发源50之间的位置关系满足数学表达式1。并且,只要在基板11通过蒸发源50期间的部分或全部时间内满足数学表达式1,即可达到上述减薄空穴注入层14A和空穴输送层14B的膜厚的效果。

[0147] 此外,在形成有机层14的空穴注入层14A和空穴输送层14B的步骤中,由于以下原因,优选应满足数学表达式1。空穴注入层14A和空穴输送层14B在有机层14中具有较高导电性,并且相邻有机EL器件10R、10G和10B之间容易形成漏电路径。

[0148] 形成有机层14之后,如图14和图15所示,与第一实施方式一样,形成第二电极15。从而,形成如图3和图4所示的有机EL器件10R、10G和10B。

[0149] 随后,如图4所示,与第一实施方式一样,在有机EL器件10R、10G和10B上形成由上述材料制成的保护膜16和粘附层17。将此产物与配置有彩色滤光器41和遮光膜42的密封基板40贴合。从而,制成了图1至图4所示的显示单元。

[0150] 图21是空穴注入层14A和空穴输送层14B在沟槽30内的厚度分布的第一仿真结果。作为仿真条件,假设了沟槽30的宽度w为 $0.4\mu\text{m}$ 、深度d为 $3.0\mu\text{m}$ 、从沟槽30的入口边缘到蒸发源50的偏移距离X为200mm、基板11与蒸发源50之间的距离Y为600mm、并且蒸发源50的指向性n值为2的一种旋转蒸发法(见图18)。空穴注入层14A和空穴输送层14B的沟槽30外的厚度(目标厚度)为10nm。

[0151] 从图21可看出,基板11上的沟槽30与蒸发源50之间的位置关系满足数学表达式1,并且空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1直到沟槽30的深度d1达到 $1.2\mu\text{m}$ 之前都是恒定的。在沟槽30的深度d1大于 $1.2\mu\text{m}$ 的情况下(由图21中的虚线圈出的部分),空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1随沟槽30的深度变大而变小(由图21中的虚线圈出的部分)。

[0152] 图22是空穴注入层14A和空穴输送层14B在沟槽30内的厚度分布的第二仿真结果。作为仿真条件,假设了沟槽30的宽度w为 $0.6\mu\text{m}$ 、深度d为 $2.0\mu\text{m}$ 、运送方向上的成膜宽度53为200mm、基板11与蒸发源50之间的距离Y为100mm、并且蒸发源50的指向性n值为10的线性蒸发(见图19和图20)。空穴注入层14A和空穴输送层14B在沟槽30外的厚度(目标厚度)为10nm。

[0153] 从图22可看出,基板11上的沟槽30与蒸发源50之间的位置关系满足数学表达式1,并且空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1直到沟槽30的深度d1达到 $0.6\mu\text{m}$ 之前都是恒定的。在沟槽30的深度d1大于 $0.6\mu\text{m}$ 的情况下(由图22中的虚线圈出的部分),空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1随沟槽30的深度变大而变小。

[0154] 图23是空穴注入层14A和空穴输送层14B在沟槽30内的厚度分布的第三仿真结果。作为仿真条件,假设了沟槽30的宽度w为 $0.6\mu\text{m}$ 、深度d为 $1.5\mu\text{m}$ 、从沟槽30的入口边缘到蒸发源50的偏移距离X为150mm、基板11与蒸发源50之间的距离Y为500mm、并且蒸发源50的指向性n值为2的旋转蒸发法(见图18)。空穴注入层14A和空穴输送层14B在沟槽30外的厚度(目标厚度)为10nm。

[0155] 从图23可看出,基板11上的沟槽30与蒸发源50之间的位置关系不满足数学表达式1,并且空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1即使在沟槽30的深度变得很大之后都是恒定的。然而,空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1被减薄至约为其沟槽30外厚度t2的十分之一,这意味着获得了通过沟槽30减薄膜厚的效果。

[0156] 即,可以发现,在形成有机层14的步骤中满足了数学表达式1的情况下,可以更多地减薄空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1、可以更多地增大电阻、并且可以更好地抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。

[0157] [第三实施方式]

[0158] 图24示出了在根据本公开第三实施方式的显示单元中的显示区的一部分的平面结构。在本实施方式中,为多个有机EL器件10R、10G和10B的各行在列方向上配置沟槽30。从而,抑制了第二电极15的电压降,并提高了图像质量。除了这一点,本实施方式的显示单元具有与上述第一或第二实施方式同样的结构、同样的功能和同样的效果,并且可被类似地制造。

[0159] 例如,在相邻有机EL器件10R、10G和10B的列与列之间的区域配置具有与有机EL器件10R、10G和10B的长边几乎相同的长度的各沟槽30。沟槽30之间在列方向上具有间距L。

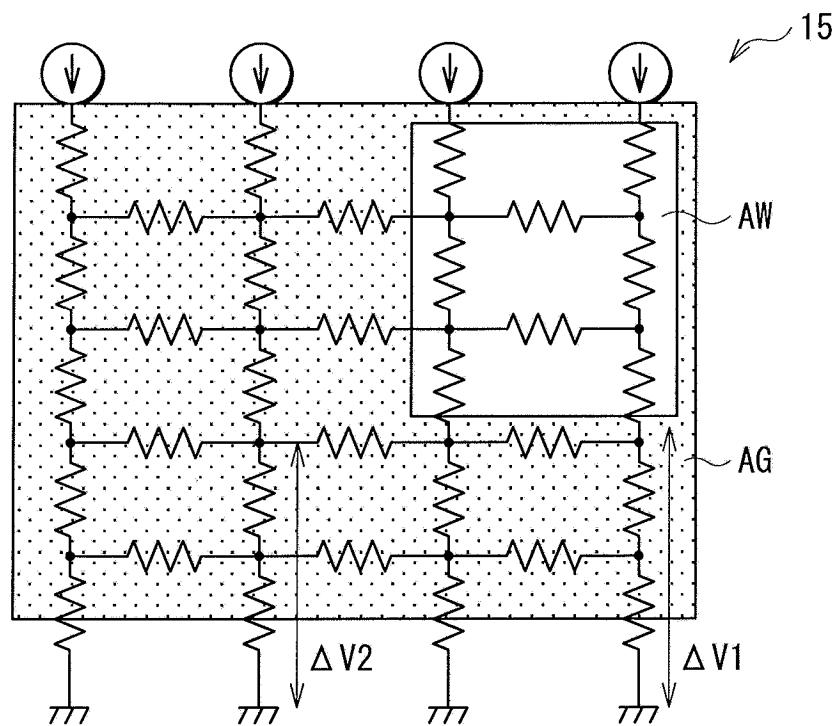

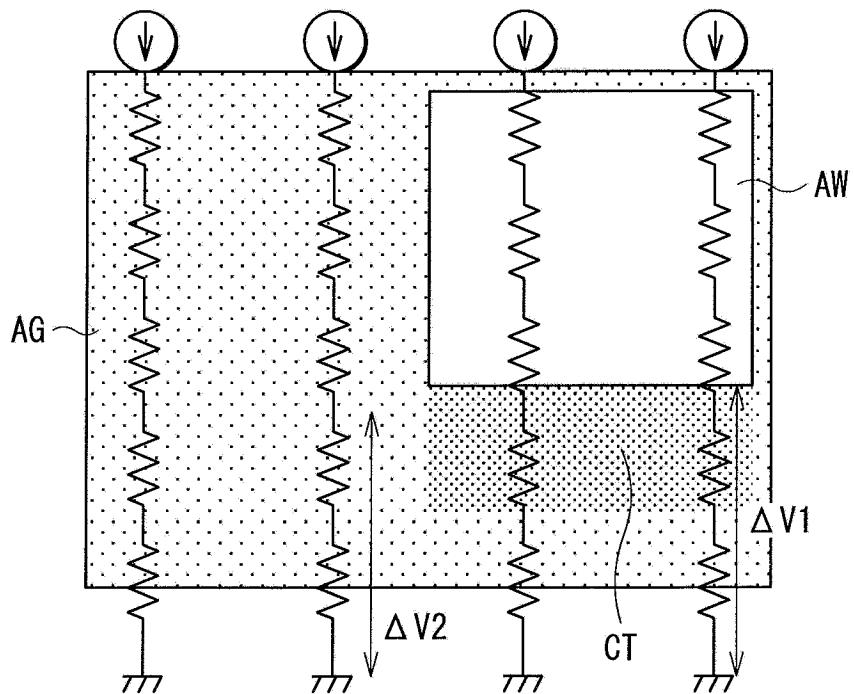

[0160] 图25示出了在本实施方式中第二电极15的等效电路,并且示出了在重叠在该等效电路上的右上区域AW显示白且其他区域AG显示灰的情况下显示状态。在本实施方式的第二电极15的等效电路中,电阻元件在列方向和行方向两个方向上被连接成格子状。因此,白显示区AW的电压降 $\Delta V1$ 近似等于灰显示区AG的电压降 $\Delta V2$ ( $\Delta V1 \approx \Delta V2$ )。从而,显示均匀的灰色。

[0161] 同时,图26示出了在第一实施方式中第二电极15的等效电路,并且示出了在重叠在该等效电路上的右上区域AW显示白且其他区域AG显示灰的情况下显示状态。在第一实施方式的第二电极15的等效电路中,电阻元件仅在列方向上被连接,并未在行方向上被连接。因此,白显示区AW的电压降 $\Delta V1$ 大于灰显示区AG的电压降 $\Delta V2$ ( $\Delta V1 > \Delta V2$ )。从而,减小了在白显示区AW上下的有机EL器件10R、10G和10B中流通的驱动电流 $Ids$ (见图27),并在相对于白显示区AW的纵向上发生暗串扰CT。串扰CT与正常灰显示区AG之间的亮度差约为10%。电流 $Ids$ 由数学表达式2来表示。

[0162] [数学表达式2]

$$[0163] Ids = \left( V_{sig} - \frac{C_p}{C_s + C_p} \Delta V_{cath} \right)^2$$

[0164] 图28和图29示出了在改变各沟槽30之间的列方向上的间距L(见图24)和第二电极15的Mg-Ag合金层厚度的情况下,第二电极15的列方向上的电阻R1和第二电极15的行方向上的电阻R2的仿真结果。

[0165] 从图29可以看出,在为多个有机EL器件10R、10G和10B的各行配置沟槽30的本实施方式中,与为多个有机EL器件10R、10G和10B的多个行连续配置沟槽30的第一实施方式相比,第二电极15的行方向上的电阻R2明显被降低。即,可以发现,在为多个有机EL器件10R、10G和10B的各行在列方向上配置沟槽30的情况下,可能降低第二电极15的行方向上的电阻R2。

[0166] 此外,将沟槽30之间的列方向上的间距L为 $1.0\mu\text{m}$ 的情况与沟槽30之间的列方向上的间距L为 $2.4\mu\text{m}$ 的情况相比较,在间距L为 $2.4\mu\text{m}$ 的情况下第二电极15的行方向上的电阻R2更低。即,可以发现,在沟槽30之间的列方向上的间距L较宽的情况下,可能降低第二电极15的行方向上的电阻R2。

[0167] 图30示出了在与图28一样改变沟槽30之间的列方向上的间距L(见图24)和第二电极15的Mg-Ag合金层厚度的情况下,电压降的仿真结果。作为仿真条件,假设显示区110的整个表面上的电流值为15mA,仅点亮了通过分割显示区110而获得的25个块中的两个块。因此,流通的电流为 $15\text{mA}/25*2 = 1.2\text{mA}$ 。电压降是电流流通的列中的电压V1与电流不流通的列中的电压V2之间的差( $V1 - V2$ )。并且,在图30中,串扰成为视觉上可容许水平的程度的基准值是20mV。

[0168] 从图30可以看出,在为多个有机EL器件10R、10G和10B的各行配置沟槽30的本实施方式中,与为多个有机EL器件10R、10G和10B的多个行连续配置沟槽30的第一实施方式相比,电压降明显被减小。即,可以发现,在为多个有机EL器件10R、10G和10B的各行在列方向上配置沟槽30的情况下,可以减小电压降,并且可以抑制图像质量的下降。

[0169] 此外,若在沟槽30之间的列方向上的间距L为 $1.0\mu\text{m}$ 的情况、沟槽30之间的列方向上的间距L为 $2.15\mu\text{m}$ 的情况、以及沟槽30之间的列方向上的间距L为 $2.4\mu\text{m}$ 的情况下进行比

较,则在间距L较宽的情况下,电压降较低。在各沟槽30之间的列方向上的间距L为 $1.0\mu\text{m}$ 的情况下,为获得等于或小于基准值的串扰,第二电极15的Mg-Ag合金层的厚度可能要等于或大于 $4.6\text{nm}$ 。同时,在沟槽30之间的列方向上的间距L为 $2.15\mu\text{m}$ 的情况下以及在沟槽30之间的列方向上的间距L为 $2.4\mu\text{m}$ 的情况下,即便第二电极15的Mg-Ag合金层的厚度为 $4.0\text{nm}$ ,串扰也等于或小于基准值。即,可以发现,在沟槽30之间的列方向上的间距L较宽的情况下,可以减小电压降以提高图像质量。

[0170] [第四实施方式]

[0171] 图31示出了在根据本公开第四实施方式的显示单元中的显示区的一部分的截面结构。根据第四实施方式的显示单元,除了沟槽30是由第一绝缘膜21的第一沟槽31和第二绝缘膜22的第二沟槽32以两步骤方式构成的之外,具有与上述第一至第三实施方式类似的结构、类似的功能和类似的效果,并且可以与上述第一至第三实施方式类似的方式来制造。

[0172] 第一绝缘膜21与第一实施方式一样,例如具有从 $100\text{nm}$ 至 $1000\text{nm}$ (包括端点)的厚度,并且由氮氧化硅(SiON)或氧化硅(SiO<sub>2</sub>或SiO)构成。

[0173] 在本实施方式中,由于以下原因,第二绝缘膜22优选由高温形成的SiO<sub>2</sub>构成。即,在增大SiO<sub>2</sub>的膜密度的情况下,刻蚀时的速率低于第一绝缘膜21的刻蚀速率,从而形成遮盖部32A。这里的高温成膜具体是指在大约从 $400^\circ\text{C}$ 到 $500^\circ\text{C}$ (包括端点)下成膜。例如,在从 $250^\circ\text{C}$ 到 $350^\circ\text{C}$ (包括端点)下形成第一绝缘膜21的SiO<sub>2</sub>。

[0174] 第二沟槽32的宽度w2比第一沟槽31的宽度w1窄。换句换说,在第二沟槽32的周边配置了突向第一沟槽31中心的遮蔽部32A。从而,如图32所示,尽管空穴注入层14A和空穴输送层14B被附着到第二沟槽32的内部,但空穴注入层14A和空穴输送层14B在第二沟槽32与第一沟槽31之间的边界处被完全切断。因此,可以抑制相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。此外,在第一实施方式中,为充分减薄空穴注入层14A和空穴输送层14B在沟槽30内的厚度t1,第二沟槽32可能要有几百微米的深度d。然而,本实施方式中不存在这一需要。

[0175] 例如,沟槽32的宽度w2优选等于或小于有机层14的总膜厚,且具体地,优选从 $10\text{nm}$ 到 $150\text{nm}$ (包括端点)。因此,如图32所示,发光层14C可以跨过第二沟槽32连续。从而,电子输送层14D和第二电极15可以在沟槽30上方保持连续且不被截断成部分。因此,可以避免第二电极15被沟槽30切断的现象发生,并且可以在列方向以及行方向上将沟槽配置成格子状。

[0176] 例如,可以如下制造该显示单元。由于制造步骤类似于第一实施方式,故将参照图9至图15给予描述。

[0177] 首先,如图9所示,与第一实施方式一样,在基板11上方形成包括像素驱动电路140的驱动电路层12和由SiON或SiO<sub>2</sub>构成的第一绝缘膜21。

[0178] 接下来,如图10所示,与第一实施方式一样,在第一绝缘膜21上为多个有机EL器件10R、10G和10B的每一个形成第一电极13。

[0179] 随后,如图11所示,与第一实施方式一样,形成由高温形成的SiO<sub>2</sub>构成的第二绝缘膜22。

[0180] 在此之后,例如通过光刻法和干法刻蚀,配置穿透第二绝缘膜22的第二沟槽32并在第一绝缘膜21中配置第一沟槽31。

[0181] 在配置了第二沟槽32之后,再对第一沟槽31和第二沟槽32进行湿法刻蚀。作为用

于湿法刻蚀的化学药品,优选使用氢氟酸。从而,在湿法刻蚀速率高的第一绝缘膜21中增大了第一沟槽31的宽度w1,同时在湿法刻蚀速率低的第二绝缘膜22中,第二沟槽32的宽度w2比第一沟槽31的宽度w1窄。在第二沟槽32的周边,形成了突向第一沟槽31中央的遮蔽部32A。

[0182] 关于沟槽30的平面形状,可以与第一实施方式一样,遍及多个有机EL器件10R、10G和10B的多个行连续地配置沟槽30。并且,可以与第三实施方式一样,为多个有机EL器件10R、10G和10B的各行配置沟槽30。

[0183] 在配置了具有第一沟槽31和第二沟槽32的阶梯状沟槽30之后,如图13至图15所示,与第一或第二实施方式一样,在第一电极13和第二绝缘膜22上方,例如通过蒸发法形成有机层14的空穴注入层14A、空穴输送层14B、发光层14C和电子输送层14D。

[0184] 在形成了有机层14之后,如图14和图15所示,与第一实施方式一样,形成第二电极15。从而,形成了如图3和图4所示的有机EL器件10R、10G和10B。

[0185] 随后,如图4所示,与第一实施方式一样,在有机EL器件10R、10G和10B上形成由上述材料制成的保护膜16和粘附层17。将此产物与配置有彩色滤光器41和遮光膜42的密封基板40贴合。从而,制成了图1至图4所示的显示单元。

[0186] 在上述实施方式中,已对第二沟槽32的侧面是垂直面的情况给予了描述。然而,第二沟槽32的侧面可以是如图33所示的倒锥形状(第二沟槽32的宽度随着第二沟槽32加深而变宽)。

#### [0187] [第五实施方式]

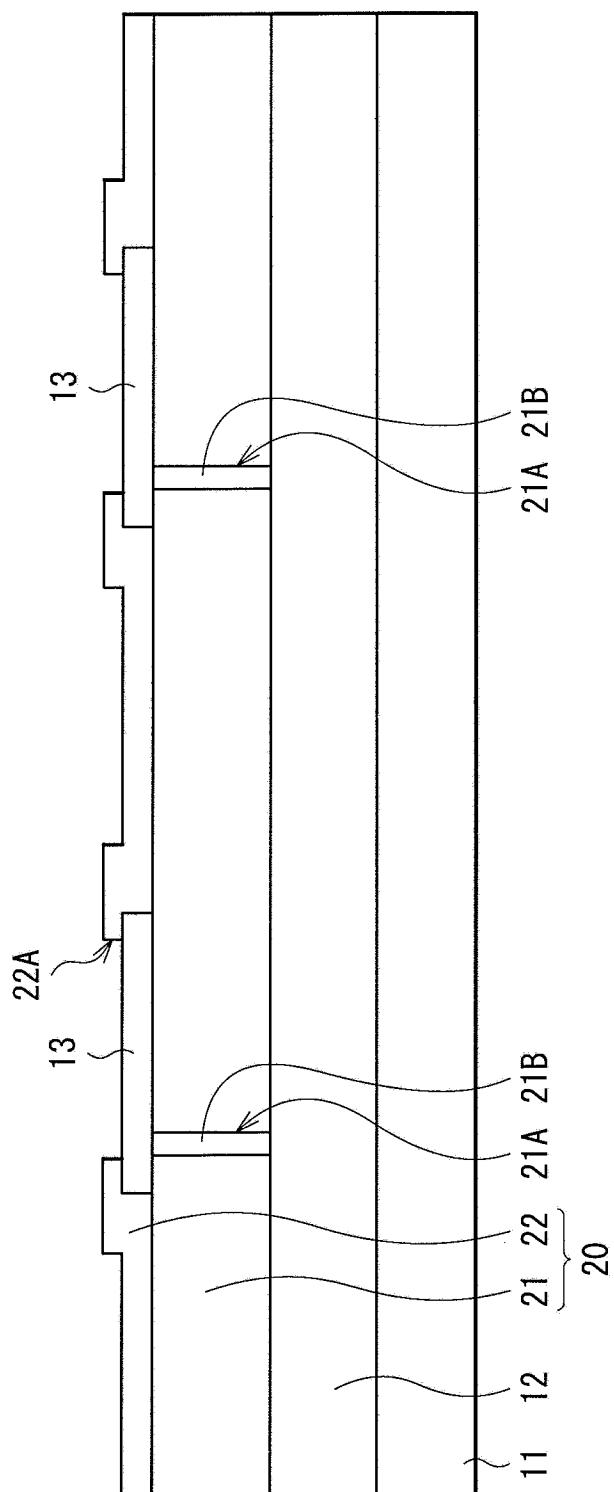

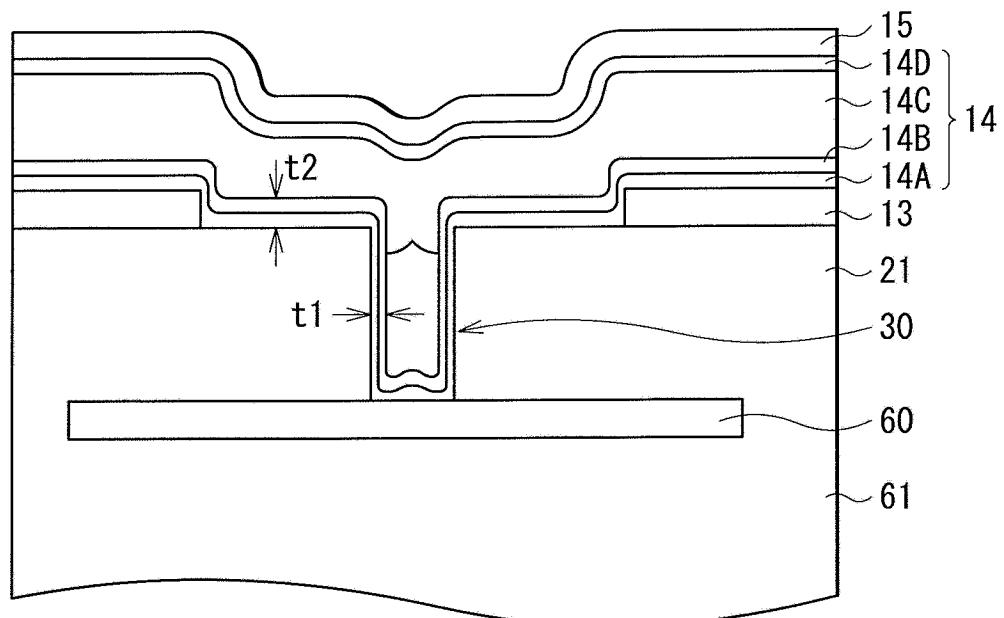

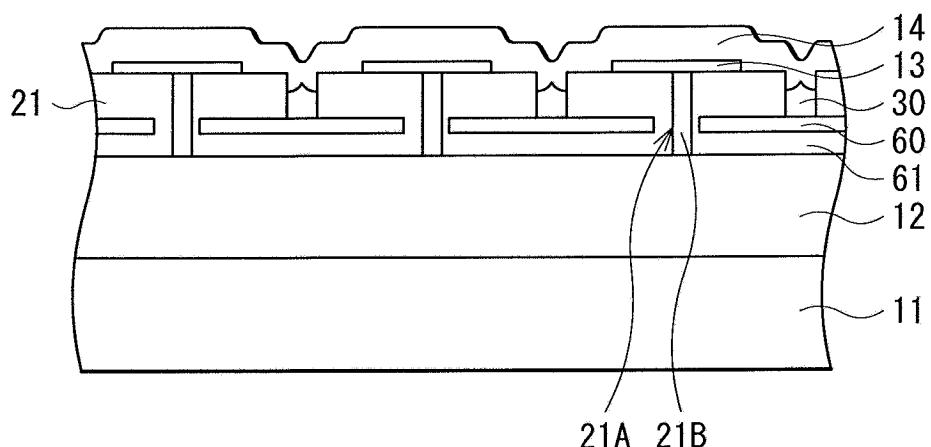

[0188] 图34示出了在根据本公开第五实施方式的显示单元中的显示区的一部分的截面结构。图35示出了在图34所示的沟槽30附近的区域的放大图。在本实施方式中,在沟槽30的底面上配置导电膜60。通过将导电膜60连接到预定电位,几乎完全抑制了相邻有机EL器件10R、10G和10B之间的驱动电流泄漏。并且,在本实施方式中,省去第二绝缘膜22,且仅配置第一绝缘膜21作为绝缘膜20。除了这些点,本实施方式的显示单元具有与第一至第三实施方式类似的结构、类似的功能和类似的效果。

[0189] 如上所述,导电膜60被连接到诸如地电位和第二电极15的电位(阴极电位)的预定电位。从而,通过空穴注入层14A和空穴输送层14B传输的漏电流被短路至导电膜60,且几乎完全抑制了相邻有机EL器件10R、10G和10B之间的漏电流。第二电极15由于以下原因而在显示区110以外的区域中被连接至辅助配线(未示出)。即,由于有机层14针对多个有机EL器件10R、10G和10B共同被配置,所以不可能针对各个有机EL器件10R、10G和10B将第二电极15与辅助配线连接。

[0190] 导电膜60是由诸如氮化钛(TiN)的导电材料制成。导电膜60优选是能遮挡进入驱动电路层12的像素驱动电路140的驱动晶体管Tr1或写入晶体管Tr2的光的遮光层。

[0191] 关于沟槽30的平面形状,可以与第一实施方式一样,遍及多个有机EL器件10R、10G和10B的多个行连续地配置沟槽30。并且,可以与第三实施方式一样,为多个有机EL器件10R、10G和10B的各行配置沟槽30。

[0192] 例如,可以如下制造该显示单元。由于制造步骤类似于第一实施方式,故将参照图9至图15给予描述。

[0193] 首先,如图36A所示,与由图9所示步骤表示的第一实施方式一样,在基板11上形成

包括像素驱动电路140的驱动电路层12。

[0194] 接下来,如图36B所示,在驱动电路层12上配置层间绝缘膜61,并在层间绝缘膜61上形成由上述材料制成的导电膜60。

[0195] 随后,如图36C所示,与由图9所示步骤表示的第一实施方式一样,在层间绝缘膜61和导电膜60上形成具有接触孔21A的第一绝缘膜21。在此之后,再如图36C所示,在接触孔21A中形成插塞21B。

[0196] 在形成第一绝缘膜21之后,如图36D所示,与由图10所示步骤表示的第一实施方式一样,在第一绝缘膜21上为多个有机EL器件10R、10G和10B中的每一个形成第一电极13。

[0197] 在形成第一电极13之后,如图37A和图37B所示,通过光刻法和刻蚀在第一绝缘膜21中配置沟槽30,使得沟槽30的底面到达导电膜60。

[0198] 在配置了沟槽30之后,如图38所示,与由图13至图15所示步骤表示的第一或第二实施方式一样,在第一电极13和第一绝缘膜21上方,例如通过蒸发法形成有机层14的空穴注入层14A、空穴输送层14B、发光层14C和电子输送层14D。

[0199] 在形成了有机层14之后,如图14和图15所示,与第一实施方式一样,形成第二电极15。从而,形成了如图3和图4所示的有机EL器件10R、10G和10B。

[0200] 随后,如图4所示,与第一实施方式一样,在有机EL器件10R、10G和10B上形成由上述材料制成的保护膜16和粘附层17。将此产物与配置有彩色滤光器41和遮光膜42的密封基板40贴合。从而,制成了图1至图4所示的显示单元。

[0201] [模块与应用实例]

[0202] 将对上述实施方式所述的显示单元的应用实例给予描述。上述实施方式的显示单元可应用于诸如电视设备、数码相机、笔记本个人电脑、如手机等的便携式终端设备以及摄像机等的用于将外部输入的视频信号或内部生成的视频信号显示为图像或视频的任何领域的电子装置的显示单元。

[0203] [模块]

[0204] 例如,上述实施方式的显示单元作为如图39所示的模块被并入诸如后述第一和第二应用实例的电子装置中。在该模块中,例如,在基板11的一边上配置从密封基板40露出来的区域310,并在露出的区域310中通过延长信号线驱动电路120和扫描线驱动电路130的配线形成外部连接端(未示出)。外部连接端可配置有用于输入和输出信号的柔性印刷电路(FPC)320。

[0205] [第一应用实例]

[0206] 图40A和图40B示出了应用上述实施方式的显示单元的拍摄装置(带有可互换镜头的单镜头反光数码相机)的外观。该拍摄装置例如具有位于相机体411的正面右侧的可互换拍摄镜头单元(可互换镜头)412和位于正面左侧的由摄影者把持的手持部413。在相机体411背面近似中央的部分中,配置了监视器414。在监视器414的上方配置了取景器(目镜窗)415。摄影者能够观察到由拍摄镜头单元412导入的目标物的光像,并在取景器415上通过观察图像来确定照片构成。取景器415是由根据上述实施方式的显示单元构成的。

[0207] [第二应用实例]

[0208] 图41示出了应用上述实施方式的显示单元的头戴式显示器的外观。该头戴式显示器例如具有位于眼镜状显示部421两侧的戴在用户头上的耳挂部422。显示部421是由根据

上述实施方式的显示单元构成的。

[0209] 尽管已参照实施方式对本公开进行了描述,但本公开不限于上述实施方式,并且可进行各种修改。例如,在上述实施方式中,已对通过减薄空穴注入层14A和空穴输送层14B在沟槽30内的厚度来抑制有机发光器件10R、10G和10B之间的漏电流的情况给予了描述。然而,至少减薄了空穴注入层14A或空穴输送层14B在沟槽30内的厚度就足够了。并且,在有机层14中,空穴注入层14A的导电性特别高。因此,通过至少减薄空穴注入层14A在沟槽30内的厚度,即可以减小有机发光器件10R、10G和10B之间的漏电流。此外,在省去空穴输送层14B的情况下,通过减薄空穴注入层14A在沟槽30内的厚度,可以减小有机发光器件10R、10G和10B之间的漏电流。

[0210] 另外,在上述实施方式中,已对从第二电极15一侧提取发光层产生的光的情况(顶发光)作为实例给予了描述。然而,也可以从第一电极13一侧提取发光层产生的光(底发光)。在该情况下,第一电极13由ITO、IZO(注册商标)、SnO<sub>2</sub>等制成的透明电极构成。第二电极15由诸如金(Au)、铂(Pt)、镍(Ni)、铬(Cr)、铜(Cu)、钨(W)、铝(Al)、钼(Mo)和银(Ag)等金属元素的单质或合金构成的反射电极构成。并且,第二电极15可由上述反射电极和上述透明电极的复合膜构成。此外,在底发光型情况下,彩色滤光器41和遮光膜42可被配置在基板11一侧,例如可被配置在驱动电路层12与第一绝缘膜21之间。

[0211] 并且,例如,各层的材料、厚度、成膜方法、成膜条件等不限于上述实施方式所述那些,并且可采用其他材料、其他厚度、其他成膜方法以及其他成膜条件。

[0212] 从上述示例性实施方式以及本公开的变形例中至少可以获得以下结构。

[0213] (1)一种显示单元,包括位于基板上的:

[0214] 多个有机EL器件;以及

[0215] 绝缘膜,配置在多个有机EL器件之间的器件间区域中,该绝缘膜包括位于彼此相邻的有机EL器件之间的位置中的沟槽。

[0216] (2)根据(1)所述的显示单元,其中,有机EL器件包括:

[0217] 第一电极,针对多个有机EL器件中的每一个进行配置,

[0218] 有机层,针对多个有机EL器件而被公共地配置在第一电极和绝缘膜上,且包括空穴注入层或空穴输送层、以及发光层;以及

[0219] 第二电极,针对多个有机EL器件而被公共地配置在有机层上,并且

[0220] 空穴注入层或空穴输送层在沟槽内的厚度小于其在沟槽外的厚度。

[0221] (3)根据(2)所述的显示单元,其中,空穴注入层或空穴输送层在沟槽内的厚度向沟槽的深度方向变小。

[0222] (4)根据(1)至(3)中的任一项所述的显示单元,其中,多个有机EL器件具有在一个方向上延伸的矩形形状,并且被排列在与其短边平行的行方向上和与其长边平行的列方向上,并且

[0223] 遍及多个有机EL器件的多个行在列方向上连续地配置沟槽。

[0224] (5)根据(1)至(3)中的任一项所述的显示单元,其中,多个有机EL器件具有矩形形状,并且被排列在与其短边平行的行方向上和与其长边平行的列方向上,并且

[0225] 针对多个有机EL器件的每一行在列方向上配置沟槽。

[0226] (6)根据(4)或(5)所述的显示单元,其中,多个有机EL器件在行方向上的节距等于

或小于约30μm。

[0227] (7)根据(1)至(6)中的任一项所述的显示单元,其中,绝缘膜包括第一绝缘膜和第二绝缘膜,第一绝缘膜被配置在基板与多个有机EL器件之间,并且第二绝缘膜被配置在第一绝缘膜上的器件间区域中,并且

[0228] 沟槽包括第一沟槽和第二沟槽,第一沟槽被配置在第一绝缘膜中,并且第二沟槽被配置在第二绝缘膜中,与第一沟槽相通,且具有比第一沟槽的宽度更窄的宽度。

[0229] (8)根据(2)至(6)中的任一项所述的显示单元,包括位于沟槽的底面上的导电膜,

[0230] 其中,导电膜被连接至预定电位。

[0231] (9)根据(8)所述的显示单元,其中,预定电位是地电位或第二电极的电位。

[0232] (10)根据(8)或(9)所述的显示单元,包括:

[0233] 驱动电路,包括基板与多个有机EL器件之间、基板与绝缘膜之间的晶体管,

[0234] 其中,导电膜是遮光层。

[0235] (11)根据(1)至(10)中的任一项所述的显示单元,其中,发光层是发射白光的层,并且

[0236] 有机EL器件包括将白光提取为红光、绿光或蓝光的彩色滤光器。

[0237] (12)一种制造显示单元的方法,该方法包括:

[0238] 在基板上形成多个有机EL器件;以及

[0239] 在多个有机EL器件之间的器件间区域中形成绝缘膜,

[0240] 其中,在绝缘膜的形成中,在绝缘膜的彼此相邻的有机EL器件之间的位置处配置沟槽。

[0241] (13)根据(12)所述的制造显示单元的方法,其中,形成多个有机EL器件包括:

[0242] 针对多个有机EL器件中的每一个形成第一电极;

[0243] 在第一电极和绝缘膜上,针对多个有机EL器件公共地形成有机层,该有机层包括空穴注入层或空穴输送层、以及发光层;以及

[0244] 在有机层上,针对多个有机EL器件公共地形成第二电极,并且

[0245] 其中,在绝缘膜中配置了沟槽之后执行有机层的形成。

[0246] (14)根据(13)所述的制造显示单元的方法,其中,通过蒸发法执行有机层的形成,并且满足数学表达式1,

[0247] (数学表达式1)

[0248]  $X/Y > w/d$

[0249] 其中,X表示从沟槽的入口边缘到蒸发源的偏移距离,Y表示基板与蒸发源之间的距离,w表示沟槽的宽度,并且d表示沟槽的深度。

[0250] (15)根据(14)所述的制造显示单元的方法,其中,在有机层的形成中,蒸发法是在旋转基板的同时进行膜的形成的旋转蒸发法,并且在旋转基板一周期间内的部分或全部时间内满足数学表达式1。

[0251] (16)根据(14)所述的制造显示单元的方法,其中,在有机层的形成中,蒸发法是在蒸发源和基板在某个方向上相对移动的同时进行膜的形成的线性蒸发法,并且在基板通过蒸发源期间内的部分或全部时间内满足数学表达式1。

[0252] (17)根据(14)至(16)中的任一项所述的制造显示单元的方法,其中,在有机层中

的空穴注入层或空穴输送层的形成中,满足数学表达式1。

[0253] 本公开包括涉及于2011年3月31日在日本专利局提交的日本在先专利申请JP 2011-079619所公开的主题,其全部内容通过引用结合于此。

[0254] 本领域技术人员应当理解,在所附权利要求或其等价物范围内,可根据设计需求和其他因素,进行各种修改、组合、再组合和替换。

图1

图2

## 列方向

层叠方向 → 行方向

图3

图4

图5

图6

图7A

图7B

图7C

图8A

图8B

图8C

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22

图23

列方向

↑

层叠方向 → 行方向

图24

图25

图26

图27

图28

|     | MgAg 厚度        | R1       | 第三实施方式          |                 |

|-----|----------------|----------|-----------------|-----------------|

|     |                |          | L=1.0 $\mu$ m   | L=2.4 $\mu$ m   |

| 4nm | 85 $\Omega$    | $\infty$ | 743 $\Omega$    | 310 $\Omega$    |

| 5nm | 42.5 $\Omega$  | $\infty$ | 371.5 $\Omega$  | 155 $\Omega$    |

| 6nm | 28.33 $\Omega$ | $\infty$ | 247.67 $\Omega$ | 103.33 $\Omega$ |

| 7nm | 21.25 $\Omega$ | $\infty$ | 185.75 $\Omega$ | 77.5 $\Omega$   |

| 8nm | 18.21 $\Omega$ | $\infty$ | 159.21 $\Omega$ | 66.43 $\Omega$  |

图29

图30

图31

图32

图33

图34

图35

图36A

图36B

图36C

图36D

图37A

图37B

图38

图39

图40A

图40B

图41

|                |                                                                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示单元及其制造方法                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">CN102738200B</a>                                                                                                                                                                  | 公开(公告)日 | 2016-08-03 |

| 申请号            | CN201210080760.9                                                                                                                                                                              | 申请日     | 2012-03-23 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                          |         |            |

| [标]发明人         | 山田二郎<br>横山诚一<br>长谷川英史<br>槙田笃哉<br>上杉昌尚<br>权藤胜一<br>市川朋芳<br>山下淳一                                                                                                                                 |         |            |

| 发明人            | 山田二郎<br>横山诚一<br>长谷川英史<br>槙田笃哉<br>上杉昌尚<br>权藤胜一<br>市川朋芳<br>山下淳一                                                                                                                                 |         |            |

| IPC分类号         | H01L27/32 H01L51/52                                                                                                                                                                           |         |            |

| CPC分类号         | H01L27/3211 H01L27/322 H01L27/3246 H01L27/3258 H01L27/3272 H01L51/504 H01L51/5218<br>H01L51/5281 H01L51/5284 H01L2251/5315 H01L2251/558 H01L27/14625 H01L51/5012 H01L2227/32<br>H01L2251/5338 |         |            |

| 代理人(译)         | 余刚                                                                                                                                                                                            |         |            |

| 审查员(译)         | 王一帆                                                                                                                                                                                           |         |            |

| 优先权            | 2011079619 2011-03-31 JP                                                                                                                                                                      |         |            |

| 其他公开文献         | CN102738200A                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                                                                                                                                |         |            |

**摘要(译)**

一种显示单元及其制造方法，该显示单元在基板上包括：多个有机EL器件；以及配置在多个有机EL器件之间的器件间区域中的绝缘膜。该绝缘膜包括位于彼此相邻的有机EL器件之间的位置中的沟槽。