(12) 发明专利申请

(10) 申请公布号 CN 102982768 A

(43) 申请公布日 2013. 03. 20

(21) 申请号 201210571455. X

(22) 申请日 2012. 12. 19

(71) 申请人 四川虹视显示技术有限公司

地址 611731 四川省成都市高新区(西区)

科新西街 168 号

(72) 发明人 周刚 田朝勇 刘宏

(74) 专利代理机构 成都宏顺专利代理事务所

(普通合伙) 51227

代理人 周永宏

(51) Int. Cl.

G09G 3/32(2006. 01)

权利要求书 1 页 说明书 4 页 附图 4 页

(54) 发明名称

一种 AMOLED 面板行驱动的分区、寻址方法及其电路

(57) 摘要

本发明为了压缩 AMOLED 面板行寻址电路部分占用的空间、简化行寻址电路结构、增加单张基板切割面板数量,提出了一种 AMOLED 面板行驱动的分区、寻址方法及其电路。其分区方法中,被寻址的各像素行由一 N 维坐标标识区分,用于标识不同像素行的各维度坐标值为以 1 开始顺序编号至所有像素行均被编号的正整数的集合的各元素,同一维度的坐标值相同的行的集合作为一个分区, N 为不大于像素行数的质因数数的正整数。本发明的行寻址电路使原本结构复杂的移位寄存器电路被组合逻辑单元及解码器单元所替代,可以有效减少了面板行寻址的电路规模,增加单张基板切割 CELL 的数量;同时行驱动电路规模的缩小,也会减少产品出现缺陷的概率。

1. 一种 AMOLED 面板行驱动的分区方法, 其特征在于: 被寻址的各像素行由一 N 维坐标标识区分, 用于标识不同像素行的各维度坐标值为以 1 开始顺序编号至所有像素行均被编址的正整数的集合的各元素, 同一维度的坐标值相同的行的集合作为一个分区, N 为不大于像素行数的质因数数的正整数。

2. 一种与所述分区方法相应的寻址电路, 包括,

若干组逻辑电路、电平转换电路和数字缓冲电路, 所述一组逻辑电路、电平转移电路和数字缓冲电路对应于一像素行,

其特征在于,

所述任一像素行对应一组合逻辑单元, 所述任一组合逻辑单元还包括 N 个输入端, 所述任一组合逻辑单元的各输入端以对应像素行的 N 维坐标的各维度坐标值标号加以区分, 所述组合逻辑单元的输入端到输出端执行逻辑与或与非的动作;

所述组合逻辑单元通过依次连接逻辑电路、电平转换电路和数字缓冲电路后与像素行连接实现与像素行对应;

还包括,

解码单元, 包括 N 组解码器, 其中任一组解码器包括一个地址输入端和多个输出选通端, 所述输出选通端以像素行坐标的某一维度的坐标值一一对应标识加以区分, 所述不同的解码器对应的像素行坐标值的维度不同, 所述输出选通端数与用于所述解码器标识的相应的维度坐标最大值一致;

控制单元, 所述控制单元包含地址输出端, 所述地址输出端与所述解码单元连接用于向解码单元输入地址信息, 所述控制单元用于生成所述地址信息;

所述组合逻辑单元各输入端与相应坐标的解码器输出端对应, 所述对应包括同时满足组合逻辑单元输入端坐标的维度值与解码器对应的维度值相同和组合逻辑单元输入端的坐标值与解码器的坐标值相同的条件。

3. 一种与所述行驱动的分区方法相应的寻址方法, 其特征在于, 控制单元生成寻址信息, 所述寻址信息输入解码单元, 所述解码单元对地址信息解码后输出给组合逻辑单元, 组合逻辑单元根据解码单元输出的信息选通相应的像素行。

4. 根据权利要求 3 所述的寻址方法, 所述地址信息包含与 N 组解码器对应的 N 维坐标信息, 所述某一维度的坐标信息被输入与该维度对应的一组解码器用于选通相应坐标信息对应的输出选通端。

## 一种 AMOLED 面板行驱动的分区、寻址方法及其电路

### 技术领域

[0001] 本发明属于显示技术领域,涉及矩阵型显示面板的寻址方法及寻址电路,具体涉及一种有源矩阵有机发光二极体面板(Active Matrix/Organic Light Emitting Diode, AMOLED)行驱动的分区方法、寻址方法及寻址电路。

### 背景技术

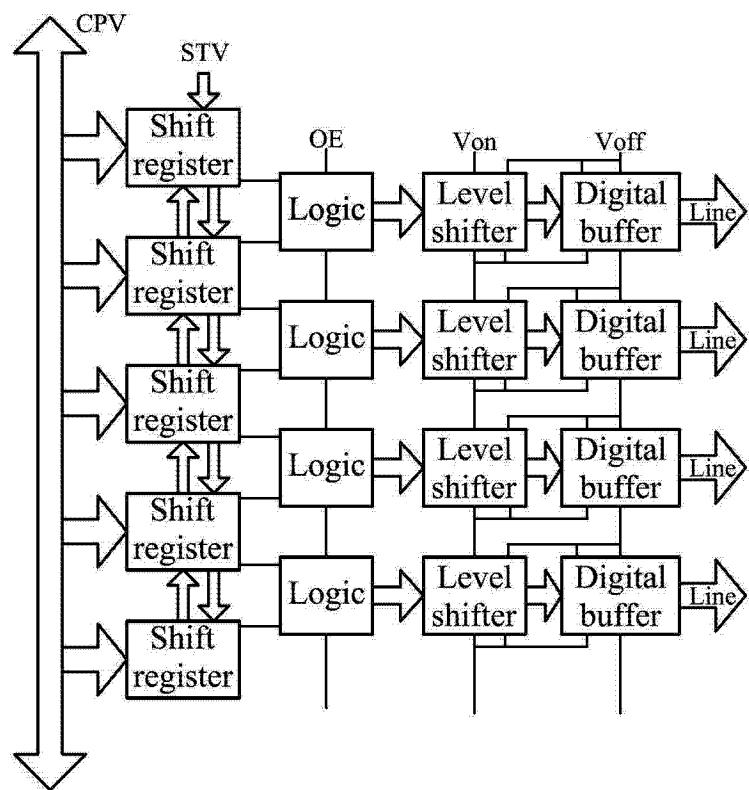

[0002] 现有的AMOLED面板行驱动(Gate Drive)电路多采用TFT工艺制作在阵列(ARRAY)的周边。如图1所示,所述的行驱动电路主要包含移位寄存器(Shift register)、逻辑电路(Logic)、电平转换电路(Level shifter)和数字缓冲电路(Digital buffer)四部分。所述逻辑电路用于调整行扫描信号的输出,避免因行扫描信号延迟而带来的两根相邻扫描线之间信号重叠的影响,所述逻辑单元通常采用或门和与门串联的结构,常用于现有的TFT-LCD行驱动电路中;所述移位寄存器通过依次连接逻辑电路、电平转换电路和数字缓冲电路后与像素行连接,以保持与像素行的对应关系。

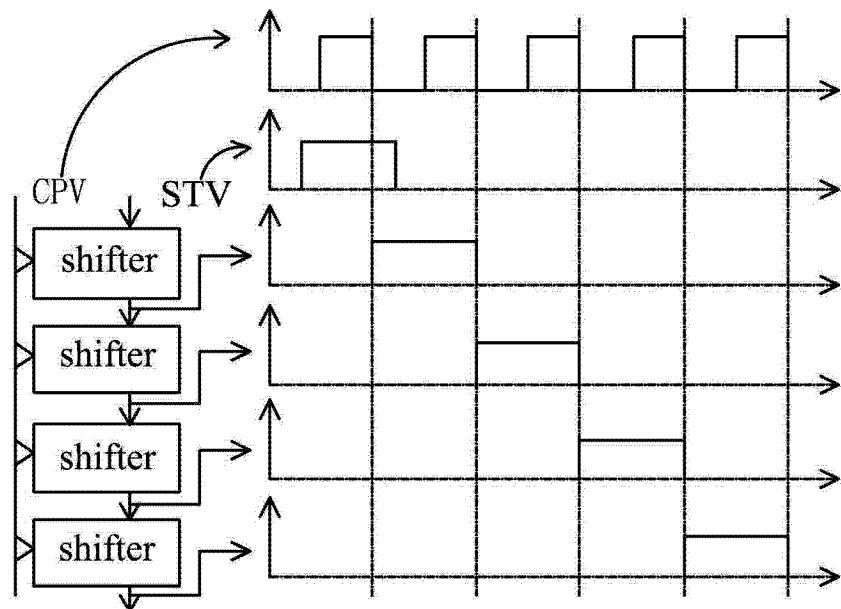

[0003] 其中移位寄存器在时钟信号(CPV)与扫描线的第一个同步信号(STV)的控制下完成行驱动寻址。以扫描一帧图像为例,现有的寻址电路的寻址过程如图2所示:步骤1,行驱动同步信号STV输入到第一级移位寄存器,表示一帧扫描开始;步骤2,移位寄存器在行驱动时钟信号CPV和上一级移位寄存器输出信号的共同控制下进行进位操作,改变当前移位寄存器的输出状态;步骤3,所有的移位寄存器以步骤2的方式依次输出行驱动信号直到最后一行被选通,从而实现对AMOLED面板所有行的寻址。

[0004] 上述现有技术中的AMOLED面板行驱动寻址方式有以下特点:1、由移位寄存器实现寻址功能;2、按从上到下(或从下到上)顺序逐行寻址,无分区或块的概念。

[0005] 然而,现有技术中用到的移位寄存器电路较复杂,使得行驱动电路(分布在面板周边水平方向)会占用较多的面板空间,影响单张基板切割面板数量;同时,随着电路的复杂程度增加,面板制作的难度也会增加,从而导致产品可靠性和生产良率降低。

### 发明内容

[0006] 本发明的目的是为了压缩AMOLED面板行寻址电路部分占用的空间、简化行寻址电路结构、增加单张基板切割面板数量,提出了一种AMOLED面板行驱动的分区、寻址方法及其电路。

[0007] 本发明的技术方案是:一种AMOLED面板行驱动的分区方法,其特征在于:被寻址的各像素行由一N维坐标标识区分,用于标识不同像素行的各维度坐标值为以1开始顺序编号至所有像素行均被编号的正整数的集合的各元素,同一维度的坐标值相同的行的集合作为一个分区,N为不大于像素行数的质因数数的正整数。

[0008] 为了解决上述问题,本发明还提出了一种与所述分区方法相应的寻址电路,包括,

[0009] 若干组逻辑电路、电平转换电路和数字缓冲电路,所述一组逻辑电路、电平转移电路和数字缓冲电路对应于一像素行,

- [0010] 其特征在于，

- [0011] 所述任一像素行对应一组合逻辑单元，所述任一组合逻辑单元还包括 N 个输入端，所述任一组合逻辑单元的各输入端以对应像素行的 N 维坐标的各维度坐标值标号加以区分，所述组合逻辑单元的输入端到输出端执行逻辑与或与非的动作；

- [0012] 所述组合逻辑单元通过依次连接逻辑电路、电平转换电路和数字缓冲电路后与像素行连接实现与像素行对应；

- [0013] 还包括，

- [0014] 解码单元，包括 N 组解码器，其中任一组解码器包括一个地址输入端和多个输出选通端，所述输出选通端以像素行坐标的某一维度的坐标值一一对应标识加以区分，所述不同的解码器对应的像素行坐标值的维度不同，所述输出选通端数与用于所述解码器标识的相应的维度坐标最大值一致；

- [0015] 控制单元，所述控制单元包含地址输出端，所述地址输出端与所述解码单元连接用于向解码单元输入地址信息，所述控制单元用于生成所述地址信息；

- [0016] 所述组合逻辑单元各输入端与相应坐标的解码器输出端对应，所述对应包括同时满足组合逻辑单元输入端坐标的维度值与解码器对应的维度值相同和组合逻辑单元输入端的坐标值与解码器的坐标值相同的条件。

- [0017] 为了解决上述问题，本发明还提出了一种与所述行驱动的分区方法相应的寻址方法，其特征在于，控制单元生成寻址信息，所述寻址信息输入解码单元，所述解码单元对地址信息解码后输出给组合逻辑单元，组合逻辑单元根据解码单元输出的信息选通相应的像素行。

- [0018] 进一步的，所述地址信息包含与 N 组解码器对应的 N 维坐标信息，所述某一维度的坐标信息被输入与该维度对应的一组解码器用于选通相应坐标信息对应的输出选通端。

- [0019] 本发明的有益效果是：本发明的行寻址电路使原本结构复杂的移位寄存器电路被组合逻辑单元及解码器单元所替代，并且使用本发明的分区及寻址方法使面板上寻址用的驱动电路单元减少，可以有效减少了面板行寻址的电路规模，压缩电路占用的面板空间，增加单张基板切割 CELL 的数量；同时行驱动电路规模的缩小，也会减少产品出现缺陷的概率，提高产品的可靠性以及良率，进一步达到提升产品性能和降低产品成本的目的。

## 附图说明

- [0020] 图 1 为现有的行驱动电路框图；

- [0021] 图 2 为现有的行寻址方式工作原理的示意图；

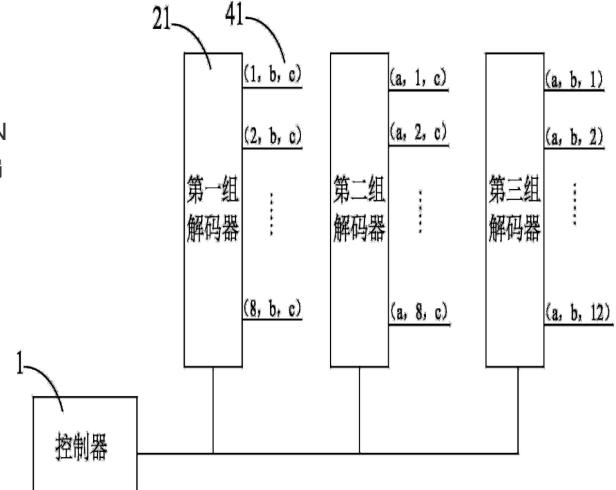

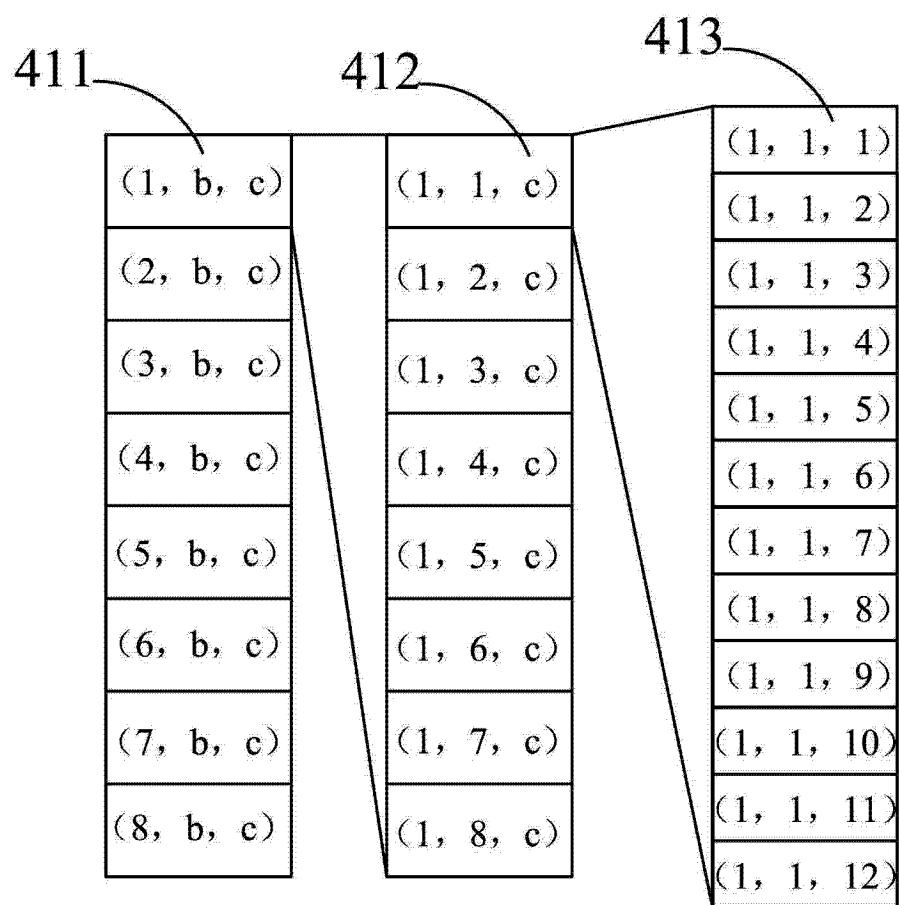

- [0022] 图 3 为本发明的一实施例的行分区示意图；

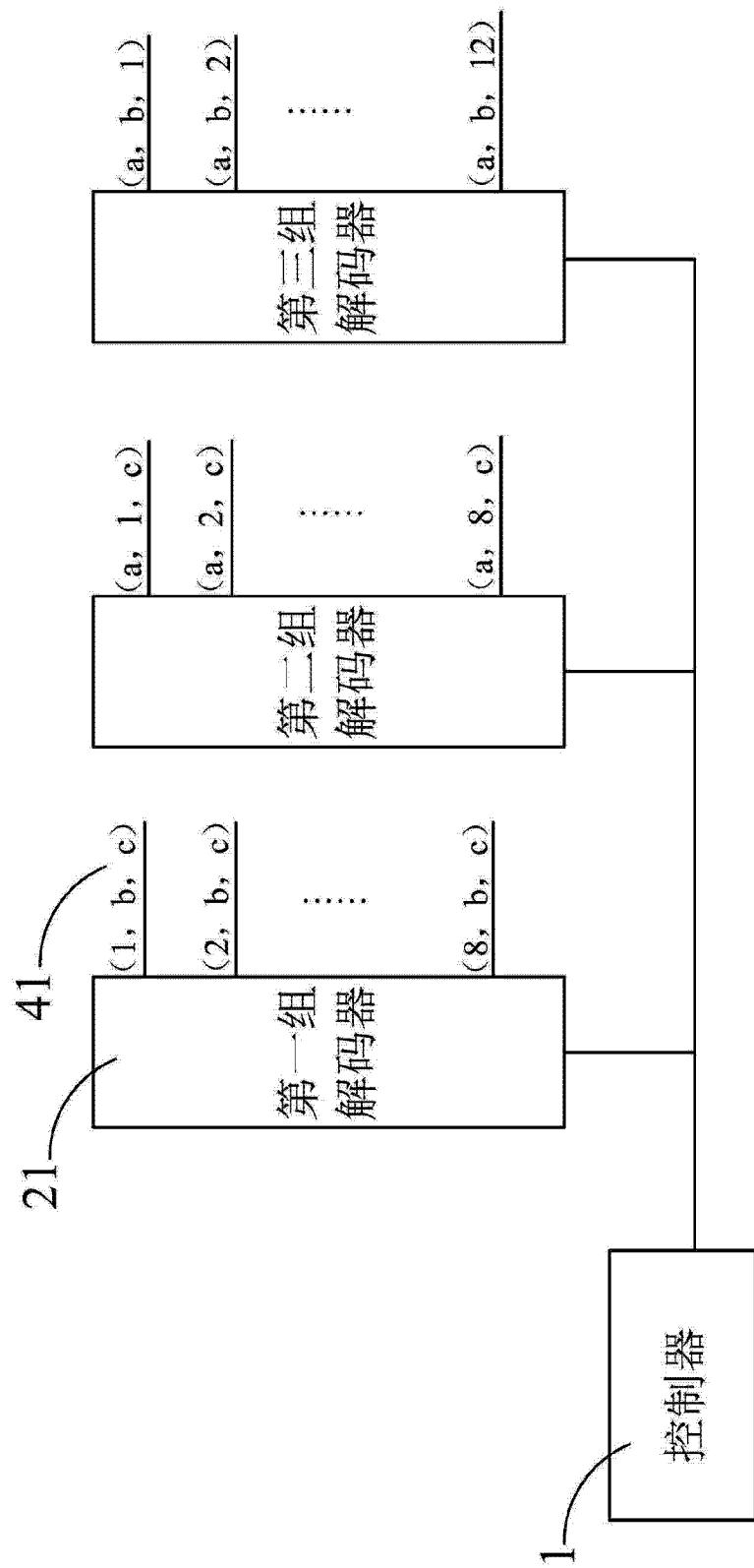

- [0023] 图 4 为本发明的一实施例的行驱动的寻址电路框图；

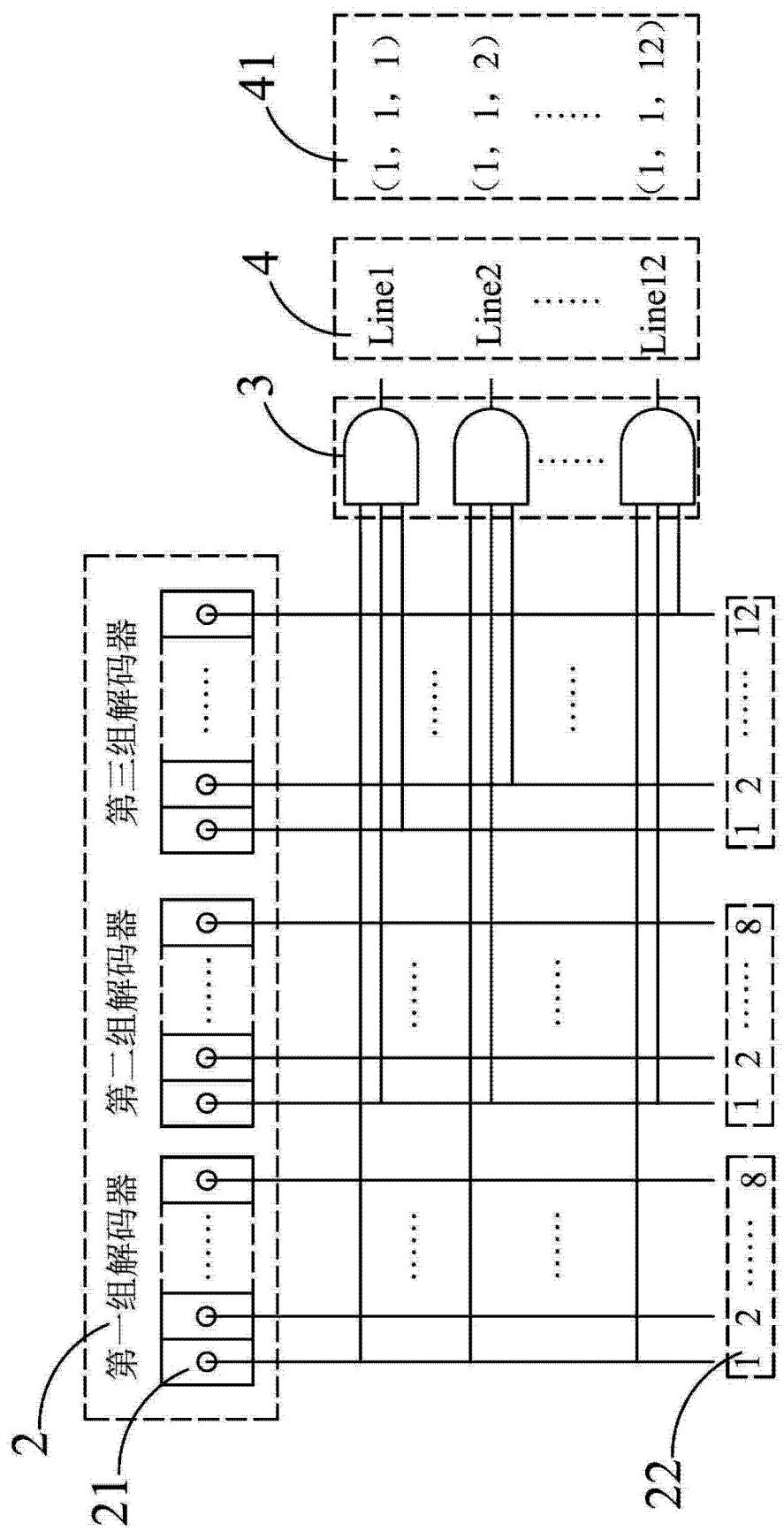

- [0024] 图 5 为本发明的一实施例的部分行与解码器单元对应关系示意图。

- [0025] 附图标记说明：控制器 1、解码器单元 2、解码器 21、解码器输出端坐标 22、逻辑单元 3、像素行 4、像素行坐标 41、第一像素行坐标 411、第二像素行坐标 412、第三像素行坐标 413、a 为整数 1 到 8 的集合、b 为整 1 到 8 的数集合、c 整数 1 到 12 的集合。

## 具体实施方式

[0026] 下面结合附图和具体实施例对本发明作进一步说明。

[0027] 如图 3 和图 5 所示,本实施例所述的一种 AMOLED 面板行驱动的分区方法,被寻址的各像素行 4 由一 N 维坐标 41 标识用以区分,所述用于标识不同像素行 4 的各维度坐标值为以 1 开始顺序编号至所有像素行均被编号的正整数的集合的各元素,所述同一维度的坐标值相同的像素行的集合作为一个分区,N 为不大于像素行数的质因数数的正整数。

[0028] 如图 1、图 3、图 4 及图 5 所示,本实施例所述的一种与所述行驱动的分区方法相应的寻址电路,包括,

[0029] 逻辑电路、电平转换电路和数字缓冲电路,所述一组逻辑电路、电平转换电路和数字缓冲电路对应于一行像素行 4,

[0030] 所述任一像素行 4 对应一组逻辑单元 3,所述任一组逻辑单元 3 还包括 N 个输入端,所述任一组逻辑单元的各输入端以对应像素行 4 的 N 维坐标 41 的各维度坐标值标号加以区分,所述组合逻辑单元的输入端到输出端执行逻辑与或与非的动作;

[0031] 所述组合逻辑单元 3 通过依次连接逻辑电路、电平转换电路和数字缓冲电路后与像素行连接实现与像素行对应;

[0032] 还包括,

[0033] 解码单元 2,包括 N 组解码器 21,其中任一组解码器 21 包括一个地址输入端和多个输出选通端,所述输出选通端以像素行坐标 41 的某一维度的坐标值一一对应标识成解码器输出端坐标 22 加以区分,所述不同的解码器 21 对应的像素行坐标值的维度不同,所述输出选通端数不小于用于所述解码单元标识的相应的维度坐标最大值;

[0034] 控制单元 1,所述控制单元 1 包含地址输出端,所述地址输出端与所述解码单元 2 连接用于向解码单元 2 输入地址信息,所述控制单元用于生成所述地址信息;

[0035] 所述组合逻辑单元 3 各输入端与相应坐标解码器 21 输出端对应,所述对应包括同时满足组合逻辑单元 3 输入端坐标的维度值与解码器 21 对应的维度值相同和组合逻辑单元 3 输入端的坐标值与解码器 21 的坐标值相同的条件。

[0036] 所述组合逻辑单元 3 具体通过逻辑与门或与非门实现。

[0037] 所述解码单元 2 具体通过解码器和 / 或译码器和 / 或移位寄存器实现。

[0038] 本实施例所述的一种与所述行驱动的分区方法相应的寻址方法,所述控制单元 1 生成寻址信息,所述寻址信息输入解码单元 2,所述解码单元 2 对地址信息解码后输出给组合逻辑单元 3,组合逻辑单元 3 根据解码单元 2 输出的信息选通相应的像素行 4;

[0039] 所述地址信息包含与 N 组解码器对应的 N 维坐标信息,所述某一维度的坐标信息被输入与该维度对应的一组解码器 21 用于选通相应坐标信息对应的输出选通端。

[0040] 所述的解码单元 2 对地址信息解码后输出给组合逻辑单元 3 具体通过地址总线实现。

[0041] 所述控制单元顺序或随机选择地变化生成并输出寻址信息,以实现对其他像素行的寻址。

[0042] 如图 3、图 4 和图 5 所示,以像素行为 768 行的 AMOLED 面板为例,

[0043] 一种行驱动的分区方法,所述用于像素行标识的坐标维度 N 的值为 3,一维坐标值为 a (a 为 1 至 8 的正整数集合),二维坐标值为 b (b 为 1 至 8 的正整数集合),三维坐标值为 c (c 为 1 至 12 的正整数集合)。

[0044] 图 3 所示为本实施例的像素行分区示意图, 其中一维坐标值 a 可取 1 至 8 的正整数之一, 一维坐标相同的各像素行作为一个分区, 比如图 3 中第二像素行坐标 412 和第三像素行坐标 413 所示的分区的像素行坐标的一维坐标值均为 1, 即第一像素行坐标 411 的一维坐标值 a=1, 属于同一分区。

[0045] 如图 3 所示, 根据一维坐标值的不同, 所述像素行 768 行被平均分为 8 个分区, 每个分区 96 行; 同理, 根据二维坐标值的不同, 所述像素行 768 行被平均分为 8 个分区, 每个分区 96 行; 根据三维坐标值的不同, 所述像素行 768 行被平均分为 12 个分区, 每个分区 64 行。容易发现, 所述任一像素行均同时属于三个分区。

[0046] 本领域的普通技术人员应该理解, 上述分区方法仅仅是为了便于理解本发明的原理而举出的具体实施例, 根据本发明的技术方案, 所述分区方法并不局限于本具体实施例。比如像素行为 768 行的面板各像素行还可以由一四维坐标加以区分; 也可以是三维坐标: 其中, a 取不大于 16 的正整数集合, b 取不大于 8 的正整数的集合, c 取不大于 6 的正整数的集合; 所述分区方法可以是平均分陪像素行, 也可以不是平均分。

[0047] 应用于上述实施例的一组寻址信号包括三路信号 SCANi、SCANj 和 SCANk, 所述三路信号均为周期性脉冲信号, SCANi 的周期为 16.667ms 与帧周期相同, 脉冲宽度为 2083.3us, SCANi<sub>1-0</sub> 到 SCAN i<sub>1-7</sub> 依次延迟 2083.3us; SCANj 的周期为 2083.3us, 脉冲宽度为 260.4us, SCANj<sub>2-0</sub> 到 SCANj<sub>2-7</sub> 依次延迟 260.4us; SCANk 的周期为 260.4us, 脉冲宽度为 21.7us, SCANk<sub>3-0</sub> 到 SCAN k<sub>3-11</sub> 依次延迟 21.7us。

[0048] 三路信号分别输出寻址信号到三输入的与门电路, 一共有  $8*8*12=768$  个组合, 每个组合选出唯一的一条扫描行, 从而实现对 768 行的寻址。

[0049] 本领域的普通技术人员将会意识到, 这里所述的实施例是为了帮助读者理解本发明的原理, 应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合, 这些变形和组合仍然在本发明的保护范围内。

图 1

图 2

图 3

图 4

图 5

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种AMOLED面板行驱动的分区、寻址方法及其电路                      |         |            |

| 公开(公告)号        | <a href="#">CN102982768A</a>                   | 公开(公告)日 | 2013-03-20 |

| 申请号            | CN201210571455.X                               | 申请日     | 2012-12-19 |

| [标]申请(专利权)人(译) | 四川虹视显示技术有限公司                                   |         |            |

| 申请(专利权)人(译)    | 四川虹视显示技术有限公司                                   |         |            |

| 当前申请(专利权)人(译)  | 四川虹视显示技术有限公司                                   |         |            |

| [标]发明人         | 周刚<br>田朝勇<br>刘宏                                |         |            |

| 发明人            | 周刚<br>田朝勇<br>刘宏                                |         |            |

| IPC分类号         | G09G3/32 G09G3/3225                            |         |            |

| 代理人(译)         | 周永宏                                            |         |            |

| 其他公开文献         | CN102982768B                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明为了压缩AMOLED面板行寻址电路部分占用的空间、简化行寻址电路结构、增加单张基板切割面板数量，提出了一种AMOLED面板行驱动的分区、寻址方法及其电路。其分区方法中，被寻址的各像素行由N维坐标标识区分，用于标识不同像素行的各维度坐标值为以1开始顺序编号至所有像素行均被编号的正整数的集合的各元素，同一维度的坐标值相同的行的集合作为一个分区，N为不大于像素行数的质因数数的正整数。本发明的行寻址电路使原本结构复杂的移位寄存器电路被组合逻辑单元及解码器单元所替代，可以有效减少了面板行寻址的电路规模，增加单张基板切割CELL的数量；同时行驱动电路规模的缩小，也会减少产品出现缺陷的概率。