## (12)发明专利申请

(10)申请公布号 CN 107978617 A

(43)申请公布日 2018.05.01

(21)申请号 201610919397.3

(22)申请日 2016.10.21

(71) 申请人 上海和辉光电有限公司

地址 201506 上海市金山区工业区九工路

1568号

(72)发明人 陈凯凯 高志豪 屈晓娟

(74)专利代理机构 北京同达信恒知识产权代理有限公司 11291

代理人 黄志华

(51) Int.Cl.

H01L 27/32(2006.01)

权利要求书2页 说明书7页 附图10页

(54)发明名称

## 一种像素阵列

### (57) 摘要

本发明提供一种像素阵列，涉及有机发光二极管显示技术领域，方法包括：像素阵列包括第一像素组以及第二像素组，第一像素组包括连续排列的至少两个第一子像素和一个第二子像素，第二像素组包括连续排列的至少两个第三子像素和一个第二子像素；第一像素组和第二像素组以第一方向重复排列，第一像素组所在的直线与第二像素组所在的直线相平行且交替重复排列；像素阵列中至多四个相邻的最小排列单元中包括的第一子像素、第二子像素以及第三子像素的数量相同。本发明实施例中，通过上述像素阵列，有效的解决了现有技术中R色和G色在OLED高PPI时难以制作相应开口的问题，保证了三种像素的发光率。

1. 一种像素阵列,其特征在于,

所述像素阵列包括第一像素组以及第二像素组,所述第一像素组包括连续排列的至少两个第一子像素和一个第二子像素,所述第二像素组包括连续排列的至少两个第三子像素和一个第二子像素;

所述第一像素组以及所述第二像素组延第一方向重复排列,所述第一像素组所在的直线与所述第二像素组所在的直线相平行且交替重复排列;

所述像素阵列中至多四个相邻的最小排列单元中包括的所述第一子像素、所述第二子像素以及所述第三子像素的数量相同。

2. 根据权利要求1所述的像素阵列,其特征在于,所述第一像素组中任意相邻的两个子像素的中心延所述第一方向之间的距离相等,所述第二像素组中任意相邻的两个子像素的中心延所述第一方向之间的距离相等。

3. 根据权利要求1所述的像素阵列,其特征在于,所述每一子像素的形状为以下形状中的任一一种:

四边形,圆形,三角形,椭圆形。

4. 根据权利要求1所述的像素阵列,其特征在于,所述第一像素组还包括:

连续排列在所述第二子像素后的至少两个所述第三子像素;

所述第二像素组还包括:

连续排列在所述第二子像素后的至少两个所述第一子像素。

5. 根据权利要求1所述的像素阵列,其特征在于,所述像素阵列中的各第二子像素延第二方向排列,且所述第二方向与所述第一方向不平行。

6. 根据权利要求5所述的像素阵列,其特征在于,所述第一方向上的任一所述第二子像素相邻的四个子像素构成平行四边形,并且所述平行四边形相邻顶点的子像素为相异的子像素。

7. 根据权利要求5所述的像素阵列,其特征在于,每一个所述最小排列单元中排列两种不同类型的子像素。

8. 根据权利要求7所述的像素阵列,其特征在于,所述第一方向与所述第二方向之间的夹角为45度。

9. 根据权利要求5所述的像素阵列,其特征在于,每一个所述最小排列单元中排列三种不同类型的子像素。

10. 根据权利要求9所述的像素阵列,其特征在于,在每一个所述最小排列单元中,所述第二子像素位于所述最小排列单元的第一交点,所述第一子像素位于所述最小排列单元的第一交点与所述最小排列单元的第一顶点连线上的任一位置,所述第三子像素位于所述最小排列单元的第一交点与所述最小排列单元的第二顶点连线上的任一位置;

其中,所述第一交点为第一斜线与第二斜线的交点,所述第一斜线为所述第一顶点与第二等分点的连线,所述第二斜线为所述第二顶点与第一等分点的连线,所述第一等分点和所述第二等分点位于所述最小排列单元中所述第一顶点和所述第二顶点所在边的对边上,所述第一等分点和所述第二等分点为所述对边的三等分点,所述第一等分点为远离所述第二顶点的等分点,所述第二等分点为远离所述第一顶点的等分点。

11. 根据权利要求1~10任一所述的像素阵列,其特征在于,所述第一子像素为红色像

素,所述第二子像素为蓝色像素,所述第三子像素为绿色像素。

## 一种像素阵列

### 技术领域

[0001] 本发明涉及发光二极管显示技术领域,尤其涉及一种像素阵列。

### 背景技术

[0002] 在平板显示技术中,有机发光二极管(Organic Light-Emitting Diode,OLED)显示器以其轻薄、主动发光、快响应速度、广视角、色彩丰富及高亮度、低功耗、耐高低温等众多优点而被业界公认为是继液晶显示器(LCD)之后的第三代显示技术。按驱动方式,OLED分为被动式OLED(Passive Matrix OLED,PMOLED)及主动式OLED(Active Matrix OLED,AMOLED),PMOLED也称为无源矩阵OLED,AMOLED也称为有源矩阵OLED,其中PMOLED只能制作小尺寸、低分辨率的显示面板,AMOLED因通过在每个像素中集成薄膜晶体管(TFT)和电容器并由电容器维持电压的方法进行驱动,因而可以实现大尺寸、高分辨率面板,是当前研究的重点及未来显示技术的发展方向。

[0003] 但现有的OLED很难满足电子设备对显示屏的高解析度、高亮度的要求,因为由于RGB各自使用自身的材料,对应材料的发光效率又不相同。其中B色的材料发光效率最差。在显示屏使用过程中B色最容易衰减,为了减弱B色的衰弱,现有技术中需要增大B色对应的金属掩模板的开口,所以R色和G色的相对应的金属掩模板的开口就相对减小,当现有技术中,OLED在解析度达到高PPI(每英寸像素数)时,R色以及G色在对应金属掩模板上开口被压缩的更小会无法制作,最终限制了OLED的像素PPI。

[0004] 综上所述,现有技术中不能提供一种适应高解析度的OLED的像素阵列。

### 发明内容

[0005] 本发明提供一种像素阵列,用于解决现有技术中OLED在解析度达到300PPI(每英寸像素数)以上时,R色以及G色在对应金属掩模板上开口被压缩的更小会无法制作的问题。

[0006] 本发明实施例提供一种像素阵列,

[0007] 所述像素阵列包括第一像素组以及第二像素组,所述第一像素组包括连续排列的至少两个第一子像素和一个第二子像素,所述第二像素组包括连续排列的至少两个第三子像素和一个第二子像素;

[0008] 所述第一像素组以及所述第二像素组延第一方向重复排列,所述第一像素组所在的直线与所述第二像素组所在的直线相平行且交替重复排列;

[0009] 所述像素阵列中至多四个相邻的最小排列单元中包括的所述第一子像素、所述第二子像素以及所述第三子像素的数量相同。

[0010] 本发明实施例中,通过第一像素组以及第二像素的重复排列,并且第一像素组与第二像素组中连续排列了两种像素以及另一种像素,保证了在做三种像素的金属掩膜的开口时,能够把两个第一像素或者第三像素的开口做成一个开口,有效的解决了现有技术中R色和G色在OLED高PPI时难以制作相应开口的问题,并且,通过所述像素阵列中至多四个相邻的最小排列单元中包括的所述第一子像素、所述第二子像素以及所述第三子像素的数量

相同的限定,保证了三种像素的发光率。

[0011] 进一步地,

[0012] 所述第一像素组中任意相邻的两个子像素的中心延所述第一方向之间的距离相等,所述第二像素组中任意相邻的两个子像素的中心延所述第一方向之间的距离相等。

[0013] 本发明实施例中,第一像素组以及第二像素组中的任意相邻的两个子像素的中心延第一方向之间的距离相等,便于在金属掩膜板上制作规则的开口。

[0014] 进一步地,所述每一子像素的形状为以下形状中的任一一种:

[0015] 四边形,圆形,三角形,椭圆形。

[0016] 本发明实施例中,子像素的形状有多种,可以方便制作像素对应的金属掩膜板上的多种样式的开口。

[0017] 进一步地,所述第一像素组还包括:

[0018] 连续排列在所述第二子像素后的至少两个所述第三子像素;

[0019] 所述第二像素组还包括:

[0020] 连续排列在所述第二子像素后的至少两个所述第一子像素。

[0021] 本发明实施例中,在第一像素组以及第二像素组中的第二像素后还可以分别连续排列两个第三子像素以及两个第一子像素,保证了在做三种像素的金属掩膜的开口时,能够把两个第一像素或者第三像素的开口做成一个开口,有效的解决了现有技术中R色和G色在OLED高PPI时难以制作相应开口的问题。

[0022] 进一步地,所述像素阵列中的各第二子像素延第二方向排列,且所述第二方向与所述第一方向不平行。

[0023] 本发明实施例中,将第二子像素延第二方向排列,可以方便规律的在金属掩膜板上制作第二子像素的开口。

[0024] 进一步地,所述第一方向上的任一所述第二子像素相邻的四个子像素构成平行四边形,并且所述平行四边形相邻顶点的子像素为相异的子像素。

[0025] 本发明实施例中,当确定了第二子像素的排列方向后,还需要确定第一子像素以及第三子像素的相对位置,第一方向上的任一第二子像素相邻的四个子像素构成平行四边形能够固定四个子像素的相对位置,更好的制作各个像素对应的金属掩膜板的开口。

[0026] 进一步地,每一个所述最小排列单元中排列两种不同类型的子像素。

[0027] 本发明实施例中,可以在最小排列单元中排列两种不同的子像素,减少金属掩膜板上开口的难度。

[0028] 进一步地,所述第一方向与所述第二方向之间的夹角为45度。

[0029] 本发明实施例中,当第一方向与第二方向之间的夹角为45度时,减少了金属掩膜板的开口的制作难度,并且金属掩膜板的开口的规律性更强,降低了制作工艺的难度。

[0030] 进一步地,每一个所述最小排列单元中排列三种不同类型的子像素。

[0031] 本发明实施例中,在一个最小排列单元中排列三种不同类型的子像素,既能够保证三种像素的发光率,又能够提高OLED的PPI。

[0032] 进一步地,在每一个所述最小排列单元中,所述第二子像素位于所述最小排列单元的第一交点,所述第一子像素位于所述最小排列单元的第一交点与所述最小排列单元的第一顶点连线上的任一位置,所述第三子像素位于所述最小排列单元的第一交点与所述最

小排列单元的第二顶点连线上的任一位置；

[0033] 其中，所述第一交点为第一斜线与第二斜线的交点，所述第一斜线为所述第一顶点与第二等分点的连线，所述第二斜线为所述第二顶点与第一等分点的连线，所述第一等分点和所述第二等分点位于所述最小排列单元中所述第一顶点和所述第二顶点所在边的对边上，所述第一等分点和所述第二等分点为所述对边的三等分点，所述第一等分点为远离所述第二顶点的等分点，所述第二等分点为远离所述第一顶点的等分点。

[0034] 本发明实施例中，按照上述排列方法排列三个不同种类的子像素既保证了金属掩膜板上第一子像素以及第三子像素的开口率，又保证了能够满足OLED高PPI的需要。

[0035] 进一步地，所述第一子像素为红色像素，所述第二子像素为蓝色像素，所述第三子像素为绿色像素。

[0036] 本发明实施例中，加大了红色像素以及绿色像素对应的金属掩膜板的开口率，减小了在OLED高PPI的制作工艺中，制作红色像素以及绿色像素对应的金属掩膜板的开口的工艺难度。

## 附图说明

[0037] 为了更清楚地说明本发明实施例中的技术方案，下面将对实施例描述中所需要使用的附图作简要介绍，显而易见地，下面描述中的附图仅仅是本发明的一些实施例，对于本领域的普通技术人员来讲，在不付出创造性劳动性的前提下，还可以根据这些附图获得其他的附图。

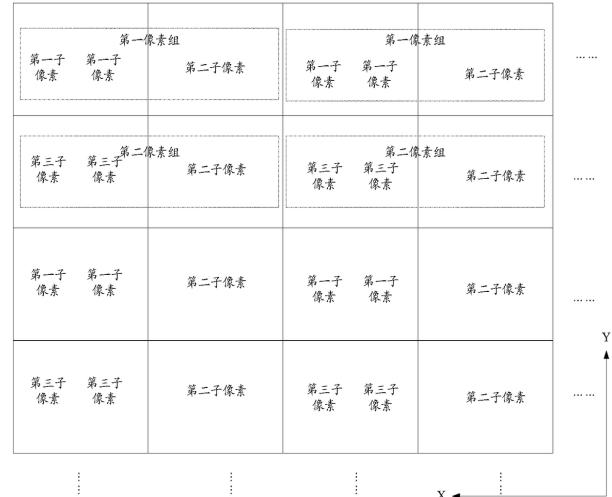

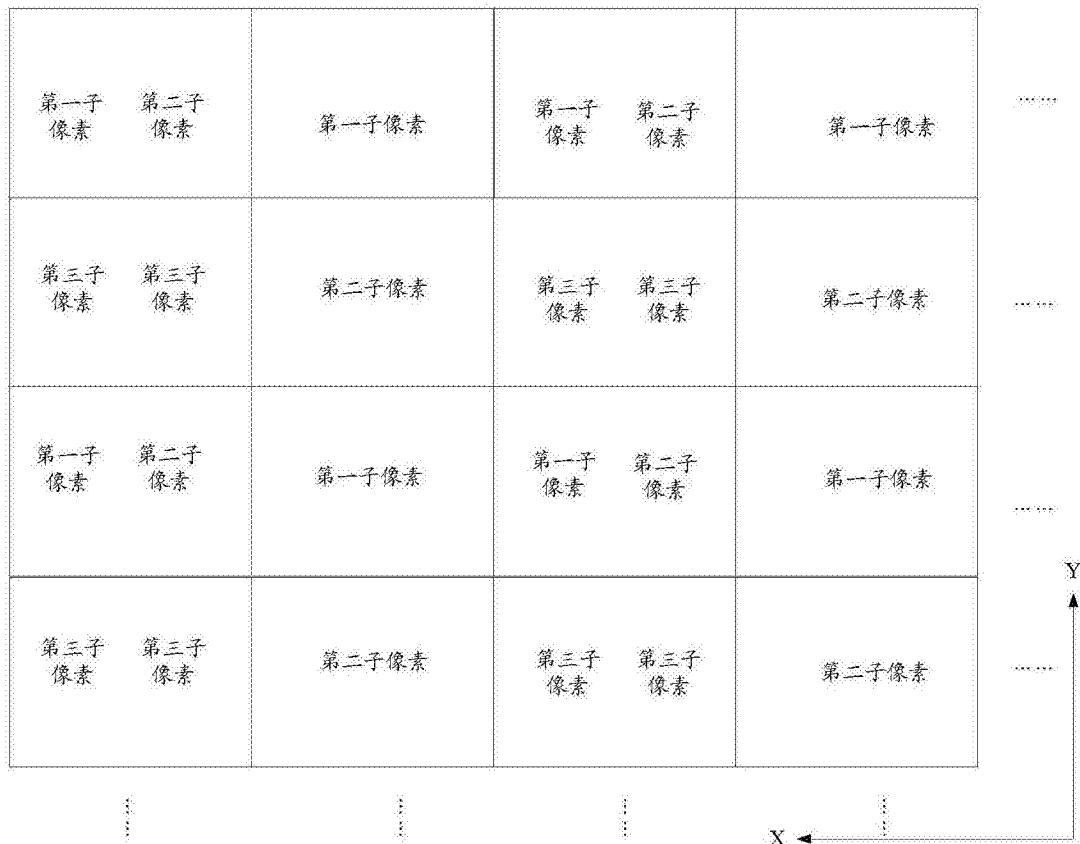

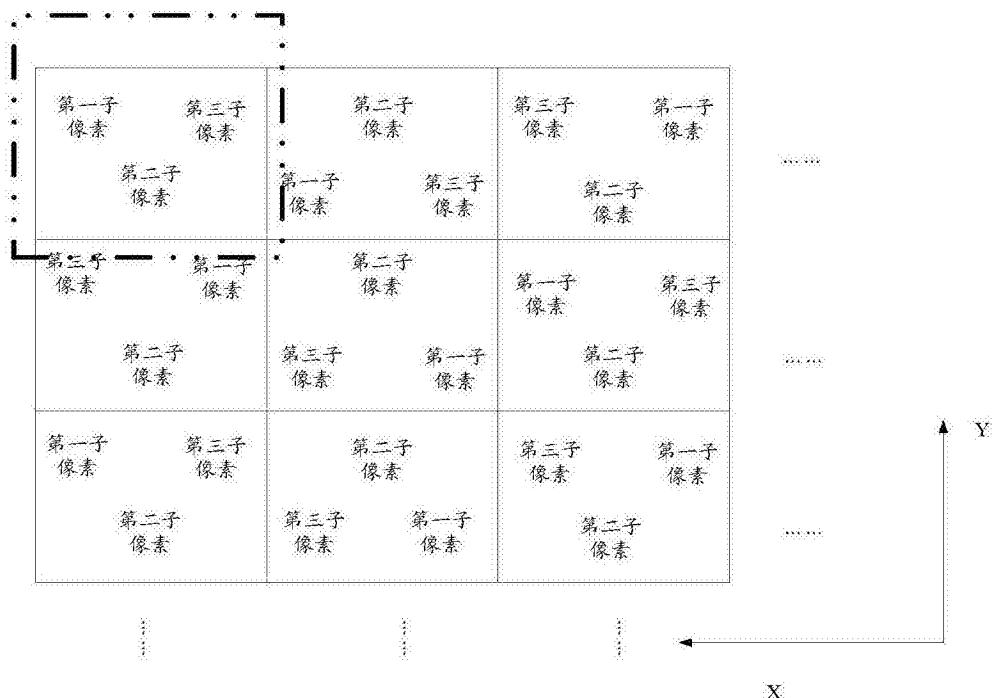

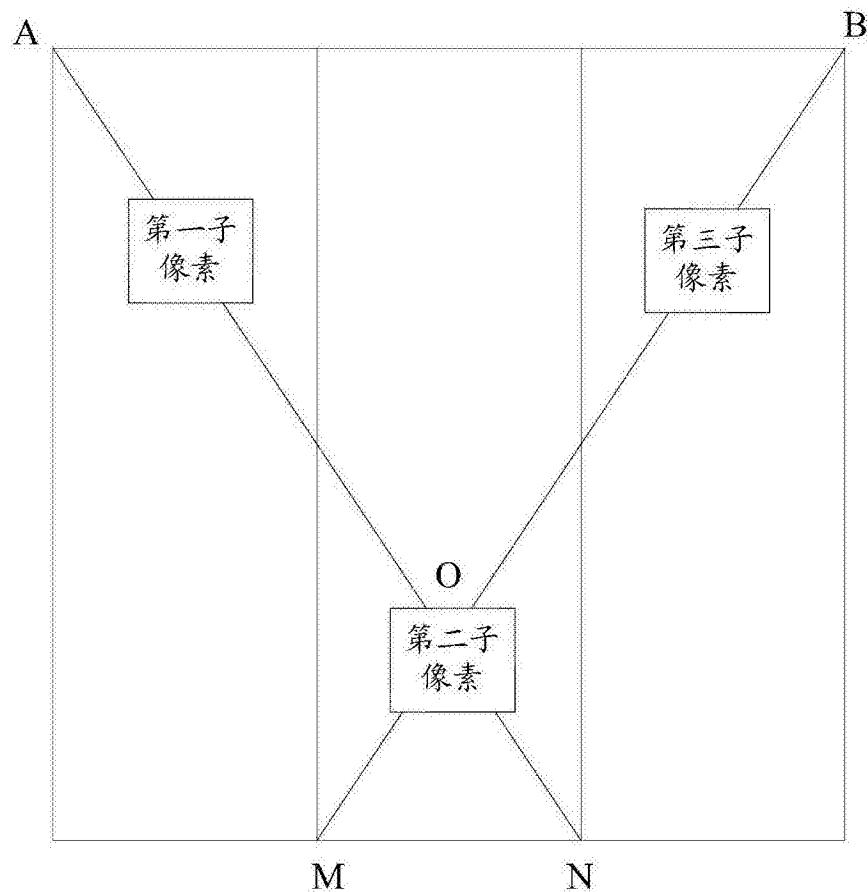

[0038] 图1为本发明实施例提供的一种像素阵列的结构示意图；

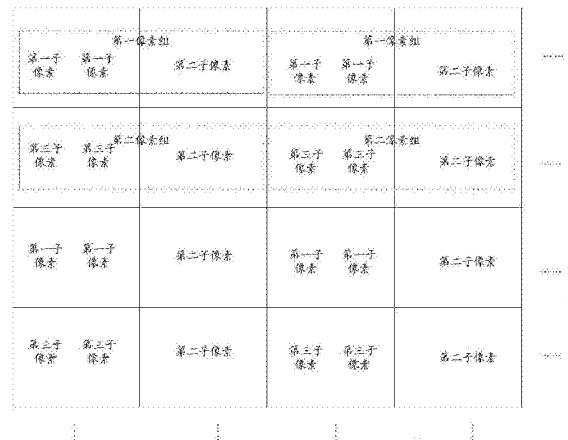

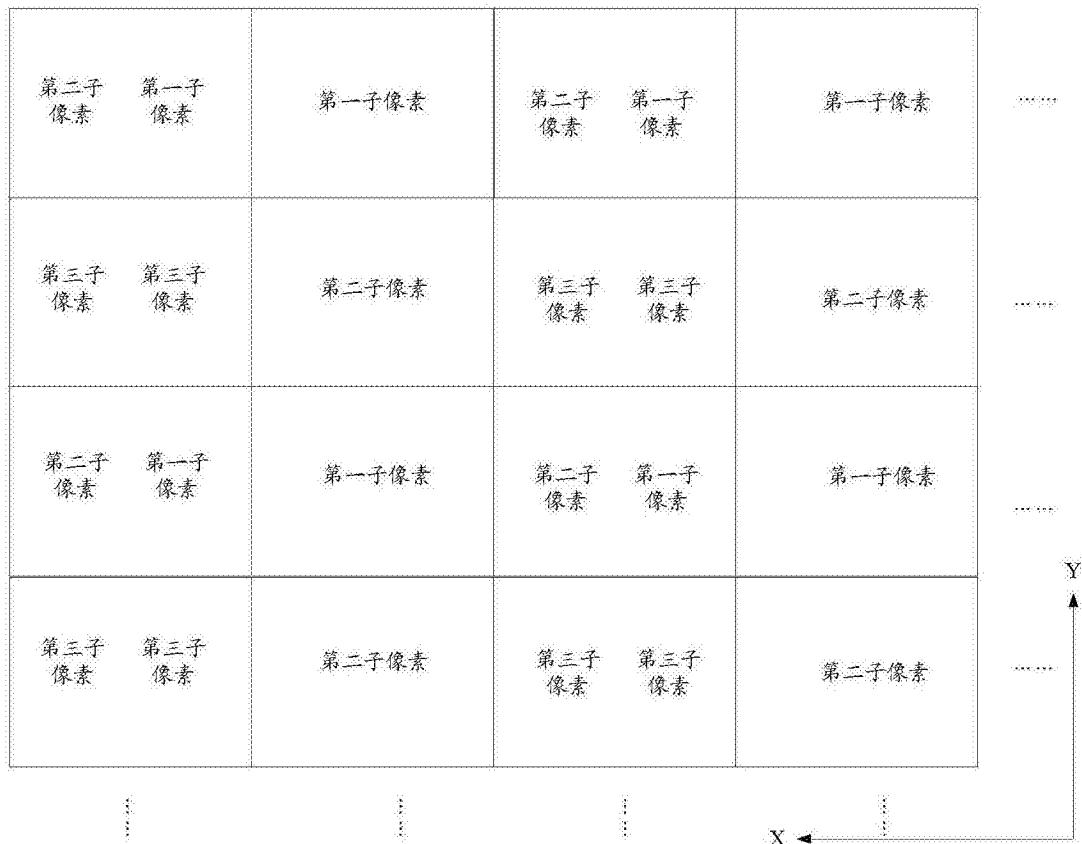

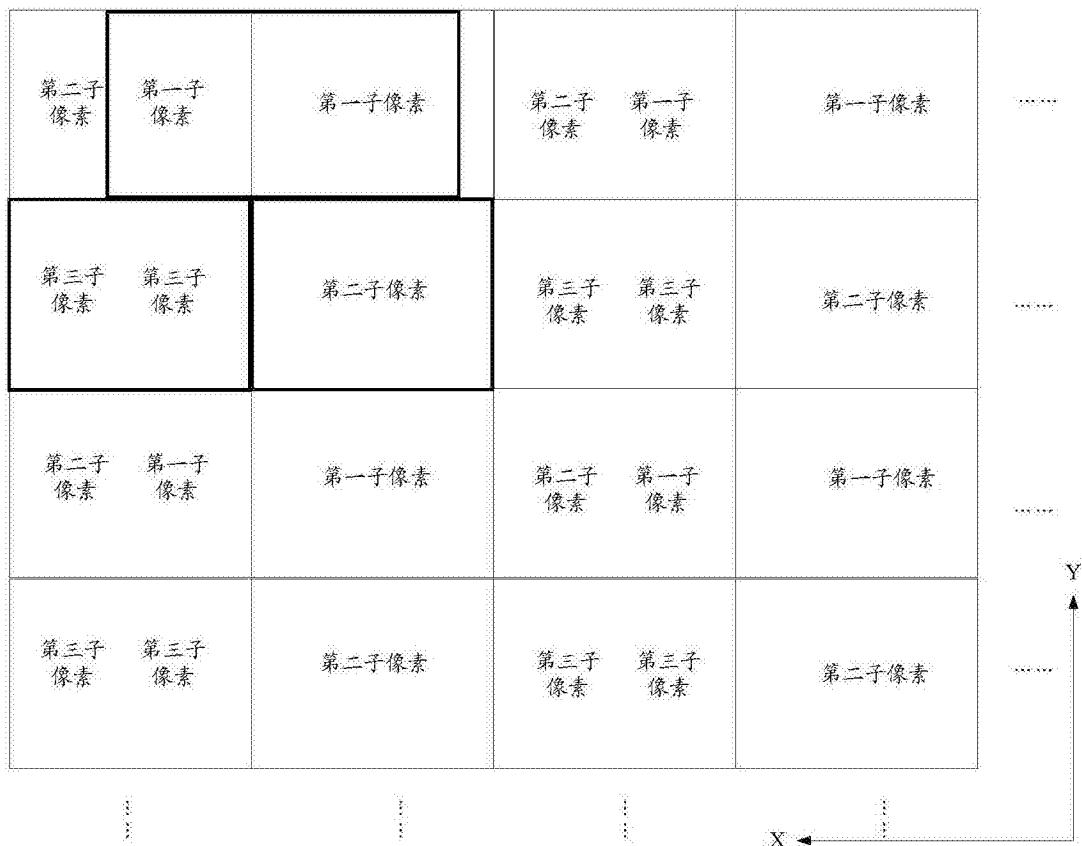

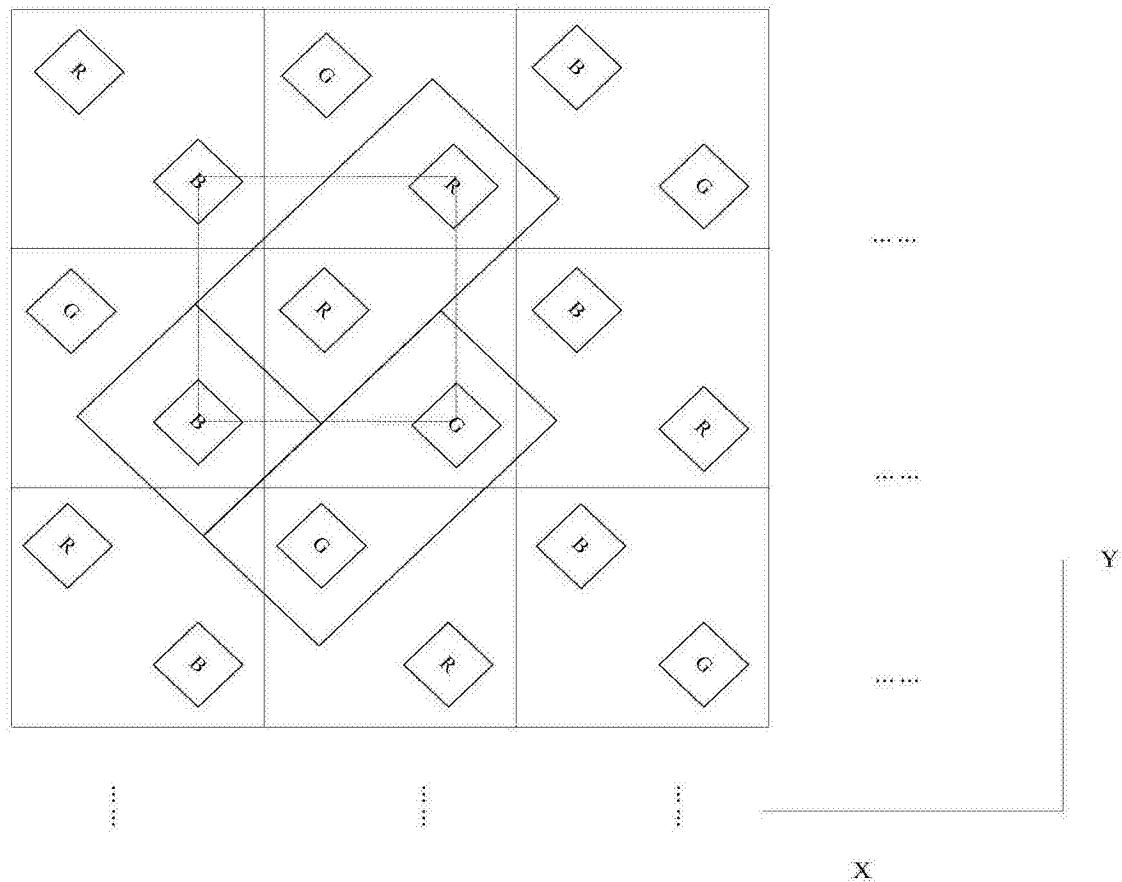

[0039] 图2为本发明实施例提供的另一种像素阵列的结构示意图；

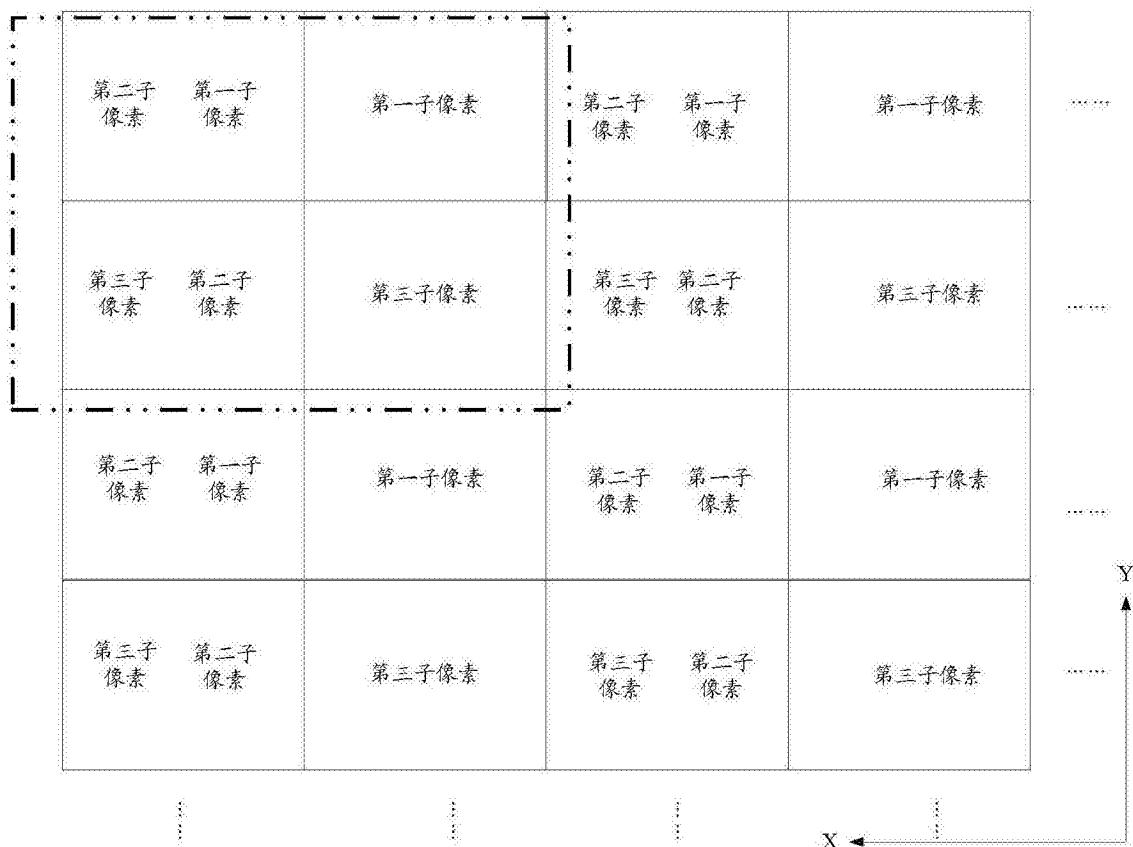

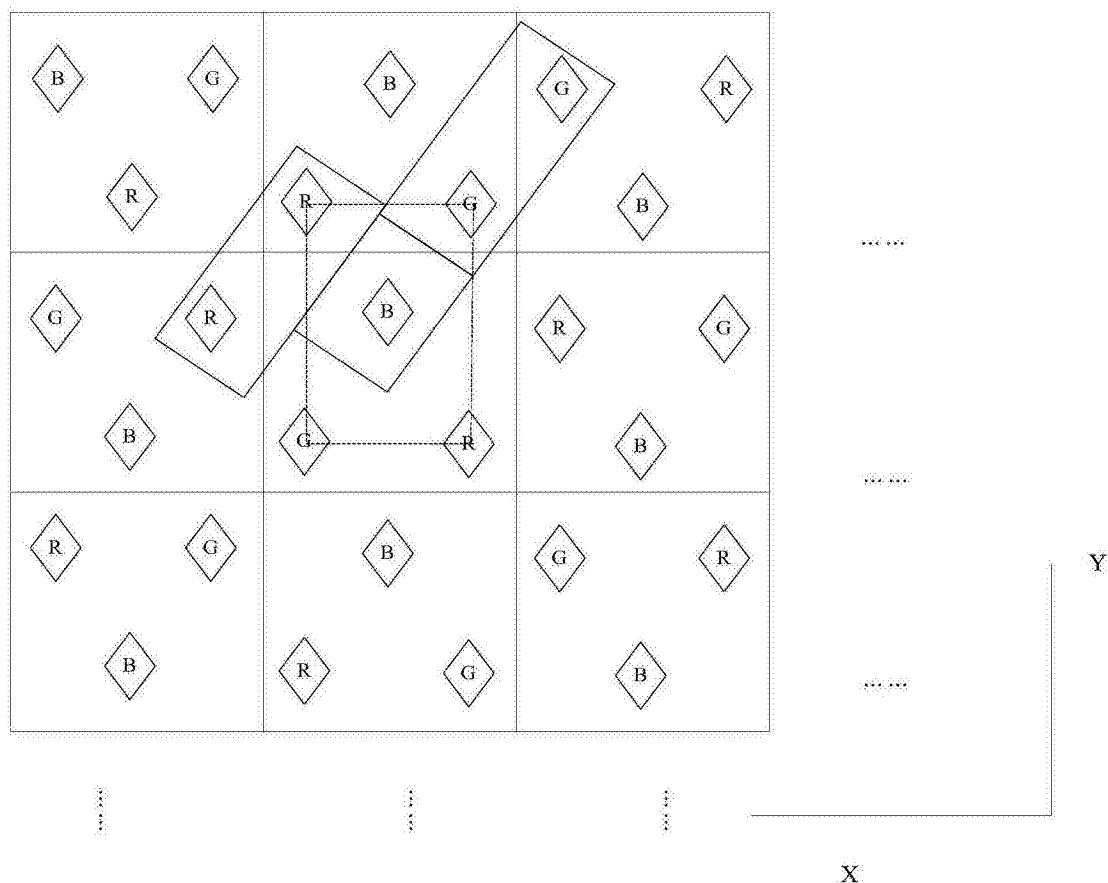

[0040] 图3为本发明实施例提供的另一种像素阵列的结构示意图；

[0041] 图4为本发明实施例提供的另一种像素阵列的结构示意图；

[0042] 图5为本发明实施例提供的四个最小排列单元中的子像素数量相等的像素阵列的结构示意图；

[0043] 图6为本发明实施例提供的1.5个最小排列单元中的子像素数量相等的像素阵列的结构示意图；

[0044] 图7为本发明实施例提供的1个最小排列单元中的子像素数量相等的像素阵列的结构示意图；

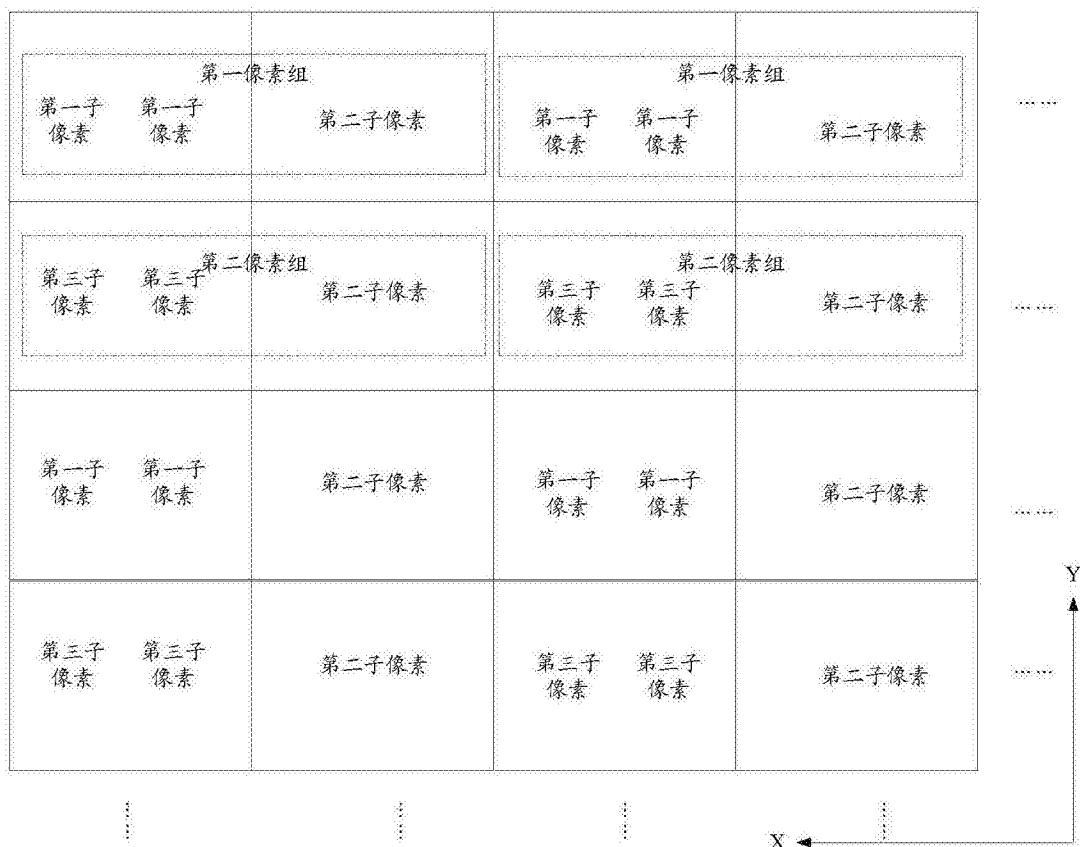

[0045] 图8为本发明实施例提供的另一种像素阵列的结构示意图；

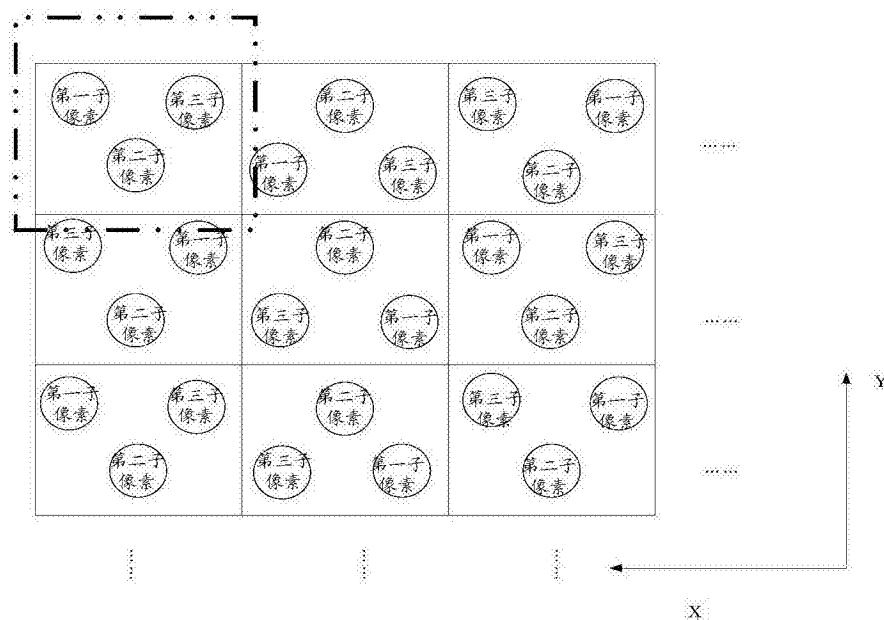

[0046] 图9为本发明实施例提供的子像素为圆形的一种像素阵列的结构示意图；

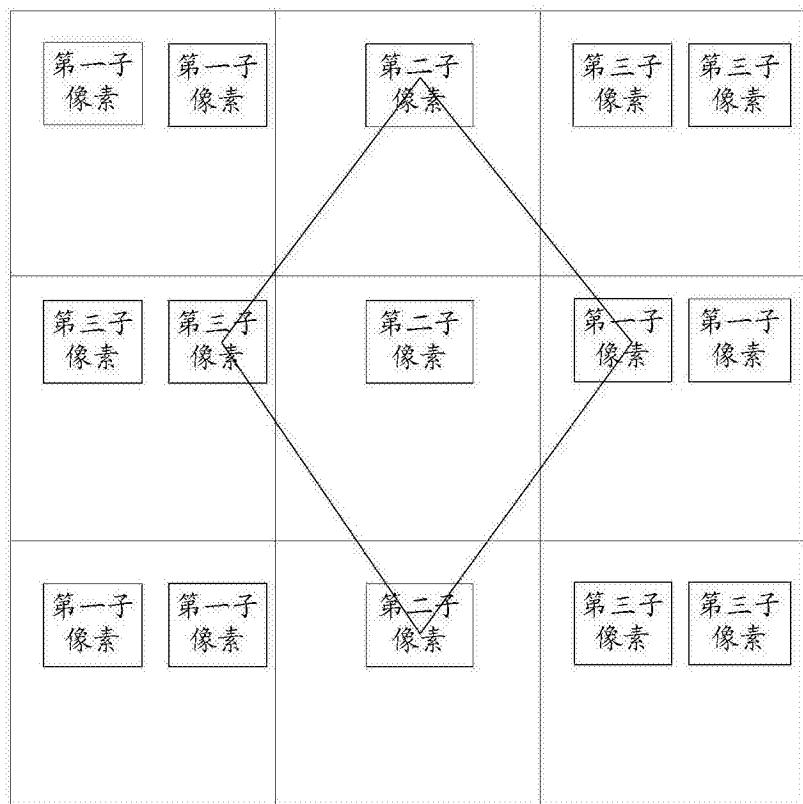

[0047] 图10为本发明实施例提供的第二子像素相邻的四个子像素构成的平行四边形的示意图；

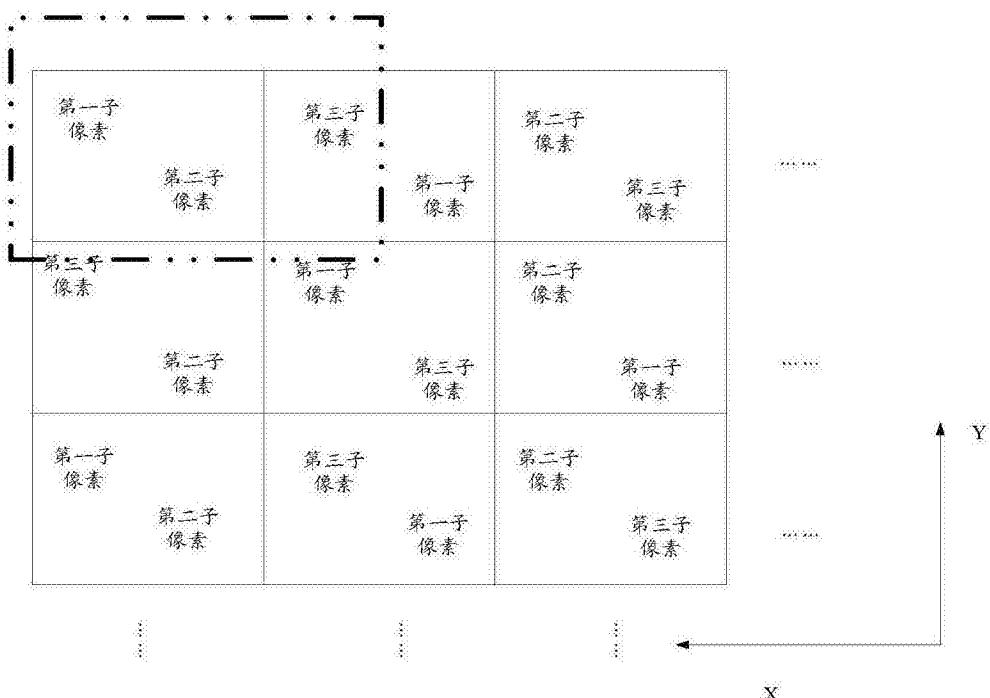

[0048] 图11为本发明实施例提供的在最小排列单元中排列三个不同的子像素的一种像素阵列的结构示意图；

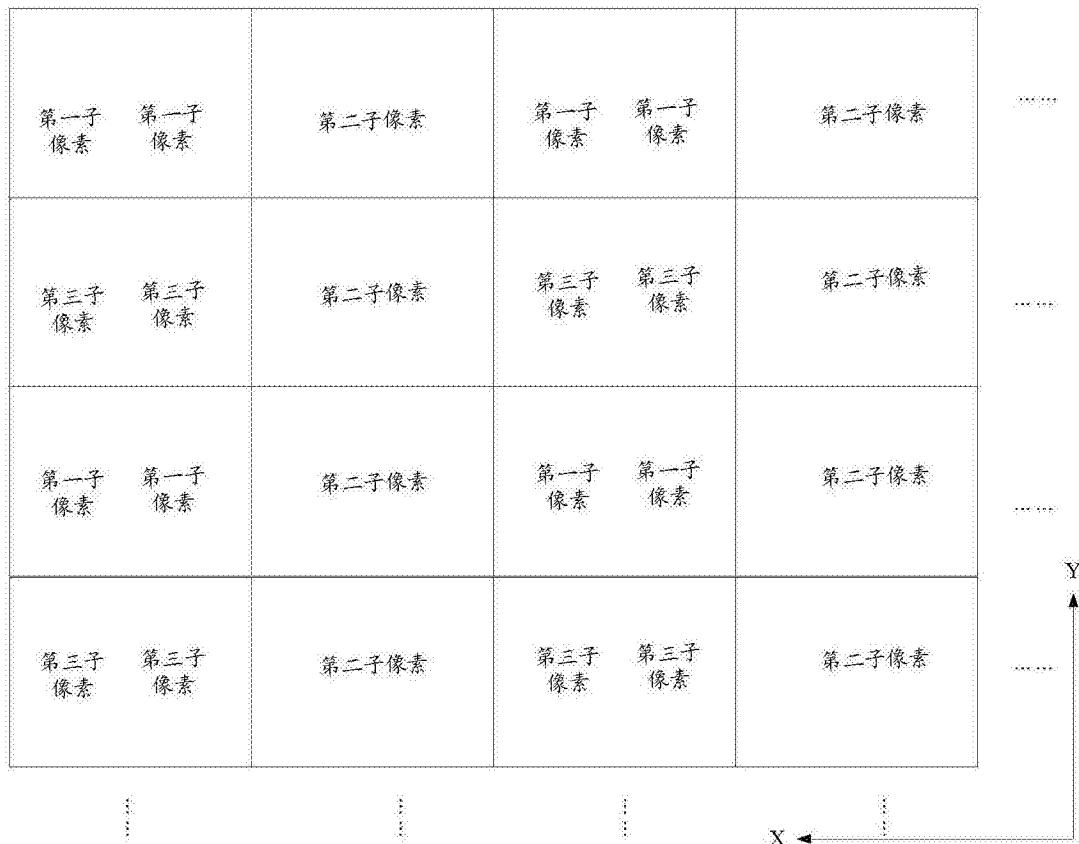

[0049] 图12为本发明实施例提供的实施例一的一种像素阵列的结构示意图；

[0050] 图13为本发明实施例提供的实施例二的一种像素阵列的结构示意图。

## 具体实施方式

[0051] 为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述,显然,所描述的实施例仅仅是本发明一部份实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

[0052] 本发明实施例提供一种像素阵列,如图1所示,所述像素阵列包括第一像素组以及第二像素组,所述第一像素组包括连续排列的至少两个第一子像素和一个第二子像素,所述第二像素组包括连续排列的至少两个第三子像素和一个第二子像素;

[0053] 所述第一像素组以第一方向重复排列,所述第二像素组以所述第一方向重复排列,所述第一像素组所在的直线与所述第二像素组所在的直线相平行且交替重复排列;

[0054] 所述像素阵列中至多四个相邻的最小排列单元中包括的所述第一子像素、所述第二子像素以及所述第三子像素的数量相同。

[0055] 在本发明实施例中,如图1所示,每一个方格表示最小排列单元,即像素阵列的最小区域,第一像素组以及第二像素组重复排列在由最小排列单元组成的像素阵列区域内;在本发明实施例中,规定每一个最小排列单元为正方形,形成的像素阵列区域为矩形,规定矩形的两个方向轴,X轴与Y轴。

[0056] 在本发明实施例中,第一像素组与第二像素组相互平行,且第一像素组与第二像素组是延第一方向重复排列的,如图1所示,图1表示的是第一方向为与X轴平行的方向排列的第一像素组以及第二像素组,当然,可选的,在本发明实施例中,如图2所示,还包括第一方向为与X轴成夹角的第一像素组以及第二像素组的排列方式,当然,夹角为大于零度的夹角。

[0057] 可选的,在本发明实施例中,图1与图2仅表示了一种可选的像素阵列方式,在本发明实施例中,以图1以及图2中第一行第一列的最小排列单元为第一像素组的起始排列单元,以第二行第一列的最小排列单元为第二像素组的起始排列单元,则在本发明实施例中还包括,第一像素组的起始排列单元中在像素阵列区域内第一像素组中的第一个像素不是起始的第一子像素,而是连续排列的第二子像素,如图3所示;或者是在像素阵列区域内的第一像素组中起始排列单元中的第一个像素为第二子像素,如图4所示;当然,第二像素组的排列方式也可以按照上述方法进行调整,在此不做赘述。

[0058] 可选的,在本发明实施例中,像素阵列区域内的第一像素组中的排列方式以及第二像素组中的排列方式可以同时进行错位变换,如图5所示,在第一像素组的起始排列单元中,第一个子像素为第二子像素,在第二像素组的起始排列单元中,第一个子像素为第三子像素;当然上述只是错位变换的一种可选的实施例,所有的错位变换方式都在本发明实施例的保护范围内。

[0059] 在本发明实施例中,当确定了第一像素组以及第二像素组的排列方式后,还需要保证每种子像素的发光效果,所以在本发明实施例中,规定了在至多相邻的四个最小排列单元中,第一子像素、第二子像素以及第三子像素的数量相同。

[0060] 可选的,在4个相邻的最小排列单元中,包括的第一子像素、第二子像素以及第三子像素的数量相同的排列方式如图1~5所示。其中,4个相邻的最小单元指的是能够构成“田”字格形式的四个最小排列单元。

[0061] 可选的,如图6所示,在1.5个相邻的最小排列单元中,包括的第一子像素、第二子

像素以及第三子像素的数量相同。

[0062] 可选的,如图7所示,在1个最小排列单元中,包括的第一子像素、第二子像素以及第三子像素的数量相同。

[0063] 在本发明实施例中,可选的,第一子像素为红色像素,在本发明实施例中用R表示,第二子像素为蓝色像素,在本发明实施例中用B表示,第三子像素为绿色像素,在本发明实施例中用G表示;当然,在本发明实施例中,第一子像素与第三子像素可以互换。

[0064] 在本发明实施例中,为了保证在OLED的PPI持续增高时,减小R色以及G色对应的金属掩膜板的开口制作难度,所以将两个R以及两个G制作成一个开口,有效的减小了金属掩膜板的开口的制作难度,例如,如图8所示,黑色边框表示的是在金属掩膜板进行开口的对应于像素阵列的位置,在本发明实施例中,两个第一子像素以及两个第三子像素使用一个开口,开口面积变大,有效的减小了金属掩膜板的开口的制作难度。

[0065] 可选的,在本发明实施例中,如图7所示,为了在金属掩膜板制作开口时形成规律,减小工艺难度,第一像素组中的相邻的两个子像素的中心延第一方向之间的距离相等,第二像素组中的相邻的两个子像素的中心延第一方向之间的距离相等。

[0066] 可选的,在本发明实施例中,每一种子像素的形状可以为四边形、圆形、三角形、椭圆形中的任一一种,以便于在金属掩膜板上对应进行开口。例如,如图9所示,每一种子像素的形状为圆形。

[0067] 在本发明实施例中,除了上述第一像素组以及第二像素组的排列方式外,还包括如图10的排列方式,即第一像素组还包括连续排列在第二子像素后的至少两个第三子像素;第二像素组还包括,连续排列在第二子像素后的至少两个第一子像素。当然,其它的第一像素组以及第二像素组的重复排列方式都在本发明实施例的保护范围内。

[0068] 可选的,在本发明实施例中,如图1~10所示,所述像素阵列中的各第二子像素延第二方向排列,且所述第二方向与所述第一方向不平行。在本发明实施例中,以图1为例,第一方向为平行于X轴的方向,图1中第二子像素的中心连线的方向为第二方向,第二方向为平行与Y轴的方向,第一方向与第二方向不平行。

[0069] 可选的,在本发明实施例中,第一方向上的任一第二子像素相邻的四个子像素构成平行四边形,并且平行四边形相邻顶点的子像素为不同种类的子像素。在本发明实施例中,当确定了第二子像素的中心位于第二方向上后,还需要根据第二子像素确定第一子像素以及第三子像素的关系,所以在本发明实施例中,当确定了第二子像素的位置后,根据第二子像素相邻的四个子像素构成平行四边形的特征,能够确定第一子像素以及第三子像素的位置。

[0070] 可选的,在本发明实施例中,如图10所示,第二子像素相邻的四个子像素指的是与第二子像素位置最近的四个子像素,以第二行第二列的最小排列单元中的第二子像素为例,相邻的四个子像素为第二方向上相邻的两个子像素以及第一方向上相邻的两个子像素。

[0071] 可选的,在本发明实施例中,每一个最小排列单元中排列两种不同类型的子像素。例如,如图6所示,每一个最小排列单元中排列了两种不同类型的子像素,与现有技术相比,增加了OLED的PPI。

[0072] 可选的,在本发明实施例中,若每一个最小排列单元中排列两种不同类型的子像

素时,为了减小制作金属掩膜板上子像素对应的开口的制作难度,第二像素的第二排列方向与第一方向的夹角成45度,如图6所示。

[0073] 可选的,在本发明实施例中,为了能够符合现有技术对OLED高PPI的要求,在每一个最小排列单元中排列三个子像素,如图7所示。

[0074] 可选的,在本发明实施例中,为了既能够在每一个最小排列单元中排列三个子像素,又需要保证三个子像素的发光率,还要保证第一子像素与第三子像素对应的金属掩膜板的开口增大,如图11所示,在本发明实施例中,还提供一种像素阵列方式,图11中的方格表示的是最小排列单元,M与N为最小排列单元中任一条边的两个三等分点,A为该边的对边靠近M点的最小排列单元的顶点,B为该边的对边靠近N点的最小排列单元的顶点,连接A点与N点,形成第一斜线,连接B点与M点,形成第二斜线,第一斜线与第二斜线的交点为0点,则将第二子像素放在0点的位置上,将第一子像素放在0点与A点的连线的任一位置上,将第三子像素放在0点与B点的连线的任一位置上。当然,本发明实施例中,第一子像素与第三子像素的位置可以交换,在此不做赘述。

[0075] 为了更好地说明本发明实施例中的内容,在此举例说明。

#### [0076] 实施例一

[0077] 在本发明实施例中,如图12所示,第一子像素为R,第二像素为B,第三子像素为G,第一像素组为R-R-B,第二像素组为G-G-B,则将第一像素组延第一方向连续重复排列,第二像素组延第一方向连续重复排列,并且,在本发明实施例中,第一方向为与Y轴夹角为45度方向;

[0078] 像素阵列区域内,每一个最小排列单元中包括两种不同种类的子像素,并且在像素阵列区域内,B色按照第二方向排列,即第二方向平行于Y轴方向;

[0079] 在像素阵列区域内,第一像素组与第二像素中的R、G、B之间的距离相等;

[0080] R、G、B三个子像素的形状为矩形,且矩形中的一条对角线平行于Y轴;

[0081] 可选的,在本发明实施例中,为了保证B色的发光率,还可以将B色的面积做的比R、G色大;

[0082] 可选的,在本发明实施例中,R、G、B三个子像素的形状可以为其它形状;

[0083] 排列区域内两个R色外的方框表示两个R色对应在金属掩膜板上的位置为同一个开口,两个G色外的方框表示两个G色对应在金属掩膜板上的位置为同一个开口;

[0084] R相邻的4个子像素能够组成矩形,R色在矩形的对角线交点的位置,相邻4个子像素中每两个相邻的子像素为不同像素。

#### [0085] 实施例二

[0086] 为了能够更好的满足OLED的高PPI的要求,在本发明实施例中,如图13所示,在每一个最小排列单元中排列三个子像素,提高OLED的物理PPI;

[0087] 其中,第一子像素为R,第二子像素为B,第三子像素为G,第一像素组为R-R-B,第二像素组为G-G-B,则将第一像素组延第一方向连续重复排列,第二像素组延第一方向连续重复排列;

[0088] 在每一个最小排列单元中,B位于最小排列单元的第一交点,R位于最小排列单元的第一交点与最小排列单元的第一顶点连线上的任一位置,B位于最小排列单元的第一交点与最小排列单元的第二顶点连线上的任一位置;

[0089] 其中,第一交点为第一斜线与第二斜线的交点,第一斜线为第一顶点与第二等分点的连线,第二斜线为第二顶点与第一等分点的连线,第一等分点和第二等分点位于最小排列单元中第一顶点和第二顶点所在边的对边上,第一等分点和第二等分点为对边的三等分点,第一等分点为远离第二顶点的等分点,第二等分点为远离第一顶点的等分点。

[0090] 在最小排列单元中,根据上述几何关系,可以确定第一单元的方向与Y轴成夹角为  $\text{Arc Tan}(2/3) \approx 33.66^\circ$ ;

[0091] 在像素阵列区域内,B色按照第二方向排列,即第二方向平行于Y轴方向;

[0092] 在像素阵列区域内,第一像素组与第二像素中的R、G、B之间的距离相等;

[0093] R、G、B三个子像素的形状为平行四边形,且平行四边形的一条对角线平行于Y轴;

[0094] 可选的,在本发明实施例中,为了保证B色的发光率,还可以将B色的面积做的比R、G色大;

[0095] 可选的,在本发明实施例中,R、G、B三个子像素的形状可以为其它形状;

[0096] 可选的,在本发明实施例中,R、G、B三个子像素的形状为相邻两边夹角为 $33.66^\circ$ 的平行四边形;

[0097] 排列区域内两个R色外的方框表示两个R色对应在金属掩膜板上的位置为同一个开口,两个G色外的方框表示两个G色对应在金属掩膜板上的位置为同一个开口;

[0098] R相邻的4个子像素能够组成矩形,R色在矩形的矩形的对角线交点的位置,相邻4个子像素中每两个相邻的子像素为不同像素。

[0099] 本发明是参照根据本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0100] 这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0101] 这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0102] 尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

[0103] 显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素阵列                                         |         |            |

| 公开(公告)号        | <a href="#">CN107978617A</a>                   | 公开(公告)日 | 2018-05-01 |

| 申请号            | CN201610919397.3                               | 申请日     | 2016-10-21 |

| [标]申请(专利权)人(译) | 上海和辉光电有限公司                                     |         |            |

| 申请(专利权)人(译)    | 上海和辉光电有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 上海和辉光电有限公司                                     |         |            |

| [标]发明人         | 陈凯凯<br>高志豪<br>屈晓娟                              |         |            |

| 发明人            | 陈凯凯<br>高志豪<br>屈晓娟                              |         |            |

| IPC分类号         | H01L27/32                                      |         |            |

| CPC分类号         | H01L27/3211 H01L27/3218                        |         |            |

| 代理人(译)         | 黄志华                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供一种像素阵列，涉及有机发光二极管显示技术领域，方法包括：像素阵列包括第一像素组以及第二像素组，第一像素组包括连续排列的至少两个第一子像素和一个第二子像素，第二像素组包括连续排列的至少两个第三子像素和一个第二子像素；第一像素组和第二像素组以第一方向重复排列，第一像素组所在的直线与第二像素组所在的直线相平行且交替重复排列；像素阵列中至多四个相邻的最小排列单元中包括的第一子像素、第二子像素以及第三子像素的数量相同。本发明实施例中，通过上述像素阵列，有效的解决了现有技术中R色和G色在OLED高PPI时难以制作相应开口的问题，保证了三种像素的发光率。