(12)发明专利

(10)授权公告号 CN 103682175 B

(45)授权公告日 2016.09.07

(21)申请号 201310435444.3

(51)Int.Cl.

(22)申请日 2013.09.23

H01L 51/56(2006.01)

(65)同一申请的已公布的文献号

H01L 27/32(2006.01)

申请公布号 CN 103682175 A

G09G 3/3241(2016.01)

(43)申请公布日 2014.03.26

(56)对比文件

(30)优先权数据

US 2004/0259326 A1, 2004.12.23, 说明书第0002、0332-0843段以及说明书附图25-26、28-30、43.

13/625,301 2012.09.24 US

CN 1739129 A, 2006.02.22, 说明书第9页的22行到第11页倒数第1行以及说明书附图3.

13/658,473 2012.10.23 US

US 2010/0178738 A1, 2010.07.15, 说明书第0005段.

(73)专利权人 国际商业机器公司

审查员 苏治平

地址 美国纽约

(72)发明人 李宁 D·K·萨达那

(74)专利代理机构 北京市中咨律师事务所

11247

代理人 贺月娇 于静

权利要求书3页 说明书10页 附图6页

(54)发明名称

形成包括具有半导体驱动电路的OLED显示器的结构的方法和半导体结构

(57)摘要

本发明涉及形成包括具有半导体驱动电路的OLED显示器的结构的方法和半导体结构。采用剥落来产生单晶半导体层。在剥落之前在单晶半导体衬底上形成互补金属氧化物半导体(CMOS)逻辑和存储器件。可以在剥落之前或之后形成有机发光二极管(OLED)驱动电路、太阳能电池单体、传感器、电池等。剥落的单晶半导体层可以被转移到衬底。OLED显示器可以形成在剥落的单晶半导体层中，以实现这样的结构：该结构包括集成在所述单晶半导体层上的具有半导体驱动电路的OLED显示器和其它功能器件。

1. 一种形成包括具有半导体驱动电路的OLED显示器的结构的方法,所述方法包括:

提供单晶半导体衬底,所述单晶半导体衬底具有形成在该单晶半导体衬底的暴露表面上的至少逻辑和存储器件;

在其上形成有所述至少逻辑和存储器件的所述单晶半导体衬底的所述暴露表面上形成表面保护层;

在所述表面保护层上方形成应力源层,所述应力源层具有导致在单晶半导体衬底内发生剥落型断裂的临界厚度和应力值;

剥落所述单晶半导体衬底,以提供剥落的单晶半导体层,所述剥落的单晶半导体层具有位于其表面上的所述至少逻辑和存储器件;

将衬底形成在所述剥落的单晶半导体层的与具有位于其上的所述至少逻辑和存储器件的表面相反的表面上;以及

在所述剥落的单晶半导体层上并且与所述至少逻辑和存储器件相邻地形成有机发光二极管(OLED)显示器。

2. 根据权利要求1所述的方法,其中所述单晶半导体衬底还包括位于所述单晶半导体衬底的所述暴露表面上并且与所述至少逻辑和存储器件相邻的OLED驱动电路,其中所述OLED驱动电路在形成所述表面保护层之前形成。

3. 根据权利要求1所述的方法,还包括在所述形成所述OLED显示器之前在所述剥落的单晶半导体层的一部分上形成OLED驱动电路。

4. 根据权利要求1所述的方法,其中形成所述表面保护层包括:选择Ti/W、Ti、Cr或Ni中的一者作为表面保护材料;以及沉积所述表面保护材料。

5. 根据权利要求1所述的方法,其中所述单晶半导体衬底的断裂韧度低于所述应力源层的断裂韧度。

6. 根据权利要求5所述的方法,其中所述应力源层包括金属、聚合物或它们的任何组合。

7. 根据权利要求6所述的方法,其中所述应力源层至少包括所述聚合物,并且所述聚合物是剥落引发带层。

8. 根据权利要求6所述的方法,其中所述应力源层包括所述金属,并且所述金属是镍。

9. 根据权利要求1所述的方法,其中在室温下进行所述剥落。

10. 根据权利要求1所述的方法,其中在低于室温的温度下进行所述剥落。

11. 根据权利要求1所述的方法,还包括在剥落之前在所述应力源层顶上形成处理衬底。

12. 根据权利要求1所述的方法,还包括在形成所述衬底之后去除所述应力源层。

13. 根据权利要求1所述的方法,还包括在形成所述衬底之前去除所述应力源层。

14. 根据权利要求1所述的方法,其中所述衬底是玻璃或塑料,并且通过接合而被形成在所述剥落的单晶半导体层的与具有位于其上的所述至少逻辑和存储器件的表面相反的表面上。

15. 根据权利要求1所述的方法,其中所述OLED显示器形成在OLED驱动电路上。

16. 根据权利要求15所述的方法,其中所述形成所述OLED显示器包括形成底部发射OLED器件阵列,其中所述底部发射OLED器件阵列的每个底部发射OLED器件包括底部透明电

极、有机电致发光材料和顶部电极。

17. 根据权利要求16所述的方法,其中所述形成所述底部发射OLED器件阵列包括:蚀刻位于相邻OLED驱动电路之间的所述剥落的单晶半导体层的暴露部分;以及形成所述底部透明电极,其中所述底部透明电极的一部分与位于所述剥落的单晶半导体层下方的衬底的最上表面直接接触。

18. 根据权利要求15所述的方法,其中所述形成所述OLED显示器包括形成顶部发射OLED器件阵列,其中所述顶部发射OLED器件阵列的每个顶部发射OLED器件包括底部电极、有机电致发光材料和顶部透明电极。

19. 一种按照如权利要求1—18中任意一项所述的方法形成的半导体结构,包括:

单晶半导体层,所述单晶半导体层具有位于该单晶半导体层的一部分上的有机发光二极管(OLED)显示器以及位于该单晶半导体层的另一部分上的CMOS逻辑和存储器件,所述OLED显示器具有下伏的OLED驱动电路。

20. 根据权利要求19所述的半导体结构,其中所述单晶半导体层包括选自Si、Ge、SiGe、SiGeC、SiC、Ge合金、GaSb、GaP、GaAs、InAs和InP的半导体材料。

21. 根据权利要求19所述的半导体结构,其中所述单晶半导体层包括硅。

22. 根据权利要求19所述的半导体结构,其中所述OLED驱动电路包括多个薄膜晶体管。

23. 根据权利要求19所述的半导体结构,还包括位于所述单晶半导体层的又一部分上的太阳能电池单体、电池、或传感器中的至少一者。

24. 根据权利要求19所述的半导体结构,还包括位于所述单晶半导体层的直接下方的玻璃衬底。

25. 根据权利要求19所述的半导体结构,还包括位于所述单晶半导体层的直接下方的塑性衬底。

26. 根据权利要求19所述的半导体结构,其中所述单晶半导体层具有小于100微米的厚度。

27. 根据权利要求19所述的半导体结构,其中所述OLED显示器包括底部发射OLED器件阵列。

28. 根据权利要求27所述的半导体结构,其中所述底部发射OLED器件阵列的每个底部发射OLED器件包括底部透明电极、有机电致发光材料和顶部电极。

29. 根据权利要求27所述的半导体结构,其中所述底部电极的一部分与位于所述单晶半导体层下方的衬底的最上表面直接接触。

30. 根据权利要求19所述的半导体结构,其中所述OLED显示器包括顶部发射OLED器件阵列。

31. 根据权利要求30所述的半导体结构,其中所述顶部发射OLED器件阵列的每个顶部发射OLED器件包括底部电极、有机电致发光材料和顶部透明电极。

32. 根据权利要求31所述的半导体结构,其中所述底部电极、所述有机电致发光材料和所述顶部透明电极中的每一者具有垂直地彼此一致的侧壁表面。

33. 根据权利要求19所述的半导体结构,其中所述OLED显示器包括OLED器件阵列,所述OLED器件阵列的每个OLED器件包括位于底部电极和顶部电极之间的作为有机电致发光材料的导电聚合物。

34. 根据权利要求33所述的半导体结构,其中所述底部电极或所述顶部电极之一包括透明导电氧化物。

35. 根据权利要求34所述的半导体结构,其中所述透明导电氧化物包括掺氟的锡氧化物(SnO<sub>2</sub>:F)、掺铝的锌氧化物(ZnO:Al)、锡氧化物(SnO)或铟锡氧化物。

36. 根据权利要求35所述的半导体结构,其中所述底部电极由铟锡氧化物构成。

37. 根据权利要求35所述的半导体结构,其中所述顶部电极由铟锡氧化物构成。

38. 根据权利要求33所述的半导体结构,其中所述导电聚合物包括聚对苯乙炔。

## 形成包括具有半导体驱动电路的OLED显示器的结构的方法和 半导体结构

### 技术领域

[0001] 本公开涉及形成半导体结构的方法,更具体地,涉及形成这样的半导体结构的方法:该半导体结构包括集成在同一单晶半导体衬底上的具有有机发光二极管(OLED)驱动电路的OLED显示器、逻辑和存储器件以及其它功能器件。本公开还涉及使用本公开的方法形成的半导体结构。

### 背景技术

[0002] 近年来,诸如计算笔记本和个人数字助理(PDA)的移动信息和电信装置经历了快速的发展。这种装置正变得更轻且更高效。最近,平板显示器正变得越来越普遍地用于这些装置。当前,液晶显示器(LCD)被用作平板显示器,但是LCD具有一些缺点,例如需要背景照明以及有线的视角。

[0003] 除了液晶,有机发光二极管——所谓的“有机LED”或“OLED”——也可以用在平板显示器中。这种OLED与LCD相比具有更高的发光效率以及增加的视角。OLED的基本特征是特定有机材料的电致发光。所述特定有机材料以一级近似确定由对应的OLED发射的光的颜色,即波长。

[0004] 典型的OLED包括通常由玻璃或类似的透明材料制成的衬底。阳极层位于衬底上。阳极层可以由具有相对高功函数的材料制成并且对于可见光是基本透明的。用于阳极层的典型材料是铟锡氧化物(ITO)。电致发光材料层位于阳极层上,用作有机OLED的发射层。用于形成发射层的常见材料是诸如例如聚对苯乙炔(PPV)以及像三(8-羟基喹啉)铝(Alq<sub>3</sub>)那样的分子。在分子的情况下,发射层典型地包括若干层分子。具有较低功函数的材料(如铝(AI)、钙(Ca)或镁(Mg))的阴极层位于发射层上。在OLED的操作期间,阴极层和阳极层被连接到电源。

[0005] 电致发光的基本原理以及因此OLED的基本原理如下:阳极层和阴极层向发射层中注入电荷载流子,即电子和空穴。在发射层中,电荷载流子被输运并且电荷相反的电荷载流子形成所谓的激子,即受激状态。激子通过产生光而辐射衰变至基态。然后所产生的光被OLED通过由例如ITO的透明材料制成的阳极层发射。所产生的光的颜色取决于用于有机层的材料。

[0006] 此外,已知所谓的多层OLED。多层OLED包括多个阴极层和/或多个有机层和/或多个阳极层。通过使用多个有机层,OLED的效率与包括单个有机层的有机LED相比增加。多个有机层的两个有机层之间的界面对于至少一种电荷载流子类型可以用作降低流过二极管的电流的阻挡物(barrier)。因此,所述至少一种电荷载流子类型在所述界面处聚集并且因此电子和空穴的复合概率增加,得到更高效率的OLED。

### 发明内容

[0007] 提供了一种成本有效的方法,该方法在将诸如例如逻辑(Logic)、存储器、太阳能

电池单体、电池和/或传感器的各种电子功能器件(function)与OLED显示器集成在单片半导体材料上的同时,改善了OLED驱动电路的性能。特别地,本公开利用剥落(spalling)以产生剥落的包含用于OLED显示器的驱动电路的半导体材料,同时集成包括例如逻辑、存储器、传感器、电池和/或太阳能电池单体的很多功能器件。OLED显示器的驱动电路得到改善,具有更大的驱动电流和更长的寿命。因此通过使用本公开的方法,使得逻辑、存储器和其它装置的单片集成成为可能。

[0008] 具体地,采用剥落来产生单晶半导体层。在剥落之前在单晶半导体衬底上形成互补金属氧化物半导体(CMOS)逻辑和存储器件。可以在剥落之前或之后形成OLED驱动电路、太阳能电池单体、传感器、电池等。剥落的单晶半导体层可以被转移到衬底。OLED显示器可以形成在剥落的单晶半导体层中以实现这样的结构:该结构包括集成在所述单晶半导体层上的具有半导体驱动电路的OLED显示器和其它功能器件。

[0009] 在本公开的一个方面,提供了一种形成包括具有半导体驱动电路的OLED显示器的结构的方法。本公开的方法包括提供单晶半导体衬底,该单晶半导体衬底具有形成在该单晶半导体衬底的暴露表面上的至少逻辑和存储器件。然后在其上形成有所述至少逻辑和存储器件的所述单晶半导体衬底的暴露表面上形成表面保护层。然后在所述表面保护层上方形成应力源层并且之后执行剥落。该剥落提供剥落的单晶半导体层,该剥落的单晶半导体层具有位于其表面上的所述至少逻辑和存储器件。将衬底形成在所述剥落的单晶半导体层的与具有位于其上的所述至少逻辑和存储器件的表面相反的表面上。接下来,在所述剥落的单晶半导体层上并且与所述至少逻辑和存储器件相邻地形成有机发光二极管(OLED)显示器。

[0010] 在本公开的其它方面,提供了一种半导体结构。该半导体结构包括单晶半导体层,所述单晶半导体层具有位于该单晶半导体层的一部分上的OLED显示器以及位于该单晶半导体层的另一部分上的CMOS逻辑和存储器件,所述OLED显示器具有下伏的(underlying) OLED驱动电路。

## 附图说明

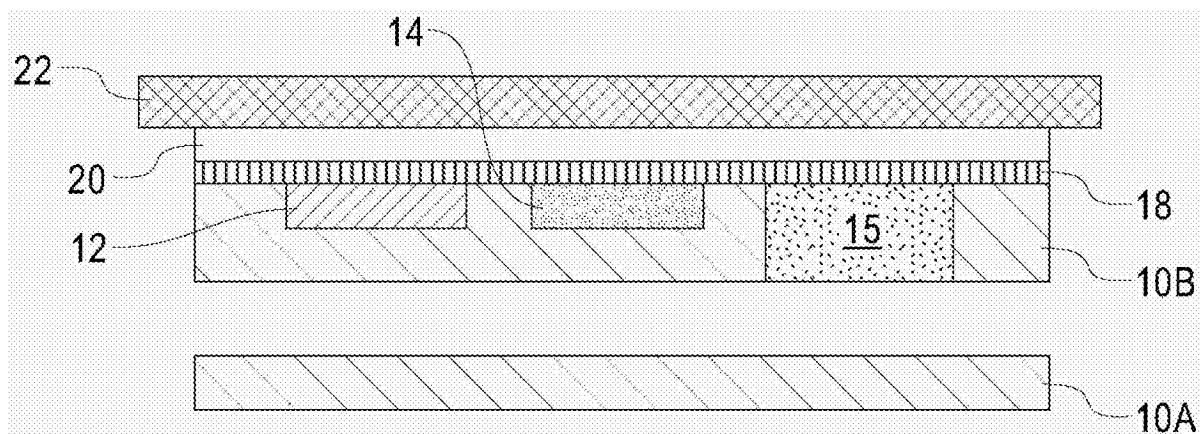

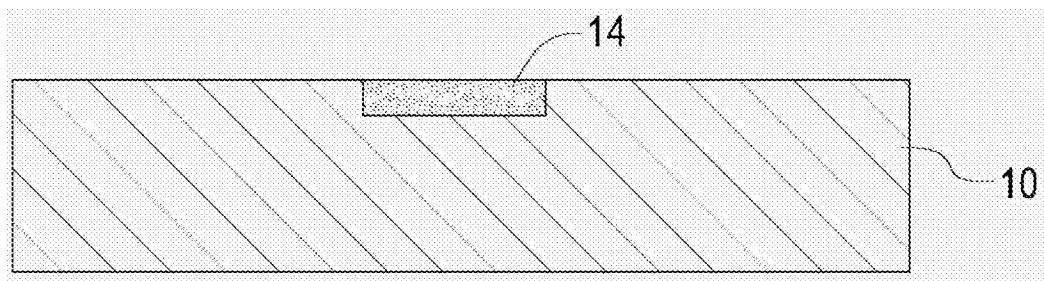

[0011] 图1是(通过横截面视图)示例出根据本公开的第一方法实施例的单晶半导体衬底的图示,该单晶半导体衬底至少包括在其上制造的OLED驱动电路以及逻辑和存储器件。

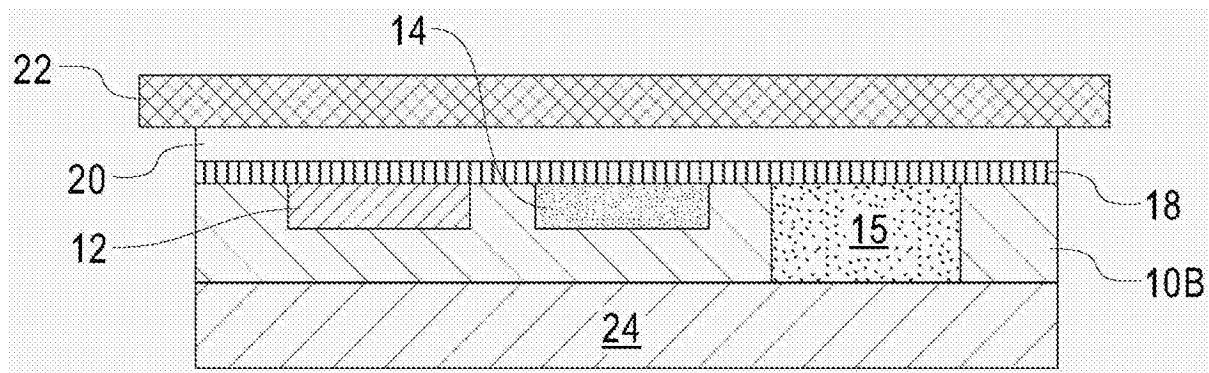

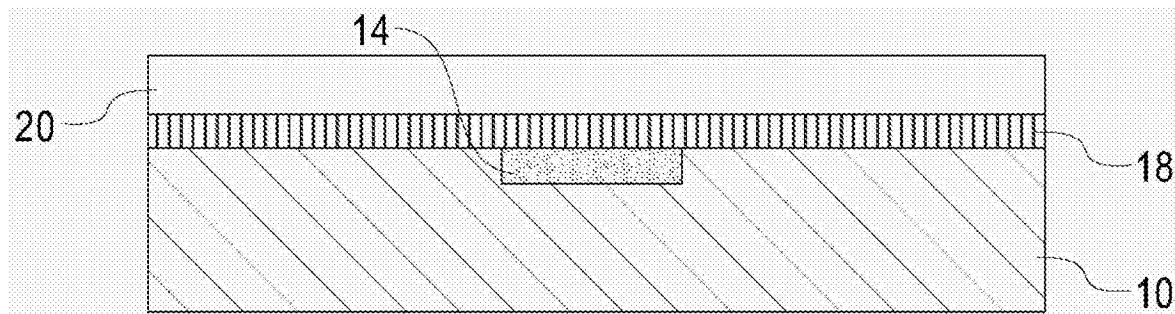

[0012] 图2是(通过横截面视图)示例出在单晶半导体衬底的暴露表面上形成表面保护层之后以及在表面保护层上方形成应力源层之后的图1的结构的图示。

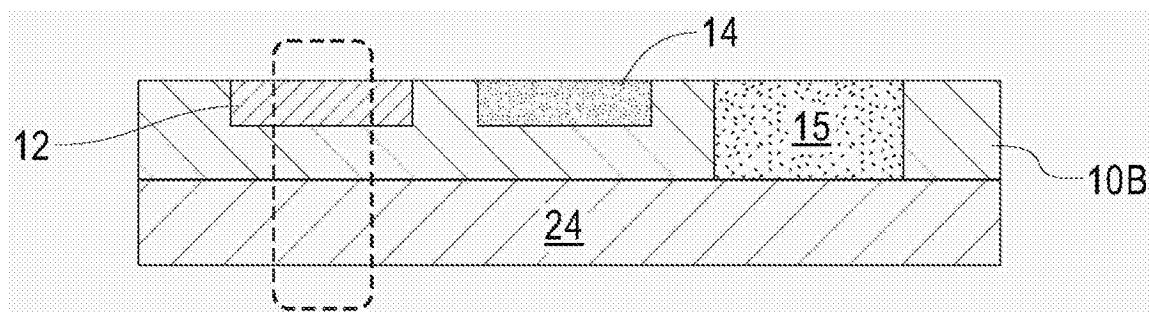

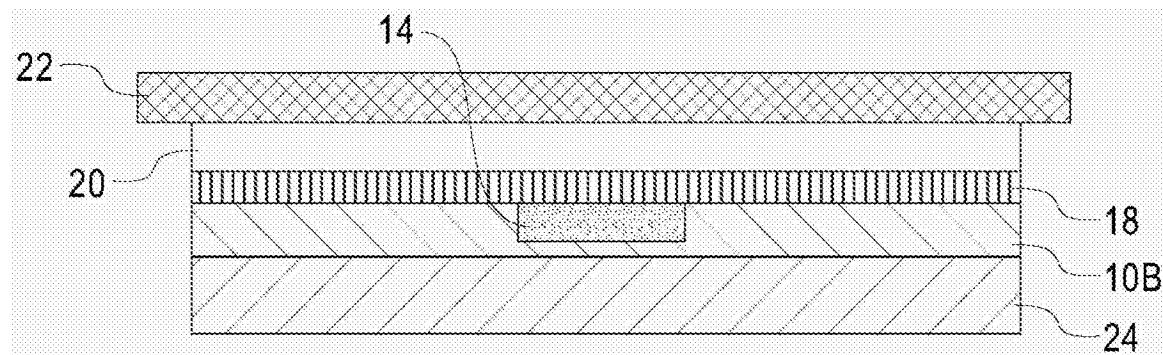

[0013] 图3是(通过横截面视图)示例出在应力源层上方形成处理衬底(handle substrate)之后并且在剥落之后的图2的结构的图示。

[0014] 图4是(通过横截面视图)示例出在剥落的单晶半导体层的最底部表面上形成衬底之后的图3的结构的图示。

[0015] 图5是(通过横截面视图)示例出在从剥落的单晶半导体层去除所述处理衬底、应力源层和表面保护层之后的图4的结构的图示。

[0016] 图6是图5所示例的结构的图示,示出了沿着进入以及伸出纸的平面的圈出区域中的OLED驱动电路。

[0017] 图7A是根据本公开的其中提供具有底部发射OLED显示器的实施例、在蚀刻位于相

邻OLED驱动电路之间的所述剥落的单晶半导体层的暴露部分之后的图6所示例的结构的图示。

[0018] 图7B是在形成底部透明电极之后的图7A所示例的结构的图示。

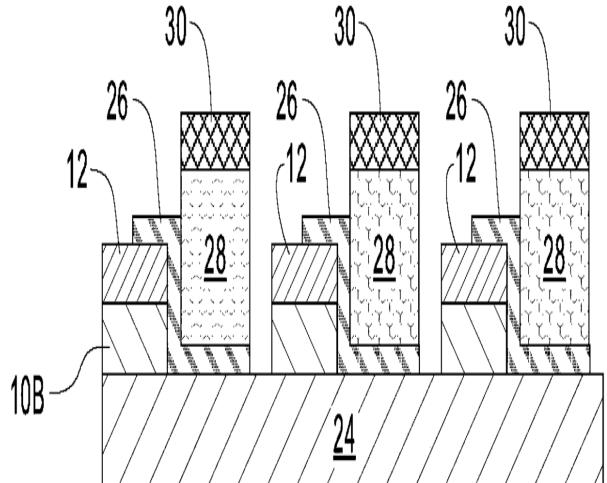

[0019] 图7C是在形成有机电致发光材料和顶部电极之后的图7B所示例的结构的图示。

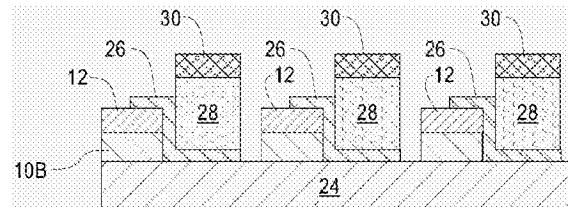

[0020] 图8是根据本公开的其中提供具有顶部发射的OLED显示器的实施例、在沉积底部电极、有机电致发光材料和顶部透明电极之后的图6所示例的结构的图示。

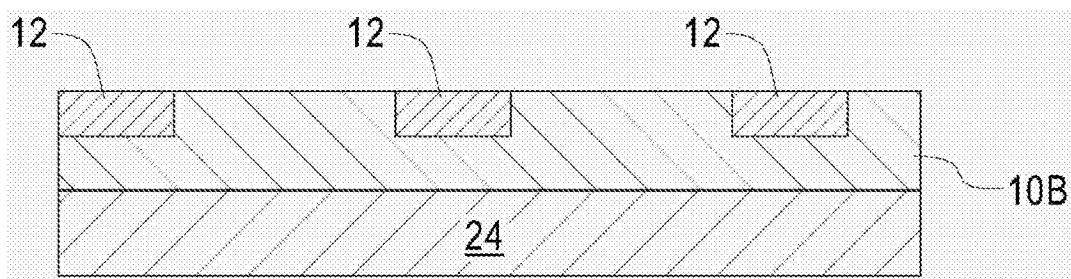

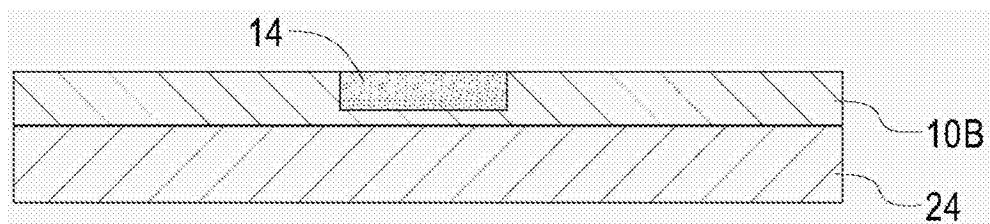

[0021] 图9是(通过横截面视图)示例出根据本公开的第二方法实施例的单晶半导体衬底的图示,该单晶半导体衬底包括在其上制造的逻辑和存储器件。

[0022] 图10是(通过横截面视图)示例出在单晶半导体衬底的暴露表面上形成表面保护层之后以及在所述表面保护层上方形成应力源层之后的图9的结构的图示。

[0023] 图11是(通过横截面视图)示例出在应力源层上方形成处理衬底之后并且在剥落之后的图10的结构的图示。

[0024] 图12是(通过横截面视图)示例出在剥落的单晶半导体层的最底部表面上形成衬底之后的图11的结构的图示。

[0025] 图13是(通过横截面视图)示例出在从剥落的单晶半导体层去除所述处理衬底、应力源层和表面保护层之后的图12的结构的图示。

[0026] 图14是(通过横截面视图)示例出在形成可选的其它功能器件之后并且在形成OLED驱动电路之后的图13的结构的图示。

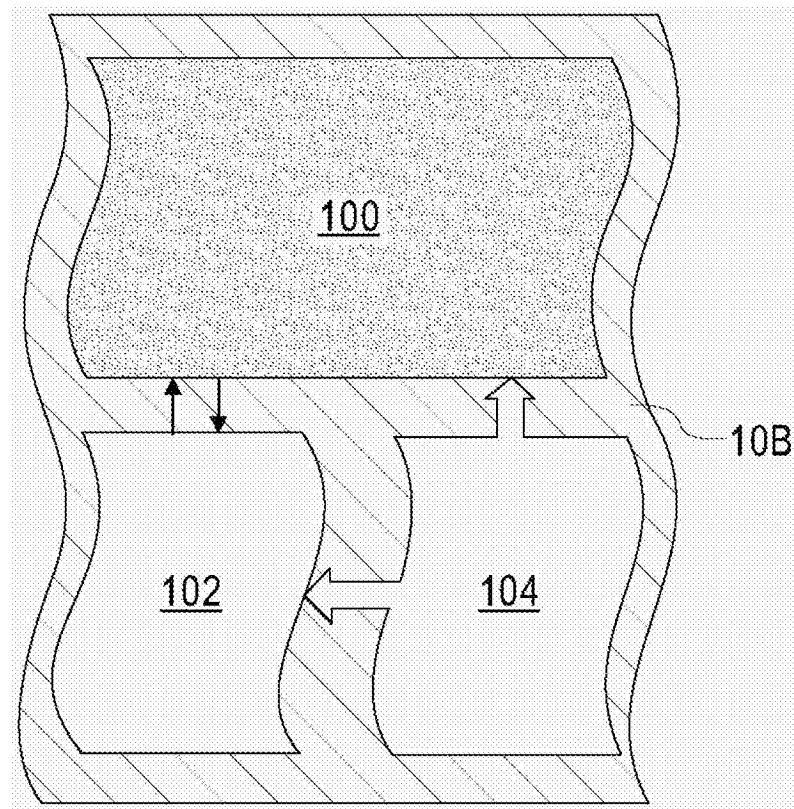

[0027] 图15是(通过自顶向下视图)示例出根据本公开的半导体结构的图示,该半导体结构包括集成在同一单晶半导体层上的具有OLED驱动电路的OLED显示器、CMOS逻辑和存储器件以及其它功能器件。

## 具体实施方式

[0028] 现在将参考下面的讨论和本申请的附图更详细地描述提供了用于形成半导体结构的方法的本公开,在所述半导体结构中具有OLED驱动电路的OLED显示器、CMOS逻辑和存储器件、以及其它功能器件被集成在同一单晶半导体衬底上。注意,本申请的附图是仅为了示例的目的而提供的,因此它们未按比例绘制。在附图和后面的描述中,相似的材料用相似附图标记指代。为了下文的描述,词语“上”、“下”、“右”、“左”、“垂直”、“水平”、“顶部”、“底部”及其派生词应当涉及在本申请的附图中取向的部件、层和/或材料。

[0029] 在下面的描述中,阐述了大量的特定细节,例如具体的结构、部件、材料、尺寸、处理步骤和技术,以便提供对本发明的彻底的理解。然而,本领域普通技术人员将理解,本公开可以在没有这些特定细节的情况下以可行的备选工艺选项来实施。在其它情况下,未详细描述公知的结构或处理步骤,以免使本公开的各种实施例模糊不清。

[0030] 诸如显示器、逻辑、存储器、电池、传感器等的电子模块通常分开制造并且连接到一起以实现电子系统。这种构造有缺点。例如,OLED显示器由基于非晶硅或多晶硅的薄膜晶体管(TFT)驱动。然而,这些技术有缺点(非晶硅的驱动电流小且寿命短;多晶硅需要精确的工艺控制以及相对高的处理温度)并且能够用增加成本的单晶硅驱动电路改善。同样,逻辑和存储器形成在单晶硅芯片上并且不能与显示器和其它功能器件单片集成。这种混合方法使得系统不是那么有效率并且增加了封装成本。此外,随着触摸屏显示器作为人-机界面在

电子装置中变得越来越重要,需要成本有效的方式来提高OLED驱动电路的性能以及将各种电子功能器件与OLED显示器集成在单片半导体材料上。

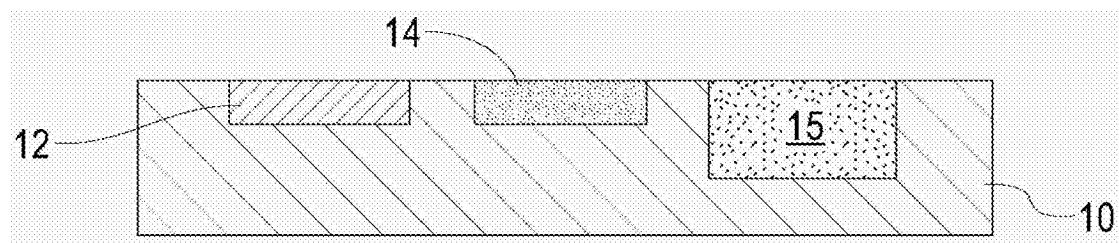

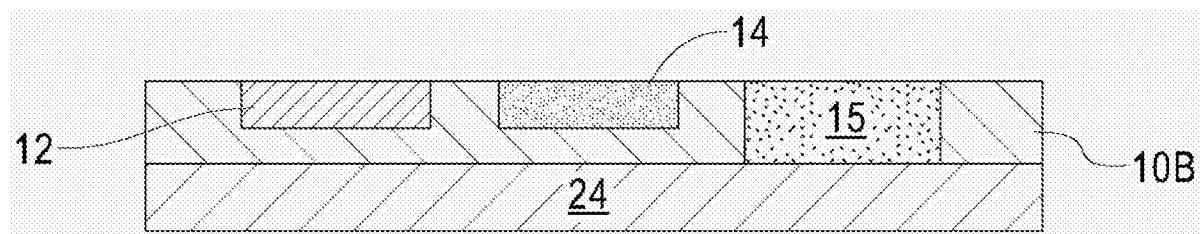

[0031] 首先参考图1,示例了根据本公开的第一方法实施例的单晶半导体衬底10,该单晶半导体衬底10至少包括在其上制造的OLED驱动电路12以及逻辑和存储器件14。单晶半导体衬底10还可以包括也形成于其上的其它功能器件,例如传感器、电池和/或太阳能电池单体。在图1中,元件15表示能够在单晶半导体衬底10上制造的这些其它功能器件。

[0032] 注意,尽管图中示出了OLED驱动电路12、逻辑和存储器件14以及其它功能器件15位于衬底10内,但是本领域技术人员将理解,OLED驱动电路12、逻辑和存储器件14以及其它功能器件可位于单晶半导体衬底10的表面上和/或内。本公开的图仅仅提供了这些功能器件可能存在于单晶半导体衬底10上的位置的表示。

[0033] 与术语单晶半导体衬底10结合使用的术语“单晶”表示其中整个样品的晶格直到样品的边缘是连续的并且不中断的,其中没有晶界。能够在本公开中采用的单晶半导体衬底10包括其断裂韧度小于随后描述的应力源材料的断裂韧度的半导体材料。断裂韧度是描述包含裂纹的材料的抗断裂的能力的特性。断裂韧度标记为 $K_{Ic}$ 。下标Ic表示在垂直于裂纹的法向张应力下打开的I型裂纹,并且c意味着它是临界值。I型断裂韧度典型地是最重要的值,这是因为剥落型断裂通常发生在衬底中的II型应力(剪切)为零的位置处,并且通常在负载条件下不存在III型应力(撕裂)。断裂韧度是表达当存在裂纹时材料对于脆性断裂的抗耐性的定量方式。

[0034] 单晶半导体衬底10的半导体材料可以包括但是不限于Si、Ge、SiGe、SiGeC、SiC、Ge合金、GaSb、GaP、GaAs、InAs、InP、以及所有其它III-V或II-VI化合物半导体。典型地,单晶半导体衬底10由硅构成。在一些实施例中,单晶半导体衬底10是体半导体材料。在其它实施例中,单晶半导体衬底10可以包括层叠半导体材料,诸如例如绝缘体上半导体或聚合物衬底上半导体。能够用作单晶半导体衬底10的绝缘体上半导体衬底的示例性例子包括绝缘体上硅和绝缘体上硅锗。

[0035] 单晶半导体衬底10可以是掺杂的、未掺杂的或包含掺杂区域和未掺杂区域。

[0036] OLED驱动电路12、逻辑和存储器件14、以及诸如例如传感器、电池和/或太阳能电池单体的其它功能器件15可以使用本领域技术人员公知的技术形成。可以利用本公开的方法将包括OLED驱动电路12、逻辑和存储器件14、以及其它功能器件15的衬底10的上部从单晶半导体衬底10的剩余部分去除。

[0037] 贯穿本公开使用术语“OLED驱动电路”来表示利用诸如薄膜晶体管(TFT)元件的沉积以及通过光刻和蚀刻对这些元件进行构图的常规技术形成的TFT的网络,即阵列。本申请中未提供关于OLED驱动电路的具体细节,以免使得本公开的方法变得模糊不清。

[0038] 贯穿本公开使用术语“逻辑器件”来表示能够利用诸如晶体管元件的沉积以及通过光刻和蚀刻对这些元件进行构图的常规技术制造的CMOS晶体管的阵列。本申请中未提供关于逻辑器件的具体细节,以免使得本公开的方法变得模糊不清。

[0039] 贯穿本公开使用术语“存储器件”来表示能够存储信息的CMOS晶体管和电容器的阵列。可以利用本领域技术人员公知的常规技术制造所述存储器件。本申请中未提供关于存储器件的具体细节,以免使得本公开的方法变得模糊不清。

[0040] 注意,尽管本公开的该实施例在本公开的此点描述和示例了存在于单晶半导体衬

底10上的OLED驱动电路12、逻辑和存储器件14以及其它功能器件15，但是本公开和方法不限于仅仅这种实施例。其它实施例是可能的，只要在本公开的此点至少逻辑和存储器件14形成在单晶半导体衬底10上即可。

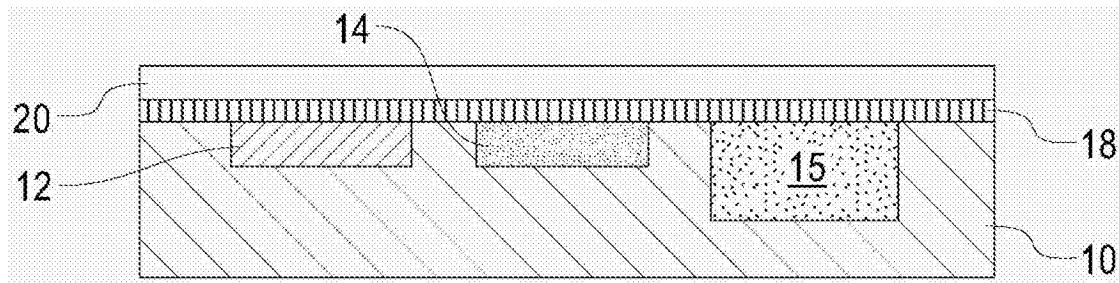

[0041] 参考图2，示例了在单晶半导体衬底10的暴露表面上形成表面保护层18之后以及在所述表面保护层18上方形成应力源层20之后的图1的结构。

[0042] 在本公开中采用的表面保护层18包括可以用作随后形成的应力源层20的蚀刻停止层的任何材料。在本公开的一个实施例中，表面保护层18可以包括但是不限于Ti/W、Ti、Cr、Ni或它们的任何组合。通常，并且当将Ni用作应力源层20的材料时，表面保护层18包含Ti。表面保护层18可以包括单个层或者其可以包括含有至少两个不同的层的多层结构。

[0043] 表面保护层18可以在室温(15°C-40°C，即288K到313K)或更高的温度下形成。在一个实施例中，表面保护层18可以在20°C(293K)到180°C(353K)的温度下形成。在另一个实施例中，表面保护层18可以在20°C(293K)到60°C(333K)的温度下形成。

[0044] 可以利用本领域技术人员公知的沉积技术形成表面保护层18。例如，可以通过溅射、化学气相沉积、等离子体增强化学气相沉积、化学溶液沉积、物理气相沉积以及镀敷(plating)，形成表面保护层18。当采用溅射沉积时，溅射沉积工艺可以进一步包括在沉积之前的原位溅射清洁工艺。

[0045] 在一个实施例中，表面保护层18典型地具有5nm到200nm的厚度，其中100nm到150nm的厚度更典型。在本公开中也可以采用在上述厚度范围以下和/或以上的表面保护层18的其它厚度。

[0046] 在一些实施例中，并且在形成应力源层20之前，可以在表面保护层18上形成可选的镀敷籽层(未示出)。典型地在随后要形成的应力源材料是金属的实施例中采用所述可选的镀敷籽层，并且使用镀敷来形成包含金属的应力源材料。可选的镀敷籽层用来选择性地促进预先选择的包含金属的应力源材料的随后镀敷。可选的镀敷籽层可以包括例如单层Ni或诸如Al(底部)/Ti/Ni(顶部)的两种或更多种金属的层叠结构。

[0047] 该可选的镀敷籽层的厚度可以根据该可选的镀敷籽层的(一种或多种)材料以及形成其所使用的技术而变化。典型地，该可选的镀敷籽层的厚度为2nm到400nm。所述可选的镀敷籽层可以通过常规沉积工艺形成，所述沉积工艺包括例如：化学气相沉积(CVD)、等离子体增强化学气相沉积(PECVD)、原子层沉积(ALD)、以及可以包括蒸镀和/或溅射的物理气相沉积(PVD)技术。

[0048] 根据本公开，表面保护层18以及可选的镀敷籽层(如果采用)在不导致在单晶半导体衬底10内发生自发剥落的温度下形成。“自发”的意思是发生薄材料层从单晶半导体衬底10的去除而无需采用任何人工手段来引发用于使薄材料层从单晶半导体衬底10断开的裂纹形成和传播。“人工”的意思是裂纹形成和传播明显用于使薄材料层从单晶半导体衬底10断开。

[0049] 本公开中采用的应力源层20包括当在剥落温度下位于单晶半导体衬底10顶上时受到张应力的任何材料。因此，应力源材料在此处也可以称为应力引发材料。根据本公开，应力源层20具有导致在单晶半导体衬底10内发生剥落型断裂的临界厚度和应力值。“剥落型断裂”是指裂纹形成在单晶半导体衬底10内并且负荷力的组合将裂纹轨迹保持在应力源/衬底界面下方的深度。“临界条件”的意思是对于给定的应力源材料和单晶半导体衬底

材料组合,应力源层20的厚度值和应力源值被选择为使得剥落型断裂是可能的(能够产生大于衬底的K<sub>IC</sub>的K<sub>I</sub>值)。

[0050] 应力源层20的厚度被选择为在单晶半导体衬底10内提供期望的(一个或多个)断裂深度。例如,如果将应力源层20选择为Ni,则断裂将在应力源层20下方约2到3倍的Ni厚度的深度处发生。应力源层20的应力值被选择为满足剥落型断裂的临界条件。这可以通过转化由 $t^* = [(2.5 \times 10^6)(K_{IC}^{3/2})]/\sigma^2$ 给出的经验方程估计,其中 $t^*$ 是临界应力源层厚度(以微米为单位),K<sub>IC</sub>是单晶半导体衬底10的断裂韧度(以MPa·m<sup>1/2</sup>为单位),并且 $\sigma$ 是应力源层20的应力值(以Mpa或兆帕斯卡为单位)。上述表达式是指导,在实践中,能够在比由上述表达式预测的值小了至多20%的应力或厚度值下发生剥落。

[0051] 当在单晶半导体衬底10上方施加时处于张应力下并且因此可以用作应力源层20的材料的示例性例子包括但不限于金属、诸如剥落引发带(tape)层的聚合物或者其任何组合。应力源层20可以包括一种应力源材料,或者可以采用包括至少两层不同的应力源材料的多层应力源结构。

[0052] 在一个实施例中,应力源层20是金属。在另一个实施例中,应力源层20是剥落引发带。在又一个实施例中,应力源层20可以包括具有下部和上部两部分(two-part)应力源层。所述两部分应力源层的上部可以由剥落引发带层构成。

[0053] 当采用金属作为应力源层20时,所述金属可以包括例如Ni、Cr、Fe或W。也可以采用这些金属的合金。在一个实施例中,应力源层20包括由Ni构成的至少一个层。

[0054] 当采用聚合物作为应力源层20时,所述聚合物是由重复结构单元构成的大的高分子。这些子单元典型地通过共价化学键连接。能够用作应力源层的聚合物的示例性例子包括但不限于聚酰亚胺、聚酯、聚烯烃、聚丙烯酸酯、聚氨酯、聚乙酸乙烯酯以及聚氯乙烯。

[0055] 当将剥落引发带层用作应力源层20时,剥落引发带层包括任何在用于形成该带的第一温度下为柔性的、软的并且无应力、但是在剥落期间使用的第二温度下为牢固的、易延展的并且可伸长的压敏带。“压敏带”是指在施加压力的情况下将有粘性而不需要用于活化的溶剂、热或水的粘合带。在第二温度下所述带中的张应力主要是由于单晶半导体衬底10(具有较低的热膨胀系数)与所述带(具有较高的热膨胀系数)之间的热膨胀失配引起的。

[0056] 典型地,在本公开中用作应力源层20的压敏带至少包括粘着层和基体层。用于该压敏带的粘着层和基体层的材料包括具有或没有合适的增塑剂的诸如例如丙烯酸脂类、聚酯、烯烃和乙烯树脂(vinyl)的聚合物材料。增塑剂是能够增加它们所添加到的聚合物材料的塑性的添加剂。

[0057] 应力源层20能够利用任何公知的沉积工艺形成。通常,通过浸渍涂布、旋涂、刷涂、溅射、化学气相沉积、等离子体增强化学气相沉积、化学溶液沉积、物理气相沉积和镀敷中的任何一种完成沉积以形成包括金属或聚合物作为应力源材料的应力源层20。在一些实施例中,当应力源层20是带时,可以用手或用机械装置施加应力源层20。

[0058] 应力源层20可以在处于室温(15°C-40°C)的第一温度下形成。在另一个实施例中,当采用了带层时,带层可以在从15°C到60°C的第一温度下形成。

[0059] 如果应力源层20具有金属性质,则其典型地具有从3μm到50μm的范围内的厚度,其中4μm到7μm的范围内的厚度是更典型的。在本公开中也可以采用在上述厚度范围以下和/或以上的应力源层20的其它厚度。

[0060] 如果应力源层20具有聚合物性质,则其典型地具有从10μm到200μm的范围内的厚度,其中50μm到100μm的范围内的厚度是更典型的。在本公开中也可以采用在上述厚度范围以下和/或以上的应力源层20的其它厚度。

[0061] 参考图3,示例了在应力源层20上方形成处理衬底22之后并且在剥落之后的图2的结构。在本公开的一些实施例中,可以省略处理衬底22。因此,处理衬底是本公开的可选部件。本公开中采用的处理衬底22包括任何具有典型地小于30cm的最小曲率半径的柔性材料。能够用作处理衬底22的柔性材料的示例性例子包括金属箔或聚酰亚胺箔。

[0062] 处理衬底22可以用于在处理剥落部分——即,在应力源层20下方且在单晶半导体衬底10的断裂表面上方的单晶半导体衬底10的部分——时提供更好的断裂控制和更多通用性。此外,处理衬底22可用于在剥落期间引导裂纹传播。本公开的处理衬底22典型地但不必需地在处于室温(15°C-40°C)的第一温度下形成。

[0063] 处理衬底22可以利用本领域技术人员公知的沉积技术形成,所述沉积技术包括例如浸渍涂布、旋涂、刷涂、溅射、化学气相沉积、等离子体增强化学气相沉积、化学溶液沉积、物理气相沉积和镀敷。在一些实施例中,处理衬底22可以手动地或通过机械装置而被施加在应力源层20顶部。

[0064] 处理衬底22典型地具有从1μm到数mm的厚度,其中70μm到120μm的厚度是更典型的。在本公开中也可以采用在上述厚度范围以下和/或以上的处理衬底22的其它厚度。

[0065] 可以在室温下或者在低于室温的温度下开始剥落。在一个实施例中,在室温(即,20°C到40°C)下进行剥落。在另一个实施例中,在低于20°C的温度下进行剥落。在又一个实施例中,剥落发生在77K或更低的温度。在再一个实施例中,剥落发生在低于206K的温度。在又一个实施例中,剥落发生在175K到130K的温度。

[0066] 当使用低于室温的温度时,可以通过利用任何冷却装置将所述结构冷却下降至室温以下来实现低于室温的剥落工艺。例如,可以通过将所述结构放置在液氮浴、液氦浴、冰浴、干冰浴、超临界流体浴或任何低温环境液体或气体中实现冷却。

[0067] 当在低于室温的温度下进行剥落时,通过允许剥落的结构处于室温下而允许剥落的结构缓慢温暖至室温,使剥落的结构返回到室温。或者,可以利用任何加热装置将剥落的结构加热到室温。

[0068] 如图3所示,剥落将单晶半导体衬底10的不包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的部分从单晶半导体衬底10的包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的另一部分去除。在图中,元件10A指单晶半导体衬底10的不包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的部分,而元件10B是指单晶半导体衬底10的包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的部分。

[0069] 此处也将元件10B称为剥落的单晶半导体层(或简言之,剥落层),而元件10A在此处可以称为非剥落层。如图所示,包含单晶半导体衬底10的包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的部分的剥落层10B仍然包含表面保护层18、应力源层20和处理衬底22。

[0070] 在本公开的一个实施例中,剥落层10B具有小于100微米的厚度。在本公开的另一个实施例中,剥落层10B具有小于50微米的厚度。在本公开的又一个实施例中,剥落层10B具有25微米到40微米的厚度。

[0071] 现在参考图4,示例了在剥落层10B的与包含OLED驱动电路12、逻辑和存储器件14以及其它功能器件15的表面相反的最底部表面上形成衬底24之后的图3的结构。衬底24可以是刚性的或柔性的,并且可以包括例如半导体材料、玻璃、陶瓷、带或塑料。典型地,衬底24由玻璃或塑料构成。衬底24可以通过接合而被形成在剥落层10B的最底部表面上。可以在室温直到约300°C的温度下实现接合。

[0072] 可以在存在或不存在表面保护层18、应力源层20和处理衬底22的条件下将衬底24施加到剥落层10B。在图4所示例的实施例中,在存在表面保护层18、应力源层20和处理衬底22的条件下,将衬底24形成在剥落层10B上。

[0073] 参考图5,示例了在从剥落层10B去除处理衬底22、应力源层20和表面保护层18之后的图4的结构。可以利用本领域技术人员公知的常规技术从剥落层10B去除处理衬底22、应力源层20和表面保护层18。

[0074] 例如,在一个实施例中,可以使用王水(HNO<sub>3</sub>/HCl)来去除处理衬底22、应力源层20、可选的镀敷籽层和表面保护层18。在另一个实施例中,可以使用UV或热处理来去除处理衬底22,之后通过化学蚀刻来去除应力源层20,之后通过不同的化学蚀刻来去除可选的镀敷籽层和表面保护层18。

[0075] 现在参考图6,示例了图5所示的结构,示出了沿着进入以及伸出纸的平面的圈出区域中的OLED驱动电路。具体地,图6示出了包括衬底24、剥落层10B和OLED驱动电路12的阵列(即,存在于剥落层10B内和上的TFT)的结构。

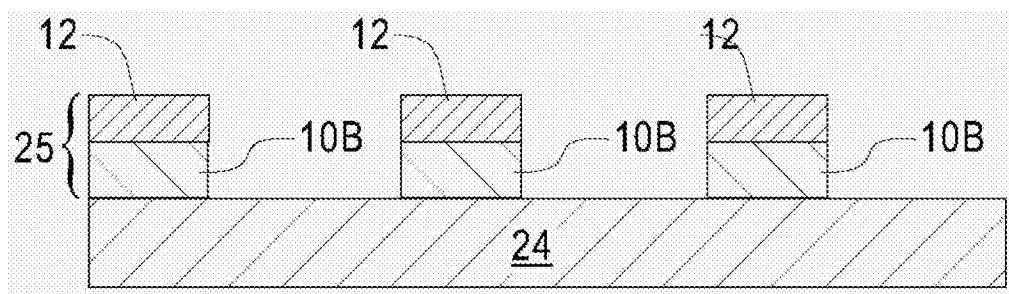

[0076] 现在参考图7A,示例了根据其中提供底部发射的OLED显示器的本公开的实施例、在蚀刻位于相邻薄膜晶体管之间的剥落层10B的暴露部分之后的图6所示的结构。利用相对于OLED驱动电路选择性地蚀刻半导体材料的选择性蚀刻工艺,进行对剥落的单晶半导体层10B的暴露部分的蚀刻,该蚀刻在衬底24的最上表面的顶上停止。该蚀刻提供了从顶部到底部包括OLED驱动电路12以及剥落的单晶半导体层10B的剩余部分的材料叠层25。

[0077] 在本公开的一个实施例中,选择性蚀刻工艺可以包括蚀刻掩膜(通常是氧化物层)的沉积以及利用诸如例如四甲基氢氧化铵(TMAH)或KOH蚀刻的湿法化学蚀刻、或包括例如氟基化学物质的干法蚀刻进行的硅蚀刻。可以在剥落层10B的其它部分上形成阻挡掩膜(未示出),以便保护包括逻辑和存储器件14及其它功能器件15的区域。

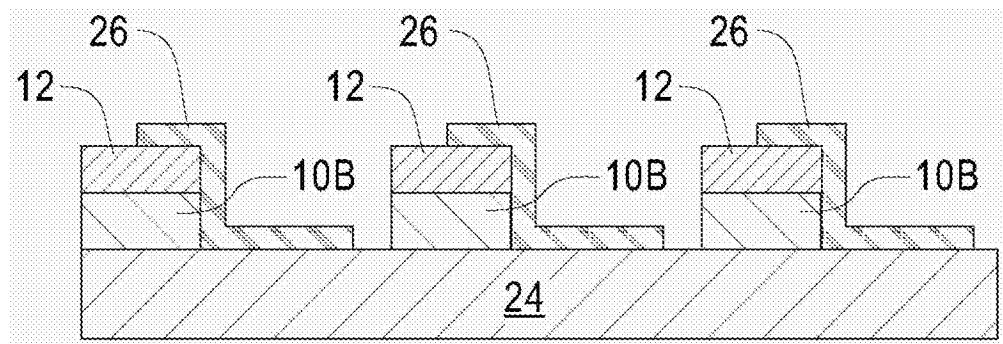

[0078] 现在参考图7B,示例了在形成底部透明电极26之后的图7A的结构。底部透明电极26形成在材料叠层25的最上表面上以及位于相邻材料叠层25之间的衬底24的暴露的最上表面上。底部透明电极可以包括透明导电氧化物,所述透明导电氧化物例如是但不限于掺氟的锡氧化物(SnO<sub>2</sub>:F)、掺铝的锌氧化物(ZnO:Al)、锡氧化物(SnO)和铟锡氧化物(InSnO<sub>2</sub>或简言之,ITO)。也可以使用这种透明导电氧化物的多层叠层作为底部电极26。

[0079] 底部透明电极26的厚度可以根据所采用的透明导电材料的类型及用于形成透明导电材料的技术而改变。典型地,并且在一个实施例中,底部透明电极26的厚度在从20nm到500nm的范围内。也可以采用其它厚度,包括小于20nm和/或大于500nm的厚度。用于最小化从Si的表面的反射的底部透明电极26的最佳厚度在70nm到110nm的范围内。

[0080] 底部透明电极26典型地使用诸如溅射或CVD的沉积工艺形成。适用于形成底部透明电极材料的CVD工艺的例子包括但不限于APCVD、LPCVD、PECVD、MOCVD及其组合。溅射的例子包括但不限于RF和DC磁控溅射。在一些实施例中,可以在底部透明电极材料的沉积之后

进行构图工艺。

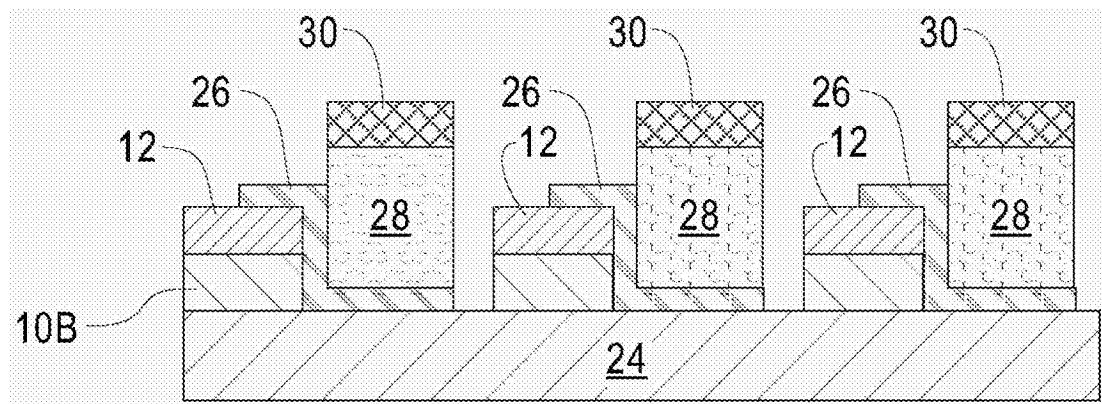

[0081] 现在参考图7C,示例了在形成有机电致发光材料28和顶部电极30之后的图7B的结构。如图所示,有机电致发光材料28和顶部电极30位于底部透明电极26的位于衬底24的暴露表面上的部分上方。

[0082] 在本公开中采用的有机电致发光材料28包括响应于电流而发射光的任何有机材料或有机材料的多层叠层,所述有机材料包括例如有机金属螯合物、导电聚合物、荧光染料、磷光染料以及共轭树枝状大分子(*conjugated dendrimer*)。可以用作有机电致发光材料28的有机材料的例子包括但不限于聚对苯乙炔(PPV)、聚萘乙炔(PNV)、三(2-苯基吡啶)铱(Ir(ppy)<sub>3</sub>)以及三(8-羟基喹啉)铝(Alq<sub>3</sub>)。

[0083] 有机电致发光材料28可以通过常规技术形成,所述常规技术包括例如旋涂、浸渍涂布、浸没以及化学气相沉积。典型地,并且在一个实施例中,有机电致发光材料28的厚度在从数nm到数百nm的范围内。也可以采用包括前述范围以上和/或以下厚度的其它厚度。

[0084] 在一些实施例中,顶部电池30可以包括具有低于底部透明电极26的功函数的材料或材料的多层叠层。例如,顶部电极30可以由铝(Al)、钙(Ca)和/或镁(Mg)构成。在另一个实施例中,顶部电极30可以包括上面提及的透明导电氧化物之一。顶部电极30可以利用任何沉积工艺形成,所述沉积工艺包括例如通过遮蔽掩模的溅射和热蒸镀。典型地,并且在一个实施例中,顶部电极30的厚度在从20nm到100nm的范围内。也可以采用包括前述范围以上和/或以下厚度的其它厚度。

[0085] 在本公开的该实施例的底部发射OLED显示器件中,有机电致发光材料28和顶部电极30可以具有垂直地彼此一致的侧壁表面。

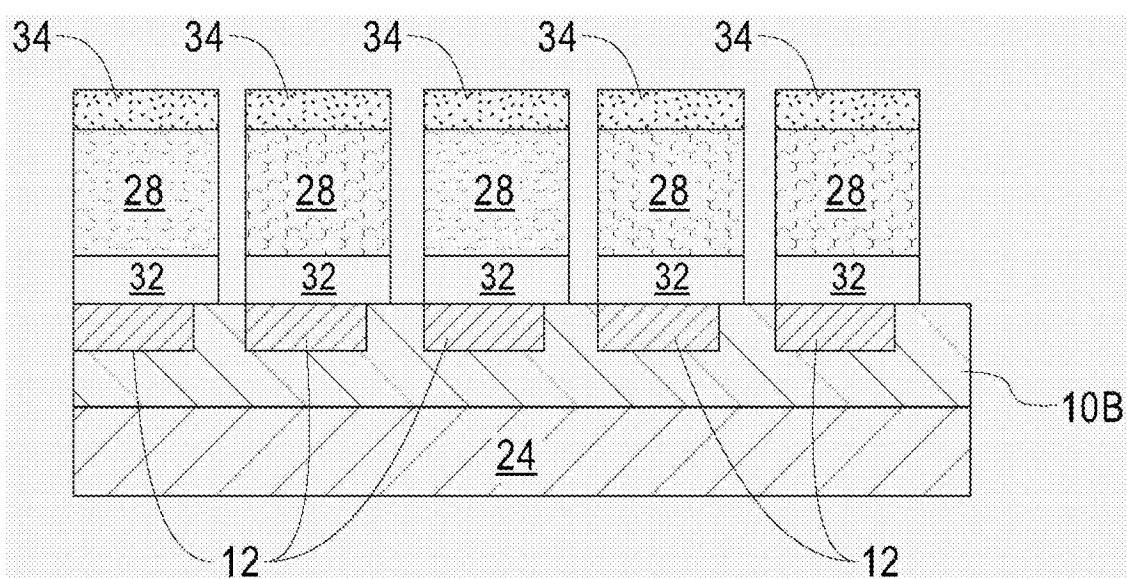

[0086] 现在参考图8,图8是根据其中提供具有顶部发射的OLED显示器的本公开的实施例、在沉积底部电极32、有机电致发光材料28和顶部透明电极34之后的图6所示例的结构的表示。在本公开的该实施例中,底部电极32包括以上提及的用于顶部电极30的材料之一,而顶部透明电极34包括以上提及的用于底部透明电极26的材料之一。在本公开的底部发射实施例中,可以如上所述地形成底部电极32、有机电致发光材料28和顶部透明电极34。

[0087] 在本公开的该实施例的顶部发射OLED显示器件中,底部电极32、有机电致发光材料28和顶部透明电极24可以具有垂直地彼此一致的侧壁表面。

[0088] 现在参考图9,示例了根据本公开的第二方法实施例的单晶半导体衬底10,该单晶半导体衬底10包括在其上制造的CMOS逻辑和存储器件14。特别地,该实施例利用类似于图1所示例的结构,但OLED驱动电路12和其它功能器件还未形成于单晶半导体衬底10中。

[0089] 现在参考图10,示例了在单晶半导体衬底10的暴露表面上形成表面保护层18之后以及在所述表面保护层18上方形成应力源层20之后的图9的结构。表面保护层18和应力源层20与如上所述形成图2所示结构时的表面保护层18和应力源层20相同。

[0090] 现在参考图11,示例了在应力源层20上方形成处理衬底22之后并且在剥落之后的图10的结构。在一些实施例中,可以省略处理衬底22。处理衬底22及其形成装置与如上所述形成图3所示结构时的相同。在本公开的该实施例中使用的剥落工艺与在本公开的前述实施例中提及的剥落工艺相同。在该实施例中,剥落层10B仅包括位于其上的CMOS逻辑和存储器件14。

[0091] 现在参考图12,示例了在剥落层10B的最底部表面上形成衬底24之后的图11的结

构。在该实施例中使用的衬底24包括在形成图4所示的结构时在上文中提及的衬底之一。同样,上文中提及的接合技术可以在此处用于形成图12所示的结构。

[0092] 现在参考图13,示例了在从剥落层10B去除处理衬底22、应力源层20和表面保护层18之后的图12的结构。处理衬底22、应力源层20和表面保护层18的去除包括在形成图5所示结构时在上文中提及的技术之一。在一些实施例中,可以在将衬底24形成在剥落的单晶半导体衬底10B的最底部表面上之前去除处理衬底22、应力源层20和表面保护层18。

[0093] 现在参考图14,示例了在形成可选的其它功能器件15之后并且在形成OLED驱动电路12之后图13的结构。可选的其它功能器件15和OLED器件电路12与上文中结合本公开的图1描述的相同。

[0094] 在提供图14所示的结构之后,可以使用图7A-7C中使用的工艺来提供具有底部发射的OLED显示器,或者使用图8中的工艺来形成具有顶部发射的OLED显示器。

[0095] 不管使用上述实施例中的哪一个或者不管提供具有底部发射还是顶部发射的OLED显示器,本公开的方法都提供诸如例如图15中所示的半导体结构,该半导体结构包括集成在同一单晶半导体层(即剥落层10B)上的OLED显示器100、CMOS逻辑和存储器件102、以及其他功能器件104。OLED驱动电路位于OLED显示器100下方。OLED显示器可以包括多个顶部发射OLED器件或者多个底部发射OLED器件。

[0096] 尽管关于本公开的优选实施例特别示出和描述了本公开,但是本领域技术人员将理解,在不脱离本公开的精神和范围的情况下,可以做出前述和其它形式和细节上的变化。因此,本公开旨在不限于所描述和示例的确切形式和细节,而是落入所附权利要求的范围内。

图1

图2

图3

图4

图5

图6

图7A

图7B

图7C

图8

图9

图10

图11

图12

图13

图14

图15

|                |                                                    |         |            |

|----------------|----------------------------------------------------|---------|------------|

| 专利名称(译)        | 形成包括具有半导体驱动电路的OLED显示器的结构的方法和半导体结构                  |         |            |

| 公开(公告)号        | <a href="#">CN103682175B</a>                       | 公开(公告)日 | 2016-09-07 |

| 申请号            | CN201310435444.3                                   | 申请日     | 2013-09-23 |

| [标]申请(专利权)人(译) | 国际商业机器公司                                           |         |            |

| 申请(专利权)人(译)    | 国际商业机器公司                                           |         |            |

| 当前申请(专利权)人(译)  | 国际商业机器公司                                           |         |            |

| [标]发明人         | 李宁<br>DK萨达那                                        |         |            |

| 发明人            | 李宁<br>D·K·萨达那                                      |         |            |

| IPC分类号         | H01L51/56 H01L27/32 G09G3/3241 H01L27/12           |         |            |

| CPC分类号         | G09G3/3208 H01L27/3244 H01L2227/323 H01L2227/326   |         |            |

| 代理人(译)         | 贺月娇<br>于静                                          |         |            |

| 审查员(译)         | 苏治平                                                |         |            |

| 优先权            | 13/625301 2012-09-24 US<br>13/658473 2012-10-23 US |         |            |

| 其他公开文献         | CN103682175A                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>     |         |            |

#### 摘要(译)

本发明涉及形成包括具有半导体驱动电路的OLED显示器的结构的方法和半导体结构。采用剥落来产生单晶半导体层。在剥落之前在单晶半导体衬底上形成互补金属氧化物半导体 ( CMOS ) 逻辑和存储器件。可以在剥落之前或之后形成有机发光二极管 ( OLED ) 驱动电路、太阳能电池单体、传感器、电池等。剥落的单晶半导体层可以被转移到衬底。OLED显示器可以形成在剥落的单晶半导体层中，以实现这样的结构：该结构包括集成在所述单晶半导体层上的具有半导体驱动电路的OLED显示器和其它功能器件。