(12)发明专利申请

(10)申请公布号 CN 111063282 A

(43)申请公布日 2020.04.24

(21)申请号 201911177923.3

(22)申请日 2019.11.27

(71)申请人 武汉华星光电半导体显示技术有限公司

地址 430079 湖北省武汉市东湖新技术开发区高新大道666号光谷生物创新园C5栋305室

(72)发明人 张娣

(74)专利代理机构 深圳紫藤知识产权代理有限公司 44570

代理人 杨艇要

(51)Int.Cl.

G09G 3/00(2006.01)

G09G 3/3208(2016.01)

权利要求书2页 说明书5页 附图2页

(54)发明名称

显示面板的测试电路及OLED显示器

(57)摘要

本申请提供了一种显示面板的测试电路，所述测试电路包括：三条输入数据信号线，所述三条输入数据信号线包括R数据信号线、G数据信号线以及B数据信号线；三条控制电压信号线，所述控制电压信号线包括R控制电压信号线、G控制电压信号线以及B控制电压信号线；多个测试单元，每一所述测试单元包括六个选通模块，所述六个选通模块的输出端与所述像素结构的6列子像素分别连接，其中，每一所述选通模块的输出端与一列子像素中的各个子像素分别连接；每一所述选通模块的输入端分别对应列的子像素所对应的一条数据信号线或两条数据信号线连接；每一所述选通模块的控制端分别对应列的子像素所对应的一条控制电压信号线或两条控制电压信号线连接。

1. 一种显示面板的测试电路，所述显示面板包括多个阵列排布的像素结构，每一所述像素结构包括四个呈矩形阵列排布的像素单元，每一所述像素单元包括一R子像素、G子像素以及B子像素，其中每一列子像素包括两种子像素或一种子像素；其特征在于，所述测试电路包括：

三条输入数据信号线，所述三条输入数据信号线包括R数据信号线、G数据信号线以及B数据信号线；

三条控制电压信号线，所述控制电压信号线包括R控制电压信号线、G控制电压信号线以及B控制电压信号线；

多个测试单元，每一所述测试单元包括六个选通模块，所述六个选通模块的输出端与所述像素结构的6列子像素分别连接，其中，每一所述选通模块的输出端与一列子像素中的各个子像素分别连接；每一所述选通模块的输入端分别对应列的子像素所对应的一条数据信号线或两条数据信号线连接；每一所述选通模块的控制端分别对应列的子像素所对应的一条控制电压信号线或两条控制电压信号线连接。

2. 根据权利要求1所述的显示面板的测试电路，其特征在于，所述六个选通模块包括：

第一选通模块，其包括第一开关管以及第二开关管，所述第一开关管的输出端与所述第二开关管的输出端连接且与一列像素结构中的第一列子像素连接，所述第一开关管输入端与所述G数据信号线连接，所述第二开关管的输入端与所述B数据信号线连接，所述第一开关管的控制端与所述G控制电压信号线连接，所述第二开关管的控制端与所述B控制电压信号线连接；

第二选通模块，其包括第三开关管，所述第三开关管的输入端与所述G数据信号线连接，所述第三开关管的输出端与一列像素结构中的第二列子像素连接。

3. 根据权利要求2所述的显示面板的测试电路，其特征在于，所述六个选通模块还包括：

第三选通模块，其包括第四开关管以及第五开关管，所述第四开关管的输出端与所述第五开关管的输出端连接且与一列像素结构中的第三列子像素连接，所述第四开关管输入端与所述B数据信号线连接，所述第五开关管的输入端与所述R数据信号线连接，所述第四开关管的控制端与所述B控制电压信号线连接，所述第五开关管的控制端与所述R控制电压信号线连接；

第四选通模块，其包括第六开关管以及第七开关管，所述第六开关管的输出端与所述第七开关管的输出端连接且与一列像素结构中的第四列子像素连接，所述第六开关管输入端与所述B数据信号线连接，所述第七开关管的输入端与所述R数据信号线连接，所述第六开关管的控制端与所述B控制电压信号线连接，所述第七开关管的控制端与所述R控制电压信号线连接。

4. 根据权利要求3所述的显示面板的测试电路，其特征在于，所述六个选通模块还包括：

第五选通模块，其包括第八开关管，所述第八开关管的输入端与所述G数据信号线连接，所述第八开关管的输出端与一列像素结构中的第五列子像素连接；

第六选通模块，其包括第九开关管以及第十开关管，所述第九开关管的输出端与所述第十开关管的输出端连接且与一列像素结构中的第六列子像素连接，所述第九开关管输入

端与所述B数据信号线连接,所述第十开关管的输入端与所述R数据信号线连接,所述第九开关管的控制端与所述B控制电压信号线连接,所述第十开关管的控制端与所述R控制电压信号线连接。

5.根据权利要求4所述的显示面板的测试电路,其特征在于,所述G控制电压信号线传输的电压为低电平信号,使得所述第二选通模块以及所述第五选通模块处于导通状态。

6.根据权利要求4所述的显示面板的测试电路,其特征在于,与同一所述R控制电压信号线或同一所述B控制电压信号线连接的开关管的导通状态相同,所述R控制电压信号线连接的开关管的导通状态与所述B控制电压信号线连接的开关管的导通状态相反。

7.根据权利要求4所述的显示面板的测试电路,其特征在于,所述第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为场效应薄膜晶体管。

8.根据权利要求7所述的显示面板的测试电路,其特征在于,所述第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为P型场效应薄膜晶体管。

9.根据权利要求1所述的显示面板的测试电路,其特征在于,所述显示面板为OLED显示面板。

10.一种OLED显示器,其特征在于,包括权利要求1-9任一项所述的显示面板的测试电路。

## 显示面板的测试电路及OLED显示器

### 技术领域

[0001] 本申请涉及显示技术领域,具体涉及一种显示面板的测试电路及OLED 显示器。

### 背景技术

[0002] OLED色域广、对比度高、节能、可折叠性,在新世代显示器中具有强的竞争。AMOLED技术是柔性显示重点发展方向之一。目前OLED发光区设计分为:Real RGB\伪像素设计。伪像素设计适用于高像素密度的显示屏,通常应用于手机面板设计。伪像素设计通常应用于Pad等大屏设计,对像素密度要求略低。伪像素设计设计显示效果更佳,然而发光器件排布致密,FMM 张网存在较高要求。因此,现有技术具有缺陷,急需改进。

### 发明内容

[0003] 本申请的目的是提供一种显示面板的测试电路及OLED显示器,具有实现对新型的显示面板进行点亮测试的效果,可以提高产品合格率。

[0004] 本申请提供了一种显示面板的测试电路,所述显示面板包括多个阵列排布的像素结构,每一所述像素结构包括四个呈矩形阵列排布的像素单元,每一所述像素单元包括一R子像素、G子像素以及B子像素,其中每一列子像素包括两种子像素或一种子像素;所述测试电路包括:

[0005] 三条输入数据信号线,所述三条输入数据信号线包括R数据信号线、G 数据信号线以及B数据信号线;

[0006] 三条控制电压信号线,所述控制电压信号线包括R控制电压信号线、G 控制电压信号线以及B控制电压信号线;

[0007] 多个测试单元,每一所述测试单元包括六个选通模块,所述六个选通模块的输出端与所述像素结构的6列子像素分别连接,其中,每一所述选通模块的输出端与一列子像素中的各个子像素分别连接;每一所述选通模块的输入端分别对应列的子像素所对应的一条数据信号线或两条数据信号线连接;每一所述选通模块的控制端分别对应列的子像素所对应的一条控制电压信号线或两条控制电压信号线连接。

[0008] 在本申请所述的显示面板的测试电路中,所述六个选通模块包括:

[0009] 第一选通模块,其包括第一开关管以及第二开关管,所述第一开关管的输出端与所述第二开关管的输出端连接且与一列像素结构中的第一列子像素连接,所述第一开关管输入端与所述G数据信号线连接,所述第二开关管的输入端与所述B数据信号线连接,所述第一开关管的控制端与所述G控制电压信号线连接,所述第二开关管的控制端与所述B控制电压信号线连接;

[0010] 第二选通模块,其包括第三开关管,所述第三开关管的输入端与所述G 数据信号线连接,所述第三开关管的输出端与一列像素结构中的第二列子像素连接。

[0011] 在本申请所述的显示面板的测试电路中,所述六个选通模块还包括:

[0012] 第三选通模块,其包括第四开关管以及第五开关管,所述第四开关管的输出端与

所述第五开关管的输出端连接且与一列像素结构中的第三列子像素连接,所述第四开关管输入端与所述B数据信号线连接,所述第五开关管的输入端与所述R数据信号线连接,所述第四开关管的控制端与所述B控制电压信号线连接,所述第五开关管的控制端与所述R控制电压信号线连接;

[0013] 第四选通模块,其包括第六开关管以及第七开关管,所述第六开关管的输出端与所述第七开关管的输出端连接且与一列像素结构中的第四列子像素连接,所述第六开关管输入端与所述B数据信号线连接,所述第七开关管的输入端与所述R数据信号线连接,所述第六开关管的控制端与所述B控制电压信号线连接,所述第七开关管的控制端与所述R控制电压信号线连接。

[0014] 在本申请所述的显示面板的测试电路中,所述六个选通模块还包括:

[0015] 第五选通模块,其包括第八开关管,所述第八开关管的输入端与所述G 数据信号线连接,所述第八开关管的输出端与一列像素结构中的第五列子像素连接;

[0016] 第六选通模块,其包括第九开关管以及第十开关管,所述第九开关管的输出端与所述第十开关管的输出端连接且与一列像素结构中的第六列子像素连接,所述第九开关管输入端与所述B数据信号线连接,所述第十开关管的输入端与所述R数据信号线连接,所述第九开关管的控制端与所述B控制电压信号线连接,所述第十开关管的控制端与所述R控制电压信号线连接。

[0017] 在本申请所述的显示面板的测试电路中,所述G控制电压信号线传输的电压为低电平信号,使得所述第二选通模块以及所述第五选通模块处于导通状态。

[0018] 在本申请所述的显示面板的测试电路中,与同一所述R控制电压信号线或同一所述B控制电压信号线连接的开关管的导通状态相同,所述R控制电压信号线连接的开关管的导通状态与所述B控制电压信号线连接的开关管的导通状态相反。

[0019] 在本申请所述的显示面板的测试电路中,所述第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为场效应薄膜晶体管。

[0020] 在本申请所述的显示面板的测试电路中,所述第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为P型场效应薄膜晶体管。

[0021] 在本申请所述的显示面板的测试电路中,所述显示面板为OLED显示面板。

[0022] 一种OLED显示器,包括上述任一项所述的显示面板的测试电路。

[0023] 本申请通过采用新型的测试电路,通过设置多个选通模块,从而实现对新型的显示面板进行点亮测试的效果,可以提高产品合格率。

## 附图说明

[0024] 为了更清楚地说明本申请中的技术方案,下面将对实施方式描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施方式,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

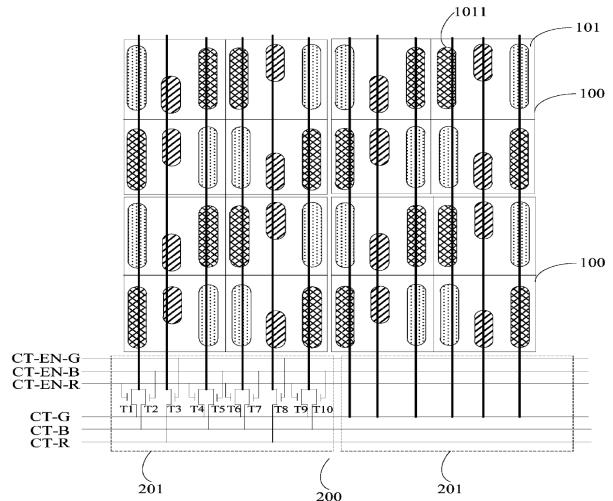

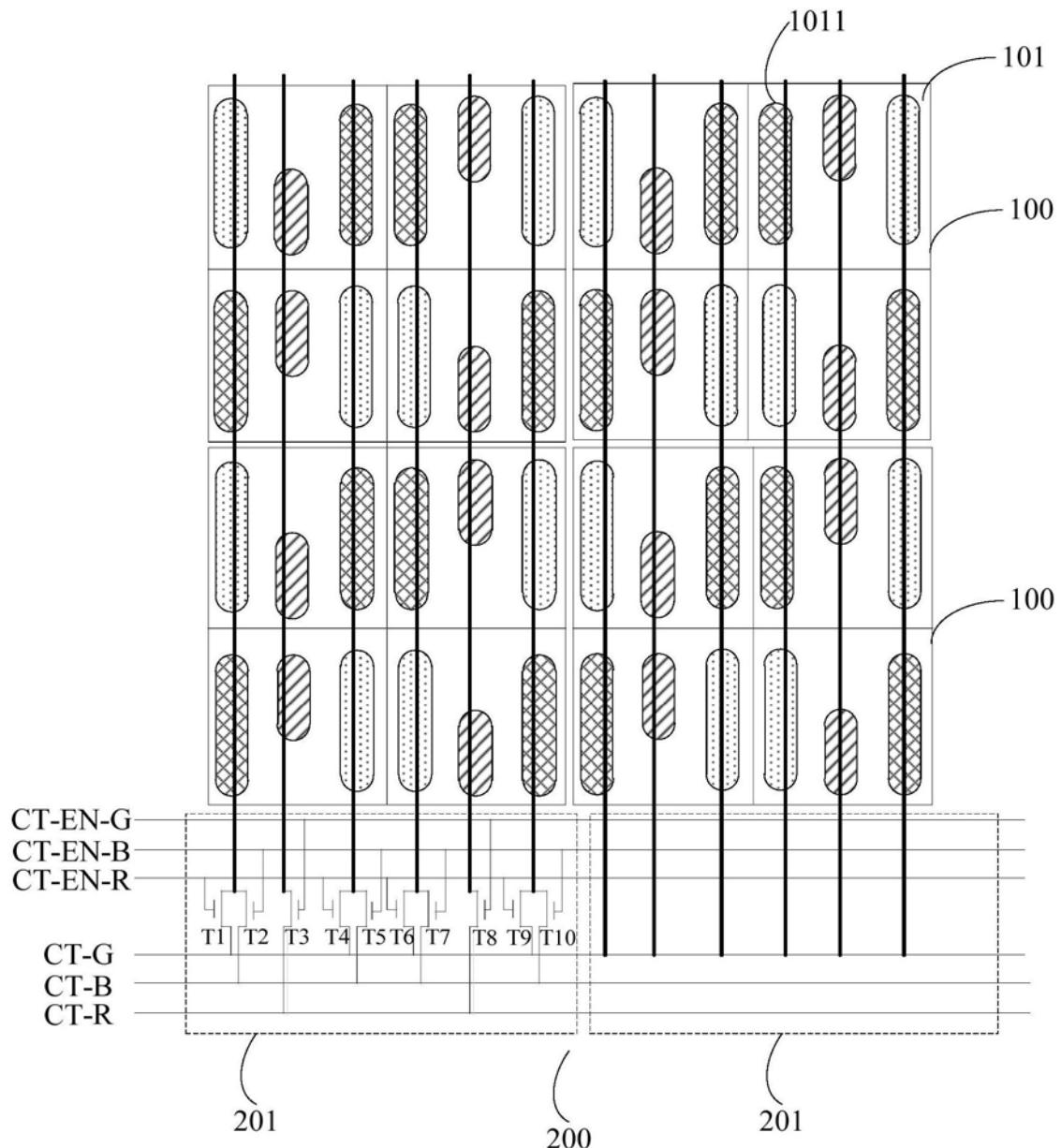

[0025] 图1为本申请一些实施例中的显示面板的测试电路的结构示意图。

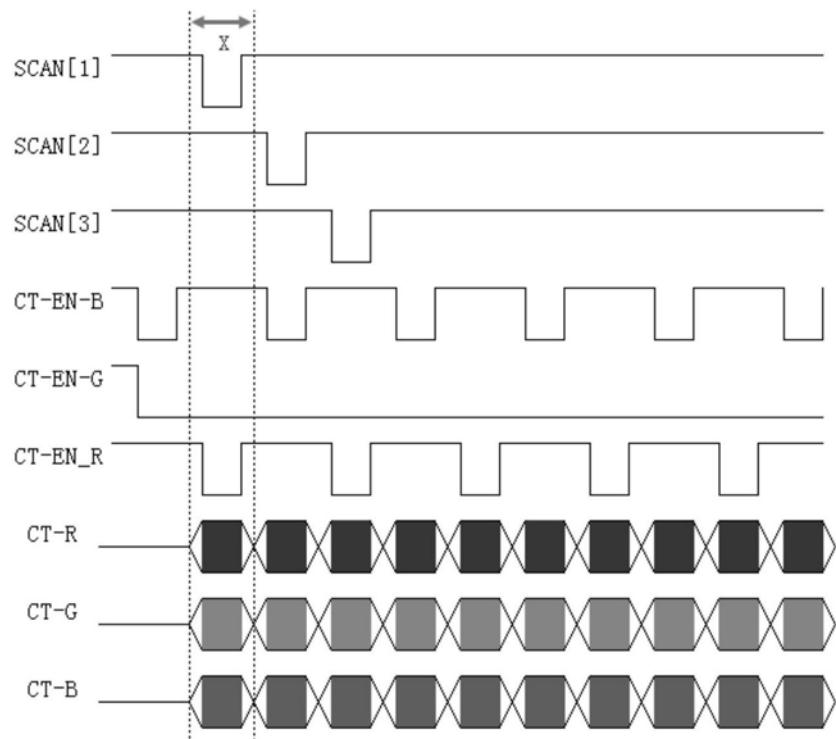

[0026] 图2为本申请一些实施例中的显示面板的测试电路的第一种时序图。

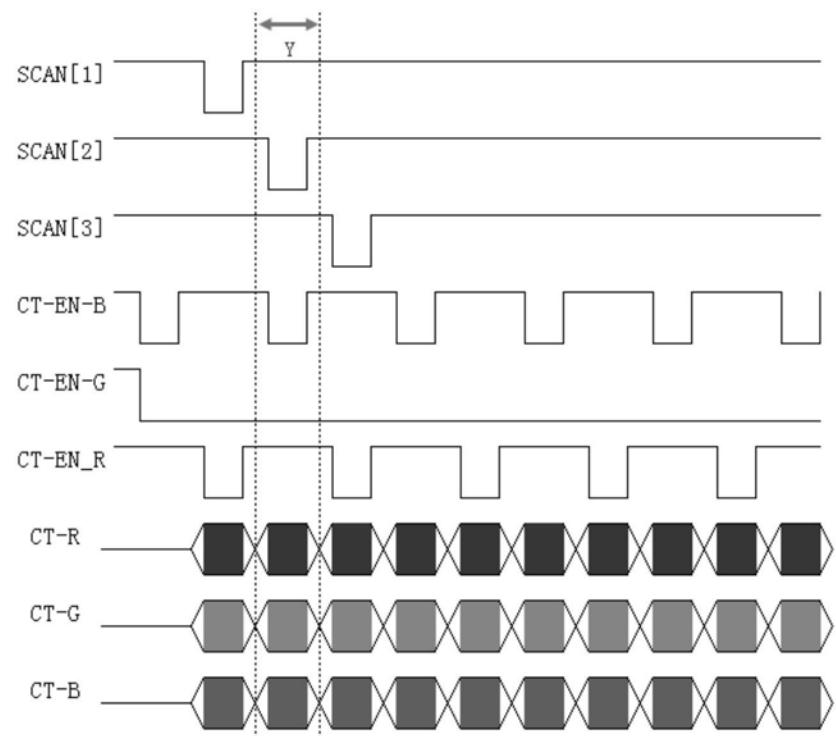

[0027] 图3为本申请一些实施例中的显示面板的测试电路的第二种时序图。

### 具体实施方式

[0028] 这里所公开的具体结构和功能细节仅仅是代表性的，并且是用于描述本申请的示例性实施例的目的。但是本申请可以通过许多替换形式来具体实现，并且不应当被解释成仅仅受限于这里所阐述的实施例。

[0029] 在本申请的描述中，需要理解的是，术语“中心”、“横向”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系，仅是为了便于描述本申请和简化描述，而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作，因此不能理解为对本申请的限制。此外，术语“第一”、“第二”仅用于描述目的，而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此，限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本申请的描述中，除非另有说明，“多个”的含义是两个或两个以上。另外，术语“包括”及其任何变形，意图在于覆盖不排他的包含。

[0030] 在本申请的描述中，需要说明的是，除非另有明确的规定和限定，术语“安装”、“相连”、“连接”应做广义理解，例如，可以是固定连接，也可以是可拆卸连接，或一体地连接；可以是机械连接，也可以是电连接；可以是直接相连，也可以通过中间媒介间接相连，可以是两个元件内部的连通。对于本领域的普通技术人员而言，可以具体情况理解上述术语在本申请中的具体含义。

[0031] 这里所使用的术语仅仅是为了描述具体实施例而不意图限制示例性实施例。除非上下文明确地另有所指，否则这里所使用的单数形式“一个”、“一项”还意图包括复数。还应当理解的是，这里所使用的术语“包括”和/或“包含”规定所陈述的特征、整数、步骤、操作、单元和/或组件的存在，而不排除存在或添加一个或更多其他特征、整数、步骤、操作、单元、组件和/或其组合。

[0032] 请参照图1，图1是本申请一些实施例中的一种显示面板的测试电路的结构示意图。该显示面板的测试电路用于显示面板的点亮测试。

[0033] 该显示面板包括多个阵列排布的像素结构100，每一所述像素结构100包括四个呈矩形阵列排布的像素单元101，每一所述像素单元101包括一R子像素、G子像素以及B子像素这三个子像素1011，其中每一列子像素1011包括两种子像素1011或一种子像素1011。

[0034] 具体地，该测试电路200包括：三条输入数据信号线CT-R\CT-G\CT-B、三条控制电压信号线CT-EN-R\CT-EN-G\CT-EN-B以及多个测试单元201。

[0035] 其中，该三条输入数据信号线包括R数据信号线CT-R、G数据信号线CT-G 以及B数据信号线CT-B。控制电压信号线包括R控制电压信号线CT-EN-R、G控制电压信号线CT-EN-G 以及B控制电压信号线CT-EN-B。

[0036] 其中，该每一所述测试单元201包括六个选通模块，所述六个选通模块的输出端与所述像素结构100的6列子像素1011分别连接，其中，每一所述选通模块的输出端与一列子像素1011中的各个子像素1011分别连接；每一所述选通模块的输入端分别对应列的子像素1011所对应的一条数据信号线或两条数据信号线连接；每一所述选通模块的控制端分别对应列的子像素所对应的一条控制电压信号线或两条控制电压信号线连接。

[0037] 具体地,该六个选通模块包括:第一选通模块、第二选通模块、第三选通模块、第四选通模块、第五选通模块、第六选通模块。

[0038] 其中,该第一选通模块包括第一开关管T1以及第二开关管T2,所述第一开关管T1的输出端与所述第二开关管T2的输出端连接且与一列像素结构100 中的第一列子像素1011连接,所述第一开关管T1输入端与所述G数据信号线CT-R连接,所述第二开关管T2的输入端与所述B数据信号线CT-B连接,所述第一开关管T1的控制端与所述G控制电压信号线CT-G连接,所述第二开关管T2的控制端与所述B控制电压信号线连接。

[0039] 其中,该第二选通模块包括第三开关管T3,所述第三开关管T3的输入端与所述G数据信号线CT-G连接,所述第三开关管T3的输出端与一列像素结构中的第二列子像素1011连接。

[0040] 其中,该第三选通模块包括第四开关管T4以及第五开关管T5,所述第四开关管T4的输出端与所述第五开关管T5的输出端连接且与一列像素结构100 中的第三列子像素1011连接,所述第四开关管T4输入端与所述B数据信号线CT-B连接,所述第五开关管T5的输入端与所述R数据信号线连接,所述第四开关管T4的控制端与所述B控制电压信号线连接,所述第五开关管T5 的控制端与所述R控制电压信号线连接。

[0041] 其中,该包括第六开关管T6以及第七开关管T7,所述第六开关管T6的输出端与所述第七开关管T7的输出端连接且与一列像素结构中的第四列子像素连接,所述第六开关管T6输入端与所述B数据信号线连接,所述第七开关管T7的输入端与所述R数据信号线连接,所述第六开关管T6的控制端与所述B控制电压信号线连接,所述第七开关管T7的控制端与所述R控制电压信号线CT-EN-R连接。

[0042] 其中,该第五选通模块包括第八开关管T8,所述第八开关管T8的输入端与所述G数据信号线连接,所述第八开关管的输出端与一列像素结构中的第五列子像素连接。

[0043] 其中,该第六选通模块包括第九开关管T9以及第十开关管T10,所述第九开关管T9的输出端与所述第十开关管T10的输出端连接且与一列像素结构中的第六列子像素连接,所述第九开关管T9输入端与所述B数据信号线连接,所述第十开关管T10的输入端与所述R数据信号线连接,所述第九开关管T9 的控制端与所述B控制电压信号线连接,所述第十开关管的控制端与所述R 控制电压信号线CT-EN-R连接。

[0044] 在一些实施例中,该第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为场效应薄膜晶体管。第一开关管、第二开关管、第三开关管、第四开关管、第五开关管、第六开关管、第七开关管、第八开关管、第九开关管、第十开关管均为P型场效应薄膜晶体管。

[0045] 其中,具体驱动第一行像素结构时,输入数据信号线的时序控制如图2 所示,Scan [1]控制第一行100的数据信号写入,Scan[2]控制第2行像素结构100的写入。第一行数据信号驱动第一行像素结构100时间段为X,第一行写入RGBBGR……数据,成功驱动第一行像素结构100。

[0046] 其中,具体驱动第二行像素结构时,输入数据信号线的时序控制如图3 所示,Scan [2]控制第2行数据信号写入,第二行数据信号驱动第二行像素结构100时间段为Y,随着第一行写入BGRRGB……数据,成功驱动第二行像素结构100。后续每一行驱动:奇数行CT工作状态与第一行像素结构一致,偶数行工作状态与第二行像素结构一致。

[0047] 驱动时,该G控制电压信号线传输的电压为低电平信号,使得所述第二选通模块以及所述第五选通模块处于导通状态。该与同一所述R控制电压信号线或同一所述B控制电压信号线连接的开关管的导通状态相同,所述R控制电压信号线连接的开关管的导通状态与所述B控制电压信号线连接的开关管的导通状态相反。

[0048] 本申请通过采用新型的测试电路,通过设置多个选通模块,从而实现对新型的显示面板进行点亮测试的效果,可以提高产品合格率。

[0049] 本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施方式的说明只是用于帮助理解本申请。同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

图1

图2

图3

|         |                              |                      |            |

|---------|------------------------------|----------------------|------------|

| 专利名称(译) | 显示面板的测试电路及OLED显示器            |                      |            |

| 公开(公告)号 | <a href="#">CN111063282A</a> | 公开(公告)日              | 2020-04-24 |

| 申请号     | CN201911177923.3             | 申请日                  | 2019-11-27 |

| [标]发明人  | 张娣                           |                      |            |

| 发明人     | 张娣                           |                      |            |

| IPC分类号  | G09G3/00 G09G3/3208          |                      |            |

| CPC分类号  | G09G3/006 G09G3/3208         |                      |            |

| 外部链接    | <a href="#">Espacenet</a>    | <a href="#">Sipo</a> |            |

### 摘要(译)

本申请提供了一种显示面板的测试电路，所述测试电路包括：三条输入数据信号线，所述三条输入数据信号线包括R数据信号线、G数据信号线以及B数据信号线；三条控制电压信号线，所述控制电压信号线包括R控制电压信号线、G控制电压信号线以及B控制电压信号线；多个测试单元，每一所述测试单元包括六个选通模块，所述六个选通模块的输出端与所述像素结构的6列子像素分别连接，其中，每一所述选通模块的输出端与一列子像素中的各个子像素分别连接；每一所述选通模块的输入端分别对应列的子像素所对应的一条数据信号线或两条数据信号线连接；每一所述选通模块的控制端分别对应列的子像素所对应的一条控制电压信号线或两条控制电压信号线连接。