(12)发明专利申请

(10)申请公布号 CN 110164373 A

(43)申请公布日 2019.08.23

(21)申请号 201910444513.4

(22)申请日 2019.05.27

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

申请人 合肥鑫晟光电科技有限公司

(72)发明人 黄勇潮 成军 王东方 刘军

张扬 王庆贺 周斌 何敏

(74)专利代理机构 北京同达信恒知识产权代理

有限公司 11291

代理人 郭润湘

(51)Int.Cl.

G09G 3/3225(2016.01)

H01L 27/32(2006.01)

权利要求书1页 说明书5页 附图4页

(54)发明名称

一种像素驱动电路及其制备方法、OLED显示

面板

(57)摘要

本发明涉及显示技术领域,公开了一种像素驱动电路及其制备方法、OLED显示面板、显示装置,该像素驱动电路包括:驱动晶体管和存储电容,其中,驱动晶体管包括:依次层叠设置于衬底基板上的有源层、栅绝缘层、栅极、层间介质层和源漏电极;存储电容包括:依次层叠设置的第一电极、层间介质层和第二电极,第一电极与源漏电极中的漏电极电连接,第二电极与源漏电极同层设置且相互绝缘,第二电极与栅极电连接;层间介质层位于第一电极和第二电极之间部分的厚度小于其它部分的厚度。该像素驱动电路中,在电容区的层间介质层的厚度较薄,则电容区的面积不发生变化,电容区的层间介质层厚度减小,电容增大,有效提高驱动晶体管效率,提高像素亮度。

1. 一种像素驱动电路,其特征在于,包括:驱动晶体管和存储电容,其中,所述驱动晶体管包括:依次层叠设置于衬底基板上的有源层、栅绝缘层、栅极、层间介质层和源漏电极;

所述存储电容包括:依次层叠设置的第一电极、所述层间介质层和第二电极,所述驱动晶体管的有源层中导体化部分的一部分构成所述第一电极,所述第一电极与所述驱动晶体管的源漏电极中的漏电极电连接,所述第二电极与所述源漏电极同层设置且相互绝缘,所述第二电极与所述栅极电连接;

所述层间介质层位于所述第一电极和第二电极之间部分的厚度小于其它部分的厚度。

2. 根据权利要求1所述的像素驱动电路,其特征在于,所述层间介质层位于所述第一电极与所述第二电极之间部分的厚度大于或等于  $2000\text{Å}$  且小于或等于  $3500\text{Å}$ 。

3. 根据权利要求2所述的像素驱动电路,其特征在于,所述层间介质层位于所述第一电极与所述第二电极之间部分的厚度为  $2500\text{Å}$ 。

4. 根据权利要求1所述的像素驱动电路,其特征在于,所述第一电极位于所述有源层中半导体部分的一侧,且所述第一电极和所述有源层中半导体部分在所述衬底基板上的正投影位于所述源漏电极中的源电极和漏电极在所述衬底基板上的正投影之间。

5. 根据权利要求1所述的像素驱动电路,其特征在于,还包括开关晶体管,所述开关晶体管的栅极与第一扫描信号线电连接,所述开关晶体管的源漏电极与所述驱动晶体管的源漏电极同层设置,所述开关晶体管的源漏电极中的源电极与数据线电连接,所述开关晶体管的源漏电极中的漏电极与所述驱动晶体管的栅极电连接。

6. 根据权利要求5所述的像素驱动电路,其特征在于,还包括用于对所述像素驱动电路进行数据电压补偿的补偿晶体管,所述补偿晶体管的栅极与第二扫描信号线电连接,且所述补偿晶体管的源漏电极中的源电极与所述驱动晶体管的漏电极电连接,所述补偿晶体管的源漏电极中的漏电极与补偿检测线电连接。

7. 一种如权利要求1-6任一项所述的像素驱动电路的制备方法,其特征在于,包括:

在衬底基板上依次形成驱动晶体管的有源层,并对所述有源层进行部分导体化,其中,所述有源层中导体化的一部分构成存储电容的第一电极;

在所述有源层上依次形成栅绝缘层、所述驱动晶体管的栅极和层间介质层;

在所述层间介质层形成之后,对所述层间介质层中与所述存储电容的第一电极对应的部位进行减薄处理,以使所述层间介质层中与所述第一电极对应部分的厚度小于其它部分的厚度;

在所述层间介质层上形成所述驱动晶体管的源漏电极和与所述第一电极相对设置的第二电极,所述第二电极与所述驱动晶体管的源漏电极相互绝缘。

8. 根据权利要求7所述的制备方法,其特征在于,采用干刻工艺对所述层间介质层中与所述第一电极对应部位进行减薄处理。

9. 一种OLED显示面板,其特征在于,包括如权利要求1-6任一项所述的像素驱动电路。

10. 一种显示装置,其特征在于,包括如权利要求9所述的OLED显示面板。

## 一种像素驱动电路及其制备方法、OLED显示面板

### 技术领域

[0001] 本发明涉及显示技术领域,特别涉及一种像素驱动电路及其制备方法、OLED显示面板、显示装置。

### 背景技术

[0002] 在OLED显示领域,在阵列基板的TFT工艺中,由于高PPI的技术不断发展,要求阵列基板中的金属的厚度越来越厚,相应的绝缘层的厚度也越来越厚,由于绝缘层的厚度增加,相应的每个子像素单元中的电容区域的绝缘层厚度也会增加,如此,就会导致子像素单元的存储电容Cst减小,从而容易导致TFT效率下降。

### 发明内容

[0003] 本发明公开了一种像素驱动电路及其制备方法、OLED显示面板、显示装置,该像素驱动电路中,对比于现有技术中在电容区的部位的层间介质层,本发明实施例中的在电容区的层间介质层的厚度较薄,则电容区的面积不发生变化,电容区的层间介质层厚度减小,电容增大,可以有效提高驱动晶体管的效率,提高像素亮度。

[0004] 为达到上述目的,本发明提供以下技术方案:

[0005] 一种像素驱动电路,包括:驱动晶体管和存储电容,其中,

[0006] 所述驱动晶体管包括:依次层叠设置于衬底基板上的有源层、栅绝缘层、栅极、层间介质层和源漏电极;

[0007] 所述存储电容包括:依次层叠设置的第一电极、所述层间介质层和第二电极,所述驱动晶体管的有源层中导体化部分的一部分构成所述第一电极,所述第一电极与所述驱动晶体管的源漏电极中的漏电极电连接,所述第二电极与所述源漏电极同层设置且相互绝缘,所述第二电极与所述栅极电连接;

[0008] 所述层间介质层位于所述第一电极和第二电极之间部分的厚度小于其它部分的厚度。

[0009] 上述像素驱动电路中包括有驱动晶体管和存储电容,驱动晶体管包括一次层叠设置的有源层、栅绝缘层、栅极、层间介质层和源漏电极,上述驱动晶体管的有源层中与栅极相对的部分为半导体,需要与源漏电极连接的部分为导体化,存储电容包括依次层叠设置的第一电极、所述层间介质层和第二电极,第一电极和第二电极相对的区域会构成一个电容区,其中,第一电极可以为上述驱动晶体管的有源层中导体化部分中的一部分构成,且第一电极与驱动晶体管的源漏电极中的漏电极电连接,即,第一电极可以由有源层中与驱动晶体管的源漏电极中的漏电极相对应的部分的一部分构成,即有源层中与源漏电极中的漏电极相对应的导体化部分划分为两部分,一部分与源漏电极中的漏电极相对电连接,另一部分构成第一电极,第二电极为与驱动晶体管的源漏电极同层设置且相互绝缘的一个电极,且第二电极与驱动晶体管的栅极电连接,其中,层间介质层中位于第一电极与第二电极之间且与第一电极和第二电极相对的部分的厚度小于其它部分的厚度,即,层间介质层中位于

电容区的部分的厚度比其它部分薄,相比于现有技术中,层间介质层的厚度一致,则对比于现有技术中在电容区的部位的层间介质层,本发明中的在电容区的层间介质层的厚度较薄,则电容区的面积不发生变化,电容区的层面介质层厚度减小,电容增大,可以有效提高驱动晶体管的效率,提高像素亮度。

[0010] 优选地,所述层间介质层位于所述第一电极与所述第二电极之间部分的厚度大于或等于2000Å且小于等于3500Å。

[0011] 优选地,所述层间介质层位于所述第一电极与所述第二电极之间部分的厚度为2500Å。

[0012] 优选地,所述第一电极位于所述有源层中半导体部分的一侧,且所述第一电极和所述有源层中半导体部分在所述衬底基板上的正投影位于所述源漏电极中的源电极和漏电极在所述衬底基板上的正投影之间。

[0013] 优选地,所述像素驱动电路还包括开关晶体管,所述开关晶体管的栅极与第一扫描信号线电连接,所述开关晶体管的源漏电极与所述驱动晶体管的源漏电极同层设置,所述开关晶体管的源漏电极中的源电极与数据线电连接,所述开关晶体管的源漏电极中的漏电极与所述驱动晶体管的栅极电连接。

[0014] 优选地,所述像素驱动电路还包括用于对所述像素驱动电路进行数据电压补偿的补偿晶体管,所述补偿晶体管的栅极与第二扫描信号线电连接,且所述补偿晶体管的源漏电极中的源电极与所述驱动晶体管的漏电极电连接,所述补偿晶体管的源漏电极中的漏电极与补偿检测线电连接。

[0015] 本发明还提供了一种如上述技术方案提供的任意一种像素驱动电路的制备方法,所述制备方法包括:

[0016] 在衬底基板上依次形成驱动晶体管的有源层,并对所述有源层进行部分导体化,其中,所述有源层中导体化的一部分构成存储电容的第一电极;

[0017] 在所述有源层上依次形成栅绝缘层、所述驱动晶体管的栅极和层间介质层;

[0018] 在所述层间介质层形成之后,对所述层间介质层中与所述存储电容的第一电极对应的部位进行减薄处理,以使所述层间介质层中与所述第一电极对应部分的厚度小于其它部分的厚度;

[0019] 在所述层间介质层上形成所述驱动晶体管的源漏电极和与所述第一电极相对设置的第二电极,所述第二电极与所述驱动晶体管的源漏电极相互绝缘。

[0020] 优选地,采用干刻工艺对所述层间介质层中与所述第一电极对应部位进行减薄处理。

[0021] 基于相同的发明构思,本发明还提供了一种OLED显示面板,包括上述技术方案提供的任意一种像素驱动电路。

[0022] 基于相同的发明构思,本发明还提供了一种显示装置,包括上述技术方案提供的OLED显示面板。

## 附图说明

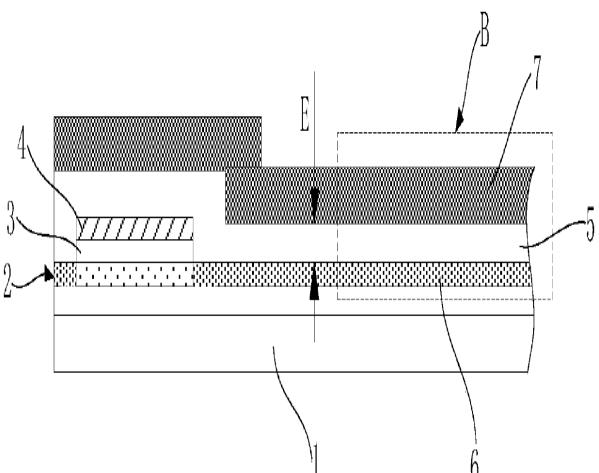

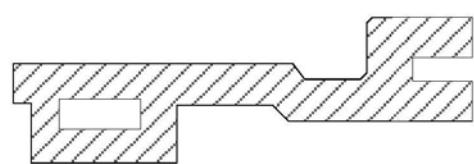

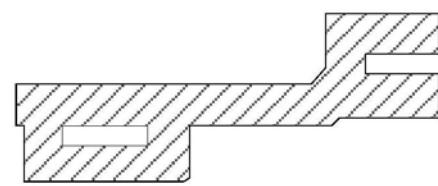

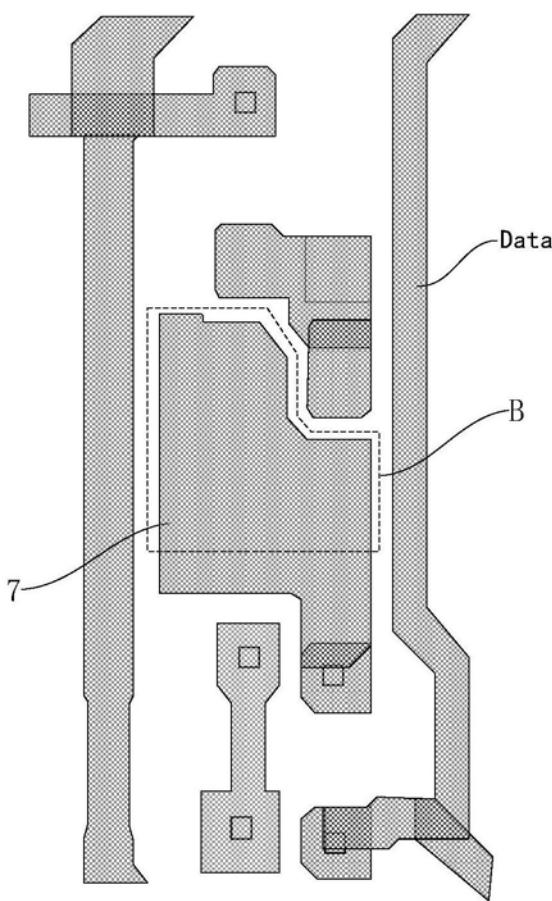

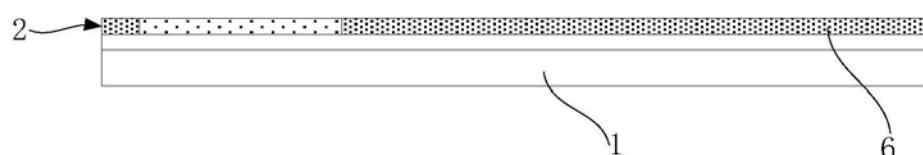

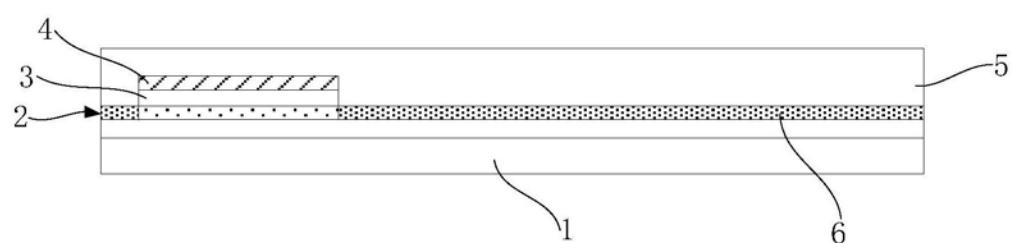

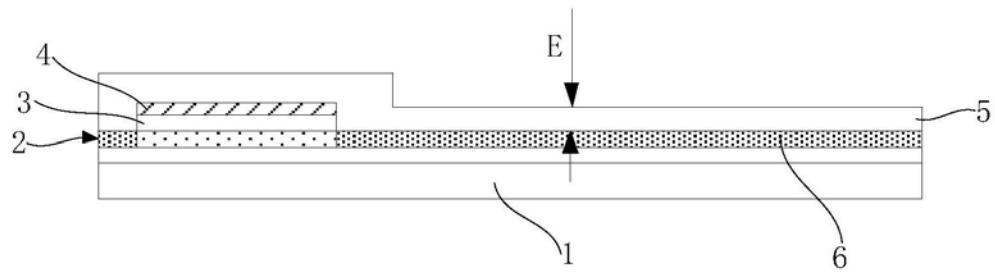

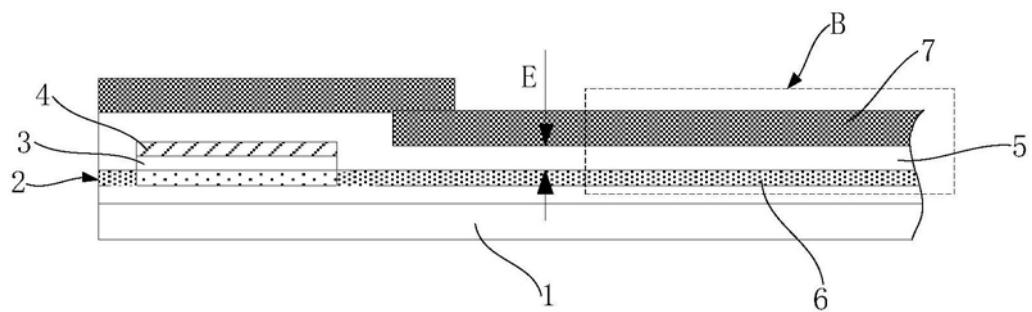

[0023] 图1为本发明实施例提供的一种像素驱动电路的膜层结构俯视图;

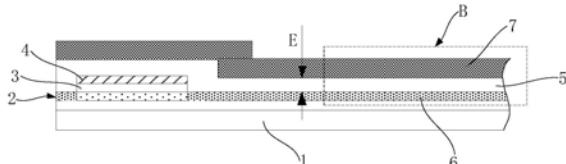

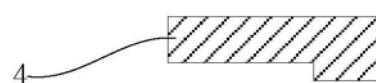

- [0024] 图2为图1中像素驱动电路的驱动晶体管的有源层所在膜层的俯视图；

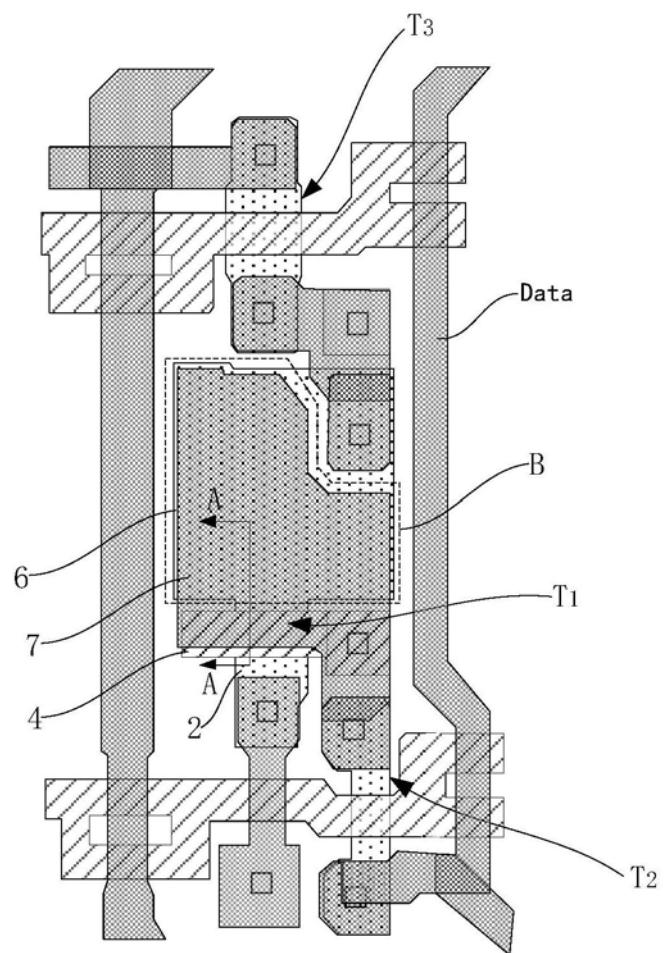

[0025] 图3为图1中像素驱动电路的驱动晶体管的栅极所在膜层的俯视图；

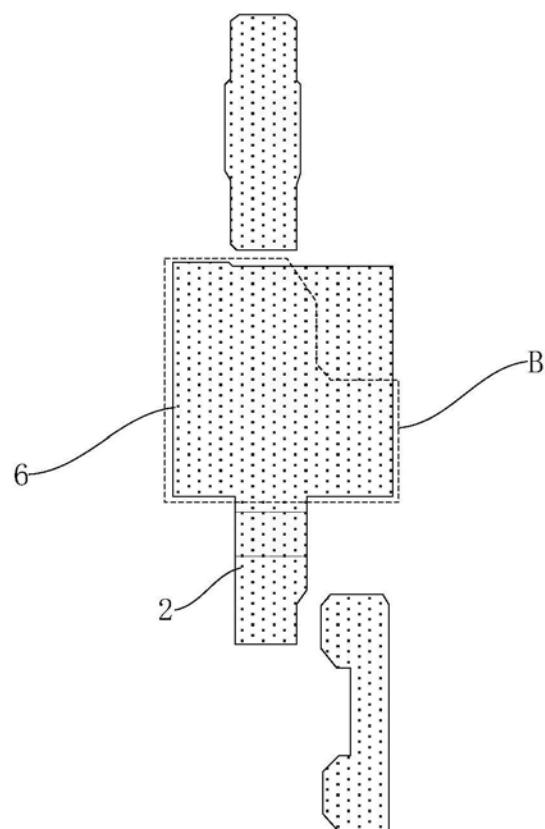

[0026] 图4为图1中像素驱动电路的存储电容的第二电极所在膜层的俯视图；

[0027] 图5至图8为本发明实施例提供的图1中的像素驱动电路的制备过程中沿A-A处的膜层变化示意图；

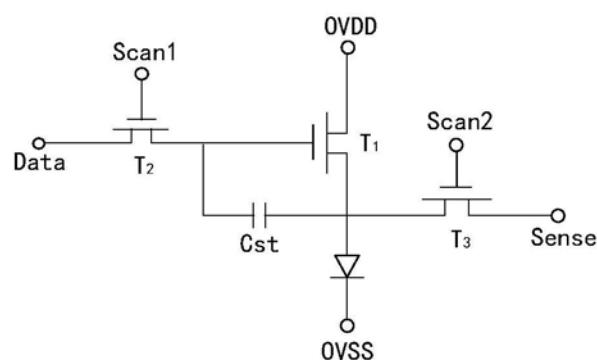

[0028] 图9为本发明实施例提供的一种像素驱动电路的等效电路图；

[0029] 图标:1-衬底基板；2-有源层；3-栅绝缘层；4-栅极；5-层间介质层；6-第一电极；7-第二电极；T1-驱动晶体管；T2-开关晶体管；T3-补偿晶体管。

## 具体实施方式

[0030] 下面将结合本发明实施例中的附图，对本发明实施例中的技术方案进行清楚、完整地描述，显然，所描述的实施例仅仅是本发明一部分实施例，而不是全部的实施例。基于本发明中的实施例，本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例，都属于本发明保护的范围。

[0031] 请参考图1至图3以及图8和图9，其中，图8为图1中沿A-A向的截面示意图，本发明实施例提供了一种像素驱动电路，包括：驱动晶体管T1和存储电容Cst，其中，驱动晶体管T1包括：依次层叠设置于衬底基板1上的有源层2、栅绝缘层3、栅极4、层间介质层5和源漏电极；存储电容Cst包括：依次层叠设置的第一电极6、层间介质层5和第二电极7，驱动晶体管T1的有源层2中导体化部分的一部分构成第一电极6，第一电极6与驱动晶体管T1的源漏电极中的漏电极电连接，第二电极7与源漏电极同层设置且相互绝缘，第二电极7与栅极4电连接；层间介质层5位于第一电极6和第二电极7之间部分的厚度小于其它部分的厚度。

[0032] 上述像素驱动电路中包括有驱动晶体管T1和存储电容Cst，如图1至图3以及图8所示，驱动晶体管T1包括一次层叠设置的有源层2、栅绝缘层3、栅极4、层间介质层5和源漏电极，上述驱动晶体管T1的有源层2中与栅极4相对的部分为半导体，需要与源漏电极连接的部分为导体化，存储电容Cst包括依次层叠设置的第一电极6、上述层间介质层5和第二电极7，第一电极6和第二电极7相对的区域会构成一个电容区B(如图1中虚线所围成的区域)，其中，第一电极6可以为上述驱动晶体管的有源层2中导体化部分中的一部分构成，且第一电极6与驱动晶体管的源漏电极中的漏电极电连接，即，第一电极6可以由有源层2中与驱动晶体管的源漏电极中的漏电极对应的部分的一部分构成，即有源层2中与源漏电极中的漏电极对应的导体化部分划分为两部分，一部分与源漏电极中的漏电极相对电连接，另一部分构成第一电极6，第二电极7为与驱动晶体管的源漏电极同层设置且相互绝缘的一个电极，且第二电极7与驱动晶体管的栅极4电连接，其中，层间介质层5中位于第一电极6与第二电极7之间且与第一电极6和第二电极7相对的部分的厚度小于其它部分的厚度，即，层间介质层5中位于电容区的部分的厚度比其它部分薄，相比于现有技术中，层间介质层5的厚度一致，则对于现有技术中在电容区的部位的层间介质层5，本发明实施例中的在电容区的层间介质层5的厚度较薄，则电容区的面积不发生变化，电容区的层间介质层厚度减小，电容增大，提高驱动晶体管效率，可以有效提高驱动晶体管效率，提高像素亮度。

[0033] 上述像素驱动电路中，如图8所示，层间介质层5位于第一电极6与第二电极7之间部分的厚度E大于或等于2000Å且小于或等于3500Å，为保证第一电极6与第二电极7之间的

层间介质层5不被击穿,层间介质层5位于第一电极6和第二电极7之间的部分不能太薄,厚度E可以设置在2000Å ~ 3500Å,具体地,层间介质层5位于第一电极6与第二电极7之间部分的厚度可以设置为2500Å,既可以使层间介质层5位于第一电极6和第二电极7之间的部分不被击穿,厚度又较薄,有利于增大电容区的电容。需要说明的是,层间介质层5位于第一电极6与第二电极7之间部分的厚度也可以设置为2300Å、3000Å或3200Å,或者其它厚度值,本实施例不做局限。

[0034] 根据图1和图8所示,上述像素驱动电路中,第一电极6位于有源层2中半导体部分的一侧,且第一电极6和有源层2中的半导体部分在衬底基板1上的正投影位于源漏电极中的源电极和漏电极在衬底基板1上的正投影之间。即,有源层2中与源漏电极的源电极和漏电极接触连接的部分位于第一电极6和半导体部分的两边,便于与源漏电极中的源电极和漏电极的连接。

[0035] 具体地,如图1和图9所示,上述像素驱动电路中还包括开关晶体管T2,开关晶体管T2的栅极与第一扫描信号线Scan1电连接,开关晶体管T2的源漏电极与驱动晶体管T1的源漏电极同层设置且相互绝缘,开关晶体管T2的源漏电极中的源电极与数据线Data电连接,用于载入第一电压信号,开关晶体管T2的源漏电极中的漏电极与驱动晶体管T1的栅极4电连接,用于给驱动晶体管的栅极4输入第二电压信号。

[0036] 具体地,如图1和图9所示,上述像素驱动电路还包括用于对像素驱动电路进行数据电压补偿的补偿晶体管T3,补偿晶体管T3的栅极与第二扫描信号线Scan2电连接,且补偿晶体管T3的源漏电极中的源电极与驱动晶体管T1的漏电极电连接,补偿晶体管T3的源漏电极中的漏电极与补偿检测线Sense电连接,上述像素驱动电路中设置补偿晶体管T3,补偿晶体管T3与补偿检测线Sense电连接,可以对像素驱动电路中的数据电压进行补偿,有效提高显示效果。

[0037] 结合图1至图8所示,本发明还提供了一种如上述实施例提供的任意一种像素驱动电路的制备方法,制备方法包括:

[0038] 步骤S101,参考图5和图2所示,在衬底基板1上形成驱动晶体管T1的有源层2,并对有源层2进行部分导体化,其中,有源层2中导体化部分的一部分构成存储电容的第一电极6;

[0039] 步骤S102,参考图6和图3所示,在有源层2上依次形成栅绝缘层3、驱动晶体管T1的栅极4和层间介质层5;

[0040] 步骤S103,参考图7所示,在层间介质层5形成之后,对层间介质层5中与存储电容的第一电极6对应的部位进行减薄处理,以使层间介质层5中与第一电极6对应部分的厚度E小于其它部分的厚度;

[0041] 步骤S104,参考图8和图4所示,在层间介质层5上形成驱动晶体管的源漏电极和与第一电极6相对设置的第二电极7,第二电极7与驱动晶体管T1的源漏电极相互绝缘,源漏电极与有源层2中导体化部分电连接,第二电极7贯穿栅绝缘层3和层间介质层5与驱动晶体管T1的栅极4电连接。

[0042] 上述制备方法中,首先,按照步骤S101,结合图1,参考图5和图2所示,在衬底基板1上形成驱动晶体管T1的有源层2,对有源层2进行部分导体化,其中,有源层2中导体化部分

的一部分可以构成储存电容的第一电极6,然后,根据步骤S102,参考图6和图3所示,在有源层2上依次形成栅绝缘层3、驱动晶体管的栅极4和层间介质层5,在层间介质层5形成之后,根据步骤S103,参考图7所示,在层间介质层5与存储电容的第一电极6对应的部位进行减薄处理,使层间介质层5中与第一电极6对应的部分的厚度E减小,并在层间介质层5中形成第一过孔和第二过孔,其中,第一过孔与驱动晶体管的有源层2中导体化部分对应,且用于后续制备的驱动晶体管的源漏电极与有源层2的导体化部分电连接,第二过孔与驱动晶体管的栅极4对应,用于后续制备的存储电容的第二电极7与驱动晶体管的栅极4电连接,接着根据步骤S104,参考图8和图4所示,在层间介质层5上形成驱动晶体管的源漏电极、与第一电极6相对设置的第二电极7,驱动晶体管的源漏电极通过第一过孔与驱动晶体管的有源层2中导体化部分电连接,第二电极7与驱动晶体管的源漏电极相互绝缘,且第二电极7通过第二过孔与驱动晶体管的栅极4电连接。

[0043] 具体地,上述制备方法中,采用干刻工艺对层间介质层5中与第一电极6对应部位进行减薄处理。

[0044] 基于相同的发明构思,本发明实施例还提供了一种OLED显示面板,包括上述技术方案提供的任意一种像素驱动电路。

[0045] 基于相同的发明构思,本发明实施例还提供了一种显示装置,包括上述技术方案提供的OLED显示面板。

[0046] 需要说明的是,上述实施例中提到的驱动晶体管、开关晶体管和补偿晶体管中的源电极为电信号的输入电极,漏电极为电信号的输出端,其中,晶体管包括P型和N型,不同类型的晶体管的源、漏电极的信号输入和输出会有不同,但仅是对电信号的输入电极和输出电极的名称不同,不改变晶体管在电路中的电信号路径方向,所以,本实施例中的驱动晶体管、开关晶体管和补偿晶体管为N型的,也可以是P型,其中,上述驱动晶体管、开关晶体管和补偿晶体管的源漏电极中的源电极和漏电极可以根据其类型互换名称,并不影响上述像素驱动电路中的电信号路径方向。

[0047] 显然,本领域的技术人员可以对本发明实施例进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

图1

图2

图3

图4

图5

图6

图7

图8

图9

|                |                                                 |         |            |

|----------------|-------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素驱动电路及其制备方法、OLED显示面板                         |         |            |

| 公开(公告)号        | <a href="#">CN110164373A</a>                    | 公开(公告)日 | 2019-08-23 |

| 申请号            | CN201910444513.4                                | 申请日     | 2019-05-27 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                   |         |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                   |         |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                   |         |            |

| [标]发明人         | 黄勇潮<br>成军<br>王东方<br>刘军<br>张扬<br>王庆贺<br>周斌<br>何敏 |         |            |

| 发明人            | 黄勇潮<br>成军<br>王东方<br>刘军<br>张扬<br>王庆贺<br>周斌<br>何敏 |         |            |

| IPC分类号         | G09G3/3225 H01L27/32                            |         |            |

| CPC分类号         | G09G3/3225 H01L27/3244                          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>  |         |            |

### 摘要(译)

本发明涉及显示技术领域，公开了一种像素驱动电路及其制备方法、OLED显示面板、显示装置，该像素驱动电路包括：驱动晶体管和存储电容，其中，驱动晶体管包括：依次层叠设置于衬底基板上的有源层、栅绝缘层、栅极、层间介质层和源漏电极；存储电容包括：依次层叠设置的第一电极、层间介质层和第二电极，第一电极与源漏电极中的漏电极电连接，第二电极与源漏电极同层设置且相互绝缘，第二电极与栅极电连接；层间介质层位于第一电极和第二电极之间部分的厚度小于其它部分的厚度。该像素驱动电路中，在电容区的层间介质层的厚度较薄，则电容区的面积不发生变化，电容区的层间介质层厚度减小，电容增大，有效提高驱动晶体管效率，提高像素亮度。