(12)发明专利申请

(10)申请公布号 CN 111192898 A

(43)申请公布日 2020.05.22

(21)申请号 201910243306.2

(22)申请日 2019.03.28

(71)申请人 广东聚华印刷显示技术有限公司

地址 510000 广东省广州市广州中新广州

知识城凤凰三路17号自编五栋388

(72)发明人 史文 陈亚文

(74)专利代理机构 广州华进联合专利商标代理

有限公司 44224

代理人 郑彤 欧阳柏乐

(51)Int.Cl.

H01L 27/32(2006.01)

H01L 51/52(2006.01)

H01L 51/56(2006.01)

权利要求书2页 说明书7页 附图3页

(54)发明名称

像素结构、有机发光二极管及其制备方法

(57)摘要

本发明涉及一种像素结构、有机发光二极管及其制备方法,该像素结构包括衬底;像素电极,设于衬底上,像素电极具有设置于像素坑内的第一段,且第一段远离衬底的一面为凹凸的非平面,第一段包括:表示沿垂直于衬底的方向,离衬底距离最近的第一位点和离衬底距离最近的第二位点,第一位点和第二位点之间的段差A=D-d,其中,D表示第一位点和衬底之间的距离,d表示第二位点和衬底之间的距离;像素界定层满足以下公式:40A≥C≥10A+B其中,B表示像素电极的厚度,C表示像素界定层的厚度。上述像素结构能够有效地克服像素电极不同位置之间的段差所造成成膜不均的问题。

1. 一种像素结构,其特征在于,包括:

衬底;

像素界定层,设于所述衬底上,所述像素界定层围合形成像素坑;

像素电极,设于所述衬底上,所述像素电极具有设置于所述像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括,沿垂直于所述衬底的方向,离所述衬底距离最近的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;其中,所述像素界定层满足以下公式:

$$40A \geq C \geq 10A+B,$$

B表示所述像素电极的厚度,C表示所述像素界定层的厚度。

2. 根据权利要求1所述的像素结构,其特征在于,所述像素界定层满足以下公式: $25A \geq C \geq 20A+B$ 。

3. 根据权利要求1所述的像素结构,其特征在于,所述像素电极和所述衬底之间还设置有钝化层。

4. 根据权利要求1-3任一项所述的像素结构,其特征在于,所述像素电极的所述第一位点和所述第二位点之间的段差为190nm-210nm。

5. 根据权利要求4所述的像素结构,其特征在于,所述像素界定层的厚度为 $3.5\mu\text{m}-5\mu\text{m}$ 。

6. 一种有机发光二极管,其特征在于,包括像素结构和发光层,所述像素结构包括:

衬底;

像素界定层,设于所述衬底上,所述像素界定层围合形成像素坑;

像素电极,设于所述衬底上,所述像素电极具有设置于所述像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括,沿垂直于所述衬底的方向,离所述衬底距离最近的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;其中,所述像素界定层满足以下公式:

$$40A \geq C \geq 10A+B,$$

B表示所述像素电极的厚度,C表示所述像素界定层的厚度;

所述发光层设置在所述像素坑中。

7. 根据权利要求6所述的有机发光二极管,其特征在于,所述像素界定层满足以下公式: $25A \geq C \geq 20A+B$ 。

8. 一种有机发光二极管的制备方法,其特征在于,包括以下步骤:

提供衬底;

在所述衬底上设置像素电极,其中,所述像素电极具有用于设置于像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括,沿垂直于所述衬底的方向,离所述衬底距离最近的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;

的距离；

在所述衬底上层叠像素界定层，所述像素界定层围合成像素坑，且使所述像素电极的至少部分区域露出于所述像素坑；且所述像素界定层满足以下公式： $40A \geq C \geq 10A+B$ ， $B$ 表示所述像素电极的厚度， $C$ 表示所述像素界定层的厚度；在所述像素坑中制备发光层。

9. 根据权利要求8所述的制备方法，其特征在于，在所述像素坑中制备发光层的步骤包括以下步骤：

将用于形成所述发光层的墨水沉积至所述像素坑内；

第一次干燥至所述像素坑内的墨水的液面与所述像素坑的边缘齐平；

将所述像素坑内的墨水凝固；

对经过凝固的墨水进行第二次干燥，制得所述发光层。

10. 根据权利要求9所述的制备方法，其特征在于，采用一维真空干燥工艺进行所述第一次干燥，所述第一次干燥的真空度为 $20\text{ torr} \sim 100\text{ torr}$ ；和/或

所述第二次干燥的真空度为 $10^{-8}\text{ torr} \sim 10^{-4}\text{ torr}$ 。

## 像素结构、有机发光二极管及其制备方法

### 技术领域

[0001] 本发明涉及电子显示技术领域,特别涉及像素结构、有机发光二极管及其制备方法。

### 背景技术

[0002] 有机电致发光二极管(OLED)由于其具有自发光、反应快、视角广、亮度高、轻薄等优点,成为未来显示的主流。特别是顶发射型OLED由于其中开口率方面的优势,尤其是高分辨显示面板方面,得到越来越广泛的应用。但,顶发射型结构的OLED的像素电极和基板之间存在走线、电容结构以及部分薄膜晶体管等,导致像素电极不平,即像素电极的表面不同位置存在段差。特别对于顶栅结构的驱动薄膜晶体管,由于驱动薄膜晶体管形成膜层较多,遮光层以及源漏电极层等需要设置在像素电极下方,导致此区域的整体膜层偏高,相对应此区域的像素电极离基板距离较远,会更进一步增加像素电极的段差。像素电极的段差的存在对于发光层各功能层的形成十分不利,很难形成均一化的薄膜。

### 发明内容

[0003] 基于此,有必要提供一种像素结构、有机发光二极管及其制备方法。该像素结构能够有效地克服像素电极的段差所造成的成膜不均的问题。

[0004] 一种像素结构,包括:

[0005] 衬底;

[0006] 像素界定层,设于所述衬底上,所述像素界定层围合形成像素坑;

[0007] 像素电极,设于所述衬底上,所述像素电极具有设置于所述像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括:沿垂直于所述衬底的方向,离所述衬底距离最近的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;

[0008] 其中,所述像素界定层满足以下公式:

[0009]  $40A \geq C \geq 10A+B$

[0010] 其中,B表示所述像素电极的厚度,C表示所述像素界定层的厚度。

[0011] 在其中一实施方式中,所述像素界定层满足以下公式: $25A \geq C \geq 20A+B$ 。

[0012] 在其中一实施方式中,所述像素电极和所述衬底之间还设置有钝化层。

[0013] 在其中一实施方式中,所述像素电极的所述第一位点和所述第二位点之间的段差为190nm-210nm。

[0014] 在其中一实施方式中,所述像素界定层的厚度为 $3.5\mu\text{m}-5\mu\text{m}$ 。

[0015] 一种有机发光二极管,包括像素结构和发光层,所述像素结构包括:

[0016] 衬底;

- [0017] 像素界定层,设于所述衬底上,所述像素界定层围合形成像素坑;

- [0018] 像素电极,设于所述衬底上,所述像素电极具有设置于所述像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括:沿垂直于所述衬底的方向,离所述衬底距离最远的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;

- [0019] 其中,所述像素界定层满足以下公式:

- [0020]  $40A \geq C \geq 10A+B$ ,

- [0021] B表示所述像素电极的厚度,C表示所述像素界定层的厚度;

- [0022] 所述发光层设置在所述像素坑中。

- [0023] 在其中一实施例中,所述有机发光二级管中的所述像素界定层满足以下公式: $25A \geq C \geq 20A+B$ 。

- [0024] 一种有机发光二极管的制备方法,包括以下步骤:

- [0025] 提供衬底;

- [0026] 在所述衬底上设置像素电极,其中,所述像素电极具有用于设置于像素坑内的第一段,且所述第一段远离所述衬底的一面为凹凸的非平面,所述第一段包括:沿垂直于所述衬底的方向,离所述衬底距离最远的第一位点和离所述衬底距离最近的第二位点,所述第一位点和所述第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于所述衬底的方向,所述第一位点和所述衬底之间的距离,d表示沿垂直于所述衬底的方向,所述第二位点和所述衬底之间的距离;

- [0027] 在所述衬底上层叠像素界定层,所述像素界定层围合成像素坑,且使所述像素电极的至少部分区域露出于所述像素坑;所述像素界定层满足以下公式: $40A \geq C \geq 10A+B$ ,B表示所述像素电极的厚度,C表示所述像素界定层的厚度;

- [0028] 在所述像素坑中制备发光层。

- [0029] 在其中一实施例中,在所述像素坑中制备发光层的步骤包括以下步骤:

- [0030] 将用于形成所述发光层的墨水沉积至所述像素坑内;

- [0031] 第一次干燥至所述像素坑内的墨水的液面与所述像素坑的边缘齐平;

- [0032] 将所述像素坑内的墨水凝固;

- [0033] 对经过凝固的墨水层进行第二次干燥,制得所述发光层。

- [0034] 在其中一实施例中,采用一维真空干燥工艺进行所述第一次干燥,所述第一次干燥的真空度为 $20\text{torr} \sim 100\text{torr}$ ;和/或

- [0035] 所述第二次干燥的真空度为 $10^{-8}\text{torr} \sim 10^{-4}\text{torr}$ 。

- [0036] 上述像素结构根据像素电极内第一位点和第二位点之间的段差和像素电极的厚度来调整像素界定层的厚度,可以有效地减小像素电极段差所造成的成膜不均,保证发光区内均匀有效的发光面积,进而保证显示面板的发光性能。且上述像素结构仅需调整像素界定层厚度即可减小像素电极段差所造成的影响,降低成膜工艺要求,可以大幅度简化制备工艺,降低生产成本。

## 附图说明

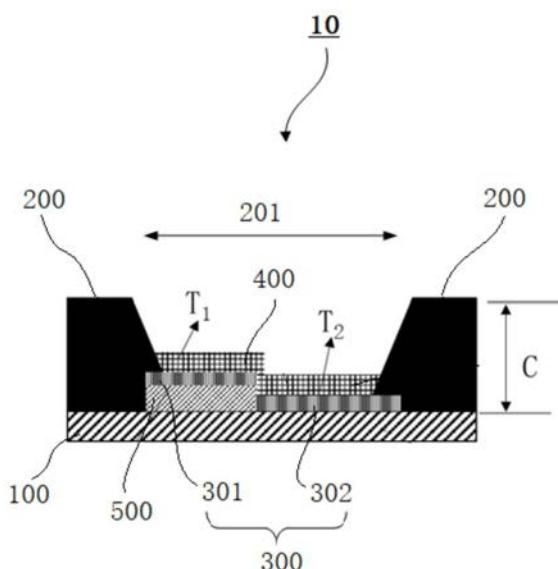

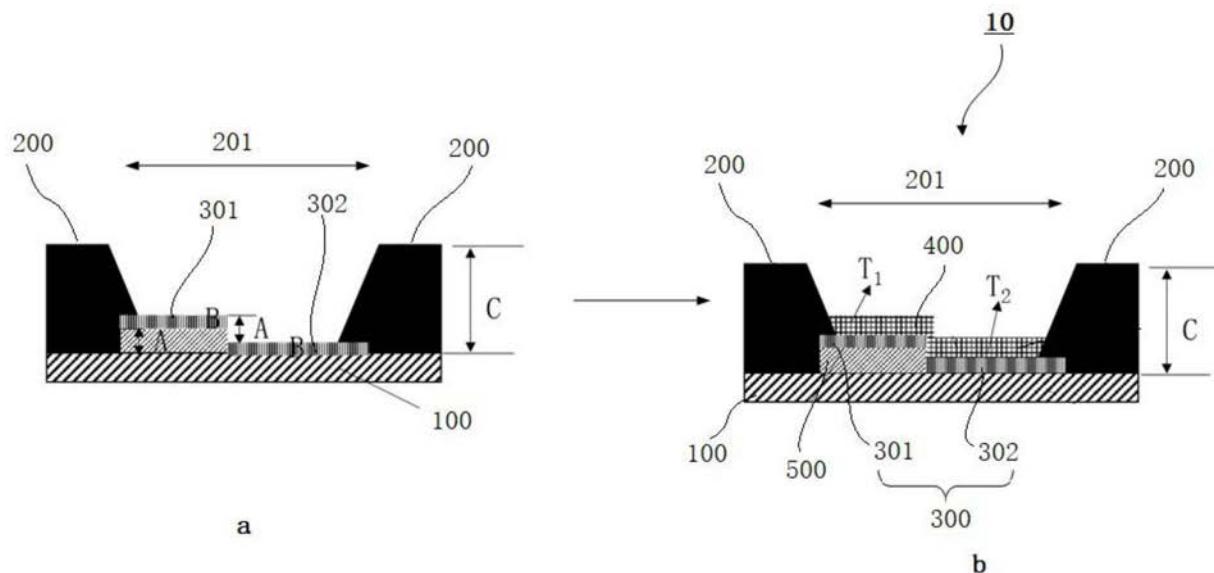

- [0037] 图1为本发明一实施方式的像素结构的示意图；

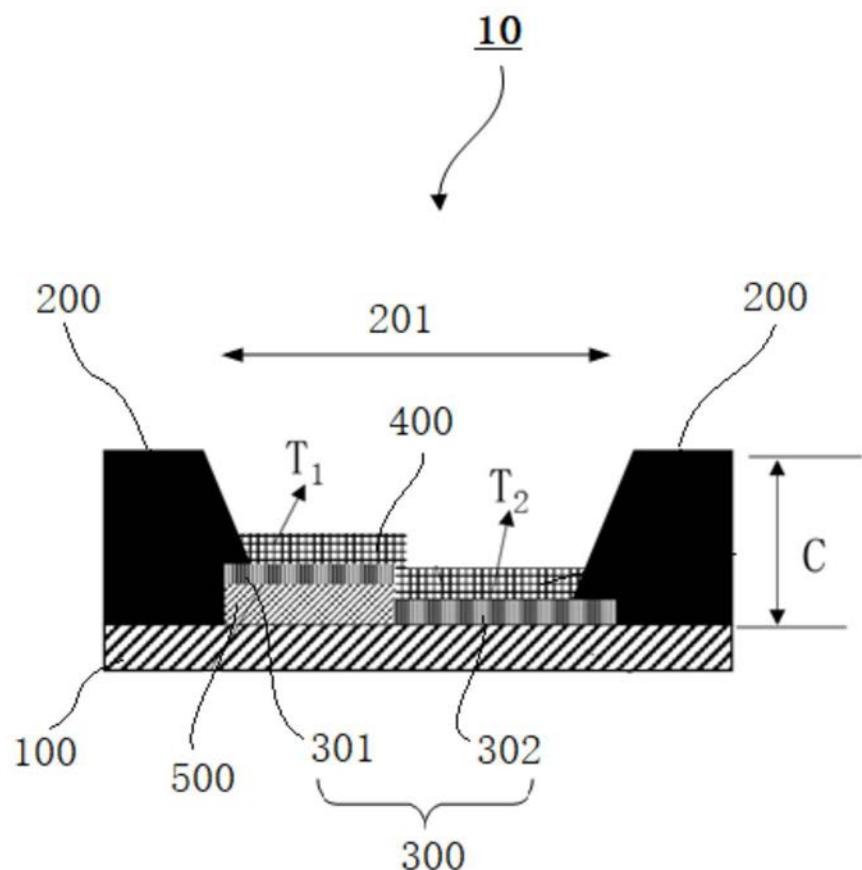

- [0038] 图2为本发明一实施方式的像素结构的示意图；

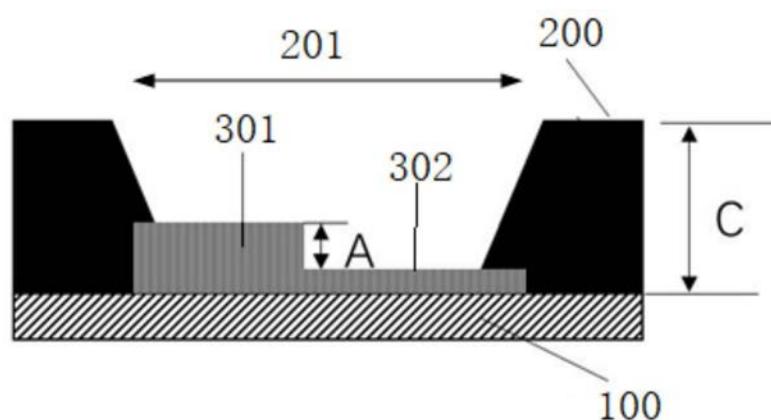

- [0039] 图3为本发明一实施方式的像素结构的示意图；

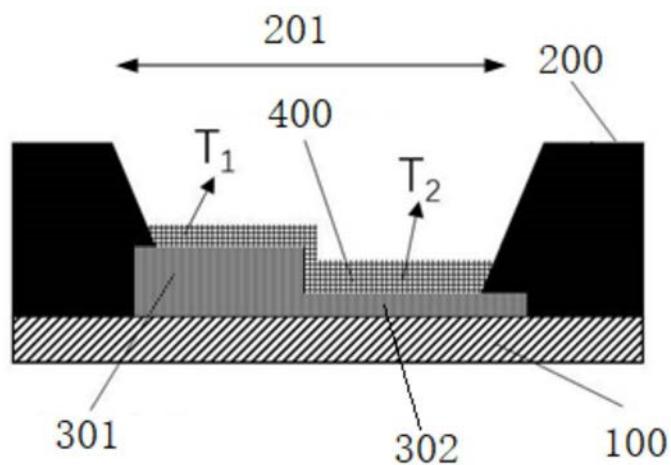

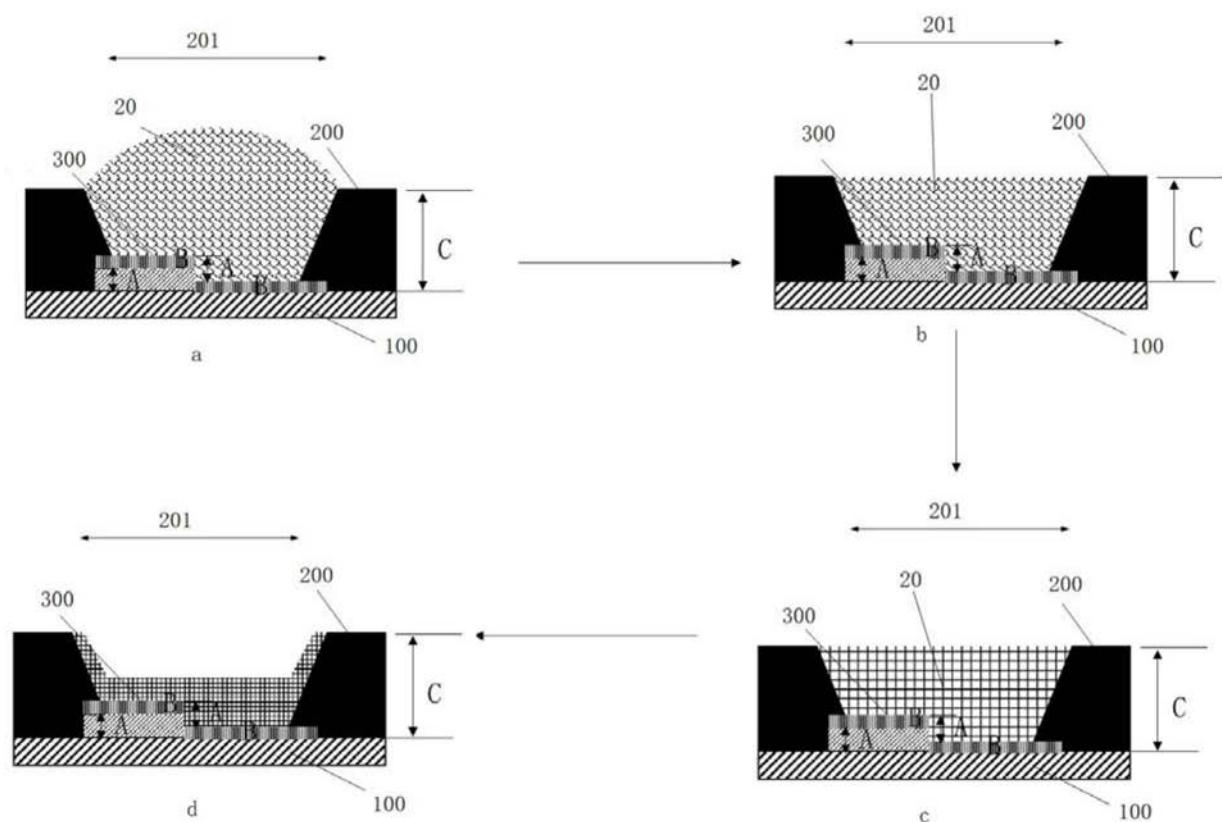

- [0040] 图4为制备图1所示的像素结构的流程图；

- [0041] 图5为本发明一实施方式的制备发光器件的流程图。

## 具体实施方式

[0042] 为了便于理解本发明，下面将对本发明进行更全面的描述，并给出了本发明的较佳实施例。但是，本发明可以以许多不同的形式来实现，并不限于本文所描述的实施例。相反地，提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

[0043] 除非另有定义，本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的，不是旨在于限制本发明。本文所使用的术语“和/或”包括一个或多个相关的所列项目的任意的和所有的组合。

[0044] 如图1所示，本发明一实施方式的像素结构10，包括衬底100、像素界定层200和像素电极300。其中，衬底100可以为柔性衬底或者玻璃衬底。在一实施例中，衬底包含驱动TFT单元，用于驱动发光元器件，实现图像显示。

[0045] 像素界定层200层叠在衬底100上，且像素界定层200围合形成像素坑201。其中，像素坑201的形状优选为梯形，即像素坑201包括第一开口和第二开口，靠近衬底的第一开口的面积小于远离衬底的第二开口的面积，其可以由SiNx等无机材料制成采用涂布等方式沉积而成，可以为单层结构，也可以为多层结构，在此不做特别限定。

[0046] 像素电极300具有设置于像素坑201内的第一段，且像素电极300的第一段的不同位置之间存在段差，即第一段的远离衬底100的一面为凹凸的非平面。其中，第一段包括：沿垂直于衬底100的方向，距离衬底100距离最远的第一位点和距离衬底100距离最近的第二位点，第一位点和第二位点之间的段差 $A=D-d$ ，其中，D表示沿垂直于衬底100的方向，第一位点和衬底100之间的距离，d表示沿垂直于衬底100的方向，第二位点和衬底100之间的距离。

[0047] 需要说明的是，为了方便说明，列举图1-图4所示像素电极，实际形成的像素电极可以具有多个凹凸不平的部位，且凹凸部位的形状不规则，像素电极的段差是指像素电极上不同位置之间的最大高度差。如图2所示，像素电极的第一段分为两部分，第一像素电极和第二像素电极，第一像素电极表示第一位点，即像素电极的与衬底间距离最大的部位，第二像素电极表示第二位点，像素电极的与衬底间距离最小的部位。

[0048] 像素电极300可以为本领域常规像素电极材料制备而成，更具体地，像素电极300可以为如ITO等的透明像素电极，也可以为如ITO/Ag/ITO等的反射像素电极，在此不做特别限定。像素电极300的设置方式也为本领域常规设置方式，在此不做特别限定。

[0049] 另外，上述像素结构10中像素界定层200满足以下公式： $40A \geq C \geq 10A+B$ ，其中，A表示像素电极300的第一位点301和第二位点302之间的段差，B表示像素电极300的厚度，C表示像素界定层的厚度。可以理解的是，像素电极不同部位的厚度可以存在本领域允许范围

内的偏差,此时,B表示像素电极的平均厚度。

[0050] 需要说明的是,形成各像素坑的像素界定层的厚度可以相同或不同,在此不做特别限定。

[0051] 如图3所示,在上述像素结构10的像素电极300上沉积功能薄膜400,该功能薄膜400可以为形成发光层、空穴注入层、空穴传输层、光发射层、电子传输层和电子注入层等的一层或多层薄膜,在此不做特别显示。当采用低温高真空凝固、升华的VCD工艺时,第一像素电极301上沉积的薄膜厚度 $T_1$ 与第二像素电极302上沉积的薄膜厚度 $T_2$ 之间的厚度比满足式(I):

$$[0052] T_1:T_2 = (C-A-B) / (C-B) = 1-A / (C-B) \quad \text{式 (I)}$$

[0053] 可理解,第一像素电极301上沉积的薄膜厚度 $T_1$ 与第二像素电极302上沉积的薄膜厚度 $T_2$ 之间的厚度比,等于第一像素电极301上与第二像素电极302上打印的墨水层的厚度比。从式(I)可以看出, $T_1$ 和 $T_2$ 之间的厚度差主要与像素电极的段差A,即沿垂直于衬底的方向,第一像素电极301和第二像素电极302之间的高度差,以及像素界定层200的厚度C相关。当像素界定层200的厚度C越大, $T_1$ 与 $T_2$ 就越接近。因此,可以通过大幅增加像素界定层的厚度,减小显示面板内pixel内像素电极段差造成的薄膜不均匀影响。

[0054] 在一实施例中, $C \geq 10A+B$ ,此时pixel内部的薄膜厚度差控制规格在10%以内。即像素界定层200的厚度要大于10倍段差加上像素电极的厚度,而常规像素结构,为了方便像素发光区的制备,通常将像素界定层的厚度限定在800nm-1500nm,相当于4-6倍段差左右,远小于本发明像素界定层的厚度。

[0055] 在一实施例中, $C \geq 20A+B$ ,此时pixel内部的薄膜厚度差控制规格在5%以内。即像素界定层的厚度要大于20倍段差加上像素电极的厚度,这远大于常规的像素界定层厚度。

[0056] 在一实施例中, $C \geq 33A+B$ ,此时pixel内部的薄膜厚度差控制规格在3%以内。

[0057] 在一实施例中, $40A \geq C \geq 10A+B$ ,以方便后续发光区的制备。在另一实施例中, $35A \geq C \geq 10A+B$ 。在另一实施例中, $33A \geq C \geq 20A+B$ 。在另一实施例中, $25A \geq C \geq 20A+B$ 。

[0058] 在一实施例中,像素电极采用ITO/Ag/ITO作为阳极,像素电极的厚度为140nm左右,像素电极的段差A控制在200nm左右,在此条件下,当像素界定层厚度为2.2μm以上时,像素坑内的功能膜层膜厚均匀性可控制在10%以内;当像素界定层厚度为4.2μm以上时,像素坑内的功能膜层膜厚均匀性可控制在5%以内;当像素界定层厚度为6.8μm以上时,像素坑内功能膜层膜厚均匀性可控制在3%以内。

[0059] 在一实施例中,像素电极的段差为190nm-210nm,该范围内的段差较易控制。

[0060] 在一实施例中,像素界定层的厚度为3.5-5μm。由于像素界定层采用涂布的方式沉积,沉积后需要通过光刻掩膜的方式得到像素发光区,故像素界定层不能太厚,否则在后续的曝光显影过程中存在残留;由于OLED的各功能层对厚度的敏感程度各异,故将像素界定层的厚度控制在3.5-5μm范围内不仅远大于常规像素界定层,能够给控制膜厚均匀性至少为5%,保证最终的显示效果较佳,还能通过一般的工艺制得,降低工艺流程、设备需求,降低生产成本。

[0061] 另外,可以如图1所示在像素电极300和衬底100之间设置有钝化层500,以方便调节像素电极的段差。

[0062] 一种像素结构100的制备方法,包括以下步骤:

[0063] S101:提供衬底。

[0064] 更具体地,获取包含TFT阵列的衬底基板。

[0065] S102:在衬底100上设置像素电极300,像素电极具有用于设置在像素坑内的第一段,且第一段的远离衬底100的一面为凹凸不平的非平面,第一段包括:沿垂直于衬底100的方向,离衬底100距离最近的第一位点和离衬底距离最近的第二位点,第一位点和第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于衬底100的方向,第一位点和衬底100之间的距离,d表示沿垂直于衬底100的方向,第二位点和衬底100之间的距离。

[0066] 如图2和图3所示,像素电极300的第一段分为两部分,第一像素电极301和第二像素电极302,其中第一像素电极301即为离衬底100距离最近的第一位点,第二像素电极302即为离衬底100距离最近的第二位点,即第一像素电极301的远离衬底100的一面和衬底100之间的距离为D,第二像素电极302的远离衬底100的一面和衬底之间的距离为d,像素电极的段差A为第一像素电极301和第二像素电极302之间的高度差 $D-d$ 。

[0067] 像素电极为本领域常规像素电极材料制备,可以透明像素电极,如ITO等;也可以是反射像素电极,如ITO/Ag/ITO等,可通过溅射的方式形成各像素电极。

[0068] S103:在衬底100上层叠像素界定层200,像素界定层200围合成像素坑201,且使像素电极300的至少部分区域露出于像素坑201。

[0069] 可以采用涂布的方法形成上述像素界定层200,并裸露出像素电极300的部分区域。

[0070] 其中,像素界定层满足以下公式:

[0071]  $40A \geq C \geq 10A+B$ ,其中,A表示像素电极的第一位点和第二位点之间的段差,B表示像素电极的厚度,C表示像素界定层的厚度。如此,可以通过调整像素界定层的厚度,减小显示面板内pixel内像素电极段差造成的薄膜不均匀影响。

[0072] 本发明一实施方式的有机发光二极管,包括像素结构和发光层,其中发光层层叠设置在像素结构的像素电极上。

[0073] 其中,像素结构包括:衬底、像素界定层和像素电极,其中像素界定层设于衬底上,像素界定层围合形成像素坑。像素电极设于衬底上,像素电极具有设置于像素坑内的第一段,且第一段远离衬底的一面为凹凸的非平面,第一段包括:沿垂直于衬底的方向,离衬底距离最近的第一位点和离衬底距离最近的第二位点,第一位点和第二位点之间的段差 $A=D-d$ ,其中,D表示沿垂直于衬底的方向,第一位点和衬底之间的距离,d表示沿垂直于衬底的方向,第二位点和衬底之间的距离;其中,像素界定层满足以下公式: $40A \geq C \geq 10A+B$ ,B表示像素电极的厚度,C表示像素界定层的厚度。

[0074] 发光层至少包括一层发光功能层,该发光功能层可以为有机发光层或钙钛矿发光层等。

[0075] 需要说明的是,有机发光二极管包括基板,阴极或阳极设置在衬底上。当阳极设置在衬底上时,有机发光二极管形成正置发光二极管;当阴极设置在衬底上时,有机发光二极管形成倒置发光二极管。

[0076] 在一些实施例中,有机发光二极管还包括用于电子功能层,电子功能层设置在阴极与发光层之间,其中,电子功能层包括电子注入层、电子传输层、空穴阻挡层中的至少一层。其中,电子注入层、电子传输层用于降低电子注入难度,空穴阻挡层用于阻挡过量的空

穴,使过量的空穴不能到达阴极形成漏电流,从而提高有机发光二极管的电流效率。

[0077] 另外,在一些实施例中,有机发光二极管还包括空穴功能层,空穴功能层设置在所述阳极与有机发光层之间,其中,空穴功能层包括空穴注入层、空穴传输层、电子阻挡层中的至少一层。其中,空穴注入层、空穴传输层用于降低空穴注入难度,电子阻挡层用于阻挡过量的电子,使过量的电子不能到达阳极形成漏电流,从而提高有机发光二极管的电流效率。

[0078] 本发明一发光器件的制备方法,包括以下步骤:

[0079] S201:如图4中a所示,提供像素结构。

[0080] 像素结构的制备方法如上所述,在此不再赘述。

[0081] S202:如图4中b所示,在像素结构的像素电极上制备发光层400。

[0082] 可以通过涂布或印刷的方法形成发光层的各功能层。具体地,步骤S202包括以下步骤:

[0083] S2021:将用于形成发光层的墨水20沉积至像素坑201内。

[0084] 如图5中a所示,将墨水沉积到像素坑201内后,由于表面张力的作用,会使得墨水液面高出像素坑201内,呈弧形,若此时直接采用低温高真空冷冻及升华工艺,最终像素坑201内部沉积的薄膜将呈现向上凸起的弧形,与墨水沉积的初始状态类似,薄膜均一性较差。

[0085] S2022:进行第一次干燥,至像素坑201内的墨水的液面与像素坑的边缘齐平。

[0086] 如图5中b所示,随着溶剂的挥发,凸起的部分会慢慢变平,随着溶剂的进一步挥发,由于墨水在像素坑201上部的钉扎作用,墨水边缘与像素坑201直接接触的部分液面由于钉扎不发生变化,而pixel1中间部分的墨水由于溶剂量的减少,同时在重力作用下会慢慢呈现下凹状。因此,通过对真空中度进行控制,使pixel1内部的液面与像素坑的边缘保持一致,从而使得像素电极上端各处的墨水量保持均匀一致。

[0087] 在一实施例中,在真空中度为20torr~100torr的条件下进行第一次干燥。在一优选实施例中,在真空中度为20torr~80torr的条件下进行第一次干燥。在进一步优选实施例中,在真空中度为20torr~60torr的条件下进行第一次干燥。

[0088] 此外,第一次干燥的时间无特别限定,可以根据所选用的溶剂进行控制,在一实施例中,干燥时间为100s~400s。在另一实施例中,干燥的时间为150s~350s。

[0089] 在步骤S2022中,可以采用一维真空中度干燥(one dimension)工艺,即VCD干燥工艺,来进行第一次干燥,采用该方法可以保证整个面板上溶剂挥发的均匀性,进而有利于形成与像素坑201的边缘齐平的墨水层。其中,一维真空中度干燥仪器通常由冷凝板和载体组成,其中载体用于承载基板,冷凝板用于冷却从基板上的墨水中挥发的溶剂。通过对冷凝板和载体的温度进行控制,来实现对蒸发速度的控制,进而控制油墨中间部位和边缘部位溶剂的挥发速度,实现薄膜的均匀化。在一实施例中,冷凝板的温度为5℃~15℃,载体的温度为20℃~30℃。在另一实施例中,冷凝板的温度为10℃,载体的温度为25℃。在一实施例中,载体和冷凝板之间的距离为1.5mm~50mm。

[0090] S2023:将像素坑201内的墨水20凝固。

[0091] 如图5中c所示,通过将像素坑201内的墨水凝固,防止墨水流动,从而不会出现边缘堆积现象,同时,由于此时墨水表面与像素坑201的边缘平齐,表面平整,因此干燥成膜后

因溶质未发生移动会形成非常平整的薄膜形态。

[0092] 在S2023的步骤中,在预设温度下等待预设时间,使像素坑内的墨水凝固。其中,预设温度和预设时间无特别限定,优选快速将像素坑内的墨水凝固,以防止液面变动。在一实施例中,预设温度为-50℃~-5℃,预设时间为100s~500s。

[0093] S2024:对经过凝固的墨水20进行第二次干燥,制得发光层400。

[0094] 如图5中d所示,由于此时墨水处于凝固状态,此时进行第二次干燥,则去除溶剂的过程中墨水不会发生流动,从而溶剂完全去除后,pixel像素电极上的溶质将会均匀沉积在像素电极上,同时也不会发生边缘堆积现象。

[0095] 其中,第二次干燥的条件无特别限定,可以根据溶剂种类进行选择,优选使溶剂直接升华的干燥条件。在一实施例中,第二次干燥的真空度为 $10^{-8}$ torr~ $10^{-4}$ torr,在该真空度下可以使残留的溶剂升华。由于此时墨水处于凝固状态不会发生流动,且液面与像素坑201的边缘齐平,墨水量均匀分布在像素电极的上端,即墨水上表面保持与像素电极平行,在此状态下通过控制真空度,使残留溶剂升华,可以使像素电极上均匀分布的溶质将均匀的沉积在像素电极上,且不会形成边缘堆积区,因此采用这个干燥方法将提升整个像素坑内201的薄膜均匀性,增大有效发光区面积。

[0096] 需要说明的是,在S2024步骤中,干燥时间和温度无特别限定,仅需能保持墨水呈凝固状态待到溶剂完全挥发为止即可。在一实施例中,第二次干燥的时间大于10s。

[0097] 需要说明的是,当发光层含有多层功能层时,选择合适的墨水重复上述步骤S2021~S2024即可。

[0098] 上述方法先通过调整像素界定层的厚度,减小像素电极段差所造成的成膜不均,然后再通过两次干燥形成发光层,进一步避免pixel内边缘堆积的现象,实现pixel内部边缘无堆积且沉积高度均匀的薄膜沉积,进而提升面板显示效果,特别是顶发射型显示面板。

[0099] 本发明另一实施方式的显示面板,包括有机发光二极管或上述制备方法制备而成的有机发光二极管。其中上述有机发光二极管或上述制备方法制备而成的有机发光二极管的结构及其功能与上述相同,在此不做赘述。该显示面板可以为任意显示装置的显示面板,例如:电脑显示屏、手机屏、平板、游戏机屏等。另外,该显示面板可以为顶发射型显示面板,其可以包含电容结构、薄膜晶体管结构等造成像素电极不平整的结构,还可以包括遮光层、缓冲层、钝化层等层级结构,根据需要进行选择,在此不做特别限定。

[0100] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0101] 以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

图1

图2

图3

图4

图5

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素结构、有机发光二极管及其制备方法                             |         |            |

| 公开(公告)号        | <a href="#">CN111192898A</a>                   | 公开(公告)日 | 2020-05-22 |

| 申请号            | CN201910243306.2                               | 申请日     | 2019-03-28 |

| [标]申请(专利权)人(译) | 广东聚华印刷显示技术有限公司                                 |         |            |

| 申请(专利权)人(译)    | 广东聚华印刷显示技术有限公司                                 |         |            |

| 当前申请(专利权)人(译)  | 广东聚华印刷显示技术有限公司                                 |         |            |

| [标]发明人         | 史文<br>陈亚文                                      |         |            |

| 发明人            | 史文<br>陈亚文                                      |         |            |

| IPC分类号         | H01L27/32 H01L51/52 H01L51/56                  |         |            |

| 代理人(译)         | 郑彤                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明涉及一种像素结构、有机发光二极管及其制备方法，该像素结构包括衬底；像素电极，设于衬底上，像素电极具有设置于像素坑内的第一段，且第一段远离衬底的一面为凹凸的非平面，第一段包括：表示沿垂直于衬底的方向，离衬底距离最远的第一位点和离衬底距离最近的第二位点，第一位点和第二位点之间的段差A=D-d，其中，D表示第一位点和衬底之间的距离，d表示第二位点和衬底之间的距离；像素界定层满足以下公式： $40A \geq C \geq 10A + B$ 其中，B表示像素电极的厚度，C表示像素界定层的厚度。上述像素结构能够有效地克服像素电极不同位置之间的段差所造成成膜不均的问题。