(12)发明专利申请

(10)申请公布号 CN 110675815 A

(43)申请公布日 2020.01.10

(21)申请号 201910918161.1

(22)申请日 2019.09.26

(71)申请人 武汉天马微电子有限公司

地址 430074 湖北省武汉市东湖新技术开发区东一产业园流芳园路8号

(72)发明人 郭亮亮 周井雄 厉天锐

(74)专利代理机构 北京晟睿智杰知识产权代理

事务所(特殊普通合伙)

11603

代理人 于淼

(51)Int.Cl.

G09G 3/3208(2016.01)

权利要求书4页 说明书13页 附图10页

(54)发明名称

像素驱动电路及其驱动方法、显示装置

(57)摘要

本发明公开了一种像素驱动电路及其驱动方法、显示装置，属于显示技术领域，像素驱动电路包括：第一发光控制模块、第二发光控制模块、驱动模块、第一数据写入模块、第二数据写入模块、第一初始化模块、复位模块、第一存储模块、有机发光元件、第一电源信号端、第二电源信号端、数据信号端、第一扫描信号端、第二扫描信号端、参考电压端、发光控制信号端、第一节点、第二节点和第三节点。本发明有效缓解了像素驱动电路中驱动模块存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。

1. 一种像素驱动电路，其特征在于，包括：第一发光控制模块、第二发光控制模块、驱动模块、第一数据写入模块、第二数据写入模块、第一初始化模块、复位模块、第一存储模块、有机发光元件、第一电源信号端、第二电源信号端、数据信号端、第一扫描信号端、第二扫描信号端、参考电压端、发光控制信号端、第一节点、第二节点和第三节点；

所述第一发光控制模块的控制端与所述发光控制信号端电连接，所述第一发光控制模块的第一端与所述第一电源信号端电连接，所述第一发光控制模块的第二端与所述第二节点电连接；

所述第二发光控制模块的控制端与所述发光控制信号端电连接，所述第二发光控制模块的第一端与所述第三节点电连接，所述第二发光控制模块的第二端与所述有机发光元件的阳极电连接；

所述驱动模块的控制端与所述第一节点电连接，所述驱动模块的第一端与所述第二节点电连接，所述驱动模块的第二端与所述第三节点电连接；

所述第一数据写入模块的控制端与所述第二扫描信号端电连接，所述第一数据写入模块的第一端与所述数据信号端电连接，所述第一数据写入模块的第二端与所述第二节点电连接；

所述第二数据写入模块的控制端与所述第二扫描信号端电连接，所述第二数据写入模块的第一端与所述第一节点电连接，所述第二数据写入模块的第二端与所述第三节点电连接；

所述第一初始化模块的控制端与所述第一扫描信号端电连接，所述第一初始化模块的第一端与所述参考电压端电连接，所述第一初始化模块的第二端与所述第一节点电连接；

所述复位模块的控制端与所述第一扫描信号端电连接，所述复位模块的第一端与所述第一电源信号端电连接，所述复位模块的第二端与所述第三节点电连接；

所述第一存储模块的第一端与所述第一电源信号端电连接，所述第一存储模块的第二端与所述第一节点电连接；

所述有机发光元件的阴极与所述第二电源信号端电连接。

2. 根据权利要求1所述的像素驱动电路，其特征在于，

所述第一发光控制模块包括第一晶体管，所述第一晶体管的栅极与所述发光控制信号端电连接，所述第一晶体管的第一极与所述第一电源信号端电连接，所述第一晶体管的第二极与所述第二节点电连接；

所述第一数据写入模块包括第二晶体管，所述第二晶体管的栅极与所述第二扫描信号端电连接，所述第二晶体管的第一极与所述数据信号端电连接，所述第二晶体管的第二极与所述第二节点电连接；

所述驱动模块包括第三晶体管，所述第三晶体管的栅极与所述第一节点电连接，所述第三晶体管的第一极与所述第二节点电连接，所述第三晶体管的第二极与所述第三节点电连接；

所述第二数据写入模块包括第四晶体管，所述第四晶体管的栅极与所述第二扫描信号端电连接，所述第四晶体管的第一极与所述第一节点电连接，所述第四晶体管的第二极与所述第三节点电连接；

所述第一初始化模块包括第五晶体管，所述第五晶体管的栅极与所述第一扫描信号端

电连接,所述第五晶体管的第一极与所述参考电压端电连接,所述第五晶体管的第二极与所述第一节点电连接;

所述第二发光控制模块包括第六晶体管,所述第六晶体管的栅极与所述发光控制信号端电连接,所述第六晶体管的第一极与所述第三节点电连接,所述第六晶体管的第二极与所述有机发光元件的阳极电连接;

所述复位模块包括第七晶体管,所述第七晶体管的栅极与所述第一扫描信号端电连接,所述第七晶体管的第一极与所述第一电源信号端电连接,所述第七晶体管的第二极与所述第三节点电连接;

所述第一存储模块包括第一电容,所述第一电容的第一端与所述第一电源信号端电连接,所述第一电容的第二端与所述第一节点电连接。

3.根据权利要求2所述的像素驱动电路,其特征在于,还包括第二初始化模块和第四节点,所述第二初始化模块的控制端与所述第一扫描信号端电连接,所述第二初始化模块的第一端与所述参考电压端电连接,所述第二初始化模块的第二端与所述第四节点电连接,所述第四节点与所述第二发光控制模块的第二端、所述有机发光元件的阳极电连接。

4.根据权利要求3所述的像素驱动电路,其特征在于,

所述第二初始化模块包括第八晶体管,所述第八晶体管的栅极与所述第一扫描信号端电连接,所述第八晶体管的第一极与所述参考电压端电连接,所述第八晶体管的第二极与所述第四节点电连接。

5.根据权利要求4所述的像素驱动电路,其特征在于,

所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管和所述第八晶体管均为P型晶体管。

6.根据权利要求4所述的像素驱动电路,其特征在于,还包括第二存储模块,所述第二存储模块的第一端与所述第二数据写入模块的第一端电连接,所述第二存储模块的第二端与所述第二数据写入模块的控制端电连接。

7.根据权利要求6所述的像素驱动电路,其特征在于,

所述第二存储模块包括第二电容,所述第二电容的第一端与所述第四晶体管的第一极电连接,所述第二电容的第二端与所述第四晶体管的栅极电连接。

8.一种像素驱动电路的驱动方法,其特征在于,所述驱动方法用于驱动权利要求1至7任一所述的驱动电路;所述驱动方法包括:

第一时段,所述参考电压端的信号通过所述第一初始化模块传输至所述第一节点,所述第一初始化模块用于实现所述第一节点的复位,所述第一电源信号端的信号通过所述复位模块传输至所述第三节点,所述第三节点的信号通过所述驱动模块传输至所述第二节点,所述复位模块用于实现所述第二节点和所述第三节点的复位;

第二时段,所述数据信号端的信号通过所述第一数据写入模块传输至所述第二节点,所述第二节点的信号通过所述驱动模块传输至所述第三节点,所述第三节点的信号通过所述第二数据写入模块传输至所述第一节点,所述第一存储模块用于实现所述第一节点的充电、抓取所述驱动模块的阈值电压;

第三时段,所述第一电源信号端的信号通过所述第一发光控制模块传输至所述第二节点,所述第二电源信号端的信号通过所述第二发光控制模块传输至所述第三节点,所述第

一存储模块用于补偿所述驱动模块的阈值电压，所述驱动模块用于生成驱动所述有机发光元件的驱动电流；

所述参考电压端的电压为负电压，所述第一电源信号端的电压为正电压。

9. 根据权利要求8所述像素驱动电路的驱动方法，其特征在于，

所述第一发光控制模块包括第一晶体管，所述第一晶体管的栅极与所述发光控制信号端电连接，所述第一晶体管的第一极与所述第一电源信号端电连接，所述第一晶体管的第二极与所述第二节点电连接；

所述第一数据写入模块包括第二晶体管，所述第二晶体管的栅极与所述第二扫描信号端电连接，所述第二晶体管的第一极与所述数据信号端电连接，所述第二晶体管的第二极与所述第二节点电连接；

所述驱动模块包括第三晶体管，所述第三晶体管的栅极与所述第一节点电连接，所述第三晶体管的第一极与所述第二节点电连接，所述第三晶体管的第二极与所述第三节点电连接；

所述第二数据写入模块包括第四晶体管，所述第四晶体管的栅极与所述第二扫描信号端电连接，所述第四晶体管的第一极与所述第一节点电连接，所述第四晶体管的第二极与所述第三节点电连接；

所述第一初始化模块包括第五晶体管，所述第五晶体管的栅极与所述第一扫描信号端电连接，所述第五晶体管的第一极与所述参考电压端电连接，所述第五晶体管的第二极与所述第一节点电连接；

所述第二发光控制模块包括第六晶体管，所述第六晶体管的栅极与所述发光控制信号端电连接，所述第六晶体管的第一极与所述第三节点电连接，所述第六晶体管的第二极与所述有机发光元件的阳极电连接；

所述复位模块包括第七晶体管，所述第七晶体管的栅极与所述第一扫描信号端电连接，所述第七晶体管的第一极与所述第一电源信号端电连接，所述第七晶体管的第二极与所述第三节点电连接；

所述第一存储模块包括第一电容，所述第一电容的第一端与所述第一电源信号端电连接，所述第一电容的第二端与所述第一节点电连接；

在所述第一时段，所述第五晶体管打开，所述参考电压端的信号传输至所述第一节点，所述第七晶体管打开，所述第一电源信号端的信号传输至所述第三节点，所述第三晶体管打开，所述第三节点的信号传输至所述第二节点；

在所述第二时段，所述第二晶体管打开，所述数据信号端的信号传输至所述第二节点，所述第三晶体管打开，所述第二节点的信号传输至所述第三节点，所述第四晶体管打开，所述第三节点的信号传输至所述第一节点，所述第一电容用于实现所述第一节点的充电、抓取所述第三晶体管的阈值电压；

在所述第三时段，所述第一晶体管打开，所述第一电源信号端的信号传输至所述第二节点，所述第六晶体管打开，所述第二电源信号端的信号传输至所述第三节点，所述第三晶体管打开，所述第一电容用于补偿所述第三晶体管的阈值电压，所述第三晶体管用于产生驱动所述有机发光元件的驱动电流。

10. 根据权利要求9所述的像素驱动电路的驱动方法，其特征在于，

所述第二电源信号端的电压为负电压，所述数据信号端的电压为正电压。

11. 根据权利要求9所述的像素驱动电路的驱动方法，其特征在于，

在所述第一时段，先关闭所述第一晶体管和所述第六晶体管，再打开所述第五晶体管和所述第七晶体管。

12. 根据权利要求9所述的像素驱动电路的驱动方法，其特征在于，

在所述第一时段切换至所述第二时段时，先关闭所述第五晶体管和所述第七晶体管，再打开所述第二晶体管和所述第四晶体管。

13. 根据权利要求9所述的像素驱动电路的驱动方法，其特征在于，

在所述第二时段切换至所述第三时段时，先关闭所述第二晶体管和所述第四晶体管，再打开所述第一晶体管和所述第六晶体管。

14. 一种显示装置，其特征在于，所述显示装置包括权利要求1-7任一项所述的像素驱动电路。

## 像素驱动电路及其驱动方法、显示装置

### 技术领域

[0001] 本发明涉及显示技术领域,更具体地,涉及一种像素驱动电路及其驱动方法、显示装置。

### 背景技术

[0002] 有机发光显示装置具有自发光、驱动电压低、发光效率高、响应速度快、轻薄、对比度高等优点,被认为是下一代最具有发展潜力显示装置。

[0003] 有机发光显示装置中的像素包括像素驱动电路,像素驱动电路中的驱动晶体管可产生驱动电流,发光元件响应该驱动电流而发光。现有的像素驱动电路中由于驱动晶体管存在阈值电压,从而使得有机显示装置在显示时存在迟滞现象和残影现象。

### 发明内容

[0004] 有鉴于此,本发明提供了一种像素驱动电路,包括:第一发光控制模块、第二发光控制模块、驱动模块、第一数据写入模块、第二数据写入模块、第一初始化模块、复位模块、第一存储模块、有机发光元件、第一电源信号端、第二电源信号端、数据信号端、第一扫描信号端、第二扫描信号端、参考电压端、发光控制信号端、第一节点、第二节点和第三节点;第一发光控制模块的控制端与发光控制信号端电连接,第一发光控制模块的第一端与第一电源信号端电连接,第一发光控制模块的第二端与第二节点电连接;第二发光控制模块的控制端与发光控制信号端电连接,第二发光控制模块的第一端与第三节点电连接,第二发光控制模块的第二端与有机发光元件的阳极电连接;驱动模块的控制端与第一节点电连接,驱动模块的第一端与第二节点电连接,驱动模块的第二端与第三节点电连接;第一数据写入模块的控制端与第二扫描信号端电连接,第一数据写入模块的第一端与数据信号端电连接,第一数据写入模块的第二端与第二节点电连接;第二数据写入模块的控制端与第二扫描信号端电连接,第二数据写入模块的第一端与第一节点电连接,第二数据写入模块的第二端与第三节点电连接;第一初始化模块的控制端与第一扫描信号端电连接,第一初始化模块的第一端与参考电压端电连接,第一初始化模块的第二端与第一节点电连接;复位模块的控制端与第一扫描信号端电连接,复位模块的第一端与第一电源信号端电连接,复位模块的第二端与第三节点电连接;第一存储模块的第一端与第一电源信号端电连接,第一存储模块的第二端与第一节点电连接;有机发光元件的阴极与第二电源信号端电连接。

[0005] 基于同一思想,本发明还提供了一种像素驱动电路的驱动方法,用于驱动上述像素驱动电路;驱动方法包括:第一时段,参考电压端的信号通过第一初始化模块传输至第一节点,第一初始化模块用于实现第一节点的复位,第一电源信号端的信号通过复位模块传输至第三节点,第三节点的信号通过驱动模块传输至第二节点,复位模块用于实现第二节点和第三节点的复位;第二时段,数据信号端的信号通过第一数据写入模块传输至第二节点,第二节点的信号通过驱动模块传输至第三节点,第三节点的信号通过第二数据写入模块传输至第一节点,第一存储模块用于实现第一节点的充电、抓取驱动模块的阈值电压;第

三时段，第一电源信号端的信号通过第一发光控制模块传输至第二节点，第二电源信号端的信号通过第二发光控制模块传输至第三节点，第一存储模块用于补偿驱动模块的阈值电压，驱动模块用于生成驱动有机发光元件的驱动电流；参考电压端的电压为负电压，第一电源信号端的电压为正电压。

[0006] 基于同一思想，本发明还提供了一种显示装置，包括上述像素驱动电路。

[0007] 与现有技术相比，本发明提供的像素驱动电路及其驱动方法、显示装置，至少实现了如下的有益效果：

[0008] 本发明提供的像素驱动电路，在第一时段，通过第一扫描信号端输入信号控制第一初始化模块的导通，通过第一初始化模块将参考电压端的信号传输至第一节点，实现第一节点的复位；通过第一扫描信号端输入信号控制复位模块的导通，通过复位模块将第一电源信号端的信号传输至第三节点，通过第一节点的信号控制驱动模块的导通，通过驱动模块将第三节点的信号传输至第二节点，实现第二节点和第三节点的复位。在第二时段，通过第一扫描信号端输入信号控制第一初始化模块和复位模块的关闭，通过第二扫描信号端输入信号控制第一数据写入模块和第二数据写入模块的导通，通过第一数据写入模块将数据信号端的信号传输至第二节点，通过驱动模块将第二节点的信号传输至第三节点，通过第二数据写入模块将第三节点的电位传输至第一节点，通过第一存储模块实现对第一节点的充电、对驱动模块的阈值的抓取。在第三时段，通过第二扫描信号端输入信号控制第一数据写入模块和第二数据写入模块的关闭，通过发光控制信号端输入信号控制第一发光控制模块和第二发光控制模块的导通，通过第一发光控制模块将第一电源信号端的信号传输至第二节点，通过第一存储模块实现对驱动模块的阈值的补偿，驱动模块形成驱动电流，通过第二发光控制模块使得驱动电流传输至有机发光元件的阳极，有机发光元件根据驱动电流发光。本实施例提供的像素驱动电路在第一时段对与驱动模块的控制端相连接的第一节点、与驱动模块的第一端相连接的第二节点和与驱动模块的第二端电连接的第三节点进行复位，可使得第一节点、第二节点和第三节点的电压在每一帧的第一时段均被复位在一个固定值上，可降低上一帧施加于第一节点、第二节点和第三节点的电压对下一帧第一节点、第二节点和第三节点的电压的影响，提高第二时段中第一存储模块对驱动模块的阈值的抓取的准确性，第一存储模块在第三时段根据在第二时段抓取的驱动模块的阈值对驱动模块的阈值进行补偿，有效缓解了像素驱动电路中驱动模块存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。

[0009] 第一初始化模块的控制端和复位模块的控制端均与第一扫描信号端电连接，在第一时段，通过第一扫描信号端输入信号控制第一初始化模块的导通，通过第一初始化模块将参考电压端的信号传输至第一节点，实现第一节点的复位；同时通过第一扫描信号端输入信号控制复位模块的导通，通过复位模块将第一电源信号端的信号传输至第三节点，通过第一节点的信号控制驱动模块的导通，通过驱动模块将第三节点的信号传输至第二节点，实现第二节点和第三节点的复位，使得通过第一扫描信号端可在第一时段同时实现第一节点、第二节点和第三节点的复位，无需另外设置信号线实现第二节点和第三节点的复位，也无需增加时间段实现第二节点和第三节点的复位，减少有机显示装置中的排线难度，同时减小有机显示装置中芯片的负载能力；复位模块的第一端与第一电源信号端电连接，可通过第一电源信号端的电位实现第二节点和第三节点的复位，无需另外设置信号线给第

二节点和第三节点提供信号,进一步减少有机显示装置中的排线难度。

[0010] 当然,实施本发明的任一产品不必特定需要同时达到以上所述的所有技术效果。

[0011] 通过以下参照附图对本发明的示例性实施例的详细描述,本发明的其它特征及其优点将会变得清楚。

## 附图说明

[0012] 被结合在说明书中并构成说明书的一部分的附图示出了本发明的实施例,并且连同其说明一起用于解释本发明的原理。

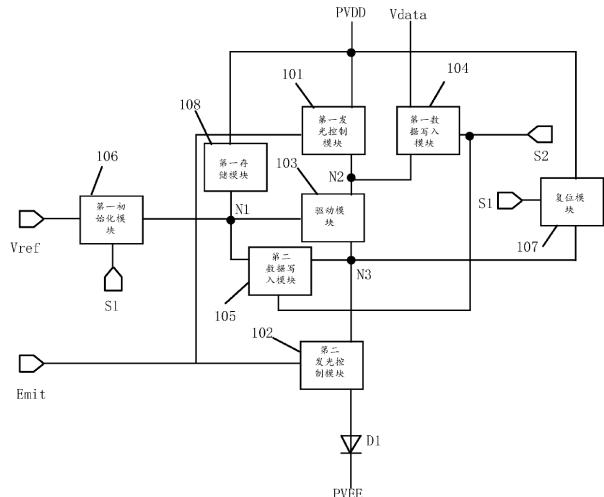

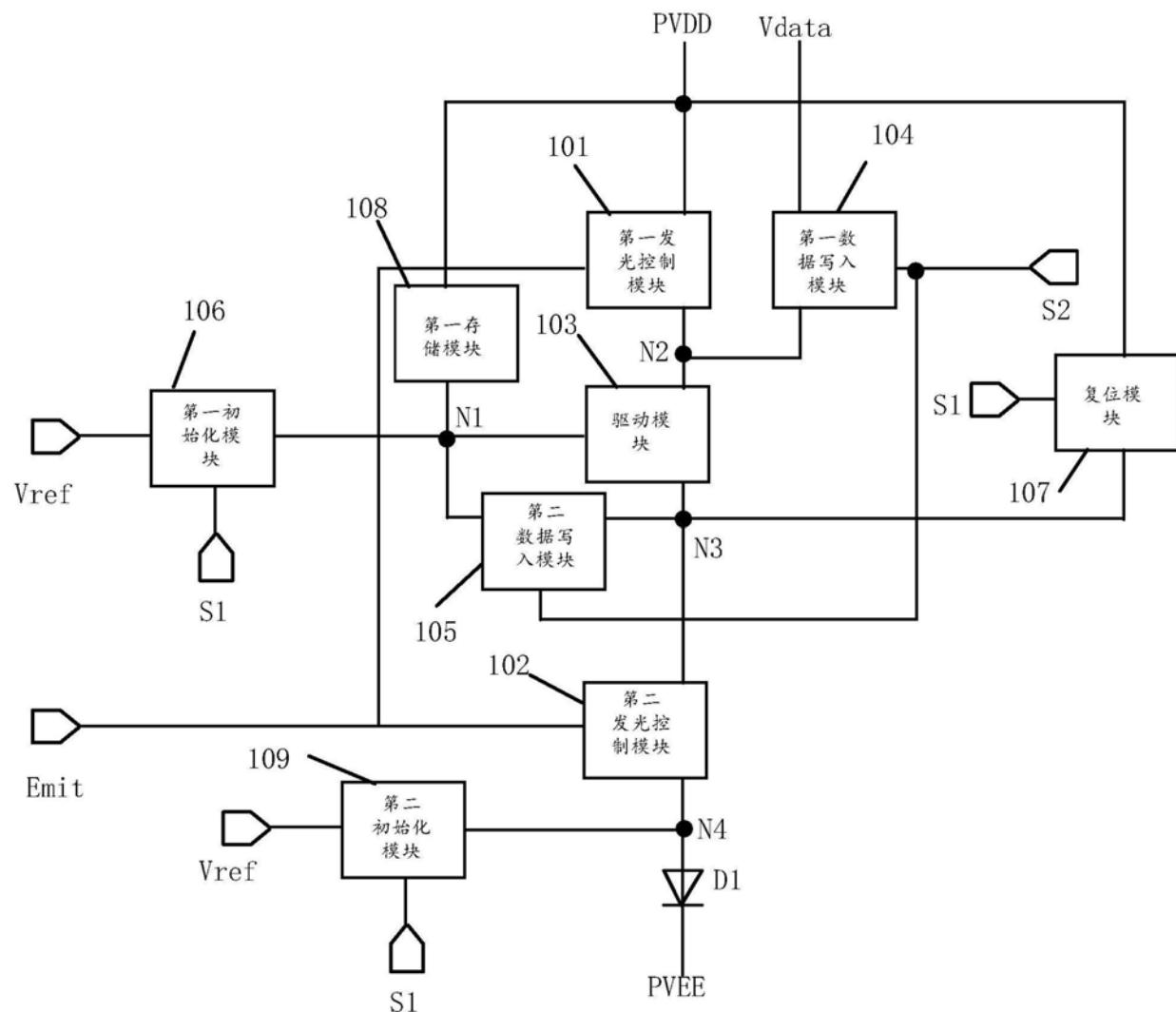

[0013] 图1是本发明提供的一种像素驱动电路的框架结构示意图;

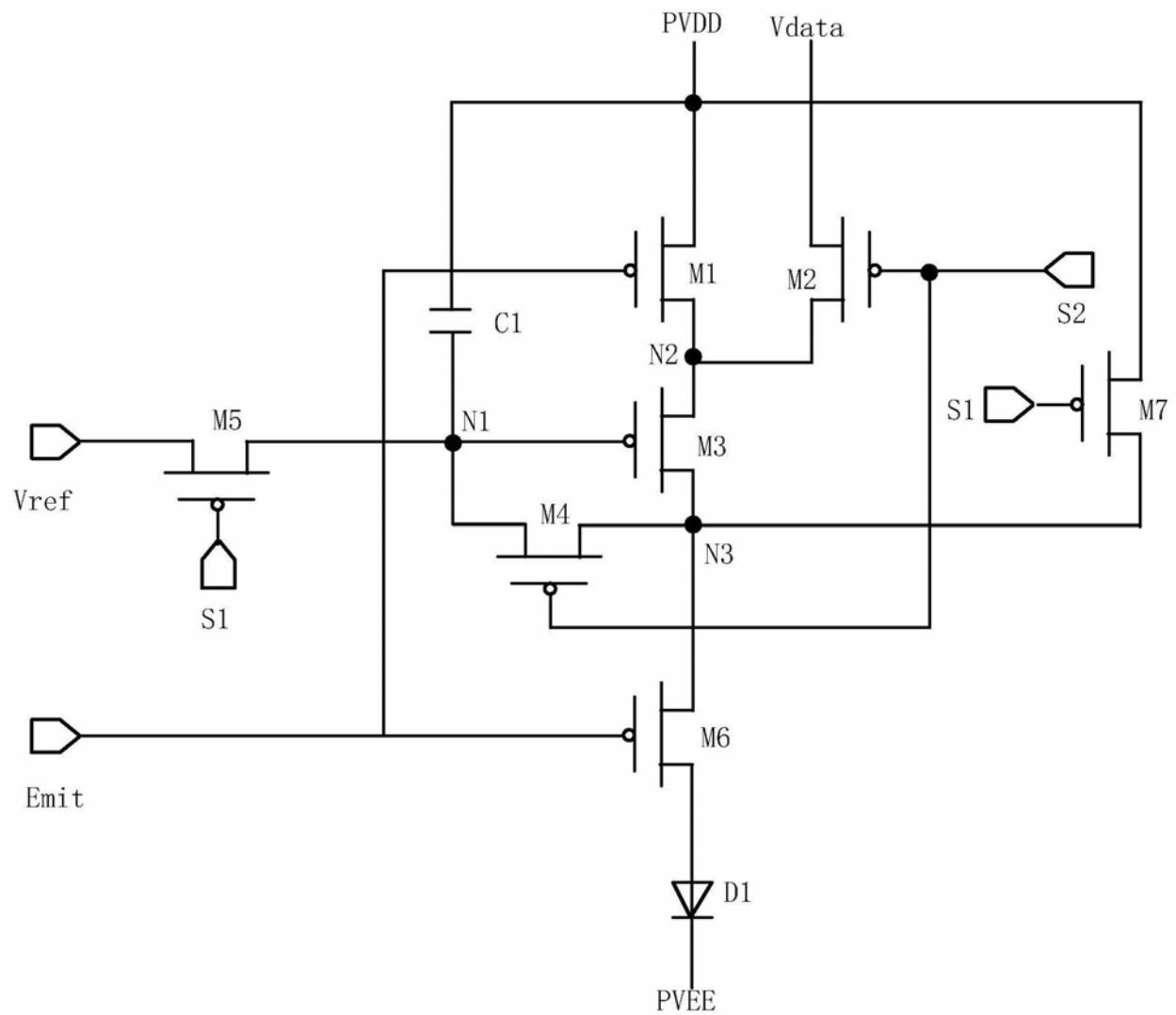

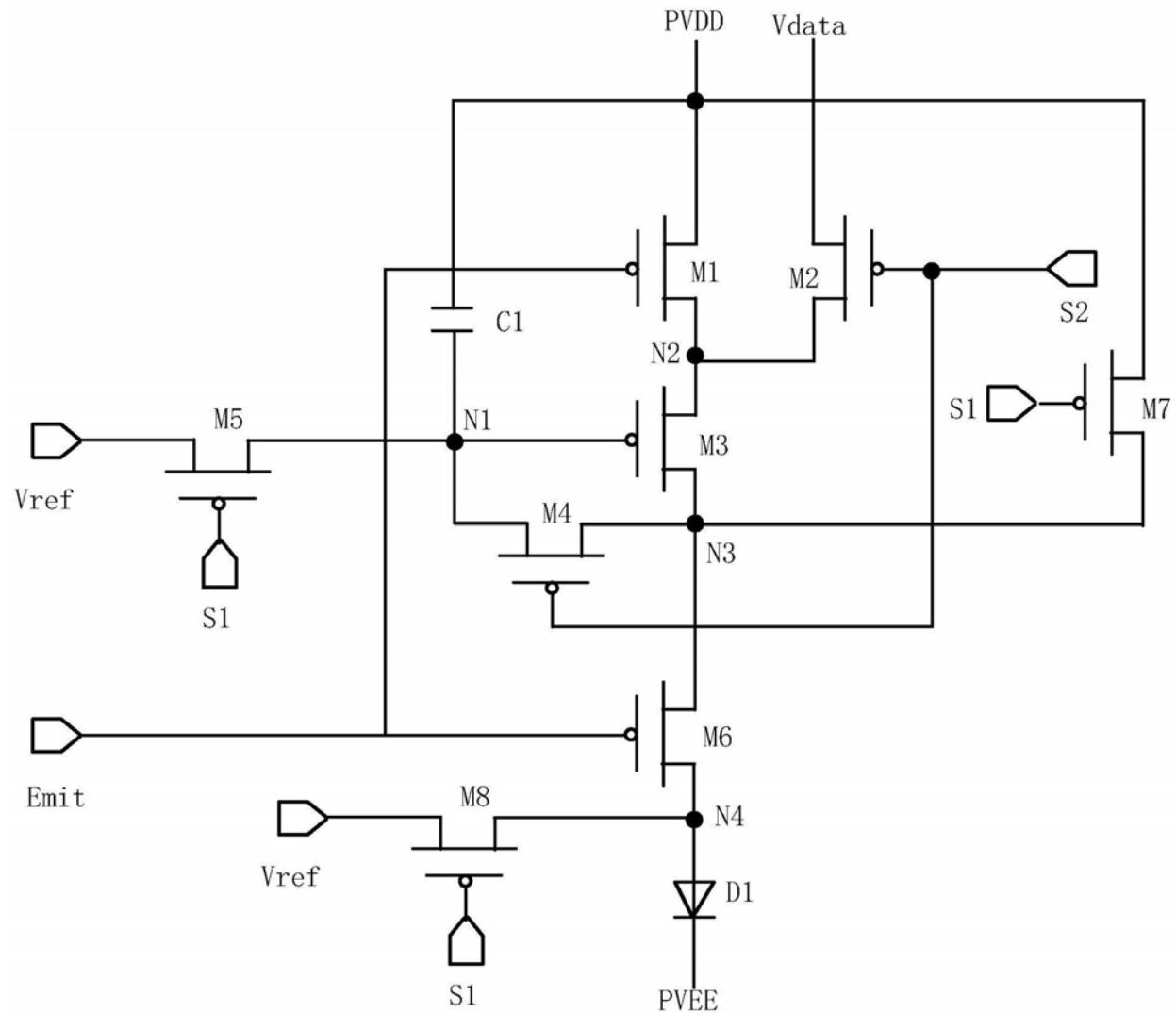

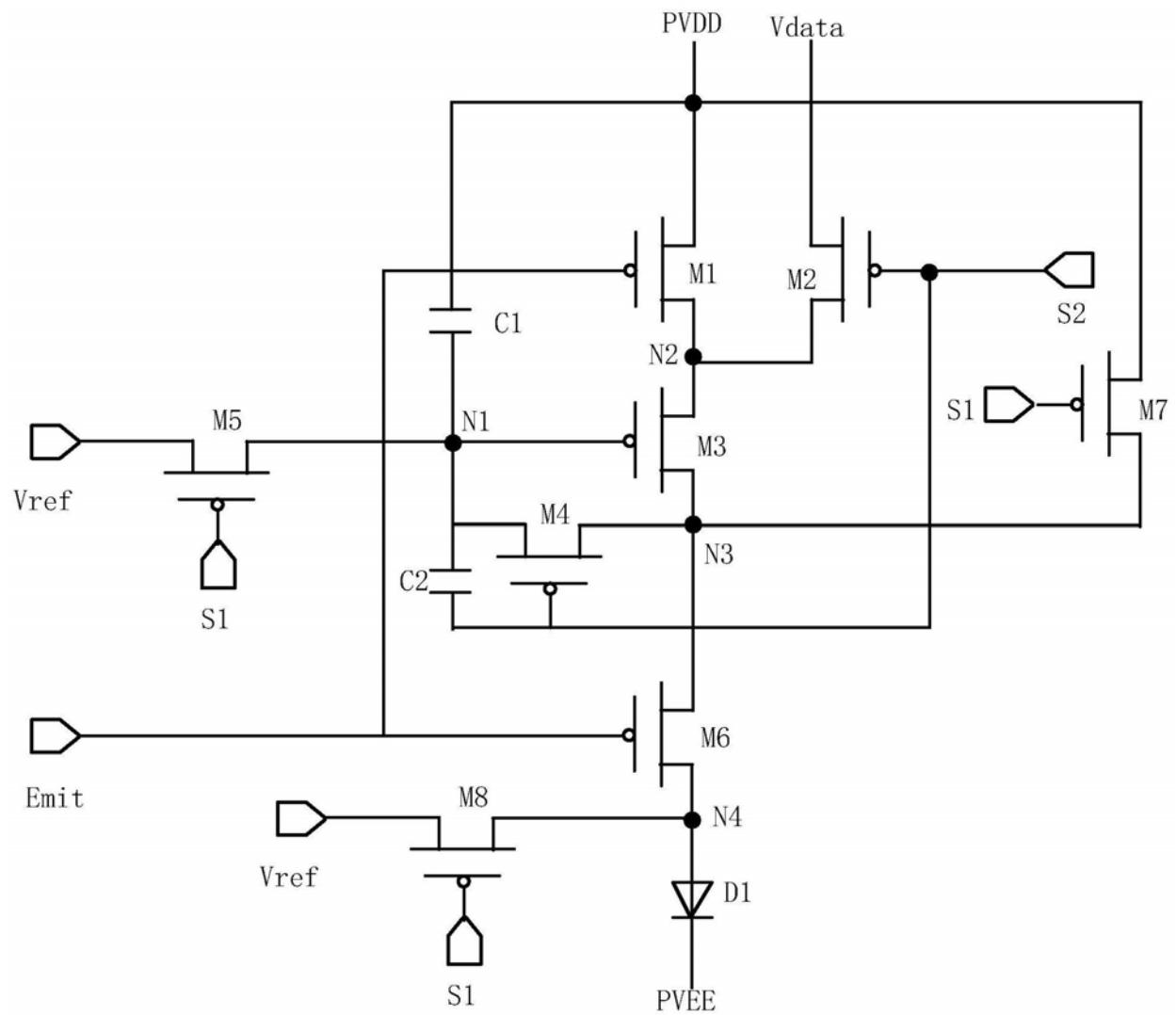

[0014] 图2是本发明提供的一种像素驱动电路的电路示意图;

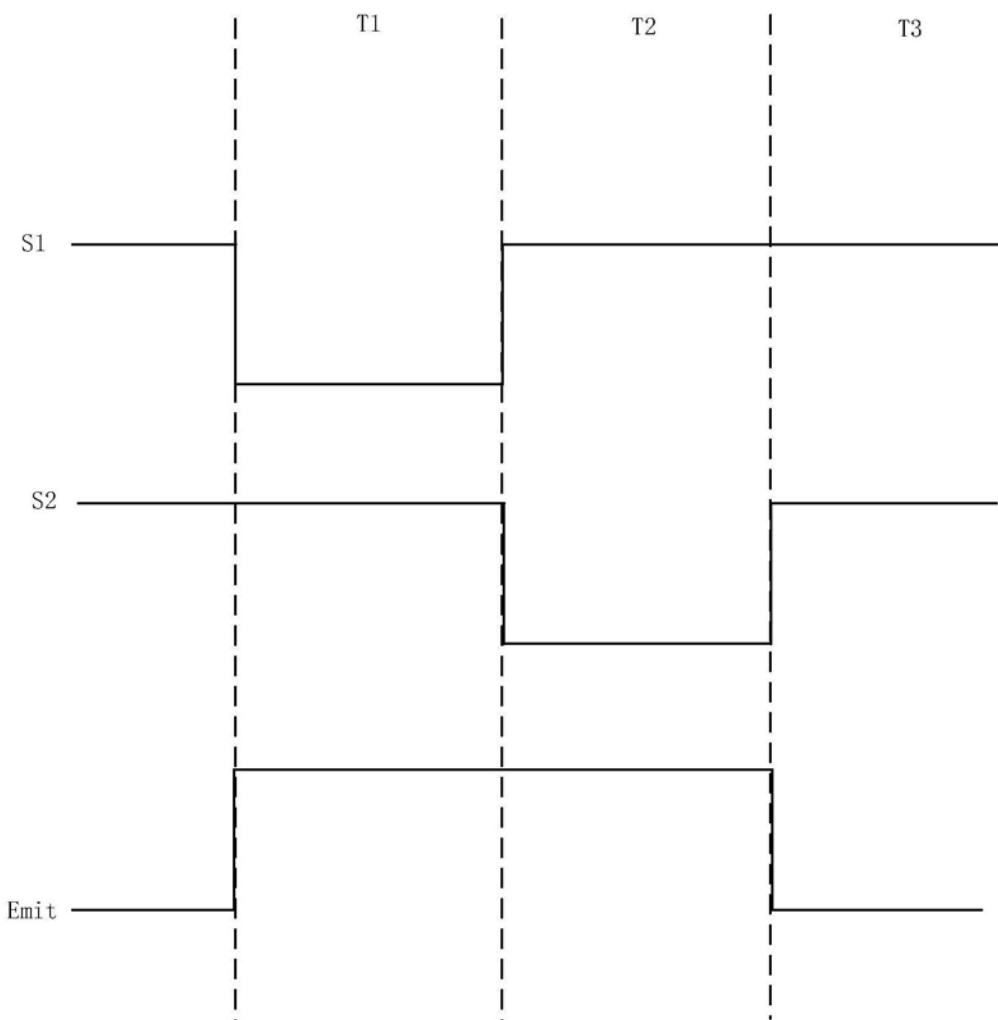

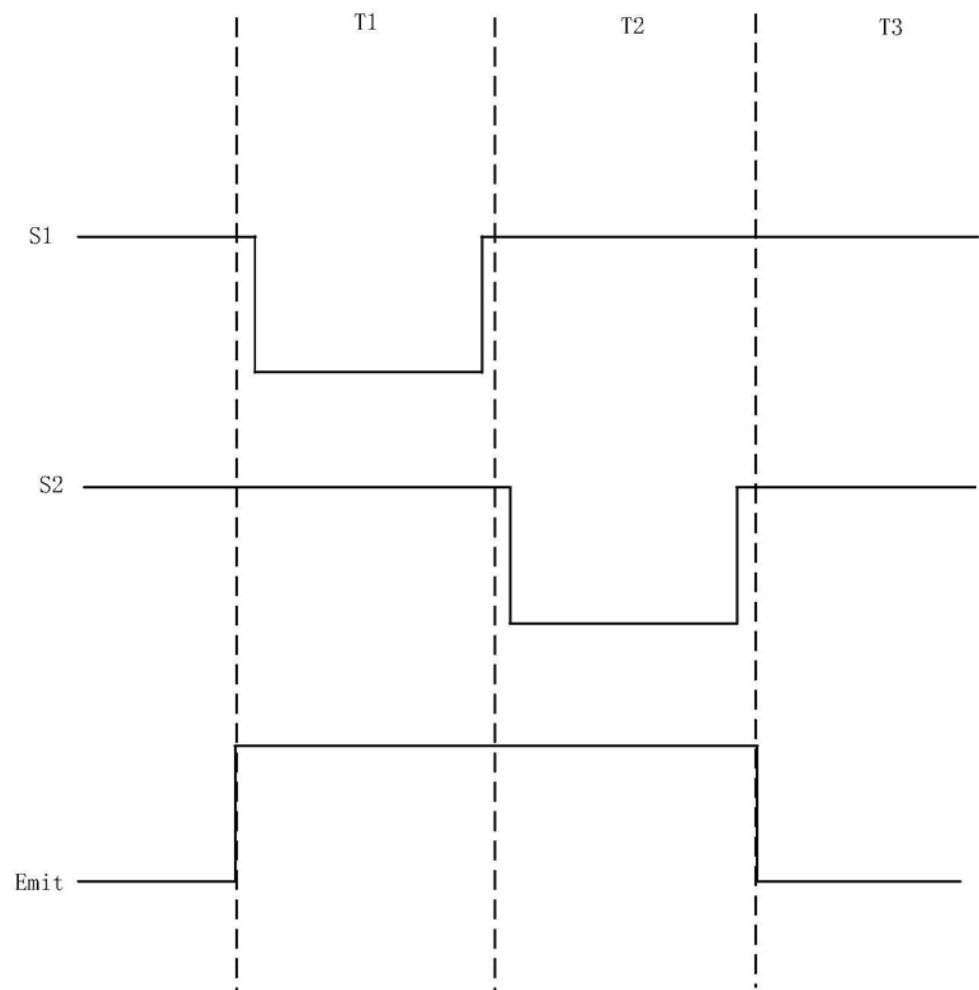

[0015] 图3是本发明提供的像素驱动电路的一种驱动时序图;

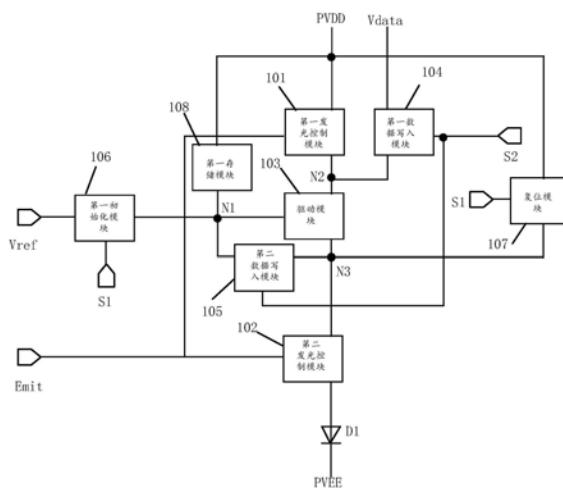

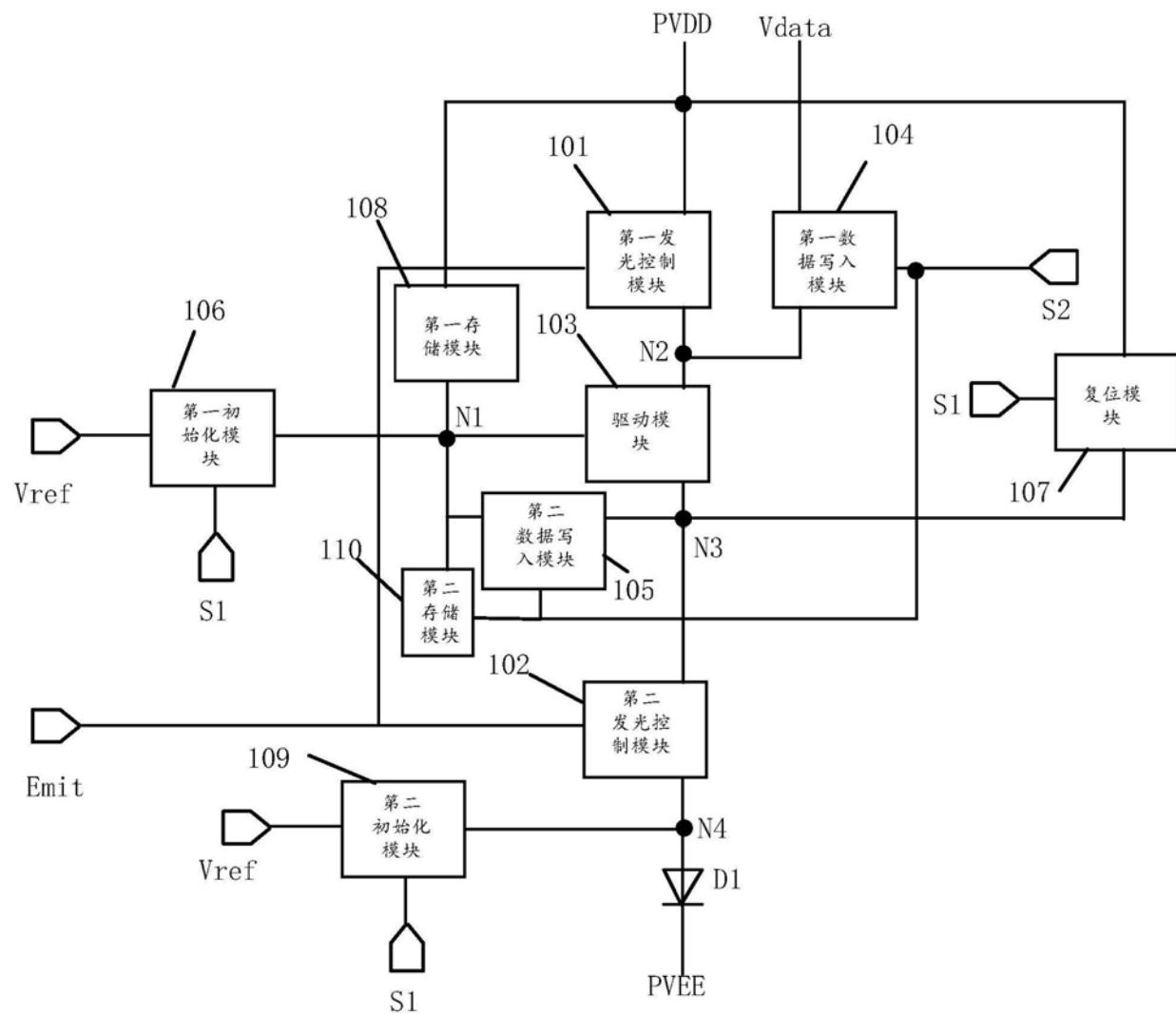

[0016] 图4是本发明提供的另一种像素驱动电路的框架结构示意图;

[0017] 图5是本发明提供的另一种像素驱动电路的电路示意图;

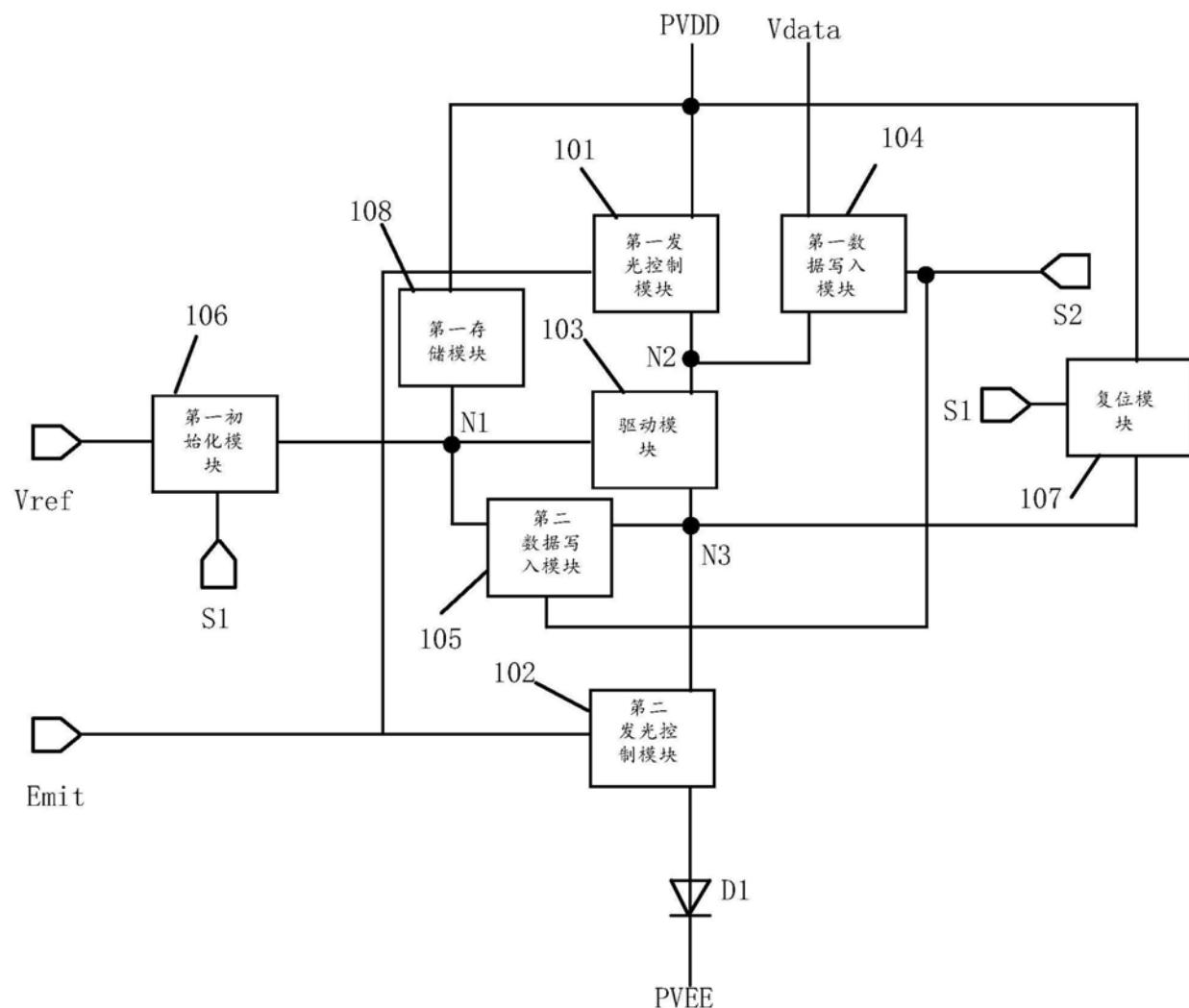

[0018] 图6是本发明提供的又一种像素驱动电路的框架结构示意图;

[0019] 图7是本发明提供的又一种像素驱动电路的电路示意图;

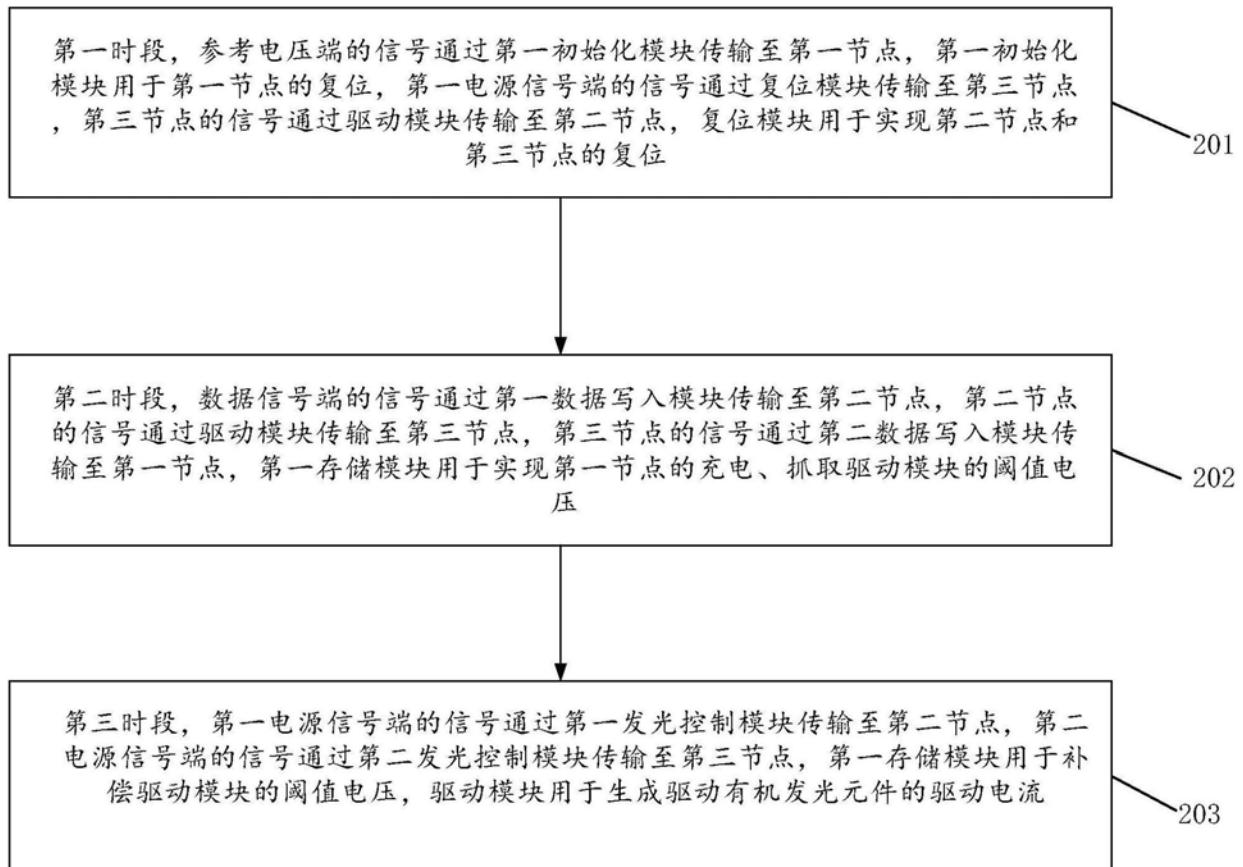

[0020] 图8是本发明提供的像素驱动电路的驱动方法的一种工作流程示意图;

[0021] 图9是本发明提供的像素驱动电路的另一种驱动时序图;

[0022] 图10是本发明提供的一种显示装置的平面结构示意图。

## 具体实施方式

[0023] 现在将参照附图来详细描述本发明的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本发明的范围。

[0024] 以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本发明及其应用或使用的任何限制。

[0025] 对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。

[0026] 在这里示出和讨论的所有例子中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它例子可以具有不同的值。

[0027] 应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

[0028] 图1是本发明提供的一种像素驱动电路的框架结构示意图,参考图1,本实施例提供一种像素驱动电路,包括:第一发光控制模块101、第二发光控制模块102、驱动模块103、第一数据写入模块104、第二数据写入模块105、第一初始化模块106、复位模块107、第一存储模块108、有机发光元件D1、第一电源信号端PVDD、第二电源信号端PVEE、数据信号端Vdata、第一扫描信号端S1、第二扫描信号端S2、参考电压端Vref、发光控制信号端Emit、第一节点N1、第二节点N2和第三节点N3;

[0029] 第一发光控制模块101的控制端与发光控制信号端Emit电连接,第一发光控制模块101的第一端与第一电源信号端PVDD电连接,第一发光控制模块101的第二端与第二节点

N2电连接；

[0030] 第二发光控制模块102的控制端与发光控制信号端Emi<sub>t</sub>电连接，第二发光控制模块102的第一端与第三节点N3电连接，第二发光控制模块102的第二端与有机发光元件D1的阳极电连接；

[0031] 驱动模块103的控制端与第一节点N1电连接，驱动模块103的第一端与第二节点N2电连接，驱动模块103的第二端与第三节点N3电连接；

[0032] 第一数据写入模块104的控制端与第二扫描信号端S2电连接，第一数据写入模块104的第一端与数据信号端Vdata电连接，第一数据写入模块104的第二端与第二节点N2电连接；

[0033] 第二数据写入模块105的控制端与第二扫描信号端S2电连接，第二数据写入模块105的第一端与第一节点N1电连接，第二数据写入模块105的第二端与第三节点N3电连接；

[0034] 第一初始化模块106的控制端与第一扫描信号端S1电连接，第一初始化模块106的第一端与参考电压端Vref电连接，第一初始化模块106的第二端与第一节点N1电连接；

[0035] 复位模块107的控制端与第一扫描信号端S1电连接，复位模块107的第一端与第一电源信号端PVDD电连接，复位模块107的第二端与第三节点N3电连接；

[0036] 第一存储模块108的第一端与第一电源信号端PVDD电连接，第一存储模块108的第二端与第一节点N1电连接；

[0037] 有机发光元件D1的阴极与第二电源信号端PVEE电连接。

[0038] 具体的，本实施例提供的像素驱动电路，在第一时段，通过第一扫描信号端S1输入信号控制第一初始化模块106的导通，通过第一初始化模块106将参考电压端Vref的信号传输至第一节点N1，实现第一节点N1的复位；通过第一扫描信号端S1输入信号控制复位模块107的导通，通过复位模块107将第一电源信号端PVDD的信号传输至第三节点N3，通过第一节点N1的信号控制驱动模块103的导通，通过驱动模块103将第三节点N3的信号传输至第二节点N2，实现第二节点N2和第三节点N3的复位。在第二时段，通过第一扫描信号端S1输入信号控制第一初始化模块106和复位模块107的关闭，通过第二扫描信号端S2输入信号控制第一数据写入模块104和第二数据写入模块105的导通，通过第一数据写入模块104将数据信号端Vdata的信号传输至第二节点N2，通过驱动模块103将第二节点N2的信号传输至第三节点N3，通过第二数据写入模块105将第三节点N3的电位传输至第一节点N1，通过第一存储模块108实现对第一节点N1的充电、对驱动模块103的阈值的抓取。在第三时段，通过第二扫描信号端S2输入信号控制第一数据写入模块104和第二数据写入模块105的关闭，通过发光控制信号端Emi<sub>t</sub>输入信号控制第一发光控制模块101和第二发光控制模块102的导通，通过第一发光控制模块101将第一电源信号端PVDD的信号传输至第二节点N2，通过第一存储模块108实现对驱动模块103的阈值的补偿，驱动模块103形成驱动电流，通过第二发光控制模块102使得驱动电流传输至有机发光元件D1的阳极，有机发光元件D1根据驱动电流发光。本实施例提供的像素驱动电路在第一时段对与驱动模块103的控制端相连接的第一节点N1、与驱动模块103的第一端相连接的第二节点N2和与驱动模块103的第二端电连接的第三节点N3进行复位，可使得第一节点N1、第二节点N2和第三节点N3的电压在每一帧的第一时段均被复位在一个固定值上，可降低上一帧施加于第一节点N1、第二节点N2和第三节点N3的电压对下一帧第一节点N1、第二节点N2和第三节点N3的电压的影响，提高第二时段中第一存

储模块108对驱动模块103的阈值的抓取的准确性,第一存储模块108在第三时段根据在第二时段抓取的驱动模块103的阈值对驱动模块103的阈值进行补偿,有效缓解了像素驱动电路中驱动模块103存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。

[0039] 第一初始化模块106的控制端和复位模块107的控制端均与第一扫描信号端S1电连接,在第一时段,通过第一扫描信号端S1输入信号控制第一初始化模块106的导通,通过第一初始化模块106将参考电压端Vref的信号传输至第一节点N1,实现第一节点N1的复位;同时通过第一扫描信号端S1输入信号控制复位模块107的导通,通过复位模块107将第一电源信号端PVDD的信号传输至第三节点N3,通过第一节点N1的信号控制驱动模块103的导通,通过驱动模块103将第三节点N3的信号传输至第二节点N2,实现第二节点N2和第三节点N3的复位,使得通过第一扫描信号端S1可在第一时段同时实现第一节点N1、第二节点N2和第三节点N3的复位,无需另外设置信号线实现第二节点N2和第三节点N3的复位,也无需增加时间段实现第二节点N2和第三节点N3的复位,减少有机显示装置中的排线难度,同时减小有机显示装置中芯片的负载能力;复位模块107的第一端与第一电源信号端PVDD电连接,可通过第一电源信号端PVDD的电位实现第二节点N2和第三节点N3的复位,无需另外设置信号线给第二节点N2和第三节点N3提供信号,进一步减少有机显示装置中的排线难度。

[0040] 图2是本发明提供的一种像素驱动电路的电路示意图,图3是本发明提供的像素驱动电路的一种驱动时序图,参考图2和图3,可选的,其中,第一发光控制模块101包括第一晶体管M1,第一晶体管M1的栅极与发光控制信号端Emit电连接,第一晶体管M1的第一极与第一电源信号端PVDD电连接,第一晶体管M1的第二极与第二节点N2电连接;

[0041] 第一数据写入模块104包括第二晶体管M2,第二晶体管M2的栅极与第二扫描信号端S2电连接,第二晶体管M2的第一极与数据信号端Vdata电连接,第二晶体管M2的第二极与第二节点N2电连接;

[0042] 驱动模块103包括第三晶体管M3,第三晶体管M3的栅极与第一节点N1电连接,第三晶体管M3的第一极与第二节点N2电连接,第三晶体管M3的第二极与第三节点N3电连接;

[0043] 第二数据写入模块105包括第四晶体管M4,第四晶体管M4的栅极与第二扫描信号端S2电连接,第四晶体管M4的第一极与第一节点N1电连接,第四晶体管M4的第二极与第三节点N3电连接;

[0044] 第一初始化模块106包括第五晶体管M5,第五晶体管M5的栅极与第一扫描信号端S1电连接,第五晶体管M5的第一极与参考电压端Vref电连接,第五晶体管M5的第二极与第一节点N1电连接;

[0045] 第二发光控制模块102包括第六晶体管M6,第六晶体管M6的栅极与发光控制信号端Emit电连接,第六晶体管M6的第一极与第三节点N3电连接,第六晶体管M6的第二极与有机发光元件D1的阳极电连接;

[0046] 复位模块107包括第七晶体管M7,第七晶体管M7的栅极与第一扫描信号端S1电连接,第七晶体管M7的第一极与第一电源信号端PVDD电连接,第七晶体管M7的第二极与第三节点N3电连接;

[0047] 第一存储模块108包括第一电容C1,第一电容C1的第一端与第一电源信号端PVDD电连接,第一电容C1的第二端与第一节点N1电连接。

[0048] 需要说明的，本实施例中晶体管可选的为薄膜晶体管，本实施例中所说的晶体管的第一极、第二极一者为晶体管的源极、一者为晶体管的漏极。

[0049] 可以理解的是，图2示例性的示出了以第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6和第七晶体管M7均为P型晶体管，在本发明其他实施例中，第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6和第七晶体管M7还可以为N型晶体管，本发明在此不再进行赘述。

[0050] 参考电压端Vref的电压为负电压，在第一时段T1对第一节点N1进行复位，通过第五晶体管M5为第三晶体管M3提供驱动信号。

[0051] 发光控制信号端Emit在第三时段T2为第一晶体管M1和第六晶体管M6提供驱动信号；

[0052] 本实施例进一步解释说明了第一发光控制模块101、第二发光控制模块102、驱动模块103、第一数据写入模块104、第二数据写入模块105、第一初始化模块106、复位模块107和第一存储模块108的具体结构以及电连接关系，第一发光控制模块101包括第一晶体管M1，第一数据写入模块104包括第二晶体管M2，驱动模块103包括第三晶体管M3，第二数据写入模块105包括第四晶体管M4，第一初始化模块106包括第五晶体管M5，第二发光控制模块102包括第六晶体管M6，复位模块107包括第七晶体管M7，第一存储模块108包括第一电容C1。

[0053] 本实施例的像素驱动电路具体工作时，请结合图2和图3。

[0054] 在第一时段T1，第一扫描信号端S1输入低电位信号至第五晶体管M5的栅极，第五晶体管M5导通，参考电压端Vref的信号通过第五晶体管M5传输至第一节点N1，实现第一节点N1的复位；第一扫描信号端S1输入低电位信号至第七晶体管M7的栅极，第七晶体管M7导通，第一电源信号端PVDD的信号通过第七晶体管M7传输至第三节点N3。由于第一节点N1的信号传输至第三晶体管M3的栅极，第一节点N1的信号为参考电压端Vref的信号，第三节点N3的信号为第一电源信号端PVDD的信号，参考电压端Vref的信号的电压值小于第一电源信号端PVDD的信号的电压值，且第一电源信号端PVDD的信号和参考电压端Vref的信号的电压差大于第三晶体管M3的阈值电压，从而第三晶体管M3导通，第三节点N3的信号通过第三晶体管M3传输至第二节点N2，同时实现第二节点N2和第三节点N3的复位。

[0055] 在第二时段T2，第一扫描信号端S1输入高电位信号至第五晶体管M5的栅极和第七晶体管M7的栅极，第五晶体管M5和第七晶体管M7关闭，第二扫描信号端S2输入低电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极，第二晶体管M2和第四晶体管M4导通，第一数据写入模块104将数据信号端Vdata的信号通过第二晶体管M2传输至第二节点N2，第二节点N2的信号通过第三晶体管M3传输至第三节点N3，第三节点N3的电位通过第四晶体管M4传输至第一节点N1，第一电容C1实现对第一节点N1的充电、对第三晶体管M3的阈值的抓取。

[0056] 在第三时段T3，第二扫描信号端S2输入高电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极，第二晶体管M2和第四晶体管M4关闭，发光控制信号端Emit输入低电位信号至第一晶体管M1的栅极和第六晶体管M6的栅极，第一晶体管M1和第六晶体管M6导通，第一电源信号端PVDD的信号通过第一晶体管M1传输至第二节点N2，第一电容C1实现对第三晶体管M3的阈值的补偿，第三晶体管M3形成驱动电流，通过第六晶体管M6使得驱动电流传输至有机发光元件D1的阳极，有机发光元件D1根据驱动电流发光。

[0057] 本实施例提供的像素驱动电路在第一时段T1对与第三晶体管M3的栅极相连接的第一节点N1、与第三晶体管M3的第一极相连接的第二节点N2和与第三晶体管M3的第二极电连接的第三节点N3进行复位,可使得第一节点N1、第二节点N2和第三节点N3的电压在每一帧的第一时段T1均被复位在一个固定值上,可降低上一帧施加于第一节点N1、第二节点N2和第三节点N3的电压对下一帧第一节点N1、第二节点N2和第三节点N3的电压的影响,提高第二时段T2中第一电容C1对驱动模块103的阈值的抓取的准确性,第一电容C1在第三时段T3根据在第二时段T2抓取的第三晶体管M3的阈值对第三晶体管M3的阈值进行补偿,有效缓解了像素驱动电路中第三晶体管M3存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。

[0058] 图4是本发明提供的另一种像素驱动电路的框架结构示意图,参考图4,可选的,像素驱动电路还包括第二初始化模块109和第四节点N4,第二初始化模块109的控制端与第一扫描信号端S1电连接,第二初始化模块109的第一端与参考电压端Vref电连接,第二初始化模块109的第二端与第四节点N4电连接,第四节点N4与第二发光控制模块102的第二端、有机发光元件D1的阳极电连接。

[0059] 具体的,本实施例提供的像素驱动电路,在第一时段,通过第一扫描信号端S1输入信号控制第二初始化模块109的导通,通过第二初始化模块109将参考电压端Vref的信号传输至第四节点N4,实现第四节点N4的复位,可使得第四节点N4的电压在每一帧的第一时段被复位在一个固定值上,可降低上一帧施加于第四节点N4的电压对下一帧第四节点N4的电压的影响,有效避免上一帧施加于第四节点N4的电压造成有机发光元件D1在下一帧的第一时段发光。

[0060] 第一初始化模块106的控制端、复位模块107的控制端和第二初始化模块109的控制端均与第一扫描信号端S1电连接,在第一时段,通过第一扫描信号端S1输入信号控制第一初始化模块106的导通,通过第一初始化模块106将参考电压端Vref的信号传输至第一节点N1,实现第一节点N1的复位;同时通过第一扫描信号端S1输入信号控制复位模块107的导通,通过复位模块107将第一电源信号端PVDD的信号传输至第三节点N3,通过第一节点N1的信号控制驱动模块103的导通,通过驱动模块103将第三节点N3的信号传输至第二节点N2,实现第二节点N2和第三节点N3的复位;同时通过第一扫描信号端S1输入信号控制第二初始化模块109的导通,通过第二初始化模块109将参考电压端Vref的信号传输至第四节点N4,实现第四节点N4的复位,使得通过第一扫描信号端S1可在第一时段同时实现第一节点N1、第二节点N2、第三节点N3和第四节点N4的复位,无需另外设置信号线控制第二初始化模块109的导通实现第四节点N4的复位,有效简化像素驱动电路,也无需增加时间段实现第四节点N4的复位,进一步减少有机显示装置中的排线难度,且进一步减小有机显示装置中芯片的负载能力。

[0061] 图5是本发明提供的另一种像素驱动电路的电路示意图,参考图3和图5,可选的,其中,第二初始化模块109包括第八晶体管M8,第八晶体管M8的栅极与第一扫描信号端S1电连接,第八晶体管M8的第一极与参考电压端Vref电连接,第八晶体管M8的第二极与第四节点N4电连接。

[0062] 本实施例进一步解释说明了第二初始化模块109的具体结构以及电连接关系,第二初始化模块109包括第八晶体管M8。

[0063] 本实施例的像素驱动电路具体工作时,在第一时段T1,第一扫描信号端S1输入低电位信号至第八晶体管M8的栅极,第八晶体管M8导通,参考电压端Vref的信号通过第八晶体管M8传输至第四节点N4,实现第四节点N4的复位,有效避免有机发光元件D1在第一时段T1发光。

[0064] 继续参考图5,可选的,其中,第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6、第七晶体管M7和第八晶体管M8均为P型晶体管。

[0065] 需要说明的是,图3示例性的示出了以第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6、第七晶体管M7和第八晶体管M8均为P型晶体管时的驱动时序图,一般P型晶体管在低电平信号的控制下导通,在高电平信号的控制下截止。在一些可选实施例中,第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6、第七晶体管M7和第八晶体管M8也可均为N型晶体管,一般N型晶体管在高电平信号的控制下导通,在低电平信号的控制下截止,此时,本实施例中对应的驱动时序也将发生相应变化,在此不作赘述。

[0066] 图6是本发明提供的又一种像素驱动电路的框架结构示意图,参考图6,可选的,像素驱动电路还包括第二存储模块110,第二存储模块110的第一端与第二数据写入模块105的第一端电连接,第二存储模块110的第二端与第二数据写入模块105的控制端电连接。

[0067] 具体的,在像素驱动电路的制作过程中,由于生产工艺的原因,像素驱动电路中通常存在第二存储模块110。

[0068] 图7是本发明提供的又一种像素驱动电路的电路示意图,参考图3和图7,可选的,其中,第二存储模块110包括第二电容C2,第二电容C2的第一端与第四晶体管M4的第一极电连接,第二电容C2的第二端与第四晶体管M4的栅极电连接。

[0069] 具体的,在第一时段T1,第二扫描信号端S2为高电位信号,第一节点N1为参考电压端Vref的电位信号,即第二电容C2的第一端为参考电压端Vref的电位信号,第二电容C2的第二端为第二扫描信号端S2的高电位信号,在第二时段T2,第二扫描信号端S2为低电位信号,第一节点N1为第三节点N3的电位,第二电容C2的存在会影响第一节点N1的电位,影响对第三晶体管M3的阈值的抓取,因此,在实际生产过程中,第二电容C2设置的越小越好。

[0070] 图8是本发明提供的像素驱动电路的驱动方法的一种工作流程示意图,参考图1和图8,本实施例提供一种像素驱动电路的驱动方法,用于上述实施例中的像素驱动电路;驱动方法包括:

[0071] 步骤201、第一时段,参考电压端的信号通过第一初始化模块传输至第一节点,第一初始化模块用于第一节点的复位,第一电源信号端的信号通过复位模块传输至第三节点,第三节点的信号通过驱动模块传输至第二节点,复位模块用于实现第二节点和第三节点的复位;

[0072] 步骤202、第二时段,数据信号端的信号通过第一数据写入模块传输至第二节点,第二节点的信号通过驱动模块传输至第三节点,第三节点的信号通过第二数据写入模块传输至第一节点,第一存储模块用于实现第一节点的充电、抓取驱动模块的阈值电压;

[0073] 步骤203、第三时段,第一电源信号端的信号通过第一发光控制模块传输至第二节点,第二电源信号端的信号通过第二发光控制模块传输至第三节点,第一存储模块用于补偿驱动模块的阈值电压,驱动模块用于生成驱动有机发光元件的驱动电流;

[0074] 其中,参考电压端的电压为负电压,第一电源信号端的电压为正电压。

[0075] 具体的,本实施例进一步解释说明了上述实施例中的像素驱动电路的驱动方法,该驱动方法包括至少三个步骤:

[0076] 步骤201、在第一时段,通过第一扫描信号端S1输入信号控制第一初始化模块106的导通,通过第一初始化模块106将参考电压端Vref的信号传输至第一节点N1,实现第一节点N1的复位;通过第一扫描信号端S1输入信号控制复位模块107的导通,通过复位模块107将第一电源信号端PVDD的信号传输至第三节点N3,通过第一节点N1的信号控制驱动模块103的导通,通过驱动模块103将第三节点N3的信号传输至第二节点N2,实现第二节点N2和第三节点N3的复位;

[0077] 步骤202、在第二时段,通过第一扫描信号端S1输入信号控制第一初始化模块106和复位模块107的关闭,通过第二扫描信号端S2输入信号控制第一数据写入模块104和第二数据写入模块105的导通,通过第一数据写入模块104将数据信号端Vdata的信号传输至第二节点N2,通过驱动模块103将第二节点N2的信号传输至第三节点N3,通过第二数据写入模块105将第三节点N3的电位传输至第一节点N1,通过第一存储模块108实现对第一节点N1的充电、对驱动模块103的阈值的抓取;

[0078] 步骤203、在第三时段,通过第二扫描信号端S2输入信号控制第一数据写入模块104和第二数据写入模块105的关闭,通过发光控制信号端Emit输入信号控制第一发光控制模块101和第二发光控制模块102的导通,通过第一发光控制模块101将第一电源信号端PVDD的信号传输至第二节点N2,通过第一存储模块108实现对驱动模块103的阈值的补偿,驱动模块103形成驱动电流,通过第二发光控制模块102使得驱动电流传输至有机发光元件D1的阳极,有机发光元件D1根据驱动电流发光。

[0079] 继续参考图2、图3和图8,可选的,其中,第一发光控制模块101包括第一晶体管M1,第一晶体管M1的栅极与发光控制信号端Emit电连接,第一晶体管M1的第一极与第一电源信号端PVDD电连接,第一晶体管M1的第二极与第二节点N2电连接;

[0080] 第一数据写入模块104包括第二晶体管M2,第二晶体管M2的栅极与第二扫描信号端S2电连接,第二晶体管M2的第一极与数据信号端Vdata电连接,第二晶体管M2的第二极与第二节点N2电连接;

[0081] 驱动模块103包括第三晶体管M3,第三晶体管M3的栅极与第一节点N1电连接,第三晶体管M3的第一极与第二节点N2电连接,第三晶体管M3的第二极与第三节点N3电连接;

[0082] 第二数据写入模块105包括第四晶体管M4,第四晶体管M4的栅极与第二扫描信号端S2电连接,第四晶体管M4的第一极与第一节点N1电连接,第四晶体管M4的第二极与第三节点N3电连接;

[0083] 第一初始化模块106包括第五晶体管M5,第五晶体管M5的栅极与第一扫描信号端S1电连接,第五晶体管M5的第一极与参考电压端Vref电连接,第五晶体管M5的第二极与第一节点N1电连接;

[0084] 第二发光控制模块102包括第六晶体管M6,第六晶体管M6的栅极与发光控制信号端Emit电连接,第六晶体管M6的第一极与第三节点N3电连接,第六晶体管M6的第二极与有机发光元件D1的阳极电连接;

[0085] 复位模块107包括第七晶体管M7,第七晶体管M7的栅极与第一扫描信号端S1电连

接,第七晶体管M7的第一极与第一电源信号端PVDD电连接,第七晶体管M7的第二极与第三节点N3电连接;

[0086] 第一存储模块108包括第一电容C1,第一电容C1的第一端与第一电源信号端PVDD电连接,第一电容C1的第二端与第一节点N1电连接;

[0087] 在第一时段T1,第五晶体管M5打开,参考电压端Vref的信号传输至第一节点N1,第七晶体管M7打开,第一电源信号端PVDD的信号传输至第三节点N3,第三晶体管M3打开,第三节点N3的信号传输至第二节点N2;

[0088] 在第二时段T2,第二晶体管M2打开,数据信号端Vdata的信号传输至第二节点N2,第三晶体管M3打开,第二节点N2的信号传输至第三节点N3,第四晶体管M4打开,第三节点N3的信号传输至第一节点N1,第一电容C1用于实现第一节点N1的充电、抓取第三晶体管M3的阈值电压;

[0089] 在第三时段T3,第一晶体管M1打开,第一电源信号端PVDD的信号传输至第二节点N2,第六晶体管M6打开,第二电源信号端PVEE的信号传输至第三节点N3,第三晶体管M3打开,第一电容C1用于补偿第三晶体管M3的阈值电压,第三晶体管M3用于产生驱动有机发光元件D1的驱动电流。

[0090] 本实施例的像素驱动电路具体工作时,步骤201具体为:在第一时段T1,第一扫描信号端S1输入低电位信号至第五晶体管M5的栅极,第五晶体管M5导通,参考电压端Vref的信号通过第五晶体管M5传输至第一节点N1,实现第一节点N1的复位;第一扫描信号端S1输入低电位信号至第七晶体管M7的栅极,第七晶体管M7导通,第一电源信号端PVDD的信号通过第七晶体管M7传输至第三节点N3,参考电压端Vref的电压为负电压,第一节点N1的负电压信号传输至第三晶体管M3的栅极,第三晶体管M3导通,第三节点N3的信号通过第三晶体管M3传输至第二节点N2,同时实现第二节点N2和第三节点N3的复位。

[0091] 步骤202具体为:在第二时段T2,第一扫描信号端S1输入高电位信号至第五晶体管M5的栅极和第七晶体管M7的栅极,第五晶体管M5和第七晶体管M7关闭,第二扫描信号端S2输入低电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极,第二晶体管M2和第四晶体管M4导通,第一数据写入模块104将数据信号端Vdata的信号通过第二晶体管M2传输至第二节点N2,第二节点N2的信号通过第三晶体管M3传输至第三节点N3,第三节点N3的电位通过第四晶体管M4传输至第一节点N1,第一电容C1实现对第一节点N1的充电、对第三晶体管M3的阈值的抓取。

[0092] 步骤203具体为:在第三时段T3,第二扫描信号端S2输入高电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极,第二晶体管M2和第四晶体管M4关闭,发光控制信号端Emi<sub>t</sub>输入低电位信号至第一晶体管M1的栅极和第六晶体管M6的栅极,第一晶体管M1和第六晶体管M6导通,第一电源信号端PVDD的信号通过第一晶体管M1传输至第二节点N2,第一电容C1实现对第三晶体管M3的阈值的补偿,第三晶体管M3形成驱动电流,通过第六晶体管M6使得驱动电流传输至有机发光元件D1的阳极,有机发光元件D1根据驱动电流发光。

[0093] 可选的,其中,第二电源信号端PVEE的电压为负电压,数据信号端Vdata的电压为正电压。

[0094] 具体的,在第二时段T2,第一数据写入模块104将数据信号端Vdata的信号通过第二晶体管M2传输至第二节点N2,数据信号端Vdata的电压为正电压,第二节点N2的信号通过

第三晶体管M3传输至第三节点N3，第三节点N3的电位通过第四晶体管M4传输至第一节点N1，第一电容C1实现对第一节点N1的充电，在第三时段T3，第一电源信号端PVDD的信号通过第一晶体管M1传输至第二节点N2，第一电源信号端PVDD的电压为正电压，第二电源信号端PVEE的电压为负电压，第三晶体管M3形成驱动电流，通过第六晶体管M6使得驱动电流传输至有机发光元件D1的阳极，有机发光元件D1根据驱动电流发光。

[0095] 图9是本发明提供的像素驱动电路的另一种驱动时序图，参考图2、图8和图9，可选的，其中，在第一时段T1，先关闭第一晶体管M1和第六晶体管M6，再打开第五晶体管M5和第七晶体管M7。

[0096] 具体的，在第一时段T1，先通过发光控制信号端Emi<sub>t</sub>输入高电位信号至第一晶体管M1的栅极和第六晶体管M6的栅极，第一晶体管M1和第六晶体管M6关闭，通过第六晶体管M6阻断驱动电流传输至有机发光元件D1，防止在第一时段T1，第一节点N1、第二节点N2和第三节点N3复位时出现有机发光元件D1发光的现象。

[0097] 继续参考图2、图8和图9，可选的，其中，在第一时段T1切换至第二时段T2时，先关闭第五晶体管M5和第七晶体管M7，再打开第二晶体管M2和第四晶体管M4。

[0098] 具体的，在第一时段T1，第一扫描信号端S1输入低电位信号至第五晶体管M5的栅极和第七晶体管M7的栅极使得第五晶体管M5和第七晶体管M7导通，实现第一节点N1、第二节点N2和第三节点N3进行复位，之后，在第一时段T1切换至第二时段T2时，先通过第一扫描信号端S1输入高电位信号至第五晶体管M5的栅极和第七晶体管M7的栅极，第五晶体管M5和第七晶体管M7关闭，再通过第二扫描信号端S2输入低电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极，第二晶体管M2和第四晶体管M4导通，有效防止在第一时段T1转换至第二时段T2时，第一节点N1同时接收到通过第五晶体管M5传输的参考电压Vref的复位信号和通过第四晶体管M4传输的第三节点N3的充电信号导致第一节点N1出现信号冲突的现象时段。

[0099] 需要说明的是，图9中实例性的示出了在第一时段T1，先关闭第五晶体管M5和第七晶体管M7，在第二时段T2，再打开第二晶体管M2和第四晶体管M4，在本发明其他实施例中还可以在第一时段T1，先关闭第五晶体管M5和第七晶体管M7，再打开第二晶体管M2和第四晶体管M4，或在第二时段T2，先关闭第五晶体管M5和第七晶体管M7，再打开第二晶体管M2和第四晶体管M4，本发明不再一一进行赘述。

[0100] 继续参考图2、图8和图9，可选的，其中，在第二时段T2切换至第三时段T3时，先关闭第二晶体管M2和第四晶体管M4，再打开第一晶体管M1和第六晶体管M6。

[0101] 具体的，在第二时段T2，第二扫描信号端S2输入低电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极，第二晶体管M2和第四晶体管M4导通，第一数据写入模块104将数据信号端Vdata的信号通过第二晶体管M2传输至第二节点N2，第二节点N2的信号通过第三晶体管M3传输至第三节点N3，第三节点N3的电位通过第四晶体管M4传输至第一节点N1，第一电容C1实现对第一节点N1的充电，之后，在第二时段T2切换至第三时段T3时，先通过第二扫描信号端S2输入高电位信号至第二晶体管M2的栅极和第四晶体管M4的栅极，第二晶体管M2和第四晶体管M4关闭，再通过发光控制信号端Emi<sub>t</sub>输入低电位信号至第一晶体管M1的栅极和第六晶体管M6的栅极，第一晶体管M1和第六晶体管M6导通，有效避免在在第二时段T2时切换至第三时段T3时，第二节点N2同时接收到通过第一晶体管M1传输的第一电源信号端

PVDD的信号和通过第二晶体管M2传输的数据信号端Vdata的信号导致第二节点N2出现信号冲突的现象。

[0102] 基于同一发明构思，本发明实施例提供一种显示装置，包括如上所述的像素驱动电路。

[0103] 请参考图10，图10是本发明提供的一种显示装置的平面结构示意图。图10提供的显示装置1000包括本发明上述任一实施例提供的像素驱动电路。图10实施例仅以手机为例，对显示装置1000进行说明，可以理解的是，本发明实施例提供的显示装置，可以是电脑、电视、车载显示装置等其他具有显示功能的显示装置，本发明对此不作具体限制。本发明实施例提供的显示装置，具有本发明实施例提供的显示面板的有益效果，具体可以参考上述各实施例对于像素驱动电路的具体说明，本实施例在此不再赘述。

[0104] 通过上述实施例可知，本发明提供的像素驱动电路及其驱动方法、显示装置，至少实现了如下的有益效果：

[0105] 本发明提供的像素驱动电路，在第一时段，通过第一扫描信号端输入信号控制第一初始化模块的导通，通过第一初始化模块将参考电压端的信号传输至第一节点，实现第一节点的复位；通过第一扫描信号端输入信号控制复位模块的导通，通过复位模块将第一电源信号端的信号传输至第三节点，通过第一节点的信号控制驱动模块的导通，通过驱动模块将第三节点的信号传输至第二节点，实现第二节点和第三节点的复位。在第二时段，通过第一扫描信号端输入信号控制第一初始化模块和复位模块的关闭，通过第二扫描信号端输入信号控制第一数据写入模块和第二数据写入模块的导通，通过第一数据写入模块将数据信号端的信号传输至第二节点，通过驱动模块将第二节点的信号传输至第三节点，通过第二数据写入模块将第三节点的电位传输至第一节点，通过第一存储模块实现对第一节点的充电、对驱动模块的阈值的抓取。在第三时段，通过第二扫描信号端输入信号控制第一数据写入模块和第二数据写入模块的关闭，通过发光控制信号端输入信号控制第一发光控制模块和第二发光控制模块的导通，通过第一发光控制模块将第一电源信号端的信号传输至第二节点，通过第一存储模块实现对驱动模块的阈值的补偿，驱动模块形成驱动电流，通过第二发光控制模块使得驱动电流传输至有机发光元件的阳极，有机发光元件根据驱动电流发光。本实施例提供的像素驱动电路在第一时段对与驱动模块的控制端相连接的第一节点、与驱动模块的第一端相连接的第二节点和与驱动模块的第二端电连接的第三节点进行复位，可使得第一节点、第二节点和第三节点的电压在每一帧的第一时段均被复位在一个固定值上，可降低上一帧施加于第一节点、第二节点和第三节点的电压对下一帧第一节点、第二节点和第三节点的电压的影响，提高第二时段中第一存储模块对驱动模块的阈值的抓取的准确性，第一存储模块在第三时段根据在第二时段抓取的驱动模块的阈值对驱动模块的阈值进行补偿，有效缓解了像素驱动电路中驱动模块存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。

[0106] 第一初始化模块的控制端和复位模块的控制端均与第一扫描信号端电连接，在第一时段，通过第一扫描信号端输入信号控制第一初始化模块的导通，通过第一初始化模块将参考电压端的信号传输至第一节点，实现第一节点的复位；同时通过第一扫描信号端输入信号控制复位模块的导通，通过复位模块将第一电源信号端的信号传输至第三节点，通过第一节点的信号控制驱动模块的导通，通过驱动模块将第三节点的信号传输至第二节

点,实现第二节点和第三节点的复位,使得通过第一扫描信号端可在第一时段同时实现第一节点、第二节点和第三节点的复位,无需另外设置信号线实现第二节点和第三节点的复位,也无需增加时间段实现第二节点和第三节点的复位,减少有机显示装置中的排线难度,同时减小有机显示装置中芯片的负载能力;复位模块的第一端与第一电源信号端电连接,可通过第一电源信号端的电位实现第二节点和第三节点的复位,无需另外设置信号线给第二节点和第三节点提供信号,进一步减少有机显示装置中的排线难度。

[0107] 虽然已经通过例子对本发明的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上例子仅是为了进行说明,而不是为了限制本发明的范围。本领域的技术人员应该理解,可在不脱离本发明的范围和精神的情况下,对以上实施例进行修改。本发明的范围由所附权利要求来限定。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素驱动电路及其驱动方法、显示装置                              |         |            |

| 公开(公告)号        | <a href="#">CN110675815A</a>                   | 公开(公告)日 | 2020-01-10 |

| 申请号            | CN201910918161.1                               | 申请日     | 2019-09-26 |

| [标]申请(专利权)人(译) | 武汉天马微电子有限公司                                    |         |            |

| 申请(专利权)人(译)    | 武汉天马微电子有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 武汉天马微电子有限公司                                    |         |            |

| [标]发明人         | 郭亮亮<br>周井雄                                     |         |            |

| 发明人            | 郭亮亮<br>周井雄<br>厉天锐                              |         |            |

| IPC分类号         | G09G3/3208                                     |         |            |

| CPC分类号         | G09G3/3208                                     |         |            |

| 代理人(译)         | 于淼                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种像素驱动电路及其驱动方法、显示装置，属于显示技术领域，像素驱动电路包括：第一发光控制模块、第二发光控制模块、驱动模块、第一数据写入模块、第二数据写入模块、第一初始化模块、复位模块、第一存储模块、有机发光元件、第一电源信号端、第二电源信号端、数据信号端、第一扫描信号端、第二扫描信号端、参考电压端、发光控制信号端、第一节点、第二节点和第三节点。本发明有效缓解了像素驱动电路中驱动模块存在阈值电压所造成的有机显示装置在显示时存在迟滞现象和残影现象。